**TOSHIBA** TC9242P/F

TOSHIBA BIPOLAR DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TC9242P, TC9242F

# QUARTZ PLL MOTOR CONTROL

The TC9242P, TC9242F are CMOS LSIs developed for controlling the motor speed.

Since an 8bit D/A converter system has been employed for each of the speed control system (AFC) and the phase control system (APC).

Offers improved linearity.

With frequency division ratios of 1/3, 1/4 and 1/5 the standard divider is ideal for laser scanner motors.

#### **FEATURES**

- Crystal can be used up to 20MHz, and crystal reference dividing frequency is selectable from three positions of 1/3, 1/4 and 1/5.

- Lock range can be selected from two positions of 1/20 and 1/27.

- External oscillator makes possible fine adjustment of

- Lock detection output and reverse rotation signal output are provided.

- Package is DIP16PIN and SOP16PIN.

Weight

DIP16-P-300-2.54A : 1.00g (Typ.) SOP16-P-300-1.27 : 0.16g (Typ.)

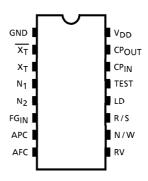

### PIN CONNECTIONS (TOP VIEW)

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to foreign exchange and foreign trade control laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

TOSHIBA TC9242P/F

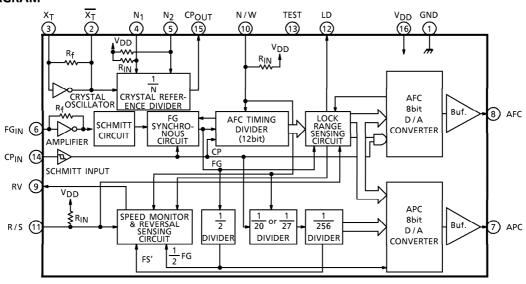

# **BLOCK DIAGRAM**

### **FUNCTIONAL EXPLANATION OF EACH TERMINAL**

| PIN No. | SYMBOL         | PIN NAME                               | FUNCTIONAL & OPERATION EXPLANATION                                                                    | REMARKS                           |

|---------|----------------|----------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------|

| 16      | ∀DD            | Power Terminal                         | $V_{DD} = 5V \pm 0.5V$ is applied.                                                                    | _                                 |

| 1       | GND            | Ground Terminal                        | Ground                                                                                                | _                                 |

| 2       | XT             | Crystal Oscillation                    | Crystal oscillator is connected.                                                                      | With a built-in feedback          |

| 3       | XT             | Terminal                               | crystal oscillator is connected.                                                                      | resistor.                         |

| 4       | N <sub>1</sub> | Reference Divided Frequency Switching  | Switching of divided frequency from the crystal reference                                             | With a built-in                   |

| 5       | N <sub>2</sub> | Terminal                               | frequency divider into 1/3, 1/4 and 1/5 is possible.                                                  | pull-up resistor.                 |

| 6       | FGIN           | FG Pulse Input Terminal                | Input terminal for pulse showing motor speed.                                                         | With a built-in amplifier.        |

| 7       | APC            | APC Output Terminal                    | Output terminal for motor phase control system. Output of 8bit D/A converter.                         | With a built-in buffer.           |

| 8       | AFC            | AFC Output Terminal                    | Output terminal for motor speed control system. Output of 8bit D/A converter.                         | With a built-in buffer.           |

| 9       | RV             | Reverse Signal Output<br>Terminal      | Terminal for motor reverse signal output.                                                             | CMOS OUTPUT                       |

| 10      | N/W            | Lock range Switching<br>Terminal       | Terminal for switching motor speed. L = 1/27, H or NC = 1/20.                                         | With a built-in pull-up resistor. |

| 11      | R/S            | RUN/STOP Input<br>Terminal             | Motor RUN/STOP signal input terminal L=RUN, H or NC=STOP                                              | With a built-in pull-up resistor. |

| 12      | LD             | Lock Detecting Terminal                | This terminal becomes "H" when the motor speed is within the lock range and otherwise "L".            | CMOS OUTPUT                       |

| 14      | CPIN           | Reference Frequency<br>Input Terminal  | Normally connected to CPOUT. For external fine adjustment input from an external oscillator.          | CMOS SCHMITT                      |

| 15      | CPOUT          | Reference Frequency<br>Output Terminal | Terminal for divided output from the crystal reference frequency divider. Normally connected to CPIN. | CMOS OUTPUT                       |

| 13      | TEST           | Output Terminal for INTERNAL TEST      | Output terminal for INTERNAL TEST. Generally open.                                                    |                                   |

TOSHIBA TC9242P/F

#### **EXPLANATION OF OPERATION**

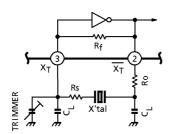

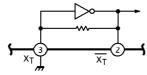

- 1. Crystal Oscillation Terminals  $(X_T, \overline{X_T})$

- The crystal oscillator is used by connecting as shown below.

※ CL of 10~30pF is appropriate.

• Crystal oscillation frequency is calculated by the following equation according to number of FG pulses of a motor to be used.

$$f_X = \frac{R}{60} \times FG' \times 128 \times (20 \text{ or } 27) \times N \text{ (Hz)}$$

Note : (20 or 27) : 20 at N/W = "H" or NC 27 at N/W = "L"

Further, fX: Crystal oscillation frequency, FG': No. of FG pulses generated per revolution of motor.

N: Ratio of frequency division of the crystal reference frequency divider. N = 3, 4, 5 (Refer to Item 9.)

- Maximum operating frequency is above 20MHz and crystals up to 20MHz can be used.

- If necessary, adjust Ro, Rs and CL to control noise from the crystal oscillator circuit or to control overtone oscillation.

#### <Reference values>

| f <sub>XT</sub> (MHz) | Ro ( $\Omega$ ) | Rs ( $\Omega$ ) | C <sub>L</sub> (pF) | No |

|-----------------------|-----------------|-----------------|---------------------|----|

| 20                    | _               | 220             | 22                  |    |

| 12                    | _               | 220             | 27                  |    |

| 8                     | _               | 220             | 30                  | No |

| 4.5                   | 2.2k            | _               | 30                  |    |

| 1.5                   | 4.7k            | _               | 30                  |    |

Note: The values in the table are the reference values. Determine the

values suitable for the

characteristics of the crystal used.

Note: When not using the crystal

oscillator circuit, always connect pin 3 (XT) to GND as shown in the diagram to overcome the effects of noise and to reduce

current consumption.

<When not using the crystal oscillator circuit>

- 2. Reference Frequency Input/Output Terminals (CPOUT, CPIN)

- Divided output  $\frac{f_X}{N}$  from the crystal reference frequency divider is available at CP<sub>OUT</sub>, which is normally connected to CP<sub>IN</sub>.

- When an external oscillator (CR oscillator, etc.) is connected to CPIN, motor speed can be finally adjusted.

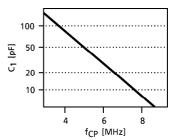

- If the effects of noise from CPIN input signal overshoot must be controlled, connect capacitor C1 as in the following diagram.

Note: When connecting capacitor C1, make sure that the input level of pin 14 (CPIN) does not fall blow the standard  $(V_{IH} \ge 0.8 \times V_{DD}, V_{L} \le 0.2 \times V_{DD})$

<Reference value>

- 3. FG Pulse Input Terminal (FGIN)

- This is the input terminal of FG pulse that shows the motor speed. This FG pulse becomes comparison frequency.

Note :

- This terminal has built-in Amplifier and Schmitt circuit. FG pulses are applied through capacitor coupling and small amplitude is enough for proper operation.

- If there is noise in the FG signal, connect capacitor C2 as shown in the diagram to control the noise.

Note : Determine the values of capacitors C1 and C2 after

checking their characteristics with fcp and ffG used.

When connecting capacitor C2, make sure that the

input level of pin 6 (FGIN) does not fall below the

standard  $(V_{in}FG \ge 0.5V_{p-p})$

4. Lock Range Switching Terminal (N/W)

This terminal is for switching the Lock range with a pull-up resistor and chattering preventive circuit.

#### (TRUTH TABLE)

| N/W     | DIVIDED<br>FREQUENCY | LOCK RANGE                      |

|---------|----------------------|---------------------------------|

| L       | <u>1</u><br>27       | +3.4~ -3.9% of reference cycle  |

| H or NC | 1 20                 | +4.6~ – 5.3% of reference cycle |

CAUTION reference frequency  $FS = f_X / N \times (20 \text{ or } 27) \times 128 \text{ (Hz)}, FS' = \frac{FS}{2}$

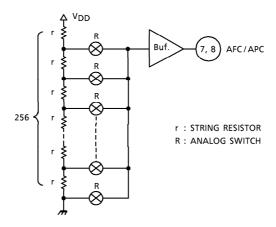

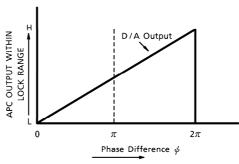

- 5. APC, AFC Output Terminal (APC, AFC)

- AFC (speed control output) is a F-V converter for FG frequency and is consisting of a 8bit D/A converter.

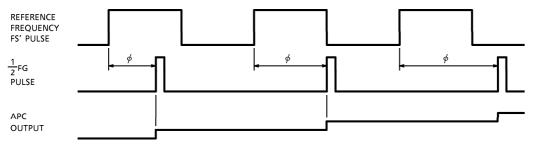

- APC (phase control output) is a phase comparator ( $\phi$ -V converter) that compares phase difference  $\phi$  between 1/2 FG and reference frequency FS', and is also consisting of a 8bit D/A converter.

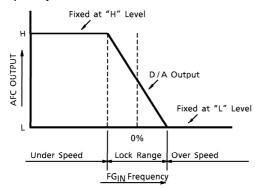

- Both APC and AFC perform the following 3 operations according to FGIN frequency.

- a. When FG<sub>IN</sub> frequency is within the lock range:

Both APC and AFC perform the normal operation for FG<sub>IN</sub>.

- b. When FG<sub>IN</sub> frequency is below the lock range (under speed): APC and AFC outputs are both fixed at "H" level.

- c. When FG<sub>IN</sub> frequency is above the lock range (over speed): APC and AFC outputs are both fixed at "L" level.

- When a motor is in STOP state (P/S = H or NC), both AFC and APC are fixed "L" level.

AFC output change status for  $FG_{IN}$  frequency

APC output change status for phase difference  $\phi$

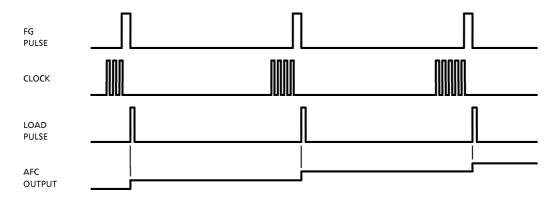

- AFC and APC timing chart within lock range.

- a. AFC (SPEED CONTROL SYSTEM)

# b. APC (PHASE CONTROL SYSTEM)

AFC OUTPUT with in Lock Range

# 6. Lock Detecting Terminal (LD)

• This terminal is the lock detecting output and is placed at "H" level when FG<sub>IN</sub> frequency is within the lock range and otherwise, placed at "L" level.

# 7. RUN/STOP Input Terminal (R/S)

- RUN/STOP signals of the motor are input to this terminal.

PLAY = L, STOP = H or NC.

- This terminal has a pull-up resistor and a chattering preventive circuit.

- During RUN (R/S=L), AFC, APC and LD perform the above-mentioned operations for FG<sub>IN</sub> frequency, and during STOP (R/S=H or NC), AFC, APC and LD are all fixed at "L" level.

- 8. Reverse Signal Output Terminal (RV)

- Reverse signal for braking the motor at time of switching of Lock range from 1/20 to 1/27 or the operation from RUN to STOP is output through this terminal.

- Change of RV output status

| PREVIOUS C                         | RV OUTPUT CHANGE<br>TO "H" LEVEL | ſ | RV OUTPUT CHANGE 7 TO "L" LEVEL           |  |  |  |

|------------------------------------|----------------------------------|---|-------------------------------------------|--|--|--|

| During Normal                      |                                  |   | When the Lock range is locked at          |  |  |  |

| Rotation                           | When the Lock range is switched  | k | 1/27, or When FG <sub>IN</sub> ≦1/8FS, or |  |  |  |

| (During Lock) at                   | from 1/20 to 1/27.               |   | when the Lock range is switched           |  |  |  |

| 1/20                               |                                  |   | from 1/27 to 1/20.                        |  |  |  |

| During Normal                      |                                  |   | When FG <sub>IN</sub> ≤ 1/8FS or when the |  |  |  |

| Rotation                           | When the operation is switched   |   | operation is switched from STOP to        |  |  |  |

| (During Lock) at from RUN to STOP. |                                  |   | ·                                         |  |  |  |

| 1/20 or 1/27                       |                                  |   | RUN.                                      |  |  |  |

- In other cases than above, RV output is not changed and fixed at "L" level.

- Further, if FG frequency rises up to 1.5 times of normal rotation at 1/20 (2 times of normal rotation at 1/27), RV output is reset.

- 9. Reference Divided Frequency Switching Terminal (N<sub>1</sub>, N<sub>2</sub>)

- Divided frequency 1/N of the crystal reference frequency divider can be switched to 1/5, 1/4 or 1/3 by number of FG pulses or a crystal used.

- This terminal has a built-in pull-up resistor.

# (TRUTH TABLE)

| N1 | N2 | 1 / N |

|----|----|-------|

| Н  | Н  | 1/5   |

| L  | Н  | 1/4   |

| Н  | L  | 1/3   |

1/N: Crystal reference divided frequency

Note: Do not use N1 = N2 = L, which is used for internal test only.

# **MAXIMUM RATINGS** (Ta = 25°C)

| CHARACTERISTIC        | SYMBOL           | RATING                    | UNIT |

|-----------------------|------------------|---------------------------|------|

| Supply Voltage        | $V_{DD}$         | -0.3~7.0                  | V    |

| Input Voltage         | VIN              | -0.3~V <sub>DD</sub> +0.3 | V    |

| Power Dissipation     | PD               | 300                       | mW   |

| Operating Temperature | T <sub>opr</sub> | <b>- 40∼85</b>            | °C   |

| Storage Temperature   | T <sub>stg</sub> | <b>- 65∼150</b>           | °C   |

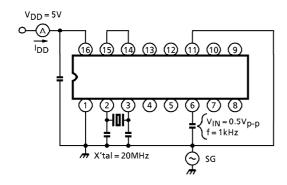

# **ELECTRICAL CHARACTERISTICS** (Unless otherwise specified Ta = 25°C, V<sub>DD</sub> = 5V)

| CHARACTERISTIC                |                  | SYMBOL             | TEST<br>CIR-<br>CUIT | TEST CONDITIONS                                        | MIN.                | TYP.                  | MAX.                  | UNIT               |  |

|-------------------------------|------------------|--------------------|----------------------|--------------------------------------------------------|---------------------|-----------------------|-----------------------|--------------------|--|

| Operating Supply Voltage      |                  | $V_{DD}$           | _                    | *                                                      | 4.5                 | 5.0                   | 5.5                   | V                  |  |

| Operating Supply Current      |                  | lDD                | 1                    | X'tal = 20MHz,<br>CP <sub>in</sub> = CP <sub>out</sub> | _                   | 15.0                  | 25.0                  | mA                 |  |

| Operating                     | XT               | fXT                | 2                    | *                                                      | 1.5                 | ~                     | 20.0                  | MHz                |  |

| Frequency                     | CPin             | fCP                | 3                    | V <sub>in</sub> Square Wave **                         | 0.3                 | ~                     | 10.0                  | MHz                |  |

| Range                         | FG <sub>in</sub> | fFG                | _                    | $V_{in} = 0.5V_{p-p}$ Sine Wave $\%$                   | _                   | ~                     | 4.0                   | kHz                |  |

| Input<br>Amplitude<br>Voltage | FG <sub>in</sub> | V <sub>in</sub> FG | 4                    | f <sub>FG</sub> = 4kHz, Sine Wave, ※<br>AC input       | 0.5                 | ?                     | V <sub>DD</sub> – 0.5 | V <sub>p-p</sub>   |  |

| AFC, APC D/A                  | Deviation        | _                  | _                    |                                                        |                     | ± 2.0                 | ± 4.0                 | LSB                |  |

| Converter                     | Resolution       | _                  | _                    |                                                        | 1                   | V <sub>DD</sub> / 256 | _                     | >                  |  |

| Pull-up Resistor              | Pull-up Resistor |                    | _                    | N1, N2, N/W, R/S                                       | 15                  | 30                    | 60                    | $\mathbf{k}\Omega$ |  |

| Input Voltage                 | "H" Level        | $V_{IH}$           |                      | N1, N2, N/W, R/S, CP <sub>in</sub>                     | $V_{DD} \times 0.8$ | ?                     | $V_{DD}$              | >                  |  |

| iliput voitage                | "L" Level        | $V_{IL}$           |                      | N1, N2, N/W, R/S, CP <sub>in</sub>                     | 0                   | ?                     | $V_{DD} \times 0.2$   |                    |  |

| Input Leak Current            |                  | l <sub>IH</sub>    | _                    | CP <sub>in</sub>                                       |                     | 1                     | ± 1.0                 | $\mu$ <b>A</b>     |  |

|                               | "H" Level        | ЮН                 |                      | RV, LD, $CP_{out} V_{OH} = 4.5V$                       | - 0.5               | <b>-</b> 2.5          | _                     |                    |  |

| Output Current                | "L" Level        | lOL                |                      | RV, LD, $CP_{out} V_{OL} = 0.5V$                       | 0.5                 | 2.5                   | _                     | mA                 |  |

| Output Current                |                  | ІОН                |                      | APC, AFC $V_{OH} = 4.5V$                               | - 0.3               | <b>–</b> 1.0          |                       |                    |  |

|                               | "L" Level        | lOL                |                      | APC, AFC $V_{OL} = 0.5V$                               | 25                  | 75                    |                       | μΑ                 |  |

| Amplifier<br>Feedback         | ХT               | Rf                 | 5                    | _                                                      | 150                 | 330                   | 660                   | kΩ                 |  |

| Resistor                      | FG <sub>in</sub> | R <sub>f</sub>     | 5                    | _                                                      | 150                 | 330                   | 660                   | $\mathbf{k}\Omega$ |  |

%: Guaranteed within the range of  $V_{DD} = 4.5 \sim 5.5 V$ ,  $T_{a} = -40 \sim 85 ^{\circ} C$

TOSHIBA TC9242P/F

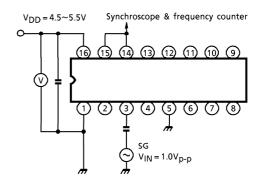

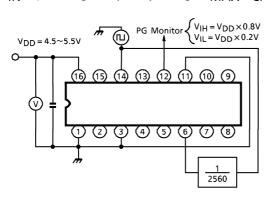

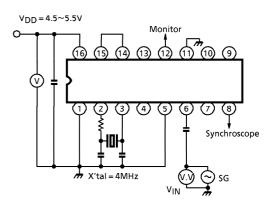

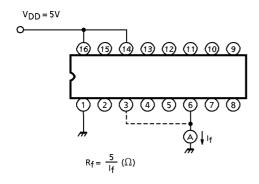

### **TEST CIRCUIT**

1. Operating Supply Current IDD

2.  $X_T$  Operating Frequency Range  $f_{MAX}(f_{XT})$

3. CP<sub>IN</sub> Operating Frequency Range f<sub>MAX</sub> (f<sub>CP</sub>)

4. FGIN Input Sensitivity VINFG

5. Amplifier Feedback Resistor Rf

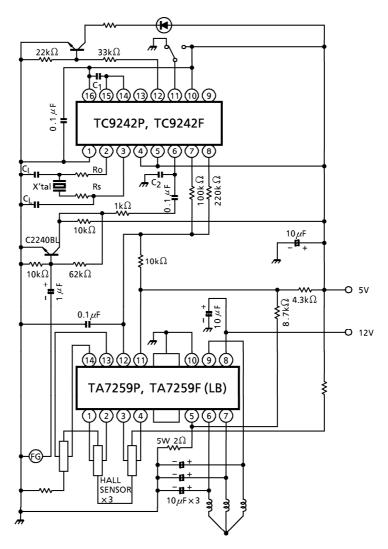

### **APPLICATION CIRCUIT**

Example of crystal oscillation frequency calculation.

When FG' (number of FG pulse) = 180 pulses and R (revolution of motor) = 200 rpm., if the dividing frequency of reference divider and lock range is set at N = 5 dividing frequency and N/W = 20, the crystal oscillation frequency  $f_X$  is as follows:

$$f_X = \frac{R}{60} \times FG' \times 128 \times 20 \times N = \frac{200}{60} \times 180 \times 128 \times 20 \times 5 = 7.68MHz$$

- Select the external filter of the differential amplifier in the application circuit depending on the response characteristics of the motor used.

- Determine values C1, C2, CL, Ro and Rs in the application circuit depending on the characteristics of the circuit.

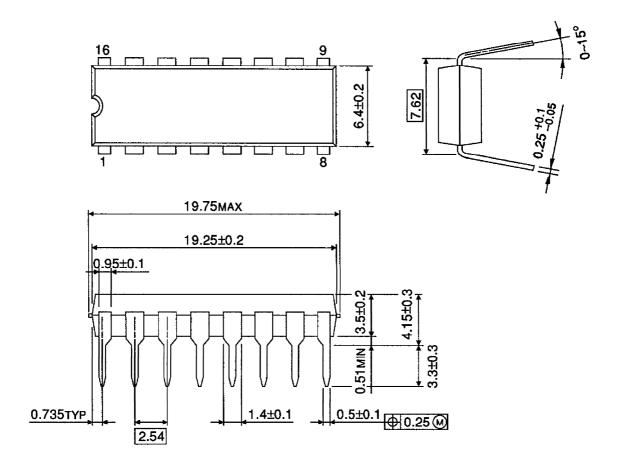

# OUTLINE DRAWING DIP16-P-300-2.54A

Unit: mm

Weight: 1.00g (Typ.)

#

Weight: 0.16g (Typ.)