# **Last-Time Buy**

This part is in production but have been determined to be LAST TIME BUY. This classification indicates that the product is obsolete and notice has been given. Sale of this device is currently restricted to existing customer applications. The device should not be purchased for new design applications because of obsolescence in the near future. Samples are no longer available.

Date of status change: December 14, 2017

Deadline for receipt of LAST TIME BUY orders: December 1, 2018

**Recommended Substitutions: Generation 4 and 5 devices**

For existing customer transition, and for new customers or new applications, contact Allegro Sales.

NOTE: For detailed information on purchasing options, contact your local Allegro field applications engineer or sales representative.

Allegro MicroSystems, LLC reserves the right to make, from time to time, revisions to the anticipated product life cycle plan for a product to accommodate changes in production capabilities, alternative product availabilities, or market demand. The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

#### **Features and Benefits**

- 2-wire serial I<sup>2</sup>C<sup>TM</sup> -compatible interface: control (write) and status (read)

- LNB voltages (8 programmable levels) compatible with all common standards including domestic Japan models

- Tracking switch-mode power converter for lowest dissipation

- Integrated converter switches and current sensing

- Provides up to 700 mA load current

- Static current limit circuit allows full current at startup and 13—18 V output transition; reliably starts wide load range

- Push-pull output stage minimizes 13→18V and 18→13V output transition times for highly capacitive loads

- Adjustable rise/fall time via external timing capacitor

- Built-in tone oscillator, factory-trimmed to 22 kHz facilitates DiSEqC<sup>TM</sup> tone encoding, even at no-load

- Four methods of 22 kHz tone generation, via I<sup>2</sup>C<sup>TM</sup> data bits and/or external pin

- Auxiliary modulation input

- LNB overcurrent with timer

- Diagnostics for output voltage level, input supply UVLO

Packages:

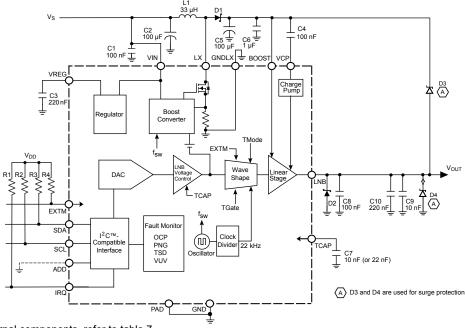

20-contact, 4 × 4 mm MLP/QFN (suffix ES)

#### Description

Intended for analog and digital satellite receivers, this single low noise block converter regulator (LNBR) is a monolithic linear and switching voltage regulator, specifically designed to provide the power and the interface signals to an LNB down converter via coaxial cable. The A8293 requires few external components, with the boost switch and compensation circuitry integrated inside of the device. A high switching frequency is chosen to minimize the size of the passive filtering components, further assisting in cost reduction. The high levels of component integration ensure extremely low noise and ripple figures.

The A8293 has been designed for high efficiency, utilizing the Allegro<sup>™</sup> advanced BCD process. The integrated boost switch has been optimized to minimize both switching and static losses. To further enhance efficiency, the voltage drop across the tracking regulator has been minimized.

For DiSEqC<sup>TM</sup> communications, several schemes are available for generating tone signals, all the way down to no-load, and using either the internal clock or an external time source.

Continued on the next page...

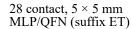

### **Functional Block Diagram**

For recommended external components, refer to table 7

## Single LNB Supply and Control Voltage Regulator

#### **Description (continued)**

A comprehensive set of fault registers are provided, which comply with all the common standards, including: overcurrent, thermal shutdown, undervoltage, and power not good.

The device uses a 2-wire bidirectional serial interface, compatible with the  $I^2C^{TM}$  standard, that operates up to 400 kHz.

The A8293 is supplied in two lead (Pb) free MLP/QFN packages: ES, 20-contact, 4 mm  $\times$  4 mm, 0.75 nominal overall height, and ET, 28-contact, 5 mm  $\times$  5 mm, 0.90 nominal overall height.

#### **Selection Guide**

| Part Number               | Packing <sup>1</sup>                               | Description                                                            |  |

|---------------------------|----------------------------------------------------|------------------------------------------------------------------------|--|

| A8293SESTR-T <sup>2</sup> | 7 in. reel, 1500 pieces/reel<br>12 mm carrier tape | ES package, MLP/QFN surface mount 4 mm × 4 mm × 0.75 mm nominal height |  |

| A8293SETTR-T <sup>2</sup> | 7 in. reel, 1500 pieces/reel<br>12 mm carrier tape | ET package, MLP/QFN surface mount 5 mm × 5 mm × 0.90 mm nominal height |  |

#### **Absolute Maximum Ratings**

| Characteristic                  | Symbol               | Conditions         | Rating                | Units |

|---------------------------------|----------------------|--------------------|-----------------------|-------|

| Load Supply Voltage, VIN pin    | V <sub>IN</sub>      |                    | 30                    | V     |

| Output Current <sup>1</sup>     | I <sub>OUT</sub>     |                    | Internally<br>Limited | А     |

| Output Voltage, BOOST pin       |                      |                    | -0.3 to 33            | V     |

| Output Voltage, LNB pin         |                      | Surge <sup>2</sup> | -1 to 33              | V     |

| Output Voltage, LX pin          |                      |                    | -0.3 to 30            | V     |

| Output Voltage, VCP pin         | V <sub>CP</sub>      |                    | -0.3 to 41            | V     |

| Logic Input Voltage, EXTM pin   |                      |                    | -0.3 to 5             | V     |

| Logic Input Voltage, other pins |                      |                    | -0.3 to 7             | V     |

| Logic Output Voltage            |                      |                    | -0.3 to 7             | V     |

| Operating Ambient Temperature   | T <sub>A</sub>       |                    | –20 to 85             | °C    |

| Junction Temperature            | T <sub>J</sub> (max) |                    | 150                   | °C    |

| Storage Temperature             | T <sub>stg</sub>     |                    | -55 to 150            | °C    |

$<sup>^1</sup>$ Output current rating may be limited by duty cycle, ambient temperature, and heat sinking. Under any set of conditions, do not exceed the specified current ratings, or a junction temperature,  $T_J$ , of 150°C.

#### Package Thermal Characteristics\*

| Package | R <sub>θJA</sub><br>(°C/W) | PCB     |

|---------|----------------------------|---------|

| ES      | 37 (estimated)             | 4-layer |

| ET      | 32                         | 4-layer |

<sup>\*</sup> Additional information is available on the Allegro website.

<sup>&</sup>lt;sup>1</sup> Contact Allegro for additional packing options.

<sup>&</sup>lt;sup>2</sup> Leadframe plating 100% matte tin.

<sup>&</sup>lt;sup>2</sup>Use Allegro recommended Application circuit.

#### **Device Pin-out Diagram**

#### **Terminal List Table**

| Name  | Nun       | nber                                   | Function                                                               |  |

|-------|-----------|----------------------------------------|------------------------------------------------------------------------|--|

| Name  | ES ET     |                                        | runcuon                                                                |  |

| ADD   | 10        | 11                                     | Address select                                                         |  |

| FLOAT | 4, 15     | 5, 22                                  | These pins must not be connected to anything; do not ground these pins |  |

| BOOST | 1         | 1                                      | Tracking supply voltage to linear regulator                            |  |

| EXTM  | 5         | 6                                      | External modulation input                                              |  |

| GND   | 7, 14     | 8, 19                                  | Signal ground                                                          |  |

| GNDLX | 19        | 27                                     | Boost switch ground                                                    |  |

| IRQ   | 11        | 14                                     | Interrupt request                                                      |  |

| LNB   | 20        | 28                                     | Output voltage to LNB                                                  |  |

| LX    | 18        | 26                                     | Inductor drive point                                                   |  |

| NC    | 6, 13, 16 | 4, 7, 13, 15-<br>18, 20, 21,<br>23, 24 | No connection                                                          |  |

| PAD   | Pad       | Pad                                    | Exposed pad; connect to the ground plane, for thermal dissipation      |  |

| SCL   | 12        | 12                                     | I <sup>2</sup> C™-compatible clock input                               |  |

| SDA   | 9         | 10                                     | I <sup>2</sup> C™-compatible data input/output                         |  |

| TCAP  | 3         | 3                                      | Capacitor for setting the rise and fall time of the LNB output         |  |

| VCP   | 2         | 2                                      | Gate supply voltage                                                    |  |

| VIN   | 17        | 25                                     | Supply input voltage                                                   |  |

| VREG  | 8         | 9                                      | Analog supply                                                          |  |

# Single LNB Supply and Control Voltage Regulator

### **ELECTRICAL CHARACTERISTICS** at $T_A = 25$ °C, $V_{IN} = 9$ to 16 V, unless noted otherwise<sup>1</sup>

| Characteristics                              | Symbol                   | Test Conditions                                                                                                                                 | Min.  | Тур. | Max. | Units            |

|----------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|------------------|

| General                                      |                          |                                                                                                                                                 |       |      |      |                  |

| Set-Point Accuracy, Load and Line Regulation | Err                      | Relative to selected $V_{LNB}$ target level, $I_{LOAD} = 0$ to 450 mA                                                                           | -3.0  | -    | +3.0 | %                |

|                                              | I <sub>IN(Off)</sub>     | ENB bit = 0, LNB output disabled, V <sub>IN</sub> = 12 V                                                                                        | _     | _    | 10.0 | mA               |

| Supply Current                               | I <sub>IN(On)</sub>      | ENB bit = 1, LNB output enabled,<br>I <sub>LOAD</sub> = 0 mA, V <sub>IN</sub> = 12 V                                                            | ı     | _    | 19.0 | mA               |

| Boost Switch On Resistance                   | R <sub>DS(on)BOOST</sub> | I <sub>LOAD</sub> = 450 mA                                                                                                                      | -     | 300  | _    | mΩ               |

| Switching Frequency                          | f <sub>SW</sub>          |                                                                                                                                                 | 320   | 352  | 384  | kHz              |

| Switch Current Limit                         | I <sub>LIMSW</sub>       | V <sub>IN</sub> = 9 V, V <sub>OUT</sub> = 19.0 V                                                                                                | -     | 2.7  | _    | Α                |

| Linear Regulator Voltage Drop                | $\Delta V_{REG}$         | $V_{BOOST} - V_{LNB}$ , no tone signal,<br>$I_{LOAD} = 450 \text{ mA}$                                                                          | ı     | 800  | _    | mV               |

| TCAP Pin Current                             | I <sub>CHG</sub>         | TCAP capacitor (C7) charging                                                                                                                    | -12.5 | -10  | -7.5 | μΑ               |

| TOAL THI Guilent                             | I <sub>DISCHG</sub>      | TCAP capacitor (C7) discharging                                                                                                                 | 7.5   | 10   | 12.5 | μΑ               |

| Output Voltage Rise Time <sup>2</sup>        | t <sub>r(VLNB)</sub>     | For $V_{LNB}$ 13 $\rightarrow$ 18 V; $C_{TCAP}$ = 5.6 nF, $I_{LOAD}$ = 450 mA                                                                   | I     | 500  | _    | μs               |

| Output Voltage Pull-Down Time <sup>2</sup>   | t <sub>f(VLNB)</sub>     | For $V_{LNB}$ 18 $\rightarrow$ 13 V; $C_{LOAD}$ = 100 $\mu$ F, $I_{LOAD}$ = 0 mA                                                                | _     | 12.5 | _    | ms               |

| Output Reverse Current                       | I <sub>RLNB</sub>        | ENB bit = 0, V <sub>LNB</sub> = 33 V , BOOST capacitor (C5) fully charged                                                                       | -     | 1    | 5    | mA               |

| Ripple and Noise on LNB Output <sup>3</sup>  | $V_{rip,n(pp)}$          | 20 MHz BWL; reference circuit shown in Functional Block diagram; contact Allegro for additional information on application circuit board design | -     | 30   | _    | mV <sub>PP</sub> |

| Protection Circuitry                         | •                        |                                                                                                                                                 |       |      |      |                  |

| Output Overcurrent Limit <sup>4</sup>        | I <sub>LIMLNB</sub>      | V <sub>BOOST</sub> – V <sub>LNB</sub> = 800 mV                                                                                                  | _     | 700  | 800  | mA               |

| Overcurrent Disable Time                     | t <sub>DIS</sub>         |                                                                                                                                                 | _     | 48   | _    | ms               |

| VIN Undervoltage Lockout Threshold           | V <sub>UVLO</sub>        | V <sub>IN</sub> falling                                                                                                                         | 7.05  | 7.35 | 7.65 | V                |

| VIN Turn On Threshold                        | V <sub>IN(th)</sub>      | V <sub>IN</sub> rising                                                                                                                          | 7.40  | 7.70 | 8.00 | V                |

| Undervoltage Hysteresis                      | V <sub>UVLOHYS</sub>     |                                                                                                                                                 | _     | 350  | _    | mV               |

| Thermal Shutdown Threshold <sup>2</sup>      | T <sub>J</sub>           |                                                                                                                                                 | _     | 165  | _    | °C               |

| Thermal Shutdown Hysteresis <sup>2</sup>     | $\Delta T_J$             |                                                                                                                                                 | _     | 20   | _    | °C               |

| Power Not Good Flag Set                      | PNG <sub>SET</sub>       | With respect to V <sub>LNB</sub>                                                                                                                | 77    | 85   | 93   | %                |

| Power Not Good Flag Reset                    | PNG <sub>RESET</sub>     | With respect to V <sub>LNB</sub>                                                                                                                | 82    | 90   | 98   | %                |

| Power Not Good Hysteresis                    | PNG <sub>HYS</sub>       | With respect to V <sub>LNB</sub>                                                                                                                | _     | 5    | _    | %                |

| Tone                                         |                          |                                                                                                                                                 |       |      |      |                  |

| Tone Frequency                               | f <sub>TONE</sub>        |                                                                                                                                                 | 20    | 22   | 24   | kHz              |

| Tone Amplitude, Peak-to-Peak                 | V <sub>TONE(pp)</sub>    | I <sub>LOAD</sub> = 0 to 450 mA, C <sub>LOAD</sub> = 750 nF                                                                                     | 400   | 620  | 800  | mV               |

Continued on the next page...

#### ELECTRICAL CHARACTERISTICS (continued) at T<sub>A</sub> = 25°C, V<sub>IN</sub> = 9 to 16 V, unless noted otherwise<sup>1</sup>

| Characteristics                                | Symbol                 | Test Conditions                                                                                                                                                                        | Min. | Тур.  | Max. | Units |

|------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|

| Tone Duty Cycle                                | DC <sub>TONE</sub>     | I <sub>LOAD</sub> = 0 to 450 mA, C <sub>LOAD</sub> = 750 nF                                                                                                                            | 40   | 50    | 60   | %     |

| Tone Rise Time                                 | t <sub>rTONE</sub>     | I <sub>LOAD</sub> = 0 to 450 mA, C <sub>LOAD</sub> = 750 nF                                                                                                                            | 5    | 10    | 15   | μs    |

| Tone Fall Time                                 | t <sub>fTONE</sub>     | I <sub>LOAD</sub> = 0 to 450 mA, C <sub>LOAD</sub> = 750 nF                                                                                                                            | 5    | 10    | 15   | μs    |

| EXTM Logic langet                              | V <sub>EXTM(H)</sub>   |                                                                                                                                                                                        | 2.0  | _     | _    | V     |

| EXTM Logic Input                               | $V_{EXTM(L)}$          |                                                                                                                                                                                        | _    | _     | 0.8  | V     |

| EXTM Input Leakage                             | I <sub>EXTMLKG</sub>   |                                                                                                                                                                                        | -1   | _     | 1    | μA    |

| I <sup>2</sup> C™-Compatible Interface         |                        |                                                                                                                                                                                        |      |       |      |       |

| Logic Input (SDA,SCL) Low Level                | V <sub>SCL(L)</sub>    |                                                                                                                                                                                        | _    | _     | 0.8  | V     |

| Logic Input (SDA,SCL) High Level               | V <sub>SCL(H)</sub>    |                                                                                                                                                                                        | 2.0  | -     | -    | V     |

| Logic Input Hysteresis                         | V <sub>I2CIHYS</sub>   |                                                                                                                                                                                        | _    | 150   | -    | mV    |

| Logic Input Current                            | I <sub>I2CI</sub>      | V <sub>I2CI</sub> = 0 to 7 V                                                                                                                                                           | -10  | <±1.0 | 10   | μA    |

| Logic Output Voltage SDA and IRQ               | V <sub>t2COut(L)</sub> | I <sub>LOAD</sub> = 3 mA                                                                                                                                                               | _    | _     | 0.4  | V     |

| Logic Output Leakage SDA and IRQ               | V <sub>t2CLKG</sub>    | V <sub>t2COut</sub> = 0 to 7 V                                                                                                                                                         | _    | _     | 10   | μA    |

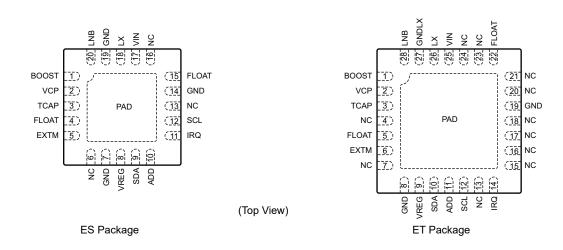

| SCL Clock Frequency                            | f <sub>CLK</sub>       |                                                                                                                                                                                        | _    | _     | 400  | kHz   |

| Output Fall Time                               | t <sub>fl2COut</sub>   | V <sub>t2COut(H)</sub> to V <sub>t2COut(L)</sub>                                                                                                                                       | _    | _     | 250  | ns    |

| Bus Free Time Between Stop/Start               | t <sub>BUF</sub>       |                                                                                                                                                                                        | 1.3  | -     | _    | μs    |

| Hold Time Start Condition                      | t <sub>HD:STA</sub>    |                                                                                                                                                                                        | 0.6  | -     | _    | μs    |

| Setup Time for Start Condition                 | t <sub>SU:STA</sub>    |                                                                                                                                                                                        | 0.6  | _     | _    | μs    |

| SCL Low Time                                   | t <sub>LOW</sub>       |                                                                                                                                                                                        | 1.3  | -     | -    | μs    |

| SCL High Time                                  | t <sub>HIGH</sub>      |                                                                                                                                                                                        | 0.6  | -     | -    | μs    |

| Data Setup Time                                | t <sub>SU:DAT</sub>    |                                                                                                                                                                                        | 100  | _     | _    | ns    |

| Data Hold Time                                 | t <sub>HD:DAT</sub>    | For t <sub>HD:DAT</sub> (min), the master device must provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the SCL signal falling edge | 0    | _     | 900  | ns    |

| Setup Time for Stop Condition                  | t <sub>su:sto</sub>    |                                                                                                                                                                                        | 0.6  | _     | -    | μs    |

| I <sup>2</sup> C™ Address Setting              |                        |                                                                                                                                                                                        |      |       |      |       |

| ADD Voltage for Address 0001,000               | Address1               |                                                                                                                                                                                        | 0    | -     | 0.7  | V     |

| ADD Voltage for Address 0001,001               | Address2               |                                                                                                                                                                                        | 1.3  | -     | 1.7  | V     |

| ADD Voltage for Address 0001,010               | Address3               |                                                                                                                                                                                        | 2.3  | -     | 2.7  | V     |

| ADD Voltage for Address 0001,011               | Address4               |                                                                                                                                                                                        | 3.3  | _     | 5.0  | V     |

| 10 peration at 16 V may be limited by power lo | as in the linear requ  | lator                                                                                                                                                                                  |      |       |      |       |

<sup>&</sup>lt;sup>1</sup>Operation at 16 V may be limited by power loss in the linear regulator.

#### I<sup>2</sup>C™ Interface Timing Diagram

5

<sup>&</sup>lt;sup>2</sup>Guaranteed by worst case process simulations and system characterization. Not production tested.

<sup>&</sup>lt;sup>3</sup>LNB output ripple and noise are dependent on component selection and PCB layout. Refer to the Application Schematic and PCB layout recommendations. Not production tested.

<sup>&</sup>lt;sup>4</sup>Current from the LNB output may be limited by the choice of Boost components.

#### **Functional Description**

#### **Protection**

The A8293 has a wide range of protection features and fault diagnostics which are detailed in the Status Register section.

#### **Boost Converter/Linear Regulator**

The A8293 solution contains a tracking current-mode boost converter and linear regulator. The boost converter tracks the requested LNB voltage to within 800 mV, to minimize power dissipation. Under conditions where the input voltage, V<sub>BOOST</sub>, is greater than the output voltage,  $V_{LNB}$ , the linear regulator must drop the differential voltage. When operating in these conditions, care must be taken to ensure that the safe operating temperature range of the A8293 is not exceeded.

The boost converter operates at 352 kHz typical: 16 times the internal 22 kHz tone frequency. All the loop compensation, current sensing, and slope compensation functions are provided

The A8293 has internal pulse-by-pulse current limiting on the boost converter and DC current limiting on the LNB output to protect the IC against short circuits. When the LNB output is shorted, the LNB output current is limited to 700 mA typical, and the IC will be shut down if the overcurrent condition lasts for more than 48 ms. If this occurs, the A8293 must be reenabled for normal operation. The system should provide sufficient time between successive restarts to limit internal power dissipation; a minimum of 2 s is recommended.

At extremely light loads, the boost converter operates in a pulse-skipping mode. Pulse skipping occurs when the BOOST voltage rises to approximately 450 mV above the BOOST target output voltage. Pulse skipping stops when the BOOST voltage drops 200 mV below the pulse skipping level.

In the case that two or more set top box LNB outputs are connected together by the customer (e.g., with a splitter), it is possible that one output could be programmed at a higher voltage than the other. This would cause a voltage on one output that is higher than its programmed voltage (e.g., 19 V on the output of a 13 V programmed voltage). The output with the highest voltage will effectively turn off the other outputs. As soon as this voltage is reduced below the value of the other outputs, the A8293 output will auto-recover to their programmed levels.

Charge Pump. Generates a supply voltage above the internal tracking regulator output to drive the linear regulator control.

**Slew Rate Control.** During either start-up, or when the output voltage at the LNB pin is transitioning, the output voltage rise

and fall times can be set by the value of the capacitor connected from the TCAP pin to GND (C<sub>TCAP</sub> or C7 in the Applications Schematic). Note that during start-up, the BOOST pin is precharged to the input voltage minus a voltage drop. As a result, the slew rate control for the BOOST pin occurs from this voltage.

The value of C<sub>TCAP</sub> can be calculated using the following formula:

$$C_{\text{TCAP}} = (I_{\text{TCAP}} \times 6) / SR$$

,

where SR is the required slew rate of the LNB output voltage, in V/s, and I<sub>TCAP</sub> is the TCAP pin current specified in the data sheet. The recommended value for C<sub>TCAP</sub>, 10 nF, should provide satisfactory operation for most applications. However, in some cases, it may be necessary to increase the value of C<sub>TCAP</sub> to avoid activating the current limit of the LNB output. One such situation is when two set-top boxes are connected in parallel. If this is the case, the following formula can be used to calculate  $C_{TCAP}$ :

$$C_{TCAP} \ge (I_{TCAP} \times 6)(2 \times C_{BOOST}) / I_{LIMLNB}$$

$$C_{TCAP} \ge (10 \ \mu A \times 6)(2 \times 100 \ \mu F) / 500 \ mA = 24 \ nF$$

.

The minimum value of C<sub>TCAP</sub> is 2.2 nF. There is no theoretical maximum value of C<sub>TCAP</sub> however too large a value will probably cause the voltage transition specification to be exceeded. Tone generation is unaffected by the value of  $C_{TCAP}$ .

Pull-Down Rate Control. In applications that have to operate at very light loads and that require large load capacitances (in the order of tens to hundreds of microfarads), the output linear stage provides approximately 40 mA of pull-down capability. This ensures that the output volts are ramped from 18 V to 13 V in a reasonable amount of time.

#### **ODT (Overcurrent Disable Time)**

If the LNB output current exceeds 700 mA, typical, for more than 48 ms, then the LNB output will be disabled and the OCP bit will be set.

#### **Short Circuit Handling**

If the LNB output is shorted to ground, the LNB output current will be clamped to 700 mA, typical. If the short circuit condition lasts for more than 48 ms, the A8293 will be disabled and the OCP bit will be set.

#### Auto-Restart

After a short circuit condition occurs, the host controller should periodically reenable the A8293 to check if the short circuit has

been removed. Consecutive startup attempts should allow at least 2 s of delay between restarts.

#### In-Rush Current

At start-up or during an LNB reconfiguration event, a transient surge current above the normal DC operating level can be provided by the A8293. This current increase can be as high as 700 mA, typical, for as long as required, up to a maximum of 48 ms.

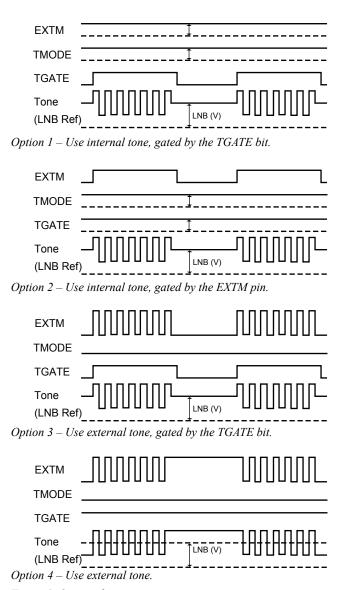

#### **Tone Generation**

The A8293 solution offers four options for tone generation, providing maximum flexibility to cover every application. The

EXTM pin (external modulation), in conjunction with the I<sup>2</sup>C<sup>TM</sup> control bits: TMODE (tone modulation) and TGATE (tone gate), provide the necessary control. The TMODE bit controls whether the tone source is either internal or external (via the EXTM pin). Both the EXTM pin and TGATE bit determine the 22 kHz control, whether gated or clocked.

Four options for tone generation are shown in figure 1. Note that when using option 4, when EXTM stops clocking, the LNB volts park at the LNB voltage, either plus or minus half the tone signal amplitude, depending on the state of EXTM. For example, if the EXTM is held low, the LNB DC voltage is the LNB programmed voltage minus 325 mV (typical).

Figure 1. Options for tone generation

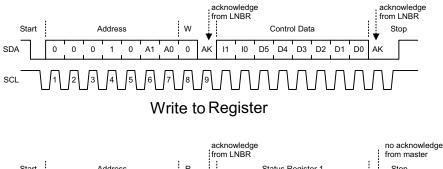

#### I<sup>2</sup>C™-Compatible Interface

This is a serial interface that uses two bus lines, SCL and SDA, to access the internal Control and Status registers of the A8293. Data is exchanged between a microcontroller (master) and the A8293 (slave). The clock input to SCL is generated by the master, while SDA functions as either an input or an open drain output, depending on the direction of the data.

#### **Timing Considerations**

The control sequence of the communication through the I<sup>2</sup>C<sup>TM</sup>-compatible interface is composed of several steps in sequence:

- 1. Start Condition. Defined by a negative edge on the SDA line, while SCL is high.

- 2. Address Cycle. 7 bits of address, plus 1 bit to indicate read (1) or write (0), and an acknowledge bit. The first five bits of the address are fixed as: 00010. The four optional addresses, de-

fined by the remaining two bits, are selected by the ADD input. The address is transmitted MSB first.

- 3. Data Cycles.

- Write -6 bits of data and 2 bits for addressing four internal control registers, followed by an acknowledge bit. See Control Register section for more information.

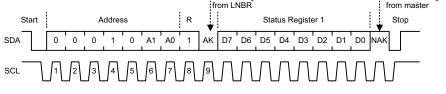

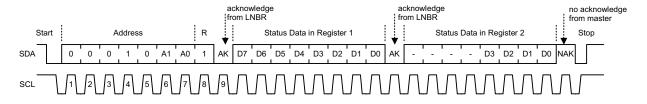

- Read Two status registers, where register 1 is read first, followed by register 2, then register 1, and so on. At the start of any read sequence, register 1 is always read first. Data is transmitted MSB first.

- 4. Stop Condition. Defined by a positive edge on the SDA line, while SCL is high. Except to indicate a Start or Stop condition, SDA must be stable while the clock is high. SDA can only be changed while SCL is low. It is possible for the Start or Stop condition to occur at any time during a data transfer. The A8293 always responds by resetting the data transfer sequence.

The Read/Write bit is used to determine the data transfer direction. If the Read/Write bit is high, the master reads the contents of

### Read One Byte from Register

Read Multiple Bytes from Register

Figure 2. I2C™ Interface. Read and write sequences.

1.508.853.5000: www.allegromicro.com

register 1, followed by register 2 if a further read is performed. If the Read/Write bit is low, the master writes data to one of the two Control registers. Note that multiple writes are not permitted. All write operations must be preceded with the address.

The Acknowledge bit has two functions. It is used by the master to determine if the slave device is responding to its address and data, and it is used by the slave when the master is reading data back from the slave. When the A8293 decodes the 7-bit address field as a valid address, it responds by pulling SDA low during the ninth clock cycle.

During a data write from the master, the A8293 also pulls SDA low during the clock cycle that follows the data byte, in order to indicate that the data has been successfully received. In both cases, the master device must release the SDA line before the ninth clock cycle, in order to allow this handshaking to occur.

During a data read, the A8293 acknowledges the address in the same way as in the data write sequence, and then retains control of the SDA line and send the data from register 1 to the master. On completion of the eight data bits, the A8293 releases the SDA line before the ninth clock cycle, in order to allow the master to acknowledge the data. If the master holds the SDA line low during this Acknowledge bit, the A8293 responds by sending the data from register 2 to the master. Data bytes continue to be sent to the master until the master releases the SDA line during the Acknowledge bit. When this is detected, the A8293 stops sending data and waits for a stop signal.

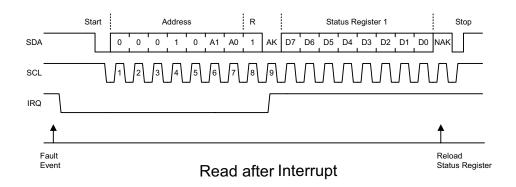

#### **Interrupt Request**

The A8293 also provides an interrupt request pin, IRQ, which is an open-drain, active-low output. This output may be connected to a common IRQ line with a suitable external pull-up and can

be used with other I<sup>2</sup>C<sup>TM</sup>-compatible devices to request attention from the master controller.

The IRQ output becomes active when either the A8293 first recognizes a fault condition, or at power-on, when the main supply,  $V_{\rm IN}$ , and the internal logic supply,  $V_{\rm REG}$ , reach the correct operating conditions. It is only reset to inactive when the I<sup>2</sup>C<sup>TM</sup> master addresses the A8293 with the Read/Write bit set (causing a read). Fault conditions are indicated by the TSD, VUV, and OCP bits, and are latched in the Status register. See the Status register section for full description.

The DIS and PNG status bits do not cause an interrupt. The PNG bit is continually updated, apart from the DIS bit, which changes when the LNB is either disabled, faulted, or is enabled.

When the master recognizes an interrupt, it addresses all slaves connected to the interrupt line in sequence, and then reads the status register to determine which device is requesting attention. The A8293 latches all conditions in the Status register until the completion of the data read. The action at the resampling point is further defined in the Status Register section. The bits in the Status register are defined such that the all-zero condition indicates that the A8293 is fully active with no fault conditions.

When  $V_{\rm IN}$  is initially applied, the I<sup>2</sup>C<sup>TM</sup>-compatible interface does not respond to any requests until the internal logic supply  $V_{\rm REG}$  has reached its operating level. Once  $V_{\rm REG}$  has reached this point, the IRQ output goes active, and the VUV bit is set. After the A8293 acknowledges the address, the IRQ flag is reset. After the master reads the status registers, the registers are updated with the VUV reset.

Figure 3. I<sup>2</sup>C™ Interface. Read sequences after interrupt request.

#### Control Registers (I<sup>2</sup>C™-Compatible Write Register)

All main functions of the A8293 are controlled through the I<sup>2</sup>C<sup>TM</sup>-compatible interface via the 8-bit Control registers. As the A8293 contains numerous control options, it is necessary to have two

control registers. Each register contains up to 6 bits of data (bit 0 to bit 5), followed by 2 bits for the register address (bit 6 and bit 7). The power-up states for the control functions are all 0s.

The following tables define the control bits for each address and the settings for output voltage:

Table 1. Control Register Address (I1, I0) = 00

| Bit | Name  | Function                                                                                       |

|-----|-------|------------------------------------------------------------------------------------------------|

| 0   | VSEL0 |                                                                                                |

| 1   | VSEL1 | See table 3, Output Voltage Amplitude Selection                                                |

| 2   | VSEL2 |                                                                                                |

| 3   | VSEL3 | 0: LNB = Low range 1: LNB = High range                                                         |

| 4   | ODT   | 1 (recommended): The ODT functions are always enabled, but setting 1 recommended at all times. |

| 5   | ENB   | 0: Disable LNB Output 1: Enable LNB Output                                                     |

| 6   | 10    | Address Bit: 0                                                                                 |

| 7   | I1    | Address Bit: 0                                                                                 |

| Bit 0 | VSEL0 | These three bits provide incremental control over the voltage on the LNB output.           |

|-------|-------|--------------------------------------------------------------------------------------------|

| Bit 1 | VSEL1 | The available voltages provide the necessary levels for all the common standards           |

| Bit 2 | VSEL2 | plus the ability to add line compensation in increments of 333 mV. The voltage             |

|       |       | levels are defined in table 3, Output Voltage Amplitude Selection.                         |

| Bit 3 | VSEL3 | Switches between the low level and high level output voltages on the LNB output.           |

|       |       | 0 selects the low level voltage and 1 selects the high level. The low-level center voltage |

|       |       | is 12.709 V nominal and the high level is 18.042 V nominal. These may be increased         |

|       |       | in steps of 333 mV using the VSEL2, VSEL1 and VSEL0 control register bits.                 |

| Bit 4 | ODT   | The overcurrent disable timer is always enabled.                                           |

| Bit 5 | ENB   | Enables the LNB output. When set to 1 the LNB output is switched on. When set to           |

|       |       | 0, the LNB output is disabled.                                                             |

| Bit 6 | I0    | Address                                                                                    |

| Bit 7 | I1    | Address                                                                                    |

Table 2. Control Register Address (I1, I0) = 10

| Bit | Name    | Function                 |  |  |

|-----|---------|--------------------------|--|--|

| 0   |         | 0: External Tone         |  |  |

| 0   | TMODE   | 1: Internal Tone         |  |  |

| 1   | TOATE   | 0: Tone Gated Off        |  |  |

| '   | 1 TGATE | 1: Tone Gated On         |  |  |

| 2   | -       | Not Used (0 recommended) |  |  |

| 3   | -       | Not Used                 |  |  |

| 4   | -       | Not Used                 |  |  |

| 5   | -       | Not Used                 |  |  |

| 6   | 10      | Address Bit: 0           |  |  |

| 7   | I1      | Address Bit: 1           |  |  |

Bit 0 TMODE Tone Mode. Selects between the use of an external 22 kHz logic signal or the use of the internal 22 kHz oscillator to control the tone generation on the LNB output. A 0 selects the external tone and a 1 selects the internal tone. See the Tone Generation section for more information

Bit 1 TGATE Tone Gate. Allows either the internal or external 22 kHz tone signals to be gated, unless the EXTM is selected for gating. When set to 0, the selected tone (via TMODE) is off. When set to 1, the selected tone is on. See Tone Generation Section for more information.

Bit 2 - Not Used.

Bit 3 - Not Used.

Bit 4 - Not Used.

Bit 5 - Not Used.

Bit 6 I0 Address.

Bit 7 I1 Address.

**Table 3. Output Voltage Amplitude Selection**

|       | •     | •     |       |         |

|-------|-------|-------|-------|---------|

| VSEL3 | VSEL2 | VSEL1 | VSEL0 | LNB (V) |

| 0     | 0     | 0     | 0     | 12.709  |

| 0     | 0     | 0     | 1     | 13.042  |

| 0     | 0     | 1     | 0     | 13.375  |

| 0     | 1     | 0     | 0     | 14.042  |

| 0     | 1     | 1     | 1     | 15.042  |

| 1     | 0     | 0     | 0     | 18.042  |

| 1     | 0     | 1     | 0     | 18.709  |

| 1     | 0     | 1     | 1     | 19.042  |

#### Status Registers (I2C™-Compatible Read Register)

The main fault conditions: overcurrent (OCP), undervoltage (VUV) and overtemperature (TSD), are all indicated by setting the relevant bits in the Status registers. In all fault cases, once the bit is set, it remains latched until the A8293 is read by the I<sup>2</sup>C<sup>TM</sup> master, assuming the fault has been resolved.

The current status of the LNB output is indicated by the disable bit, DIS. The DIS bit is set when either a fault occurs or if the LNB is disabled intentionally. This bit is latched, and is reset when the LNB is commanded on again. The power not good (PNG) is the only bit which may be reset without an I<sup>2</sup>C<sup>TM</sup> read sequence. Table 4 summarizes the condition of each bit when set and how it is reset.

As the A8293 has a comprehensive set of status reporting bits, it is necessary to have two Status registers. When performing a multiple read function, register 1 is read followed by register 2, then register 1 again and so on. Whenever a new read function is performed, register 1 is always read first.

The normal sequence of the master in a fault condition will be to detect the fault by reading the Status registers, then rereading the Status registers until the status bit is reset indicating the fault condition is reset. The fault may be detected either by continuously polling, by responding to an interrupt request (IRQ), or by detecting a fault condition externally and performing a diagnostic poll of all slave devices. Note that the fully-operational condition of the Status registers is all 0s, to simplify checking of the Status bit.

**Table 4. Status Register Bit Setting**

|            | no il cuitato regiono: Ele coming                  |             |                                          |  |  |  |

|------------|----------------------------------------------------|-------------|------------------------------------------|--|--|--|

| Status Bit | Function                                           | Set         | Reset<br>Condition                       |  |  |  |

| _          | Not used                                           | _           | Not used                                 |  |  |  |

| DIS        | LNB disabled, either intentionally or due to fault | Latched     | LNB enabled and no fault                 |  |  |  |

| OCP        | Overcurrent                                        | Latched     | I <sup>2</sup> C™ read and fault removed |  |  |  |

| PNG        | Power not good                                     | Non-latched | LNB volts in range                       |  |  |  |

| _          | Not used                                           | _           | Not used                                 |  |  |  |

| TSD        | Thermal shutdown                                   | Latched     | I <sup>2</sup> C™ read and fault removed |  |  |  |

| VUV        | Undervoltage                                       | Latched     | I <sup>2</sup> C™ read and fault removed |  |  |  |

Table 5. Status Register 1

| Bit | Name | Function                     |  |  |

|-----|------|------------------------------|--|--|

| 0   | DIS  | LNB output disabled          |  |  |

| 1   | -    | Not Used                     |  |  |

| 2   | OCP  | Overcurrent                  |  |  |

| 3   | -    | Not Used                     |  |  |

| 4   | PNG  | Power Not Good               |  |  |

| 5   | -    | Not Used                     |  |  |

| 6   | TSD  | Thermal Shutdown             |  |  |

| 7   | VUV  | V <sub>IN</sub> Undervoltage |  |  |

Bit 0 DIS

LNB Output Disabled. DIS is used to indicate the current condition of the LNB output. At power-on, or if a fault condition occurs, DIS will be set. This bit changing to 1 does not cause the IRQ to activate because the LNB output may be disabled intentionally by the I<sup>2</sup>C<sup>TM</sup> master. This bit will be reset at the end of a write sequence if the LNB output is enabled.

Bit 1 –

Bit 2 OCP

Overcurrent. If the LNB output detects an overcurrent condition, for greater than 48 ms, the LNB output will be disabled. The OCP bit will be set to indicate that an overcurrent has occurred and the disable bit, DIS, will be set. The Status register is updated on the rising edge of the 9<sup>th</sup> clock pulse in the data read sequence, where the OCP bit is reset in all cases, allowing the master to reenable the LNB output. If the overcurrent timer is not enabled, the device operate in current limit indefinitely and the OCP bit will be set. If the overcurrent condition is removed, the OCP bit will automatically be reset. Note that if the overcurrent operates long enough, and a thermal shutdown occurs, the LNB output will be disabled and the TSD bit will be set.

Bit 3 – Not used.

Not used.

Bit 4 PNG

Power Not Good. Set to 1 when the LNB output is enabled and the LNB voltage is below 85% of the programmed voltage. The PNG is reset when the LNB volts are within 90% of the programmed LNB voltage.

Bit 5 – Not used

Bit 6 TSD

Thermal Shutdown. 1 indicates that the A8293 has detected an overtemperature condition and has disabled the LNB output. The disable bit, DIS, will also be set. The status of the overtemperature condition is sampled on the rising edge of the 9<sup>th</sup> clock pulse in the data read sequence. If the condition is no longer present, then the TSD bit will be reset, allowing the master to reenable the LNB output if required. If the condition is still present, then the TSD bit will remain at 1.

Bit 7 VUV

Undervoltage Lockout. 1 indicates that the A8293 has detected that the input supply,  $V_{\rm IN}$  is, or has been, below the minimum level and an undervoltage lockout has occurred disabling the LNB outputs. The disable bit, DIS, will also be set and the A8293 will not reenable the output until so instructed by writing the relevant bit into the control registers. The status of the undervoltage condition is sampled on the rising edge of the 9th clock pulse in the data read sequence. If the condition is no longer present, then the VUV bit will be reset allowing the master to reenable the LNB output if required. If the condition is still present, then the VUV bit will remain at 1.

Table 6. Status Register 2

| Bit | Name | Function |  |  |

|-----|------|----------|--|--|

| 0   | -    | Not Used |  |  |

| 1   | -    | Not Used |  |  |

| 2   | -    | Not Used |  |  |

| 3   | -    | Not Used |  |  |

| 4   | _    | Not Used |  |  |

| 5   | _    | Not Used |  |  |

| 6   | -    | Not Used |  |  |

| 7   | _    | Not Used |  |  |

Bit 0 - Not used.

Bit 1 - Not used.

Bit 2 - Not used.

Bits 3 to 7 Not used.

# Single LNB Supply and Control Voltage Regulator

**Table 7. Component Selection Table**

| Component  | Characteristics                                                         | Manufacturer Device                                                                                         |

|------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| C1, C4, C8 | 100 nF, 50 V, X5R or X7R, 0603                                          |                                                                                                             |

| C2, C5     | 100 μF, 35 $V_{MIN}$ , ESR<75 mΩ, $I_{RIPPLE}$ > 700 mA                 | Panasonic: EEU-FM1H101B<br>ChemiCon: EKZE500ELL101MHB5D<br>Nichicon: UHC1V101MPT                            |

| C3         | 220 nF, 10 V <sub>MIN</sub> , X5R or X7R, 0402 or 0603                  |                                                                                                             |

| C6         | 1.0 μF, 25 V <sub>MIN</sub> , X5R or X7R, 1206                          | TDK: C3216X7R1E105K<br>Murata: GRM31MR71E105KA01<br>Taiyo Yuden: TMK316BJ105KL-T<br>Kemet: C1206C105K3RACTU |

| C7         | 10 nF, 10 V <sub>MIN</sub> , X5R or X7R, 0402 or 0603                   |                                                                                                             |

| C9         | 10 nF, 50 V, X5R or X7R, 0402 or 0603                                   |                                                                                                             |

| C10        | 220 nF, 50 V, X5R or X7R, 0805                                          |                                                                                                             |

| D1, D2     | Schottky diode, 40 V, 1 A, SOD-123                                      | Diodes, Inc: B140HW-7<br>Central Semi: CMMSH1-40                                                            |

| D3         | Schottky diode, 40 V, 3 A, SMA                                          | Sanken: SFPB-74<br>Vishay: B340A-E3/5AT<br>Diodes, Inc.: B340A-13-F<br>Central Senmi: CMSH3-40MA            |

| D4         | TVS, 20 V <sub>RM</sub> , 32 V <sub>CL</sub> at 500 A (8/20 μs), 3000 W | ST:LNBTVS6-221S<br>Littelfuse: SMDJ20A                                                                      |

| L1         | 33 μH, $I_{SAT}$ > 2.6 A, DCR < 90 mΩ                                   | TDK: TSL1112RA-330K2R3-PF<br>Taiyo Yuden: LHLC10TB330K<br>Coilcraft: DR0810-333L                            |

| R1 to R4   | Determined by V <sub>DD</sub> , bus capacitance, etc.                   |                                                                                                             |

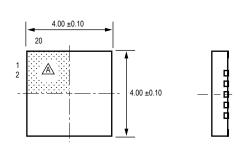

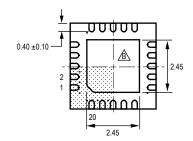

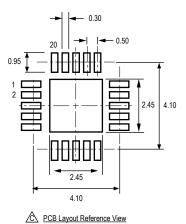

#### Package ES 20-Pin MLP/QFN

For Reference Only, not for tooling use (reference DWG-2864, JEDEC MO-220 WGGD) Dimensions in millimeters

Exact case and lead configuration at supplier discretion within limits shown

A Terminal #1 mark area

Exposed thermal pad (reference only, terminal #1 identifier appearance at supplier discretion)

Reference land pattern layout (reference IPC7351 QFN50P400X400X80-21BM)

All pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary to meet application process requirements and PCB layout tolerances; when mounting on a multilayer PCB, thermal vias at the exposed thermal pad land can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)

Coplanarity includes exposed thermal pad and terminals

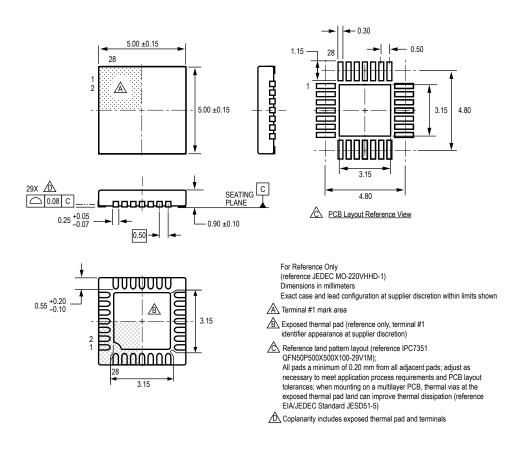

#### Package ET 28-Pin MLP/QFN

## Single LNB Supply and Control Voltage Regulator

#### **Revision History**

| Number | Date             | Description                                  |

|--------|------------------|----------------------------------------------|

| 4      | March 12, 2012   | Update Output Voltage Amplitude              |

| 5      | December 5, 2016 | Updated product status to Not for New Design |

| 6      | June 5, 2017     | Updated product status to Pre-EOL            |

| 7      | January 4, 2018  | Updated product status to Last-Time Buy      |

I<sup>2</sup>C<sup>TM</sup> is a trademark of Philips Semiconductors.

DiSEqC<sup>TM</sup> is a trademark of Eutelsat S.A.

Copyright ©2007-2018, Allegro MicroSystems, LLC

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website: www.allegromicro.com