# 8-Channel Ultra-Low Phase Noise Continuous Waveform Transmitter with Beamformer

#### **Features**

- 8-Channel Ultrasound Continuous Waveform (CW) Transmitter with Integrated Beamformer

- CW Output ±1V to ±6Vp-p with Low R<sub>ON</sub>

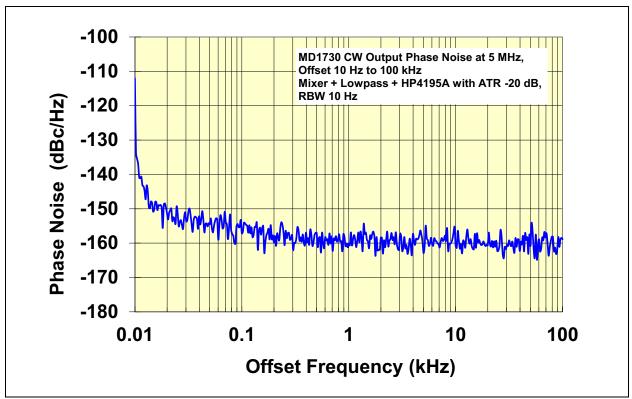

- -160 dbc/Hz Ultra-Low Phase Noise at 1 kHz Offset and 5 MHz

- 8-Bit Programmable Per-Channel Beamforming Phase Delay

- 8-Bit Programmable Dividers for CW Frequency with Input Clock Frequency up to 250 Mhz

- Input Clock Compatible with LVDS/SSTL or Single-Ended LVCMOS

- · LVCMOS 2.5V Logic for the Control I/O pins

- · Fast SPI Interface Supports up to 200 MHz

- SPI Interface Supports Daisy Chaining and Broadcasting Mode

# **Applications**

- Medical Ultrasound Imaging System for Cardiovascular Application

- · Ultrasound Fetal Heart Monitoring Device

- · Ultrasound Flow Meter

- · Programmable Array Pattern Generator

## **General Description**

The MD1730 is an 8-channel ultra-low phase noise CW transmitter with integrated beamformer. It is designed for medical ultrasound imaging systems requiring high-performance CW Doppler mode. The MD1730 has a dedicated signal path designed to minimize phase noise to the output. In addition, it has a high-speed SPI interface that enables CW beamforming features. The outputs of the MD1730 can swing up to ±6V and each output has a separate programmable phase delay. Additionally, programming the internal frequency divider register, the MD1730 can output different CW frequencies from a single clock source. For instance, when the input clock frequency is 160 MHz and the frequency divider is set to 16, an output CW frequency of 5 MHz can be obtained with a phase delay step size of 6.25 ns, which translates to an angular resolution of 11.25 degrees.

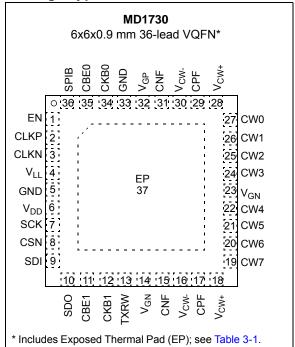

# Package Type

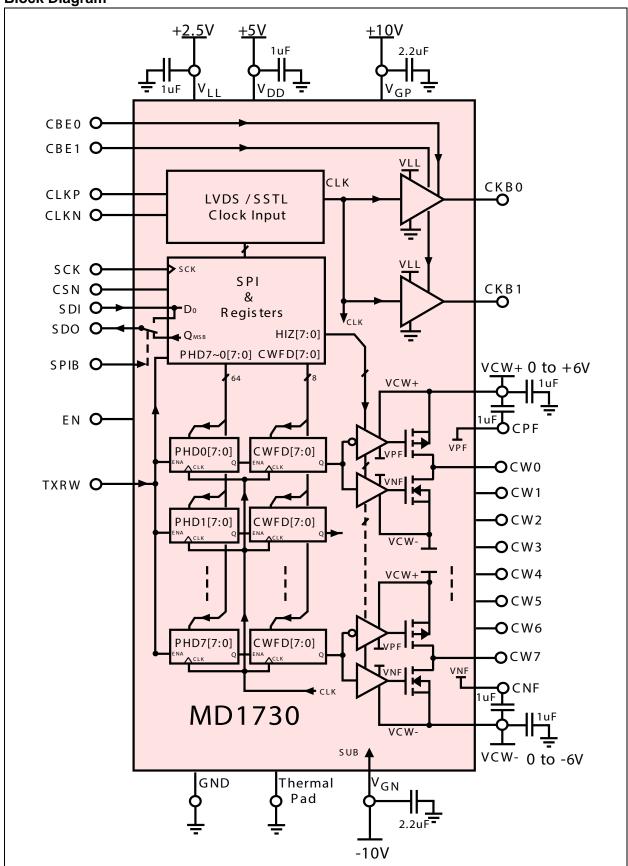

# **Block Diagram**

# **MD1730**

# 1.0 ELECTRICAL CHARACTERISTICS

# **Absolute Maximum Ratings †**

| Positive Logic Supply (V <sub>LL</sub> )                                  | 0.5V to +3.0V  |

|---------------------------------------------------------------------------|----------------|

| Positive Supply Voltage (V <sub>DD</sub> )                                |                |

| Positive Supply Voltage (V <sub>GP</sub> )                                | 0.5V to +13.5V |

| Negative Supply Voltage (V <sub>GN</sub> )                                |                |

| CW Output Positive Supply Voltage (V <sub>CW+</sub> )                     | 0.5V to +12V   |

| CW Output Negative Supply Voltage (V <sub>CW-</sub> )                     |                |

| All Digital Inputs (V <sub>IN</sub> )                                     |                |

| CW Outputs (V <sub>OUT</sub> )                                            | 12V to +12V    |

| Operating Ambient Temperature                                             | 0°C to +85°C   |

| Maximum Junction Temperature                                              | 0°C to +85°C   |

| Storage Temperature                                                       | +125°C         |

| Thermal Resistance Junction to Ambient ( $\Theta_{JA}$ , JESD51-5)        | 25°C/W         |

| Thermal Resistance Junction to Bottom Cu Pad (Θ <sub>JB</sub> , JESD51-5) |                |

| Thermal Resistance Junction to Package Top ( $\Theta_{JC}$ , JESD51-5)    |                |

| ESD Rating All Pins                                                       |                |

**† Notice:** Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

TABLE 1-1: INPUT/OUTPUT PIN DC CHARACTERISTICS

| <b>Electrical Specifications:</b> Unless otherwise indicated, $V_{LL}$ = +2.5V, $V_{GP}$ = +10V, $V_{GN}$ = -10V, $V_{CW+}$ = +6.0V, |                    |      |      |      |       |                                            |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|------|------|-------|--------------------------------------------|--|--|

| $V_{CW-} = -6.0V, V_{DD} = +5V, T_A = 25$                                                                                            | °C.                |      | 1    |      |       | T                                          |  |  |

| Parameters                                                                                                                           | Sym.               | Min. | Тур. | Max. | Units | Conditions                                 |  |  |

| Operating Supply                                                                                                                     |                    |      |      |      |       |                                            |  |  |

| Logic Supply Voltage                                                                                                                 | $V_{LL}$           | 2.35 | 2.50 | 2.65 | V     | $(V_{GP}+ V_{CW-} ) \ge 10V$               |  |  |

| VDD Supply Voltage                                                                                                                   | $V_{DD}$           | 4.75 | 5.0  | 5.25 | V     | $(V_{GN} +  V_{CW} +  ) \ge 10V$           |  |  |

| Positive Supply Voltage                                                                                                              | $V_{GP}$           | 8.0  | 10   | 12   | V     | T <sub>A</sub> = 0 to +85°C, <b>Note 2</b> |  |  |

| Negative Supply Voltage                                                                                                              | $V_{GN}$           | -12  | -10  | -8.0 | V     |                                            |  |  |

| CW Output Positive Supply                                                                                                            | V <sub>CW+</sub>   | 1.0  |      | 6.0  | V     |                                            |  |  |

| CW Output Negative Supply                                                                                                            | V <sub>CW-</sub>   | -6.0 |      | -1.0 | V     |                                            |  |  |

| V <sub>LL</sub> Quiescent Current                                                                                                    | $I_{LLQ}$          | _    | 0.02 | 0.1  | mA    | $EN = 0, f_{CLK} = f_{SCK} = 0$            |  |  |

| V <sub>DD</sub> Quiescent Current                                                                                                    | $I_{DDQ}$          | _    | 0.15 | 0.2  | mA    | All logic input no transit                 |  |  |

| V <sub>GP</sub> Quiescent Current                                                                                                    | $I_{GPQ}$          | _    | 1.0  | 2.0  | μA    |                                            |  |  |

| V <sub>GN</sub> Quiescent Current                                                                                                    | $I_{GNQ}$          | _    | 33   | 45   | μA    |                                            |  |  |

| V <sub>CW+</sub> Quiescent Current                                                                                                   | I <sub>CW+Q</sub>  | _    | 26   | 45   | μΑ    |                                            |  |  |

| V <sub>CW-</sub> Quiescent Current                                                                                                   | I <sub>CW-Q</sub>  | _    | 6    | 10   | μA    |                                            |  |  |

| V <sub>LL</sub> Enabled Current                                                                                                      | I <sub>LLEN</sub>  | _    | 6.0  | 9.0  | mA    | EN = 1, f <sub>SCK</sub> = 120 MHz         |  |  |

| V <sub>DD</sub> Enabled Current                                                                                                      | I <sub>DDEN</sub>  | _    | 0.2  | 0.3  | mA    | TXRW = 0, SDI = 0,                         |  |  |

| V <sub>GP</sub> Enabled Current                                                                                                      | I <sub>GPEN</sub>  | _    | 2.0  | 3.0  | mA    | SDO no load.                               |  |  |

| V <sub>GN</sub> Enabled Current                                                                                                      | I <sub>GNEN</sub>  | _    | 2.0  | 3.0  | mA    |                                            |  |  |

| V <sub>CW+</sub> Enabled Current                                                                                                     | I <sub>CW+EN</sub> | _    | 2.0  | 3.0  | mA    |                                            |  |  |

| V <sub>CW-</sub> Enabled Current                                                                                                     | I <sub>CW-EN</sub> | _    | 2.0  | 3.0  | mA    |                                            |  |  |

Note 1: Characterized only; not 100% tested in production.

2: Design Guidance Only (DGO).

TABLE 1-1: INPUT/OUTPUT PIN DC CHARACTERISTICS (CONTINUED)

Electrical Specifications: Unless otherwise indicated,  $V_{LL}$  = +2.5V,  $V_{GP}$  = +10V,  $V_{GN}$  = -10V,  $V_{CW+}$  = +6.0V,  $V_{CW} = -6.0V, V_{DD} = +5V, T_A = 25^{\circ}C.$ Max. Units **Conditions Parameters** Sym. Min. Typ. VII Current at CW 5MHz 2.5 3.0 mΑ EN = 1,  $f_{CLK} = 80$  MHz,  $I_{LL5}$ TXRW = 1, CW 5 MHz. V<sub>DD</sub> Current at CW 5MHz 1.0 2.0 mA  $I_{DD5}$ no load 8-channel VGP Current at CW 5MHz 6.0 10 mΑ  $I_{GP5}$ V<sub>GN</sub> Current at CW 5MHz 12 18 mΑ  $I_{GN5}$ V<sub>CW+</sub> Current at CW 5MHz 35 26 mΑ I<sub>CW+5</sub> V<sub>CW-</sub> Current at CW 5MHz 21 30 mΑ  $I_{CW-5}$ SPI & Logic Input Logic High Voltage  $V_{\text{IH}}$ 0.8 V<sub>II</sub> V 2.5V LVCMOS  $V_{II}$ V Input Logic Low Voltage 0  $0.2 \, V_{11}$  $V_{IL}$ Input Logic High Current 1.0 μΑ  $I_{1H}$ Input Logic Low Current  $I_{IL}$ μΑ SPI and Logic Input Capacitance 4.5 pF Note 1  $C_{IN}$ Output Logic High Current  $I_{OH}$ mΑ 2.5V LVCMOS **Output Logic Low Current** mΑ  $I_{OL}$ SDO Output Logic High Voltage ٧ with 5 pF load  $V_{OH}$ ٧ SDO Output Logic Low Voltage 0.35  $V_{OL}$

Note 1: Characterized only; not 100% tested in production.

2: Design Guidance Only (DGO).

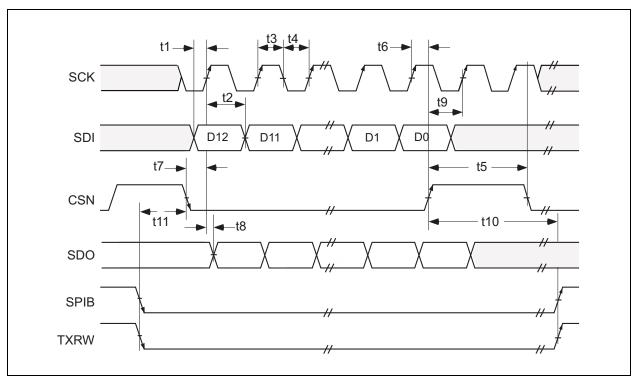

#### TABLE 1-2: SPI AND LOGIC AC ELECTRICAL SPECIFICATIONS

Electrical Specifications: Unless otherwise indicated, V<sub>LL</sub> = +2.5V, V<sub>GP</sub> = +10V, V<sub>GN</sub> = -10V, V<sub>CW+</sub> = +6.0V,  $V_{CW-} = -6.0V$ ,  $V_{DD} = +5V$ ,  $T_A = 25$ °C. **Parameters** Sym. Min. Typ. Max. Units **Conditions** Output Rise Time  $t_r$ 0.65 1.5 pF load, Note 1 Output Fall Time 0.65  $t_f$ Output Rise Propagation Delay 2.8 CLK rise 50% to output ns  $t_{dr}$ 50%, after latency. Output Fall Propagation Delay 3.0  $t_{df}$ Note 1 Channel to channel, **Delay Time Matching** ±0.5 ±1.0 ns  $t_{dm}$ Note 1, f<sub>CLK</sub> = 80 MHz SDI Valid to SCK, Setup Time 1.0 Note 1  $t_1$ 0.6 SCK To SDI Data Hold Time 2.0  $t_2$ ns SCK High Time % of 1/f<sub>CLK</sub>  $t_3$ 45 55 % Note 2 SCK Low Time % of 1/f<sub>CLK</sub> %  $t_4$ 45 55 **CSN Hi-Time** 2-cycle SCK Note 2  $t_5$ SCK Rise to CSN Rise 2.0 Note 1  $t_6$ ns CSN Low to SCK Rise 8.0 t<sub>7</sub> ns SDO Valid from SCK Rise SPIB = 0, 1.5 pF Load, t<sub>8</sub> 3.1 4.0 Note 1 CSN Rise to SCK Rise 2.0 Note 1  $t_9$ ns CSN Rise to TXRW or SPIB Rise 9-cycle SCK Note 2 t<sub>10</sub> TXRW or SPIB Fall to CSN Fall t<sub>11</sub> 1-cycle

Note 1: Characterized only; not 100% tested in production.

2: Design Guidance Only (DGO).

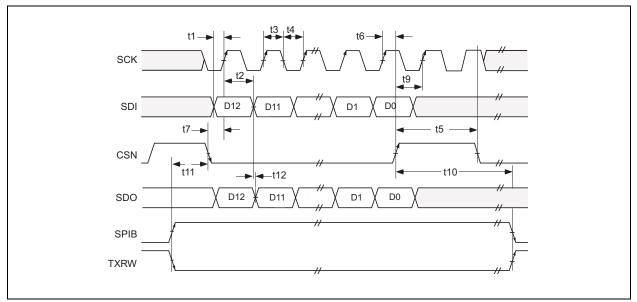

TABLE 1-2: SPI AND LOGIC AC ELECTRICAL SPECIFICATIONS (CONTINUED)

**Electrical Specifications:** Unless otherwise indicated,  $V_{LL}$  = +2.5V,  $V_{GP}$  = +10V,  $V_{GN}$  = -10V,  $V_{CW+}$  = +6.0V,  $V_{CW}$  = -6.0V,  $V_{DD}$  = +5V,  $T_A$  = 25°C. **Conditions Parameters** Sym. Min. Тур. Max. Units SDO to SDI Valid Delay 2.3 3.0 SPIB = 1, 1.5 pF Load, t<sub>12</sub> ns Note 1 TXRW Rise to CLKP Rise Note 1 2.5 ns t<sub>13</sub> Latency to CW Wave Rise t<sub>14</sub> 2-cycle CLK After TXRW = 1, PHD=0, Note 2 Latency CSN Rise to TXRW Fall CLK 2-cycle Note 2 t<sub>15</sub> SCK Clock Frequency 200 MHz Note 1  $f_{SCK}$ **EN Off Time** 20 30 Note 2 ns t<sub>EN-Off</sub> **EN On Time** 300 2.0 µF on CPF/CNF, 150 t<sub>EN-On</sub> μs Note 2

Note 1: Characterized only; not 100% tested in production.

2: Design Guidance Only (DGO).

#### TABLE 1-3: CLOCK BUFFER OUTPUTS AC/DC CHARACTERISTICS

**Electrical Specifications:** Unless otherwise indicated,  $V_{LL}$  = +2.5V,  $V_{GP}$  = +10V,  $V_{GN}$  = -10V,  $V_{CW+}$  = +6.0V,  $V_{CW-}$  = -6.0V,  $V_{DD}$  = +5V,  $V_{A}$  = 25°C.

| V <sub>CW-</sub> 0.0V, V <sub>DD</sub> - +5V, 1 <sub>A</sub> - 25 C. |                    |      |          |      |       |                                   |  |  |  |

|----------------------------------------------------------------------|--------------------|------|----------|------|-------|-----------------------------------|--|--|--|

| Parameters                                                           | Sym.               | Min. | Тур.     | Max. | Units | Conditions                        |  |  |  |

| Clock Output Frequency<br>Range                                      | f <sub>CKB</sub>   | 40   | 160      | 250  | MHz   | Note 1                            |  |  |  |

| Clock Output Duty Cycle                                              | D%                 | 45   | _        | 55   | %     | Note 2                            |  |  |  |

| CKB0,1 Rise Time                                                     | t <sub>rb</sub>    | _    | 0.6      | 1.0  | ns    | f <sub>CLK</sub> = 80 Mhz, 1.5 pF |  |  |  |

| CKB0,1 Fall Time                                                     | t <sub>fb</sub>    | ı    | 0.5      | 1.0  |       | load, Note 1                      |  |  |  |

| Output Rise Propagation Delay                                        | t <sub>drb</sub>   | _    | 2.0      | 3.0  | ns    | CLK rise to CKB, 50%, Note 1      |  |  |  |

| Output Fall Propagation Delay                                        | t <sub>dfb</sub>   | _    | 2.0      | 3.0  |       |                                   |  |  |  |

| CBE Enable Time                                                      | t <sub>cbe</sub>   | _    | 2.1      | 3.0  |       | CBE to CLK rise, 50%, Note 1      |  |  |  |

| CKB0,1 Output logic high                                             | V <sub>OHCKB</sub> | _    | $V_{LL}$ | _    | V     | Note 2                            |  |  |  |

| CKB0,1 Output Logic low                                              | V <sub>OLCKB</sub> | _    | GND      | _    | V     | Note 2                            |  |  |  |

Note 1: Characterized only; not 100% tested in production.

2: Design Guidance Only (DGO).

## TABLE 1-4: CW OUTPUTS DC/AC ELECTRICAL CHARACTERISTICS

**Electrical Specifications:** Unless otherwise indicated,  $V_{LL}$  = +2.5V,  $V_{GP}$  = +10V,  $V_{GN}$  = -10V,  $V_{CW+}$  = +6.0V,  $V_{CW-}$  = -6.0V,  $V_{DD}$  = +5V,  $V_{A}$  = 25°C.

| Parameters                       | Sym.               | Min. | Тур. | Max. | Units | Conditions                                     |

|----------------------------------|--------------------|------|------|------|-------|------------------------------------------------|

| CW Output Peak to Peak Voltage   | V <sub>CWOUT</sub> | -6.0 | -    | +6.0 | V     |                                                |

| CW Output Rise Propagation Delay | t <sub>drCW</sub>  | _    | 4.0  | 6.0  | ns    | TxCLK 50% to CWx                               |

| CW Output Fall Propagation Delay | t <sub>dfCW</sub>  | _    | 4.0  | 6.0  |       | 10%, after latency, Note 1                     |

| CW Output Maximum Current        | $I_{\text{CW}\pm}$ | ±250 | ±300 | _    | mA    | $V_{CW\pm}$ = ±5.0V, 0.1 $\Omega$ load, Note 1 |

Note 1: Characterized only; not 100% tested in production.

2: Design Guidance Only (DGO).

## TABLE 1-4: CW OUTPUTS DC/AC ELECTRICAL CHARACTERISTICS (CONTINUED)

**Electrical Specifications:** Unless otherwise indicated,  $V_{LL}$  = +2.5V,  $V_{GP}$  = +10V,  $V_{GN}$  = -10V,  $V_{CW+}$  = +6.0V,  $V_{CW-}$  = -6.0V,  $V_{DD}$  = +5V,  $V_{A}$  = 25°C.

| CW- CV- TO THE TOTAL THE T |                     |      |      |      |            |                                            |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|------|------|------------|--------------------------------------------|--|--|--|

| Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Sym.                | Min. | Тур. | Max. | Units      | Conditions                                 |  |  |  |

| Static Output Resistance PFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R <sub>ONCW</sub>   | _    | 7.5  | 12   | Ω          | RON at $V_{CW\pm} = \pm 5.0V$ ,            |  |  |  |

| Static Output Resistance NFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                     | _    | 6.5  | 11   |            | I <sub>CW±</sub> = ±100 mA load,<br>Note 1 |  |  |  |

| Change in R <sub>DS(ON)</sub> with Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ΔR <sub>ONCW</sub>  | _    | _    | 1.0  | %/C        | $V_{CW\pm} = \pm 5.0V$ , <b>Note 2</b>     |  |  |  |

| CW Phase Resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RE <sub>Phase</sub> |      | 1    | _    | CLK        | Note 2                                     |  |  |  |

| CW Phase Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | N <sub>Phase</sub>  | _    | -160 | _    | dBC/<br>Hz | CW 5 MHz,<br>1 kHz Offset, Note 1          |  |  |  |

- **Note 1:** Characterized only; not 100% tested in production.

- 2: Design Guidance Only (DGO).

### TABLE 1-5: LVDS / SSTL CLOCK INPUTS AC / DC CHARACTERISTICS

**Electrical Specifications:** Unless otherwise indicated,  $V_{LL} = +2.5V$ ,  $V_{GP} = +10V$ ,  $V_{GN} = -10V$ ,  $V_{CW+} = +6.0V$ ,  $V_{CW-} = -6.0V$ ,  $V_{DD} = +5V$ ,  $T_A = 25$ °C. **Parameters** Sym. Min. Units **Conditions** Тур. Max. CLKP/CLKN Clock Frequency 160 250 40 MHz Note 1  $f_{CLK}$ 1.0 Note 2 Clock Input Slew Rate V/ns t<sub>CSR</sub> Control/Data Input Slew Rate 1.0 V/ns  $t_{DSR}$ **Single Ended Clock Input** ٧ SSTL Reference Voltage 1.13 1.25 1.38 Note 1  $V_{REFS}$ V Note 1 DC Input Logic High  $V_{IH(DC)}$ V<sub>REFS</sub> +0.15  $V_{LL}$  +0.3 DC Input Logic Low V<sub>REFS</sub> -0.15 ٧ Note 1 V<sub>IL(DC)</sub> -0.3 ٧ AC Input Logic High  $V_{REF} = 0.5V_{LL}$ , Slew  $V_{IH(AC)}$ V<sub>REFS</sub> +0.31 rate 1.0 V/ns, Note 1 AC Input Logic Low V<sub>REFS</sub> -0.31  $V_{IL(AC)}$ **Differential Clock Input** CLK and CLK, Note 1 **AC Differential Cross Point**  $0.5V_{LL}$  -0.2  $0.5V_{11} + 0.2$  $V_{X(AC)}$ DC Input Max Swing Voltage 0.3 V<sub>LL</sub> +0.6 ٧ Note 1 V<sub>SWING(DC)</sub> AC Differential Input Voltage 0.62 ٧ Note 1  $V_{11} + 0.6$ V<sub>SWING(AC)</sub> DC Input Signal Voltage -0.3 V<sub>LL</sub> +0.3 V Note 1  $V_{IN(DC)}$

1.0

Note 1: Characterized only; not 100% tested in production.

**SLEW**

2: Design Guidance Only (DGO).

CLKP/CLKN Slew Rate

V/ns

Note 2

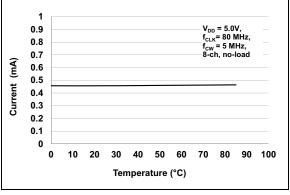

## 2.0 TYPICAL PERFORMANCE CURVES

Note:

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

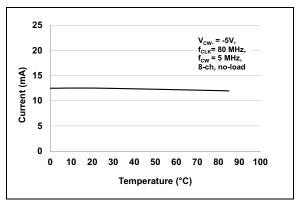

FIGURE 2-1: I<sub>DD</sub> vs. Temperature.

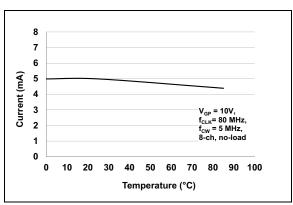

FIGURE 2-2: I<sub>VGP</sub> vs. Temperature.

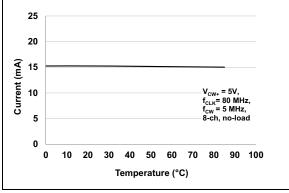

FIGURE 2-3: I<sub>VCW+</sub> vs. Temperature.

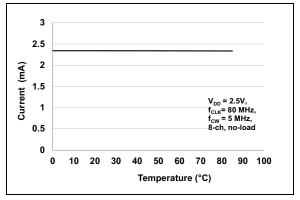

FIGURE 2-4: I<sub>VLL</sub> vs. Temperature.

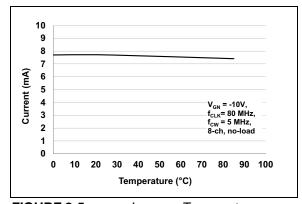

FIGURE 2-5: I<sub>VGN</sub> vs. Temperature.

FIGURE 2-6: I<sub>VCW-</sub> vs. Temperature.

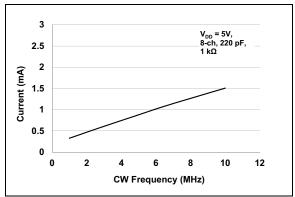

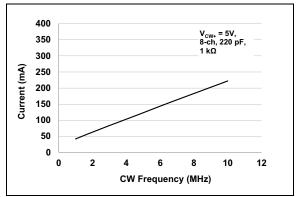

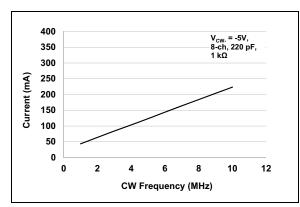

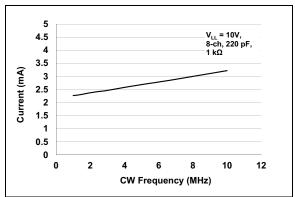

**FIGURE 2-7:** I<sub>VDD</sub> vs. CW Output Frequency.

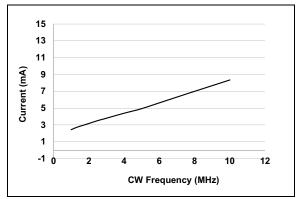

FIGURE 2-8: I<sub>VCW+</sub> vs. CW Output Frequency.

**FIGURE 2-9:**  $I_{VCW-}$  vs. CW Output Frequency.

**FIGURE 2-10:** I<sub>VLL</sub> vs. CW Output Frequency.

**FIGURE 2-11:** I<sub>VGN</sub> vs. CW Output Frequency.

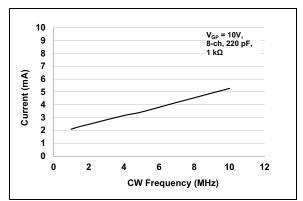

**FIGURE 2-12:**  $I_{VGP}$  vs. CW Output Frequency.

FIGURE 2-13: Typical CW Output Phase Noise Curves.

# 3.0 PIN DESCRIPTION

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| 6x6 VQFN                             | Symbol           | Pin Function                                                                                                                                                                                                                             |

|--------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                    | EN               | Device Enable Input. When EN = 0, the SPI and the internal regulator are disabled. The device is enabled when EN = 1. Note that the EN pin has no control over the clock buffers, as the clock buffers have their dedicated enable pins. |

| 2                                    | CLKP             | Positive Input of the Internal System Clock and is compatible with LVDS/SSTL. For LVCMOS 2.5V input refer to Figure 4-8.                                                                                                                 |

| 3                                    | CLKN             | Negative Input of the Internal System Clock and is compatible with LVDS/SSTL. For LVCMOS 2.5V input refer to Figure 4-8.                                                                                                                 |

| 4                                    | $V_{LL}$         | +2.5V Positive Voltage Power Supply, it requires a 1.0 μF decoupling capacitor to GND                                                                                                                                                    |

| 5, 33                                | GND              | Ground, 0V                                                                                                                                                                                                                               |

| 6                                    | $V_{DD}$         | +5V Positive Voltage Power Supply, it requires a 1.0 μF decoupling capacitor to GND                                                                                                                                                      |

| 7                                    | SCK              | Serial Peripheral Interface (SPI) clock input                                                                                                                                                                                            |

| 8                                    | CSN              | Serial Peripheral Interface (SPI) chip-select. CSN is an active-low signal.                                                                                                                                                              |

| 9                                    | SDI              | Serial Peripheral Interface (SPI) data input                                                                                                                                                                                             |

| 10                                   | SDO              | Serial Peripheral Interface (SPI) data output                                                                                                                                                                                            |

| 11, 35                               | CBE0-1           | The clock buffer enable pin. When CBEn = 0, the corresponding clock buffer is disabled. The clock buffer is enabled otherwise.                                                                                                           |

| 12, 34                               | CKB0-1           | 2.5V Single-ended Clock Buffer output pins                                                                                                                                                                                               |

| 13                                   | TXRW             | CW Transmission Control pin. When TXRW = 0, the SPI is enabled for read/write. When TXRW = 1, the SPI is disabled and the CW transmission is started.                                                                                    |

| 14, 23                               | $V_{GN}$         | -10V Negative Voltage Power Supply, it requires a 2.2 $\mu$ F capacitor to GND. The V <sub>GN</sub> supply is also the substrate and should be the most negative supply to the chip.                                                     |

| 15, 31                               | CNF              | Negative Floating Supply Bypass Capacitor pin. Connects 1 $\mu$ F/10V capacitor between this pin and the $V_{\text{CW-}}$ pin.                                                                                                           |

| 16, 30                               | V <sub>CW-</sub> | -1V to -6V Negative Voltage Power Supply for the CW output, it requires a 1.0 μF decoupling capacitor per pin to GND                                                                                                                     |

| 17, 29                               | CPF              | Positive Floating Supply Bypass Capacitor pin. Connects 1 $\mu$ F/10V capacitor between this pin and the $V_{CW+}$ pin.                                                                                                                  |

| 18, 28                               | V <sub>CW+</sub> | +1V to +6V Positive Voltage Power Supply for the CW output. It requires a 1.0 μF decoupling capacitor per pin to GND.                                                                                                                    |

| 19, 20, 21,<br>22, 24, 25,<br>26, 27 | CW0-7            | Channel 0-7 CW Waveform Output                                                                                                                                                                                                           |

| 32                                   | V <sub>GP</sub>  | +10V Positive Voltage Power Supply, it requires a 2.2 µF decoupling capacitor to GND                                                                                                                                                     |

| 36                                   | SPIB             | SPI Broadcasting Mode pin. When SPIB = 1, the broadcast mode is enabled.                                                                                                                                                                 |

| 37                                   | EP               | Exposed Thermal Pad (EP); must be connected to GND                                                                                                                                                                                       |

# **MD1730**

#### 4.0 DEVICE DESCRIPTION

## 4.1 Operation Description

The MD1730 is an 8-channel ultra-low phase noise monolithic CW transmitter. It consists of an SPI interface to program internal phase delay registers and frequency dividers to facilitate CW beamforming. It supports differential LVDS/SSTL and single-ended 2.5V LVCMOS clock inputs. The MD1730's output path is designed to provide ultra-low phase noise and can swing up to ±6V. The following sections provide a detailed overview of MD1730's feature set and operation.

# 4.2 Using The Built-in Clock Buffers

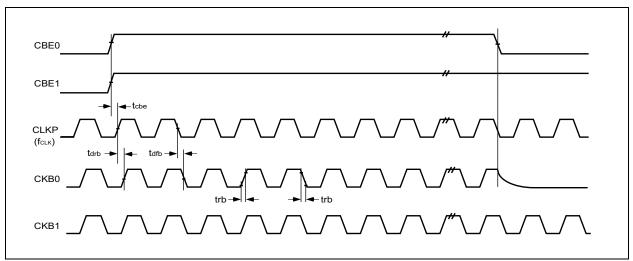

The MD1730 has two built-in single ended clock output buffers. The MD1730 can accept LVDS, SSTL25 and LVCMOS 2.5V clock at its input and provide a single-ended output buffered clock. The clock buffers are independent of the chip's main EN pin and each output clock buffer can be enabled or disabled separately using the CBE0 or CBE1 pin. The maximum clock frequency of the buffers is 250 MHz. The output timing diagram for the clock buffers is shown in Figure 4-5. As shown in the diagram CKB0 and CKB1, clock outputs are only dependent on CBE0 and CBE1 respectively. This feature makes it convenient to drive the TX pulser retiming clock input, such as the HV7321. Using the built in clock buffers will save the cost of additional buffers, reduce PCB area, simplify the system clock distribution design and improve power savings as well.

## 4.3 SPI Registers Description

#### REGISTER 4-1: SPI CONTROL REGISTER DESCRIPTION

| Data Bits               | Description                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W/R                     | The W/R is the read write control bit. When W/R = $1$ , the SPI writes the data provided at the addressed register. When W/R = $0$ , the SPI reads the data stored from the appropriate register. The read operation is disabled when SPIB = $1$ .                                                                                                                                      |

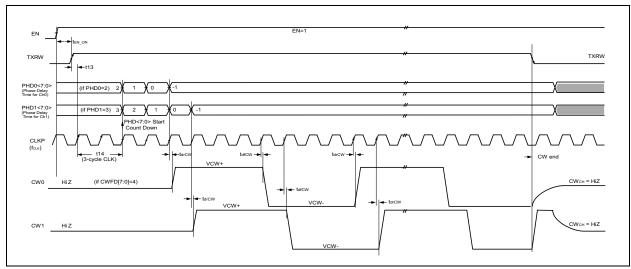

| CWFD<7:0>               | The CWFD<7:0> register stores the divisor value for setting the CW output frequency. The CW output frequency is set by using the equation ( $f_{CW} = f_{CLK}/(2*CWFD)$ ) except CWFD = 0. For CWFD = 0 the CW output frequency is $f_{CW} = f_{CLK}/2*512$ . The CW output frequency ranges from ( $f_{CLK}/512$ ) $\leq f_{CW} \leq (f_{CLK}/2)$ . The register's initial value is 0. |

| PHD <sub>CH</sub> <7:0> | $PHD_{CH}$ <7:0> sets the phase delay for each individual channel. The equation for the output delay time is $PHD$ <7:0>/ $f_{CLK}$ + $2/f_{CLK}$ once TXRW goes high. The register initial value is 0. Refer to Figure 4-4 for further details.                                                                                                                                        |

| HIZ <sub>CH</sub>       | $HIZ_{CH}$ bit enables the channel output when the corresponding bit is 0. The channel is disabled and its' output becomes high Z when the corresponding bit is 1. The default register value is 0.                                                                                                                                                                                     |

Note: CH denotes channel number 0 to 7.

REGISTER 4-2: SPI REGISTER ADDRESS AND CONTROL BITS

| W/R              | SPI Register ADD<3:0> |     |    |    |                                   | Write or Read Data <7:0> |           |           |          |         |      |      |

|------------------|-----------------------|-----|----|----|-----------------------------------|--------------------------|-----------|-----------|----------|---------|------|------|

| D12              | D11                   | D10 | D9 | D8 | D7                                | D6                       | D5        | D4        | D3       | D2      | D1   | D0   |

|                  | 0                     | 0   | 0  | 0  | 0 Channel 0 phase delay PHD0<7:0> |                          |           |           |          |         |      |      |

| 1 = Write        | 0                     | 0   | 0  | 1  | 1 Channel 1 phase delay PHD1<7:0> |                          |           |           |          |         |      |      |

| 0 = Read         | 0                     | 0   | 1  | 0  | 0 Channel 2 phase delay PHD2<7:0> |                          |           |           |          |         |      |      |

| MSB first.       | 0                     | 0   | 1  | 1  | 1 Channel 3 phase delay PHD3<7:0> |                          |           |           |          |         |      |      |

| (See             | 0                     | 1   | 0  | 0  |                                   | (                        | Channel 4 | phase d   | lelay PH | D4<7:0> |      |      |

| Section 4.3      | 0                     | 1   | 0  | 1  |                                   | (                        | Channel 5 | 5 phase d | lelay PH | D5<7:0> |      |      |

| and Section 4.4) | 0                     | 1   | 1  | 0  | Channel 6 phase delay PHD6<7:0>   |                          |           |           |          |         |      |      |

| ,                | 0                     | 1   | 1  | 1  | Channel 7 phase delay PHD7<7:0>   |                          |           |           |          |         |      |      |

|                  | 1                     | 0   | 0  | 0  | HIZ7                              | HIZ6                     | HIZ5      | HIZ4      | HIZ3     | HIZ2    | HIZ1 | HIZ0 |

|                  | 1                     | 0   | 0  | 1  |                                   | CW                       | frequenc  | y divisor | number   | CWFD<   | 7:0> |      |

**Note:** Power-On or EN = 0 sets all the registers to 0.

TABLE 4-1: PHD<7:0> PHASE DELAY TIME REGISTER DESCRIPTION

| PHD<7:0> | Delay Time to Start Transmitting      |

|----------|---------------------------------------|

| 0000000  | 0/f <sub>CLK</sub> (Power-on default) |

| 0000001  | 1/f <sub>CLK</sub>                    |

| 0000010  | 2/f <sub>CLK</sub>                    |

|          |                                       |

| 11111110 | 254/f <sub>CLK</sub>                  |

| 11111111 | 255/f <sub>CLK</sub>                  |

TABLE 4-2: CWFD<7:0> CW FREQUENCY DIVIDER REGISTER DESCRIPTION

| CWFD[7:0] | Transmit CW Frequency f <sub>CW</sub>    |

|-----------|------------------------------------------|

| 0000000   | f <sub>CLK</sub> /512 (Power-on default) |

| 0000001   | f <sub>CLK</sub> /2                      |

| 0000010   | f <sub>CLK</sub> /4                      |

| 00000011  | f <sub>CLK</sub> /6                      |

|           |                                          |

| 11111110  | f <sub>CLK</sub> /508                    |

| 11111111  | f <sub>CLK</sub> /510                    |

**Note:** The selected CW frequency is same for all the CW0~7 outputs:  $f_{CW} = f_{CLK}/2*CWFD$ . The CW frequency applies to all channels.

# 4.4 Serial Peripheral Interface (SPI)

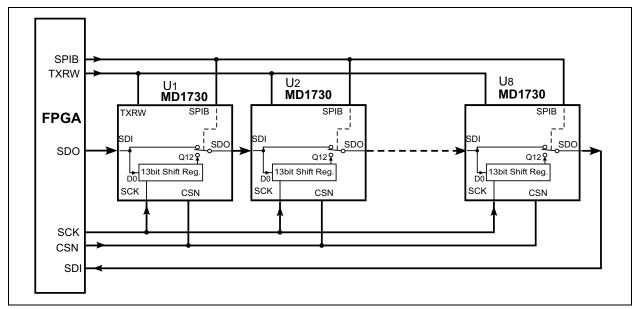

The MD1730's SPI is used to program the phase delay and frequency divider registers. The SPI supports writing at speed up to 200 MHz and the MSB is shifted in first. SPI interface supports two operating modes: daisy chain mode and broadcasting mode.

When SPIB = 0, the MD1730 is in daisy chain mode. In this mode, it supports both read and write operations.

When SPIB = 1 the chip enters the "Broadcasting" mode. In this mode, the SDI data shifts into the shift register as well as to the SDO output. In this mode, the user can write the same register of different daisy chained chips with the same value in a single write

transaction. However, when SPIB = 1 the read operation is disabled. To verify the written data for each chip, the user can revert SPIB = 0 and perform a normal read operation.

#### 4.4.1 SPI WRITE OPERATION EXAMPLES

The following is a 1-byte writing example for the register at ADD = 0011b with the data D<7:0> = 01010101 when SPIB = TXRW = 0.

- The Write operation starts with setting CSN to low.

- 2. The SCK clock is used to shift in the following SDI data:

D12 = 1, W/R bit set equal to high for write operation.

ADD<11:8> = 0011b, address for channel-3's phase delay register.

D<7:0> = 01010101b, data to be written into channel-3's phase delay register.

The SDI data is shifted in at the rising edge of SCK.

3. Once the complete data has been shifted in, the CSN should be taken high to finish the writing operation. The SDI data is latched into channel-3's phase delay register on the rising edge of the CSN signal. CSN has to be kept high for a minimum of 2-SCK cycles for the data to be written into the appropriate register.

In the case of eight chips daisy chained together as shown in Figure 4-3, there should be  $13 \times 8 = 104$  cycles of SCK before the CSN is taken high.

The MD1730 can also be used in the Broadcasting mode to write several daisy chained chips with the same data. The Broadcasting mode can be used to reduce the time required to write the SPI if several MD1730 chips need the same data. The following is a 1-byte writing example for the register at the address location ADD = 0011b with data D<7:0> =01010101b while the MD1730 is set to broadcasting mode.

- The write operation starts with setting CSN to low with TXRW = 0 and SPIB = 1.

- The SCK clock is used to shift in the following SDI data to the first MD1730 chip:

D12 = 1, W/R bit set equal to high for write operation.

ADD<11:8> = 0011b, address for the channel-3's phase delay register.

D<7:0> = 01010101, data to be written into the channel-3's phase delay register.

The SDI data is shifted in at the rising edge of SCK.

In Broadcasting mode, the same set of data shifted into the first chip's SDI is sent to all the MD1730 chips along the daisy chain. As shown is Figure 4-3 when SPIB = 1 an internal switch connects the SDI and SDO directly.

3. Once the complete data has been shifted in, the CSN should be taken high to finish the writing operation. The SDI data is latched into each chip's channel-3 phase delay register on the rising edge of the CSN signal. CSN has to be kept high for a minimum of 2-SCK cycles for the data to be written into the appropriate register.

#### 4.4.2 SPI READ OPERATION EXAMPLES

The following is a 2-byte reading example from the register at ADD = 0011b (Channel-3's phase delay register) when SPIB = TXRW = 0.

- The read operation starts with setting CSN to low.

- The SCK clock is used to shift in the following SDI data:

D12 = 0, W/R bit set equal to high for read operation.

ADD<11:8> = 0011b, address for channel-3's phase delay register.

D<7:0> = x, for a Read operation the data field is don't' care.

The SDI data is shifted in at the rising edge of SCK.

- Once the complete data has been shifted into the SPI the CSN is taken high. While CSN is high the MD1730 fetches the data located at ADD<11:9> = 0011b and places it in its internal shift register.

- 4. Once the complete data has been shifted in, the CSN should be taken high to finish the reading operation. While CSN is high the MD1730 fetches the data located at ADD<11:9> = 0011b and places it in its internal shift register. CSN has to be kept high for a minimum of 2-SCK cycles for the data to be fetched and placed into the internal shift register.

- The CSN is taken low and during the next 13 SCK clock cycles, the fetched data in the internal shift register is clocked out on the rising edge of SCK from the SDO of the MD1730.

FIGURE 4-1: SPI Register Read/Write Timing with SPIB = 0, TXRW = 0.

FIGURE 4-2: SPI Register Broadcasting Write Timing with SPIB = 1, TXRW = 0.

**Note:** When in SPIB = 1 mode, the SPI register READ operations are not available.

FIGURE 4-3: Multiple MD1730 Devices SPI Daisy Chain Connections.

#### 4.5 CW0~7 Output Timing

The CW output waveform transmission timing is crucial to an ultrasound imaging system. Any small timing variations on the output can degrade the phase noise performance. The MD1730's internal circuitry is designed to ensure ultra-low phase noise. Figure 4-4 shows an example of the output waveform timing diagram. The chip is enabled by taking the EN pin high. Then using the SPI, channel-0's and channel-1's phase delay registers (PHD0<7:0> and PHD1<7:0>) are programmed with delays of 2 and 3 respectively. The rest of the channels are set to a high impedance state by programming the HIZ<7:0> register with data 11111100b. Furthermore, the frequency divider register (CWFD<7:0>) is set to 4. After completing the SPI operation the transmission starts by asserting

TXRW high. The phase delay counter starts counting down after a two CLK cycle latency. This is illustrated in Figure 4-4 for channel 0 and channel 1. In channel 0's case, the phase delay starts counting down from 2 to 0 after the latency and once the delay reaches 0 on the next rising edge of CLK, the positive output appears on the pin CW0. Based on the value of the CWFD<7:0> register, after 4-CLK cycles the CW0 output toggles to the negative supply rail. Subsequently, after 4-CLK cycles at the negative rail, the output switches back again to the positive supply rail, completing one full CW output wave cycle. This process continues until the TXRW pin deasserts low, which shuts the transmission off and forces the channel into a high impedance state. This same procedure applies to channel 1, which is also depicted in Figure 4-4.

FIGURE 4-4: CW0~7 Output Timing Diagram.

FIGURE 4-5: Clock Buffers CKB0/1 Output Timing Diagram.

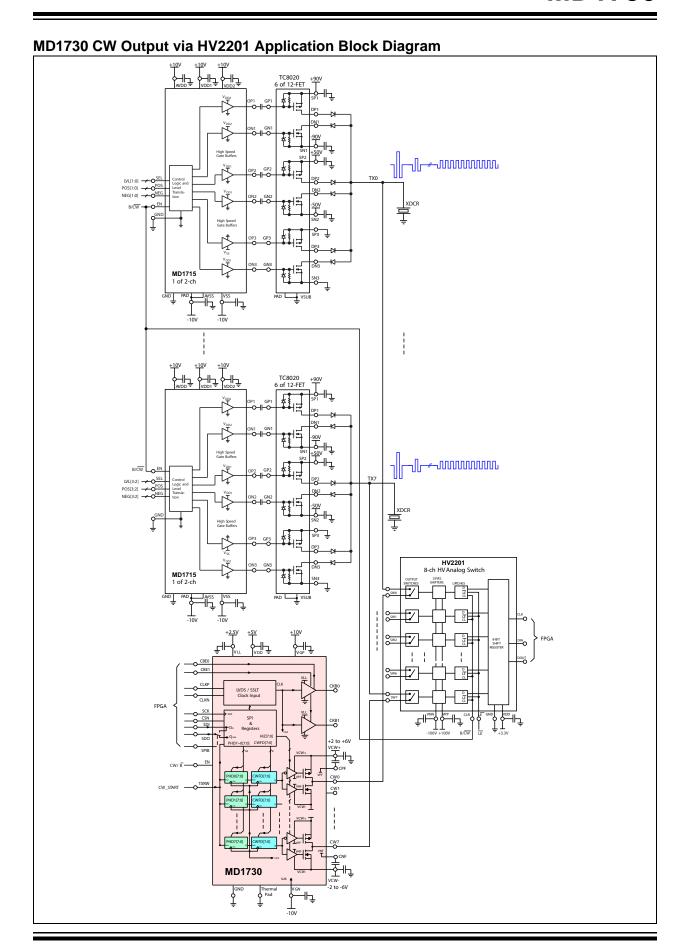

# 4.6 MD1730 Working with Two HV7321

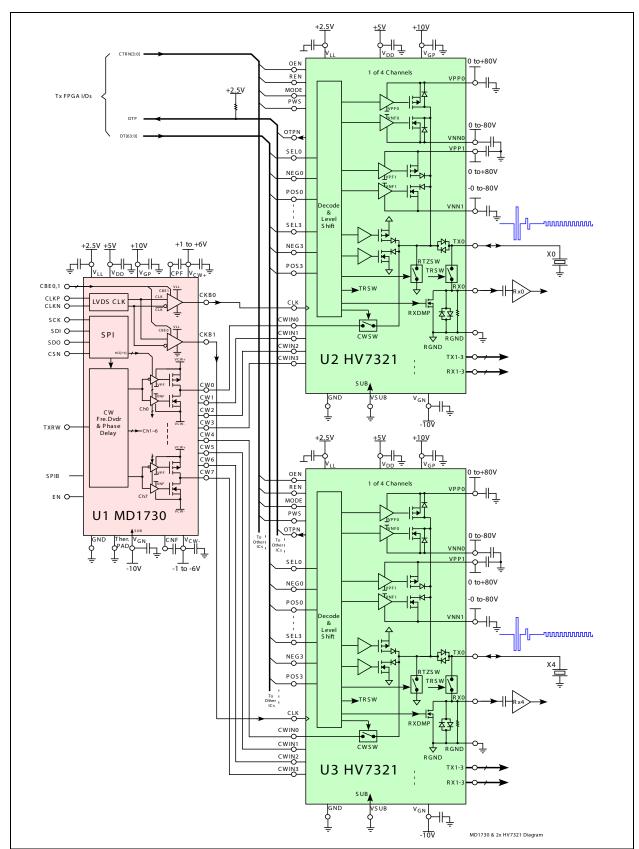

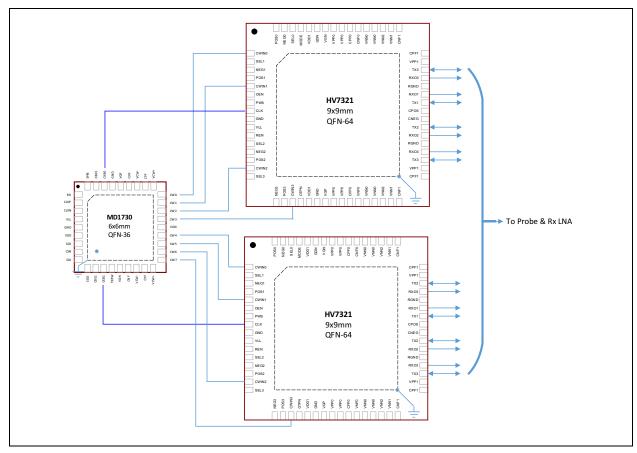

The diagrams shown in Figure 4-6 and Figure 4-7 illustrate the MD1730 driving two HV7321s.

When the HV7321 is operated in the specific mode, CW MODE = 1, along with the MD1730, the following steps should be taken to ensure the combination settings work correctly:

- Apply all power supply rails to both chips and set HV7321's OEN = REN = PWS = 1 along with MD1730's EN = 1 to enable both chips. Set all other control logic pins to zero.

- 7. Adjust the VCW+ and VCW- power supplies to the required peak-to-peak voltage levels for CW output transmission. Please note that a higher peak-to-peak transmission voltage will result in the MD1730 dissipating more power. The power dissipation on the MD1730 is proportional to the square of the peak-to-peak voltage.

- 8. Assert HV7321's MODE pin high.

- Program the MD1730 with the desired CW frequency divider and delay settings for CW transmission.

- 10. To place a channel in receive mode, set the corresponding pins SEL, NEG, POS = 011b on the HV7321. To place a channel to CW Transmit mode, set the corresponding pins SEL, NEG, POS to any other combination other than 011b on HV7321. This will put that channel of the HV7321 high voltage Tx output in High Z mode, but turn the channel's CWSW on.

In the case user wants a channel not in High Z or CW Transmit mode, then similarly, to set the channel of HV7321 to High Z and also set the MD1730's corresponding bit in the HIZ register to 1.

Once the system is ready to perform CW

Doppler measurement, assert TXRW high to

start the CW transmission on the selected

channels.

FIGURE 4-6: MD1730 Works with Two HV7321 4-Channel ±80V 2.6A 5-Level Ultrasound Pulsers.

FIGURE 4-7: MD1730 Working with Two HV7321 Pulsers Pinout and Package.

#### 4.7 CW Transmission Clock

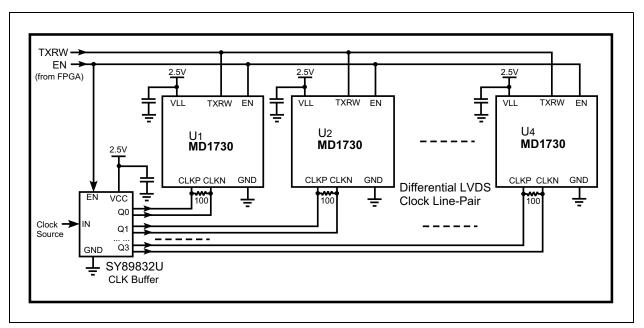

The input clock of the MD1730, used for CW transmission, can be connected either differentially or single-ended. Figure 4-8 shows the LVDS differential implementation for the transmission clock. Here the CLKP and the CLKN pins are directly driven by a LVDS clock buffer. It is highly recommended that a multiple-output LVDS clock buffer IC is used, such as the SY89832U, and that a  $100\Omega$  termination resistor is placed very close to the CLKP and CLKN pins. For successful transmission of the LVDS signal over differential traces, the following guidelines should be followed while laying out the PCB board:

- To ensure minimal reflections and to maintain the receiver's common-mode noise rejection, keep the differential traces as short as possible between the clock buffer IC and the CLKP/CLKN pins of the MD1730.

- To reduce skew, the electrical lengths between differential LVDS traces should be identical. The arrival of one differential signal before the other will create a phase difference between the signal pairs, which would create clock skew and impair the system performance.

- · Minimize the number of vias or other

- discontinuities in the signal path. To avoid discontinuities, arcs or 45-degree traces are recommended instead of 90-degree turns.

- Any parasitic loading, such as capacitance, must be present in equal amounts on each differential line.

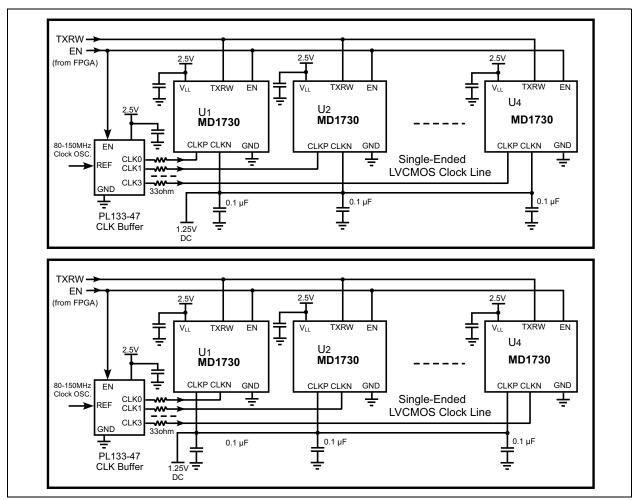

Figure 4-9 illustrates the two cases for the MD1730 used in a single-ended configuration. In these cases, one of the clock input pins, CLKP or CLKN, is connected to the  $V_{LL}/2$  voltage level and bypassed to ground with a 0.1 uF bypass capacitor. Each bypass capacitor must be placed very close to the MD1730. The other clock input pin connects to the main clock line. The PCB traces on the clock line must be designed for a  $50\Omega$  impedance with respect to the PCB ground place. Also, the clock pin must be terminated with a small  $50\Omega$  SMT resistor.

Generally, the LVCMOS input configuration provides better CW phase noise performance due to its higher amplitude swing as compared to the LVDS configuration. However, if the user needs a very high frequency clock transmission, such as 160 MHz-240 MHz range for a higher phase delay resolution, then LVDS should be used because it provides a better PCB clock trace distribution.

FIGURE 4-8: LVDS Differential Transmission Clock.

FIGURE 4-9: LVCMOS Single-Ended Transmission Clock.

# **MD1730**

## 5.0 PACKAGING INFORMATION

# 5.1 Package Marking Information

36-Lead VQFN (6x6x0.9 mm)

Example

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

e3 Pb-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (@3)

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

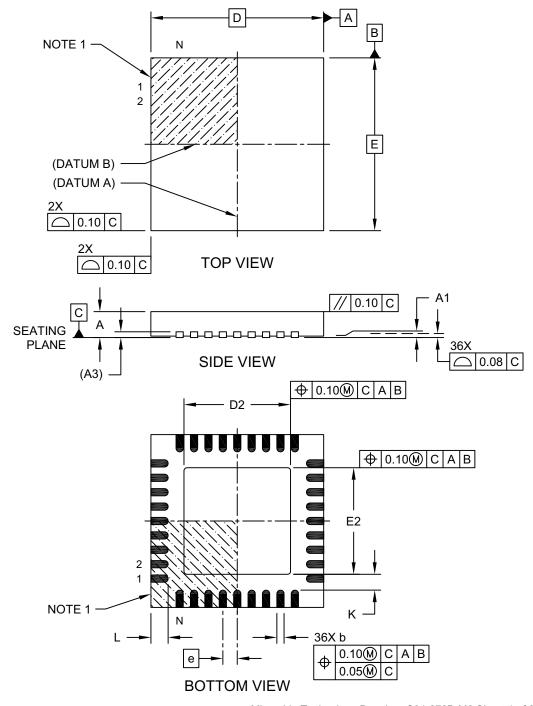

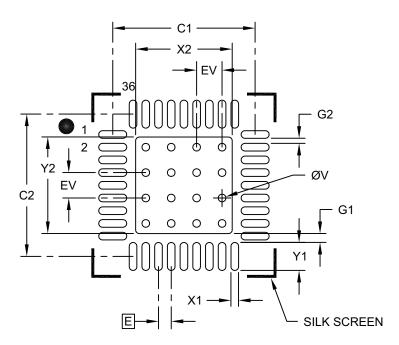

# 36-Terminal Very Thin Plastic Quad Flatpack No-Lead (M2) - 6x6x1.0mm Body [VQFN] SMSC Legacy "Sawn Quad Flatpack No-Lead [SQFN]"

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-272B-M2 Sheet 1 of 2

# 36-Terminal Very Thin Plastic Quad Flatpack No-Lead (M2) - 6x6x1.0mm Body [VQFN] SMSC Legacy "Sawn Quad Flatpack No-Lead [SQFN]"

**lote:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  |                |          |      |  |

|-------------------------|--------|----------------|----------|------|--|

| Dimension               | Limits | MIN            | NOM      | MAX  |  |

| Number of Terminals     | N      | 36             |          |      |  |

| Pitch                   | е      |                | 0.50 BSC |      |  |

| Overall Height          | Α      | 0.80 0.90 1.00 |          |      |  |

| Standoff                | A1     | 0.00           | 0.02     | 0.05 |  |

| Terminal Thickness      | A3     | 0.20 REF       |          |      |  |

| Overall Width           | Е      | 6.00 BSC       |          |      |  |

| Exposed Pad Width       | E2     | 3.60           | 3.70     | 3.80 |  |

| Overall Length          | D      | 6.00 BSC       |          |      |  |

| Exposed Pad Length      | D2     | 3.60           | 3.70     | 3.80 |  |

| Terminal Width          | b      | 0.18           | 0.25     | 0.30 |  |

| Terminal Length         | L      | 0.50           | 0.60     | 0.75 |  |

| Terminal-to-Exposed-Pad | K      | 0.45           | 0.55     | -    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-272B-M2 Sheet 2 of 2

# 36-Terminal Very Thin Plastic Quad Flatpack No-Lead (M2) - 6x6x0.9 mm Body [VQFN] SMSC Legacy "Sawn Quad Flatpack No-Lead [SQFN]"

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                                  | MILLIMETERS |      |          |      |

|----------------------------------|-------------|------|----------|------|

| Dimension                        | MIN         | NOM  | MAX      |      |

| Contact Pitch                    | Е           |      | 0.50 BSC |      |

| Optional Center Pad Width        | X2          |      |          | 3.80 |

| Optional Center Pad Length       | Y2          |      |          | 3.80 |

| Contact Pad Spacing              | C1          |      | 5.60     |      |

| Contact Pad Spacing              | C2          |      | 5.60     |      |

| Contact Pad Width (X36)          | X1          |      |          | 0.30 |

| Contact Pad Length (X36)         | Y1          |      |          | 1.10 |

| Contact Pad to Center Pad (X36)  | G1          | 0.35 |          |      |

| Space Between Contact Pads (X32) | G2          | 0.20 |          |      |

| Thermal Via Diameter             | V           |      | 0.30     |      |

| Thermal Via Pitch                | EV          |      | 1.00     |      |

#### Notes:

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2272B-M2

# APPENDIX A: REVISION HISTORY

# **Revision B (November 2016)**

The following is the list of modifications:

- Updated Section "Product Identification System".

- Minor typographical corrections.

# **Revision A (September 2016)**

• Original Release of this Document.

# **MD1730**

# PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, contact your local Microchip sales office.

[X]<sup>(1)</sup> PART NO. <u>/XX</u> **Examples: Device** Tape and Reel Temperature Package Programmable High-Voltage Ultrasound-Transmit Beamformer, MD1730-V/M2: Option Range 36LD 6x6 mm VQFN package MD1730T-V/M2: Tape and Reel, b) Device: MD1730: Programmable High-Voltage, Programmable High-Voltage Ultrasound-Transmit Beamformer Ultrasound-Transmit Beamformer, 36LD 6x6 mm VQFN package MD1730T: Programmable High-Voltage, Ultrasound-Transmit Beamformer (Tape and Reel) Note 1: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check Temperature Range: V 0°C to +85°C with your Microchip Sales Office for package availability with the Tape and Reel option. = Very Thin Plastic Quad Flat Pack, No-Lead Package: M2 Package – 6x6x1.0 mm Body, 36-Lead (VQFN)

# **MD1730**

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### **Trademarks**

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-1067-6

# Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/support

Web Address: www.microchip.com

Atlanta Duluth, GA

Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX

Tel: 281-894-5983 Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York. NY

Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong

Tel: 852-2943-5100 Fax: 852-2401-3431

**Australia - Sydney** Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Dongguan** Tel: 86-769-8702-9880

**China - Guangzhou** Tel: 86-20-8755-8029

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-3326-8000 Fax: 86-21-3326-8021

**China - Shenyang** Tel: 86-24-2334-2829

Fax: 86-24-2334-2393 China - Shenzhen

Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

**India - Pune** Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

**Korea - Seoul** Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

**Malaysia - Kuala Lumpur** Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

**Austria - Wels** Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

France - Saint Cloud Tel: 33-1-30-60-70-00

**Germany - Garching** Tel: 49-8931-9700 **Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-67-3636

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7289-7561

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820