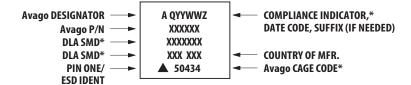

# HCPL-5300, HCPL-5301, HCPL-530K, 5962-96852

Intelligent Power Module and Gate Drive Interface Hermetically Sealed Optocouplers

## **Data Sheet**

#### **Description**

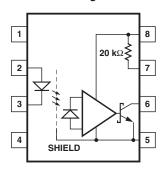

The HCPL-530X devices consist of a GaAsP LED optically coupled to an integrated high gain photo detector in a hermetically sealed package. The products are capable of operation and storage over the full military temperature range and can be purchased as either standard product or with full MIL-PRF-38534 Class Level H or K testing or from the DLA Drawing 5962-96852. All devices are manufactured and tested on a MIL-PRF-38534 certified line and are included in the DLA Qualified Manufacturers List QML-38534 for Hybrid Microcircuits. Minimized propagation delay difference between devices make these optocouplers excellent solutions for improving inverter efficiency through reduced switching dead time. An on chip 20 k $\Omega$  output pull-up resistor can be enabled by shorting output pins 6 and 7, thus eliminating the need for an external pull-up resistor in common IPM applications. Specifications and performance plots are given for typical IPM applications.

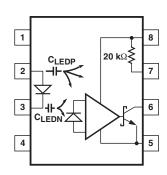

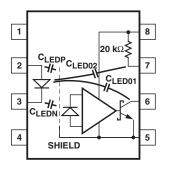

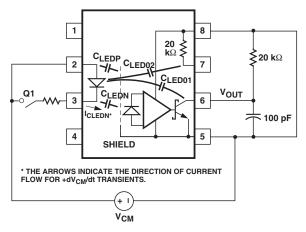

### **Schematic Diagram**

**Truth Table**

| LED | V <sub>0</sub> |

|-----|----------------|

| ON  | L              |

| OFF | Н              |

#### **Features**

- Performance specified over full military temperature Range: -55° C to +125° C

- Fast maximum propagation delays t<sub>PHL</sub> = 450 ns, t<sub>PLH</sub> = 650 ns

- Minimized pulse width distortion (PWD = 450 ns)

- High common mode rejection (CMR):  $10 \, kV/\mu s$  at  $V_{CM} = 1000 \, V$

- CTR > 30% at I<sub>F</sub> = 10 mA

- 1500 Vdc withstand test voltage

- Manufactured and tested on a MIL-PRF-38534 certified line

- Hermetically sealed packages

- Dual marked with device part number and DLA drawing number

- QML-38534, Class H and K

- HCPL-4506 function compatibility

#### **Applications**

- Military and space

- High reliability systems

- Harsh industrial environments

- Transportation, medical, and life critical systems

- IPM isolation

- Isolated IGBT/MOSFET gate drive

- · AC and brushless DC motor drives

- Industrial inverters

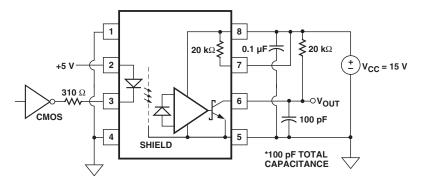

The connection of a 0.1  $\mu$ F bypass capacitor between pins 5 and 8 is recommended.

**CAUTION:** It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.

## **Selection Guide-Lead Configuration Options**

| Avago Part # and Options |             |

|--------------------------|-------------|

| Commercial               | HCPL-5300   |

| MIL-PRF-38534, Class H   | HCPL-5301   |

| MIL-PRF-38534, Class K   | HCPL-530K   |

| Standard Lead Finish     | Gold Plate  |

| Solder Dipped*           | Option #200 |

| Butt Cut/Gold Plate      | Option #100 |

| Gull Wing/Soldered*      | Option #300 |

| Class H SMD Part #       |             |

| Prescript for all below  | 5962-       |

| Gold Plate               | 9685201HPC  |

| Solder Dipped*           | 9685201HPA  |

| Butt Cut/Gold Plate      | 9685201HYC  |

| Butt Cut/Soldered*       | 9685201HYA  |

| Gull Wing/Soldered*      | 9685201HXA  |

| Class K SMD Part #       |             |

| Prescript for all below  | 5962-       |

| Gold Plate               | 9685201KPC  |

| Solder Dipped*           | 9685201KPA  |

| Butt Cut/Gold Plate      | 9685201KYC  |

| Butt Cut/Soldered*       | 9685201KYA  |

| Gull Wing/Soldered*      | 9685201KXA  |

|                          |             |

<sup>\*</sup>Solder contains lead.

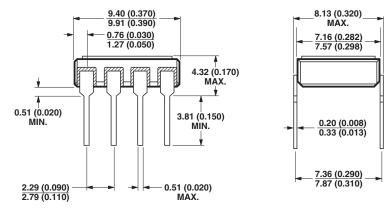

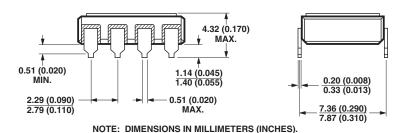

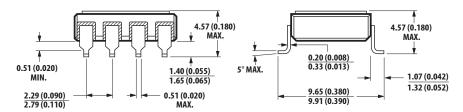

# **Outline Drawing**

NOTE: DIMENSIONS IN MILLIMETERS (INCHES).

### **Device Marking**

#### **Hermetic Optocoupler Options**

#### Option Description

Surface mountable hermetic optocoupler with leads trimmed for butt joint assembly. This option is available on commercial and hi-rel product in 8 pin DIP (see drawings below for details).

Lead finish is solder dipped rather than gold plated. This option is available on commercial and hi-rel product in 8 pin DIP. DLA Drawing part numbers contain provisions for lead finish.

Surface mountable hermetic optocoupler with leads cut and bent for gull wing assembly. This option is available on commercial and hi-rel product in 8 pin DIP (see drawings below for details). This option has solder dipped leads.

NOTE: DIMENSIONS IN MILLIMETERS (INCHES).

Note: Solder contains lead.

# **Absolute Maximum Ratings**

| Storage Temperature  Operating Temperature                    | T <sub>S</sub>       | -65  | +150            | °C |

|---------------------------------------------------------------|----------------------|------|-----------------|----|

| Operating Temperature                                         | TA                   |      |                 | -  |

| operating remperature                                         |                      | -55  | +125            | °C |

| Junction Temperature                                          | Tj                   |      | +175            | °C |

| Lead Solder Temperature                                       |                      |      | 260 for 10 sec  | °C |

| Average Input Current                                         | I <sub>F(AVG)</sub>  |      | 25              | mA |

| Peak Input Current<br>(50% duty cycle, ≤ 1 μs pulse width)    | I <sub>F(PEAK)</sub> |      | 50              | mA |

| Peak Transient Input Current<br>(≤ 1 µs pulse width, 300 pps) |                      |      | 1.0             | А  |

| Reverse Input Voltage (Pin 3-2)                               | V <sub>R</sub>       |      | 5               | V  |

| Average Output Current (Pin 6)                                | I <sub>O(AVG)</sub>  |      | 15              | mA |

| Resistor Voltage (Pin 7)                                      | V <sub>7</sub>       | -0.5 | V <sub>CC</sub> | V  |

| Output Voltage (Pin 6-5)                                      | Vo                   | -0.5 | 30              | V  |

| Supply Voltage (Pin 8-5)                                      | V <sub>CC</sub>      | -0.5 | 30              | V  |

| Output Power Dissipation                                      | Po                   |      | 100             | mW |

| Total Power Dissipation                                       | P <sub>T</sub>       |      | 145             | mW |

## **ESD Classification**

| (MIL-STD-883, Method 3015) | ( <b>△</b> ), Class 1 |

|----------------------------|-----------------------|

|----------------------------|-----------------------|

# **Recommended Operating Conditions**

| Parameter            | Symbol              | Min. | Max. | Units |

|----------------------|---------------------|------|------|-------|

| Power Supply Voltage | V <sub>CC</sub>     | 4.5  | 30   | Volts |

| Output Voltage       | Vo                  | 0    | 30   | Volts |

| Input Current (ON)   | I <sub>F(ON)</sub>  | 10   | 20   | mA    |

| Input Voltage (OFF)  | V <sub>F(OFF)</sub> | -5   | 0.8  | V     |

## **Electrical Specifications**

Over recommended operating conditions ( $T_A = -55^{\circ}$  C to +125° C,  $V_{CC} = +4.5$  V to 30 V,  $I_{F(ON)} = 10$  mA to 20 mA,  $V_{F(OFF)} = -5$  V to 0.8 V) unless otherwise specified.

| Parameter                                            | Symbol                  | Group A Subgroups <sup>[12]</sup> | Min. | Тур.* | Max. | Units | Test Conditions                                                                        | Fig. | Note    |

|------------------------------------------------------|-------------------------|-----------------------------------|------|-------|------|-------|----------------------------------------------------------------------------------------|------|---------|

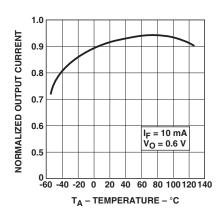

| Current Transfer Ratio                               | CTR                     | 1, 2, 3                           | 30   | 90    |      | %     | I <sub>F</sub> = 10 mA,<br>V <sub>O</sub> = 0.6 V                                      |      | 1       |

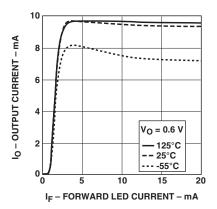

| Low Level Output<br>Current                          | I <sub>OL</sub>         | 1, 2, 3                           | 3.0  | 9.0   |      | mA    | I <sub>F</sub> = 10 mA,<br>V <sub>O</sub> = 0.6 V                                      | 1, 2 |         |

| Low Level Output<br>Voltage                          | V <sub>OL</sub>         | 1, 2, 3                           |      | 0.3   | 0.6  | V     | I <sub>O</sub> = 2.4 mA                                                                |      |         |

| Input Threshold<br>Current                           | I <sub>TH</sub>         | 1, 2, 3                           |      | 1.5   | 5.0  | mA    | $V_O = 0.8 \text{ V},$<br>$I_O = 0.75 \text{ mA}$                                      | 1    | 7       |

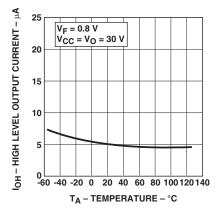

| High Level Output<br>Current                         | I <sub>OH</sub>         | 1, 2, 3                           |      | 5     | 75   | μΑ    | V <sub>F</sub> = 0.8 V                                                                 | 3    |         |

| High Level Supply<br>Current                         | I <sub>CCH</sub>        | 1, 2, 3                           |      | 0.6   | 1.5  | mA    | $V_F = 0.8 V$ ,<br>$V_O = Open$                                                        |      | 7       |

| Low Level Supply<br>Current                          | I <sub>CCL</sub>        | 1, 2, 3                           |      | 0.6   | 1.5  | mA    | I <sub>F</sub> = 10 mA,<br>V <sub>O</sub> = Open                                       |      | 7       |

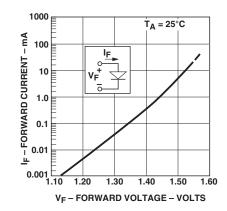

| Input Forward Voltage                                | V <sub>F</sub>          | 1, 2, 3                           | 1.0  | 1.5   | 1.8  | V     | I <sub>F</sub> = 10 mA                                                                 | 4    |         |

| Temperature Coefficient of Forward Voltage           | $\Delta V_F/\Delta T_A$ |                                   |      | -1.6  |      | mV/°C | I <sub>F</sub> = 10 mA                                                                 |      |         |

| Input Reverse<br>Breakdown Voltage                   | BV <sub>R</sub>         | 1, 2, 3                           | 5    |       |      | V     | $I_R = 100 \mu A$                                                                      |      |         |

| Input Capacitance                                    | C <sub>IN</sub>         |                                   |      | 90    |      | pF    | $f = 1 MHz$ , $V_F = 0 V$                                                              |      |         |

| Input-Output Insulation<br>Leakage Current           | I <sub>I-O</sub>        | 1                                 |      |       | 1.0  | μΑ    | RH $\leq$ 65%,<br>t = 5 sec,<br>V <sub>I-O</sub> = 1500 Vdc,<br>T <sub>A</sub> = 25° C |      | 2       |

| Resistance<br>(Input-Output)                         | R <sub>I-O</sub>        |                                   |      | 1012  |      | Ω     | V <sub>I-O</sub> = 500 Vdc                                                             |      | 2       |

| Capacitance<br>(Input-Output)                        | C <sub>I-O</sub>        |                                   |      | 2.4   |      | pF    | f = 1 MHz                                                                              |      | 2       |

| Internal Pull-up Resistor                            | R <sub>L</sub>          | 1                                 | 14   | 20    | 28   | kΩ    | T <sub>A</sub> = 25° C                                                                 |      | 4, 5, 6 |

| Internal Pull-up Resistor<br>Temperature Coefficient | $\Delta R_L/\Delta T_A$ |                                   |      | 0.014 |      | kΩ/°C |                                                                                        |      |         |

<sup>\*</sup>All typical values at 25° C,  $V_{CC} = 15 \text{ V}$ .

## Switching Specifications ( $R_L$ = 20 $k\Omega$ External)

Over recommended operating conditions: ( $T_A = -55^{\circ}$  C to  $+125^{\circ}$  C,  $V_{CC} = +4.5$  V to 30 V,  $I_{F(ON)} = 10$  mA to 20 mA,  $V_{F(OFF)} = -5$  V to 0.8 V) unless otherwise specified.

|                                                          |                                    | Group A                  |      |       |      |       |                                                |                                                                                             |                  |          |

|----------------------------------------------------------|------------------------------------|--------------------------|------|-------|------|-------|------------------------------------------------|---------------------------------------------------------------------------------------------|------------------|----------|

| Parameter                                                | Symbol                             | Subgrps. <sup>[12]</sup> | Min. | Typ.* | Max. | Units | Test Conditions                                |                                                                                             | Fig.             | Note     |

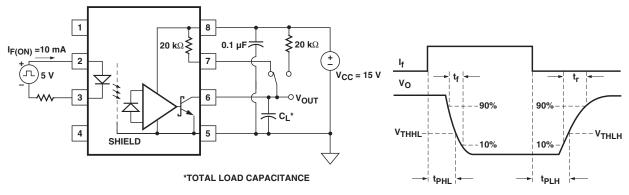

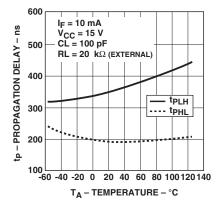

| Propagation Delay                                        | t <sub>PHL</sub>                   | 9, 10, 11                | 30   | 180   | 450  | ns    | $C_L = 100 \text{ pF}$                         | $I_{F(on)} = 10 \text{ mA},$<br>$V_{F(off)} = 0.8 \text{ V},$<br>$V_{CC} = 15.0 \text{ V},$ | 5, 7,            | 3, 4, 5, |

| Time to Low<br>Output Level                              |                                    |                          |      | 100   |      | ns    | C <sub>L</sub> = 10 pF                         |                                                                                             | 9-12             | 6, 7     |

| Propagation Delay                                        | t <sub>PLH</sub>                   | 9, 10, 11                | 250  | 350   | 650  | ns    | C <sub>L</sub> = 100 pF                        | $V_{THLH} = 2.0 V,$                                                                         |                  |          |

| Time to High<br>Output Level                             |                                    |                          |      | 130   |      |       | C <sub>L</sub> = 10 pF                         | V <sub>THHL</sub> = 1.5 V                                                                   |                  |          |

| Pulse Width<br>Distortion                                | PWD                                | 9, 10, 11                |      | 150   | 450  | ns    | C <sub>L</sub> = 100 pF                        |                                                                                             |                  | 11       |

| Propagation Delay<br>Difference Between<br>Any Two Parts | t <sub>PLH</sub> -t <sub>PHL</sub> | 9, 10, 11                | -170 | 140   | 500  | ns    |                                                |                                                                                             |                  | 8        |

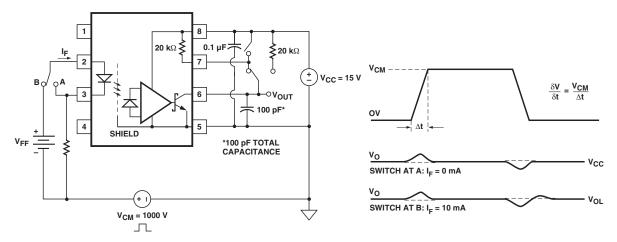

| Output High Level<br>Common Mode<br>Immunity Transient   | CM <sub>H</sub>                    | 9                        | 10   | 17    |      | kV/μs | $I_F = 0 \text{ mA},$<br>$V_O > 3.0 \text{ V}$ | $V_{CC} = 15.0 \text{ V},$ $C_L = 100 \text{ pF},$ $V_{CM} = 1000 \text{ V}_{P-P}$          | 6, 17,<br>18, 21 | 9, 13    |

| Output Low Level<br>Common Mode<br>Transient Immunity    | CM <sub>L</sub>                    | 9                        | 10   | 17    |      | kV/μs | $I_F = 10 \text{ mA}$<br>$V_O < 1.0 \text{ V}$ | T <sub>A</sub> = 25° C                                                                      |                  | 10, 13   |

<sup>\*</sup>All typical values at 25° C,  $V_{CC} = 15 \text{ V}$ .

#### Switching Specifications ( $R_L$ = Internal Pull-up)

Over recommended operating conditions: ( $T_A = -55^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{CC} = +4.5$  V to 30 V,  $I_{F(ON)} = 10$  mA to 20 mA,  $V_{F(OFF)} = -5$  V to 0.8 V) unless otherwise specified.

| Parameter                                                | Symbol                             | Group A<br>Subgrps. <sup>[12]</sup> | Min. | Тур.* | Max. | Units            | Test Conditions                                                                             | Fig.        | Note             |

|----------------------------------------------------------|------------------------------------|-------------------------------------|------|-------|------|------------------|---------------------------------------------------------------------------------------------|-------------|------------------|

| Propagation Delay<br>Time to Low<br>Output Level         | t <sub>PHL</sub>                   | 9, 10, 11                           | 20   | 185   | 500  | ns               | $I_{F(on)} = 10 \text{ mA},$<br>$V_{F(off)} = 0.8 \text{ V},$<br>$V_{CC} = 15.0 \text{ V},$ | 5, 8,       | 3, 4, 5,<br>6, 7 |

| Propagation Delay<br>Time to High<br>Output Level        | t <sub>PLH</sub>                   | 9, 10, 11                           | 220  | 415   | 750  | ns               | C <sub>L</sub> = 100 pF,<br>V <sub>THLH</sub> = 2.0 V<br>V <sub>THHL</sub> = 1.5 V          |             |                  |

| Pulse Width Distortion                                   | PWD                                | 9, 10, 11                           |      | 150   | 600  | ns               |                                                                                             |             | 11               |

| Propagation Delay<br>Difference Between<br>Any Two Parts | t <sub>PLH</sub> -t <sub>PHL</sub> | 9, 10, 11                           | -225 | 150   | 650  | ns               |                                                                                             |             | 8                |

| Output High Level<br>Common Mode<br>Transient Immunity   | CM <sub>H</sub>                    |                                     |      | 10    |      | kV/μs            |                                                                                             | 6, 21<br>-P | 9                |

| Output Low Level<br>Common Mode<br>Transient Immunity    | CM <sub>L</sub>                    |                                     |      | 10    |      | kV/μs            | I <sub>F</sub> = 16 mA<br>V <sub>O</sub> < 1.0 V                                            |             | 10               |

| Power Supply<br>Rejection                                | PSR                                |                                     |      | 1.0   |      | V <sub>P-P</sub> | Square Wave, t <sub>RISE</sub> , t <sub>FALL</sub> > 5 r<br>no bypass capacitors.           | ıs,         | 7                |

<sup>\*</sup>All typical values at  $25^{\circ}$  C,  $V_{CC} = 15$  V.

#### Notes:

- 1. CURRENT TRANSFER RATIO in percent is defined as the ratio of output collector current (I<sub>O</sub>) to the forward LED input current (I<sub>F</sub>) times 100.

- 2. Device considered a two-terminal device: Pins 1, 2, 3 and 4 shorted together and Pins 5, 6, 7 and 8 shorted together.

- 3. Pulse: f = 20 kHz, Duty Cycle = 10%

- 4. The internal 20  $k\Omega$  resistor can be used by shorting pins 6 and 7 together.

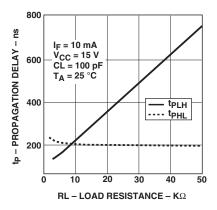

- 5. Due to the tolerance of the internal resistor, and since propagation delay is dependent on the load resistor value, performance can be improved by using an external 20 k $\Omega$  1% load resistor. For more information on how propagation delay varies with load resistance, see Figure 8.

- 6. The  $R_L = 20 \text{ k}\Omega$ ,  $C_L = 100 \text{ pF}$  represents a typical IPM (Intelligent Power Module) load.

- 7. Use of a 0.1 µF bypass capacitor connected between pins 5 and 8 can improve performance by filtering power supply line noise.

- 8. The difference in t<sub>PLH</sub> and t<sub>PHL</sub> between any two parts under the same test condition. (See IPM Dead Time and Propagation Delay Specifications

- 9. Common mode transient immunity in a Logic High level is the maximum tolerable dV<sub>CM</sub>/dt of the common mode pulse, V<sub>CM</sub>, to assure that the output will remain in a Logic High state (i.e., V<sub>O</sub> > 3.0 V).

- 10. Common mode transient immunity in a Logic Low level is the maximum tolerable  $dV_{CM}/dt$  of the common mode pulse,  $V_{CM}$ , to assure that the output will remain in a Logic Low state (i.e.,  $V_O < 1.0 \text{ V}$ ).

- 11. Pulse Width Distortion (PWD) is defined as the difference between t<sub>PLH</sub> and t<sub>PHL</sub> for any given device.

- 12. Standard parts receive 100% testing at 25°C (Subgroups 1 and 9). Hi-Rel and SMD parts receive 100% testing at 25°C, +125°C, and -55°C (Subgroups 1 and 9, 2 and 10, 3 and 11 respectively).

- 13. Parameters are tested as part of device initial characterization and after design and process changes. Parameters are guaranteed to limits specified for all lots not specifically tested.

# LED Drive Circuit Considerations For Ultra High CMR Performance

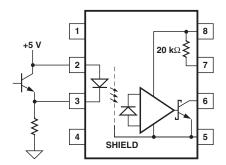

Without a detector shield, the dominant cause of optocoupler CMR failure is capacitive coupling from the input side of the optocoupler, through the package, to the detector IC as shown in Figure 14. The HCPL-530X improves CMR performance by using a detector IC with an optically transparent Faraday shield, which diverts the capacitively coupled current away from the sensitive IC circuitry. However, this shield does not eliminate the capacitive coupling between the LED and the optocoupler output pins and output ground as shown in Figure 15. This capacitive coupling causes perturbations in the LED current during common mode transients and becomes the major source of CMR failures for a shielded optocoupler. The main design objective of a high CMR LED drive circuit becomes keeping the LED in the proper state (on or off) during common mode transients. For example, the recommended application circuit (Figure 13), can achieve 10 kV/µs CMR while minimizing component complexity. Note that a CMOS gate is recommended in Figure 13 to keep the LED off when the gate is in the high state.

Another cause of CMR failure for a shielded optocoupler is direct coupling to the optocoupler output pins through  $C_{\text{LEDO1}}$  and  $C_{\text{LEDO2}}$  in Figure 15. Many factors influence the effect and magnitude of the direct coupling including: the use of an internal or external output pull-up resistor, the position of the LED current setting resistor, the connection of the unused input package pins, and the value of the capacitor at the optocoupler output (CL).

Techniques to keep the LED in the proper state and minimize the effect of the direct coupling are discussed in the next two sections.

### CMR With The LED On (CMR<sub>L</sub>)

A high CMR LED drive circuit must keep the LED on during common mode transients. This is achieved by overdriving the LED current beyond the input threshold so that it is not pulled below the threshold during a transient. The recommended minimum LED current of 10 mA provides adequate margin over the maximum  $I_{TH}$  of 5.0 mA (see Figure 1) to achieve 10 kV/ $\mu$ s CMR. Capacitive coupling is higher when the internal load resistor is used (due to  $C_{LEDO2}$ ) and an  $I_F=16$  mA is required to obtain 10 kV/ $\mu$ s CMR.

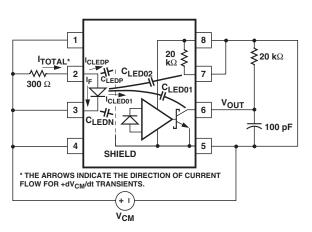

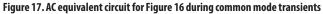

The placement of the LED current setting resistor affects the ability of the drive circuit to keep the LED on during transients and interacts with the direct coupling to the optocoupler output. For example, the LED resistor in Figure 16 is connected to the anode. Figure 17 shows the AC equivalent circuit for Figure 16 during common mode transients. During a +dV<sub>CM/dt</sub> in Figure 17, the current available at the LED anode (I<sub>TOTAL</sub>) is limited by the series resistor. The LED current (I<sub>F</sub>) is reduced from its DC value by an amount equal to the current that flows through CLEDP and CLEDO1. The situation is made worse because the current through CLEDO1 has the effect of trying to pull the output high (toward a CMR failure) at the same time the LED current is being reduced. For this reason, the recommended LED drive circuit (Figure 13) places the current setting resistor in series with the LED cathode. Figure 18 is the AC equivalent circuit for Figure 13 during common mode transients. In this case, the LED current is not reduced during a +dV<sub>CM/dt</sub> transient because the current flowing through the package capacitance is supplied by the power supply. During a -dV<sub>CM/dt</sub> transient, however, the LED current is reduced by the amount of current flowing through CLEDN. But better CMR performance is achieved since the current flowing in CLEDO1 during a negative transient acts to keep the output low.

Coupling to the LED and output pins is also affected by the connection of pins 1 and 4. If CMR is limited by perturbations in the LED on current, as it is for the recommended drive circuit (Figure 13), pins 1 and 4 should be connected to the input circuit common. However, if CMR performance is limited by direct coupling to the output when the LED is off, pins 1 and 4 should be left unconnected.

### CMR With The LED Off (CMR<sub>H</sub>)

A high CMR LED drive circuit must keep the LED off  $(V_F \le V_{F(OFF)})$  during common mode transients. For example, during a +dV<sub>CM/dt</sub> transient in Figure 18, the current flowing through C<sub>LEDN</sub> is supplied by the parallel combination of the LED and series resistor. As long as the voltage developed across the resistor is less than V<sub>F(OFF)</sub> the LED will remain off and no common mode failure will occur. Even if the LED momentarily turns on, the 100 pF capacitor from pins 6-5 will keep the output from dipping below the threshold. The recommended LED drive circuit (Figure 13) provides about 10 V of margin between the lowest optocoupler output voltage and a 3 V IPM threshold during a 10 kV/ $\mu$ s transient with  $V_{CM} = 1000 \text{ V}$ . Additional margin can be obtained by adding a diode in parallel with the resistor, as shown by the dashed line connection in Figure 18, to clamp the voltage across the LED below  $V_{F(OFF)}$ .

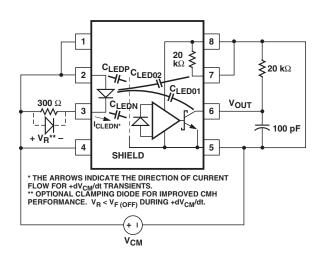

Since the open collector drive circuit, shown in Figure 19, cannot keep the LED off during a  $+ dV_{CM/dt}$  transient, it is not desirable for applications requiring ultra high CMRH performance. Figure 20 is the AC equivalent circuit for Figure 16 during common mode transients. Essentially all the current flowing through  $C_{LEDN}$  during a  $+ dV_{CM/dt}$  transient must be supplied by the LED. CMRH failures can occur at dv/dt rates where the current through the LED and  $C_{LEDN}$  exceeds the input threshold. Figure 21 is an alternative drive circuit which does achieve ultra high CMR performance by shunting the LED in the off state.

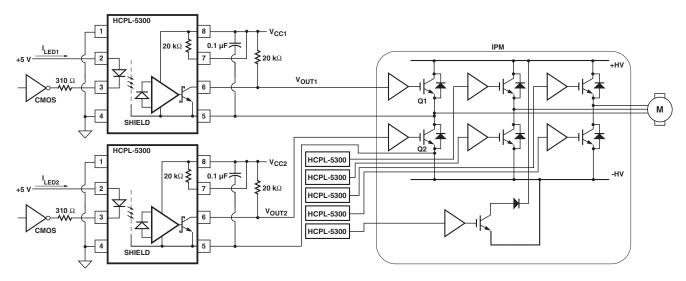

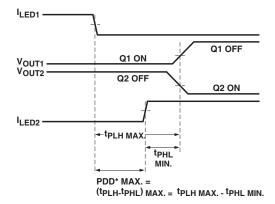

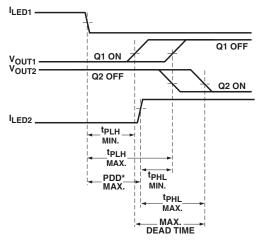

### **IPM Dead Time and Propagation Delay Specifications**

These devices include a Propagation Delay Difference specification intended to help designers minimize "dead time" in their power inverter designs. Dead time is the time period during which both the high and low side power transistors (Q1 and Q2 in Figure 22) are off. Any overlap in Q1 and Q2 conduction will result in large currents flowing through the power devices between the high and low voltage motor rails.

To minimize dead time the designer must consider the propagation delay characteristics of the optocoupler as well as the characteristics of the IPM IGBT gate drive circuit. Considering only the delay characteristics of the optocoupler (the characteristics of the IPM IGBT gate drive circuit can be analyzed in the same way) it is important to know the minimum and maximum turn-on (t<sub>PHL</sub>) and turn-off (t<sub>PLH</sub>) propagation delay specifications, preferably over the desired operating temperature range.

The limiting case of zero dead time occurs when the input to Q1 turns off at the same time that the input to Q2 turns on. This case determines the minimum delay between LED1 turn-off and LED2 turn-on, which is related to the worst case optocoupler propagation delay waveforms, as shown in Figure 23. A minimum dead time of zero is achieved in Figure 23 when the signal to turn on LED2 is delayed by ( $t_{PLH\,max}$  -  $t_{PHL\,min}$ ) from the LED1 turn off. This delay is the maximum value for the propagation delay difference specification which is specified at 500 ns for the HCPL-530X over an operating temperature range of -55° C to +125° C.

Delaying the LED signal by the maximum propagation delay difference ensures that the minimum dead time is zero, but it does not tell a designer what the maximum dead time will be. The maximum dead time occurs in the highly unlikely case where one optocoupler with the fastest  $t_{PLH}$  and another with the slowest  $t_{PHL}$  are in the same inverter leg. The maximum dead time in this case becomes the sum of the spread in the  $t_{PLH}$  and  $t_{PHL}$  propagation delays as shown in Figure 24. The maximum dead time is also equivalent to the difference between the maximum and minimum propagation delay difference specifications. The maximum dead time (due to the optocouplers) for the HCPL-530X is 670 ns (= 500 ns - (-170 ns)) over an operating temperature range of -55° C to +125° C.

Figure 1. Typical transfer characteristics

Figure 3. High level output current vs. temperature

Figure 2. Normalized output current vs. temperature

Figure 4. Input current vs. forward voltage

Figure 5. Propagation delay test circuit

Figure 6. CMR test circuit. Typical CMR waveform

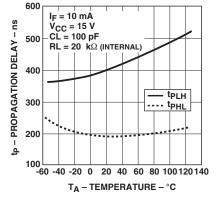

Figure 7. Propagation delay with external 20  $k\Omega$  RL vs. temperature

Figure 8. Propagation delay with internal 20  $k\Omega$  RL vs. temperature

Figure 9. Propagation delay vs. load resistance

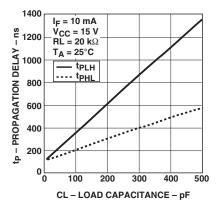

Figure 10. Propagation delay vs. load capacitance

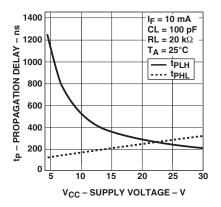

Figure 11. Propagation delay vs. supply voltage

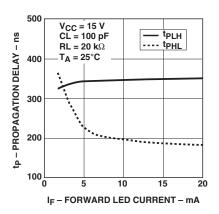

Figure 12. Propagation delay vs. input current

Figure 13. Recommended LED drive circuit

Figure 14. Optocoupler input to output capacitance model for unshielded optocouplers

Figure 15. Optocoupler input to output capacitance model for shielded optocouplers

Figure 16. LED drive circuit with resistor connected to LED anode (not recommended)

Figure 18. AC equivalent circuit for Figure 13 during common mode transients

Figure 19. Not recommended open collector LED drive circuit

Figure 20. AC equivalent circuit for Figure 19 during common mode transients

Figure 21. Recommended LED drive circuit for ultra high CMR

Figure 22. Typical application circuit

\*PDD = PROPAGATION DELAY DIFFERENCE

NOTE: THE PROPAGATION DELAYS USED TO CALCULATE PDD ARE TAKEN AT EQUAL TEMPERATURES.

Figure 23. Minimum LED skew for zero dead time

MAXIMUM DEAD TIME (DUE TO OPTOCOUPLER)

- =  $(t_{PLH\ MAX.} t_{PLH\ MIN.}) + (t_{PHL\ MAX.} t_{PHL\ MIN.})$

- =  $(t_{PLH\ MAX.} t_{PHL\ MIN.}) (t_{PLH\ MIN.} t_{PHL\ MAX.})$

- = PDD\* MAX. PDD\* MIN.

\*PDD = PROPAGATION DELAY DIFFERENCE

NOTE: THE PROPAGATION DELAYS USED TO CALCULATE THE MAXIMUM DEAD TIME ARE TAKEN AT EQUAL TEMPERATURES.

Figure 24. Waveforms for dead time calculations

# MIL-PRF-38534 Class H, Class K, and DLA SMD Test Program

Avago Technologies' Hi-Rel Optocouplers are in compliance with MIL-PRF-38534 Classes H and K. Class H and Class K devices are also in compliance with DLA drawing 5962-96852.

Testing consists of 100% screening and quality conformance inspection to MIL-PRF-38534.