escale Semiconductor

Data Sheet: Advance Information An Energy-Efficient Solution by Freescale

Document Number: MMA27XXW

Rev. 0.5, 4/2013

## Xtrinsic MMA27XXW/17XXW DSI3 **Inertial Sensor**

MMA27XXW/17XXW family, a SafeAssure solution, includes the DSI3 compatible overdamped X-axis or Z-axis satellite accelerometers.

#### **Features**

- ±25 g, ±125 g, ±187 g, ±250 g, ±375 g, X-axis nominal full-scale range

- ±250 g, Z-axis nominal full-scale range

- DSI3 compatible

- Discovery Mode for physical location identification

- High-side bus switch output driver

- Command and Response Mode support for device configuration

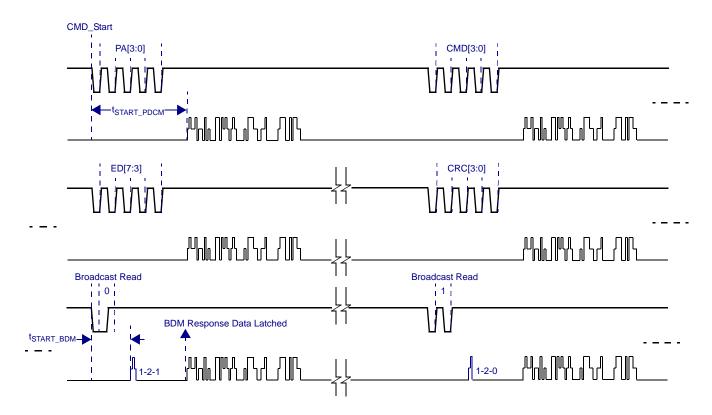

- Periodic Data Collection Mode support for acceleration data transfers

- Background Diagnostic Mode support during Periodic Data Collection Mode

- -40°C to 125°C operating temperature range

- 16 μs internal sample rate, with interpolation to 1 μs

- Six selectable low-pass filter options from 180 Hz to 1200 Hz

- Single-pole, IIR high-pass filter with fast startup and optional output rate limiting

- Pb-Free, 16-pin QFN, 6 x 6 package

#### **Referenced Documents**

- DSI3 Standard Revision 1.0, Dated February 16, 2011

- AEC-Q100, Revision G, dated May 14, 2007

|             | ORDERING INFORMATION |        |         |             |  |  |  |  |  |  |  |

|-------------|----------------------|--------|---------|-------------|--|--|--|--|--|--|--|

| Part Number | Axis                 | Range  | Package | Shipping    |  |  |  |  |  |  |  |

| MMA2702W    | Х                    | ±25 g  | 2086-01 | Rail        |  |  |  |  |  |  |  |

| MMA2712W    | Х                    | ±125 g | 2086-01 | Rail        |  |  |  |  |  |  |  |

| MMA2718W    | Х                    | ±187 g | 2086-01 | Rail        |  |  |  |  |  |  |  |

| MMA2725W    | Х                    | ±250 g | 2086-01 | Rail        |  |  |  |  |  |  |  |

| MMA2737W    | Х                    | ±375 g | 2086-01 | Rail        |  |  |  |  |  |  |  |

| MMA1725W    | Z                    | ±250 g | 2086-01 | Rail        |  |  |  |  |  |  |  |

| MMA2702WR2  | Х                    | ±25 g  | 2086-01 | Tape & Reel |  |  |  |  |  |  |  |

| MMA2712WR2  | Х                    | ±125 g | 2086-01 | Tape & Reel |  |  |  |  |  |  |  |

| MMA2718WR2  | Х                    | ±187 g | 2086-01 | Tape & Reel |  |  |  |  |  |  |  |

| MMA2725WR2  | Х                    | ±250 g | 2086-01 | Tape & Reel |  |  |  |  |  |  |  |

| MMA2737WR2  | Х                    | ±375 g | 2086-01 | Tape & Reel |  |  |  |  |  |  |  |

| MMA1725WR2  | Z                    | ±250 g | 2086-01 | Tape & Reel |  |  |  |  |  |  |  |

## MMA27XXW **MMA17XXW**

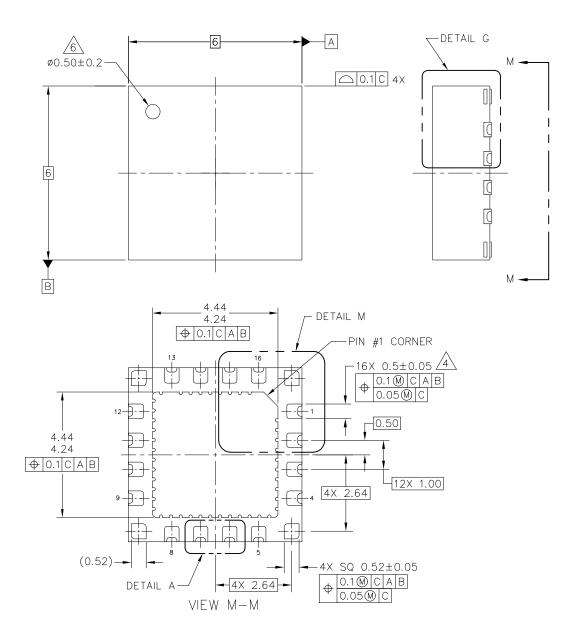

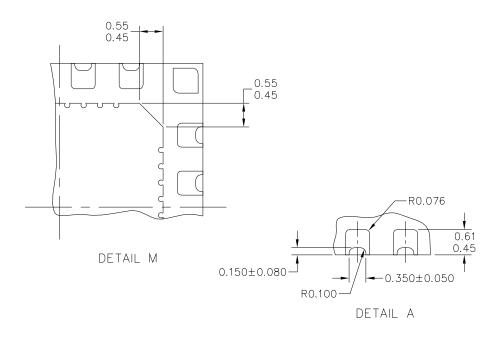

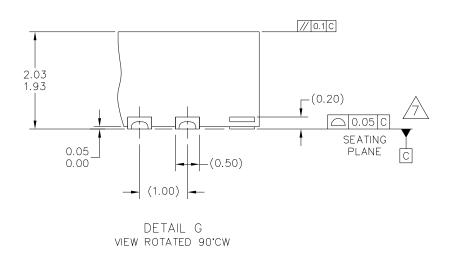

#### **Bottom View**

16-PIN QFN 6 MM X 6 MM X 2 MM **CASE 2086-01**

This document contains information on a new product. Specifications and information herein are subject to change without notice. Freescale reserves the right to change the detail © 2013 Freescale Semiconductor, Inc. All rights reserved.

## **Contents**

| 1 | Bloc  | k Diagram, Pin Descriptions, Application Diagram, and Device Orientation | . 3 |

|---|-------|--------------------------------------------------------------------------|-----|

|   | 1.1   | Block diagram                                                            |     |

|   | 1.2   | Pin descriptions.                                                        | . 4 |

|   | 1.3   | Application diagram                                                      | . 5 |

|   | 1.4   | Device orientation and device marking                                    | . 6 |

| 2 | Elect | trical Characteristics                                                   | . 7 |

|   | 2.1   | Maximum ratings                                                          | . 7 |

|   | 2.2   | Operating range                                                          | . 7 |

|   | 2.3   | Electrical characteristics - supply and I/O                              | . 8 |

|   | 2.4   | Electrical Characteristics - sensor and signal chain                     | . 9 |

|   | 2.5   | Electrical characteristics - self-test and overload                      | 10  |

|   | 2.6   | Dynamic electrical characteristics - DSI3                                | 11  |

|   | 2.7   | Dynamic electrical characteristics - signal chain                        | 12  |

|   | 2.8   | Dynamic electrical characteristics - supply and support circuitry        | 13  |

| 3 | Func  | tional Description                                                       | 14  |

|   | 3.1   | User-accessible data array                                               | 14  |

|   | 3.2   | OTP and Read/Write register array CRC verification                       | 31  |

|   | 3.3   | Voltage regulators                                                       | 33  |

|   | 3.4   | Internal oscillator                                                      | 37  |

|   | 3.5   | Acceleration signal path                                                 | 38  |

|   | 3.6   | DSI3 physical layer                                                      | 55  |

|   | 3.7   | Data transmission modes                                                  | 58  |

|   | 3.8   | Initialization timing                                                    | 59  |

|   | 3.9   | Overload response                                                        | 60  |

| 4 | DSI3  | Protocol                                                                 | 61  |

|   | 4.1   | Address assignment                                                       | 61  |

|   | 4.2   | DSI3 Command and Response Mode                                           | 62  |

|   | 4.3   | DSI3 Periodic Data Collection Mode and Background Diagnostic Mode        | 72  |

|   | 4.4   | Maximum number of devices on a network                                   | 77  |

| 5 | Exce  | ption Handling                                                           | 78  |

| 6 |       | ommended Footprint                                                       |     |

| 7 |       | age Dimensions                                                           |     |

| 8 | Revi  | sion History                                                             | 83  |

|   |       |                                                                          |     |

## **Related Documentation**

The MMA27XXW and MMA17XXW devices features and operations are described in a variety of reference manuals, user guides, and application notes. To find the most-current versions of these documents:

1. Go to the Freescale homepage at:

http://www.freescale.com/

- 2. In the Keyword search box at the top of the page, enter the device number MMA27XXW or MMA17XXW.

- 3. In the Refine Your Result pane on the left, click on the Documentation link.

# 1 Block Diagram, Pin Descriptions, Application Diagram, and Device Orientation

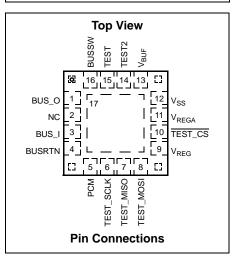

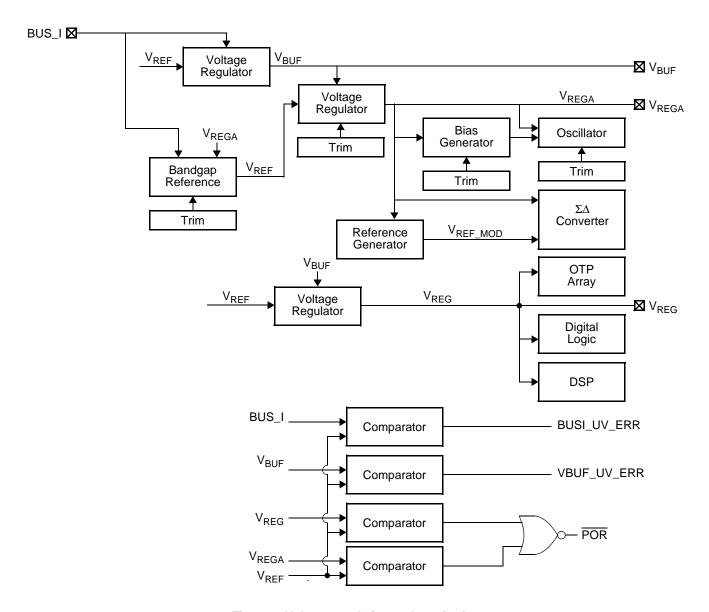

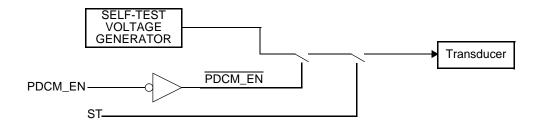

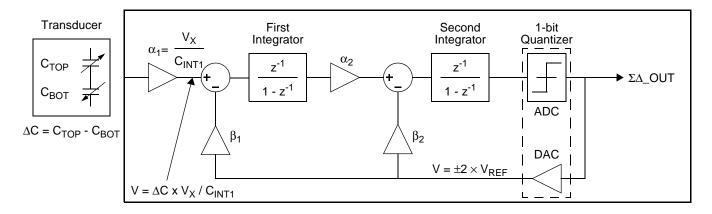

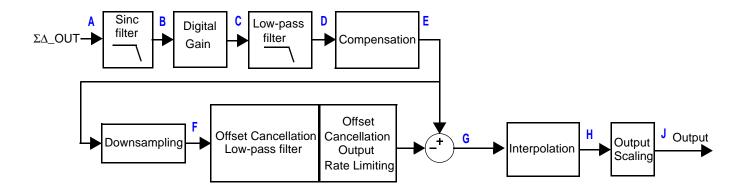

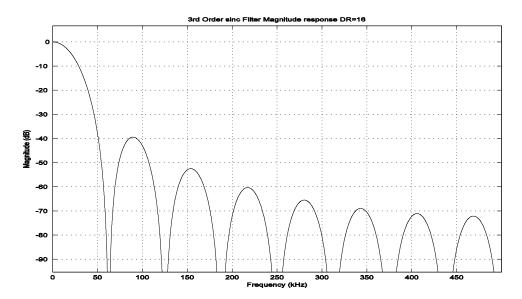

## 1.1 Block diagram

Figure 1. Internal block diagram

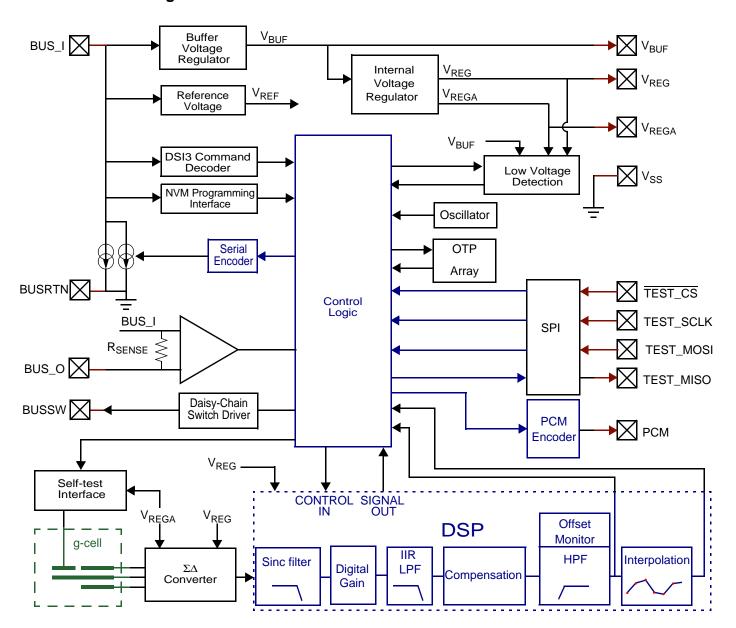

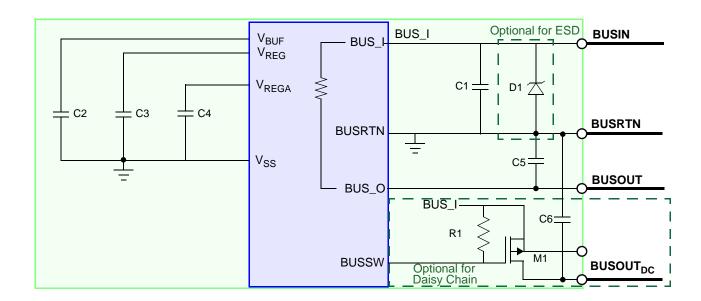

## 1.2 Pin descriptions

Figure 2. Pin connections

Table 1. Pin descriptions

| Pin | Pin name         | Formal name                 | Definition                                                                                                                                                                                                                                                                                                                                                                      |

|-----|------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | BUS_O            | Supply out                  | This pin is connected to the BUS_I pin through an internal sense resistor and provides the supply connection to the next slave in a daisy-chain configuration. An external capacitor must be connected between this pin and V <sub>SS</sub> . Reference Figure 3.                                                                                                               |

| 2   | NC               | Not connected               | This pin is not internally connected and must be left unconnected or tied to $V_{SS}$ in the application.                                                                                                                                                                                                                                                                       |

| 3   | BUS_I            | Supply and communication    | This pin is connected to the DSI supply line and supplies power to the device. An external capacitor must be connected between this pin and BUSRTN. Reference Figure 3.                                                                                                                                                                                                         |

| 4   | BUSRTN           | Supply return               | This pin is the DSI supply return node.                                                                                                                                                                                                                                                                                                                                         |

| 5   | PCM              | Pulse code modulated output | If the PCM output is enabled, this pin provides a 4 MHz PCM signal proportional to the acceleration data for test purposes. If PCM is unused, this pin must be left unconnected.                                                                                                                                                                                                |

| 6   | TEST_SCLK        | SPI clock                   | This input pin provides the serial clock to the SPI port for test purposes. An internal pull-down device is connected to this pin. This pin must be grounded or left unconnected in the application.                                                                                                                                                                            |

| 7   | TEST_MISO        | SPI data out                | This pin functions as the serial data output from the SPI port for test purposes. This pin must be left unconnected in the application.                                                                                                                                                                                                                                         |

| 8   | TEST_MOSI        | SPI data in                 | This pin functions as the serial data input to the SPI port for test purposes. An internal pull-down device is connected to this pin. This pin must be grounded or left unconnected in the application.                                                                                                                                                                         |

| 9   | V <sub>REG</sub> | Internal<br>supply          | This pin is connected to the power supply for the internal circuitry. An external capacitor must be connected between this pin and $V_{SS}$ . Reference Figure 3.                                                                                                                                                                                                               |

| 10  | TEST_CS          | Chip select                 | This input pin provides the chip select to the SPI port for test purposes. An internal pullup device is connected to this pin. This pin must be left unconnected in the application.                                                                                                                                                                                            |

| 11  | $V_{REGA}$       | Internal supply             | This pin is connected to the power supply for the internal circuitry. An external capacitor must be connected between this pin and $V_{SSA}$ . Reference Figure 3.                                                                                                                                                                                                              |

| 12  | $V_{SS}$         | Internal supply<br>return   | This pin is the power supply return node for the internal power supplies and must be connected to BUSRTN in this application.                                                                                                                                                                                                                                                   |

| 13  | V <sub>BUF</sub> | Power supply                | This pin is connected to a buffer regulator for the internal circuitry. The buffer regulator supplies the internal regulators to provide immunity from EMC and supply dropouts. An external capacitor must be connected between this pin and $V_{SS}$ . Reference Figure 3.                                                                                                     |

| 14  | TEST2            | Test pin                    | This pin is must be connected to $V_{SS}$ in the application.                                                                                                                                                                                                                                                                                                                   |

| 15  | TEST             | Test pin                    | This pin is must be connected to $V_{SS}$ in the application.                                                                                                                                                                                                                                                                                                                   |

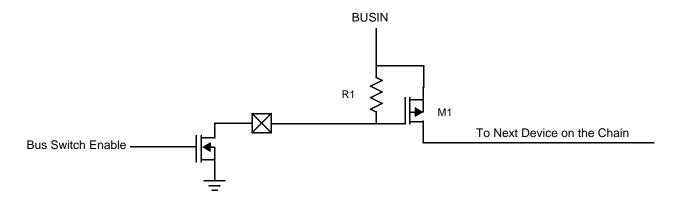

| 16  | BUSSW            | Bus switch gate drive       | This pin is the drive for a high-side, daisy-chain switch. When switch is connected, daisy-chain mode is used, this pin is connected to the gate of a p-channel FET which connects BUS_I to the next slave in the daisy chain. An external pullup resistor is required on the gate of the p-channel FET. Reference Section 3.6.4. If unused, this pin must be left unconnected. |

| 17  | PAD              | Die attach pad              | This pin is the die attach flag, and is internally connected to $V_{SS}$ . Reference Section 6 for die attach pad connection details.                                                                                                                                                                                                                                           |

|     | Corner pads      | Corner pads                 | The corner pads are internally connected to V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                   |

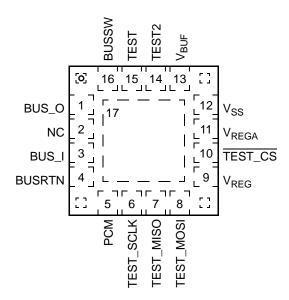

## 1.3 Application diagram

Figure 3. MMA27XXW/17XXW application diagram

Table 2. External component recommendations

| Ref Des | Туре             | Description                    | Purpose                                                                                                                            |

|---------|------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| C1      | Ceramic          | 220 pF, 10%, 50 V minimum, X7R | BUSIN EMC and ESD protection. Capacitor value is dependent on the DSI3 master device and must be chosen by the system implementer. |

| C2      | Ceramic          | 1 μF, 10%, 10 V minimum, X7R   | Voltage regulator output capacitor                                                                                                 |

| C3      | Ceramic          | 1 μF, 10%, 10 V minimum, X7R   | Voltage regulator output capacitor                                                                                                 |

| C4      | Ceramic          | 1 μF, 10%, 10 V minimum, X7R   | Voltage regulator output capacitor                                                                                                 |

| C5      | Ceramic          | 100 pF, 10%, 50 V minimum, X7R | BUSOUT EMC and ESD protection                                                                                                      |

| C6      | Ceramic          | 100 pF, 10%, 50 V minimum, X7R | BUSOUT EMC and ESD protection                                                                                                      |

| R1      | General purpose  | 100 kΩ, 5%, 200 PPM            | Pullup resistor for external high-side, daisy-chain FET                                                                            |

| M1      | P-channel MOSFET |                                | High-side, daisy-chain transistor                                                                                                  |

| D1      | Zener diode      | MMBZ27Vxxxx or equivalent      | ESD protection diode                                                                                                               |

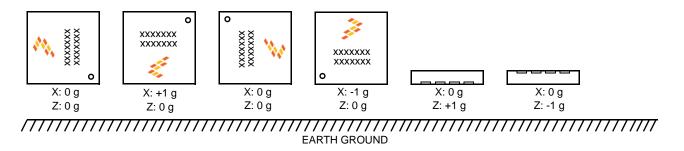

## 1.4 Device orientation and device marking

Figure 4. Device orientation diagram

### Data Code Legend:

A: Assembly Location

WL: Wafer Lot Number (g-cell Lot Number)

Y: Year

WW: Work Week

Z: Assembly Lot Number

Figure 5. Device marking

## 2 Electrical Characteristics

## 2.1 Maximum ratings

Maximum ratings are the extreme limits to which the device can be exposed without permanently damaging it.

| #  | Rating                                                                     | Symbol             | Value        | Unit |        |

|----|----------------------------------------------------------------------------|--------------------|--------------|------|--------|

| 1  | Supply voltage (BUS_I, BUS_O, BUSSW)                                       |                    |              |      |        |

| 2  | Reverse current ≤ 160 mA, t ≤ 80 ms                                        | BUS_I_REV          | -0.7         | V    | (6)    |

| 3  | Continuous                                                                 | BUS_I_MAX          | +20.0        | V    | (6)    |

| 4  | Transient (< 10 us)                                                        | BUS_I_TRANS        | +25.0        | V    | (9)    |

| 5  | V <sub>BUF</sub>                                                           |                    | -0.3 to +4.0 | V    | (6)    |

| 6  | $V_{REG}$ , $V_{REGA}$ , TEST_SCLK, TEST_CS, TEST_MOSI, TEST_MISO, PCM     |                    | -0.3 to +3.0 | >    | (6)    |

| 7  | BUS_I, BUS_O and BUSRTN current                                            |                    |              |      |        |

| 8  | Maximum duration 560 μs, with 10 ms repetition rate                        | I <sub>IN</sub>    | 200          | mA   | (6)    |

| 9  | Continuous                                                                 | I <sub>IN</sub>    | 150          | mA   | (6)    |

| 10 | Powered shock (six sides, 0.5 ms duration)                                 | 9 <sub>pms</sub>   | ±2000        | g    | (5)    |

| 11 | Unpowered shock (six sides, 0.5 ms duration)                               | 9 <sub>shock</sub> | ±2000        | g    | (5)    |

| 12 | Drop shock (to concrete, tile or steel surface, 10 drops, any orientation) | h <sub>DROP</sub>  | 1.2          | m    | (5)    |

| 13 | Electrostatic discharge (per AEC-Q100), external pins                      |                    |              |      |        |

| 14 | BUS_I, BUS_O, BUSRTN, HBM (100 pF, 1.5 k $\Omega$ )                        | V <sub>ESD</sub>   | ±4000        | V    | (5)    |

| 15 | Electrostatic discharge (per AEC-Q100)                                     |                    |              |      |        |

| 16 | HBM (100 pF, 1.5 kΩ)                                                       | V <sub>ESD</sub>   | ±2000        | V    | (5)    |

| 17 | CDM (R = $0 \Omega$ )                                                      | $V_{ESD}$          | ±500         | V    | (5)    |

| 18 | MM (200 pF, 0 Ω)                                                           | V <sub>ESD</sub>   | ±200         | V    | (5)    |

| 19 | Temperature range                                                          |                    |              |      |        |

| 20 | Storage                                                                    | T <sub>stg</sub>   | -40 to +125  | °C   | (5)    |

| 21 | Junction                                                                   | TJ                 | -40 to +150  | °C   | (9)    |

| 22 | Thermal resistance                                                         | $\theta_{JC}$      | 2.5          | °C/W | (9,11) |

## 2.2 Operating range

$V_{BUS\_I\_L} \leq (V_{BUS\_I} - V_{SS}) \leq V_{BUS\_I\_H}, \ T_L \leq T_A \leq T_H, \ \Delta T \leq 12^{\circ}C/min, \ unless \ otherwise \ specified.$

| #              | Characteristic                                                                                                                         | Symbol                      | Min                 | Тур | Max                         | Units |       |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------|-----|-----------------------------|-------|-------|

| 23             | Supply voltage (measured at BUS_I pin)                                                                                                 |                             |                     |     |                             |       |       |

| 24             | V <sub>HIGH</sub> *                                                                                                                    | V <sub>BUS_I_HIGH_max</sub> | _                   | _   | 20.0                        | V     | (1,6) |

| 25             | V <sub>LOW</sub> rising                                                                                                                | V <sub>BUS_I_LOW_Rise</sub> | 4.5                 | _   | _                           | V     | (9)   |

| 26             | V <sub>LOW</sub> falling *                                                                                                             | V <sub>BUS_I_LOW_Fall</sub> | 4.0                 | _   | _                           | V     | (1)   |

| 27             | Supply voltage (undervoltage)                                                                                                          | $V_{BUS\_I\_UV}$            | $V_{BUS\_I\_UV\_F}$ | _   | $V_{BUS\_I\_LOW\_Fall}$     | V     | (3,6) |

| 28             | Programming voltage (I <sub>RD</sub> ≤ 85 mA) Applied to BUS_I                                                                         | VPP                         | 14.0                | _   | V <sub>BUS_I_HIGH_max</sub> | V     | (6)   |

| 29<br>30<br>31 | ESD operating voltage (No device reset, $C_{BUS\_IN}$ = 220 pF, D1 = MMBZ27Vxxxx) Maximum ±15 kV air discharge, 330 pF, 2.0 k $\Omega$ | VBUS_I_ESD                  |                     |     | 12.0                        | V     | (9)   |

|                | Operating temperature range                                                                                                            |                             | T <sub>L</sub>      |     | T <sub>H</sub>              |       |       |

| 33             |                                                                                                                                        | $T_A$                       | -40                 | _   | +105                        | °C    | (1)   |

| 34             |                                                                                                                                        | $T_A$                       | -40                 | _   | +125                        | °C    | (5,6) |

## 2.3 Electrical characteristics - supply and I/O

$V_{BUS\_I\_L} \leq (V_{BUS\_I} - V_{SS}) \leq V_{BUS\_I\_H}, \ T_L \leq T_A \leq T_H, \ \Delta T \leq 12 \ ^{\circ}C/min, \ unless \ otherwise \ specified.$

| #                          | Characteristic                                                                                                                                                                                   | Symbol                                                                                                       | Min                                             | Тур                                            | Max                                            | Units       | Ĵ                              |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------|------------------------------------------------|-------------|--------------------------------|

| 35                         | Quiescent supply current<br>V <sub>BUS_I</sub> = 4 V, V <sub>BUS_I</sub> = 20 V *                                                                                                                | Iq                                                                                                           | 4.0                                             | _                                              | 8.0                                            | mA          | (1                             |

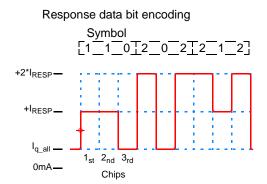

| 36<br>37                   | Response current Low * High *                                                                                                                                                                    | I <sub>RESP</sub><br>2*I <sub>RESP</sub>                                                                     | l <sub>q</sub> + 10.50<br>l <sub>q</sub> + 21.0 | l <sub>q</sub> + 12.0<br>l <sub>q</sub> + 24.0 | l <sub>q</sub> + 13.5<br>l <sub>q</sub> + 27.0 | mA<br>mA    | (1<br>(1                       |

| 38                         | V <sub>BUF</sub> current limit                                                                                                                                                                   | I <sub>INRUSH_MAX</sub>                                                                                      | _                                               | _                                              | 30                                             | mA          | (6                             |

| 39<br>40<br>41             | Internally regulated voltages $V_{BUF}, V_{BUS\_I} = 4 \text{ V}, V_{BUS\_I} = 20 \text{ V}$ $V_{REG}, V_{BUS\_I} = 4 \text{ V}$ $V_{REGA}, V_{BUS\_I} = 4 \text{ V}, V_{BUS\_I} = 20 \text{ V}$ | V <sub>BUF</sub><br>V <sub>REG</sub><br>V <sub>REGA</sub>                                                    | 3.250<br>2.400<br>2.425                         | 3.400<br>2.500<br>2.500                        | 3.550<br>2.600<br>2.575                        | V<br>V      | (1<br>(1<br>(1                 |

| 42<br>43<br>44<br>45<br>46 | Low-voltage detection threshold  BUS_I falling  V <sub>BUF</sub> falling  V <sub>REG</sub> falling  V <sub>REGA</sub> falling  Low-voltage detection hysteresis                                  | V <sub>BUS_I_UV_F</sub> V <sub>BUF_UV_F</sub> V <sub>REG_UV_F</sub> V <sub>REGA_UV_F</sub> V <sub>HYST</sub> | 3.60<br>2.80<br>2.15<br>2.15<br>0.04            | 3.75<br>3.05<br>2.25<br>2.25                   | 3.90<br>3.20<br>2.35<br>2.35                   | V<br>V<br>V | (3,6)<br>(3,6)<br>(3,6)<br>(6) |

| 47<br>48                   | External capacitor (V <sub>BUF</sub> , V <sub>REG</sub> , V <sub>REGA</sub> ) Capacitance ESR (including interconnect resistance)                                                                | C <sub>VBUF</sub> , C <sub>VREG</sub> , C <sub>VREGA</sub>                                                   | 500<br>0                                        | 1000<br>—                                      | 1500<br>200                                    | nF<br>mΩ    | (9)<br>(9)                     |

| 49<br>50                   | V <sub>LOW</sub> detection threshold (Section 3.6.1)  V <sub>LOW</sub> detection threshold  * V <sub>LOW</sub> detection hysteresis  *                                                           | V <sub>DELTA_THRESH</sub> V <sub>DELTA_THRESH_Hyst</sub>                                                     | V <sub>HIGH</sub> -1.25                         | V <sub>HIGH</sub> -1.0                         | V <sub>HIGH</sub> -0.75                        | V<br>mV     | (3,6                           |

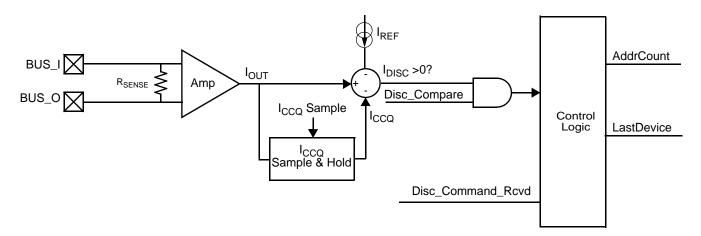

| 51<br>52                   | Discovery Mode current sense (Section 3.6.3) Sense resistor $I_{RESP} \ detection \ threshold \ (I_{BUS\_O\_q} \le 24 \ mA)$                                                                     | R <sub>SENSE</sub>                                                                                           | 1.3<br>6                                        | 2.15<br>12                                     | 3<br>18                                        | Ω<br>mA     | (6)<br>(3,6                    |

| 53                         | Bus switch output low voltage (Section 3.6.4) $I_{Load} = 100 \; \mu A$                                                                                                                          | V <sub>BUS_SW_OL</sub>                                                                                       | 0.0                                             | _                                              | 0.45                                           | >           | (3,6                           |

| 54                         | Bus switch open drain output leakage current (BUSSW) V <sub>BUSSW</sub> = 20 V                                                                                                                   | I <sub>BUS_SW_ODL</sub>                                                                                      | _                                               | _                                              | 10                                             | μΑ          | (3,6                           |

| 55                         | Output high voltage (PCM)<br>I <sub>Load</sub> = -100 μA                                                                                                                                         | V <sub>OH</sub>                                                                                              | V <sub>REG</sub> - 0.1                          | _                                              | _                                              | ٧           | (3)                            |

| 56                         | Output low voltage (PCM)<br>I <sub>Load</sub> = 100 μA                                                                                                                                           | V <sub>OL</sub>                                                                                              | _                                               | _                                              | 0.1                                            | ٧           | (3)                            |

## 2.4 Electrical Characteristics - sensor and signal chain

$V_{BUS\_I\_L} \leq (V_{BUS\_I} - V_{SS}) \leq V_{BUS\_I\_H}, \ T_L \leq T_A \leq T_H, \ \Delta T \leq 12 \ ^{\circ}C/min, \ unless \ otherwise \ specified.$

| #  | Characteristic                                                                       | Symbol                    | Min    | Тур    | Max    | Units |         |

|----|--------------------------------------------------------------------------------------|---------------------------|--------|--------|--------|-------|---------|

|    | Sensitivity (T <sub>A</sub> = 25°C, 10-bit output @ 100 Hz, referenced to 0Hz: ±5%)  | -                         |        | 7.     |        |       | 1       |

| 57 | ±25 g range *                                                                        | SENS <sub>025</sub>       | 19.456 | 20.480 | 21.504 | LSB/g | (1)     |

| 58 | ±125 g range *                                                                       | SENS <sub>125</sub>       | 3.8912 | 4.0960 | 4.3008 | LSB/g | (1)     |

| 59 | ±187 g range *                                                                       | SENS <sub>187</sub>       | 2.5944 | 2.7310 | 2.8676 | LSB/g | (1)     |

| 60 | ±250 g range *                                                                       | SENS <sub>250</sub>       | 1.9456 | 2.0480 | 2.1504 | LSB/g | (1)     |

| 61 | ±375 g range *                                                                       | SENS <sub>375</sub>       | 1.2967 | 1.3650 | 1.4333 | LSB/g | (1)     |

|    | Sensitivity ( $T_L \le T_A \le T_H$ , $V_{BUS\_I\_UV\_F} \le V_{BUS\_I} \le V_{LOW}$ |                           |        |        |        |       |         |

|    | 10-bit output @ 100 Hz, referenced to 0 Hz: ±7%)                                     | 0=110                     |        |        |        |       |         |

| 62 | ±25 g range *                                                                        | SENS <sub>025</sub>       | 19.046 | 20.480 | 21.914 | LSB/g | (1)     |

| 63 | ±125 g range *                                                                       | SENS <sub>125</sub>       | 3.8092 | 4.0960 | 4.3828 | LSB/g | (1)     |

| 64 | ±187 g range *                                                                       | SENS <sub>187</sub>       | 2.5398 | 2.7310 | 2.9222 | LSB/g | (1)     |

| 65 | ±250 g range *                                                                       | SENS <sub>250</sub>       | 1.9046 | 2.0480 | 2.1914 | LSB/g | (1)     |

| 66 | ±375 g range *                                                                       | SENS <sub>375</sub>       | 1.2694 | 1.3650 | 1.4606 | LSB/g | (1)     |

|    | Digital offset before offset cancellation (10-bit)                                   |                           |        |        |        |       |         |

| 67 | ±25 g, ±125 g, ±250 g Z-axis *                                                       | OFF <sub>10Bit</sub>      | -100   | 0      | +100   | LSB   | (1)     |

| 68 | $V_{BUS\_I\_UV\_F} \le V_{BUS\_I} \le V_{LOW}$ , ±25 g, ±125 g, ±250 g Z-axis        | OFF <sub>10Bit</sub>      | -100   | 0      | +100   | LSB   | (6)     |

| 69 | ±187 g, ±250 g X-axis, ±375 g                                                        | OFF <sub>10Bit</sub>      | -52    | 0      | +52    | LSB   | (1)     |

| 70 | $V_{BUS\_I\_UV\_F} \le V_{BUS\_I} \le V_{LOW}$ , ±187 g, ±250 g X-axis, ±375 g       | OFF <sub>10Bit</sub>      | -52    | 0      | +52    | LSB   | (6)     |

| 71 | Digital offset after offset cancellation (10-bit, all filter options)                | OFF <sub>10Bit</sub>      | -1     | 0      | +1     | LSB   | (6,8,9) |

|    | Continuous offset monitor limit                                                      |                           |        |        |        |       |         |

| 72 | 10-bit output, before compensation, ±25 g                                            | OFF <sub>MON</sub>        | -150   | _      | +150   | LSB   | (7,8)   |

| 73 | 10-bit output, before compensation, ±125 g, ±250 g Z-axis                            | OFF <sub>MON</sub>        | -120   | _      | +120   | LSB   | (7,8)   |

| 74 | 10-bit output, before compensation, ±187 g, ±250 g X-axis, ±375 g                    | OFF <sub>MON</sub>        | -70    | _      | +70    | LSB   | (7,8)   |

|    | Range of output (10-bit mode)                                                        |                           |        |        |        |       |         |

| 75 | Acceleration (signed)                                                                | RANGE <sub>Signed</sub>   | -511   |        | +511   | LSB   | (7,8)   |

| 76 | Acceleration (unsigned)                                                              | RANGE <sub>Unsigned</sub> | 1      |        | 1023   | LSB   | (7,9)   |

| 77 | Error code (signed)                                                                  | ERR <sub>Signed</sub>     | _      | -512   |        | LSB   | (7,8)   |

| 78 | Error code (unsigned)                                                                | ERR <sub>Unsigned</sub>   |        | 0      | _      | LSB   | (7,9)   |

|    | Cross-axis sensitivity                                                               |                           |        |        |        |       |         |

| 79 | Z-axis to X-axis                                                                     | $V_{ZX}$                  | -5     | _      | +5     | %     | (6)     |

| 80 | Y-axis to X-axis                                                                     | $V_{YX}$                  | -5     | _      | +5     | %     | (6)     |

| 81 | X-axis to Z-axis                                                                     | $V_{XZ}$                  | -5     |        | +5     | %     | (6)     |

| 82 | Y-axis to Z-axis                                                                     | $V_{YZ}$                  | -5     |        | +5     | %     | (6)     |

|    | System output noise peak (peak value of 100 samples @ 2 kHz)                         |                           |        |        |        |       |         |

| 83 | 10-bit mode, LPF = 180 Hz, 2-Pole, All Ranges                                        | n <sub>Peak_180</sub>     | -3     |        | +3     | LSB   | (1)     |

| 84 | 10-bit mode, LPF = 400 Hz, 4-Pole, All Ranges                                        | n <sub>Peak_400</sub>     | -4     | _      | +4     | LSB   | (6)     |

|    | System output noise average (average value of 100 samples @ 2 kHz)                   | n                         |        |        |        |       |         |

| 85 | 10-bit mode, LPF = 180 Hz, 2-pole, all ranges *                                      | n <sub>RMS_180</sub>      | _      | _      | +1.0   | LSB   | (1)     |

| 86 | 10-bit mode, LPF = 400 Hz, 4-pole, all ranges *                                      | n <sub>RMS_400</sub>      |        |        | +1.0   | LSB   | (6)     |

| 87 | Nonlinearity (10-bit output, all ranges)                                             | NL <sub>OUT</sub>         | -2     | _      | +2     | %     | (6)     |

## 2.5 Electrical characteristics - self-test and overload

$V_{BUS\_I\_L} \leq (V_{BUS\_I} - V_{SS}) \leq V_{BUS\_I\_H}, \ T_L \leq T_A \leq T_H, \ \Delta T \leq 12^{\circ}C/min, \ unless \ otherwise \ specified.$

| #   | Characteristic                                                              |   | Symbol                       | Min               | Тур                | Max                | Units | ]     |

|-----|-----------------------------------------------------------------------------|---|------------------------------|-------------------|--------------------|--------------------|-------|-------|

|     | 10-bit output during active self-test                                       |   |                              | $\Delta ST_{MIN}$ | ΔST <sub>NOM</sub> | ΔST <sub>MAX</sub> |       |       |

| 88  | ±25 g range, X-axis                                                         | * | 9 <sub>ST10 25</sub> X       | 124               | _                  | 208                | LSB   | (1)   |

| 89  | ±125 g range, X-axis                                                        | * | 9ST10_125X                   | 236               | _                  | 395                | LSB   | (1)   |

| 90  | ±187 g range, X-axis                                                        | * | 9ST10_187X                   | 156               | _                  | 263                | LSB   | (1)   |

| 91  | ±250 g range, X-axis                                                        | * | 9st10_250X                   | 117               | _                  | 198                | LSB   | (1)   |

| 92  | ±375 g range, X-axis                                                        | * | 9st10_375X                   | 77                | _                  | 131                | LSB   | (1)   |

| 93  | ±250 g range, Z-axis                                                        | * | 9ST10_250Z                   | 80                | _                  | 160                | LSB   | (1)   |

|     | Self-test accuracy: $\Delta$ from stored value, including sensitivity error |   |                              |                   |                    |                    |       |       |

| 94  | -40°C ≤ T <sub>A</sub> ≤ 125°C (Section 3.5.2)                              | * | ∆STACC                       | -10               | _                  | +10                | %     | (1,5) |

|     | Transducer clipping limit                                                   |   |                              |                   |                    |                    |       |       |

| 95  | ±25 g, X-axis, positive/negative                                            |   | 9g-cell_ClipLowX             | 400               | 470                | 500                | g     | (9)   |

| 96  | ±125 g, ±187 g, ±250 g, ±375 g, X-axis, positive/negative                   |   | 9g-cell_ClipHiX              | 1700              | 2100               | 2300               | g     | (9)   |

| 97  | ±250 g, Z-axis positive                                                     |   | gg-cell_ClipHiZP             | 2200              | 2700               | 3300               | g     | (9)   |

| 98  | ±250 g, Z-axis negative                                                     |   | 9g-cell_ClipHiZN             | -3700             | -3200              | -2700              | g     | (9)   |

|     | Sinc filter clipping limit                                                  |   |                              |                   |                    |                    |       |       |

| 99  | ±25 g, X-axis, positive/negative (MMA2702WR2)                               |   | 9ADC_Clip_25X_H              | 190               | 210                | 240                | g     | (9)   |

| 100 | ±125 g, X-axis, positive/negative (MMA2712WR2)                              |   | 9 <sub>ADC_Clip_125X_H</sub> | 920               | 1100               | 1300               | g     | (9)   |

| 101 | ±187 g, X-axis positive/negative (MMA2718WR2)                               |   | 9ADC_Clip_187X_H             | 1600              | 1900               | 2200               | g     | (9)   |

| 102 | ±250 g, X-axis positive/negative (MMA2725WR2)                               |   | 9ADC_Clip_250X_H             | 1600              | 1900               | 2200               | g     | (9)   |

| 103 | ±375 g, X-axis positive/negative (MMA2737WR2)                               |   | 9ADC_Clip_375X_H             | 1600              | 1900               | 2200               | g     | (9)   |

| 104 | ±250 g, Z-axis, positive (MMA1725WR2)                                       |   | GADC Clip 250ZPH             | 1500              | 2000               | 2500               | g     | (9)   |

| 105 | ±250 g, Z-axis, negative (MMA1725WR2)                                       |   | 9ADC_Clip_250ZNH             | -3200             | -2900              | -2500              | g     | (9)   |

## 2.6 Dynamic electrical characteristics - DSI3

$V_{BUS\_I\_L} \leq (V_{BUS\_I} - V_{SS}) \leq V_{BUS\_I\_H}, \ T_L \leq T_A \leq T_H, \ \Delta T \leq 12^{\circ} C/min, \ unless \ otherwise \ specified.$

| #          | S_LL > (VBUS_I - VSS) > VBUS_I_H, IL > IA > IH, AI > IZ<br>Characteristic            | Symbol                                                      | Min                   | Тур                  | Max                       | Units    |                |

|------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------|----------------------|---------------------------|----------|----------------|

|            | Reset recovery (all modes, excluding V <sub>BUS I</sub> voltage ramp time)           | -                                                           |                       |                      |                           |          |                |

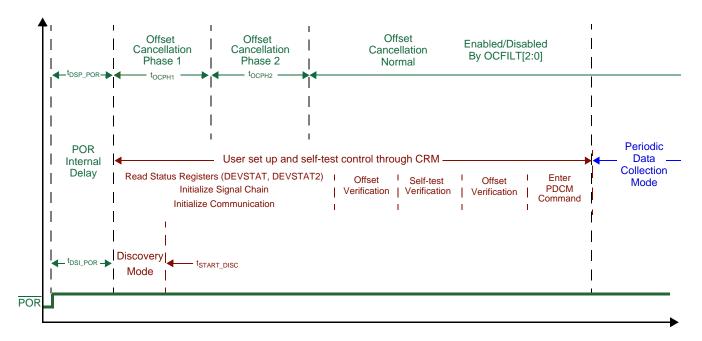

| 106        | POR to 1st command (Section 3.6)                                                     | t <sub>DSI POR</sub>                                        | _                     | 5                    | _                         | ms       | (7,8)          |

| 107        | POR to acceleration data ready (Section 3.6)                                         | t <sub>DSP_POR</sub>                                        | _                     | t <sub>DSI_POR</sub> | _                         | s        | (7,8)          |

|            | Command reception (general)                                                          |                                                             |                       |                      |                           |          |                |

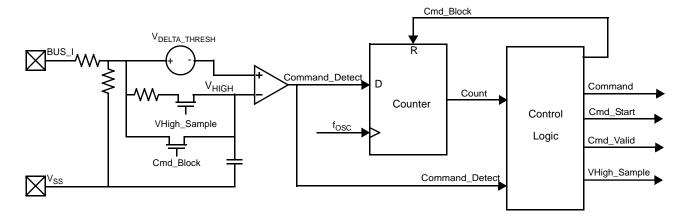

| 108        | V <sub>HIGH</sub> low-pass filter time constant (Section 3.6.1)                      | t <sub>VHIGH_RC</sub>                                       | 60                    | 120                  | 180                       | μs       | (8,9)          |

| 109        | V <sub>HIGH</sub> detection analog delay (Section 3.6.1)                             | t <sub>VHIGH_Delay</sub>                                    | _                     | _                    | 600                       | ns       | (8,9)          |

| 110        | i <sub>q</sub> low-pass filter time constant (Section 3.6.3)                         | $t_{IQ\_RC}$                                                | 200                   | 400                  | 600                       | μs       | (8,9)          |

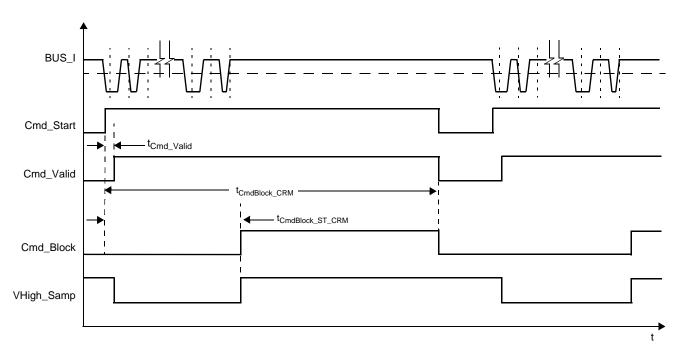

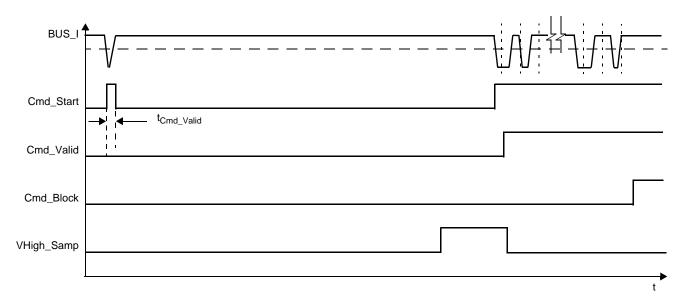

| 111        | Command valid time (Section 3.6.1)                                                   | t <sub>Cmd_Valid</sub>                                      | _                     | 2                    | _                         | μs       | (7,9)          |

|            | Response transmission (general, Section 4.2.3)                                       |                                                             |                       |                      |                           |          |                |

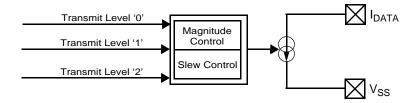

| 112        | Response slew time: 2.0 mA to 10.0 mA, 10.0 mA to 2.0 mA                             | t <sub>SLEW1_RESP</sub>                                     | 200                   | 400                  | 600                       | ns       | (6,8)          |

| 113        | Response slew time: 4.0 mA to 20.0 mA, 20.0 mA to 4.0 mA                             | t <sub>SLEW2_RESP</sub>                                     | 200                   | 400                  | 600                       | ns       | (6,8)          |

| 114        | tslew1_resp- tslew2_resp                                                             | $\Delta t_{\sf SLEW}$                                       | -100                  | _                    | 100                       | ns       | (8,9)          |

| 115        | <sup>t</sup> SLEW1_RESP_Rise <sup>-</sup> <sup>t</sup> SLEW2_RESP_Fall               | $\Delta t_{SLEW\_rf}$                                       | -250                  | _                    | 250                       | ns       | (8,9)          |

| 116        | Response current activation time: current activated to 50%                           | t <sub>ACT_RESP</sub>                                       | 200                   | 1                    | 400                       | ns       | (8,9)          |

|            | Command reception (Discovery Mode)                                                   |                                                             |                       |                      |                           |          |                |

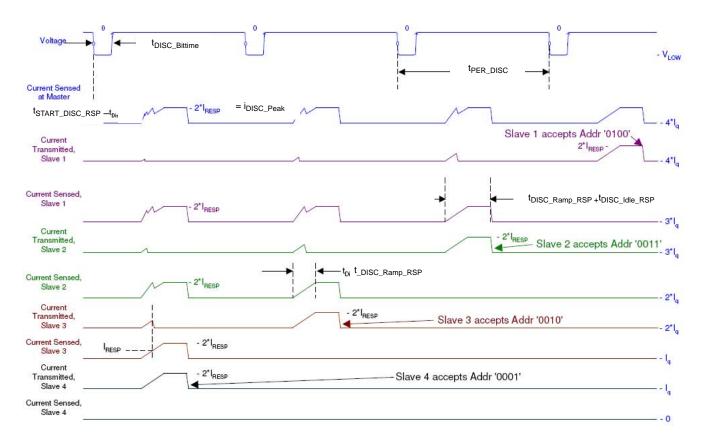

| 117        | Command start time (Section 4.1)                                                     | t <sub>START_DISC</sub>                                     | t <sub>DSI_POR</sub>  | _                    | 12                        | ms       | (7,8)          |

| 118        | Command bit time (Section 4.1)                                                       | t <sub>DISC_BitTime</sub>                                   |                       | 16                   | _                         | μs       | (7,8)          |

| 119        | Command transmission period (Section 4.1)                                            | t <sub>PER_DISC</sub>                                       | 1000/f <sub>OSC</sub> | _                    |                           | S        | (7,8)          |

| 120        | Command blocking time, Discovery Mode (Section 3.6.1)                                | t <sub>CmdBlock_DISC</sub>                                  | -                     | 96                   |                           | μs       | (7,8)          |

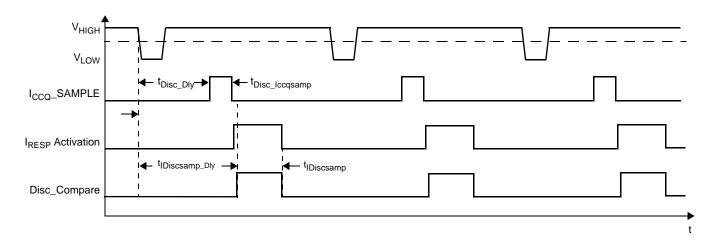

| 121<br>122 | I <sub>CCQ</sub> sample delay time (Section 3.6.3)                                   | t <sub>Disc_Dly</sub>                                       | _                     | 48                   |                           | μs       | (7,9)          |

| 122        | I <sub>CCQ</sub> sample time (Section 3.6.3)                                         | t <sub>Disc_Iccqsamp</sub>                                  |                       | 15                   |                           | μs       | (7,9)          |

| 124        | I <sub>DISC</sub> sample delay time (Section 3.6.3)                                  | t <sub>IDiscsamp_Dly</sub>                                  | _                     | 65<br>31             | _                         | μs       | (7,9)          |

|            | I <sub>DISC</sub> sample time (Section 3.6.3)                                        | t <sub>IDiscsamp</sub>                                      | _                     | 31                   | _                         | μs       | (7,9)          |

|            | Response transmission (Discovery Mode)                                               |                                                             |                       |                      |                           |          | ( <b>-</b> a)  |

| 125        | Response start delay (Section 4.1)                                                   | t <sub>START_DISC_RSP</sub>                                 | _                     | 64                   | _                         | μs       | (7,8)          |

| 126        | Response ramp time (Section 4.1)                                                     | <sup>t</sup> DISC_Ramp_RSP                                  | _                     | 16                   | _                         | μs       | (7,8)          |

| 127<br>128 | Response ramp rate (Section 4.1)                                                     | <sup>I</sup> DISC_Ramp                                      | _                     | 1.5                  | _                         | mA/μs    | (6,8)          |

| 129        | Response idle time (Section 4.1)                                                     | <sup>t</sup> DISC_ldle_RSP                                  | _                     | 16                   | _                         | μs       | (7,8)          |

| 120        | Response peak current (Section 4.1)                                                  | I <sub>DISC_Peak</sub>                                      | _                     | 2*I <sub>RESP</sub>  | _                         | mA       | (6,8)          |

|            | Command reception (Command and Response Mode)                                        | 4                                                           |                       | 0                    |                           |          | (7.0)          |

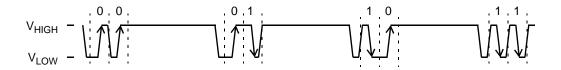

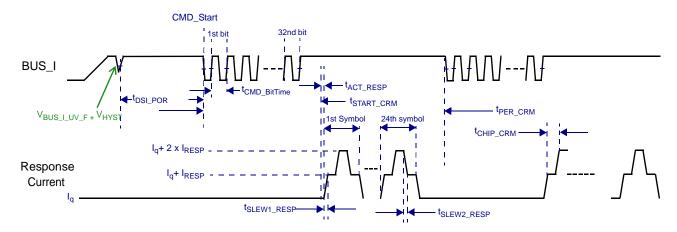

| 130        | Command bit time (Section 4.2)                                                       | <sup>t</sup> Cmd_BitTime                                    | _                     | 8                    | -                         | μs       | (7,8)          |

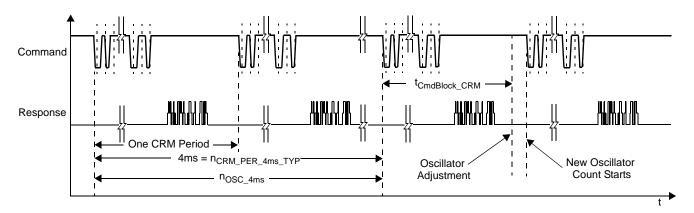

| 131<br>132 | Command transmission period (Section 4.2) Command blocking time, CRM (Section 3.6.1) | <sup>t</sup> PER_CRM                                        | t <sub>PER_PDCM</sub> | —<br>456             | 8 x t <sub>PER_PDCM</sub> | S        | (7,8)          |

| 133        | Command blocking start time, CRM (Section 3.6.1)                                     | <sup>t</sup> CmdBlock_CRM                                   |                       | 268                  |                           | μs<br>μs | (7,8)<br>(7,8) |

| 100        | Response transmission (Command and Response Mode)                                    | tCmdBlock_ST_CRM                                            |                       | 200                  | _                         | μο       | (1,0)          |

| 134        | Response transmission (Command and Response Mode)                                    | +                                                           |                       | 5                    |                           |          | (7,8)          |

| 135        | Response start time (Section 4.2)                                                    | t <sub>CHIP_CRM</sub>                                       |                       | 295                  |                           | μs       | (7,8)          |

| 100        | , ,                                                                                  | <sup>t</sup> START_CRM                                      |                       | 233                  | _                         | μs       | (1,0)          |

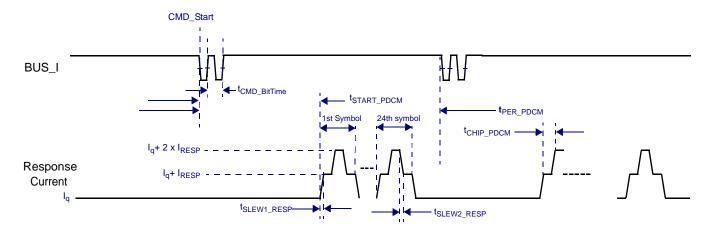

|            | Command reception (Periodic Data Collection Mode) Command bit time (Section 4.3)     | •                                                           |                       | 0                    |                           | 0        | (7.0)          |

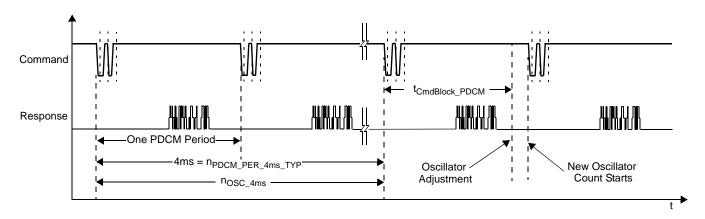

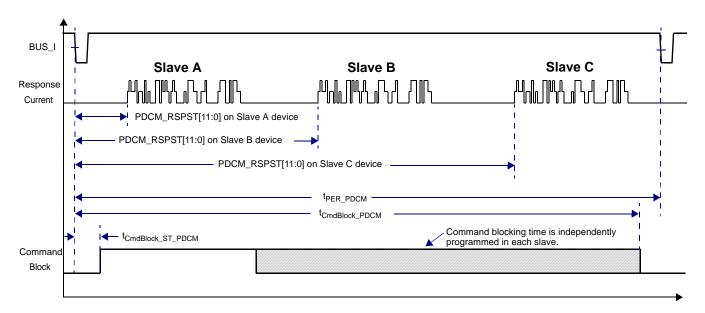

| 136        | Command transmission period (Section 4.3)                                            | t <sub>Cmd_BitTime</sub>                                    | 100                   | 8                    | 5000                      | μs       | (7,8)          |

| 137        | Command transmission period (Section 4.3)  Command transmission period resolution    | t <sub>PER_PDCM</sub>                                       | 100                   | <u> </u>             | 3000                      | μs       | (7,8)<br>(7,8) |

| 138<br>139 | Command blocking time, PDCM (Section 4.3.2)                                          | t <sub>PER_PDCM_Res</sub>                                   | 1                     | <u> </u>             | 4095                      | μs<br>μs | (7,8)          |

| 140        | Command blocking time resolution, PDCM (Section 4.3.2)                               | t <sub>CmdBlock_PDCM</sub><br>t <sub>CmdBlockRes_PDCM</sub> | _                     | 1                    | <del></del>               | μS       | (7,8)          |

| 141        | Command blocking start time, PDCM (Section 4.3.2)                                    | t <sub>CmdBlock_ST_PDCM</sub>                               | _                     | 20                   | _                         | μS       | (7,8)          |

| 142        | Command blocking start time, BDM command                                             | t <sub>CmdBlock_ST_BDM</sub>                                | _                     | 44                   | _                         | μS       | (7,8)          |

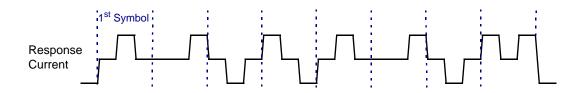

|            | Response transmission (Periodic Data Collection Mode)                                | CHIRDIOCK_21_RDIM                                           |                       | • •                  |                           |          | ( , , , ,      |

| 143        | Response chip time typical (Section 3.1.15.3)                                        | tourn prove                                                 | 3                     | _                    | 6.5                       | μs       | (7,8)          |

| 143        | Response chip resolution (Section 3.1.15.3)                                          | <sup>t</sup> CHIP_PDCM<br><sup>t</sup> CHIPRes_PDCM         |                       | 0.5                  | -                         | μS       | (7,8)          |

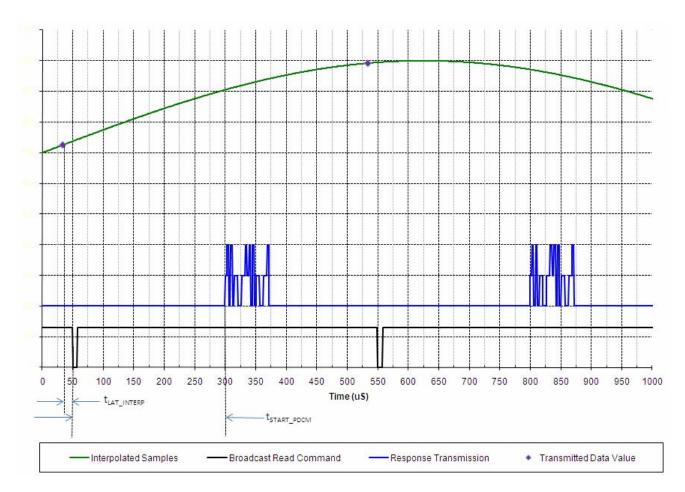

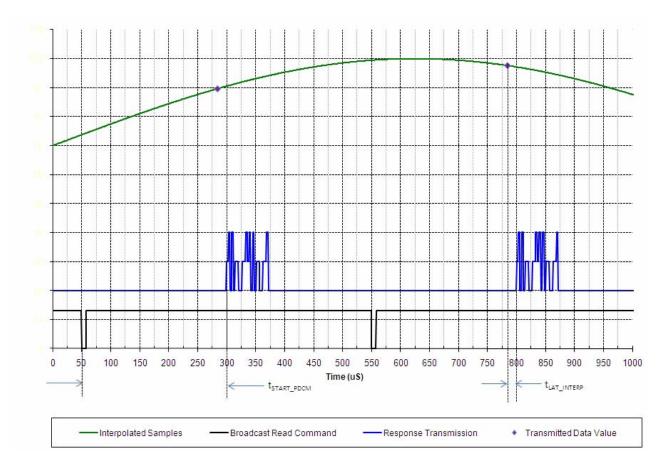

| 145        | Response start time typical (Section 4.3)                                            | t <sub>START_PDCM</sub>                                     | 20                    | _                    | 4095                      | μs       | (7,8)          |

| 146        | Response start time typical, BDM enabled (Section 4.3)                               | t <sub>START_PDCM_BDM</sub>                                 | 44                    | _                    | 4095                      | μs       | (7,8)          |

| 147        | Response start time resolution                                                       | t <sub>ST RES PDCM</sub>                                    | _                     | 1                    | _                         | μs       | (7,8)          |

|            | Response transmission (Background Diagnostic Mode)                                   | O1_INEO_I DOW                                               |                       |                      |                           | *        | ` ′            |

| 148        | Response start time (Section 4.3)                                                    | t <sub>START_BDM</sub>                                      | _                     | 20                   | _                         | μs       | (7,8)          |

|            | Register write to BUSSW active                                                       |                                                             |                       | 456                  |                           |          | (7,8)          |

|            |                                                                                      | t <sub>BS</sub>                                             |                       |                      |                           | μs       |                |

| 150        | DSI data latency                                                                     | t <sub>LAT_DSI</sub>                                        | _                     | 0.5                  | 6.25                      | μs       | (7,9)          |

|            | OTP program timing                                                                   |                                                             | Ī                     |                      | 1                         |          | Ì              |

| 151        | Time to program the user OTP array                                                   |                                                             |                       |                      | 60                        | ms       | (7,8)          |

## 2.7 Dynamic electrical characteristics - signal chain

$V_{BUS\_I\_L} \leq (V_{BUS\_I} - V_{SS}) \leq V_{BUS\_I\_H}, \ T_L \leq T_A \leq T_H, \ \Delta T \leq 12 \ ^{\circ}C/min, \ unless \ otherwise \ specified.$  **Table 3.**

| #                                                                                              | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Symbol                                                                                                                                                                                                                    | Min                                                                                                 | Тур                                                               | Max                                    | Units                                             |                                                                                        |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------|

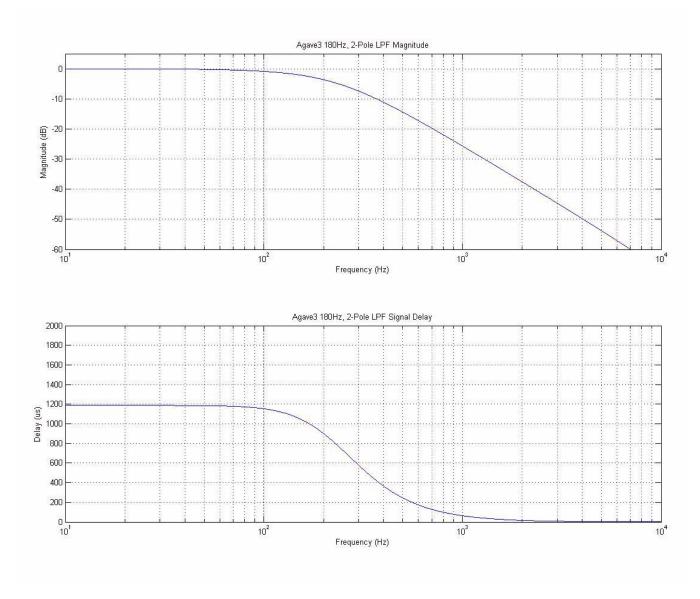

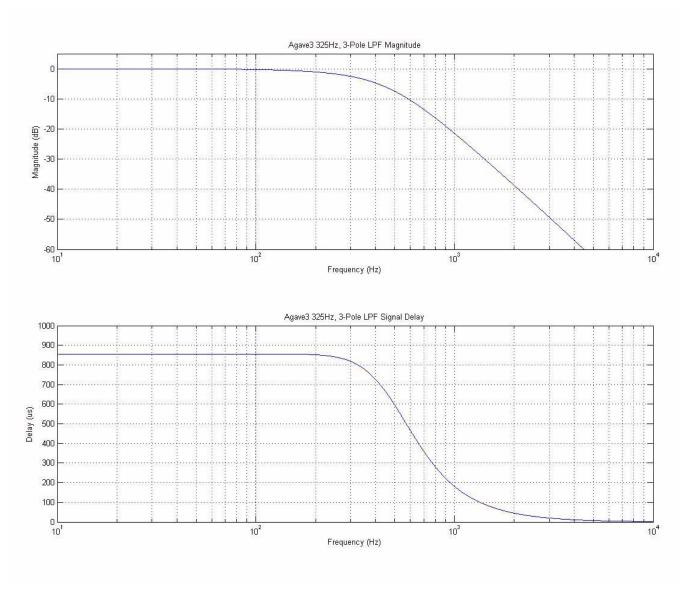

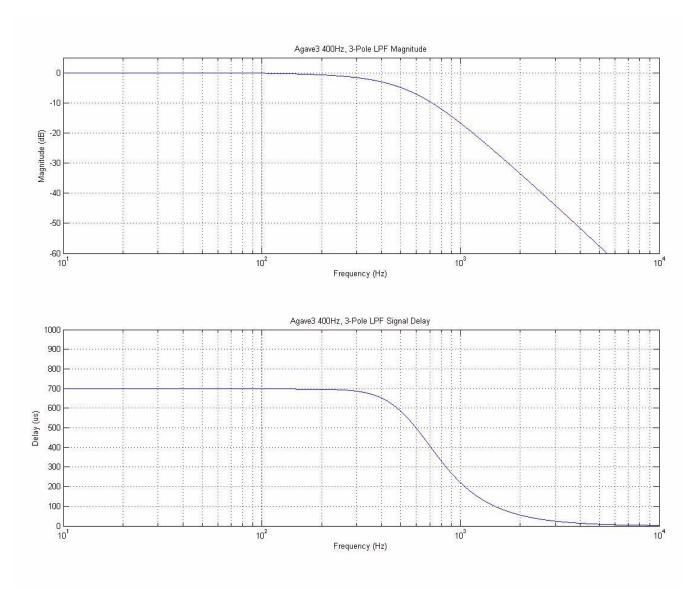

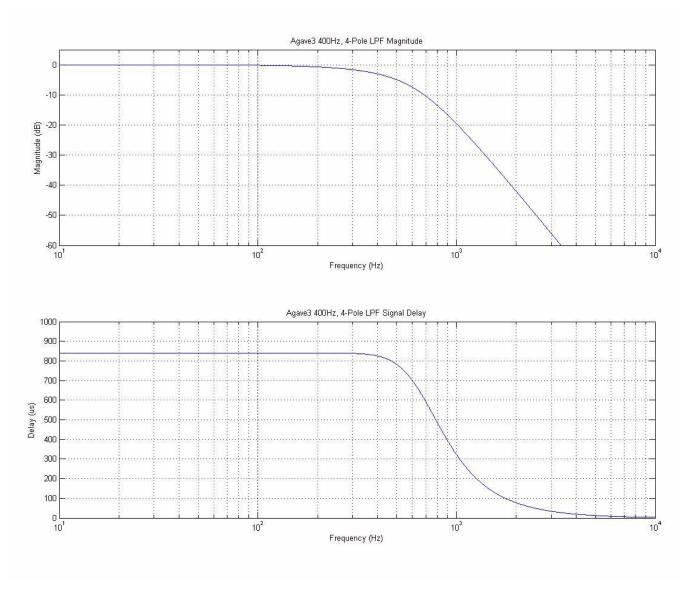

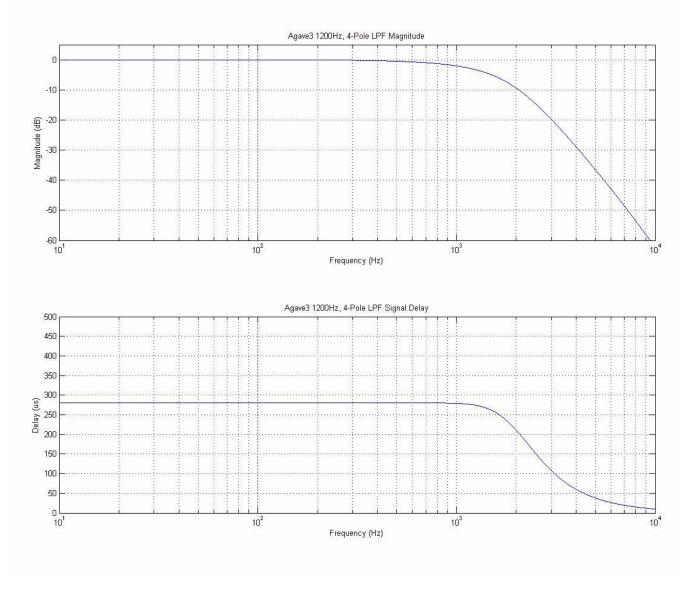

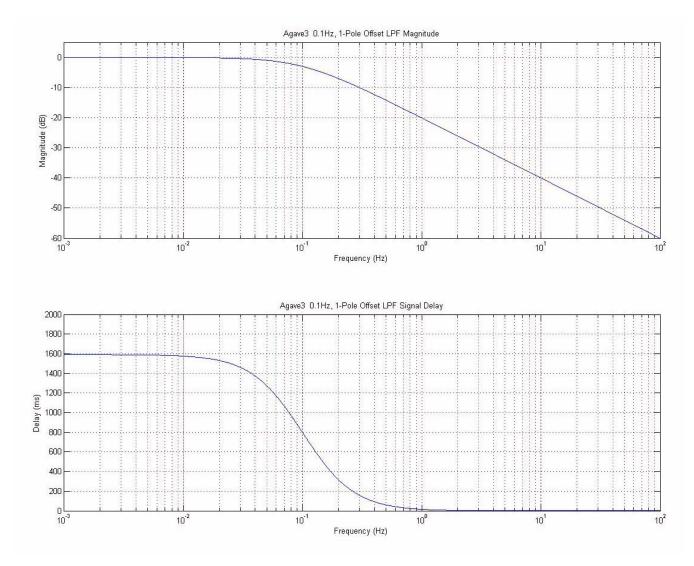

| 152<br>153<br>154<br>155<br>156<br>157<br>158                                                  | DSP low-pass filter Cutoff frequency LPF0, 2-pole (referenced to 0 Hz) Cutoff frequency LPF6, 3-pole (referenced to 0 Hz) Cutoff frequency LPF8, 3-pole (referenced to 0 Hz) Cutoff frequency LPF9, 4-pole (referenced to 0 Hz) Cutoff frequency LPF11, 4-pole (referenced to 0 Hz) Cutoff frequency LPF14, 4-pole (referenced to 0 Hz)  * Cutoff frequency LPF14, 4-pole (referenced to 0 Hz)                                                                                                                                                                                                                                                                                                                                                                                  | f <sub>C_LPF0</sub> f <sub>C_LPF6</sub> f <sub>C_LPF8</sub> f <sub>C_LPF9</sub> f <sub>C_LPF11</sub> f <sub>C_LPF14</sub>                                                                                                 | _<br>_<br>_<br>_<br>_                                                                               | 180<br>325<br>400<br>400<br>800<br>1200                           | _<br>_<br>_<br>_<br>_                  | Hz<br>Hz<br>Hz<br>Hz<br>Hz<br>Hz                  | (6,7)<br>(6,7)<br>(7,8)<br>(7,8)<br>(7,8)<br>(7,8)                                     |

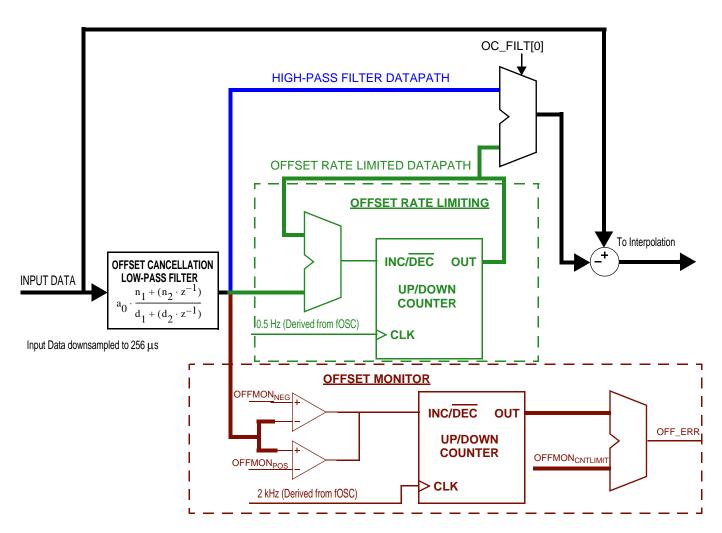

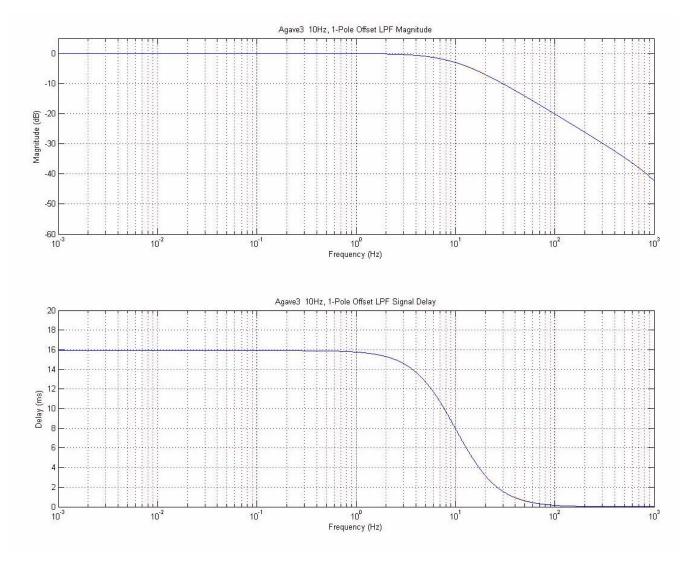

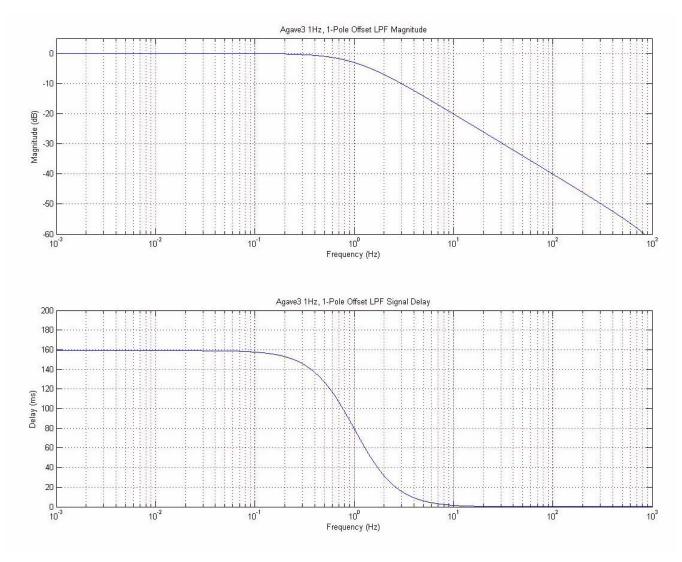

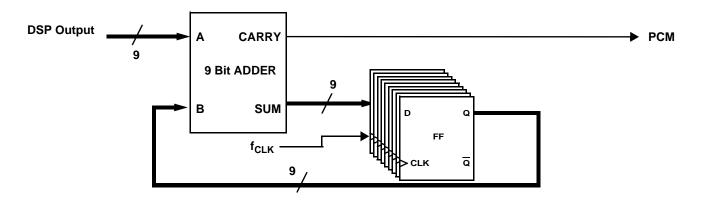

| 159<br>160<br>161<br>162<br>163<br>164<br>165<br>166<br>167                                    | DSP offset cancellation low-pass filter Offset Cancellation low-pass filter Input sample Rate Cutoff frequency, startup Phase 1, 1-pole Startup Phase 1 time Cutoff frequency, startup Phase 2, 1-pole Startup Phase 2 time Offset cancellation output update rate (10-bit) Offset cancellation output step size (10-bit) Offset monitor update rate Offset monitor count limit Offset monitor counter size                                                                                                                                                                                                                                                                                                                                                                     | toc_SampleRate fc_OCPH1 toCPH1 fc_OCPH2 toCPH2 toffRate OFFStep OFFMONOSC OFFMONCNTLIMIT OFFMONCNTSIZE                                                                                                                    | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-                                                                | 256<br>10.0<br>80<br>1.0<br>70<br>2<br>0.5<br>500<br>4096<br>8192 | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-   | μs<br>Hz<br>ms<br>Hz<br>ms<br>s<br>LSB<br>μs<br>1 | (7,9)<br>(7,9)<br>(7,9)<br>(7,9)<br>(7,9)<br>(7,9)<br>(7,9)<br>(7,8)<br>(7,8)<br>(7,8) |

| 169                                                                                            | Signal delay excluding LPF group delay and interpolation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | t <sub>SIG_DELAY</sub>                                                                                                                                                                                                    | _                                                                                                   | _                                                                 | 100                                    | μs                                                | (7,9)                                                                                  |

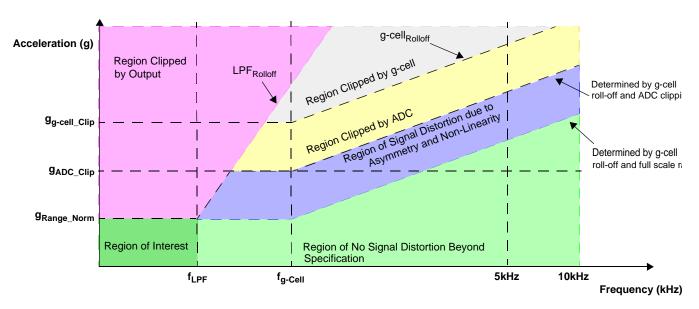

| 170<br>171<br>172<br>173<br>174<br>175<br>176<br>177<br>178<br>179<br>180<br>181<br>182<br>183 | Interpolation latency  Self-test response time (CS Rising to 90% g <sub>ST10_xxx</sub> )  Self-test activation time (180 Hz LPF)  Self-test deactivation time (180 Hz LPF)  Self-test activation time (325 Hz LPF, 3 Pole)  Self-test deactivation time (325 Hz LPF, 3 Pole)  Self-test deactivation time (400 Hz LPF, 3 or 4 Pole)  Self-test deactivation time (400 Hz LPF, 3 or 4 Pole)  Self-test activation time (800 Hz LPF)  Self-test deactivation time (800 Hz LPF)  Self-test activation time (1200 Hz LPF)  Self-test deactivation time (1200 Hz LPF)  Self-test deactivation time (1200 Hz LPF)  Sensing element rolloff frequency (-3 db)  ±25 g, X-axis  ±125 g, ±187 g, ±250 g, ±375 g, X-axis  ±250 g, Z-axis  Sensing element natural frequency  ±25 g, X-axis | tst_act_180 tst_act_180 tst_deact_180 tst_deact_180 tst_act_325 tst_act_400 tst_act_400 tst_act_800 tst_act_800 tst_act_800 tst_act_800 tst_act_800 tst_deact_800 tst_deact_800 tst_deact_800 tst_deact_800 tst_deact_800 | 2.00<br>2.00<br>1.30<br>1.30<br>1.00<br>1.00<br>0.50<br>0.50<br>0.40<br>0.40<br>938<br>3952<br>3100 | 16  1600 7200 4500                                                |                                        | ms ms ms ms ms ms ms ms Hz Hz                     | (7,9) (3,6) (3,6) (6) (6) (6) (6) (6) (6) (6) (6) (6) (                                |

| 185<br>186<br>187<br>188<br>189                                                                | ±125 g, ±187 g, ±250 g, ±375 g, X-axis<br>±250 g, Z-axis<br>Sensing element damping ratio<br>±25 g, X-axis<br>±125 g, ±187 g, ±250 g, ±375 g, X-axis<br>±250 g, Z-axis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | fgcell_xhi fgcell_zhi  Sgcell_xlo Sgcell_xhi Sgcell_xhi Sgcell_xhi                                                                                                                                                        | 26000<br>15000<br>2.76<br>1.26<br>1.40                                                              | 27500<br>17000<br>4.20<br>2.00<br>2.00                            | 28700<br>17500<br>6.77<br>3.60<br>2.90 | Hz<br>Hz                                          | (9)<br>(9)<br>(9)<br>(9)<br>(9)<br>(9)                                                 |

| 190<br>191<br>192<br>193                                                                       | Sensing element delay (@100 Hz)  ±25 g, X-axis  ±125 g, ±187 g, ±250 g, ±375 g, X-axis  ±250 g, Z-axis  Package resonance frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | fgcell_delay100_xlo fgcell_delay100_xhi fgcell_delay100_zhi fPackage                                                                                                                                                      | 63<br>13<br>35                                                                                      | 100<br>24<br>40<br>—                                              | 170<br>40<br>55<br>—                   | μs<br>ms<br>μs<br>kHz                             | (9)<br>(9)<br>(9)<br>(9)                                                               |

## 2.8 Dynamic electrical characteristics - supply and support circuitry

$V_{BUS\_I\_L} \leq (V_{BUS\_I} - V_{SS}) \leq V_{BUS\_I\_H}, \ T_L \leq T_A \leq T_H, \ \Delta T \leq 12 \ ^{\circ}C/min, \ unless \ otherwise \ specified$

| #                        | Characteristic                                                                                                                                                                                                             | Symbol                                                                                                 | Min                | Тур               | Max               | Units                |                          |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------|-------------------|-------------------|----------------------|--------------------------|

| 194<br>195               | Internal oscillator period Untrained * With oscillator training                                                                                                                                                            | fosc<br>fosc                                                                                           | 7.600<br>7.879     | 8.000<br>8.000    | 8.400<br>8.121    | MHz<br>MHz           | (1)<br>(7,8,9)           |

| 196<br>197<br>198<br>199 | Oscillator training (Section 3.4.1) Oscillator training time (CRM and PDCM) Oscillator training window (CRM and PDCM) Oscillator training adjustment threshold (CRM and PDCM) Oscillator training step size (CRM and PDCM) | t <sub>OscTrain</sub><br>OscTrain <sub>WIN</sub><br>OscTrain <sub>ADJ</sub><br>OscTrain <sub>RES</sub> | <br>3.4<br>-60<br> | 4<br>—<br>—<br>28 | <br>4.6<br>60<br> | ms<br>ms<br>µs<br>µs | (7)<br>(7)<br>(7)<br>(7) |

| 200                      | Quiescent current settling time (power applied to Iq = I <sub>IDLE</sub> ±2 mA)                                                                                                                                            | t <sub>SET</sub>                                                                                       | _                  | _                 | 4                 | ms                   | (6)                      |

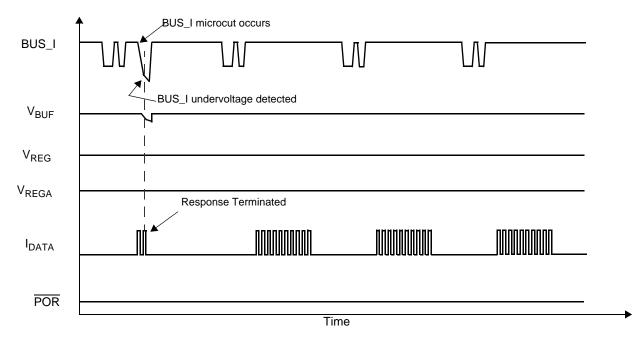

| 201<br>202               | BUS_I microcut Survival time (BUS_I disconnect without reset, $C_{BUF} = C_{REG} = C_{REGA} = 700 nF$ ) Reset time (BUS_I disconnect time to reset, $C_{BUF} = C_{REG} = C_{REGA} = 1 \mu F$ )                             | t <sub>BUS_I_MICROCUT</sub>                                                                            | 30<br>—            |                   | _<br>1000         | μs<br>μs             | (8)<br>(8)               |

| 203                      | BUS_I undervoltage detection delay BUS_I < V <sub>BUS_I_UV_F</sub> to I <sub>RESP</sub> deactivation                                                                                                                       | t <sub>BUS_I_POR</sub>                                                                                 | _                  | _                 | 5                 | μs                   | (6)                      |

| 204                      | $V_{BUF}$ undervoltage detection delay $V_{BUF} < V_{BUF_{UV_F}}$ to $I_{RESP}$ deactivation                                                                                                                               | t <sub>VBUF_POR</sub>                                                                                  | _                  | _                 | 5                 | μs                   | (6)                      |

| 205                      | V <sub>REG</sub> , V <sub>REGA</sub> undervoltage reset delay V <sub>REG</sub> < V <sub>REG_UV_F</sub> to POR assertion, V <sub>REGA</sub> < V <sub>REGA_UV_F</sub> to POR assertion                                       | t <sub>VREG_POR</sub>                                                                                  | _                  | _                 | 50                | μs                   | (6)                      |

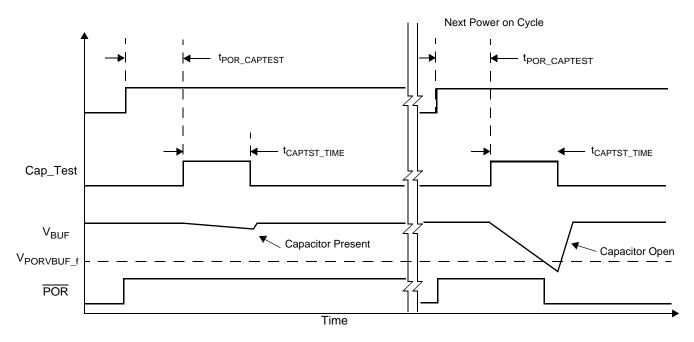

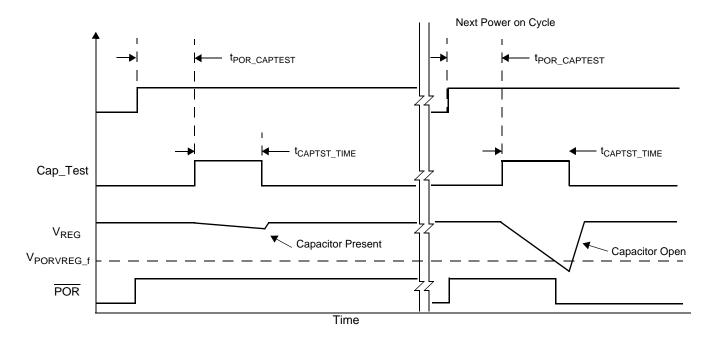

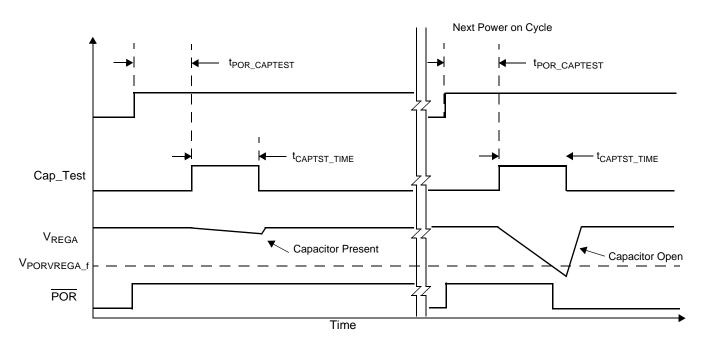

| 206<br>207               | V <sub>BUF</sub> , V <sub>REG</sub> , V <sub>REGA</sub> capacitor monitor POR to capacitor disconnect Disconnect time                                                                                                      | tpor_captest<br>tcaptst_time                                                                           |                    | 950<br>1.5        | _                 | μs<br>μs             | (7,8)<br>(7,8)           |

### **NOTES**

- 1. Parameter tested 100% at final test. Temperature = -40°C, 25°C and 105°C, V<sub>BUS\_I</sub> = 8 V, Unless otherwise stated.

- 2. Not Applicable.

- 3. Parameter verified by pass/fail testing at final test

- 4. Parameter verified by pass/fail testing at final test during safe launch.

- 5. Parameter verified by qualification testing.

- 6. Parameter verified by characterization.

- 7. Functionality guaranteed by modeling, simulation and/or design verification. Circuit integrity assured through IDDQ and scan testing. Timing is determined by internal system clock frequency.

- 8. Parameter verified by functional evaluation.

- 9. Parameter verified by simulation.

- 10. Not Applicable.

- 11. Thermal resistance between the die junction and the exposed pad; cold plate is attached to the exposed pad.

- \* Indicates critical characteristic.

## 3 Functional Description