# **ORCA® ORSPI4**

Dual SPI4 Interface and High-Speed SERDES FPSC

November 2003 Preliminary Data Sheet

Lattice Semiconductor has developed a next-generation FPSC targeted at high-speed data transmission. Built on the Series 4 reconfigurable embedded System-on-a-Chip (SoC) architecture, the ORSPI4 FPSC contains two SPI4.2 interface blocks, a high-speed Memory Controller, four channels of 0.6-3.7 Gbits/s SERDES with 8b/10b encoding and decoding and over 600K programmable system gates all on a single chip.

# **Embedded SPI4 Core Features**

- OIF-SPI4-02.0 compliant interfaces

- Dynamic timing receive interface:

- Full bandwidth up to 450 MHz DDR (900 Mbits/s) for all speed grades.

- · Bit de-skewing up to 16 phases of the clock

- Capable of aligning bit-to-bit skews as large as ±1 bit periods

### ■ Static timing receive interface:

- Speeds up to 350 MHz DDR (700 Mbits/s), for all speed grades, including Quarter-Rate mode

- Clock aligned or clock centered modes supported

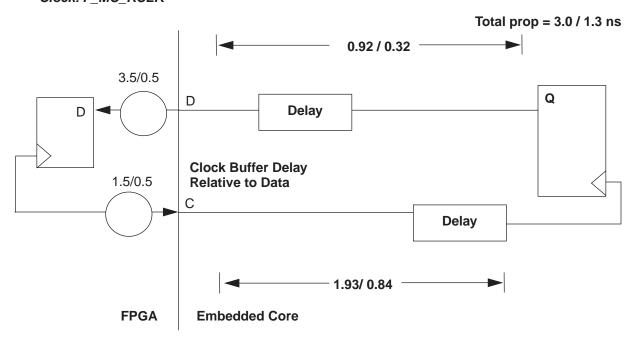

- DIP-4 and DIP-2 parity generation and checking

#### ■ Transmit Interface:

- Speeds up to 450 MHz DDR (900 Mbits/s)

- Dedicated LVDS transmit interface for improved data eye integrity

- · Automatic idle insertion

## ■ 256 logical ports:

- Embedded Calendar-based sequence port polling mechanism and bandwidth allocation.

Shadow Calendar support for smooth transition to new Calendar

- Up to 32 independent TX and 32 independent RX buffers per SPI4 interface internally. Various aggregation modes to support 1 to 32 separate embedded buffers per TX and RX

- Up to 4 independent TX and 4 independent RX clock domain transfers to the FPGA logic

## ■ FIFO status support modes:

- 1/4 rate LVTTL or 1/4 rate LVDS

- Automatic status handling or optionally under user control. Credit calculations based on burst size and status are also handled automatically

#### Configuration options as suggested in the OIF-SPI4-02.0 standard

Configures parameters such as maximum burst size, calendar length, main and shadow calendars (1K deep each), length of training sequence etc.

# Simple FIFO interface to the FPGA logic

- Provides ease of design and efficient clock domain transfers

- Loopback modes provided for system- and chip-level debug

- Embedded 32-bit internal system bus plus 4-bit parity

- Interconnects FPGA logic, microprocessor interface (MPI), embedded RAM blocks, and embedded core blocks

- Includes built-in system registers that act as the control and status center for the device

### ■ Low power operation.

- Full-rate SPI4.2 interfaces running at 450 MHz DDR (900 Mbits/sec) with dynamic alignment consumes 2 W of power or less. More efficient than FPGAs with soft-IP SPI4 solutions which consume in excess of 10 W.

- Interoperability demonstrated with ORSPI4 partners.

### **Embedded SERDES Core Features**

- Quad 600 Mbits/s to 3.7 Gbits/s SERDES:

- IEEE 802.3ae XAUI (Link State Machine & Alignment FIFOs embedded)

- ANSI X3.230:1994 1G/2G FC-compliant (Link State Machine & Alignment FIFOs embedded)

- Proven performance (same SERDES used in ORT82G5/ORT42G5 FPSCs)

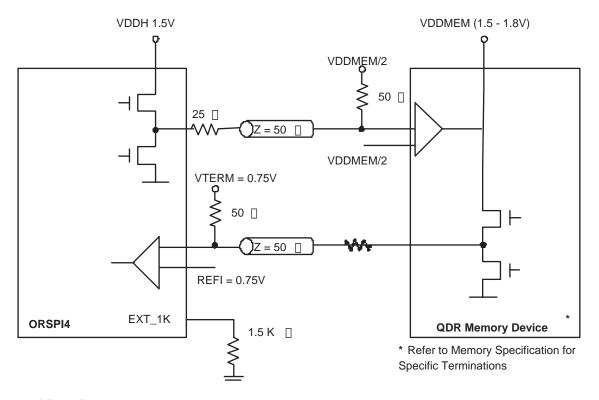

# **Embedded Memory Controller Features**

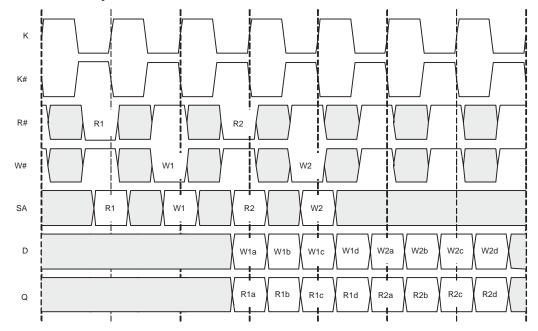

- High Performance Memory Controller for interface to external buffer memory

- Required for Layer 2 data buffering

- QDR II memory interface:

- 36-bit Input and 36-bit Output bus, 18-bit address

- 200 MHz clock rates

- 20+ Gbits/s bandwidth

- Supports 2- or 4-word burst mode

- Simple FIFO interface to FPGA

- Integrated PLL for optimized performance

- Proven performance with multiple memory suppliers

Note: The term SPI4 refers to OIF SPI-4.2 throughout this document

© 2003 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

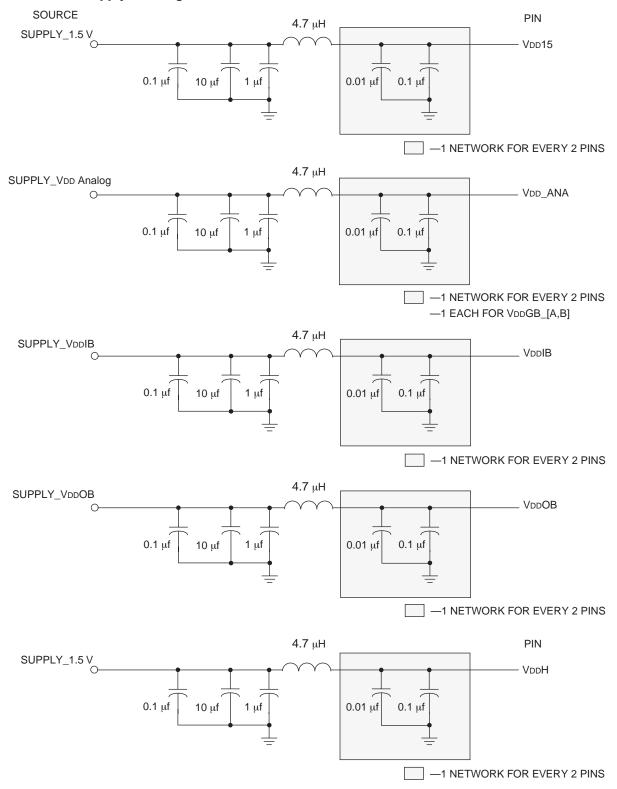

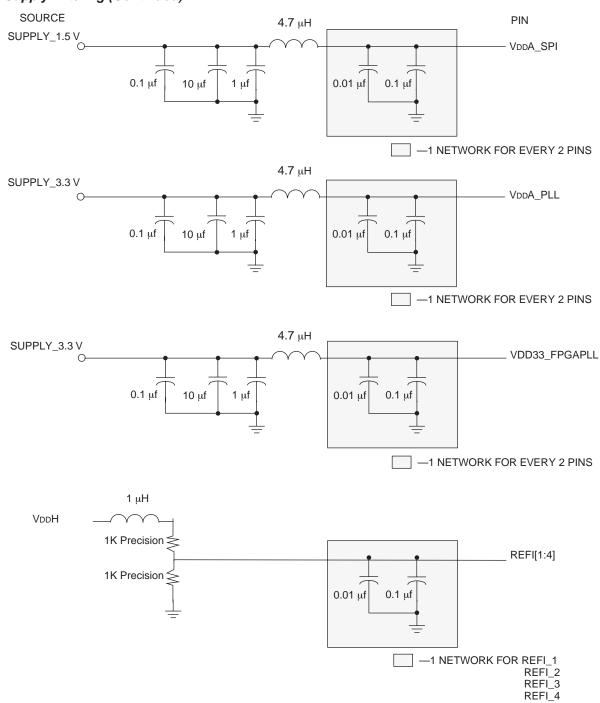

# **High-Speed ORCA Series 4 FPGA**

- Internal performance of > 250 MHz

- Over 16K programmable logic elements

- 1.5V operation (30% less power than 1.8 V operation)

- Comprehensive I/O selections including LVTTL, LVCMOS, GTL, GTL+, PECL, SSTL3/2, HSTL, ZBT, DDR, LVDS, bused-LVDS, and LVPECL

- 1036-pin fpSBGA package provides enough FPGA user I/Os (498) for 4 full-duplex XGMII interfaces, 4 full-duplex PL-3 interfaces, etc; a 40% smaller 1156-pin fpBGA package is available with 356 FPGA user I/Os

# Introduction

The SPI4 blocks provide dual 10 Gbits/s physical-to-link layer interfaces in conformance to the OIF-SPI4-02.0 specification. Each block provides a full-duplex interface with an aggregate bandwidth of 13.6 Gbits/s. This is achieved by using 16 LVDS pairs each for RX and TX operating at a maximum data rate of 900 Mbits/s with a 450 MHz DDR clock. Both static and dynamic alignment are supported at the receive interface. Dynamic alignment is used to compensate for bit-to-bit skew at higher data rates, where it becomes difficult to meet tight setup/hold requirements. DIP-4 and DIP-2 parity generation and checking are supported. Data buffering of 8K bytes for both transmit and receive is provided by embedded Dual-Port RAM in each SPI4 core. Internal 1K deep main and shadow calendar supports scheduling of up to 256 ports. The Transmit and Receive Status FIFOs can also store flow control information for up to 256 ports, the maximum specified in the SPI4 specification.

An independent QDRII Memory Controller block provides data buffering between the FPGA logic and external memory and supports a throughput of greater than 20 Gbits/s. Data is transferred to and from memory through two sets of 36-bit unidirectional data lines operating at up to 200 MHz DDR. A set of 72 data signals is available to transfer data across the core-FPGA interface and allows the system to utilize the bandwidth available with second-generation Quad Data Rate (QDRII) SRAMs. Of the 72 data signals, 8 signals can be either used for parity or data. A soft IP version of this core is also available to allow a second data buffer on this device.

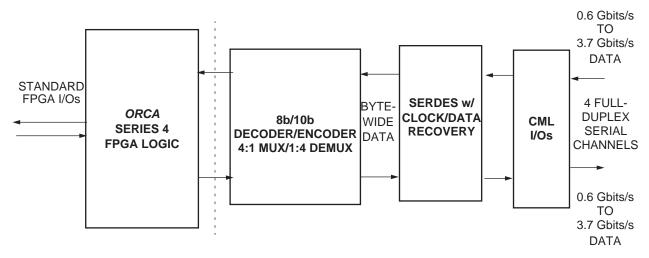

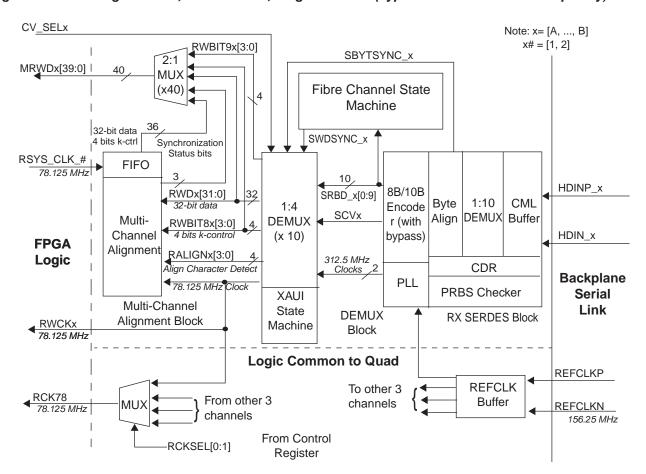

The High-Speed SERDES block supports four serial links, each operating at up to 3.7 Gbits/s (2.96 Gbits/s data rate with 8b/10b encoding and decoding), to provide four full-duplex synchronous interfaces with built-in RX Clock and Data Recovery (CDR) and transmitter preemphasis. The SERDES block is identical to that in the ORT82G5 FPSC, supports embedded 8b/10b encoding/decoding and implements link state machines for both 10G Ethernet, and 1G/2G/10G Fibre Channel. The state machines are IEEE P802.3ae/D4.01 XAUI based and also support FC (ANSI X3.230:1994) link synchronization.

Table 1. ORCA ORSPI4 — Available FPGA Logic

| Device | PFU Rows | PFU<br>Columns | Total PFUs | FPGA Max<br>User I/O | LUTs   | EBR<br>Blocks | EBR Bits<br>(K) | Usable*<br>Gates (K) |

|--------|----------|----------------|------------|----------------------|--------|---------------|-----------------|----------------------|

| ORSPI4 | 46       | 44             | 2,024      | 498/356              | 16,192 | 16            | 148             | 471-899              |

Note: The embedded core, embedded system bus, FPGA interface and MPI are not included in the above gate counts. The System Gate ranges are derived from the following: Minimum System Gates assumes 100% of the PFU's are used for logic only (No PFU RAM) with 40% EBR usage and 2 PLL's. Maximum System Gates assumes 80% of the PFU's are for logic, 20% are used for PFU RAM, with 80% EBR usage and 4 PLL's.

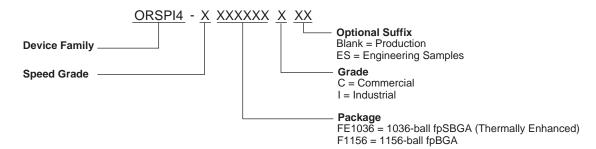

The ORSPI4 device is offered in two packages: 1036 fpSBGA and 1156 fpBGA. The 1036 package offers 498 FPGA User I/Os while the 1156 package offers 356 FPGA User I/Os. Additionally, the SERDES option is not available on the 1156 package.

# **ORSPI4 Overview**

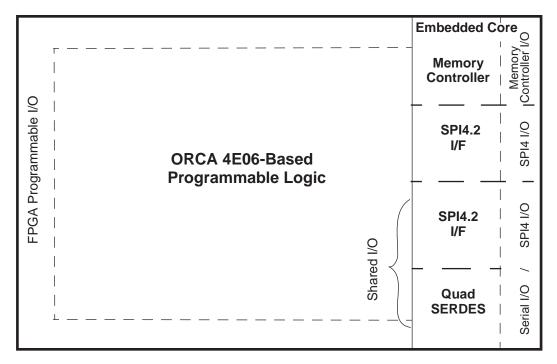

The ORSPI4 FPSC provides two SPI4.2 interface blocks, a Memory Controller and a 4-channel SERDES block, combined with FPGA logic. Based on the 1.5 V OR4E06 ORCA FPGA, it has a 46 x 44 array of Programmable Logic Cells (PLCs). The embedded core is attached to the right side of the device, as shown below, and is integrated directly into the FPGA array. A top level diagram of the basic chip configuration is shown in Figure 1.

Figure 1. ORSPI4 Basic Chip Configuration

Each of the logic blocks in the embedded core is functionally independent from the other blocks. Connections between blocks must be made through the FPGA logic. However, one of the SPI4 blocks and the SERDES block share I/Os. Hence the device may be configured to provide either two SPI4 interfaces or one SPI4 interface and one serial interface.

#### What Is an FPSC?

FPSCs, or Field-Programmable System Chips, are devices that combine field-programmable logic with ASIC or mask-programmed logic on a single device. FPSCs provide the time to market and the flexibility of FPGAs, the design effort savings of soft Intellectual Property (IP) cores, and the speed, design density, and economy of ASICs.

# **FPSC Overview**

Lattice's Series 4 FPSCs are created from Series 4 *ORCA* FPGAs. To create a Series 4 FPSC, several columns of Programmable Logic Cells are integrated with an embedded logic core. Other than replacing some FPGA gates with ASIC gates, at greater than 10:1 area efficiency, none of the FPGA functionality is changed—all of the Series 4 FPGA capability is retained including the Embedded Block RAMs, MicroProcessor Interface (MPI), boundary scan, etc. Pins from the replaced columns of programmable logic are used as I/O pins for the embedded core. The remainder of the device pins retain their FPGA functionality.

# **FPSC Gate Counting**

The total gate count for an FPSC is the sum of its embedded core (standard-cell/ASIC gates) and its FPGA gates. Because FPGA gates are generally expressed as a usable range with a nominal value, the total FPSC gate count is sometimes expressed in the same manner. Standard-cell ASIC gates are, however, 10 to 25 times more silicon-

area efficient than FPGA gates. Therefore, an FPSC with an embedded function is gate equivalent to an FPGA with a much larger gate count.

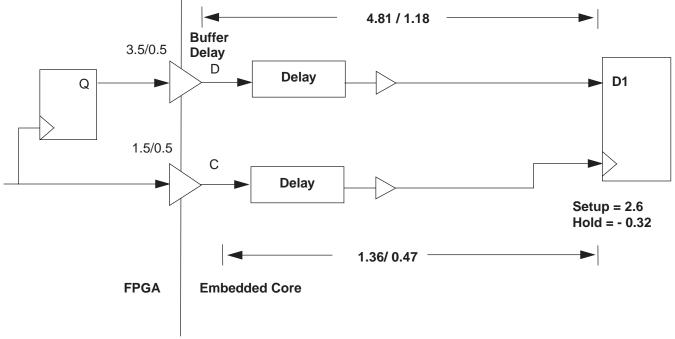

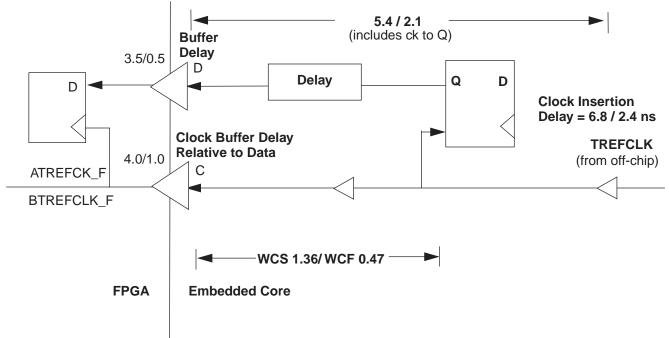

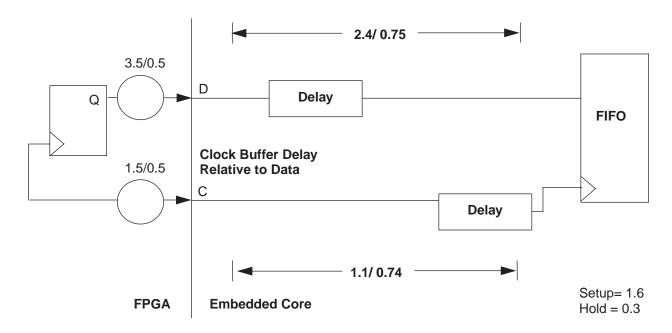

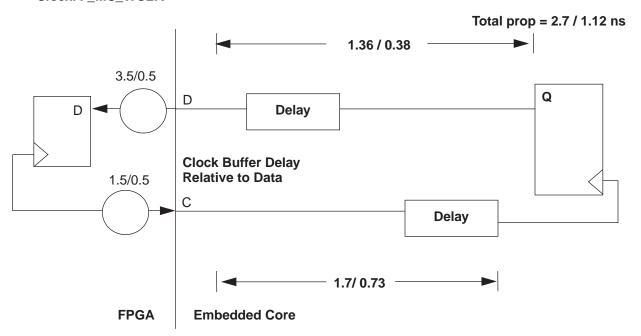

## **FPGA/Embedded Core Interface**

The interface between the FPGA logic and the embedded core has been enhanced to allow for a greater number of interface signals than on previous FPSC architectures. Compared to bringing embedded core signals off-chip, this on-chip interface is much faster and requires less power. All of the delays for the interface are precharacterized and accounted for in the *ispLEVER* Development System.

Series 4 based FPSCs expand this interface by providing a link between the embedded block and the multi-master 32-bit system bus in the FPGA logic. This system bus allows the core easy access to many of the FPGA logic functions including the Embedded Block RAMs and the microprocessor interface.

Clock spines also can pass across the FPGA/embedded core boundary. This allows for fast, low-skew clocking between the FPGA and the embedded core. Many of the special signals from the FPGA, such as DONE and global set/reset, are also available to the embedded core, making it possible to fully integrate the embedded core with the FPGA as a system.

For even greater system flexibility, FPGA configuration RAMs are available for use by the embedded core. This allows for user-programmable options in the embedded core, in turn allowing for greater flexibility. Multiple embedded core configurations may be designed into a single device with user-programmable control over which configurations are implemented, as well as the capability to change core functionality simply by reconfiguring the device.

# **FPSC Design Kit**

Development is facilitated by an FPSC design kit which, together with *ispLEVER* and third-party synthesis and simulation engines, provides all software and documentation required to design and verify an FPSC implementation. Included in the kit are the FPSC configuration manager, and compiled *Verilog* simulation models, *HSPICE* and/or IBIS models for I/O buffers, and complete online documentation. The kit's software coupled with *the* design environment, provides a seamless FPSC design environment. More information can be obtained by visiting the Lattice website at

http://www.latticesemi.com.

#### **SPI4 Protocol Overview**

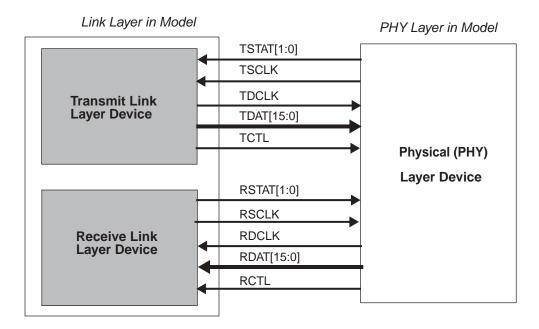

The System Packet Interface Level 4, Phase 2 (SPI4) was defined by the Optical Internetworking Forum (OIF) as an interface for packet and cell transfers between a Physical Layer (PHY) device and a link layer device for applications requiring up to 10 Gbit/s aggregate bandwidth. The system level model for the SPI4 interface is shown in Figure 2.

Figure 2. System Model for SPI4 Interface

The details of the interface are specified in the OIF document "Implementation Agreement OIF-SPI4-02.0" (www.oiforum.com). That specification is based on the system model shown in the previous figure, which, in turn, is based on the Open System Interconnect (OSI) reference model. In the system model, a "transmit interface" sends address, start and end of packet signals and error control information from a Link Layer device to a PHY device and receives flow control (status) information from the PHY device. In the other direction, a "receive interface" at the Link Layer receives data from a PHY device and sends status information to the PHY device. While this convention provides a clear framework for defining the system level functions, a clean separation between Link Layer and Physical Layer functionality is not often seen in actual implementations.

The ORSPI4 FPSC SPI4 blocks implement the basic functions defined in the standard and also implements additional options, as suggested in the standard, to configure parameters such as maximum burst size, calendar length, length of training sequence, etc. As required by the specification, the transmit and receive interfaces operate completely independently.

# **Embedded Core Overview - Functions and Features**

The embedded core contains four separate functional blocks, two SPI4 interface blocks, a high-speed Memory Controller block, and a quad SERDES block providing 4 channels of 0.6-3.7 Gbits/s SERDES. Features common to all blocks include:

- Improved PowerPC® 860 and PowerPC II high-speed synchronous MicroProcessor Interface that can be used for configuration, readback, device control, and device status; as well as for a general-purpose interface to the FPGA logic, RAMs, and embedded standard cell blocks. Glueless interface to synchronous PowerPC processors with user-configurable address space provided.

- New embedded *AMBA* ™ specification 2.0 AHB system bus (*ARM* ® processor) facilitates communication among the MicroProcessor Interface, configuration logic, and embedded core blocks.

- FPSC Design Kit available for use with *ispLEVER* development system software. Supported by industry-standard CAE tools for design entry, synthesis, simulation, and timing analysis.

# **SPI4 Interface Blocks - Overview**

The ORSPI4 FPSC provides two independent SPI4 interface blocks in the embedded core. The two SPI4 blocks are identical and the following overview applies to both blocks. In the following sections, the SPI4 protocol conventions for "transmit" and "receive" are not followed, since in various applications the ORSPI4 FPSC could be used to perform different functions at various levels in the SPI4 protocol stack. Instead, the "transmit" functions are those used to transmit data to and receive current status information from the device at the other end of the SPI4 link. The "receive" functions are those used to receive data from and transmit current status information to the device at the other end of the SPI4 link.

Each SPI4 block supports a standard 10 Gbits/s physical-to-link layer interface in conformance to the specification. This is achieved by using 16 LVDS pairs each for RX and TX that operate at a maximum data rate of 900 Mbits/s with a 450 MHz DDR clock. Data buffering of 8 Kbytes each in the transmit and receive direction (example: 256 bytes each for up to 32 ports) is provided by embedded Dual-Port RAM (DPRAM). Aggregation of buffer space is supported for systems with less than 32 ports. The internal calendar and Transmit and Receive Status FIFOs have been sized so that applications with larger numbers of ports can be supported. The ORSPI4 has been designed to support up to 256 ports, the maximum specified in the SPI4 specification.

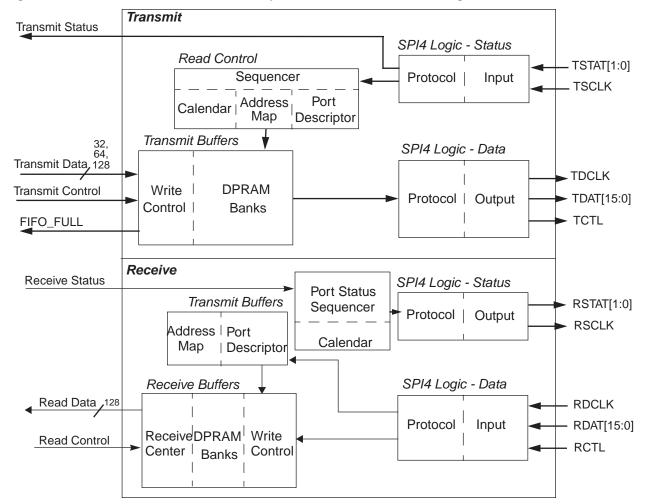

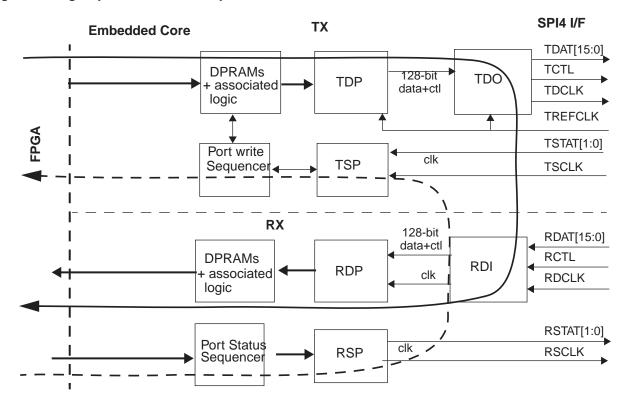

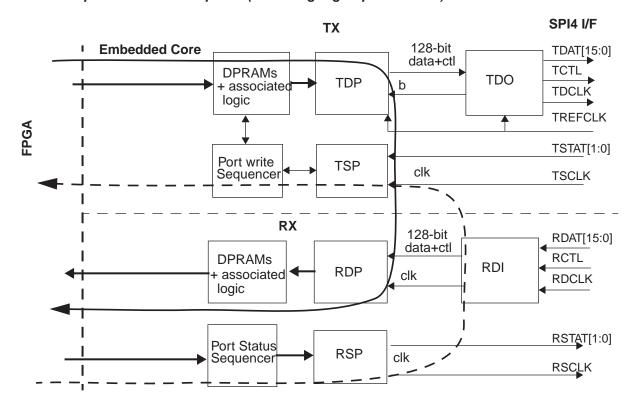

Despite operating independently, both the transmit path and the receive path logic perform similar functions and the partitioning of both logical blocks are quite similar as shown in Figure 3. The top level partitioning is between the logic blocks to transfer and process data and control information, and the logic blocks to generate, transfer and process status information.

#### **SPI4 Interface Block Features**

- Each SPI4 block provides a standard 10 Gbits/s physical-to-link layer interface in conformance to the OIF-SPI4-02.0 specification. Each interface provides an aggregate bandwidth of 13.6 Gbits/s. This is achieved by using 16 LVDS pairs each for RX and TX with a maximum data rate of 900 Mbits/s using a 450 MHz DDR clock.

- The blocks can be used for applications such as interconnecting an OC-192 framer with a proprietary packetized interface, to a network processor with a SPI4 based packet interface or vice versa.

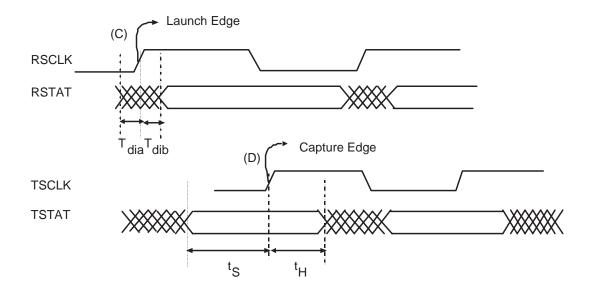

- Support for "static" or "dynamic" alignment at the receive interface. At clock rates above 350 MHz DDR, it

becomes difficult to meet the tight setup/hold requirements at the receiver using static alignment. In this case,

dynamic alignment is used to compensate for bit-to-bit skew.

- Dynamic alignment automatically compensates for Process, Voltage, and Temperature (PVT) changes in devices and systems.

- Full bandwidth up to 450 MHz DDR (900 Mbits/s throughput)

- Dynamically performs alignment based on 16 phases of the RX clock for improved accuracy

- Alignment algorithm can be done based on excessive bit errors on the DIP-4 calculation

- Clock skews up to +/- one clock cycle can be compensated by the dynamic alignment logic

- · For low speed data, static alignment can be selected through a programmable control bit

- Speeds up to 350 MHz DDR (700 Mbits/s throughput)

- Dynamic alignment is bypassed and disabled to save power in static alignment mode.

- Programmable on-edge or on-center clock/data relationship option at receiver.

- Programmable clock delay

- · Single-link and multi-link operation.

- SPI4 transmit data protocol support logic

- Combines the data and control words from the transmit FIFO (DPRAMs) into the SPI4 format

- Performs DIP-4 calculation over data and control words on the TX side and inserts into the payload control word

- · Handles all credit calculations based on the status information automatically

- Provides optional signals to FPGA interface logic for flow control:

- Current transmit Port ID (Calendar Port or user specified port # per calendar port)

- Current BURST\_VAL Parameter for that Port

- Status from that Port

- Embedded Calendar-based port polling sequence mechanism and bandwidth allocation for all 256 ports

- Programmable transmit and receive calendar tables support up to 256 ports

- Two calendars are supported in each direction

- Main Calendar (1K deep)

- Shadow Calendar (also 1K deep). User can reconfigure second calendar while operating off main calendar, and then switch on the next cycle to allow hitless operation

- All calendar configuration parameters specified in the standard (CALENDAR\_LEN, CALENDAR\_M, etc.) are supported

- Transmit and Receive Status FIFOs provided to store flow control information for up to 256 ports.

- Performs Status frame creation

- DIP-2 odd parity calculated over the status frames

- Supports either quarter-rate LVDS or LVTTL status channels

- Support for various options for flow control status creation, selectable per port:

- Based on DPRAM FIFO fill levels

- Based on status from FPGA interface per port

- Both of the above

- Dual-port RAM interface to the FPGA supports flexible data widths for both the receive and transmit FPGA/core interfaces.

- Scalable data bus enables users to configure TX interface for their respective port bandwidth requirements

- A total of 4 DPRAM banks where each of the DPRAMs can be logically partitioned into 1, 2, 4, or 8 virtual FIFOs

- Used for temporary storage and clock domain crossing

- Can be configured to provide 32-, 64-, 128-bit data bus interfaces from the FPGA (plus accompanying control signals)

- 32-bit mode: Four banks are separate and accessed independently

- 64-bit mode: Banks 0 & 1 become a single aggregation and Banks 2 & 3 become a single aggregation

- 128-bit mode: All four banks become a single aggregation

- Mixed mode: One 64-bit (two banks become a single aggregation) and two banks are separate and accessed independently

- Training pattern generation

- User controlled "alpha" repetitions of training pattern in DATA MAX T intervals

- Automatic generation of training pattern during loss of synchronization

### **Lattice Semiconductor**

- Automatic idle generation

- When no data for a given channel is available for transmit

- If the receiver on other end of the link is "satisfied" for this channel

- · Automatic training pattern and idle deletion in receive path

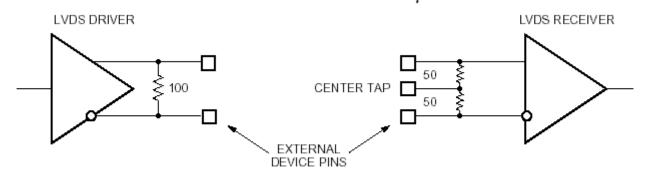

- Low-power, high performance ASIC LVDS I/Os compliant with EIA®-644

- I/O buffers support hot insertion

- I/O buffers proven to operate at over 900 MHz rates (Lattice ORLI10G FPSC uses same LVDS buffers)

- On-chip center tap termination for common mode noise reduction

- Configuration options as suggested in the OIF-SPI4-02.0 standard are supported to configure parameters such as maximum burst size, calendar length, length of training sequence, etc.

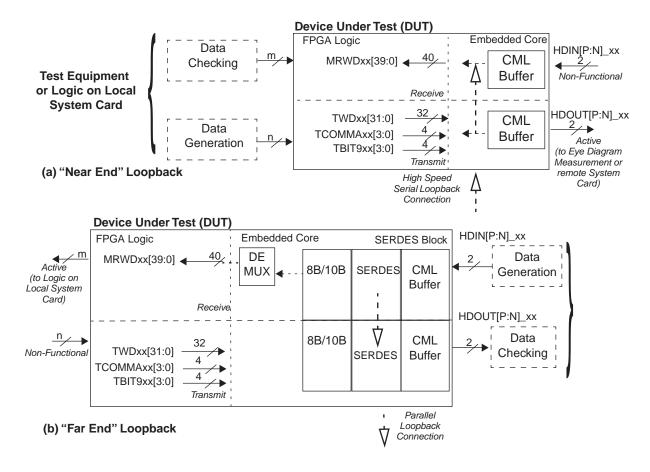

- Support for three forms of loopback:

- High-speed near end loopback which involves looping back data from the high-speed transmit block serial output to the high-speed receive block serial input. All of the logic up to the LVDS buffers is included in the loopback path. The LVDS buffers are bypassed

- Far end loopback which involves looping back the 128-bit output data from high-speed receive block to the 128-bit input of the high-speed transmit block. Data is received at the high-speed SPI4 RX interface and transmitted at the SPI4 TX interface. The transmit protocol, receive protocol and DPRAM blocks are bypassed. This works for both static and dynamic alignment modes.

- Low-speed near end loopback which excludes the high-speed blocks from the loopback path. This involves sourcing data from the FPGA, looping back the output of the transmit protocol block into the receive protocol block and observing data at the core-FPGA boundary

- Support for several SPI4 debug options:

- Under software control, DIP-4 errors can be forced by inverting the DIP-4 parity bits

- DIP-2 errors can be forced by inverting the DIP-2 parity bits

- Eight-bit counters are provided for counting DIP-4 and DIP-2 errors

- SPI4 Status Reporting Capabilities:

- Status information is reported through status registers.

- Most conditions can also cause an alarm (interrupt) to be generated

- DIP-4, DIP-2 errors

- Deskew error from high-speed RX side

- DPRAM Virtual FIFO overruns

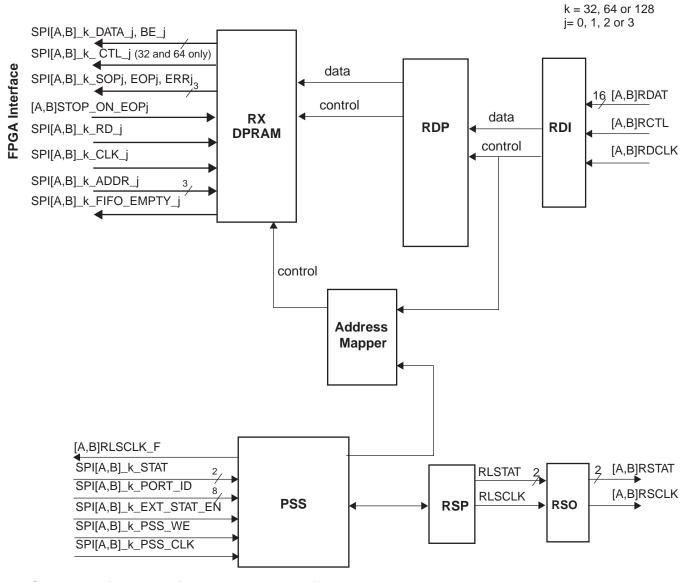

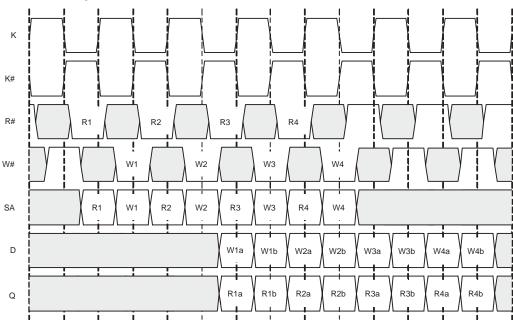

Figure 3. ORSPI4 SPI4 Interface Block - Top Level Functional Partitioning

At the embedded core/FPGA interface, data buffering is provided by banks of DPRAM partitioned into FIFOs. FIFO reads and writes are completely decoupled. Data and accompanying address, packet delineation and error identification information are written into the selected FIFO as received - either from the FPGA, in the transmit case, or from the receive link. For transmit, reads are performed from the FIFOs based on pre-programmed packet format information, a pre-programmed schedule for link access as read from calendar logic, and far end status information as received from the transmit status logic. In the receive direction, the receive status logic transmits information concerning the states of the receive buffers on the receive status links, while the FPGA logic reads data from the FIFOs as needed under control of the FPGA logic.

The read/write control functions are similar if operating with external RAM. In this case, the internal DPRAM can be used as clock domain crossing FIFOs.

Formatting/deformatting, flow control processing, and error control logic forms the interface between the DPRAM banks and the SPI4 transmit and receive blocks. This logic performs the necessary conversions between the SPI4 and FPGA/core interface formats. It also performs DIP-2 (status) and DIP-4 (control) generation/checking. Finally, the SPI4 interface blocks perform the MUX/DEMUX functions for rate conversion between the internal core data paths and the SPI4 links and also provides the needed LVDS driver and receiver functions. Either static or dynamic alignment is available at the receiver interface. Dynamic alignment is used to compensate for bit-to-bit skew at higher data rates where it becomes difficult to meet tight setup and hold timing requirements.

#### SPI4 Transmit Path Overview

The first of the major blocks in the Transmit section contains four DPRAM banks which can be configured to provide 32-bit, 64-bit or 128-bit data bus interfaces from the FPGA to the embedded core. Providing a scalable data bus enables users to tailor the transmit interface to meet their port bandwidth requirements. For example, with a POS-PHY Level 3 (PL3) interface supporting multiple PHYs (ports), a single 32-bit interface to the Transmit DPRAM is required. For an Ethernet 10 Gbits/s interface, a single port will require a single 128-bit interface to the Transmit DPRAM.

To realize the various data bus interfaces or aggregation modes, the user must configure the mode within the embedded core via the MPI interface or the system bus. Multiple DPRAM banks can be aggregated into larger FIFOs. Division of the DPRAM banks into virtual partitions (up to eight) is also possible.

The FPGA logic initiates a write to DPRAM by providing Data, Port ID, 3-bit FIFO Address and Write Enable signals to the SPI4 block. The internal FIFO controller latches the data and port control information into a temporary hold register that stores the data until an entire 128-bit line is captured, or an EOP is asserted. The 128-bit line is then written into the selected virtual FIFO.

Associated with each FPGA data write interface, there are also control information signals and a transmit clock. The FIFO control logic transparently passes the control information to the Control memory, with the exception of the Byte Enable bits (BE[3:0]), which indicate which bytes of the associated 32-bit Word are valid.

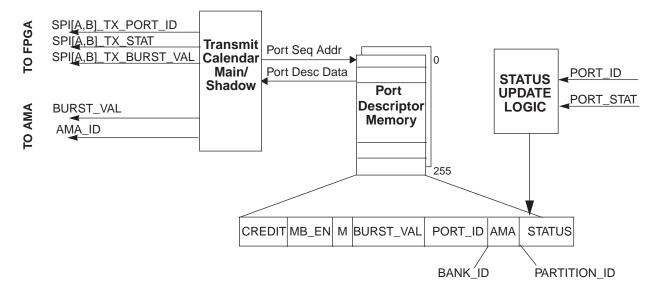

The DPRAM read logic blocks poll port data from the DPRAM banks, based on a preconfigured calendar sequence and the current status of each active port. The SPI4 calendar is a mechanism that maintains out-of-band statistics of the current status of each port supported across the SPI4 interface. The calendar is a reverse direction flow-control mechanism used to control the dynamic bandwidth allocated for the each supported port. By periodically providing far end receive status for each port, the transmitter can modulate the amount of bandwidth allocated to a particular port dynamically.

Writes to the DPRAMs from the FPGA logic are asynchronous to the calendar polling algorithm. The SPI4 transmit logic reads data from the DPRAMs according to a strict calendar sequence algorithm and will generally not read port data from the virtual FIFOs in the sequence it was written.

Both a main and a shadow calendar are provided and are each 1K deep. This enables the user to provide finer granularity of the polling sequence based on bandwidth allocated for each port. The length of the calendar table (CALENDAR\_LEN) is programmable. CALENDAR\_LEN should be at least as large as the number of active ports (channels) in the system and should not exceed the upper threshold set by the parameter (MAX\_CALENDAR\_LEN).

There are two basic modes supported for transmitting data. Within the SPI4 core, the embedded core operates identically for all modes. At the FPGA interface, processing will be done slightly differently, depending upon the mode the user requires. Each mode is discussed below.

- Embedded memory mode This mode is used when the ORSPI4 is interfacing to asynchronous FPGA interfaces, such as POS-PHY Level 3, 1GbE, Utopia Level 3, etc. and storing the data in the virtual DPRAM FIFOs. When operating in this mode, the SPI4 transmit logic will read port data from the FIFOs according to the calendar sequence. If there is no data, it will send idle data and advance to the next port. It is the user's responsibility to ensure the proper port data has been written to the virtual FIFO.

- External memory mode This mode is used in conjunction with the Memory Controller or some other external

memory based interface where data is available only after some fixed delay. In this mode the SPI4 transmit logic

instructs the FPGA as to what port data to retrieve as well as how many bursts of data to retrieve. The FPGA is

responsible to write the data read from the Memory Controller into the DPRAMs. Data is read from the DPRAM

devices by the SPI4 transmit logic according to the transmit calendar.

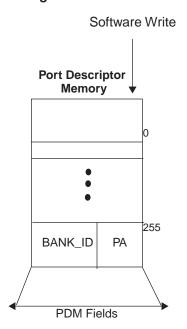

The DPRAM read logic also includes a Port Descriptor Memory (PDM) which is a user configurable memory containing a list of read control parameters for all enabled ports to be polled. The depth of the memory is 256 locations,

which corresponds to the maximum number of ports that are supported by SPI4. The PDM data is comprised of three separate segments - a 10-bit dynamic table maintained by the SPI4 logic, a static 20-bit table, and a dynamic 3-bit register file written by the FIFO Status Update (FSU) logic. The PDM provides a mapping of the SPI4 port number to the FPGA interface device/port number, removing the burden from FPGA logic.

When port data is read from the PDM, a status update bit (the U-bit) is first examined to see whether the STAT field is new or stale. If stale, then the STAT field is not considered for the rest of processing. If the STAT field is new (U-bit=1) the STAT field is used in conjunction with other field to calculate what the new Credit field for the port should be

A SATISFIED status indicates the corresponding port's FIFO is almost full, and only transfers using the remaining previously granted 16-byte blocks (if any) may be sent to corresponding port until the next status update. No additional transfers to that port are permitted.

When a HUNGRY status indication is received, transfers up to MAXBURST2 16-byte blocks or the remainder of what was previously granted (whichever is greater), may be sent to the corresponding port prior to the next status update. A STARVING status indication indicates that buffer underflow is imminent in the corresponding PHY port. When STARVING is received, transfers for up to MAXBURST1 16-byte blocks may be sent to the corresponding port prior to the next status update.

If the U-bit is cleared, this indicates the STAT field has already been used to update the Credit field on a previous Port servicing. Therefore, the Credit field should simply be reduced by BURST\_VAL. Otherwise, the Credit field is updated to the new Credit value minus BURST\_VAL. In both cases, the output of the logic is used to update the Credit field. If the Credit field is zero, and the STAT field is stale, then the port receives no service. Read accesses of the port control information need to be optimized to minimize any lost bandwidth due to the Credit field having a value of zero.

Data read from the DPRAMS is sent to the SPI4 transmit block which is responsible for the following functions:

- Combining the data and control words from the Transmit FIFO into the data format specified in the OIF SPI4 standard.

- DIP-4 calculation and insertion into the payload control word.

- Generation of idle/training control words in programmable intervals.

Training words are used to dynamically align the far end receiver. As long as a disabled status '11' is received on the SPI4 status channel, the transmit interface block sends continuous training patterns (10 training control words followed by 10 training data words). When valid status is received on the status channel, user data is normally sent on the SPI4 data link. However, users can also periodically schedule training patterns in SDATA\_MAX\_T periods. The training patterns can be repeated "ALPHA" times. Both "ALPHA" and DATA\_MAX\_T are programmable control register bits.

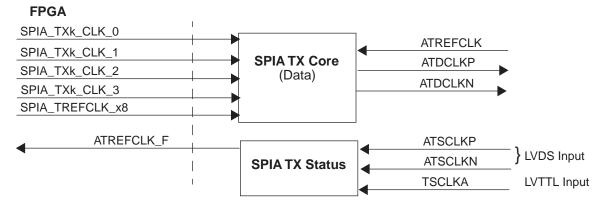

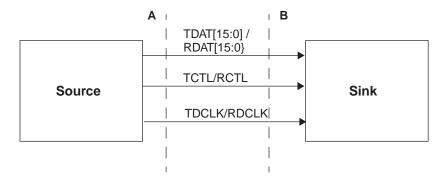

The SPI4 transmit block contains the high-speed serializer which uses the x8 clock, synthesized by an internal PLL, to generate the high-speed data from the low-speed 128-bit FIFO data. Data is transmitted off-chip using a 16-bit LVDS data bus - TDAT[15:0], a LVDS control bit - TCTL, and a source synchronous clock - TDCLK.

The 16-bit data bus and control are DDR with respect to TDCLK. In order to support 10 Gbits/s throughput, the minimum frequency of TDCLK needs to be 622 Mbits/s (311 MHz DDR). To allow considerable margin above this minimum data rate a maximum frequency of operation of 900 Mbits/s is supported.

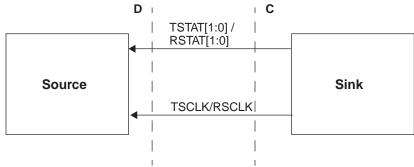

The Transmit Status Protocol (S4TSP) block provides the interface to the SPI4 Transmit Status interfaces. These signals can be either LVDS or LVCMOS buffers. The S4TSP block is responsible for the following functions:

- · FIFO Status Decoding and Buffering.

- Framing using the status framing pattern.

- DIP-2 checking of incoming status information.

The FIFO Status Update logic block reads the Port and Status information and uses this information to update Port Descriptor Memory STAT field. Whenever a valid STAT field has been updated, the associated U-bit field is set as discussed previously. This indicates that the STAT field is new and that the Credit field for that must be re-evaluated the next time it is selected as a source for transmit data.

### **SPI4 Receive Path Overview**

In the receive direction, data is received in SPI4 format on the LVDS I/Os at the receive interface. The data is written into DPRAM as received and read from the DPRAMs as requested by the FPGA logic. Control information is also interpreted and buffered and idles and training sequences are removed from the incoming data stream.

Receive FIFO status is transmitted from the Receive Status interface according to a pre-configured polling sequence contained within the Receive Calendar. Data is formatted into the SPI4 Receive Status format and sent to the physical links as either LVDS or LVTTL signals.

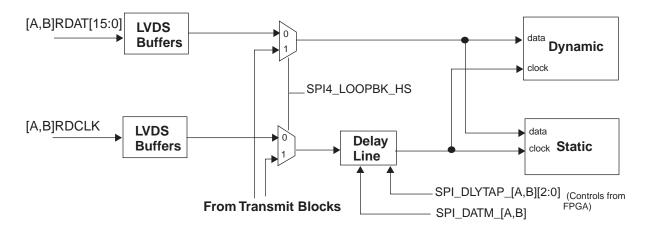

The SPI4 block contains the high-speed receive logic. Incoming LVDS signals, in SPI4 format, include the 16-bit data bus (RDAT[15:0]), a control bit (RCTL) and a source synchronous DDR clock (RDCLK). The incoming data is deserialized to a 128-bit format and the control information is converted to an 8-bit format.

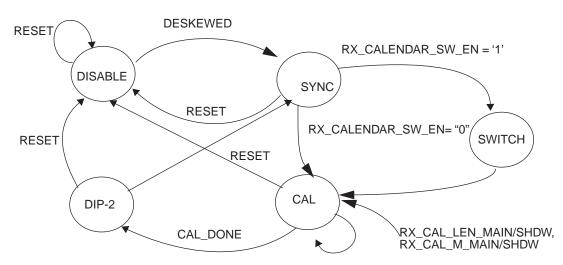

The SPI4 receive block also detects training patterns and performs dynamic alignment of the incoming data. At speeds above 700 Mbit/s (350 MHz) it becomes necessary to use dynamic alignment. Skews of up to  $\pm$  one clock period can be compensated by the dynamic alignment logic. For low speed incoming data, static alignment can be chosen through a programmable control bit. Various timing options of receive data vs. receive clock are also programmable.

The SPI4 block is responsible for decoding the in-band control information. It then forwards both the data and control information, such as link address, SOP, EOP and error, to the virtual FIFOs. The SPI4 block also parses the control words embedded within the incoming data. Using this control information, it performs the following functions:

- · Checks DIP-4 parity

- Monitors for continuous alignment (if more than a programmable number of DIP-4 parity errors exist, there may be an alignment problem).

- Removes idle/training words.

- Extracts link address and SOP, EOP and valid packet (no error) signals.

In the receive direction there are also four Dual Port Memory (DPRAM) banks that contain a total of 8K bytes available for clock domain crossing and/or temporary buffering. As with the transmit buffers, each bank can be further partitioned up to 8 virtual memories, one for each of 8 ports. The following are the characteristics of the DPRAM virtual FIFOs:

- The DPRAM memories support asynchronous reads. Each DPRAM bank can be accessed on the FPGA side with an individual clock.

- For data buffering beyond 32 ports, the DPRAM banks can be used as clock domain crossing FIFOs before writing the data and control information into an external memory. If fewer ports are supported, the virtual memories can be aggregated, providing more buffer space for each port.

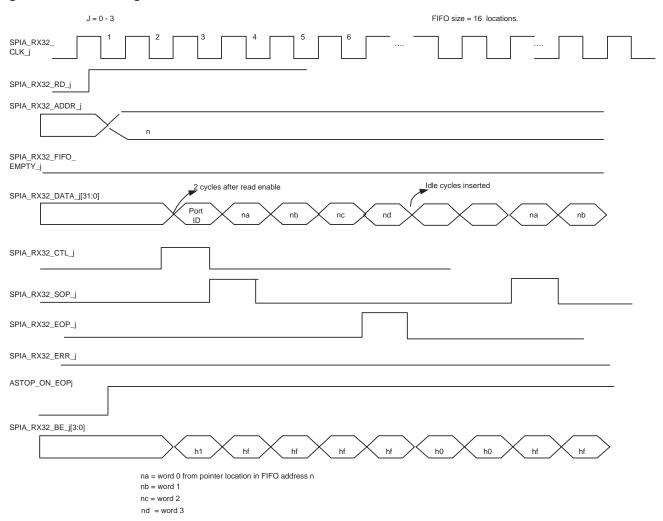

- Each DPRAM bank has a 32-bit data and 8-bit control read interface to the FPGA. When using the DPRAM memories, the data can be read as either a 32-, 64-, or 128-bit data bus with associated control signals.

- At any time, the user can poll the status of a FIFO within a DPRAM bank by providing just the read address without a valid read enable.

- A FIFO empty flag is generated by the read control logic to the FPGA. This empty flag can be programmed to indicate truly empty or < 1/4 full (1/4 full 1).

## **Lattice Semiconductor**

In addition to formatting received data and sending it to the FPGA logic, the receive block also sends status information to the SPI4 status interface.

The Port Status Sequencer (PSS) block is responsible for providing port status to the SPI4 Receive Status block logic according to a pre-configured calendar sequence. Status is derived from the fill-levels of the DPRAM FIFOs and/or from the FPGA status interface.

The SPI4 Receive Status block is responsible for FIFO status encoding, calendar management, status pattern encoding (sync bits "11"), DIP-2 calculation and optional calendar selection word encoding.

The SPI4 Receive Status block contains the low speed LVTTL output buffers and LVDS output buffers necessary for the output stage of receive status logic. The option to choose between LVTTL or LVDS outputs is done by setting a control register bit.

### **SPI4 Debugging and Statistics Gathering Support**

There are also several other features, including three loopback modes incorporated into the embedded core to assist in debugging and statistic gathering. These features involve both the transmit and receive paths.

The three forms of loopback supported directly are:

- · High-speed near-end loopback

- · Far-end high-speed loopback

- · Low-speed near-end loopback

The SPI4 blocks support the following error insertion and status reporting options for testing:

- DIP-4 odd parity is calculated over data and control words and inserted on the TX side. DIP-4 errors can be forced by inverting the DIP-4 parity bits. DIP-4 parity is then checked at the receive interface.

- DIP-2 odd parity is calculated over the status frames and inserted on the RX side. DIP-2 errors can be forced by inverting the DIP-2 parity bits. DIP-2 parity is then checked at the transmit status interface.

- Eight-bit counters are provided for counting DIP-4 and DIP-2 errors.

- Deskew error reporting for high-speed RX side dynamic alignment. This can cause an alarm.

- DPRAM FIFO overrun reporting. These can cause an alarm.

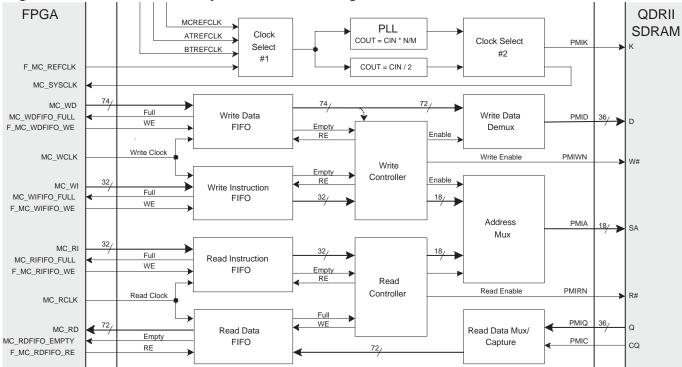

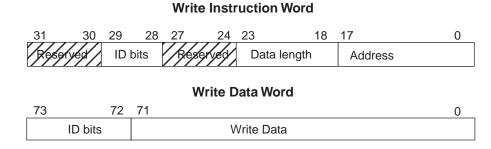

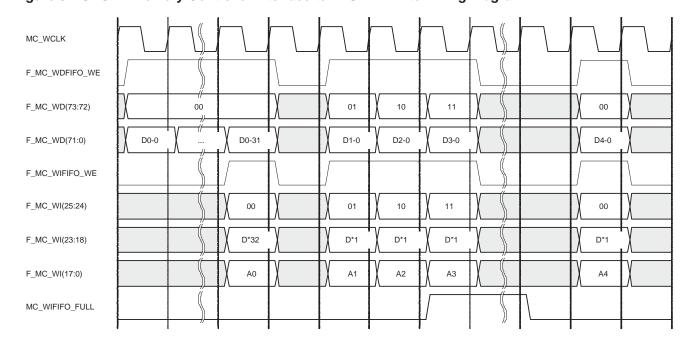

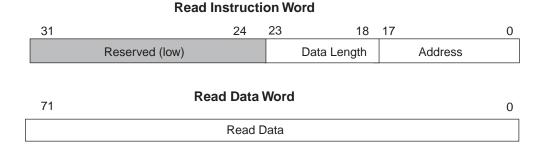

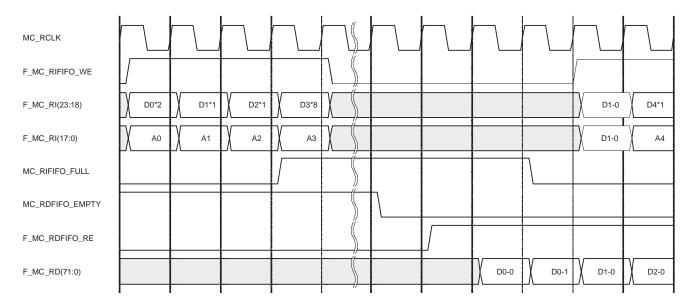

# **Memory Controller - Overview**

The Memory Controller block controls an interface to external Quad Data Rate (QDRII) SRAM for data buffering between the FPGA logic and external memory. The key features of the Memory Controller interface are described below:

# **Memory Controller Features**

- Independent Memory Controller interface to external Quad Data Rate (QDRII) SRAMs from multiple suppliers for data buffering.

- Provides additional packet buffering for > 32 ports

- Provides traffic smoothing for any number of ports

- The Controller supports a throughput of greater than 20 Gbits/s so that all the data received on the SPI4 interface at 10 Gbits/s can be buffered.

- The QDRII SRAM supports this throughput with 36 unidirectional data lines in both the read and write directions.

- The controller block provides the ability to access external QDRII SRAM through the FPGA.

- A set of 72 data signals across the core-FPGA interface

- Of the 72, 8 signals can be either used for parity or data.

- Simple asynchronous FIFO interface to FPGA for ease of design. A high-speed clock signal is provided to the FPGA as an option to make the write and read synchronous, if desired.

- The core passes the data transparently to and from the QDRII SRAM in two-word or four-word bursts. Interfaces to memory are 36 bits wide and the address buses are 18 bits wide.

- Supports the interfaces required for a 512K x 36 bit (18 Mbit) QDRII SRAM in two-word burst mode.

- Only 17 address lines are required in four-word burst mode.

- · Status/Alarm reported to user through registers

- Data length mismatch from the write controller state machine

- Data instruction coherency error

- Write data, Read data FIFO overrun and underrun errors

- · Additional high-speed Memory Controller can be implemented in FPGA gates if required.

# **SERDES Logic Block - Overview**

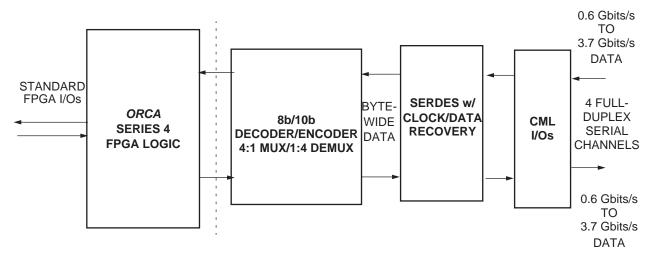

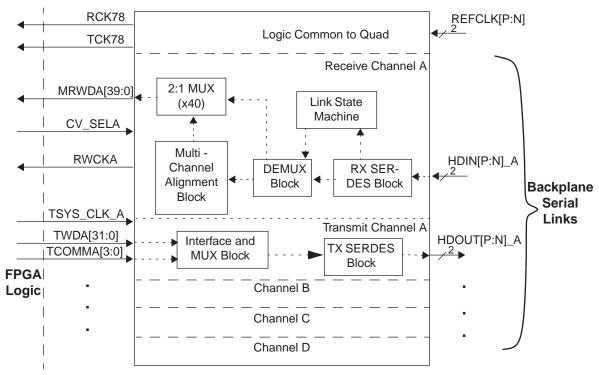

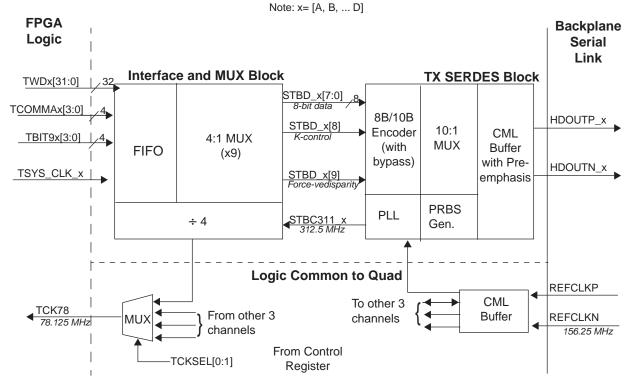

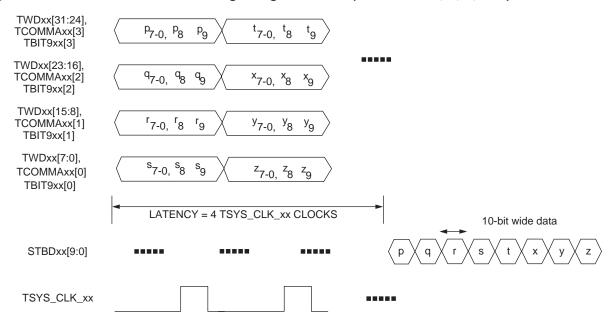

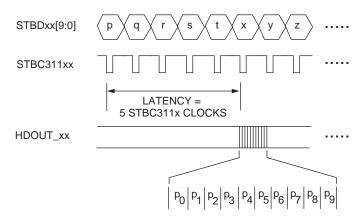

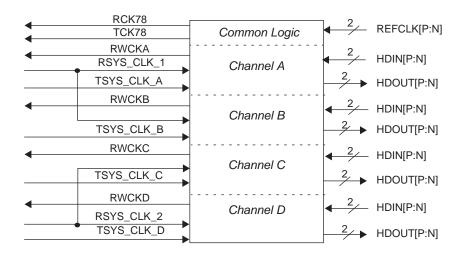

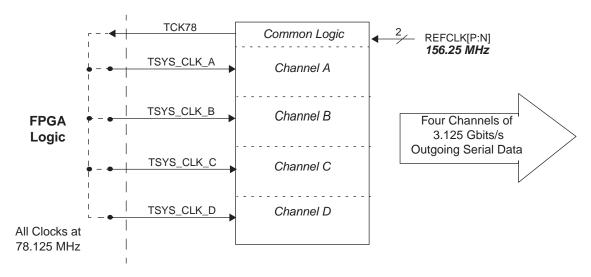

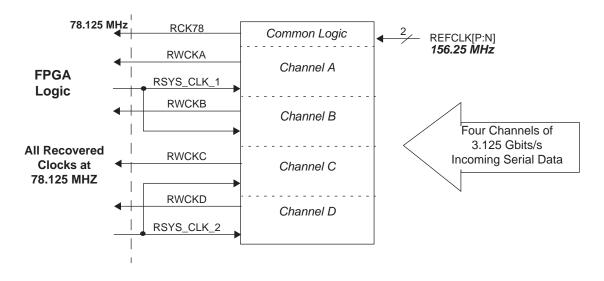

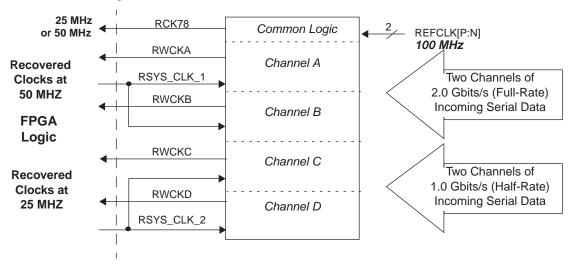

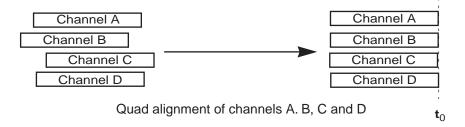

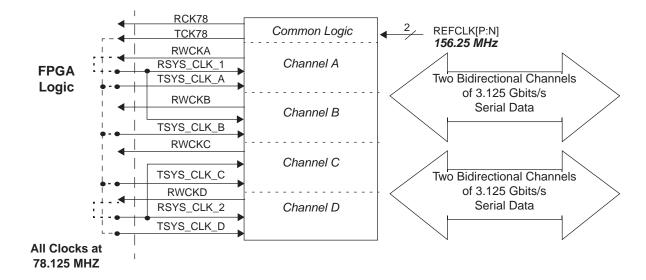

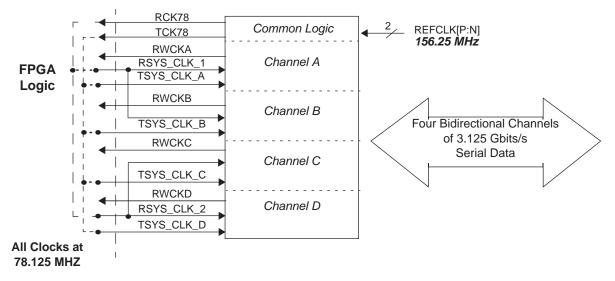

The SERDES logic block in of the ORSPI4 contains four Clock and Data Recovery (CDR) macrocells and four Serializer/Deserializer (SERDES) macrocells to support four channels of 8b/10b (*IEEE* 802.3.2002) encoded serial links. The logic block also contains Fiber Channel and XAUI-based state machines, logic to support multi-channel alignment and MUX/DEMUX logic for the FPGA/core interface. Figure 4 shows the SERDES top level block diagram and the basic data flow. Boundary scan for the SERDES only includes programmable I/Os and does not include any of the embedded block I/Os.

Figure 4. SERDES Top Level Block Diagram.

The serial channels can each operate at up to 3.7 Gbits/s (2.96 Gbits/s data rate) with a full-duplex synchronous interface with built-in clock recovery (CDR). The 8b/10b encoding provides guaranteed ones density for the CDR, byte alignment, and error detection. The core is also capable of frame synchronization and physical link monitoring. An overview of the individual blocks in the embedded core is presented in the following paragraphs. The SERDES portion of the core contains a quad transceiver block for serial data transmission at a selectable data rate of 0.6 to 3.7 Gbits/s. Each SERDES channel features high-speed 8b/10b parallel I/O interfaces to other core blocks and high-speed CML interfaces to the serial links.

#### Serializer and Deserializer (SERDES)

The SERDES portion of the core contains a transceiver block for serial data transmission at a selectable data rate of 0.6-3.7 Gbits/s. Each SERDES channel features high-speed 8b/10b parallel I/O interfaces to other core blocks and high-speed CML interfaces to the serial links.

The SERDES circuitry consists of receiver, transmitter, and auxiliary functional blocks. The receiver accepts high-speed (up to 3.7 Gbits/s) serial data. Based on data transitions, the receiver locks an analog receive PLL for each channel to retime the data, then demultiplexes the data down to parallel bytes and an accompanying clock.

The transmitter operates in the reverse direction. Parallel bytes are multiplexed up to 3.7 Gbits/s serial data for off-chip communication. The transmitter generates the necessary clocks from a lower speed reference clock.

The transceiver is controlled and configured through the system bus in the FPGA logic and through the external 8-bit microprocessor interface of the FPGA. Each channel has associated dedicated registers that are readable and writable. There are also global registers for control of common circuitry and functions.

The SERDES performs 8b/10b encoding and decoding for each channel. The 8b/10b transmission code can support either Ethernet or Fibre Channel specifications for serial encoding/decoding, special characters, and error detection.

The user can disable the 8b/10b decoder to receive raw 10-bit words, which will be rate reduced by the SERDES. If this mode is chosen, the user must also bypass the multichannel alignment FIFOs.

The SERDES macrocell contains its own dedicated PLLs for both transmit and receive clock generation. The user provides a reference clock of the appropriate frequency. The receiver PLLs extract the clock from the serial input data and re-time the data with the recovered clock.

#### MUX/DEMUX Block

The MUX/DEMUX logic converts the data format for the high-speed serial links to a wide, low-speed format for crossing the CORE/FPGA interface. The intermediate interface to the SERDES macrocell runs at 1/10th the bit

rate of the data lane. The MUX/DEMUX converts the data rate and bus width so the interface to the FPGA core can run at 1/4th this intermediate frequency, giving a range of 25.0 to 92.5 MHz for the data rates into and out of the FPGA logic.

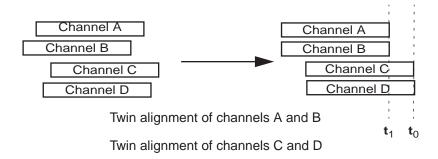

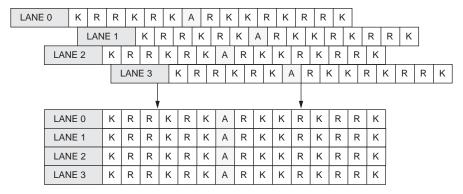

### **Multi-Channel Alignment FIFOs**

In the ORSPI4 SERDES block, the four incoming data channels can be independent of each other or can be synchronized in several ways. Two channels within a SERDES block can be aligned together; channels A and B and/or channels C and D. Finally, four channels in a SERDES block can be aligned together to form a communication channel with a bandwidth of 10 Gbits/s. Individual channels within an alignment group can be disabled (i.e., powered down) without disrupting other channels.

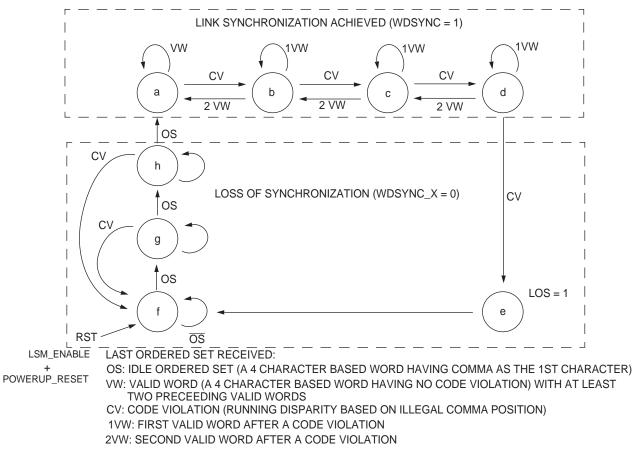

#### **XAUI and Fibre Channel Link State Machines**

Two separate link state machines are included in the architecture. A XAUI-based link state machine is included in the embedded core to implement the IEEE 802.3ae standard. A separate state machine for Fibre Channel is also implemented.

#### **FPGA/Embedded Core Interface**

In 8b/10b mode, the FPGA logic will receive/transmit 32-bits of data (up to 92.5 MHz) and four K\_CTRL bits from/to the embedded core. There are 4 data streams in each direction plus additional timing, status and control signals.

Data sent to the FPGA can be aligned using comma (/K/) characters or /A/ character as specified either by Fibre Channel or by IEEE 802.3ae for XAUI based interfaces. The alignment character is made available to the FPGA along with the data. The special characters K28.1, K28.5 and K28.7 are treated as valid comma characters by the SERDES.

If the receive channel alignment FIFOs are bypassed, then each channel will provide its own receive clock in addition to data and comma character detect signals. If the 8b/10b decoders are bypassed, then 40-bit data streams are passed to the FPGA logic. No channel alignment can be done in 8b/10b bypass mode.

### **SERDES Features**

- Four channels of 0.6-3.7G SERDES with 8b/10b encoding/decoding are supported. The SERDES quad is IEEE P802.3ae/D4.01 XAUI based and also supports the FC (ANSI X3.230:1994) link synchronization state machine specification.

- The high-speed SERDES are programmable and support serial data rates including 622 Mbits/s, 1.0 Gbits/s,

1.25 Gbits/s, 2.5 Gbits/s, 3.125 Gbits/s, and 3.7 Gbits/s. Operation has been demonstrated on design tolerance

devices at 3.7 Gbits/s across 26 in. of FR-4 backplane and at 3.2 Gbits/s across 40 in. of FR-4 backplane across

temperature and voltage specifications.

- Asynchronous operation per receive channel, with the receiver frequency tolerance based on one reference clock per four channels (separate PLL per channel).

- Ability to select full-rate or half-rate operation per transmit or receive channel by setting the appropriate control registers.

- Programmable one-half amplitude transmit mode for reduced power in chip-to-chip application.

- Transmit preemphasis (programmable) for improved receive data eye opening.

- 32-bit (8b/10b) or 40-bit (raw data) parallel internal bus for data processing in FPGA logic.

- Provides a 10 Gbits/s backplane interface to a switch fabric using four 2.5 Gbit/s links. Also supports port cards at 2.5 Gbit/s.

- 3.125 Gbits/s SERDES compliant with XAUI serial data specification for 10 Gigabit Ethernet applications.

- Most XAUI features for 10 Gigabit Ethernet are embedded including the required link state machine.

- Compliant to Fibre Channel physical layer specification.

- High-Speed Interface (HSI) function for clock/data recovery serial backplane data transfer without external clocks.

- Four-channel HSI functions provide 2.96 Gbits/s serial user data interface per channel (8b/10b encoding and decoding) for a total chip bandwidth of > 10 Gbits/s (full duplex).

- SERDES have low-power CML buffers and support 1.5 V or 1.8 V I/Os. This allows use of the SERDES with optical transceiver, coaxial copper media, shielded twisted pair wiring or high-speed backplanes such as FR-4.

- Powerdown option of SERDES HSI receiver or transmitter is on a per-channel basis.

- · Automatic lock to reference clock in the absence of valid receive data.

- High-speed and low-speed loopback test modes.

- No external components required for clock recovery and frequency synthesis.

- Built-in boundary scan (IEEE® 1149.1 and 1149.2 JTAG) for the programmable I/Os, not including the SERDES interface.

- FIFOs can align incoming data either across groups of four channels or groups of two channels. Alignment is done either using comma characters or by using the /A/ character in XAUI mode. Optional ability to bypass the alignment FIFOs for asynchronous operation between channels (Each channel includes its own clock and frame pulse or comma detect).

# **FPGA Logic Overview**

The *ORCA* Series 4 architecture is a new generation of SRAM-based programmable devices from Lattice. It includes enhancements and innovations geared toward today's high-speed systems on a single chip. Designed with networking applications in mind, the Series 4 family incorporates system-level features that can further reduce logic requirements and increase system speed. *ORCA* Series 4 devices contain many new patented enhancements and are offered in a variety of packages and speed grades.

The hierarchical architecture of the logic, clocks, routing, RAM, and system-level blocks create a seamless merge of FPGA and ASIC designs. Modular hardware and software technologies enable System-on-Chip integration with true plug-and-play design implementation.

The architecture consists of the following basic elements: Programmable Logic Cells (PLCs), Programmable I/O cells (PIOs), Embedded Block RAMs (EBRs), plus supporting system-level features. These elements are interconnected with a rich routing fabric of both global and local wires. An array of PLCs is surrounded by common interface blocks that provide an abundant interface to the adjacent PLCs or system blocks. Routing congestion around these critical blocks is eliminated by the use of the same routing fabric implemented within the programmable logic core.

Each PLC contains a Programmable Function Unit (PFU), Supplemental Logic Interconnect Cell (SLIC), local routing resources, and configuration RAM. Most of the FPGA logic is performed in the PFU, but decoders, *PAL*-like functions, and 3-state buffering can be performed in the SLIC. The PIOs provide device inputs and outputs and can be used to register signals and to perform input demultiplexing, output multiplexing, uplink and downlink functions, and other functions on two output signals.

Large blocks of 512 x 18 quad-port RAM complement the existing distributed PFU memory. The RAM blocks can be used to implement RAM, ROM, FIFO, multiplier, and CAM. Some of the other system-level functions include the MPI, PLLs, and the Embedded System Bus (ESB).

Detailed descriptions of the FPGA logic blocks can be found in the ORCA Series 4 FPGA Datasheet.

# **Programmable Logic Features**

- High-performance programmable logic:

- 0.16 μm, 7-level metal technology.

- Internal performance of >250 MHz.

- Over 600K usable system gates.

- Meets multiple I/O interface standards.

- 1.5 V operation (30% less power than 1.8 V operation), translates to greater performance.

- Traditional I/O selections:

- LVTTL (3.3V) and LVCMOS (2.5 V and 1.8 V) I/Os.

- Per pin-selectable I/O clamping diodes provide 3.3 V PCI compliance.

- Individually programmable drive capability:

- 24 mA sink/12 mA source, 12 mA sink/6 mA source, or 6 mA sink/3 mA source.

- Two slew rates supported (fast and slew-limited).

- Fast-capture input latch and input Flip-Flop (FF)/latch for reduced input setup time and zero hold time.

- Fast open-drain drive capability.

- Capability to register 3-state enable signal.

- Off-chip clock drive capability.

- Two-input function generator in output path.

- New programmable high-speed I/O:

- Single-ended: GTL, GTL+, PECL, SSTL3/2 (Class I and II), HSTL (Class I, III, IV), ZBT, and DDR.

- Double-ended: LVDS, bused-LVDS, and LVPECL. Programmable, (on/off) internal parallel termination (100 Ω) is also supported for these I/Os.

- New capability to (de)multiplex I/O signals:

- New DDR on both input and output at rates up to 350 MHz (700 Mbits/s effective rate).

- New 2x and 4x downlink and uplink capability per I/O (i.e., 50 MHz internal to 200 MHz I/O).

- Enhanced twin-quad Programmable Function Unit (PFU):

- Eight 16-bit Look-Up Tables (LUTs) per PFU.

- Nine user registers per PFU, one following each LUT, and organized to allow two nibbles to act independently, plus one extra for arithmetic operations.

- New register control in each PFU has two independent programmable clocks, clock enables, local SET/RESET, and data selects.

- New LUT structure allows flexible combinations of LUT4, LUT5, new LUT6, 4 → 1 MUX, new 8 → 1 MUX, and ripple mode arithmetic functions in the same PFU.

- 32 x 4 RAM per PFU, configurable as single- or dual-port. Create large, fast RAM/ROM blocks (128 x 8 in only eight PFUs) using the Supplemental Logic and Interconnect Cell (SLIC) decoders as bank drivers.

- Soft-Wired LUTs (SWL) allow fast cascading of up to three levels of LUT logic in a single PFU through fast internal routing which reduces routing congestion and improves speed.

- Flexible fast access to PFU inputs from routing.

- Fast-carry logic and routing to all four adjacent PFUs for nibble-wide, byte-wide, or longer arithmetic functions, with the option to register the PFU carry-out.

- Abundant high-speed buffered and non-buffered routing resources provide 2x average speed improvements over previous architectures.

- Hierarchical routing optimized for both local and global routing with dedicated routing resources. This results in faster routing times with predictable and efficient performance.

- SLIC provides eight 3-state buffers, up to a 10-bit decoder, and PAL™-like AND-OR-Invert (AOI) in each programmable logic cell.

- New 200 MHz embedded quad-port RAM blocks, 2 read ports, 2 write ports, and 2 sets of byte lane enables. Each embedded RAM block can be configured as:

- 1—512 x 18 (quad-port, two read/two write) with optional built in arbitration.

- 1—256 x 36 (dual-port, one read/one write).

- 1—1K x 9 (dual-port, one read/one write).

- 2—512 x 9 (dual-port, one read/one write for each).

- 2 RAMS with an arbitrary number of words whose sum is 512 (or less) x 18 (dual-port, one read/one write).

- Supports joining of RAM blocks.

- Two 16 x 8-bit content addressable memory (CAM) support.

- FIFO 512 x 18, 256 x 36, 1K x 9, or dual 512 x 9.

- Constant multiply (8 x 16 or 16 x 8).

- Dual variable multiply (8 x 8).

- Embedded 32-bit internal system bus plus 4-bit parity interconnects FPGA logic, MicroProcessor interface (MPI), embedded RAM blocks, and embedded standard cell blocks with 100 MHz bus performance. Included are builtin system registers that act as the control and status center for the device.

- Built-in testability:

- Full boundary scan (IEEE 1149.1 and Draft 1149.2 JTAG).

- Programming and readback through boundary scan port compliant to IEEE Draft 1532:D1.7.

- TS\_ALL testability function to 3-state all I/O pins.

- New temperature-sensing diode.

- Improved built-in clock management with Programmable Phase-Locked Loops (PPLLs) provide optimum clock modification and conditioning for phase, frequency, and duty cycle from 20 MHz up to 420 MHz. Multiplication of the input frequency up to 64x and division of the input frequency down to 1/64x possible.

- New cycle stealing capability allows a typical 15% to 40% internal speed improvement after final place and route.

This feature also enables compliance with many setup/hold and clock to out I/O specifications and may provide reduced ground bounce for output buses by allowing flexible delays of switching output buffers.

# **Programmable Logic System Features**

- PCI local bus compliant for FPGA I/Os.

- Improved *PowerPC*® 860 and *PowerPC* II high-speed synchronous microprocessor interface can be used for configuration, readback, device control, and device status, as well as for a general-purpose interface to the FPGA logic, RAMs, and embedded standard cell blocks. Glueless interface to synchronous *PowerPC* processors with user-configurable address space provided.

- New embedded AMBA ™ specification 2.0 AHB system bus (ARM® processor) facilitates communication among the microprocessor interface, configuration logic, Embedded Block RAM, FPGA logic, and embedded standard cell blocks.

- Variable size bused readback of configuration data capability with the built-in microprocessor interface and system bus.

- Internal, 3-state, and bidirectional buses with simple control provided by the SLIC.

- New clock routing structures for global and local clocking significantly increases speed and reduces skew (<200 ps for OR4E04).</li>

- New local clock routing structures allow creation of localized clock trees.

- Two new edge clock routing structures allow up to six high-speed clocks on each edge of the device for improved setup/hold and clock to out performance.

- New Double-Data Rate (DDR) and Zero-Bus Turn-around (ZBT) memory interfaces support the latest highspeed memory interfaces.

- New 2x/4x uplink and downlink I/O capabilities interface high-speed external I/Os to reduced speed internal logic.

- Meets Universal Test and Operations PHY Interface for ATM (UTOPIA) levels 1, 2, and 3; as well as POS-PHY3.

#### **PLC Logic**

Each PFU within a PLC contains eight 4-input (16-bit) LUTs, eight latches/FFs, and one additional Flip-Flop that may be used independently or with arithmetic functions.

The PFU is organized in a twin-quad fashion; two sets of four LUTs and FFs that can be controlled independently. Each PFU has two independent programmable clocks, clock enables, local set/reset, and data selects. LUTs may also be combined for use in arithmetic functions using fast-carry chain logic in either 4-bit or 8-bit modes. The carry-out of either mode may be registered in the ninth FF for pipelining.

Each PFU may also be configured as a synchronous 32 x 4 single- or dual-port RAM or ROM. The FFs (or latches) may obtain input from LUT outputs or directly from invertible PFU inputs, or they can be tied high or tied low. The FFs also have programmable clock polarity, clock enables, and local set/reset.

The SLIC is connected from PLC routing resources and from the outputs of the PFU. It contains eight 3-state, bidirectional buffers, and logic to perform up to a 10-bit AND function for decoding, or an AND-OR with optional INVERT to perform *PAL*-like functions. The 3-state drivers in the SLIC and their direct connections from the PFU outputs make fast, true, 3-state buses possible within the FPGA, reducing required routing and allowing for real-world system performance.

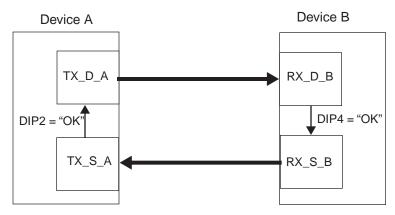

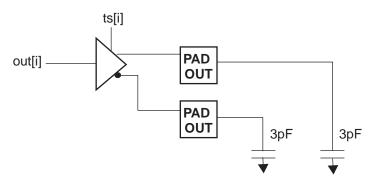

#### Programmable I/O

The Series 4 PIO addresses the demand for the flexibility to select I/Os that meet system interface requirements. I/Os can be programmed in the same manner as in previous *ORCA* devices, with the additional new features which allow the user the flexibility to select new I/O types that support High-Speed Interfaces.

Each PIO contains four programmable I/O pads and is interfaced through a common interface block to the FPGA array. The PIO is split into two pairs of I/O pads with each pair having independent clock enables, local set/reset, and global set/reset. On the input side, each PIO contains a programmable latch/Flip-Flop, which enables very fast latching of data from any pad. The combination provides for very low setup requirements and zero hold times for signals coming on-chip. It may also be used to demultiplex an input signal, such as a multiplexed address/data signal, and register the signals without explicitly building a demultiplexer with a PFU.

On the output side of each PIO, an output from the PLC array can be routed to each output Flip-Flop, and logic can be associated with each I/O pad. The output logic associated with each pad allows for multiplexing of output signals and other functions of two output signals.

The output FF, in combination with output signal multiplexing, is particularly useful for registering address signals to be multiplexed with data, allowing a full clock cycle for the data to propagate to the output. The output buffer signal can be inverted, and the 3-state control can be made active-high, active-low, or always enabled. In addition, this 3-state signal can be registered or nonregistered.

The Series 4 I/O logic has been enhanced to include modes for speed uplink and downlink capabilities. These modes are supported through shift register logic, which divides down incoming data rates, or multiplies up outgoing data rates. This new logic block also supports high-speed DDR mode requirements where data is clocked into and out of the I/O buffers on both edges of the clock.

The new programmable I/O cell allows designers to select I/Os which meet many new communication standards permitting the device to hook up directly without any external interface translation. They support traditional FPGA standards as well as high-speed, single-ended, and differential-pair signaling. Based on a programmable, bank-oriented I/O ring architecture, designs can be implemented using 3.3 V, 2.5 V, 1.8 V, and 1.5 V referenced output levels.

# Routing

The abundant routing resources of the Series 4 architecture are organized to route signals individually or as buses with related control signals. Both local and global signals utilize high-speed buffered and non-buffered routes. One PLC segmented (x1), six PLC segmented (x6), and bused half chip (xHL) routes are patterned together to provide high connectivity with fast software routing times and high-speed system performance.

Eight fully distributed primary clocks are routed on a low-skew, high-speed distribution network and may be sourced from dedicated I/O pads, PLLs, or the PLC logic. Secondary and edge-clock routing is available for fast regional clock or control signal routing for both internal regions and on device edges. Secondary clock routing can be sourced from any I/O pin, PLLs, or the PLC logic.

The improved routing resources offer great flexibility in moving signals to and from the logic core. This flexibility translates into an improved capability to route designs at the required speeds when the I/O signals have been locked to specific pins.

# **System-Level Features**

The Series 4 also provides system-level functionality by means of its microprocessor interface, Embedded System Bus, quad-port Embedded Block RAMs, universal programmable Phase-Locked Loops, and the addition of highly tuned networking specific Phase-Locked Loops. These functional blocks allow for easy, glueless system interfacing and the capability to adjust to varying conditions in today's high-speed networking systems.

#### **MicroProcessor Interface**

The MPI provides a glueless interface between the FPGA and *PowerPC* microprocessors. Programmable in 8-bit, 16-bit, and 32-bit interfaces with optional parity to the *Motorola® PowerPC* 860 bus, it can be used for configuration and readback, as well as for FPGA control and monitoring of FPGA status. All MPI transactions utilize the Series 4 Embedded System Bus at 66 MHz performance.

A system-level microprocessor interface to the FPGA user-defined logic following configuration, through the system bus, including access to the Embedded Block RAM and general user-logic, is provided by the MPI. The MPI supports burst data read and write transfers, allowing short, uneven transmission of data through the interface by including data FIFOs. Transfer accesses can be single beat (1 x 4 bytes or less), 4-beat (4 x 4 bytes), 8-beat (8 x 2 bytes), or 16-beat (16 x 1 bytes).

## System Bus

An on-chip, multimaster, 8-bit system bus with 1-bit parity facilitates communication among the MPI, configuration logic, FPGA control, and status registers, Embedded Block RAMs, as well as user logic. Utilizing the *AMBA* specification Rev 2.0 AHB protocol, the Embedded System Bus offers arbiter, decoder, master, and slave elements. Master and slave elements are also available for the user-logic and a slave interface is used for control and status of the embedded backplane transceiver portion of the ORSPI4.

The system bus control registers can provide control to the FPGA such as signaling for reprogramming, reset functions, and PLL programming. Status registers monitor INIT, DONE, and system bus errors. An interrupt controller is integrated to provide up to eight possible interrupt resources. Bus clock generation can be sourced from the microprocessor interface clock, configuration clock (for slave configuration modes), internal oscillator, user clock from routing, or from the port clock (for JTAG configuration modes).

#### **Phase-Locked Loops**

Four user PLLs are provided by the ORSPI4 FPSC. Programmable PLLs can be used to manipulate the frequency, phase, and duty cycle of a clock signal. Each PLL is capable of manipulating and conditioning clocks from 20 MHz to 420 MHz. Frequencies can be adjusted from 1/8x to 8x, the input clock frequency. Each programmable PLL provides two outputs that have different multiplication factors but can have the same phase relationships. Duty cycles and phase delays are programmable (12.5% steps of the clock period increments). An automatic input buffer delay compensation mode is available for phase delay. Each PPLL provides two outputs that can have programmable (12.5% steps) phase differences.

# **FPGA Configuration**

The FPGA functionality is determined by internal configuration RAM. The FPGAs internal initialization/configuration circuitry loads the configuration data at power-up or under system control. The configuration data can reside externally in an EEPROM or any other storage media. Serial EEPROMs provide a simple, low pin-count method for configuring FPGAs.

The RAM is loaded by using one of several configuration modes. Supporting the traditional master/slave serial, master/slave parallel, and asynchronous peripheral modes, the Series 4 also utilizes its microprocessor interface and Embedded System Bus to perform both programming and readback. Daisy chaining of multiple devices and partial reconfiguration are also permitted.

Other configuration options include the initialization of the embedded-block RAM memories and FPSC memory, as well as system bus options and bit stream error checking. Programming and readback through the JTAG (IEEE 1149.2) port is also available, meeting In-System Programming (ISP) standards (IEEE 1532 Draft).

# **FPSC Configuration**

Configuration of the ORSPI4 occurs in two stages: FPGA bit-stream configuration and embedded core setup.

Prior to becoming operational, the FPGA goes through a sequence of states, including power-up, initialization, configuration, start-up, and operation. The FPGA logic is configured by standard FPGA bit-stream configuration means as discussed in the *ORCA* Series 4 FPGA data sheet.

After the FPGA configuration is complete, the options for the embedded core are set based on the contents of registers that are accessed through the FPGA system bus. The system bus itself can be driven by an external *PowerPC* compliant microprocessor via the MPI block or via a user master interface in FPGA logic. A simple IP block that drives the system by using the user register interface and very little FPGA logic is available in the *MPI/System Bus Technical Note (TN-1017)*. This IP block sets up the embedded core via a state machine and allows the ORSPI4 to work in an independent system without an external microprocessor interface.

# **ORSPI4 Package Options**

The ORSPI4 FPSC is available in two package options: a 1036 fpSBGA and a 1156 fpBGA. The 1036 pin package provides an OR4E06 FPGA array (16,192 LEs, 148 Kbits of Embedded Block RAM), 498 FPGA user I/Os, two SPI4 interfaces (or one SPI4 interface and a quad high-speed SERDES interface), and a high-speed QDRII SRAM Controller. The 1156 pin package provides an OR4E06 FPGA array (16,192 LEs, 148 Kbits of Embedded Block RAM), 356 FPGA user I/Os, two SPI4 interfaces (SERDES interface not available on this package), and a high-speed QDRII SRAM Controller.

#### Additional Information

Contact your local Lattice representative for additional information regarding the *ORCA* Series 4 FPGA devices, or visit our website at: http://www.latticesemi.com/orca

# **Links to Specs and Standards**

Optical Internetworking Forum - OIF-SPI4-02.0 - www.oiforum.com

Fibre Channel Physical and Signaling Interface - FC-PH ANSI X3.230-1994 - www.t11.org

10 Gigabit Ethernet - IEEE P802.3ae - www.ieee.org

18Mb QDR-II SRAM 2-word burst – MT54W512H36B - www.cypress.com/products/micron/micron.cfm

18Mb QDR-II SRAM 4-word burst – MT54W512H36B - www.cypress.com/products/micron/micron.cfm

36Mb QDR-II SRAM 2-word burst - KTR323682M - www.samsung.com/Products/Semiconductor/SRAM/index.htm

36Mb QDR-II SRAM 4-word burst – KTR323684M - www.samsung.com/Products/Semiconductor/SRAM/index.htm

# **ORSPI4 SPI4 Data Formats**

The data format across the SPI4 interface follows the OIF SPI4 convention where the lowest byte number occupies the highest bit positions within the 16-bit word as shown in Figure 5. On payload transfers that do not end on an even byte boundary, the unused byte (after the last valid byte) on bit positions 7 through 0 is set to all zeroes as shown in Figure 5.

Figure 5. SPI4 Byte and Bit Ordering

|      | 15     | 7 0              |

|------|--------|------------------|

|      | Byte 0 | Byte 1           |

| TDAT | Byte 2 | Byte 3           |

|      | Byte 4 | x (set to zeros) |

|      | 15     | 7 0              |

| RDAT | Byte 0 | Byte 1           |

|      | Byte 2 | Byte 3           |

|      | Byte 4 | x (set to zeros) |

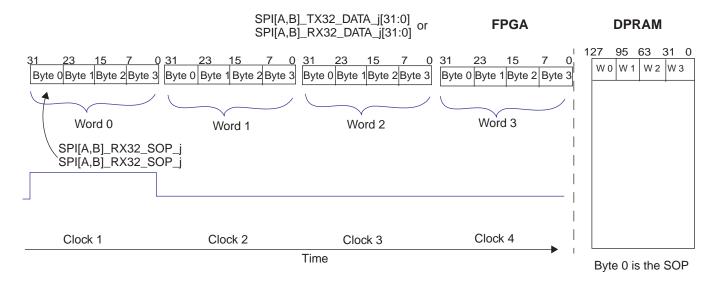

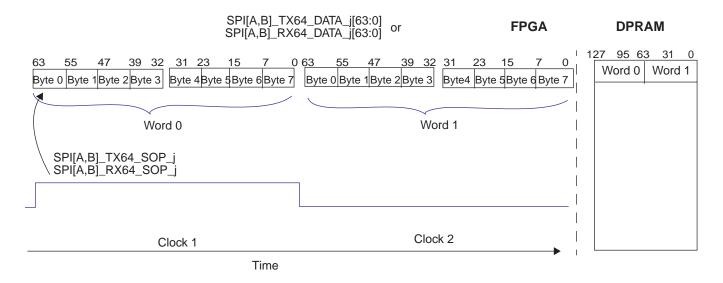

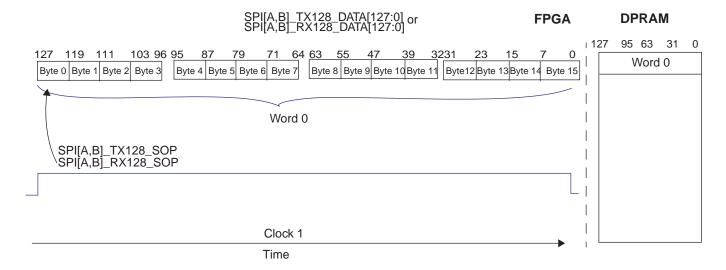

At the FPGA-embedded core RX and TX interface, the same SPI4 convention is followed wherein the lowest byte number occupies the highest bit positions within a word. This is the same in all operating modes - 32-bit, 64-bit and 128-bit.

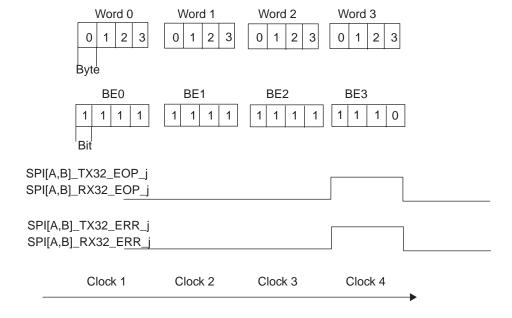

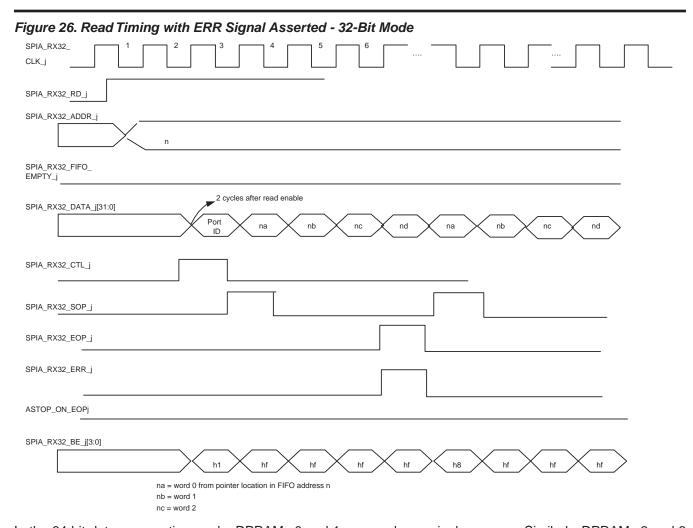

Byte enables for all data except EOP should be "1". During an EOP, the last valid byte enable within a 32-bit, 64-bit or 128-bit word indicates the last byte for the packet. Figure 6 shows EOP signal being asserted during Word 3. In Figure 6, the last valid byte enable within "1110" in Word 3 indicates the EOP. The valid byte enables during an EOP are "1111", "1110", "1100" and "1000". If the packet was errored, the ERR signal is asserted and will remain asserted until EOP as shown in Figure 6

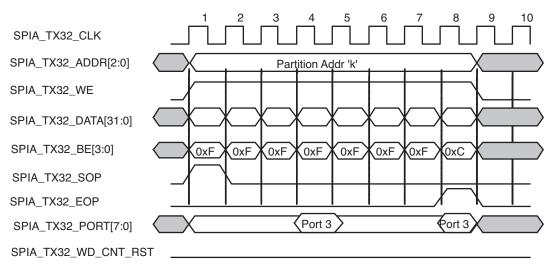

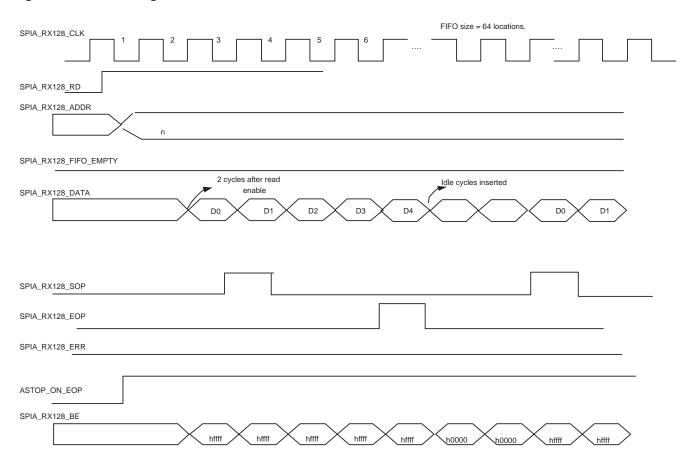

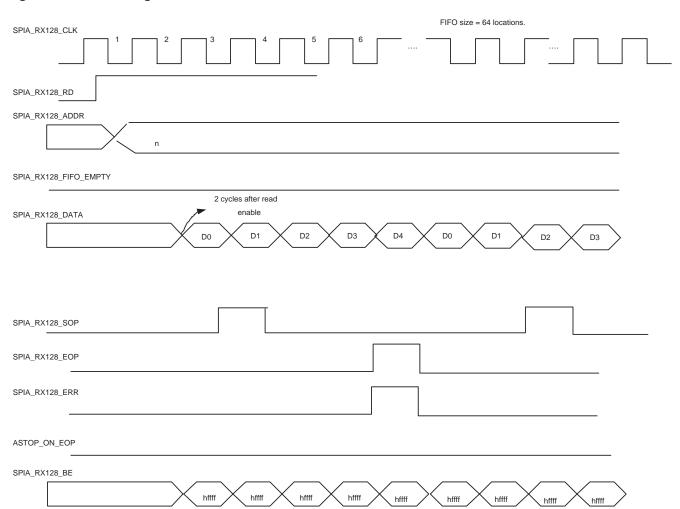

Figure 6. Example of EOP Indication in 32-Bit Mode

The bit ordering in the data format in the 32-bit aggregation mode is shown in Figure 7. In 32-bit mode, data transfers are done in 4-word bursts with the exception of an EOP. As shown in the figure, SOP is always aligned to the most significant 32-bit word, Word 0 of a 4-word burst. The first byte of a packet is always Word 0. The SOP indicator is high during Word 0. EOP can be any byte within the 32-bit word. The last valid byte enable within a 32-bit word indicates the end of packet. The EOP signal can be high during Word 0, Word 1, Word 2 or Word 3. It should be used in conjunction with the byte enables to determine the last byte in that data transfer. If data transfers do not end on Word 3, then the burst is terminated and Word 0 of the next burst is sent to the user. For example, if EOP occurs during Word 2, Word 3 will be discarded and Word 0 of the next word will be sent to the user.

Figure 7. Byte and Bit Ordering in 32-Bit Operating Mode

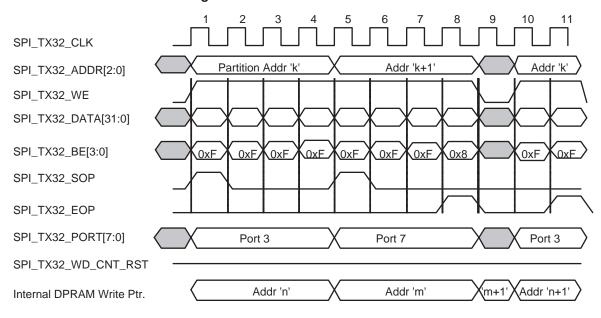

The bit ordering in the data format in the 64-bit aggregation mode is shown in Figure 8. In 64-bit mode, data transfers are done in 2-word bursts with the exception of an EOP. As shown in the figure, SOP is always aligned to the most significant 64-bit Word 0 of a 2-word burst. The first byte of a packet is always Word 0. The SOP indicator is high during word Word 0.

Figure 8. Byte and Bit Ordering in 64-Bit Mode

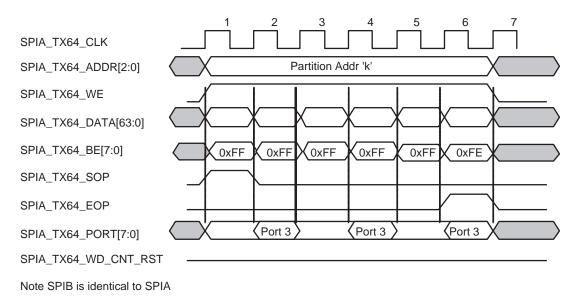

The bit ordering in the data format in the 128-bit aggregation mode is shown in Figure 9. The first byte of a packet is always byte 0 of the 128-bit word. As shown in the figure, SOP is always aligned to the most significant 64-bit Word 0 of a 2-word burst. SOP is always aligned to byte 0 of the 128-bit word.

Figure 9. Byte and Bit Ordering in 128-Bit Mode

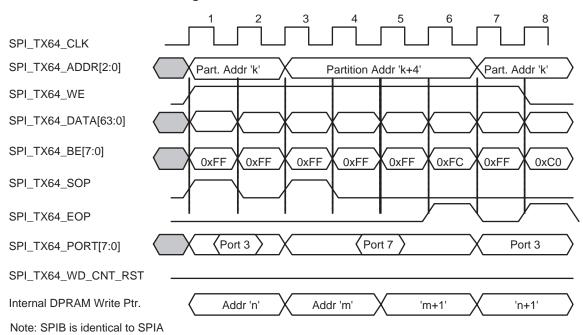

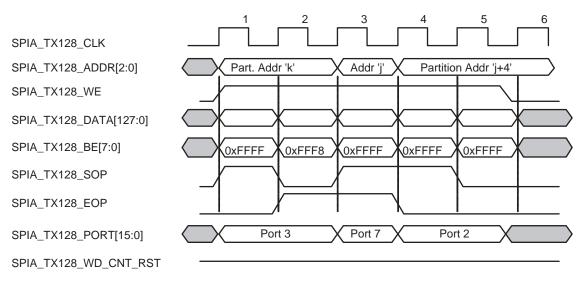

# **SPI4 Transmit Path Functional Description**

This section describes the transmit section of the SPI4 interface. The ORSPI4 device contains two identical, yet independent Transmit SPI4 compliant interfaces within the FPSC. The description provided within this section is applicable to both Transmit SPI4 interfaces.

The Transmit SPI4 interface supports the following features:

- Independent TX interface that is not tied to associated Receive SPI4 interface

- 10 Gbit/s data throughput

- 4 dual-port memories used to provide 256 Bytes of buffering for up to 32 ports. If support for more than 32 ports is required, the dual-port memories can be used, or they can be used for clock crossing purposes while data is buffered with external memory.

- Simple FIFO-like interface from FPGA to SPI4 TX embedded core block.

- Calendar Control Logic, including the Transmit Calendar, Shadow Calendar and support for up to 256 ports (the maximum allowable number of SPI4 ports).

- Mixed data width aggregation modes at the user Transmit interface. 32, 64, and 128-bit modes are supported.

- Programmable calendar table, supporting all calendar configuration parameters as specified in the SPI4 standard.

- Feedback to FPGA of currently serviced SPI4 port.

The Transmit SPI4 logic enables users to write port data from a variety of interfaces and associated clock domains using Dual Port RAMs (DPRAM) for temporary storage and clock domain crossing. Data is written into the DPRAM banks from the FPGA and read according to a pre-configured transmit calendar sequence. Data is formatted into the SPI4 format and transmitted to the physical links as LVDS signals, as specified by OIF-SPI4-02.0.

In addition to the transmit data path, out-of-band status information is received on the Transmit Status lines. This information is used, along with preconfigured Calendar sequence information, to schedule the servicing of SPI4 port for data transmission. The status information is also passed back to the FPGA logic. There are also several other features incorporated into the embedded core such as parallel loopback and SPI4 loopback to assist in debugging and statistic gathering.

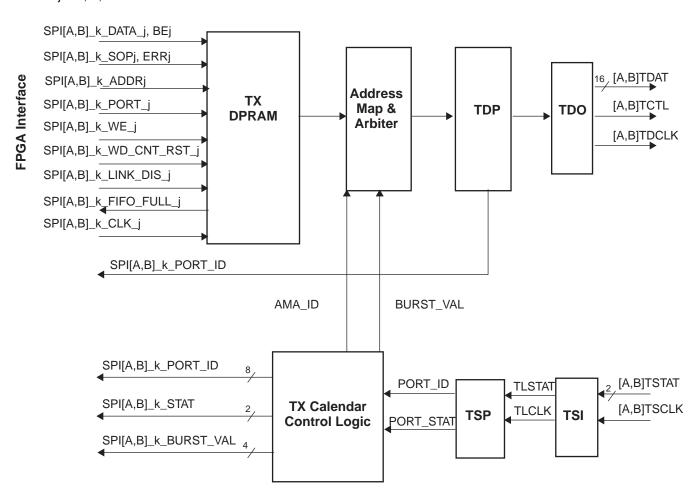

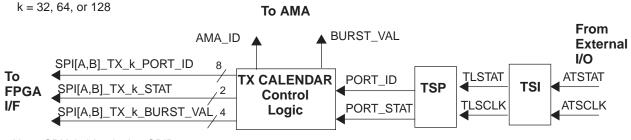

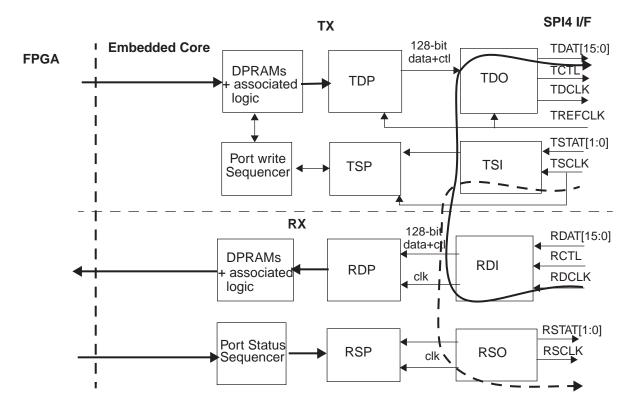

The major blocks associated with the ORSPI4 transmitter are:

- Four Transmit DPRAM Banks

- Address Map and Arbiter (AMA)

- Transmit Calendar Control Logic

- Port Write Sequencer Logic (PWS)

- SPI4 Logic Data

- SPI4 Transmit Data Logic (TDP)

- SPI4 Transmit I/O Interface (TDO)

- SPI4 Transmit Status Logic (TSP)

- SPI4 Transmit Status Interface (TSI)

- SPI4 Transmit Status Protocol (TSP)

These blocks will be described in detail in the following sections. The ORSPI4 Transmit functional block diagram is shown in Figure 10.

.

Figure 10. ORSPI4 Transmit Functional Block Diagram

k = TX32, TX64 or TX128j = 0, 1, 2 or 3

## **ORSPI4 Transmit Functional Block Overview**