## DUAL FORWARD-CONDUCTING P-GATE THYRISTORS PROGRAMMABLE OVERVOLTAGE PROTECTORS

## TISP61060 Gated Protector Series

**Dual Voltage-Programmable Protectors**

- Third Generation Design using Vertical Power Technology

- Wide -5 V to -85 V Programming Range

- High 150 mA min. Holding Current

- Reduced V<sub>BAT</sub> Supply Current

Triggering Current is Typically 50x Lower

Negative Value Power Induction Current Removes Need for Extra Protection Diode

#### Rated for LSSGR & FCC Surges

| Standard    | Wave Shape | I <sub>TSP</sub> |

|-------------|------------|------------------|

| LSSGR       | 10/1000 μs | 30               |

| FCC Part 68 | 10/160 μs  | 45               |

| LSSGR       | 2/10 μs    | 50               |

Surface Mount and Through-Hole Options

- TISP61060P for Plastic DIP

- TISP61060D for Small-Outline

- TISP61060DR for Taped and Reeled Small-Outline

#### **Functional Replacements for**

| Part Numbers                 | Functional<br>Replacement |

|------------------------------|---------------------------|

| TCM1030P, TCM1060P, LB1201AB | TISP61060P                |

| TCM1030D, TCM1060D, LB1201AS | TISP61060D                |

| TCM1030DR, TCM1060DR         | TISP61060DR               |

...... UL Recognized Components

## Description

The TISP61060 is a dual forward-conducting buffered p-gate overvoltage protector. It is designed to protect monolithic SLICs (Subscriber Line Interface Circuits), against overvoltages on the telephone line caused by lightning, a.c. power contact and induction. The TISP61060 limits voltages that exceed the SLIC supply rail voltage.

The SLIC line driver section is typically powered from 0 V (ground) and a negative voltage in the region of -10 V to -70 V. The protector gate is connected to this negative supply. This references the protection (clipping) voltage to the negative supply voltage. As the protection voltage will track the negative supply voltage, the overvoltage stress on the SLIC is minimized. (See Applications Information.)

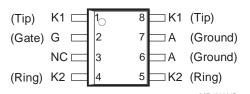

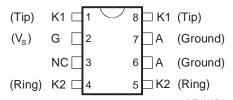

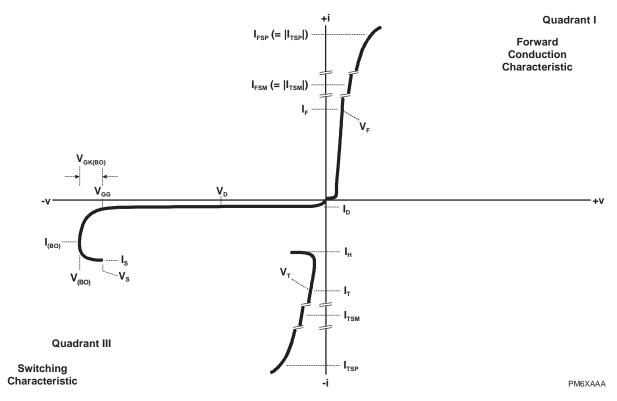

## D Package (Top View)

NC - No internal connection Terminal typical application names shown in parenthesis

## P Package (Top View)

NC - No internal connection Terminal typical application names shown in parenthesis

#### **Device Symbol**

Terminals K1, K2 and A correspond to the alternative line designators of T, R and G or A, B and C. The negative protection voltage is controlled by the voltage,  $V_{GG}$ , applied to the G terminal.

Positive overvoltages are clipped to ground by diode forward conduction. Negative overvoltages are initially clipped close to the SLIC negative supply rail value. If sufficient current is available from the overvoltage, then the protector will crowbar into a low voltage on-state condition. As the current subsides the high holding current of the crowbar prevents d.c. latchup.

These monolithic protection devices are fabricated in ion-implanted planar vertical power structures for high reliability and in normal system operation they are virtually transparent. The buffered gate design reduces the loading on the SLIC supply during overvoltages caused by power cross and induction.

## BOURNS®

## **Absolute Maximum Ratings**

| Rating                                                                              | Symbol           | Value       | Unit  |

|-------------------------------------------------------------------------------------|------------------|-------------|-------|

| Repetitive peak off-state voltage, $V_{GK} = 0$ , -40 °C $\leq T_{J} \leq 85$ °C    | $V_{DRM}$        | -100        | V     |

| Repetitive peak gate-cathode voltage, $V_{KA} = 0$ , -40 °C $\leq T_{J} \leq 85$ °C | $V_{GKRM}$       | -85         | V     |

| Non-repetitive peak on-state pulse current (see Notes 1 and 2)                      |                  |             |       |

| 10/1000 μs                                                                          | Izon             | 30          | A     |

| 10/160 μs                                                                           | I <sub>TSP</sub> | 45          |       |

| 2/10 μs                                                                             |                  | 50          |       |

| Non-repetitive peak on-state current (see Notes 1 and 2)                            |                  |             |       |

| 60 Hz sine-wave, 25 ms                                                              | I <sub>TSM</sub> | 6           | A rms |

| 60 Hz sine-wave, 2 s                                                                |                  | 1           |       |

| Continuous on-state current (see Note 2)                                            | I <sub>TM</sub>  | 0.3         | Α     |

| Continuous forward current (see Note 2)                                             | I <sub>FM</sub>  | 0.3         | Α     |

| Operating free-air temperature range                                                | T <sub>A</sub>   | -40 to +85  | °C    |

| Junction temperatur e                                                               | T <sub>J</sub>   | -40 to +150 | °C    |

| Storage temperature range                                                           | T <sub>stg</sub> | -40 to +150 | °C    |

| Lead temperature 1.6 mm (1/16 inch) from case for 10 s                              | T <sub>L</sub>   | 260         | °C    |

- NOTES: 1. Initially the protector must be in thermal equilibrium with -40 °C ≤ T<sub>J</sub> ≤ 85 °C. The surge may be repeated after the device returns to its initial conditions.

- 2. The rated current values may be applied either to the Ring to Ground or to the Tip to Ground terminal pairs. Additionally, both terminal pairs may have their rated current values applied simultaneously (in this case the Ground terminal current will be twice the rated current value of an individual terminal pair). Above 85 °C, derate linearly to zero at 150 °C lead temperature.

## **Recommended Operating Conditions**

|                | Component                 |  | Тур | Max | Unit |

|----------------|---------------------------|--|-----|-----|------|

| C <sub>G</sub> | Gate decoupling capacitor |  | 100 |     | nF   |

## Electrical Characteristics, -40 °C ≤ T<sub>J</sub> ≤ 85 °C (Unless Otherwise Noted)

|                   | Parameter Test Conditions |                                                                               | Min     | Тур  | Max | Unit |    |

|-------------------|---------------------------|-------------------------------------------------------------------------------|---------|------|-----|------|----|

| L                 | Off-state current         | $V_D = -85 \text{ V}, V_{GK} = 0$                                             | = 25 °C |      |     | 5    | μΑ |

| ID                | On-state current          | T <sub>J</sub>                                                                | = 85 °C |      |     | 50   | μΑ |

|                   |                           | dv/dt = -250 V/ms, Source Resistance = 300 $\Omega$ , V <sub>GG</sub> = -50 V |         |      |     | -53  |    |

| V <sub>(BO)</sub> | Breakover voltage         | $dv/dt = -250$ V/ms, Source Resistance = 300 Ω, $V_{GG} = -65$ V              |         |      |     | -68  | V  |

| , ,               |                           | $I_T$ = 12.5 A, 10/1000 μs, Source Resistance = 80 $\Omega$ , $V_{GG}$ = -50  | 0 V     |      |     | -55  |    |

| I <sub>S</sub>    | Switching current         | $dv/dt = -250$ V/ms, Source Resistance = 300 Ω, $V_{GG} = -50$ V              |         | -100 |     |      | mA |

|                   |                           | I <sub>T</sub> = 1 A                                                          |         |      |     | 3    |    |

| VT                | On-state voltage          | I <sub>T</sub> = 10 A                                                         |         |      |     | 4    | V  |

| VT                | On-state voltage          | I <sub>T</sub> = 16 A                                                         |         |      |     | 5    | ٧  |

|                   |                           | I <sub>T</sub> = 30 A                                                         |         |      |     | 7    |    |

## Electrical Characteristics, -40 $^{\circ}$ C $\leq$ T $_{J}$ $\leq$ 85 $^{\circ}$ C (Unless Otherwise Noted) (Continued)

|                  | Parameter                | Test Conditions                                                              | Min   | Тур | Max | Unit |

|------------------|--------------------------|------------------------------------------------------------------------------|-------|-----|-----|------|

|                  |                          | I <sub>F</sub> = 1 A                                                         |       |     | 2   |      |

| VF               | Forward voltage          | $I_{F} = 10 \text{ A}$                                                       |       |     | 4   | V    |

| ''               |                          | I <sub>F</sub> = 16 A                                                        |       |     | 5   | -    |

|                  |                          | $I_{F} = 30 \text{ A}$                                                       |       |     | 5   |      |

| I <sub>H</sub>   | Holding current          | $I_T = -1$ A, di/dt = +1A/ms , $V_{GG} = -50$ V                              | -150  |     |     | mA   |

|                  | Gate reverse current     | $T_J = 25 ^{\circ}\text{C}$                                                  |       |     | 5   | μΑ   |

| I <sub>GAS</sub> | Gate reverse current     | $V_{GG}$ = -85 V, K and A terminals connected $T_{J}$ = 85 °C                |       |     | 50  | μΑ   |

| I <sub>GT</sub>  | Gate trigger current     | $I_T = -1 \text{ A, } t_{p(g)} \ge 20  \mu\text{s, } V_{GG} = -50 \text{ V}$ |       |     | 15  | mA   |

| dv/dt            | Critical rate of rise of | V <sub>GG</sub> = -50 V, (see Note 3)                                        | -1000 |     |     | V/us |

| av/at            | off-state voltage        | VGG = 30 V, (See Note 3)                                                     | 1000  |     |     | ν/μ3 |

| Co               | Anode-cathode off-       | $f = 1 \text{ MHz}, V_d = 0.1 \text{ V}, I_G = 0, \text{ (see Note 4)}$      |       | 85  |     | pF   |

| 0                | state capacitance        | $V_D = -50 \text{ V}$                                                        |       | 10  |     | pF   |

NOTES: 3. Linear rate of rise, maximum voltage limited to 80  $\%~V_{GG}$  .

4. These capacitance measurements employ a three terminal capacitance bridge incorporating a guard circuit. The unmeasured device terminals are a.c. connected to the guard terminal of the bridge.

## **Thermal Characteristics**

|                 | Parameter                               | Test Conditions                                  | i         | Min | Тур | Max | Unit |

|-----------------|-----------------------------------------|--------------------------------------------------|-----------|-----|-----|-----|------|

| $R_{\theta JA}$ | Junction to free air thermal resistance | P <sub>tot</sub> = 0.8 W, T <sub>A</sub> = 25 °C | D Package |     |     | 170 | °C/W |

| ТθЈА            | Junction to free all triefmarresistance | 5 cm <sup>2</sup> , FR4 PCB                      | P package |     |     | 125 | C/VV |

## **Parameter Measurement Information**

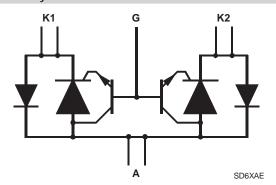

Figure 1. Voltage-Current Characteristic

#### **DEVICE PARAMETERS**

## General

Thyristor based overvoltage protectors, for telecommunications equipment, became popular in the late 1970s. These were fixed voltage breakover triggered devices, likened to solid state gas discharge tubes. As these were new forms of thyristors, the existing thyristor terminology did not cover their special characteristics. This resulted in the invention of new terms based on the application usage and device characteristic. Initially, there was a wide diversity of terms to describe the same thing, but today the number of terms have reduced and stabilized.

Programmable (gated) overvoltage protectors are relatively new and require additional parameters to specify their operation. Similar to the fixed voltage protectors, the introduction of these devices has resulted in a wide diversity of terms to describe the same thing. To help promote an understanding of the terms and their alternatives, this section has a list of alternative terms and the parameter definitions used for this data sheet. In general, the Bourns approach is to use terms related to the device internal structure, rather than its application usage as a single device may have many applications each using a different terminology for circuit connection.

## Alternative Symbol Cross-Reference Guide

This guide is intended to help the translation of alternative symbols to those used in this data sheet. As in some cases the alternative symbols have no substance in international standards and are not fully defined by the originators, users must confirm symbol equivalence. No liability will be assumed from the use of this guide.

#### Cross-Reference for TISP61060 and TCM1030/60

| TISP61060 Parameter                                                                 | Data Sheet<br>Symbol | Alternative<br>Symbol | Alternative Parameter                          |

|-------------------------------------------------------------------------------------|----------------------|-----------------------|------------------------------------------------|

| Ratings & Characteristics                                                           |                      | TCM1060, TCM1030      |                                                |

| Non-repetitive peak on-state pulse current                                          | I <sub>TSP</sub>     | -                     | Non-repetitive peak surge current              |

| Non-repetitive peak on-state current                                                | I <sub>TSM</sub>     | -                     | Non-repetitive peak surge current,10 ms        |

| Non-repetitive peak on-state current                                                | I <sub>TSM</sub>     | -                     | Continuous 60-Hz sinewave, 2 s                 |

| Forward voltage                                                                     | V <sub>F</sub>       | $V_{CF}$              | Forward clamping voltage                       |

| Forward current                                                                     | I <sub>F</sub>       | I <sub>FM</sub>       | Peak forward current                           |

| On-state voltage                                                                    | V <sub>T</sub>       | V <sub>C</sub>        | Reverse clamping voltage                       |

| On-state current                                                                    | I <sub>T</sub>       | I <sub>TM</sub>       | Peak reverse current                           |

| Switching current                                                                   | I <sub>S</sub>       | I <sub>trip</sub>     | Trip current                                   |

| Breakover voltage                                                                   | V <sub>(BO)</sub>    | $V_{trip}$            | Trip voltage                                   |

| Gate reverse current (with A and K terminals connected)                             | I <sub>GAS</sub>     | I <sub>D</sub>        | Stand-by current, TIP & RING at GND            |

| Off-state current                                                                   | I <sub>D</sub>       | I <sub>D</sub>        | Stand-by current, TIP & RING at V <sub>S</sub> |

| Off-state voltage                                                                   | V <sub>D</sub>       | V <sub>S</sub>        | Supply voltage                                 |

| Gate-cathode breakover voltage                                                      | V <sub>GK(BO)</sub>  | V <sub>OS</sub>       | Transient overshoot voltage                    |

| Gate voltage, (V <sub>GG</sub> is gate supply voltage referenced to the A terminal) | V <sub>G</sub>       | V <sub>S</sub>        | Supply voltage                                 |

| Off-state capacitance                                                               | C <sub>O</sub>       | C <sub>off</sub>      | Off-state capacitance                          |

| Terminals                                                                           |                      |                       | TCM1060, TCM1030                               |

| Cathode 1                                                                           | K1                   | Tip                   | Tip                                            |

| Cathode 2                                                                           | K2                   | Ring                  | Ring                                           |

| Anode                                                                               | Α                    | GND                   | Ground                                         |

| Gate                                                                                | G                    | V <sub>S</sub>        | Supply voltage                                 |

# **BOURNS®**

## Cross-Reference for TISP61060 and LB1201AB

| TISP 61060 Parameter                                                                | Data Sheet<br>Symbol | Alternative<br>Symbol | Alternative Parameter    |

|-------------------------------------------------------------------------------------|----------------------|-----------------------|--------------------------|

| Ratings & Characteristics                                                           |                      | LB1201AB              |                          |

| Non-repetitive peak on-state pulse current                                          | I <sub>TSP</sub>     | I <sub>P</sub>        | Pulse current            |

| Non-repetitive peak on-state current                                                | I <sub>TSM</sub>     | l <sub>P</sub>        | RMS pulse current, 60 Hz |

| On-state voltage                                                                    | V <sub>T</sub>       | V <sub>ON</sub>       | On-state voltage         |

| Switching current                                                                   | I <sub>S</sub>       | I <sub>t</sub>        | Trip current             |

| Breakover voltage                                                                   | V <sub>(BO)</sub>    | $V_{T}$               | Trip voltage             |

| Maximum continuous on- state current                                                | I <sub>TM</sub>      | I <sub>C</sub>        | On-state current         |

| Maximum continuous forwar d current                                                 | I <sub>FM</sub>      | I <sub>C</sub>        | On-state current         |

| Gate voltage, (V <sub>GG</sub> is gate supply voltage referenced to the A terminal) | V <sub>G</sub>       | V <sub>S</sub>        | Supply voltage           |

| Off-state capacitance                                                               | Co                   | C <sub>OFF</sub>      | Off-state capacitance    |

| Terminals                                                                           | •                    |                       | LB1201AB                 |

| Cathode 1                                                                           | K1                   | Tip                   | Tip                      |

| Cathode 2                                                                           | K2                   | Ring                  | Ring                     |

| Anode                                                                               | A                    | GND                   | Ground                   |

| Gate                                                                                | G                    | V <sub>S</sub>        | Supply voltage           |

#### APPLICATIONS INFORMATION

## **Electrical Characteristics**

The electrical characteristics of a thyristor overvoltage protector are strongly dependent on junction temperature, T<sub>J</sub>. Hence a characteristic value will depend on the junction temperature at the instant of measurement. The values given in this data sheet were measured on commercial testers, which generally minimize the temperature rise caused by testing.

#### **Gated Protector Evolution and Characteristics**

This section covers three topics. First, it is explained why gated protectors are needed. Second, the performance of the original IC (integrated circuit) based version is described. Third, the performance improvements given by the TISP61060 are detailed.

#### **Purpose of Gated Protectors**

Fixed voltage thyristor overvoltage protectors have been used since the early 1980s to protect monolithic SLICs (Subscriber Line Interface Circuits) against overvoltages on the telephone line caused by lightning, a.c. power contact and induction. As the SLIC was usually powered from a fixed voltage negative supply rail, the limiting voltage of the protector could also be a fixed value. The TISP1072F3 is a typical example of a fixed voltage SLIC protector.

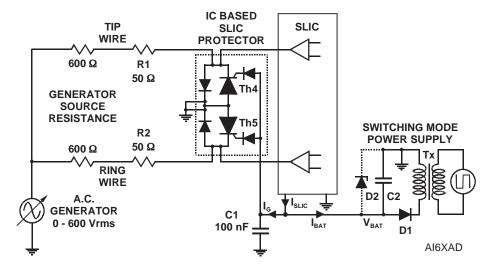

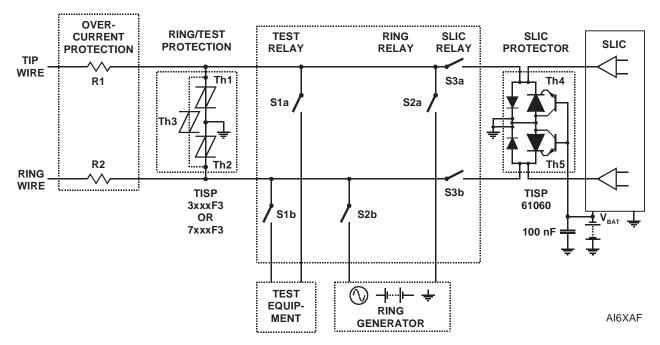

SLICs have become more sophisticated. To minimize power consumption, some designs automatically adjust the supply voltage, V<sub>BAT</sub>, to a value that is just sufficient to drive the required line current. For short lines the supply voltage would be set low, but for long lines, a higher supply voltage would be generated to drive sufficient line current. The optimum protection for this type of SLIC would be given by a protection voltage which tracks the SLIC supply voltage. This can be achieved by connecting the protection thyristor gate to the SLIC supply, Figure 2. This gated (programmable) protection arrangement minimizes the voltage stress on the SLIC, no matter what value of supply voltage.

Figure 2. Simplified IC Based SLIC Protector Circuit

#### **IC Based Protectors**

In 1986, an IC based gated protector was proposed (A 90 V Switching Regulator and Lightning Protection Chip Set, Robert K. Chen, Thomas H. Lerch, Johnathan S. Radovsky, D. Alan Spires, IEEE Solid-State Circuits Conference, February 20, 1986, pp 178/9 and pp 340/1). Commercially, this resulted in the AT&T Microelectronics LB1201AB device and the higher current Texas Instruments Inc. TCM1060 device.

This implementation consisted of four diodes and two high holding current thyristors. Positive overvoltages on the line wires are clipped to ground by forward conduction of the wire to ground diodes. Negative overvoltages are initially clipped close to the SLIC negative supply rail, V<sub>BAT</sub>, by conduction of the thyristor cathode-gate and gate series diode. This means that the protection voltage level for slow wave forms will be about 1.5 V lower than the SLIC supply voltage. If sufficient current is available from the overvoltage, then the thyristor will switch into a low voltage on-state condition. When the thyristor crowbars, the two series gate diodes prevent the SLIC supply from being shorted to ground via the thyristor gate. As the overvoltage subsides the high holding current of the crowbar prevents d.c. latchup (see Figure 1).

#### Impulse Protection Performance

The impulse protection voltage will be the sum of the gate supply ( $V_{BAT}$ ) and the impulse peak gate-cathode voltage ( $V_{GK(BO)}$ ). Capacitor C1 provides the pulse of gate current that occurs during fast rising impulses. The protection voltage will be increased if there is a long connection between the gate decoupling capacitor, C1, and the gate terminal. During the initial rise of a fast impulse (e.g. 2/10), the gate current ( $I_C$ ) is the same as the cathode current ( $I_C$ ). Rates of 70 A/ $\mu$ s can cause inductive voltages of 0.7 V in 2.5 cm of printed wiring track. To minimize this inductive voltage increase of protection voltage, the length of the capacitor to gate terminal tracking should be minimized. Inductive voltages in the protector cathode wiring can increase the protection voltage. These voltages can be minimized by routing the SLIC connection through the protector as shown in Figure 2.

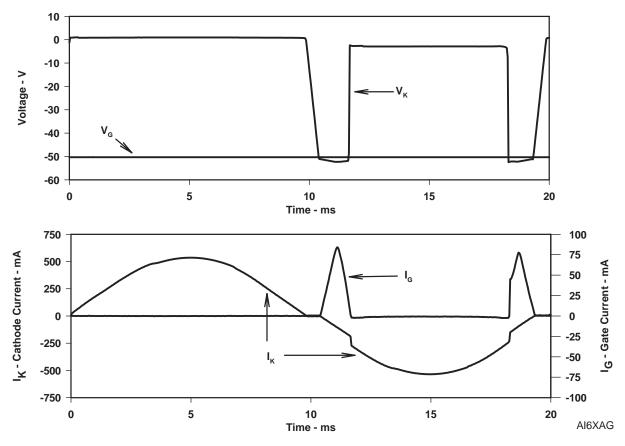

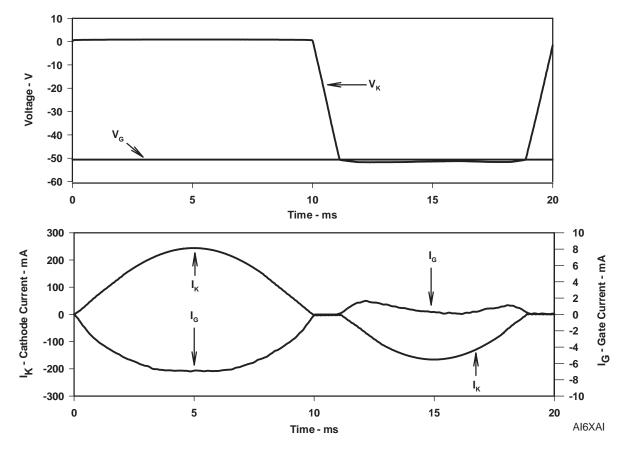

Figure 3. IC Protector Power Cross Wave Forms

## **AC Protection Performance**

Figure 2 shows a typical a.c. power cross test circuit. A variable voltage a.c. source is applied to the line card via  $600 \Omega$  series resistors. On the line card there are further series resistors R1 and R2. These resistors provide overcurrent protection by fusing or going high resistance under high current a.c. conditions.

Figure 3 shows the gate and cathode a.c. power line cross voltage and current wave forms of the IC based protector. Positive voltages are clipped at about +1 V by diode conduction. Negative voltages are clipped to about -52 V as the SLIC supply voltage was -50 V. Sufficient current (200 mA) was available to cause the thyristor to switch into the low-voltage on-state condition. At the end of the negative half cycle, the thyristor switches off when the current falls below the holding current value (300 mA). Switch-off and re-clipping at -52 V causes a second pulse of gate current. The wire current drawn by the protector is quasi-sinusoidal.

During the positive a.c. voltage period (diode clipping) there is no gate current. During the negative a.c. voltage period there are two triangular pulses of gate current, which peak at about 80 mA. This is current which flows into the gate terminal as indicated by the  $I_G$  current arrow in Figure 2. This direction of current charges the  $V_{BAT}$  supply. This would not be a problem if the  $V_{BAT}$  supply was a rechargeable battery.

#### **AC Protection Performance (continued)**

However, often the supply is generated from a switching mode power supply or the SLIC supply feed has a series diode which blocks reverse (charging) current flow to the battery. In these cases the supply can only sink current in the direction shown by the  $I_{BAT}$  arrow in Figure 2. Unless the SLIC current,  $I_{SLIC}$ , is equal or greater than  $I_G$  the value of  $V_{BAT}$  will increase, possibly to a level which causes destruction of the SLIC.

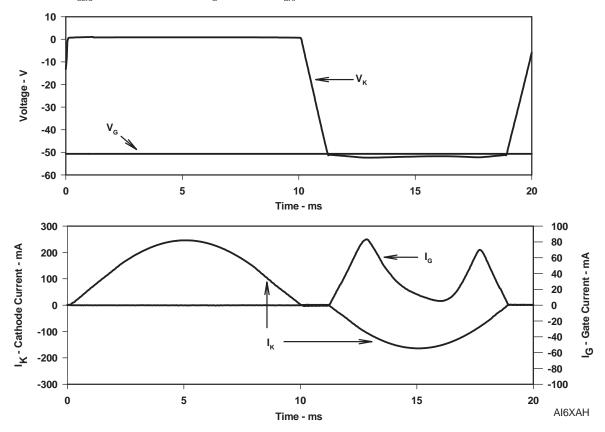

Figure 4. IC Protector High Impedance Power Cross Clipping Wave Forms

The maximum average value of  $I_G$  occurs when the thyristor only clips the voltage and the peak cathode current is just beginning to approach the switching ( $I_S$ ) value, see Figure 4. The average current is maximized under high source impedance conditions (e.g. 600  $\Omega$ ). In the case of the LB1201AB, it is recommended that the supply should be able to absorb 700 mA of "wrong way" current. If the supply cannot absorb the current then a shunt breakdown diode is recommended to provided a path for the gate current to ground (D2 in Figure 2). High power diodes are expensive, so diode D2 is usually low power, purposely selected to fail under this a.c. condition and protect the SLIC.

## TISP61060 Buffered Gate Protector

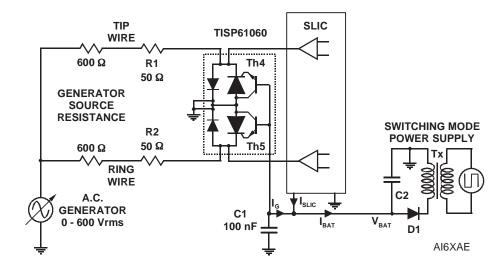

The TISP61060 improves on the original IC based design in three ways, Figure 5. First, the thin lateral IC structure has been changed to a vertical power device structure for increased area efficiency and greater energy capability. Second, the series gate diodes have been changed to transistor buffers. The maximum current injected into the gate supply is then reduced by the transistors gain factor ( $H_{FE}$ ). Third, some current from the positive voltage diode conduction has been diverted to the gate terminal which subtracts from the normal gate current. In most cases, this allows any previously used SLIC supply rail shunt protection diode to be removed. Although the SLIC supply is taken to a terminal that is internally connected to transistor bases, the terminal is still designated as the gate terminal, G.

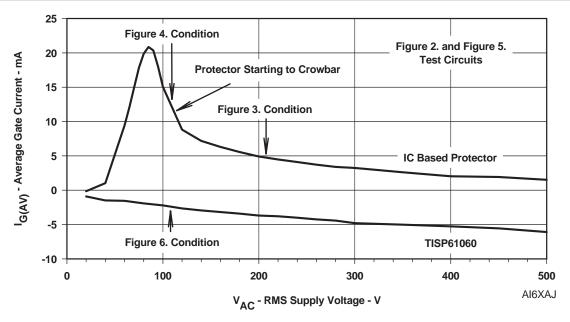

Figure 6 shows the high impedance a.c. waveforms for the TISP61060. As the TISP61060 replaces the IC based protector's gate diode with a transistor, the peak gate current is reduced by over 50 times. In addition there is a compensating negative gate current flow during diode conduction. The TISP61060 has the maximum value of peak gate current specified and so allows for a designer to design for limit conditions. Most IC protectors do not specify this parameter. Figure 7 shows the improvement due to the TISP61060. These plots show the full cycle average gate current against rms a.c. voltage. The IC based protector has a substantial positive gate current which will always charge the SLIC supply, possibly causing an overvoltage. The TISP61060 has a negative gate current and so cannot overvoltage the SLIC.

## TISP61060 Buffered Gate Protector (Continued)

Figure 5. TISP61060 Buffered Gate Protector

Figure 6. TISP61060 High Impedance Power Cross Clipping Wave Forms

# **BOURNS®**

## TISP61060 Buffered Gate Protector (Continued)

Figure 7. Average Gate Current vs AC Supply Voltage in Figures 2 And 5

## Circuit Component Values

The TISP61060 is a functional replacement for three devices, the LB1201, TCM1030 and TCM1060. These devices have a minimum value of series limiting resistor (R1 and R2 in Figure 2) which will ensure that the impulse surge current will not exceed the device rated value. This is summarized in the table below.

| De        | vice                               | 10/1000<br>1 kV, 10 Ω | 10/160<br>1.5 kV, 7.5 Ω | 2/10<br>2.5 kV, 5 Ω | Recommended Minimum Series Resistance $\Omega$ |

|-----------|------------------------------------|-----------------------|-------------------------|---------------------|------------------------------------------------|

|           | I <sub>TSP</sub> A                 | 12.5                  | 18.5                    | 23                  |                                                |

| LB1201    | Minimum Series<br>Resistance Ω     | 70                    | 73.6                    | 104                 | 100                                            |

|           | I <sub>TSP</sub> A                 | 16                    | 25                      | 35                  |                                                |

| TCM1030   | Minimum Series Resistance $\Omega$ | 52.5                  | 52.5                    | 66.4                | 100                                            |

|           | I <sub>TSP</sub> A                 | 30                    | 45                      | 50                  |                                                |

| TCM1060   | Minimum Series<br>Resistance Ω     | 23.3                  | 25.8                    | 45                  | 50                                             |

|           | I <sub>TSP</sub> A                 | 30                    | 45                      | 50                  |                                                |

| TISP61060 | Minimum Series<br>Resistance Ω     | 23.3                  | 25.8                    | 45                  | 50                                             |

**BOURNS®**

#### Circuit Component Values (Continued)

This table shows that the TISP61060 has impulse ratings which are higher or equal to those of the other three devices. Similarly, the TISP61060 has a.c. ratings which are higher or equal to those of the other three devices. A series overcurrent protector should be included in the wire feed to prevent exceeding the TISP61060 a.c. ratings. As covered earlier, the gate decoupling capacitor should be 100 nF and should be mounted as close to the protector as possible.

#### **Application Circuit**

Figure 8 shows a typical TISP61060 SLIC card protection circuit. The incoming line wires, R and T, connect to the relay matrix via the series overcurrent protection. Fusible resistors, fuses and positive temperature coefficient (PTC) resistors can be used for overcurrent protection. Resistors will reduce the prospective current from the surge generator for both the TISP61060 and the ring/test protector. The TISP7xxxF3 protector has the same protection voltage for any terminal pair. This protector is used when the ring generator configuration may be ground or battery-backed. For dedicated ground-backed ringing generators, the TISP3xxxF3 gives better protection as its inter-wire protection voltage is twice the wire to ground value.

Figure 8. Typical Application Circuit

Relay contacts 3a and 3b connect the line wires to the SLIC via the TISP61060 protector. The protector gate reference voltage comes from the SLIC negative supply (V<sub>BAT</sub>). A 100 nF gate capacitor sources the high gate current pulses caused by fast rising impulses.

#### **MECHANICAL DATA**

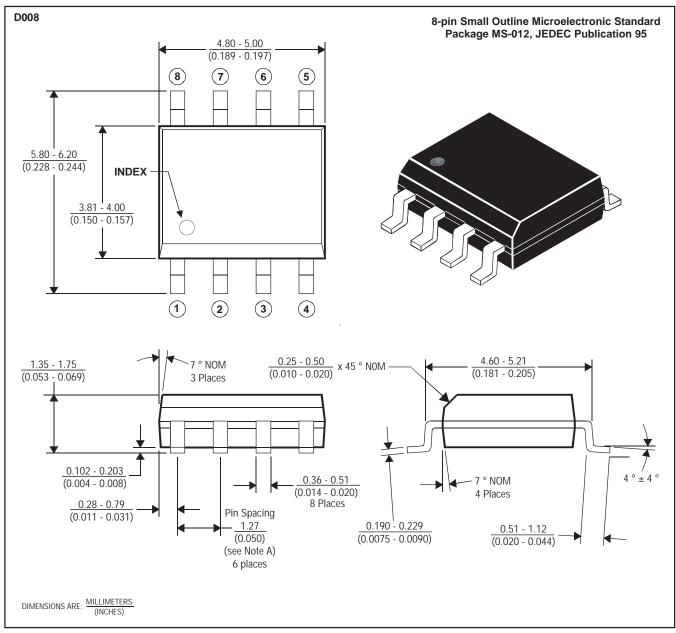

#### D008 Plastic Small-outline Package

This small-outline package consists of a circuit mounted on a lead frame and encapsulated within a plastic compound. The compound will withstand soldering temperature with no deformation, and circuit performance characteristics will remain stable when operated in high humidity conditions. Leads require no additional cleaning or processing when used in soldered assembly.

MDXXAAE

NOTES: A. Leads are within 0.25 (0.010) radius of true position at maximum material condition.

- B. Body dimensions do not include mold flash or protrusion.

- C. Mold flash or protrusion shall not exceed 0.15 (0.006).

- D. Lead tips to be planar within  $\pm 0.051$  (0.002).

SEPTEMBER 1995 — REVISED JUNE 2003

## **MECHANICAL DATA**

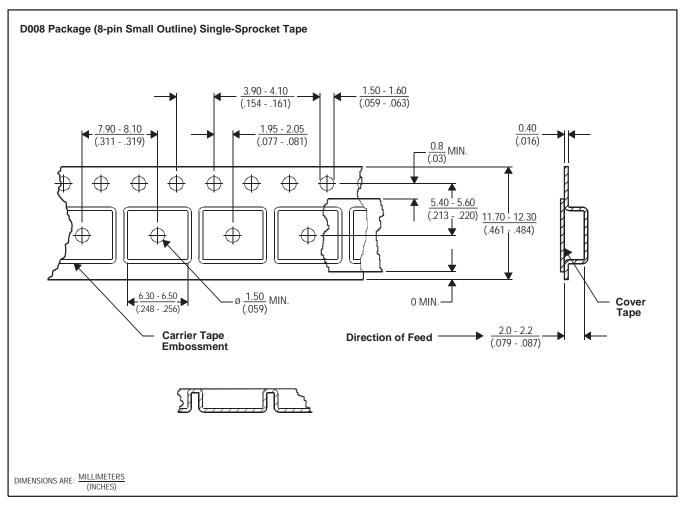

## **D008 Tape Dimensions**

NOTES: A. Taped devices are supplied on a reel of the following dimensions:-

MDXXATC

Reel diameter:  $\frac{330 + 0.0/-4.0}{(12.99 + 0.0/-.157)}$

Reel hub diameter:  $\frac{100 \pm 2.0}{(3.937 \pm .079)}$

Reel axial hole:  $\frac{13.0 \pm 0.2}{(.512 \pm .008)}$

B. 2500 devices are on a reel.

#### **MECHANICAL DATA**

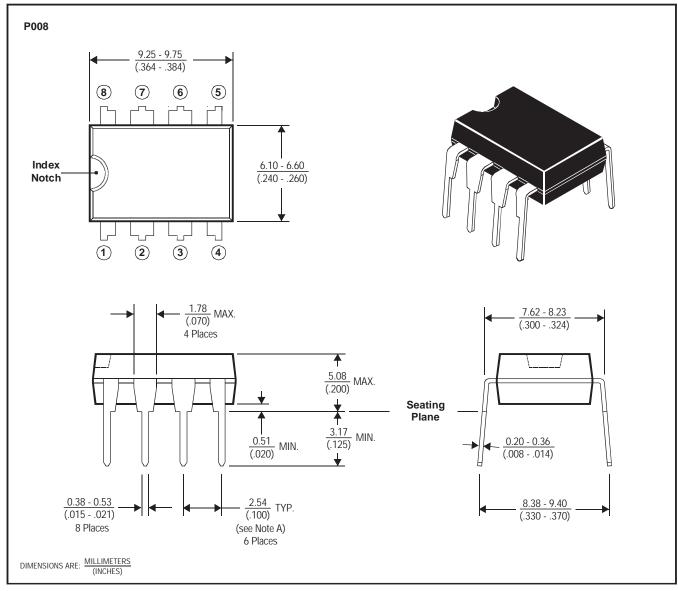

## P008 - Plastic Dual-In-Line Package

This dual-in-line package consists of a circuit mounted on a lead frame and encapsulated within a plastic compound. The compound will withstand soldering temperature with no deformation, and circuit performance characteristics will remain stable when operated in high humidity conditions The package is intended for insertion in mounting-hole rows on 7.62 (0.300) centers. Once the leads are compressed and inserted, sufficient tension is provided to secure the package in the board during soldering. Leads require no additional cleaning or processing when used in soldered assembly.

MDXXCF

- NOTES: A. Each pin centerline is located within 0.25 (0.010) of its true longitudinal position.

- B. Dimensions fall within JEDEC MS001 R-PDIP-T, 0.300" Dual-In-Line Plastic Family.

- C. Details of the previous dot index P008 package style, drawing reference MDXXABA, are given in the earlier publications.

## **Bourns Sales Offices**

| Region        | Phone           | Fax             |

|---------------|-----------------|-----------------|

| The Americas: | +1-909-781-5500 | +1-909-781-5700 |

| Europe:       | +41-41-7685555  | +41-41-7685510  |

| Asia-Pacific: | +886-2-25624117 | +886-2-25624116 |

## **Technical Assistance**

| Region        | Phone           | Fax             |

|---------------|-----------------|-----------------|

| The Americas: | +1-909-781-5500 | +1-909-781-5700 |

| Europe:       | +41-41-7685555  | +41-41-7685510  |

| Asia-Pacific: | +886-2-25624117 | +886-2-25624116 |

## www.bourns.com

Bourns® products are available through an extensive network of manufacturer's representatives, agents and distributors. To obtain technical applications assistance, a quotation, or to place an order, contact a Bourns representative in your area.