# Ringing FlexiSLIC

Subscriber Line Interface Circuit PBL 38774/1, Version 2.0

Wired Communications

Never stop thinking.

# Ringing FlexiSLIC Revision History: 2003-06-18 Previous Version: Page Subjects (major changes since last revision)

ABM®, ACE®, AOP®, ARCOFI®, ASM®, ASP®, DigiTape®, DuSLIC®, EPIC®, ELIC®, FALC®, GEMINAX®, IDEC®, INCA®, IOM®, IPAT®-2, ISAC®, ITAC®, IWE®, IWORX®, MUSAC®, MuSLIC®, OCTAT®, OptiPort®, POTSWIRE®, QUAT®, QuadFALC®, SCOUT®, SICAT®, SICOFI®, SIDEC®, SLICOFI®, SMINT®, SOCRATES®, VINETIC®, 10BaseV®, 10BaseVX® are registered trademarks of Infineon Technologies AG. 10BaseS™, EasyPort™, VDSLite™ are trademarks of Infineon Technologies AG. Microsoft® is a registered trademark of Microsoft Corporation, Linux® of Linus Torvalds, Visio® of Visio Corporation, and FrameMaker® of Adobe Systems Incorporated.

The information in this document is subject to change without notice.

#### Edition 2003-06-18

Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany

© Infineon Technologies AG 2003.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| Table o                                                                     | of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page                    |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 1<br>1.1<br>1.2<br>1.3<br>1.4                                               | Overview Features Typical Applicationsh Description Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7<br>7<br>8             |

| 2                                                                           | Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10                      |

| <b>3</b><br>3.1                                                             | Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                         |

| <b>4</b><br>4.1<br>4.2<br>4.3                                               | Functional Description and Applications Information Introduction Design Supporting Tools Recommended Components                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27<br>28                |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11 | $\begin{array}{c} \textbf{Transmission} \\ \textbf{General} \\ \textbf{Two-Wire Impedance} \\ \textbf{Two-Wire to Four-Wire Gain} \\ \textbf{Four-Wire to Two-Wire Gain} \\ \textbf{Four-Wire to Four-Wire Gain} \\ \textbf{Hybrid Function} \\ \textbf{Longitudinal Impedance} \\ \textbf{Capacitors $C_{\text{TC}}$ and $C_{\text{RC}}$ (Optional)} \\ \textbf{AC - DC Separation Capacitor, $C_{\text{HP}}$} \\ \textbf{Capacitor $C_{\text{LP}}$} \\ \textbf{Adaptive Overhead Voltage, AOV} \\ \textbf{Metering Applications} \\ \end{array}$ | 32 33 34 34 35 36 36 37 |

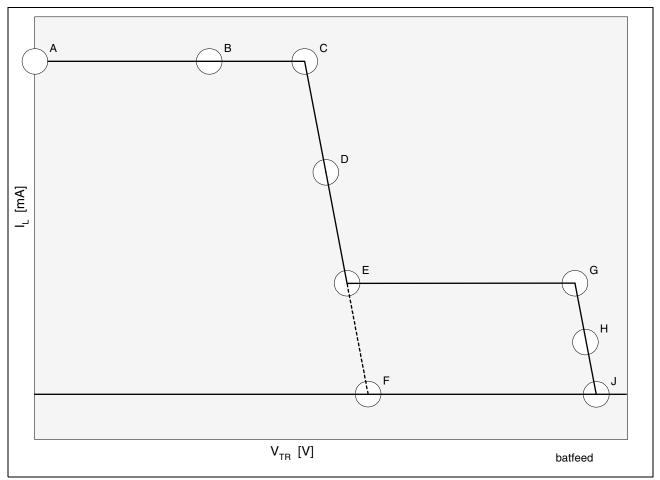

| 6<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.5.1<br>6.5.2                      | $\begin{array}{c} \textbf{Battery Feed and Automatic Battery Switching} \\ \textbf{Constant Current Feed Region} \\ \textbf{Resistive Feed Region} \\ \textbf{On-Hook Region} \\ \textbf{Optimizing $V_{\text{TB}}$} \\ \textbf{Silent Polarity Reversal} \\ \textbf{Polarity Reversal Time} \\ \textbf{Polarity Reversal Setup Time} \\ \end{array}$                                                                                                                                                                                              | 40<br>41<br>41<br>43    |

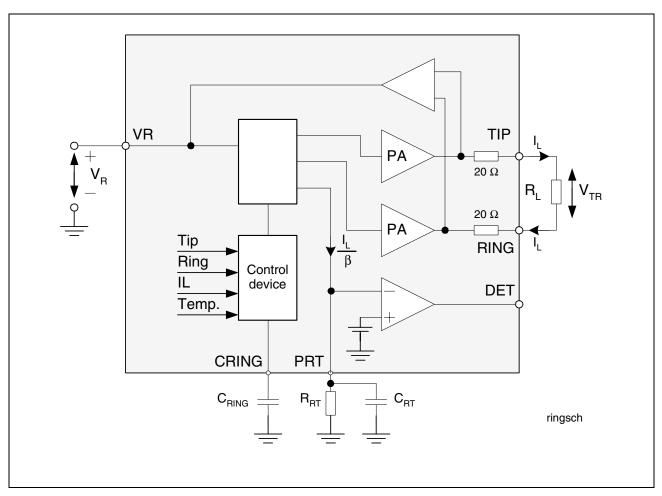

| <b>7</b><br>7.1<br>7.2<br>7.2.1                                             | Ringing Voltage Calculation of the Input Signal Calculation of the Ring-Trip Threshold Nominal Ring-Trip Current                                                                                                                                                                                                                                                                                                                                                                                                                                   | 49<br>49                |

| 8                                                                           | Maximum Loop Length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52                      |

| Table of                                             | Contents                                                                                                                                                                                                                                                                                                                                                                                                                | Page                       |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 8.1<br>8.2                                           | Ringing Voltage, Waveform and Number of RENs                                                                                                                                                                                                                                                                                                                                                                            |                            |

| 9<br>9.1<br>9.1.1<br>9.1.2<br>9.1.3                  | Power Dissipation Considerations Thermal Design Considerations Ringing Power Dissipation On-Hook Ringing Power Dissipation Off-Hook Off-Hook Power Dissipation                                                                                                                                                                                                                                                          | 55<br>55<br>57             |

| 10<br>10.1<br>10.2<br>10.3<br>10.4                   | Loop Monitoring Functions  Detector Output (DET)  Loop Current Detector  Ground Key Detector, Loop Ground Fault Detector  Loop Voltage Measurement                                                                                                                                                                                                                                                                      | 59<br>59<br>59             |

| 11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7 | Control Inputs  Open Circuit (C3, C2, C1 = 0, 0, 0)  Ringing (C3, C2, C1 = 0, 0, 1)  Active (C3, C2, C1 = 0, 1, 0)  Active, Loop Voltage Measurement (C3, C2, C1 = 0, 1, 1)  TIPX Open (C3, C2, C1 = 1, 0, 0)  Active, Ground Key and Loop Ground Fault (C3, C2, C1 = 1, 0, 1)  Active Reversal, Loop Current Detector (C3, C2, C1 = 1, 1, 0)  Active Reversal, Ground Key and Loop Ground Fault (C3, C2, C1 = 1, 1, 0) | 61<br>61<br>61<br>61<br>61 |

| <b>12</b><br>12.1<br>12.2<br>12.3                    | Overtemperature and Overvoltage Protection  Analog Temperature Guard                                                                                                                                                                                                                                                                                                                                                    | 63<br>63                   |

| 13                                                   | Power-Up Sequence                                                                                                                                                                                                                                                                                                                                                                                                       | 64                         |

| 14                                                   | Printed Circuit Board Layout                                                                                                                                                                                                                                                                                                                                                                                            | 64                         |

| <b>15</b><br>15.1<br>15.2                            | Package Outlines 28-Pin SOIC Package 32-pin MLP Package                                                                                                                                                                                                                                                                                                                                                                 | 65                         |

Data Sheet 4 DS1, 2003-06-18

| List of Figure | es F                                                                               | Page |

|----------------|------------------------------------------------------------------------------------|------|

| Figure 1       | Block Diagram                                                                      | 9    |

| Figure 2       | Pin Configuration 28L-SOIC (top view) and 32L-MLP (top view)                       |      |

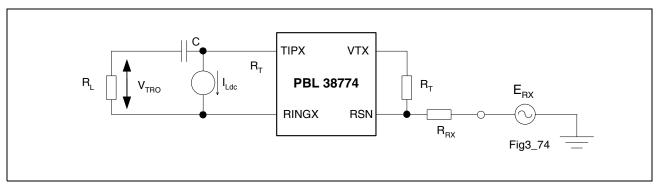

| Figure 3       | Overload Level, $V_{TRO}$ , Two-Wire Port                                          | . 25 |

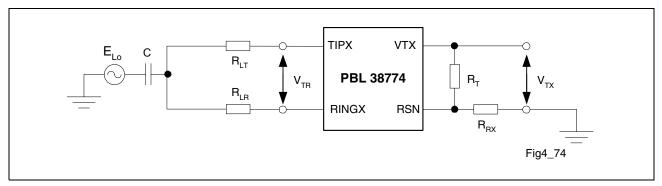

| Figure 4       | Longitudinal to Metallic, $B_{LME}$ and Longitudinal to Four-Wire,                 |      |

|                | $B_{LFE}$ Balance                                                                  | . 25 |

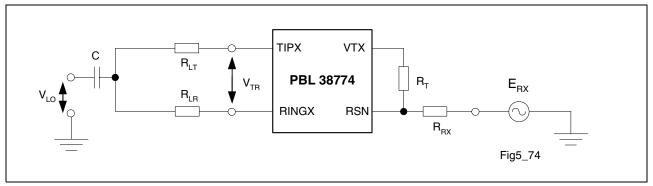

| Figure 5       | Metallic to Longitudinal, $B_{\mathrm{MLE}}$ and Four-Wire to Longitudinal Balance | ,    |

|                | $B_{\sf FLE}$                                                                      | . 25 |

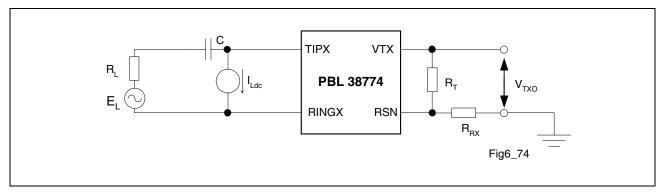

| Figure 6       | Overload Level, $V_{TXO}$ , Four-Wire Transmit Port                                | . 26 |

| Figure 7       | Frequency Response, Insertion Loss, Gain Tracking                                  | . 26 |

| Figure 8       | TIP Open Voltage                                                                   | . 26 |

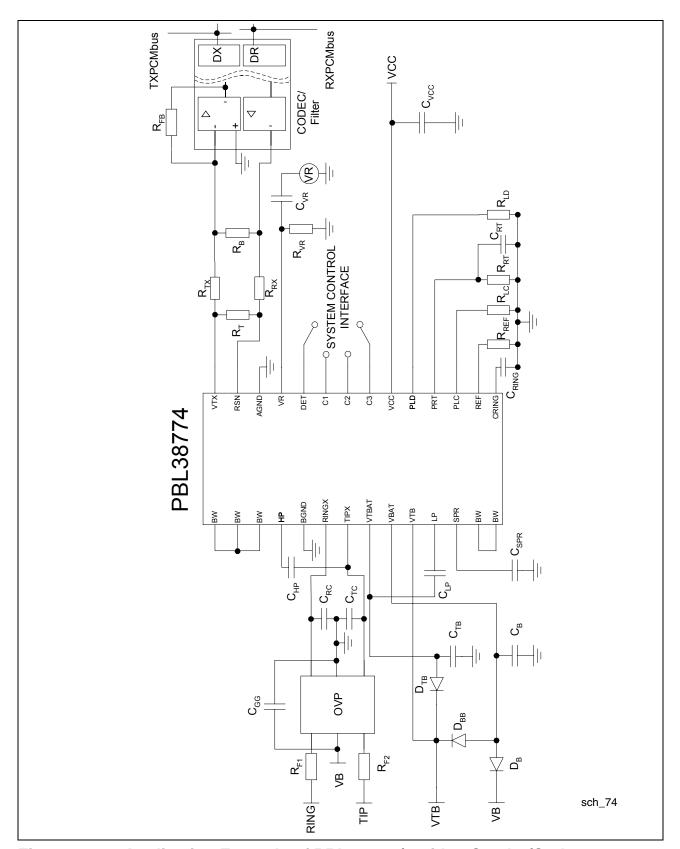

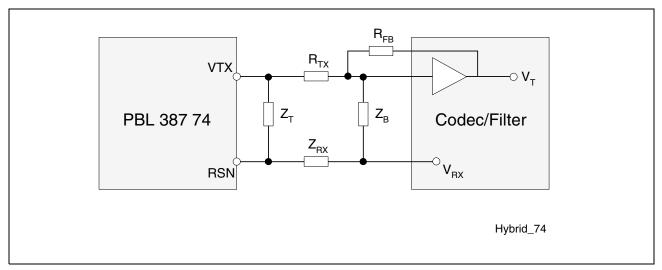

| Figure 9       | Application Example of PBL 38774/1 with a Combo/Codec                              |      |

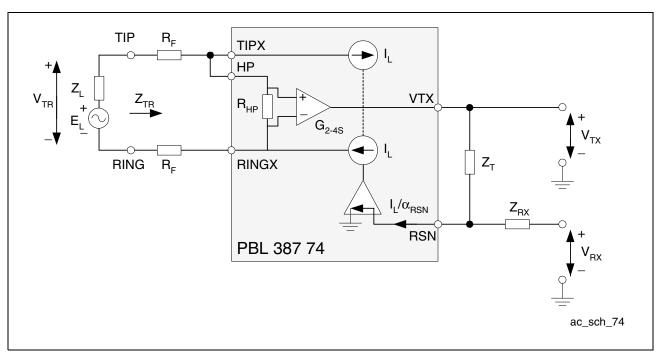

| Figure 10      | Simplified AC Model of PBL 38774/1                                                 |      |

| Figure 11      | Hybrid Function                                                                    | . 35 |

| Figure 12      | The AOV Function                                                                   | . 38 |

| Figure 13      | Battery Feed Characteristics                                                       | . 42 |

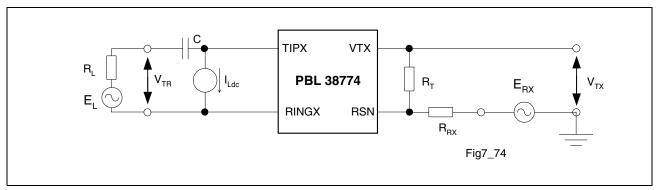

| Figure 14      | Ring Loop Schematic                                                                | . 45 |

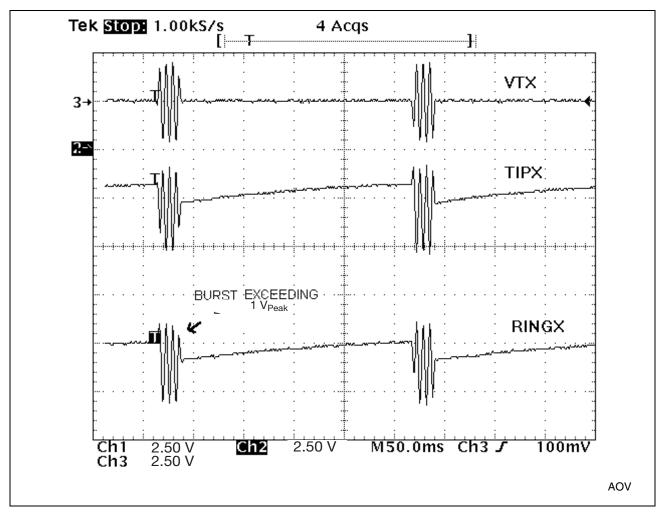

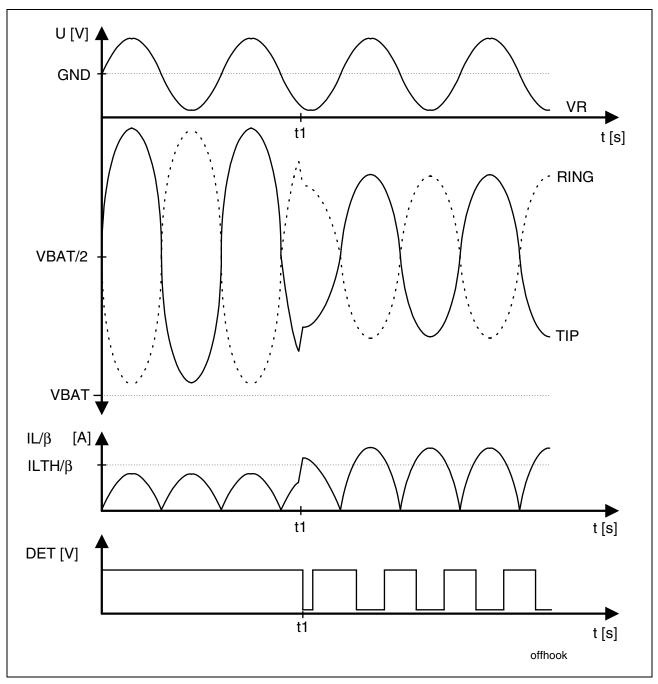

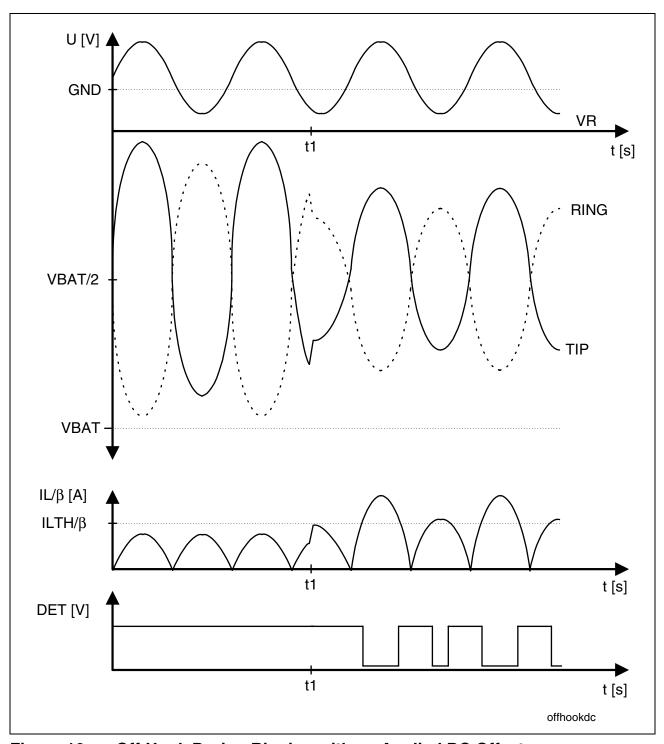

| Figure 15      | Off-Hook During Ringing                                                            |      |

| Figure 16      | Off-Hook During Ringing with an Applied DC Offset                                  |      |

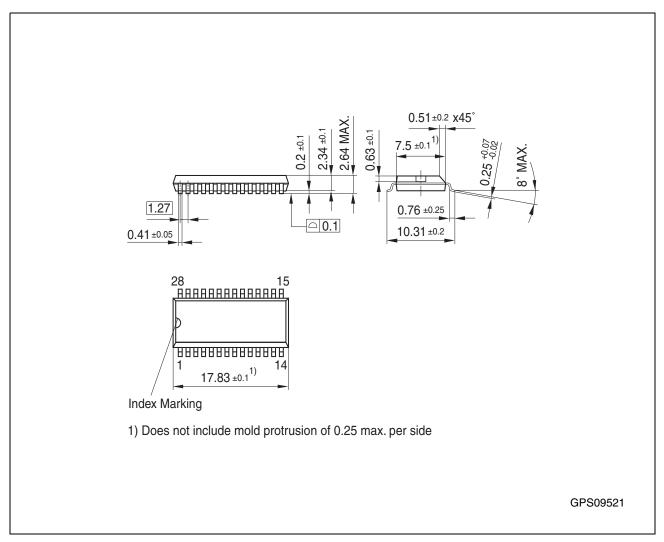

| Figure 17      | P-DSO-28-20 (28-Pin SOIC)                                                          |      |

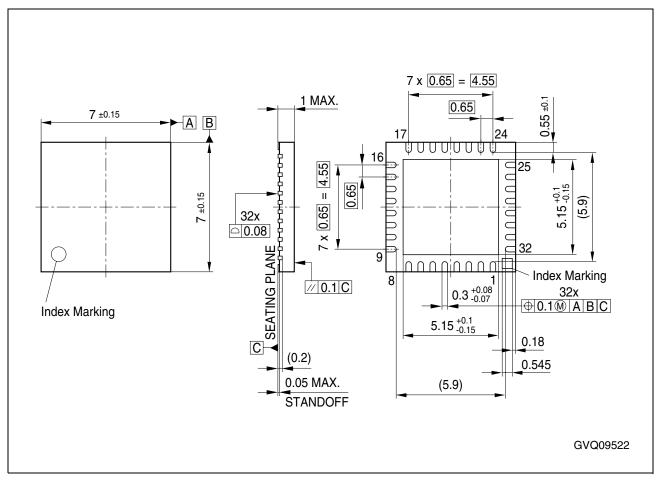

| Figure 18      | P-VQFN-32-6 (32-Pin MLP)                                                           | . 66 |

| s                                                 | Page                                                                                                                                                                                                                                                       |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Definition and Functions                      | 10                                                                                                                                                                                                                                                         |

| SLIC Operating States                             | 13                                                                                                                                                                                                                                                         |

| Absolute Maximum Ratings                          | 14                                                                                                                                                                                                                                                         |

| Operating Range                                   | 16                                                                                                                                                                                                                                                         |

| Characteristics                                   | 17                                                                                                                                                                                                                                                         |

| Functional Description                            | 27                                                                                                                                                                                                                                                         |

| Resistors (values according to IEC-63 E96 series) | 30                                                                                                                                                                                                                                                         |

| Capacitors (values according to IEC-63 E6 series) | 30                                                                                                                                                                                                                                                         |

| Optional Capacitors                               | 31                                                                                                                                                                                                                                                         |

| Diodes                                            | 31                                                                                                                                                                                                                                                         |

|                                                   | Pin Definition and Functions SLIC Operating States Absolute Maximum Ratings Operating Range Characteristics Functional Description Resistors (values according to IEC-63 E96 series) Capacitors (values according to IEC-63 E6 series) Optional Capacitors |

Data Sheet 6 DS1, 2003-06-18

# Ringing FlexiSLIC Subscriber Line Interface Circuit

PBL 38774/1

#### Version 2.0

#### 1 Overview

#### 1.1 Features

- On-chip ringing generation

- Balanced, up to 81 VPeak

- Any waveform

- 5 REN ringing load

- Automatic gain control of ring signal (AGC-R)

- Short circuit safe

- Low on-hook power consumption in Active (65 mW @  $V_{\rm BAT}$  = -80 V)

- Automatic current controlled battery switching between on-hook battery ( $V_{\rm BAT}$ ) and talk battery ( $V_{\rm TBAT}$ )

- Pulse metering and on-hook transmission

- UL-1950 and MTU compliant on-hook line voltage

- 3.3 V compatible logic interface

- Programmable Ring-Trip level

- Silent or fast polarity reversal

# P-DSO-28-20

# 1.2 Typical Applicationsh

- Integrated Access Device (IAD)

- Residential gateways

- Voice over DSL (VoDSL)

- Voice over IP (VoIP)

- Terminal adapters (CPE)

- ISDN terminal adapters

- Routers

- Cable modems

- Other Shortloop applications

| Туре           | Package     |

|----------------|-------------|

| PBL 38774/1 SO | P-DSO-28-20 |

| PBL 38774/1 ML | P-VQFN-32-6 |

Data Sheet 7 DS1, 2003-06-18

Overview

# 1.3 Description

The ringing FlexiSLIC PBL 38774/1 Subscriber Line Interface Circuit (SLIC) is a 90 V bipolar integrated circuit for use in short loop applications. The PBL 38774/1 SLIC has been optimized for low power consumption, low total line interface cost and for a high degree of flexibility in various applications.

The PBL 38774/1 SLIC supplies a balanced, sinewave, square or trapezoidal ringing signal of up to 81 VPeak (85 V DC supply) to the subscriber line across a load of up to 5 REN. The PBL 38774/1 supplies programmable constant current to the subscriber loop, sourced from the talk battery. The On-Hook line voltage of 43 V to 56 V is derived from the battery. All battery switching is internal to the device and is automatic. To further reduce power consumption the automatic gain control for the ring signal (AGC-R) keeps the level always adjusted to the maximum, that can be sourced from the available battery.

The SLIC incorporates loop current, ground key and ring-trip detection functions. The PBL 38774/1 is compatible with loop start and ground start signalling. Two- to four-wire and four- to two-wire voice frequency (vf) signal conversion is accomplished by the SLIC in conjunction with a standard codec. The line terminating impedance and balance impedance is programmable and may be complex or real for worldwide compliance.

Longitudinal balance specifications and other device characteristics are in compliance with Telcordia (Bellcore) and ITU-T requirements.

Tip and ring voltages are UL-1950 compliant; i.e. no two-wire line voltage exceeds 56 V. The PBL 38774/1 SLIC is packaged in a surface mount 28-pin SOIC or 32-pin MLP (32-pin VQFN) package.

Data Sheet 8 DS1, 2003-06-18

**Overview**

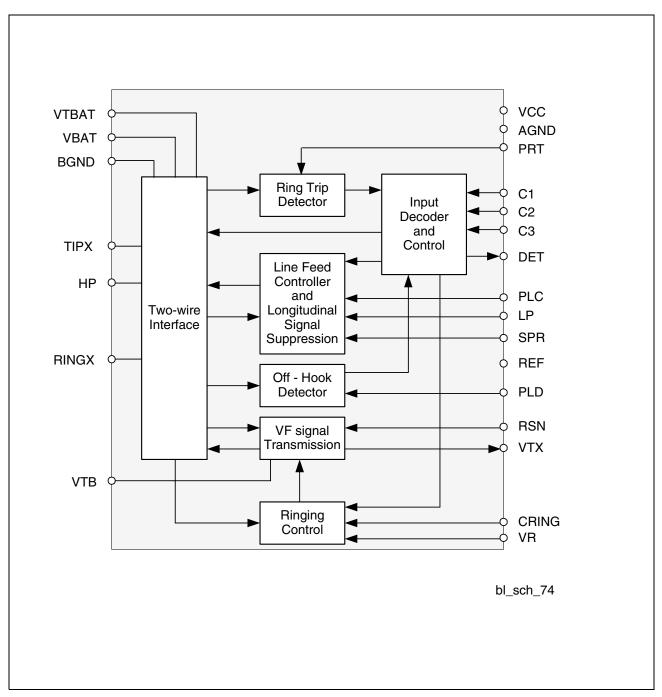

# 1.4 Block Diagram

Figure 1 Block Diagram

Data Sheet 9 DS1, 2003-06-18

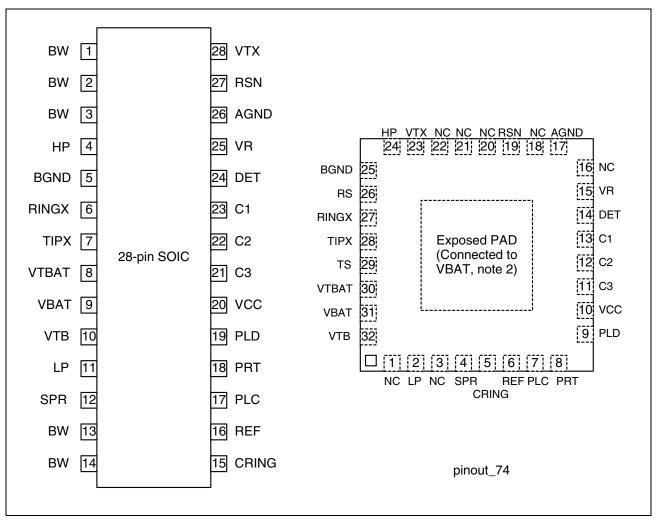

Figure 2 Pin Configuration 28L-SOIC (top view) and 32L-MLP (top view).

Table 1 Pin Definition and Functions

| SOIC<br>Pin No. | MLP<br>Pin No. | Name  | I/O | Function                                                                                                  |

|-----------------|----------------|-------|-----|-----------------------------------------------------------------------------------------------------------|

| 1,2,3,13,14     | -              | BW    | -   | Batwing <sup>1)</sup>                                                                                     |

| 4               | 24             | HP    | 1   | High Pass AC/DC separation capacitor $C_{\rm HP}$ connects between this pin and TIPX.                     |

| 5               | 25             | BGND  | I   | Battery Ground. Shall be tied together with AGND.                                                         |

| 6               | 27             | RINGX | Ο   | The RINGX pin connects to the ring lead of the two-wire interface via over voltage protection components. |

Table 1

Pin Definition and Functions (cont'd)

| SOIC<br>Pin No. | MLP<br>Pin No. | Name  | I/O | Function                                                                                                                                                                                  |  |  |  |

|-----------------|----------------|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7               | 28             | TIPX  | 0   | The TIPX pin connects to the tip lead of the two-wire interface via over voltage protection components.                                                                                   |  |  |  |

| 8               | 30             | VTBAT | I   | Talk Battery. The DC loop current is supplied to TIPX and RINGX from this battery voltage Negative with respect to BGND.                                                                  |  |  |  |

| 9               | 31             | VBAT  | I   | On-hook and Ringing Battery supply voltage. Negative with respect to BGND.                                                                                                                |  |  |  |

| 10              | 32             | VTB   | I   | Internal SLIC bias voltage. Connected to the talk battery supply. Refer to the application diagram in Figure 9. May be connected to any voltage between -32 V and -10 V.                  |  |  |  |

| 11              | 2              | LP    | I   | Low Pass saturation guard filter capacitor $C_{\rm LP}$ connects between this pin and VTBAT to filter out noise and improve $PSRR$ .                                                      |  |  |  |

| 12              | 4              | SPR   | I   | Silent Polarity Reversal. The capacitor $C_{\rm SPR}$ connects between this pin and AGND. Required when soft polarity reveral is necesary.                                                |  |  |  |

| 15              | 5              | CRING | I   | The capacitor $C_{\rm RING}$ connects between this pin and AGND. Required for the ring loop.                                                                                              |  |  |  |

| 16              | 6              | REF   | I   | A 15 k $\Omega$ resistor connected between this pin and AGND sets an internal SLIC reference current. The value must not be changed.                                                      |  |  |  |

| 17              | 7              | PLC   | I   | Programmable Line Current. The constant current DC feed is programmed by a resistor $R_{LC}$ , connected from this pin to AGND.                                                           |  |  |  |

| 18              | 8              | PRT   | 0   | Programmable Ring-trip Resistor, $R_{\rm RT}$ , connected between this pin and AGND. The capacitor, $C_{\rm RT}$ , together with resistor, $R_{\rm RT}$ , filters the ring-trip detector. |  |  |  |

| 19              | 9              | PLD   | 0   | Programmable Loop detector threshold. The loop detection threshold is set by a resistor, $R_{\rm LD}$ , between this pin and AGND.                                                        |  |  |  |

| 20              | 10             | VCC   | I   | +5 V power supply.                                                                                                                                                                        |  |  |  |

**Table 1 Pin Definition and Functions** (cont'd)

| SOIC<br>Pin No. | MLP<br>Pin No.                   | Name | I/O | Function                                                                                                                                                                                                                                    |

|-----------------|----------------------------------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21              | 11                               | C3   | I   | C1, C2, C3 are digital inputs, which control                                                                                                                                                                                                |

| 22              | 12                               | C2   | I   | the SLIC operating states. Refer to <b>Table 2</b>                                                                                                                                                                                          |

| 23              | 13                               | C1   | I   | for details.                                                                                                                                                                                                                                |

| 24              | 14                               | DET  | О   | Detector output. Active low when indicating loop or ring-trip detection, active high when indicating ground key detection.                                                                                                                  |

| 25              | 15                               | VR   | I   | Low voltage ring signal input.                                                                                                                                                                                                              |

| 26              | 17                               | AGND | I   | Analog Ground, shall be tied to BGND.                                                                                                                                                                                                       |

| 27              | 19                               | RSN  | I   | Receive Summing Node. 400 times the current flowing out of this pin equals the metallic (transversal) current flowing from RINGX to TIPX. Programming networks for two-wire impedance and receive gain connect to the receive summing node. |

| 28              | 23                               | VTX  | 0   | Transmit vf output. The AC voltage difference between TIPX and RINGX, the AC metallic voltage, is reproduced at VTX with a gain of 0.5. The two-wire impedance programming network connects between VTX and RSN.                            |

| -               | 26                               | RS   | I   | RINGX Sense connects to RINGX with a short lead.                                                                                                                                                                                            |

| -               | 29                               | TS   | I   | TIPX Sense connects to TIPX with a short lead                                                                                                                                                                                               |

| -               | 1,3,16,18,<br>20,21,22,<br>26,29 | NC   | -   | Not Connected, must be left open.                                                                                                                                                                                                           |

<sup>1)</sup> A batwing is a package pin, which provides a low thermal resistance path to the silicon chip via the lead frame. By soldering the batwing pins to PCB copper foil the device can be efficiently cooled. Note that batwing pins are at the same voltage as the VBAT pin (substrate voltage).

<sup>2)</sup> Exposed pad should be connected to  $V_{\it BAT}$ , note that this is used for cooling the chip.

Table 2 SLIC Operating States

| State | C3 | C2 | C1 | SLIC Operating State            | Active Detector (DET Response)                                       |  |  |

|-------|----|----|----|---------------------------------|----------------------------------------------------------------------|--|--|

| 0     | 0  | 0  | 0  | Open circuit                    | No active detector (DET is set high)                                 |  |  |

| 1     | 0  | 0  | 1  | Ringing                         | Ring-trip detector (DET active low)                                  |  |  |

| 2     | 0  | 1  | 0  | Active                          | Loop current detector (DET active low)                               |  |  |

| 3     | 0  | 1  | 1  | Active                          | Loop voltage measurement (DET pulse train)                           |  |  |

| 4     | 1  | 0  | 0  | TIPX open circuit, RINGX active | Loop detector, RINGX current (DET active low)                        |  |  |

| 5     | 1  | 0  | 1  | Active                          | Ground key detector and loop ground fault detector (DET active high) |  |  |

| 6     | 1  | 1  | 0  | Active, reverse polarity        | Loop current detector (DET active low)                               |  |  |

| 7     | 1  | 1  | 1  | Active, reverse polarity        | Ground key detector and loop ground fault detector (DET active high) |  |  |

# 3 Electrical Characteristics

Table 3 Absolute Maximum Ratings

| Parameter                                                      | Symbol       |           | Value | s            | Unit | Note/<br>Test Condition                                       |

|----------------------------------------------------------------|--------------|-----------|-------|--------------|------|---------------------------------------------------------------|

|                                                                |              | min.      | typ.  | max.         |      |                                                               |

| Temperature, Humidity                                          | •            |           |       |              |      |                                                               |

| Storage temperature range                                      | $T_{Stg}$    | -55       | _     | +150         | °C   | _                                                             |

| Operating temperature range                                    | $T_{Amb}$    | -40       | _     | +110         | °C   | _                                                             |

| Operating junction temperature range <sup>1)</sup>             | $T_{J}$      | -40       | _     | +140         | °C   | _                                                             |

| Power Supply (-40 ° C ≤T <sub>Amb</sub>                        | , ≤+85 ° C)  | •         | •     | •            | 1    |                                                               |

| $\overline{V_{	ext{CC}}}$ with respect to AGND                 | $V_{\sf CC}$ | -0.4      | _     | 6.5          | V    | _                                                             |

| $\overline{V_{\mathrm{TB}}}$ with respect to AGND              | $V_{TB}$     | $V_{BAT}$ | _     | 0.4          | V    | _                                                             |

| $\overline{V_{\mathrm{TBAT}}}$ with respect to AGND/BGND       | $V_{TBAT}$   | $V_{BAT}$ | _     | 0.4          | V    | -                                                             |

| $\overline{V_{\mathrm{BAT}}}$ with respect to BGND, continuous | $V_{BAT}$    | -85       | _     | 0.4          | V    | _                                                             |

| Power Dissipation                                              |              | •         | •     | •            | 1    |                                                               |

| Continuous power dissipation                                   | $P_{D}$      | _         | _     | 1.5          | W    | <i>T</i> <sub>Amb</sub> ≤+85 ° C                              |

| Peak power dissipation                                         | $P_{PD}$     | _         | _     | 4            | W    | $T_{\rm Amb}$ = +85 °C,<br>t < 100 ms,<br>$t_{\rm Rep}$ > 1 s |

| Ground                                                         |              | •         | •     | •            | 1    |                                                               |

| Voltage between AGND and BGND                                  | $V_{G}$      | -5        | _     | $V_{\sf CC}$ | V    | _                                                             |

| Digital Inputs, Outputs (C1,                                   | C2, C3, D    | ET)       | •     | •            | 1    |                                                               |

| Input voltage                                                  | $V_{ID}$     | -0.4      | _     | $V_{\sf CC}$ | V    | _                                                             |

| Output voltage (DET not active)                                | $V_{OD}$     | -0.4      | _     | $V_{\sf CC}$ | V    | _                                                             |

| Output current (DET)                                           | $I_{OD}$     | _         | _     | 30           | mA   | _                                                             |

| Ring Voltage, Input $(V_{\rm R})$                              |              |           |       |              |      |                                                               |

| Input voltage                                                  | $V_{R}$      | -1.1      | _     | $V_{\sf CC}$ | V    | _                                                             |

Data Sheet 14 DS1, 2003-06-18

Table 3

Absolute Maximum Ratings (cont'd)

| Parameter                                                                                                         | Symbol                  | Values                |        |               | Unit                | Note/                                              |  |  |  |

|-------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------|--------|---------------|---------------------|----------------------------------------------------|--|--|--|

|                                                                                                                   |                         | min.                  | typ.   | max.          |                     | Test Condition                                     |  |  |  |

| TIPX and RINGX Terminals (-40 $^{\circ}$ C $\leq T_{\text{Amb}} \leq$ +85 $^{\circ}$ C, $V_{\text{BAT}} =$ -75 V) |                         |                       |        |               |                     |                                                    |  |  |  |

| TIPX or RINGX current                                                                                             | $I_{TIPX}, \ I_{RINGX}$ | -100                  | _      | 100           | mA                  | _                                                  |  |  |  |

| TIPX or RINGX voltage, continuous (referenced to AGND)                                                            | $V_{TA},V_{RA}$         | $V_{BAT}$             | _      | 2             | V                   | _                                                  |  |  |  |

| TIPX or RINGX <sup>2)</sup>                                                                                       | $V_{TA},V_{RA}$         | V <sub>BAT</sub> - 15 | _      | 5             | V                   | pulse < 10 ms,<br>$t_{\text{Rep}} > 10 \text{ s}$  |  |  |  |

| TIPX or RINGX <sup>2)</sup>                                                                                       | $V_{TA},V_{RA}$         | V <sub>BAT</sub> - 20 | _      | 10            | V                   | pulse < 1 $\mu$ s,<br>$t_{Rep}$ > 10 s             |  |  |  |

| TIP or RING <sup>2)3)</sup>                                                                                       | $V_{TA},V_{RA}$         | V <sub>BAT</sub> - 25 | _      | 15            | V                   | pulse < 250 ns,<br>$t_{\text{Rep}} > 10 \text{ s}$ |  |  |  |

| <b>TIPX and RINGX Terminals</b>                                                                                   | s (-40 ° C <i>≤I</i>    | ` <sub>Amb</sub> ≤+8  | 85 °C, | $V_{BAT} = -$ | 80 V) <sup>4)</sup> |                                                    |  |  |  |

| TIPX or RINGX current                                                                                             | $I_{TIPX}, \ I_{RINGX}$ | -100                  | _      | 100           | mA                  | _                                                  |  |  |  |

| TIPX or RINGX voltage, continuous (referenced to AGND)                                                            | $V_{TA},V_{RA}$         | $V_{BAT}$             | _      | 2             | V                   |                                                    |  |  |  |

| TIPX or RINGX <sup>2)</sup>                                                                                       | $V_{TA},V_{RA}$         | V <sub>BAT</sub> - 10 | _      | 5             | V                   | pulse < 10 ms,<br>$t_{\text{Rep}} > 10 \text{ s}$  |  |  |  |

| TIPX or RINGX <sup>2)</sup>                                                                                       | $V_{TA},V_{RA}$         | V <sub>BAT</sub> - 15 | _      | 10            | V                   | pulse < 1 $\mu$ s,<br>$t_{Rep}$ > 10 s             |  |  |  |

| TIP or RING <sup>2)3)</sup>                                                                                       | $V_{TA},V_{RA}$         | V <sub>BAT</sub> - 15 | _      | 15            | V                   | pulse < 250 ns, $t_{\text{Rep}} > 10 \text{ s}$    |  |  |  |

<sup>1)</sup> The circuit includes thermal protection. Operation above max. junction temperature may degrade device reliability.

Data Sheet 15 DS1, 2003-06-18

<sup>2)</sup> With the diodes  $D_B$  and  $D_{TB}$  included, see Figure 9.

<sup>3)</sup>  $R_{\rm F1}$  and  $R_{\rm F2}$  > 20  $\Omega$  is also required. Pulse is supplied to RING and TIP outside  $R_{\rm F1}$  and  $R_{\rm F2}$ .

<sup>4)</sup> If the same duration is needed as in VBat = -75 V add a diode to the HP pin to VBat (Anode to VBat, Catode to HP pin).

Attention: Stresses above the max. values listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit.

Table 4 Operating Range

| Parameter                                                         | Symbol    | Values |      |      | Unit | Note/          |

|-------------------------------------------------------------------|-----------|--------|------|------|------|----------------|

|                                                                   |           | min.   | typ. | max. |      | Test Condition |

| Ambient temperature                                               | $T_{Amb}$ | -40    | _    | +85  | °C   | _              |

| $\overline{V_{\mathrm{CC}}}$ with respect to AGND                 | $V_{CC}$  | 4.75   | _    | 5.25 | V    | _              |

| $\overline{V_{\mathrm{TB}}}$ with respect to A/BGND <sup>1)</sup> | $V_{TB}$  | -32    | _    | -10  | V    | _              |

| $V_{\mathrm{BAT}}$ with respect to BGND                           | $V_{BAT}$ | -80    | _    | _    | V    | _              |

<sup>1)</sup> The voltage of  $V_{\rm TB}$  sets the maximum line length, see Figure 13. The diode  $D_{\rm TB}$  is required, see Figure 9.

Note: In the operating range, the functions given in the circuit description are fulfilled.

Data Sheet 16 DS1, 2003-06-18

#### 3.1 Characterictics

The specification is made with following setup: -40 ° C  $\leq$   $T_{\rm Amb}$   $\leq$ +85 ° C,  $V_{\rm CC}$  = +5 V  $\pm$ 5%,  $V_{\rm TBAT}$  = -32 V to -10 V,  $V_{\rm BAT}$  = -80 V,  $Z_{\rm L}$  = 600  $\Omega$ ,  $V_{\rm R}$  = 0.81 Vpeak,  $R_{\rm LC}$  = 18.7 k $\Omega$ , ( $I_{\rm L}$  = 26.8 mA),  $R_{\rm LD}$  = 49.9 k $\Omega$ ,  $R_{\rm F1}$  =  $R_{\rm F2}$  = 0,  $R_{\rm Ref}$  = 15.0 k $\Omega$ ,  $R_{\rm RT}$  = 62.4 k $\Omega$ ,  $C_{\rm HP}$  = 33 nF,  $C_{\rm LP}$  = 0.47  $\mu$ F,  $R_{\rm T}$  = 120 k $\Omega$ ,  $R_{\rm RX}$  = 120 k $\Omega$ ,  $R_{\rm VR}$  = 200 k $\Omega$ ,  $C_{\rm VR}$  = 0.47  $\mu$ F; Current definition: current is positive if flowing into a pin unless stated otherwise.

Table 5 Characteristics

| Parameter                                                                              | Symbol               | Values |                      |      | Unit                        | Note/                                                                          |

|----------------------------------------------------------------------------------------|----------------------|--------|----------------------|------|-----------------------------|--------------------------------------------------------------------------------|

|                                                                                        |                      | min.   | typ.                 | max. |                             | Test Condition                                                                 |

| Two-Wire Port                                                                          |                      |        | <b>.</b>             | •    | •                           |                                                                                |

| Overload level <sup>1)</sup> , see Figure 3, Active                                    | $V_{TRO}$            | 1.0    | _                    | _    | VPeak                       | Off-Hook, $I_{LDC} \ge 10 \text{ mA},$ 1% THD                                  |

|                                                                                        |                      | 1.0    | -                    | _    | VPeak                       | On-Hook,<br>I <sub>LDC</sub> ≤5 mA                                             |

|                                                                                        |                      | _      | 0.7                  | -    | VPeak                       | Metering, $I_{\rm LDC} \geq$ 10 mA, $Z_{\rm LM} =$ 200 $\Omega$ , $f =$ 16 kHz |

| Input impedance <sup>2)</sup>                                                          | $Z_{TRX}$            | _      | Z <sub>T</sub> / 200 | _    | Ω                           | -                                                                              |

| Longitudinal impedance                                                                 | $Z_{LOT}, \ Z_{LOR}$ | _      | 20                   | 35   | Ω/wire                      | 0 < f < 100 Hz                                                                 |

| Longitudinal current limit                                                             | $I_{LOT}, \ I_{LOR}$ | 28     | _                    | _    | mA <sub>rms</sub> /<br>wire | Active                                                                         |

| Longitudinal to metallic balance (Active),(IEEE                                        | $B_{LM}$             | 58     | 70                   | _    | dB                          | 0.2 kHz <i>⊈</i> ≤ 1.0 kHz                                                     |

| standard 455-1985), $Z_{\text{TRX}} = 736 \ \Omega$                                    |                      | 54     | 70                   | _    | dB                          | 1.0 kHz < <i>f</i> < 3.4 kHz                                                   |

| Longitudinal to metallic balance (Active),                                             | $B_{LME}$            | 58     | 70                   | _    | dB                          | 0.2 kHz <i>⊈</i> ≤ 1.0 kHz                                                     |

| $B_{\text{LME}} = 20 \times \log(E_{\text{LO}}/V_{\text{TR}}),$<br>see <b>Figure 4</b> |                      | 54     | 70                   | _    | dB                          | 1.0 kHz < <i>f</i> < 3.4 kHz                                                   |

Data Sheet 17 DS1, 2003-06-18

Table 5Characteristics (cont'd)

| Parameter                                                                                                                                 | Symbol               | Values |      |      | Unit  | Note/                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------|------|------|-------|-------------------------------------------------------------|

|                                                                                                                                           |                      | min.   | typ. | max. | 1     | Test Condition                                              |

| Longitudinal to four-wire balance (Active),                                                                                               | $B_{LFE}$            | 58     | 76   | _    | dB    | 0.2 kHz <i>≤</i> ≤ 1.0 kHz                                  |

| $B_{\text{LFE}} = 20 \times \log(E_{\text{LO}}/V_{\text{TX}}),$<br>see <b>Figure 4</b>                                                    |                      | 54     | 76   | _    | dB    | 1.0 kHz < <i>f</i> < 3.4 kHz                                |

| Metallic to longitudinal balance (Active), $B_{\rm MLE} = 20 \times \log(V_{\rm TR}/V_{\rm LO}),$ $E_{\rm RX} = 0$ V, see <b>Figure 5</b> | $B_{MLE}$            | 40     | 58   | _    | dB    | 0.2 kHz < <i>f</i> < 3.4 kHz                                |

| Four-wire to longitudinal balance (Active), $B_{\rm FLE} = 20 \times \log(E_{\rm RX}/V_{\rm LO})$ , see <b>Figure 5</b>                   | $B_{FLE}$            | 40     | 58   | _    | dB    | 0.2 kHz < <i>f</i> < 3.4 kHz                                |

| Two-wire return loss <sup>3)</sup>                                                                                                        | r                    | 25     | _    | _    | dB    | 0.2 kHz < <i>f</i> < 0.5 kHz                                |

| $r = 20 \times \log \frac{ Z_{\text{TRX}} + Z_{\text{L}} }{ Z_{\text{TRX}} - Z_{\text{L}} }$                                              |                      | 27     | _    | _    | dB    | 0.5 kHz < <i>f</i> < 1.0 kHz                                |

|                                                                                                                                           |                      | 23     | _    | _    | dB    | 1.0 kHz < <i>f</i> < 3.4 kHz                                |

| TIPX idle voltage                                                                                                                         | $V_{TI}$             | _      | -0.9 | _    | V     | Active, $I_L = 0$                                           |

| RINGX idle voltage                                                                                                                        | $V_{RI}$             | _      | -51  | _    | V     | Active, $I_L = 0$                                           |

| Open loop voltage                                                                                                                         | $ V_{TR} $           | 43     | 50   | 56   | V     | Active, $I_L = 0$                                           |

| Four-Wire Transmit Por                                                                                                                    | t (V <sub>TX</sub> ) |        |      |      |       |                                                             |

| Overload level <sup>4)</sup> , see <b>Figure 6</b>                                                                                        | $V_{TXO}$            | 0.5    | -    | _    | VPeak | Off-Hook, $I_L \ge$ 10 mA, Load imp. > 20 k $\Omega$ 1% THD |

|                                                                                                                                           |                      | 0.5    | _    | _    | VPeak | On-Hook, $I_{L} \le$ 5 mA,<br>Load imp. > 20 k $\Omega$ ,   |

| Output offset voltage                                                                                                                     | $V_{TX}$             | -100   | _    | 100  | mV    | _                                                           |

| Output impedance                                                                                                                          | $Z_{TX}$             | _      | 5    | 20   | Ω     | 0.2 kHz < <i>f</i> < 3.4 kHz                                |

Table 5

Characteristics (cont'd)

| Parameter                                                                                                                   | Symbol           | Values |          |        | Unit  | Note/                        |

|-----------------------------------------------------------------------------------------------------------------------------|------------------|--------|----------|--------|-------|------------------------------|

|                                                                                                                             |                  | min.   | typ.     | max.   |       | Test Condition               |

| Four-Wire Receive Port                                                                                                      | (receive s       | ummin  | g node : | = RSN) | 1     |                              |

| RSN DC offset voltage                                                                                                       | $V_{RSNdc}$      | -25    | _        | 25     | mV    | $I_{RSN} = 0 \text{ mA}$     |

| RSN impedance                                                                                                               |                  | _      | 10       | 50     | Ω     | 0.2 kHz < <i>f</i> < 3.4 kHz |

| RSN current to metallic loop current $I_L$ gain, $\alpha_{RSN}$                                                             | $I_{RSN}$        | _      | 400      | _      | ratio | 0.3 kHz < <i>f</i> < 3.4 kHz |

| Frequency Response                                                                                                          |                  |        |          |        |       | •                            |

| Two-wire to four-wire, relative to 0 dBm,                                                                                   | G <sub>2-4</sub> | -0.15  | -        | 0.15   | dB    | 0.3 kHz < <i>f</i> < 3.4 kHz |

| 1.0 kHz, $E_{RX} = 0$ V, see Figure 7                                                                                       |                  | -0.5   | -0.1     | 0.1    | dB    | f = 8 kHz, 12 kHz,<br>16 kHz |

| Four-wire to two-wire, relative to 0 dBm,                                                                                   | G <sub>4-2</sub> | -0.15  | _        | 0.15   | dB    | 0.3 kHz < <i>f</i> < 3.4 kHz |

| 1.0 kHz, $E_{LO} = 0 \text{ V}$ , see                                                                                       |                  | -1.0   | -0.2     | 0      | dB    | f = 8 kHz, 12 kHz            |

| Figure 7                                                                                                                    |                  | -1.0   | -0.3     | 0      | dB    | f = 16 kHz                   |

| Four-wire to four-wire, relative to 0 dBm, 1.0 kHz, $E_{LO} = 0$ V, see Figure 7                                            | G <sub>4-4</sub> | -0.15  | _        | 0.15   | dB    | 0.3 kHz < <i>f</i> < 3.4 kHz |

| Insertion Loss                                                                                                              |                  |        |          |        |       |                              |

| Two-wire to four-wire <sup>5)</sup> ,<br>$G_{2-4} = 20 \times \log(V_{TX}/V_{TR})$ ,<br>$E_{RX} = 0$ V, see <b>Figure 7</b> | G <sub>2-4</sub> | -6.22  | -6.02    | -5.82  | dB    | 0 dBm, 1.0 kHz               |

| Four-wire to two-wire <sup>5)6)</sup> ,<br>$G_{4-2} = 20 \times log(V_{TR}/V_{RX})$ ,<br>$E_L = 0$ V, see <b>Figure 7</b>   | G <sub>4-2</sub> | -0.2   | _        | 0.2    | dB    | 0 dBm, 1.0 kHz               |

| Gain Tracking                                                                                                               |                  |        |          |        |       |                              |

| Two-wire to four-wire <sup>7)</sup> , $R_{LDC} \leq k\Omega$ , Ref.                                                         |                  | -0.1   | _        | 0.1    | dB    | -40 dBm to<br>+3 dBm         |

| -10 dBm, 1.0 kHz, see Figure 7                                                                                              |                  | -0.2   | _        | 0.2    | dB    | -55 dBm to<br>-40 dBm        |

Data Sheet 19 DS1, 2003-06-18

Table 5Characteristics (cont'd)

| Parameter                                                                     | Symbol              |             | Values      |                         | Unit  | Note/                                                              |

|-------------------------------------------------------------------------------|---------------------|-------------|-------------|-------------------------|-------|--------------------------------------------------------------------|

|                                                                               |                     | min.        | typ.        | max.                    |       | Test Condition                                                     |

| Four-wire to two-wire <sup>7)</sup> , $R_{LDC} \leq 2 \text{ k}\Omega$ , Ref. |                     | -0.1        | _           | 0.1                     | dB    | -40 dBm to<br>+3 dBm                                               |

| -10 dBm, 1.0 kHz, see Figure 7                                                |                     | -0.2        | _           | 0.2                     | dB    | -55 dBm to<br>-40 dBm                                              |

| Noise                                                                         | 1                   |             |             | _                       | 1     |                                                                    |

| Idle channel noise at two-wire port <sup>8)</sup> (TIPX-                      |                     | _           | 7           | 12                      | dBrnC | C-message weighting                                                |

| RINGX)                                                                        |                     | _           | -83         | -78                     | dBmp  | Psophometrical weighting                                           |

| Harmonic Distortion                                                           |                     |             |             |                         |       |                                                                    |

| Two-wire to four-wire, see Figure 7                                           |                     | _           | _           | -50                     | dB    | 0.3 kHz < <i>f</i> < 3.4 kHz                                       |

|                                                                               |                     |             |             |                         |       | 0 dBm, 1.0 kHz<br>test signal                                      |

| Four-wire to two-wire                                                         |                     | _           | _           | -50                     | dB    | 0.3 kHz < <i>f</i> < 3.4 kHz                                       |

|                                                                               |                     |             |             |                         |       | 0 dBm, 1.0 kHz<br>test signal                                      |

| Battery Feed Character                                                        | istics              |             |             | _                       | 1     |                                                                    |

| Constant loop current                                                         | I <sub>LConst</sub> | $I_{LProg}$ | $I_{LProg}$ | $I.08 \times I_{LProg}$ | mA    | 18 mA < I <sub>LProg</sub> < 30 mA                                 |

|                                                                               |                     |             |             |                         |       | $R_{\rm LC} = \frac{500}{I_{\rm LProg}}$                           |

|                                                                               |                     |             |             |                         |       | $-\frac{10.4 \times \ln(32 \times I_{LProg})}{I_{LProg}}$          |

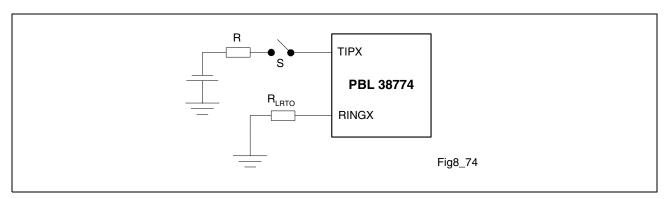

| Tip Open Circuit, (See                                                        | igure 8)            |             |             |                         |       | •                                                                  |

| Tip open circuit TIPX current                                                 | I <sub>Leak</sub>   |             | -100        |                         | μΑ    | S = Closed<br>$R_L = 600 \Omega$                                   |

| Tip open circuit RINGX current                                                | $I_{LRTO}$          |             | $I_{L}$     |                         | mA    | $R_{\text{LRTO}} = 0$<br>$V_{\text{BAT}} = -80 \text{ V}$          |

|                                                                               |                     |             | 19          |                         | mA    | $R_{\mathrm{LRTO}}$ = 2,5 k $\Omega$<br>$V_{\mathrm{BAT}}$ = -80 V |

Table 5Characteristics (cont'd)

| Parameter                                           | Symbol           |                      | Values     |                        | Unit              | Note/                                                                                     |

|-----------------------------------------------------|------------------|----------------------|------------|------------------------|-------------------|-------------------------------------------------------------------------------------------|

|                                                     |                  | min.                 | typ.       | max.                   |                   | Test Condition                                                                            |

| Tip open circuit<br>RINGX Voltage                   | $V_{RTO}$        |                      | -48.5      |                        | V                 | I <sub>LRTO</sub> < 23 mA                                                                 |

| Tip Voltage<br>(ground start)                       |                  | -4                   | 0          |                        | V                 | Active, S = Open<br>Ring lead via<br>150 Ω to GND                                         |

| Tip Voltage<br>(ground start)                       |                  | -6                   | 0          |                        | V                 | Active, Tip lead to -48 V via 7 k $\Omega$ (S = Closed) Ring lead via 150 $\Omega$ to GND |

| Open circuit loop current                           |                  | -100                 | 0          | 100                    | μΑ                | $R_{L} = 0 \ \Omega$                                                                      |

| <b>Loop Current Detector</b>                        |                  |                      |            |                        |                   |                                                                                           |

| Programmable threshold, $I_{LTh} = 500/R_{LD}$      | $I_{LTh}$        | $0.9 \times I_{LTh}$ | $I_{LTh}$  | $I.1 \times I_{LTh}$   | mA                | I <sub>LTh</sub> > 10 mA                                                                  |

| Ringing                                             |                  | •                    | •          | •                      | •                 |                                                                                           |

| VR input impedance                                  |                  | 50                   | _          | _                      | ΜΩ                | _                                                                                         |

| Input bias current VR                               |                  | _                    | 7          | _                      | nA                | _                                                                                         |

| VR input voltage                                    | VR <sub>PK</sub> | _                    | 0.81       | _                      | V <sub>Peak</sub> | Ref to AGND                                                                               |

| Ring injection suppression                          |                  | _                    | 100        | _                      | dB                | Active, $R_{\rm L} = 600 \ \Omega$                                                        |

| Ringing gain <sup>9)</sup>                          |                  | _                    | 94         | _                      | ratio             | $V_{R}$ to two-wire                                                                       |

| Ringing voltage total distortion <sup>9)</sup>      |                  | _                    | 0.4        | 2                      | %                 | $R_{L} = 1.4 \text{ k}\Omega,$<br>$f_{VR} = 25 \text{ Hz}$                                |

| Voltage offset between TIPX and RINGX <sup>9)</sup> |                  | _                    | 0          | _                      | V                 |                                                                                           |

| Common mode voltage TIPX and RINGX                  |                  | -0.4                 | 0          | 0.4                    | V                 | Related to $V_{\rm BAT}/2 + 0.65$                                                         |

| Ring-Trip Detector                                  |                  |                      |            |                        |                   |                                                                                           |

| Ring-trip current threshold <sup>10)</sup>          | $I_{LRTh}$       | $I_{LRTh}$           | $I_{LRTh}$ | $I.12 \times I_{LRTh}$ | mA                | -                                                                                         |

Table 5Characteristics (cont'd)

| Parameter                                 | Symbol                | Values        |         |              | Unit | Note/                                                                                            |

|-------------------------------------------|-----------------------|---------------|---------|--------------|------|--------------------------------------------------------------------------------------------------|

|                                           |                       | min.          | typ.    | max.         |      | Test Condition                                                                                   |

| <b>Loop Voltage Measure</b>               | ment                  |               | •       | •            |      |                                                                                                  |

| Frequency                                 |                       | _             | f       | _            | Hz   | $f = 900 \times 10^3 / ( V_{TR}  + 1)$                                                           |

| <b>Ground Key Detector a</b>              | nd Loop (             | Ground        | Fault I | Detecto      |      |                                                                                                  |

| Ground key detector threshold             |                       | 9             | 15      | 19           | mA   | _                                                                                                |

| Digital Inputs (C1, C2, C                 | C3)                   | •             | 1       | -            | •    |                                                                                                  |

| Input low voltage                         | $V_{IL}$              | 0             | _       | 0.5          | V    | _                                                                                                |

| Input high voltage                        | $V_{IH}$              | 2.5           | _       | $V_{\sf CC}$ | V    | _                                                                                                |

| Input low current                         | $ I_{IL} $            | -200          | _       | _            | μΑ   | $V_{\rm IL} = 0.5 \ { m V}$                                                                      |

| Input high current                        | I <sub>IH</sub> I     | -100          | _       | _            | μΑ   | V <sub>IH</sub> = 2.5 V                                                                          |

| <b>Detector Output (DET)</b>              |                       |               |         |              |      |                                                                                                  |

| Output low voltage                        | $V_{OL}$              | _             | 0.1     | 0.6          | V    | $I_{OL} = 1 \text{ mA}$                                                                          |

| Internal pull-up resistor to $V_{\rm CC}$ |                       | _             | 10      | _            | kΩ   | _                                                                                                |

| Power Dissipation <sup>11)</sup> (V       | <sub>BAT</sub> -80 V, | $V_{BAT} = 0$ | -24 V)  | •            |      |                                                                                                  |

| Power Dissipation                         | $P_1$                 | _             | 16      | _            | mW   | Open circuit                                                                                     |

| Power Dissipation                         | $P_2$                 | _             | 65      | _            | mW   | Active,<br>Longitudinal<br>current 0 mA<br>$I_{\rm L}=0$ mA                                      |

| Power Dissipation                         | $P_3$                 | _             | 500     | _            | mW   | Active, $R_L = 300 \Omega$ (Off-hook)                                                            |

| Power Dissipation                         | $P_4$                 | _             | 290     | _            | mW   | Active, $R_L = 600 \Omega$ (Off-hook)                                                            |

| Power Dissipation                         | $P_5$                 | _             | 320     | _            | mW   | Ringing, $R_L = 7 \text{ k}\Omega$<br>(AC load $\approx$ 1REN), Sine wave, 20 Hz, max. amplitude |

Table 5Characteristics (cont'd)

| Parameter                                    | Symbol              | Values |       |      | Unit | Note/                                                |

|----------------------------------------------|---------------------|--------|-------|------|------|------------------------------------------------------|

|                                              |                     | min.   | typ.  | max. |      | Test Condition                                       |

| <b>Power Supply Curre</b>                    | $nts (V_{BAT} = -8$ | 0 V)   | 1     | •    |      |                                                      |

| $\overline{V_{\rm CC}}$ current              | $I_{\rm CC}$        | _      | 1.4   | _    | mA   | Open circuit                                         |

| $\overline{V_{TBAT}}$ current                | $I_{TBAT}$          | _      | 0     | _    | mA   | Open circuit                                         |

| $V_{TB}$ current                             | $I_{TB}$            | _      | -0.13 | _    | mA   | Open circuit                                         |

| $\overline{V_{BAT}}$ current                 | $I_{BAT}$           | _      | -0.07 | _    | mA   | Open circuit                                         |

| $\overline{V_{\rm CC}}$ current              | $I_{\rm CC}$        | _      | 2.4   | _    | mA   | Active, On-hook                                      |

| $\overline{V_{TBAT}}$ current                | $I_{TBAT}$          | _      | 0     | _    | mA   | Active, On-hook                                      |

| $\overline{V_{TB}}$ current                  | $I_{TB}$            | _      | -0.2  | _    | mA   | Active, On-hook                                      |

| $\overline{V_{BAT}}$ current                 | $I_{BAT}$           | _      | -0.6  | _    | mA   | Active, On-hook                                      |

| $V_{\rm CC}$ current                         | $I_{CC}$            | _      | 7.1   | _    | mA   | Ringing, On-hook,<br>No ring signal                  |

| $\overline{V_{TBAT}}$ current                | $I_{TBAT}$          | _      | 0     | _    | mA   | Ringing, On-hook,<br>No ring signal                  |

| $\overline{V_{TB}}$ current                  | $I_{TB}$            | _      | -1    | _    | mA   | Ringing, On-hook,<br>No ring signal                  |

| $\overline{V_{BAT}}$ current                 | $I_{BAT}$           | _      | -2.7  | _    | mA   | Ringing, On-hook,<br>No ring signal                  |

| Power Supply Reject                          | tion Ratios         | •      | 1     | •    | •    |                                                      |

| $\overline{V_{\rm CC}}$ to 2-wire port       |                     | 30     | 45    | _    | dB   | Active, $f = 1 \text{ kHz}$ , $V_n = 100 \text{ mV}$ |

| $\overline{V_{\rm CC}}$ to 4-wire port       |                     | 36     | 51    | _    | dB   | Active, $f = 1 \text{ kHz}$ , $V_n = 100 \text{ mV}$ |

| $V_{TB}$ to 2-wire port                      |                     | 28.5   | 60    | _    | dB   | Active, $f = 1 \text{ kHz}$ , $V_n = 100 \text{ mV}$ |

| V <sub>TB</sub> to 4-wire port               |                     | 34.5   | 66    | _    | dB   | Active, $f = 1 \text{ kHz}$ , $V_n = 100 \text{ mV}$ |

| V <sub>BAT</sub> to 2-wire port              |                     | 40     | 60    | _    | dB   | Active, $f = 1 \text{ kHz}$ , $V_n = 100 \text{ mV}$ |

| $\overline{V_{\mathrm{BAT}}}$ to 4-wire port |                     | 46     | 66    | _    | dB   | Active, $f = 1 \text{ kHz}$ , $V_n = 100 \text{ mV}$ |

#### Table 5 Characteristics (cont'd)

| Parameter                      | Symbol            | Values |      |      | Unit | Note/          |

|--------------------------------|-------------------|--------|------|------|------|----------------|

|                                |                   | min.   | typ. | max. |      | Test Condition |

| Temperature Guard              | <u> </u>          |        |      |      |      |                |

| Junction threshold temperature | $T_{JG}$          | _      | 155  | _    | °C   | _              |

| Thermal Resistance             |                   |        |      |      |      |                |

| Junction to pin                | $\Theta_{\sf JP}$ | _      | 22   | _    | °C/W | SOIC package   |

| Junction to ambient            | $\Theta_{\sf JA}$ | _      | 41.6 | _    | °C/W | SOIC package   |

| Junction to pin                | $\Theta_{\sf JP}$ | _      | 3    | _    | °C/W | MLP package    |

| Junction to ambient            | $\Theta_{\sf JA}$ | _      | 27   | _    | °C/W | MLP package    |

- 1) The overload level is automatically expanded to needed signal level, maximum 1.7 VPeak when the signal level is > 1.0 VPeak, and is specified at the two-wire port with the signal source at the four-wire receive port. For more information see **Chapter 5.11**.

- 2) The two-wire impedance is programmable by selection of external component values according to:

$Z_{\text{TRX}} = Z_{\text{T}}/(|\mathsf{G}_{2\text{-4S}} \times \alpha_{\text{RSN}}|)$  where:

$Z_{TRX}$  = impedance between the TIPX and RINGX terminals

$Z_T$  = programming network between the VTX and RSN terminals

$G_{2-4S}$  = transmit gain, nominally = 0.5