### CA3054

Dual Independent Differential Amp for Low Power Applications from DC to 120MHz

FN388 Rev.6.00 Jan 13, 2017

The CA3054 consists of two independent differential amplifiers with associated constant current transistors on a common monolithic substrate. The six NPN transistors which comprise the amplifiers are general purpose devices which exhibit low 1/f noise and a value of  $f_T$  in excess of 300MHz. These feature make the CA3054 useful from DC to 120MHz. Bias and load resistors have been omitted to provide maximum application flexibility.

The monolithic construction of the CA3054 provides close electrical and thermal matching of the amplifiers. This feature makes these devices particularly useful in dual channel applications where matched performance of the two channels is required.

# Ordering Information

| PART NUMBER<br>(BRAND)   | TEMP.<br>RANGE (°C) | PACKAGE                               | PKG.<br>DWG.# |

|--------------------------|---------------------|---------------------------------------|---------------|

| CA3054M96<br>(3054)      | 0 to 85             | 14 Ld SOIC<br>Tape and Reel           | M14.15        |

| CA3054MZ<br>(CA3054MZ)   | 0 to 85             | 14 Ld SOIC<br>(Pb-free)               | M14.15        |

| CA3054MZ96<br>(CA3054MZ) | 0 to 85             | 14 Ld SOIC Tape<br>and Reel (Pb-free) | M14.15        |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

### **Features**

- Two Differential Amplifiers on a Common Substrate

- · Independently Accessible Inputs and Outputs

- Maximum Input Offset Voltage.....±5mV

- Temperature Range................ 0°C to 85°C

- Pb-Free Plus Anneal Available (RoHS Compliant)

## **Applications**

- Dual Sense Amplifiers

- · Dual Schmitt Triggers

- Multifunction Combinations

- RF/Mixer/Oscillator; Converter/IF

- IF Amplifiers (Differential and/or Cascode)

- · Product Detectors

- · Doubly Balanced Modulators and Demodulators

- · Balanced Quadrature Detectors

- · Cascade Limiters

- · Synchronous Detectors

- Pairs of Balanced Mixers

- · Synthesizer Mixers

- Balanced (Push-Pull) Cascode Amplifiers

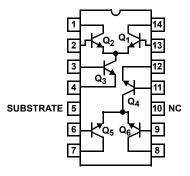

#### **Pinout**

CA3054 (SOIC) TOP VIEW

# **Absolute Maximum Ratings** $T_A = 25$ °C

| Collector-to-Emitter Voltage, V <sub>CEO</sub>            | 15V  |

|-----------------------------------------------------------|------|

| Collector-to-Base Voltage, V <sub>CBO</sub>               | 20V  |

| Collector-to-Substrate Voltage, V <sub>CIO</sub> (Note 1) | 20V  |

| Emitter-to-Base Voltage, V <sub>EBO</sub>                 | . 5V |

| Collector Current, IC                                     | 0mA  |

#### **Operating Conditions**

| Temperature Range. |  | 0°C to 85°C |

|--------------------|--|-------------|

|--------------------|--|-------------|

#### **Thermal Information**

| Thermal Resistance (Typical, Note 2)           | θ <sub>JA</sub> (°C/W) |

|------------------------------------------------|------------------------|

| SOIC Package                                   | 140                    |

| Maximum Junction Temperature (Die)             |                        |

| Maximum Junction Temperature (Plastic Package) | 150°C                  |

| Maximum Storage Temperature Range65            | 5°C to 150°C           |

| Maximum Lead Temperature (Soldering 10s)       | 300°C                  |

| (Lead Tips Only)                               |                        |

| Maximum Power Dissipation (Any One Transistor) | 300mW                  |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1. The collector of each transistor of the CA3054 is isolated from the substrate by an integral diode. The substrate must be connected to a voltage which is more negative than any collector voltage in order to maintain isolation between transistors and provide for normal transistor action. The substrate should be maintained at signal (AC) ground by means of a suitable grounding capacitor, to avoid undesired coupling between transistors.

- 2.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

### **Maximum Voltage Ratings**

The following chart gives the range of voltages which can be applied to the terminals listed vertically with respect to the terminals listed horizontally. For example, the voltage range of the vertical Terminal 2 with respect to Terminal 4 is +15V to -5V.

## Maximum Current Ratings

| (NOTE 4) TERM NO. | 13 | 14     | 1      | 2      | 3      | 4       | 6      | 7      | 8      | 9      | 11     | 12      | 5                      | (NOTE 4) TERM NO. | I <sub>IN</sub> mA | I <sub>OUT</sub> |

|-------------------|----|--------|--------|--------|--------|---------|--------|--------|--------|--------|--------|---------|------------------------|-------------------|--------------------|------------------|

| 13                |    | 0, -20 | Note 3 | +5, -5 | Note 3 | +15, -5 | Note 3  | Note 3                 | 13                | 5                  | 0.1              |

| 14                |    |        | Note 3 | Note 3 | Note 3 | +20, 0  | Note 3  | +20, 0                 | 14                | 50                 | 0.1              |

| 1                 |    |        |        | +20, 0 | Note 3 | +20, 0  | Note 3  | +20, 0                 | 1                 | 50                 | 0.1              |

| 2                 |    |        |        |        | Note 3 | +15, -5 | Note 3  | Note 3                 | 2                 | 5                  | 0.1              |

| 3                 |    |        |        |        |        | +1, -5  | Note 3  | Note 3                 | 3                 | 5                  | 0.1              |

| 4                 |    |        |        |        |        |         | Note 3  | Note 3                 | 4                 | 0.1                | 50               |

| 6                 |    |        |        |        |        |         |        | 0, -20 | Note 3 | +5, -5 | Note 3 | +15, -5 | Note 3                 | 6                 | 5                  | 0.1              |

| 7                 |    |        |        |        |        |         |        |        | Note 3 | Note 3 | Note 3 | Note 3  | +20, 0                 | 7                 | 50                 | 0.1              |

| 8                 |    |        |        |        |        |         |        |        |        | +20, 0 | Note 3 | Note 3  | +20, 0                 | 8                 | 50                 | 0.1              |

| 9                 |    |        |        |        |        |         |        |        |        |        | Note 3 | +15, -5 | Note 3                 | 9                 | 5                  | 0.1              |

| 11                |    |        |        |        |        |         |        |        |        |        |        | -1, -5  | Note 3                 | 11                | 5                  | 0.1              |

| 12                |    |        |        |        |        |         |        |        |        |        |        |         | Note 3                 | 12                | 0.1                | 50               |

| 5                 |    |        |        |        |        |         |        |        |        |        |        |         | Ref.<br>Sub-<br>strate |                   |                    | ,                |

#### NOTES:

- 3. Voltages are not normally applied between these terminals. Voltages appearing between these terminals will be safe if the specified limits between all other terminals are not exceeded.

- 4. Terminal No. 10 of CA3054 is not used.

## **Electrical Specifications** T<sub>A</sub> = 25°C

| PARAMETER                                                            | SYMBOL                                                                | TEST CONDITIONS                               | MIN | TYP             | MAX | UNIT  |  |  |  |  |

|----------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------|-----|-----------------|-----|-------|--|--|--|--|

| DC CHARACTERISTICS For Each Differential Amplifier                   |                                                                       |                                               |     |                 |     |       |  |  |  |  |

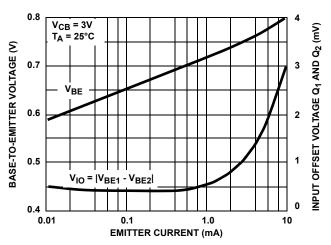

| Input Offset Voltage (Figure 8)                                      | V <sub>IO</sub>                                                       | $V_{CB} = 3V$ , $I_{E(Q3)} = I_{E(Q4)} = 2mA$ | -   | 0.45            | 5   | mV    |  |  |  |  |

| Input Offset Current (Figure 9)                                      | I <sub>IO</sub>                                                       | $V_{CB} = 3V, I_{E(Q3)} = I_{E(Q4)} = 2mA$    | -   | 0.3             | 2   | μΑ    |  |  |  |  |

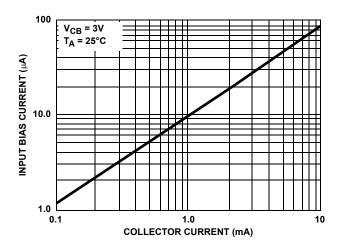

| Input Bias Current (Figure 5)                                        | lį                                                                    | $V_{CB} = 3V$ , $I_{E(Q3)} = I_{E(Q4)} = 2mA$ | -   | 10              | 24  | μΑ    |  |  |  |  |

| Quiescent Operating Current Ratio (Figure 5)                         | $\frac{I_{C(Q1)}}{I_{C(Q2)}} \text{ or } \frac{I_{C(Q5)}}{I_{C(Q6)}}$ | $V_{CB} = 3V$ , $I_{E(Q3)} = I_{E(Q4)} = 2mA$ | -   | 0.98 to<br>1.02 | -   | -     |  |  |  |  |

| Temperature Coefficient Magnitude of Input Offset Voltage (Figure 7) | <u>Δ</u> V <sub>IO</sub> ΔΤ                                           | $V_{CB} = 3V$ , $I_{E(Q3)} = I_{E(Q4)} = 2mA$ | -   | 1.1             | -   | μV/°C |  |  |  |  |

# **Electrical Specifications** $T_A = 25^{\circ}C$ (Continued)

| PARAMETER                                                                                 | SYMBOL                           | TEST C                                                               | TEST CONDITIONS                                      |          |                           | MAX   | UNIT  |

|-------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------|------------------------------------------------------|----------|---------------------------|-------|-------|

| FOR EACH TRANSISTOR                                                                       |                                  |                                                                      |                                                      |          |                           |       |       |

| DC Forward Base-to-Emitter Voltage                                                        | V <sub>BE</sub>                  | V <sub>CB</sub> = 3V                                                 | $I_C = 50\mu A$                                      | -        | 0.630                     | 0.700 | V     |

| (Figure 8)                                                                                |                                  |                                                                      | $I_C = 1mA$                                          | -        | 0.715                     | 0.800 | V     |

|                                                                                           |                                  |                                                                      | $I_C = 3mA$                                          | -        | 0.750                     | 0.850 | V     |

|                                                                                           |                                  |                                                                      | I <sub>C</sub> = 10mA                                | -        | 0.800                     | 0.900 | V     |

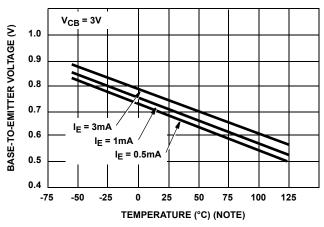

| Temperature Coefficient of Base-to-Emitter Voltage (Figure 6)                             | $\frac{\Delta V_{BE}}{\Delta T}$ | V <sub>CB</sub> = 3V, I <sub>C</sub> =                               | = 1mA                                                | -        | -1.9                      | -     | μV/°C |

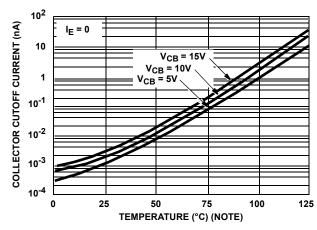

| Collector Cutoff Current (Figure 4)                                                       | I <sub>CBO</sub>                 | V <sub>CB</sub> = 10V, I <sub>E</sub>                                | = 0                                                  | -        | 0.002                     | 100   | nA    |

| Collector-to-Emitter Breakdown Voltage                                                    | V <sub>(BR)CEO</sub>             | $I_C = 1mA$ , $I_B =$                                                | 0                                                    | 15       | 24                        | -     | V     |

| Collector-to-Base Breakdown Voltage                                                       | V <sub>(BR)CBO</sub>             | $I_C = 10 \mu A, I_E =$                                              | = 0                                                  | 20       | 60                        | Ð     | V     |

| Collector-to-Substrate Breakdown<br>Voltage                                               | V <sub>(BR)CIO</sub>             | $I_C = 10\mu A, I_{CI}$                                              | = 0                                                  | 20       | 60                        | -     | V     |

| Emitter-to-Base Breakdown Voltage                                                         | V <sub>(BR)EBO</sub>             | I <sub>E</sub> = 10μA, I <sub>C</sub> =                              | = 0                                                  | 5        | 7                         | ī     | ٧     |

| DYNAMIC CHARACTERISTICS                                                                   |                                  |                                                                      |                                                      |          |                           |       |       |

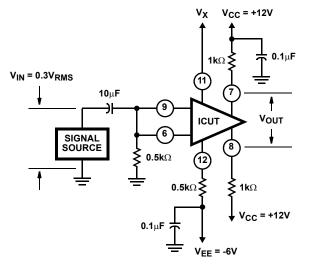

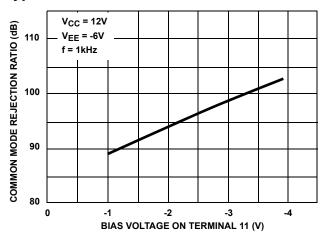

| Common Mode Rejection Ratio for each<br>Amplifier (Figures 1, 10)                         | CMRR                             | V <sub>CC</sub> = 12V, V <sub>E</sub><br>V <sub>X</sub> = -3.3V, f = |                                                      | -        | 100                       | -     | dB    |

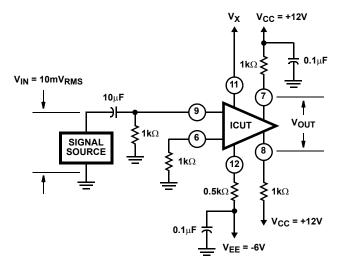

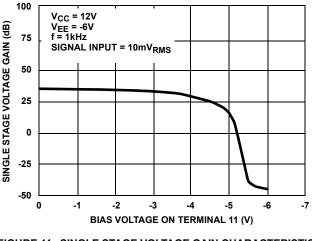

| AGC Range, One Stage (Figures 2, 11)                                                      | AGC                              | V <sub>CC</sub> = 12V, V <sub>E</sub><br>V <sub>X</sub> = -3.3V, f = |                                                      | -        | 75                        | -     | dB    |

| Voltage Gain, Single Stage Double-Ended<br>Output (Figures 2, 11)                         | А                                | V <sub>CC</sub> = 12V, V <sub>E</sub><br>V <sub>X</sub> = -3.3V, f = |                                                      | -        | 32                        | -     | dB    |

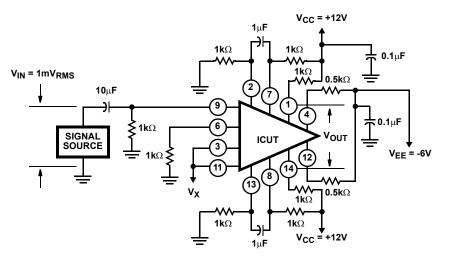

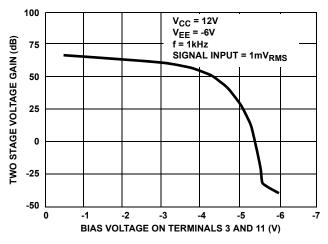

| AGC Range, Two Stage (Figures 3, 12)                                                      | AGC                              | V <sub>CC</sub> = 12V, V <sub>E</sub><br>V <sub>X</sub> = -3.3V, f = |                                                      | -        | 105                       | -     | dB    |

| Voltage Gain, Two Stage Double-Ended Output (Figures 3, 12)                               | Α                                | V <sub>CC</sub> = 12V, V <sub>E</sub><br>V <sub>X</sub> = -3.3V, f = |                                                      | -        | 60                        | -     | dB    |

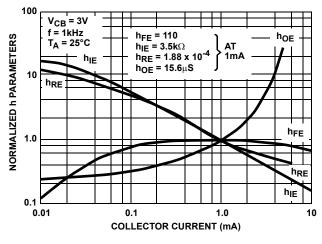

| Low Frequency, Small Signal Equivalent Circuit<br>Characteristics (For Single Transistor) |                                  |                                                                      |                                                      |          |                           |       |       |

| Forward Current Transfer Ratio (Figure 13)                                                | h <sub>FE</sub>                  | $f = 1kHz, V_{CE}$                                                   | $= 3V, I_C = 1mA$                                    | -        | 110                       | -     | -     |

| Short Circuit Input Impedance (Figure 13)                                                 | h <sub>IE</sub>                  | f = 1kHz, V <sub>CE</sub>                                            | = 3V, I <sub>C</sub> = 1mA                           | -        | 3.5                       | ī     | kΩ    |

| Open Circuit Output Impedance<br>(Figure 13)                                              | h <sub>OE</sub>                  | f = 1kHz, V <sub>CE</sub>                                            | f = 1kHz, V <sub>CE</sub> = 3V, I <sub>C</sub> = 1mA |          |                           | -     | μS    |

| Open Circuit Reverse Voltage Transfer<br>Ratio (Figure 13)                                | h <sub>RE</sub>                  | f = 1kHz, V <sub>CE</sub>                                            | = 3V, I <sub>C</sub> = 1mA                           | -        | 1.8 x<br>10 <sup>-4</sup> | -     | -     |

| 1/f Noise Figure for Single Transistor                                                    | NF                               | f = 1kHz, V <sub>CE</sub> =                                          | = 3V                                                 | -        | 3.25                      | -     | dB    |

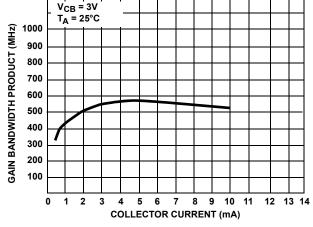

| Gain Bandwidth Product for Single<br>Transistor (Figure 14)                               | f <sub>T</sub>                   | V <sub>CE</sub> = 3V, I <sub>C</sub> =                               | V <sub>CE</sub> = 3V, I <sub>C</sub> = 3mA           |          |                           | -     | MHz   |

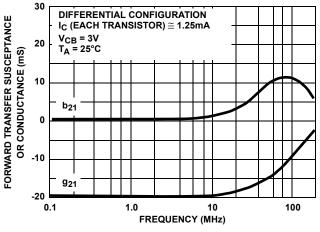

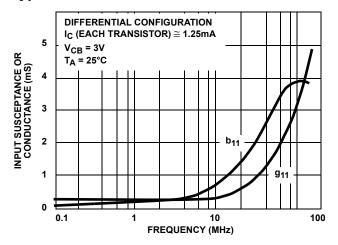

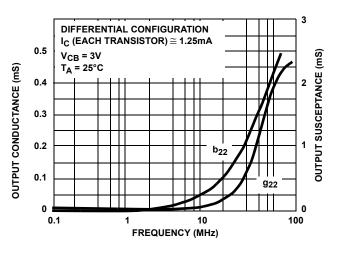

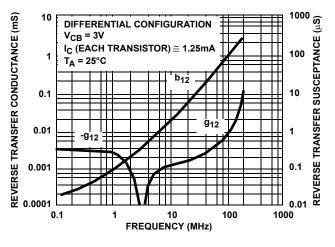

| Admittance Characteristics; Differential Circuit Configuration (For Each Amplifier)       |                                  |                                                                      |                                                      |          |                           |       |       |

| Forward Transfer Admittance (Figure 15)                                                   | Y <sub>21</sub>                  | V <sub>CB</sub> = 3V, f =<br>Each Collector                          | -                                                    | -20 + j0 | -                         | mS    |       |

| Input Admittance (Figure 16)                                                              | Y <sub>11</sub>                  | V <sub>CB</sub> = 3V, f =<br>Each Collector                          |                                                      | -        | 0.22 +<br>j0.1            | -     | mS    |

| Output Admittance (Figure 17)                                                             | Y <sub>22</sub>                  | V <sub>CB</sub> = 3V, f = Each Collector                             |                                                      | -        | 0.01 +<br>j0              | -     | mS    |

| Reverse Transfer Admittance (Figure 18)                                                   | Y <sub>12</sub>                  | V <sub>CB</sub> = 3V, f =<br>Each Collector                          |                                                      | -        | -0.003<br>+ j0            | -     | mS    |

# **Electrical Specifications** $T_A = 25^{\circ}C$ (Continued)

| PARAMETER                                                                      | SYMBOL          | TEST CONDITIONS                                                        | MIN | TYP               | MAX | UNIT |

|--------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------|-----|-------------------|-----|------|

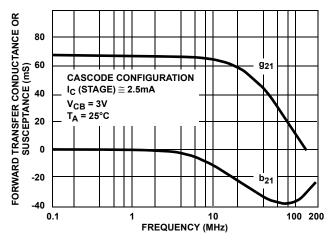

| Admittance Characteristics; Cascode Circuit Configuration (For Each Amplifier) |                 |                                                                        |     |                   |     |      |

| Forward Transfer Admittance (Figure 19)                                        | Y <sub>21</sub> | $V_{CB}$ = 3V, f = 1MHz<br>Total Stage I <sub>C</sub> $\approx$ 2.5 mA | -   | 68 - j0           | -   | mS   |

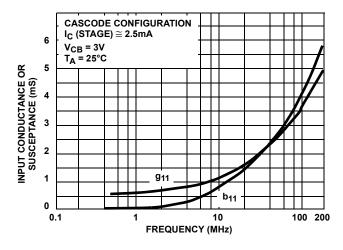

| Input Admittance (Figure 20)                                                   | Y <sub>11</sub> | $V_{CB}$ = 3V, f = 1MHz<br>Total Stage I <sub>C</sub> $\approx$ 2.5 mA | -   | 0.55 +<br>j0      | -   | mS   |

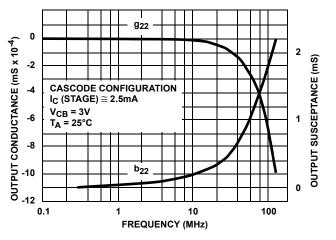

| Output Admittance (Figure 21)                                                  | Y <sub>22</sub> | $V_{CB}$ = 3V, f = 1MHz<br>Total Stage I <sub>C</sub> $\approx$ 2.5 mA | -   | 0 +<br>j0.02      | -   | mS   |

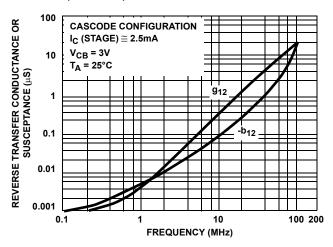

| Reverse Transfer Admittance (Figure 22)                                        | Y <sub>12</sub> | $V_{CB}$ = 3V, f = 1MHz<br>Total Stage I <sub>C</sub> $\approx$ 2.5 mA | -   | 0.004 -<br>j0.005 | -   | μS   |

| Noise Figure                                                                   | NF              | f = 100MHz                                                             | -   | 8                 | -   | dB   |

# **Test Circuits**

FIGURE 1. COMMON MODE REJECTION RATIO TEST SETUP

FIGURE 2. SINGLE STAGE VOLTAGE GAIN TEST SETUP

FIGURE 3. TWO STAGE VOLTAGE GAIN TEST SETUP

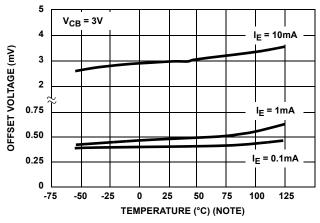

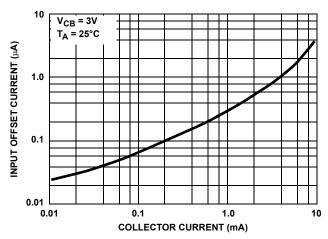

# **Typical Performance Curves**

NOTE: For CA3054 use data from 0°C to 85°C only.

FIGURE 4. COLLECTOR-TO-BASE CUTOFF CURRENT vs

TEMPERATURE FOR EACH TRANSISTOR

NOTE: For CA3054 use data from 0°C to 85°C only.

FIGURE 6. BASE-TO-EMITTER VOLTAGE FOR EACH TRANSISTOR vs TEMPERATURE

FIGURE 8. STATIC BASE-TO-EMITTER VOLTAGE AND INPUT

OFFSET VOLTAGE FOR DIFFERENTIAL PAIRS vs

EMITTER CURRENT

FIGURE 5. INPUT BIAS CURRENT vs COLLECTOR CURRENT FOR EACH TRANSISTOR

NOTE: For CA3054 use data from 0°C to 85°C only.

FIGURE 7. OFFSET VOLTAGE vs TEMPERATURE FOR DIFFERENTIAL PAIRS

FIGURE 9. INPUT OFFSET CURRENT FOR MATCHED

DIFFERENTIAL PAIRS vs COLLECTOR CURRENT

# Typical Performance Curves (Continued)

FIGURE 10. COMMON MODE REJECTION RATIO CHARACTERISTIC

FIGURE 11. SINGLE STAGE VOLTAGE GAIN CHARACTERISTIC

FIGURE 12. TWO STAGE VOLTAGE GAIN CHARACTERISTIC

FIGURE 13. FORWARD CURRENT TRANSFER RATIO ( $h_{FE}$ ), SHORT CIRCUIT INPUT IMPEDANCE ( $h_{IE}$ ), OPEN CIRCUIT OUTPUT IMPEDANCE ( $h_{OE}$ ), AND OPEN CIRCUIT REVERSE VOLTAGE TRANSFER RATIO ( $h_{RE}$ ) vs COLLECTOR CURRENT FOR EACH TRANSISTOR

FIGURE 14. GAIN BANDWIDTH PRODUCT (f<sub>T</sub>) vs COLLECTOR CURRENT

FIGURE 15. FORWARD TRANSFER ADMITTANCE (Y<sub>21</sub>) vs FREQUENCY

# Typical Performance Curves (Continued)

FIGURE 16. INPUT ADMITTANCE (Y<sub>11</sub>)

FIGURE 17. OUTPUT ADMITTANCE (Y22) vs FREQUENCY

FIGURE 18. REVERSE TRANSFER ADMITTANCE (Y<sub>12</sub>) vs FREQUENCY

FIGURE 19. FORWARD TRANSFER ADMITTANCE  $(Y_{21})$  vs FREQUENCY

FIGURE 20. INPUT ADMITTANCE (Y<sub>11</sub>) vs FREQUENCY

FIGURE 21. OUTPUT ADMITTANCE (Y22) vs FREQUENCY

# Typical Performance Curves (Continued)

FIGURE 22. REVERSE TRANSFER ADMITTANCE (Y<sub>12</sub>) vs FREQUENCY

© Copyright Intersil Americas LLC 2004-2005. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="https://www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>