Commercial/Express

- MCS<sup>®</sup> 51 Microcontroller Compatible Instruction Set

- Pin Compatible with 44-lead PLCC and 40-lead PDIP MCS 51 Sockets

- Fast Instruction Pipeline

- 16-bit Internal Code Fetch

- 8-bit, Min 2-clock External Code Fetch in Page Mode

- User-selectable Configurations:

- External Wait States (0-3 wait states)

- Page Mode

- 64K External Code Memory Space

- 64K External Data Memory Space

- ROM/OTPROM Options: 8 Kbytes (SA), 16 Kbytes (SB) or without ROM/OTPROM

- 256 Bytes On-Chip RAM

- Power Management

- Idle Mode

- Powerdown Mode

- 32 Programmable I/O Lines

- Seven Maskable Interrupt Sources with Four Programmable Priority Levels

- Three Flexible 16-bit Timer/counters

- Hardware Watchdog Timer

- Programmable Counter Array

- High-speed Output

- Compare/Capture Operation

- Pulse Width Modulator

- Watchdog Timer

- Programmable Serial I/O Port

- Framing Error Detection

- Automatic Address Recognition

- High-performance CHMOS Technology

- Static Standby to 16-MHz Operation

- Package Options (PDIP, PLCC)

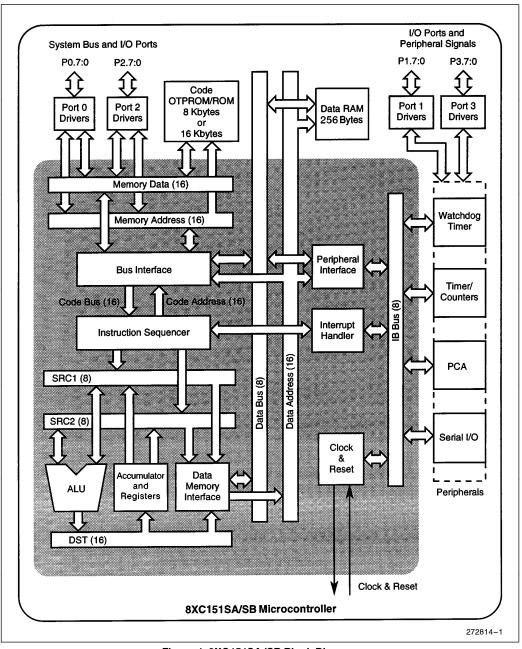

The 8XC151SA/SB has an MCS 51 microcontroller compatible instructon set. It is available in 40-pin PDIP and 44-lead PLCC compatible with the MCS 51 microcontroller. The 8XC151SA/SB has 256 bytes of on-chip RAM and is available in 8/16 Kbytes of on-chip ROM/OTPROM or without ROM/OTPROM. A variety of new features such as programmable wait states, page mode and extended ALE can be selected using the new user-programmable configuration.

Figure 1. 8XC151SA/SB Block Diagram

#### **TEMPERATURE RANGE**

With the commercial (standard) temperature option, the device operates over the temperature range 0°C to +70°C. The express temperature option provides -40°C to +85°C device operation.

#### PROLIFERATION OPTIONS

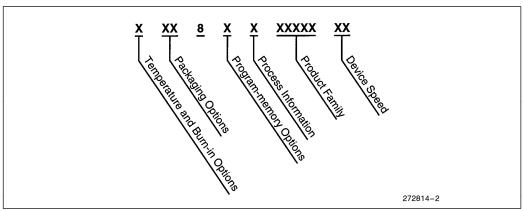

Table 1 lists the proliferation options. See Figure 2 for the 8XC151SA/SB family nomenclature.

**Table 1. Proliferation Options**

| 8XC151SA/SB (0 MHz $_{-}$ 16 MHz; 5V $\pm$ 10%) |            |  |

|-------------------------------------------------|------------|--|

| 80C151SB                                        | CPU-only   |  |

| 83C151SA                                        | 8K ROM     |  |

| 83C151SB                                        | 16K ROM    |  |

| 87C151SA                                        | 8K OTPROM  |  |

| 87C151SB                                        | 16K OTPROM |  |

#### PROCESS INFORMATION

This device is manufactured on a complimentary high-performance metal-oxide semiconductor (CHMOS) process. Additional process and reliability information is available in Intel's *Components Quality and Reliability Handbook* (order number 210997).

All thermal impedance data is approximate for static air conditions at 1 watt of power dissipation. Values change depending on operating conditions and application requirements. The Intel *Packaging Handbook* (order number 240800) describes Intel's thermal impedance test methodology.

**Table 2. Thermal Characteristics**

| Package Type | $\theta_{JA}$ | $\theta$ JC |

|--------------|---------------|-------------|

| 44-Lead PLCC | 46°C/W        | 16°C/W      |

| 40-Pin PDIP  | 45°C/W        | 16°C/W      |

#### PACKAGE OPTIONS

Table 3 lists the 8XC151SA/SB packages.

**Table 3. Package Information**

| Pkg. | Definition         | Temperature    |

|------|--------------------|----------------|

| N    | 44-Lead PLCC       | 0°C to +70°C   |

| Р    | 40-Pin Plastic DIP | 0°C to +70°C   |

| TN   | 44-Lead PLCC       | -40°C to +85°C |

| TP   | 40-Pin Plastic DIP | -40°C to +85°C |

Figure 2. The 8XC151SA/SB Family Nomenclature

**Table 4. Description of Product Nomenclature**

| Parameter                       | Options | Description                                                                        |

|---------------------------------|---------|------------------------------------------------------------------------------------|

| Temperature and Burn-in Options | no mark | Commercial operating temperature range (0°C to 70°C) with Intel standard burn-in.  |

|                                 | Т       | Express operating temperature range ( - 40°C to 85°C) with Intel standard burn-in. |

| Packaging Options               | N       | 44-lead Plastic Leaded Chip Carrier (PLCC)                                         |

|                                 | Р       | 40-pin Plastic Dual In-line Package (PDIP)                                         |

| Program Memory 0                |         | Without ROM/OTPROM                                                                 |

| Options                         | 3       | ROM                                                                                |

|                                 | 7       | User programmable OTPROM                                                           |

| Process Information             | С       | CHMOS                                                                              |

| Product Family                  | 151     | 8-bit controller architecture                                                      |

| Device Memory Options           | SA/SB   | 256 bytes RAM/8/16 Kbyte ROM/OTPROM or without ROM/OTPROM                          |

| Device Speed                    | 16      | External clock frequency                                                           |

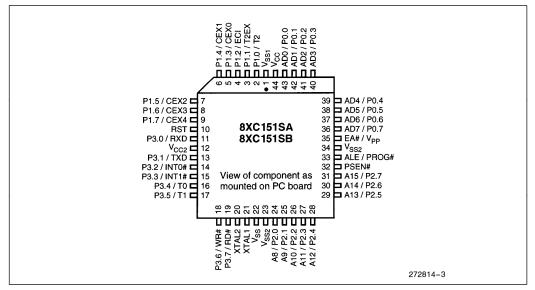

Figure 3. 8XC151SA/SB 44-Lead PLCC Package

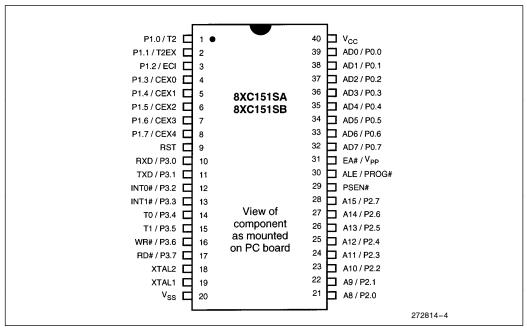

Figure 4. 8XC151SA/SB 40-Pin PDIP and Ceramic DIP Packages

Table 5. PLCC/DIP Signal Assignment Arranged by Functional Categories

| Address & Data |               |    |  |  |  |  |

|----------------|---------------|----|--|--|--|--|

| Name           | Name PLCC DIP |    |  |  |  |  |

| AD0/P0.0       | 43            | 39 |  |  |  |  |

| AD1/P0.1       | 42            | 38 |  |  |  |  |

| AD2/P0.2       | 41            | 37 |  |  |  |  |

| AD3/P0.3       | 40            | 36 |  |  |  |  |

| AD4/P0.4       | 39            | 35 |  |  |  |  |

| AD5/P0.5       | 38            | 34 |  |  |  |  |

| AD6/P0.6       | 37            | 33 |  |  |  |  |

| AD7/P0.7       | 36            | 32 |  |  |  |  |

| A8/P2.0        | 24            | 21 |  |  |  |  |

| A9/P2.1        | 25            | 22 |  |  |  |  |

| A10/P2.2       | 26            | 23 |  |  |  |  |

| A11/P2.3       | 27            | 24 |  |  |  |  |

| A12/P2.4       | 28            | 25 |  |  |  |  |

| A13/P2.5       | 29            | 26 |  |  |  |  |

| A14/P2.6       | 30            | 27 |  |  |  |  |

| A15/P2.7       | 31            | 28 |  |  |  |  |

| Processsor Control  |    |    |  |  |

|---------------------|----|----|--|--|

| Name PLCC DIP       |    |    |  |  |

| P3.2/INT0#          | 14 | 12 |  |  |

| P3.3/INT1#          | 15 | 13 |  |  |

| EA#/V <sub>PP</sub> | 35 | 31 |  |  |

| RST                 | 10 | 9  |  |  |

| XTAL1               | 21 | 18 |  |  |

| XTAL2               | 20 | 19 |  |  |

| Input/Output  |    |    |  |  |  |

|---------------|----|----|--|--|--|

| Name PLCC DIP |    |    |  |  |  |

| P1.0/T2       | 2  | 1  |  |  |  |

| P1.1/T2EX     | 3  | 2  |  |  |  |

| P1.2/ECI      | 4  | 3  |  |  |  |

| P1.3/CEX0     | 5  | 4  |  |  |  |

| P1.4/CEX1     | 6  | 5  |  |  |  |

| P1.5/CEX2     | 7  | 6  |  |  |  |

| P1.6/CEX3     | 8  | 7  |  |  |  |

| P1.7/CEX4     | 9  | 8  |  |  |  |

| P3.0/RXD      | 11 | 10 |  |  |  |

| P3.1/TXD      | 13 | 11 |  |  |  |

| P3.4/T0       | 16 | 14 |  |  |  |

| P3.5/T1       | 17 | 15 |  |  |  |

| Power & Ground      |        |    |  |  |

|---------------------|--------|----|--|--|

| Name PLCC DIP       |        |    |  |  |

| V <sub>CC</sub>     | 44     | 40 |  |  |

| V <sub>CC2</sub>    | 12     | _  |  |  |

| $V_{SS}$            | 22     | 20 |  |  |

| V <sub>SS1</sub>    | 1      | _  |  |  |

| V <sub>SS2</sub>    | 23, 34 | _  |  |  |

| EA#/V <sub>PP</sub> | 35     | 31 |  |  |

| Bus Control & Status |    |    |  |  |

|----------------------|----|----|--|--|

| Name PLCC DIP        |    |    |  |  |

| P3.6/WR#             | 18 | 16 |  |  |

| P3.7/RD#             | 19 | 17 |  |  |

| ALE/PROG#            | 33 | 30 |  |  |

| PSEN#                | 32 | 29 |  |  |

Table 6. Signal Assignments Arranged by Package Number

| PLCC | DIP | Name             |

|------|-----|------------------|

| 1    | _   | V <sub>SS1</sub> |

| 2    | 1   | P1.0/T2          |

| 3    | 2   | P1.1/T2EX        |

| 4    | 3   | P1.2/ECI         |

| 5    | 4   | P1.3/CEX0        |

| 6    | 5   | P1.4/CEX1        |

| 7    | 6   | P1.5/CEX2        |

| 8    | 7   | P1.6/CEX3        |

| 9    | 8   | P1.7/CEX4        |

| 10   | 9   | RST              |

| 11   | 10  | P3.0/RXD         |

| 12   | _   | V <sub>CC2</sub> |

| 13   | 11  | P3.1/TXD         |

| 14   | 12  | P3.2/INT0#       |

| 15   | 13  | P3.3/INT1#       |

| 16   | 14  | P3.4/T0          |

| 17   | 15  | P3.5/T1          |

| 18   | 16  | P3.6/WR#         |

| 19   | 17  | P3.7/RD#         |

| 20   | 18  | XTAL2            |

| 21   | 19  | XTAL1            |

| 22   | 20  | V <sub>SS</sub>  |

| PLCC | DIP | Name                |

|------|-----|---------------------|

| 23   | _   | V <sub>SS2</sub>    |

| 24   | 21  | A8/P2.0             |

| 25   | 22  | A9/P2.1             |

| 26   | 23  | A10/P2.2            |

| 27   | 24  | A11/P2.3            |

| 28   | 25  | A12/P2.4            |

| 29   | 26  | A13/P2.5            |

| 30   | 27  | A14/P2.6            |

| 31   | 28  | A15/P2.7            |

| 32   | 29  | PSEN#               |

| 33   | 30  | ALE/PROG#           |

| 34   | _   | $V_{SS2}$           |

| 35   | 31  | EA#/V <sub>pp</sub> |

| 36   | 32  | AD7/P0.7            |

| 37   | 33  | AD6/P0.6            |

| 38   | 34  | AD5/P0.5            |

| 39   | 35  | AD4/P0.4            |

| 40   | 36  | AD3/P0.3            |

| 41   | 37  | AD2/P0.2            |

| 42   | 38  | AD1/P0.1            |

| 43   | 39  | AD0/P0.0            |

| 44   | 40  | V <sub>CC</sub>     |

#### SIGNAL DESCRIPTIONS

**Table 7. Signal Descriptions**

| Signal<br>Name                 | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                               | Multiplexed<br>With                 |

|--------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| A15:8†                         | 0    | Address Lines. Upper address lines for the external bus.                                                                                                                                                                                                                                                                                                                                                  | P2.7:0                              |

| AD7:0†                         | 1/0  | Address/Data Lines. Multiplexed lower address lines and data lines for external memory.                                                                                                                                                                                                                                                                                                                   | P0.7:0                              |

| ALE                            | 0    | Address Latch Enable. ALE signals the start of an external bus cycle and indicates that valid address information is available on lines A15:8 and AD7:0. An external latch can use ALE to demultiplex the address from the address/data bus.                                                                                                                                                              | PROG#                               |

| CEX4:0                         | 1/0  | Programmable Counter Array (PCA) Input/Output Pins. These are input signals for the PCA capture mode and output signals for the PCA compare mode and PCA PWM mode.                                                                                                                                                                                                                                        | P1.6:3<br>P1.7                      |

| EA#                            | I    | External Access. Directs program memory accesses to on-chip or off-chip code memory. For EA# = 0, all program memory accesses are off-chip. For EA# = 1, an access is to on-chip ROM/OTPROM if the address is within the range of the on-chip ROM/OTPROM; otherwise the access is off-chip. The value of EA# is latched at reset. For devices without on-chip ROM/OTPROM, EA# must be strapped to ground. | Vpp                                 |

| ECI                            | I    | PCA External Clock Input. External clock input to the 16-bit PCA timer.                                                                                                                                                                                                                                                                                                                                   | P1.2                                |

| INT1:0#                        | I    | External Interrupts 0 and 1. These inputs set bits IE1:0 in the TCON register. If bits IT1:0 in the TCON register are set, bits IE1:0 are set by a falling edge on INT1#/INT0#. If bits INT1:0 are clear, bits IE1:0 are set by a low level on INT1:0#.                                                                                                                                                   | P3.3:2                              |

| PROG#                          | I    | <b>Programming Pulse.</b> The programming pulse is applied to this pin for programming the on-chip OTPROM.                                                                                                                                                                                                                                                                                                | ALE                                 |

| P0.7:0                         | 1/0  | Port 0. This is an 8-bit, open-drain, bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                             | AD7:0                               |

| P1.0<br>P1.1<br>P1.2<br>P1.7:3 | I/O  | Port 1. This is an 8-bit, bidirectional I/O port with internal pullups.                                                                                                                                                                                                                                                                                                                                   | T2<br>T2EX<br>ECI<br>CEX3:0<br>CEX4 |

| P2.7:0                         | 1/0  | Port 2. This is an 8-bit, bidirectional I/O port with internal pullups.                                                                                                                                                                                                                                                                                                                                   | A15:8                               |

<sup>†</sup> The descriptions of A15:8/P2.7:0 and AD7:0/P0.7:0 are for the nonpage-mode chip configuration (compatible with 44-lead PLCC and 40-pin DIP MCS 51 microcontrollers). If the chip is configured for page-mode operation, port 0 carries the lower address bits (A7:0), and port 2 carries the upper address bits (A15:8) and the data (D7:0).

Table 7. Signal Descriptions (Continued)

| Signal<br>Name                                   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                        | Multiplexed<br>With                         |

|--------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| P3.0<br>P3.1<br>P3.3:2<br>P3.5:4<br>P3.6<br>P3.7 | I/O  | Port 3. This is an 8-bit, bidirectional I/O port with internal pullups.                                                                                                                                                                                                                                                                                                                                                            | RXD<br>TXD<br>INT1:0#<br>T1:0<br>WR#<br>RD# |

| PSEN#                                            | 0    | <b>Program Store Enable.</b> Read signal output. This output is asserted for a memory address range that depends on bits RD0 and RD1 in configuration byte UCONFIG0.                                                                                                                                                                                                                                                               | _                                           |

| RD#                                              | 0    | Read. Read signal output to external data memory.                                                                                                                                                                                                                                                                                                                                                                                  | P3.7                                        |

| RST                                              | I    | <b>Reset.</b> Reset input to the chip. Holding this pin high for 64 oscillator periods while the oscillator is running resets the device. The port pins are driven to their reset conditions when a voltage greater than $V_{IH1}$ is applied, whether or not the oscillator is running. This pin has an internal pulldown resistor, which allows the device to be reset by connecting a capacitor between this pin and $V_{CC}$ . | _                                           |

|                                                  |      | Asserting RST when the chip is in idle mode or powerdown mode returns the chip to normal operation.                                                                                                                                                                                                                                                                                                                                |                                             |

| RXD                                              | 1/0  | Receive Serial Data. RXD sends and receives data in serial I/O mode 0 and receives data in serial I/O modes 1, 2, and 3.                                                                                                                                                                                                                                                                                                           | P3.0                                        |

| T1:0                                             | I    | Timer 1:0 External Clock Inputs. When timer 1:0 operates as a counter, a falling edge on the T1:0 pin increments the count.                                                                                                                                                                                                                                                                                                        | P3.5:4                                      |

| T2                                               | 1/0  | <b>Timer 2 Clock Input/Output.</b> For the timer 2 capture mode, this signal is the external clock input. For the clock-out mode, it is the timer 2 clock output.                                                                                                                                                                                                                                                                  | P1.0                                        |

| T2EX                                             | ı    | Timer 2 External Input. In timer 2 capture mode, a falling edge initiates a capture of the timer 2 registers. In auto-reload mode, a falling edge causes the timer 2 registers to be reloaded. In the updown counter mode, this signal determines the count direction:  1 = up, 0 = down.                                                                                                                                          | P1.1                                        |

| TXD                                              | 0    | <b>Transmit Serial Data.</b> TXD outputs the shift clock in serial I/O mode 0 and transmits serial data in serial I/O modes 1, 2, and 3.                                                                                                                                                                                                                                                                                           | P3.1                                        |

| V <sub>CC</sub>                                  | PWR  | Supply Voltage. Connect this pin to the $\pm$ 5V supply voltage.                                                                                                                                                                                                                                                                                                                                                                   | _                                           |

| V <sub>CC2</sub>                                 | PWR  | Secondary Supply Voltage 2. This supply voltage connection is provided to reduce power supply noise. Connection of this pin to the +5V supply voltage is recommended. However, when using the 8XC151SA/SB as a pin-for-pin replacement for the 8XC51FX, V <sub>SS2</sub> can be unconnected without loss of compatibility. (Not available on DIP)                                                                                  | _                                           |

| V <sub>PP</sub>                                  | I    | <b>Programming Supply Voltage.</b> The programming supply voltage is applied to this pin for programming the on-chip OTPROM.                                                                                                                                                                                                                                                                                                       | EA#                                         |

<sup>†</sup> The descriptions of A15:8/P2.7:0 and AD7:0/P0.7:0 are for the nonpage-mode chip configuration (compatible with 44-lead PLCC and 40-pin DIP MCS 51 microcontrollers). If the chip is configured for page-mode operation, port 0 carries the lower address bits (A7:0), and port 2 carries the upper address bits (A15:8) and the data (D7:0).

Table 7. Signal Descriptions (Continued)

| Signal<br>Name   | Туре | Description                                                                                                                                                                                                                                                                                                                              | Multiplexed<br>With |

|------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| V <sub>SS</sub>  | GND  | Circuit Ground. Connect this pin to ground.                                                                                                                                                                                                                                                                                              | _                   |

| V <sub>SS1</sub> | GND  | <b>Secondary Ground.</b> This ground is provided to reduce ground bounce and improve power supply bypassing. Connection of this pin to ground is recommended. However, when using the 8XC151SA/SB as a pinfor-pin replacement for the 8XC51BH, V <sub>SS1</sub> can be unconnected without loss of compatibility. (Not available on DIP) |                     |

| V <sub>SS2</sub> | GND  | Secondary Ground 2. This ground is provided to reduce ground bounce and improve power supply bypassing. Connection of this pin to ground is recommended. However, when using the 8XC151SA/SB as a pin-for-pin replacement for the 8XC51FX, V <sub>SS2</sub> can be unconnected without loss of compatibility. (Not available on DIP)     |                     |

| WR#              | 0    | Write. Write signal output to external memory.                                                                                                                                                                                                                                                                                           | P3.6                |

| XTAL1            | I    | Input to the On-chip, Inverting, Oscillator Amplifier. To use the internal oscillator, a crystal/resonator circuit is connected to this pin. If an external oscillator is used, its output is connected to this pin. XTAL1 is the clock source for internal timing.                                                                      |                     |

| XTAL2            | 0    | Output of the On-chip, Inverting, Oscillator Amplifier. To use the internal oscillator, a crystal/resonator circuit is connected to this pin. If an external oscillator is used, leave XTAL2 unconnected.                                                                                                                                | _                   |

<sup>†</sup> The descriptions of A15:8/P2.7:0 and AD7:0/P0.7:0 are for the nonpage-mode chip configuration (compatible with 44-lead PLCC and 40-pin DIP MCS 51 microcontrollers). If the chip is configured for page-mode operation, port 0 carries the lower address bits (A7:0), and port 2 carries the upper address bits (A15:8) and the data (D7:0).

#### **ELECTRICAL CHARACTERISTICS**

#### **ABSOLUTE MAXIMUM RATINGS\***

#### NOTE:

Maximum power dissipation is based on package heat-transfer limitations, not device power consumption.

# **OPERATING CONDITIONS\***

| T <sub>A</sub> (Ambient Temperature Under B | ias):             |

|---------------------------------------------|-------------------|

| Commercial                                  |                   |

| Express                                     | -40°C to $+85$ °C |

| V <sub>CC</sub> (Digital Supply Voltage)    | 4.5V to 5.5V      |

| V <sub>SS</sub>                             |                   |

NOTICE: This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available. Verify with your local Intel Sales office that you have the latest data sheet before finalizing a design.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

#### DC CHARACTERISTICS

Parameter values apply to all devices unless otherwise indicated.

Table 8. DC Characteristics at  $V_{CC} = 4.5V - 5.5V$

| Symbol           | Parameter                                            | Min                                                                     | Typical | Max                      | Units    | Test Conditions                                                                                                                              |

|------------------|------------------------------------------------------|-------------------------------------------------------------------------|---------|--------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage (except EA#)                       | -0.5                                                                    |         | 0.2V <sub>CC</sub> - 0.1 | <b>V</b> |                                                                                                                                              |

| V <sub>IL1</sub> | Input Low Voltage<br>(EA#)                           | 0                                                                       |         | 0.2V <sub>CC</sub> - 0.3 | >        |                                                                                                                                              |

| V <sub>IH</sub>  | Input High Voltage<br>(except XTAL1, RST)            | 0.2V <sub>CC</sub> + 0.9                                                |         | V <sub>CC</sub> + 0.5    | >        |                                                                                                                                              |

| V <sub>IH1</sub> | Input High Voltage<br>(XTAL1, RST)                   | 0.7V <sub>CC</sub>                                                      |         | V <sub>CC</sub> + 0.5    | ٧        |                                                                                                                                              |

| V <sub>OL</sub>  | Output Low Voltage<br>(Port 1, 2, 3)                 |                                                                         |         | 0.3<br>0.45<br>1.0       | >        | $\begin{split} I_{OL} &= 100 \ \mu\text{A} \\ I_{OL} &= 1.6 \ \text{mA} \\ I_{OL} &= 3.5 \ \text{mA} \\ \text{(Note 1, Note 2)} \end{split}$ |

| V <sub>OL1</sub> | Output Low Voltage<br>(Port 0, ALE, PSEN#)           |                                                                         |         | 0.3<br>0.45<br>1.0       | ٧        | $\begin{split} I_{OL} &= 200 \ \mu\text{A} \\ I_{OL} &= 3.2 \ \text{mA} \\ I_{OL} &= 7.0 \ \text{mA} \\ \text{(Note 1, Note 2)} \end{split}$ |

| V <sub>OH</sub>  | Output High Voltage<br>(Port 1, 2, 3, ALE,<br>PSEN#) | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |         |                          | V        | $I_{OH} = -10 \mu A$<br>$I_{OH} = -30 \mu A$<br>$I_{OH} = -60 \mu A$<br>(Note 3)                                                             |

#### NOTES:

1. Under steady-state (non-transient) conditions,  $I_{\mbox{OL}}$  must be externally limited as follows:

Maximum I<sub>OL</sub> per port pin: 10 mA

Maximum I<sub>OL</sub> per 8-bit port:

port 0 26 mA ports 1–3 15 mA

Maximum Total I<sub>OL</sub> for

all output pins 71 mA

If  $I_{OL}$  exceeds the test conditions,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 2. Capacitive loading on ports 0 and 2 may cause spurious noise pulses above 0.4V on the low-level outputs of ALE and ports 1, 2, and 3. The noise is due to external bus capacitance discharging into the port 0 and port 2 pins when these pins change from high to low. In applications where capacitive loading exceeds 100 pF, the noise pulses on these signals may exceed 0.8V. It may be desirable to qualify ALE or other signals with a Schmitt trigger or CMOS-level input logic.

- Capacitive loading on ports 0 and 2 causes the V<sub>OH</sub> on ALE and PSEN# to drop below the specification when the address lines are stabilizing.

- 4. Typical values are obtained using  $V_{CC} = 5.0$ ,  $T_A = 25^{\circ}C$  and are not guaranteed.

Table 8. DC Characteristics at  $V_{CC} = 4.5V - 5.5V$  (Continued)

| Symbol           | Parameter                                                                  | Min                                                                    | Typical        | Max  | Units | Test Conditions                                                                                                |

|------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------|----------------|------|-------|----------------------------------------------------------------------------------------------------------------|

| V <sub>OH1</sub> | Output High Voltage<br>(Port 0 in External<br>Address)                     | $V_{CC} - 0.3$<br>$V_{CC} - 0.7$<br>$V_{CC} - 1.5$                     |                |      | V     | $I_{OH}=-200~\mu A$<br>$I_{OH}=-3.2~m A$<br>$I_{OH}=-7.0~m A$                                                  |

| V <sub>OH2</sub> | Output High Voltage<br>(Port 2 in External<br>Address during Page<br>Mode) | V <sub>CC</sub> -0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                |      | V     | $\begin{split} I_{OH} &= -200~\mu\text{A} \\ I_{OH} &= -3.2~\text{mA} \\ I_{OH} &= -7.0~\text{mA} \end{split}$ |

| I <sub>IL</sub>  | Logical 0 Input Cur-<br>rent (Port 1, 2, 3)                                |                                                                        |                | -50  | μΑ    | $V_{IN} = 0.45V$                                                                                               |

| ILI              | Input Leakage Cur-<br>rent (Port 0)                                        |                                                                        |                | ± 10 | μΑ    | 0.45 < V <sub>IN</sub> < V <sub>CC</sub>                                                                       |

| I <sub>TL</sub>  | Logical 1-to-0 Transition Current (Port 1, 2, 3)                           |                                                                        |                | -650 | μΑ    | $V_{IN} = 2.0V$                                                                                                |

| R <sub>RST</sub> | RST Pulldown Resistor                                                      | 40                                                                     |                | 225  | kΩ    |                                                                                                                |

| C <sub>IO</sub>  | Pin Capacitance                                                            |                                                                        | 10<br>(Note 4) |      | pF    | $F_{OSC} = 16 \text{ MHz}$<br>$T_A = 25^{\circ}\text{C}$                                                       |

| I <sub>PD</sub>  | Powerdown Current                                                          |                                                                        | 10<br>(Note 4) | < 20 | μΑ    |                                                                                                                |

| I <sub>DL</sub>  | Idle Mode Current                                                          |                                                                        | 13<br>(Note 4) | 20   | mA    | F <sub>OSC</sub> = 16 MHz                                                                                      |

| Icc              | Operating Current                                                          |                                                                        | 71<br>(Note 4) | 85   | mA    | F <sub>OSC</sub> = 16 MHz                                                                                      |

#### NOTES:

1. Under steady-state (non-transient) conditions,  $I_{\mbox{OL}}$  must be externally limited as follows:

$Maximum \ I_{OL} \ per \ port \ pin: \quad 10 \ mA$

Maximum I<sub>OL</sub> per 8-bit port:

port 0 26 mA ports 1–3 15 mA

Maximum Total I<sub>OL</sub> for

all output pins 71 mA

If  $I_{OL}$  exceeds the test conditions,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 2. Capacitive loading on ports 0 and 2 may cause spurious noise pulses above 0.4V on the low-level outputs of ALE and ports 1, 2, and 3. The noise is due to external bus capacitance discharging into the port 0 and port 2 pins when these pins change from high to low. In applications where capacitive loading exceeds 100 pF, the noise pulses on these signals may exceed 0.8V. It may be desirable to qualify ALE or other signals with a Schmitt trigger or CMOS-level input logic.

- Capacitive loading on ports 0 and 2 causes the V<sub>OH</sub> on ALE and PSEN# to drop below the specification when the address lines are stabilizing.

- 4. Typical values are obtained using  $V_{CC}=5.0$ ,  $T_A=25^{\circ}C$  and are not guaranteed.

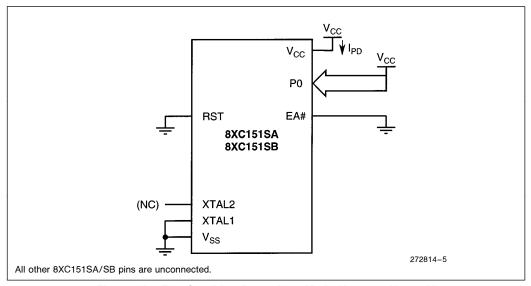

Figure 5. I<sub>PD</sub> Test Condition, Powerdown Mode,  $V_{CC}=2.0V-5.5V$

#### **AC Characteristics**

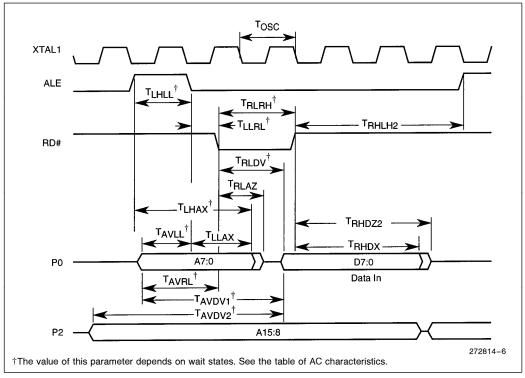

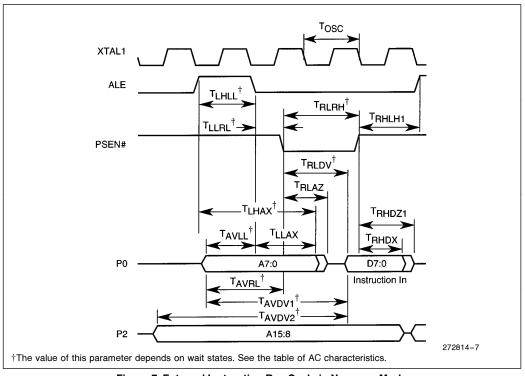

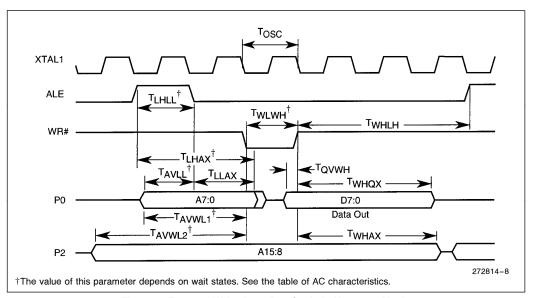

Table 8 lists AC timing parameters for the 8XC151SA/SB with no wait states. External wait states can be added by extending PSEN#/RD#/WR# and/or by extending ALE. In the table, Notes 3 and 5 mark parameters affected by an ALE wait

state, and Notes 4 and 5 mark parameters affected by a PSEN#/RD#/WR# wait state.

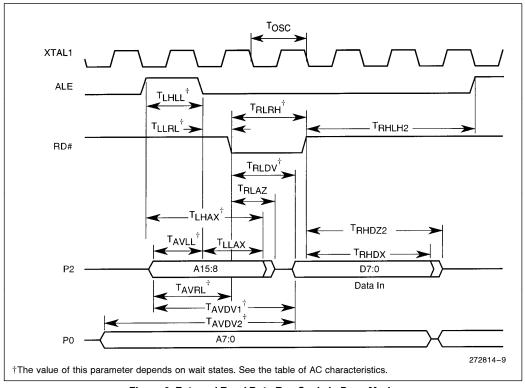

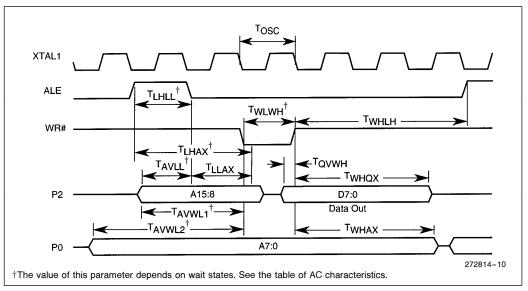

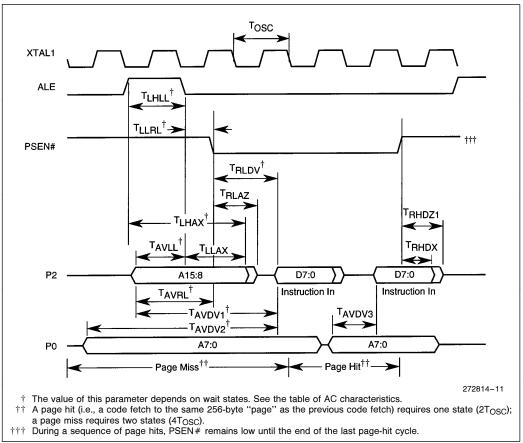

Figures 5-11 show the bus cycles with the timing parameters.

Table 9. AC Characteristics (Capacitive Loading = 50 pF)

| Symbol                | Parameter                                           | @ Max F <sub>OSC</sub> (1) F <sub>OSC</sub> Variable |     |                                   | Units |           |

|-----------------------|-----------------------------------------------------|------------------------------------------------------|-----|-----------------------------------|-------|-----------|

| Cymbo.                | r di dinotoi                                        | Min                                                  | Max | Min                               | Max   |           |

| Fosc                  | XTAL1 Frequency                                     | N/A                                                  | N/A | 0                                 | 16    | MHz       |

| T <sub>OSC</sub>      | 1/F <sub>OSC</sub><br>@ 12 MHz<br>@ 16 MHz          | N/A                                                  | N/A | 83.3<br>62.5                      |       | ns        |

| T <sub>LHLL</sub>     | ALE Pulse Width<br>@ 12 MHz<br>@ 16 MHz             | 68.3<br>47.5                                         |     | (1+2M)<br>T <sub>OSC</sub> - 15   |       | ns<br>(3) |

| T <sub>AVLL</sub>     | Address Valid to ALE Low<br>@ 12 MHz<br>@ 16 MHz    | 58.3<br>37.5                                         |     | (1+2M)<br>T <sub>OSC</sub> - 25   |       | ns<br>(3) |

| T <sub>LLAX</sub>     | Address Hold after ALE Low<br>@ 12 MHz<br>@ 16 MHz  | 10<br>10                                             |     | 10                                |       | ns        |

| T <sub>RLRH</sub> (2) | RD# or PSEN# Pulse Width<br>@ 12 MHz<br>@ 16 MHz    | 151.6<br>110                                         |     | 2(1 + N)<br>T <sub>OSC</sub> - 15 |       | ns<br>(4) |

| T <sub>WLWH</sub>     | WR# Pulse Width<br>@ 12 MHz<br>@ 16 MHz             | 151.6<br>110                                         |     | 2(1 + N)<br>T <sub>OSC</sub> - 15 |       | ns<br>(4) |

| T <sub>LLRL</sub> (2) | ALE Low to RD# or PSEN# Low<br>@ 12 MHz<br>@ 16 MHz | 58.3<br>37.5                                         |     | Tosc - 25                         |       | ns        |

| T <sub>LHAX</sub>     | ALE High to Address Hold<br>@ 12 MHz<br>@ 16 MHz    | 83.3<br>62.5                                         |     | (1+2M)<br>T <sub>OSC</sub>        |       | ns<br>(3) |

- 1. 16 MHz.

- 2. Specifications for PSEN# are identical to those for RD#.

- 3. In the formula, M = Number of wait states (0 or 1) for ALE.

- 4. In the formula, N=Number of wait states (0, 1, 2, or 3) for RD#/PSEN#/WR#.

- 5. "Typical" specifications are untested and not guaranteed.

Table 9. AC Characteristics (Capacitive Loading = 50 pF) (Continued)

| Symbol                | Parameter                                                               | @ Max F <sub>OSC</sub> (1) |              | F <sub>OSC</sub> Variable |                                   | Units     |

|-----------------------|-------------------------------------------------------------------------|----------------------------|--------------|---------------------------|-----------------------------------|-----------|

| Cymbo.                | T drainotor                                                             | Min                        | Max          | Min                       | Max                               |           |

| T <sub>RLDV</sub> (2) | RD#/PSEN# Low to valid Data/Instruction In<br>@ 12 MHz<br>@ 16 MHz      |                            | 111.6<br>70  |                           | 2(1+N)<br>T <sub>OSC</sub> - 55   | ns<br>(4) |

| T <sub>RHDX</sub> (2) | RD#/PSEN# Data/Instruction Hold after RD# and PSEN# High                | 0                          |              | 0                         |                                   | ns        |

| T <sub>RLAZ</sub> (2) | RD#/PSEN# Low to Address Float                                          | Typ. = 0 (5)               | 2            | Typ. = 0 (5)              | 2                                 | ns        |

| T <sub>RHDZ1</sub>    | Instruction Float after RD#/PSEN# High @ 12 MHz @ 16 MHz                |                            | 0            |                           | 0                                 | ns        |

| T <sub>RHDZ2</sub>    | Data Float after RD#/PSEN# High<br>@ 12 MHz<br>@ 16 MHz                 |                            | 151.6<br>110 |                           | 2T <sub>OSC</sub><br>-15          | ns        |

| T <sub>RHLH1</sub>    | RD#/PSEN# High to ALE High (Instruction)<br>@ 12 MHz<br>@ 16 MHz        | 0                          |              | 0                         |                                   | ns        |

| T <sub>RHLH2</sub>    | RD#/PSEN# High to ALE High (Data)<br>@ 12 MHz<br>@ 16 MHz               | 156.6<br>115               |              | 2T <sub>OSC</sub> - 10    |                                   | ns        |

| T <sub>WHLH</sub>     | WR# High to ALE High<br>@ 12 MHz<br>@ 16 MHz                            | 166.6<br>125               |              | 2T <sub>OSC</sub>         |                                   | ns        |

| T <sub>AVDV1</sub>    | Address (P0) Valid to Valid Data/Instruction In<br>@ 12 MHz<br>@ 16 MHz |                            | 253.2<br>170 |                           | 4(1+M/2)<br>T <sub>OSC</sub> - 80 | ns<br>(3) |

| T <sub>AVDV2</sub>    | Address (P2) Valid to Valid Data/Instruction In<br>@ 12 MHz<br>@ 16 MHz |                            | 268.2<br>185 |                           | 4(1+M/2)<br>T <sub>OSC</sub> - 65 | ns<br>(3) |

| T <sub>AVDV3</sub>    | Address (P0) Valid to Valid Instruction In<br>@ 12 MHz<br>@ 16 MHz      |                            | 116.6<br>75  |                           | 2T <sub>OSC</sub><br>-50          | ns        |

- 1. 16 MHz.

- 2. Specifications for PSEN# are identical to those for RD#.

- 3. In the formula, M = Number of wait states (0 or 1) for ALE.

- 4. In the formula, N=Number of wait states (0, 1, 2, or 3) for RD#/PSEN#/WR#.

- 5. "Typical" specifications are untested and not guaranteed.

Table 9. AC Characteristics (Capacitive Loading = 50 pF) (Continued)

| Symbol                | Parameter                                              | @ Max F      | osc (1) | F <sub>OSC</sub> Varia          | ble | Units     |

|-----------------------|--------------------------------------------------------|--------------|---------|---------------------------------|-----|-----------|

| - Cymbol              | i didirecei                                            | Min          | Max     | Min                             | Max |           |

| T <sub>AVRL</sub> (2) | Address Valid to RD#/PSEN# Low<br>@ 12 MHz<br>@ 16 MHz | 126.6<br>85  |         | 2(1+M)<br>T <sub>OSC</sub> - 40 |     | ns<br>(3) |

| T <sub>AVWL1</sub>    | Address (P0) Valid to WR # Low<br>@ 12 MHz<br>@ 16 MHz | 126.6<br>85  |         | 2(1+M)<br>T <sub>OSC</sub> - 40 |     | ns<br>(3) |

| T <sub>AVWL2</sub>    | Address (P2) Valid to WR # Low<br>@ 12 MHz<br>@ 16 MHz | 141.6<br>100 |         | 2(1+M)<br>T <sub>OSC</sub> -25  |     | ns<br>(3) |

| T <sub>WHQX</sub>     | Data Hold after WR # High<br>@ 12 MHz<br>@ 16 MHz      | 58.3<br>37.5 |         | T <sub>OSC</sub> - 25           |     | ns        |

| T <sub>QVWH</sub>     | Data Valid to WR # High<br>@ 12 MHz<br>@ 16 MHz        | 146.6<br>105 |         | 2(1+N)<br>T <sub>OSC</sub> - 20 |     | ns<br>(4) |

| T <sub>WHAX</sub>     | WR# High to Address Hold<br>@ 12 MHz<br>@ 16 MHz       | 146.6<br>105 |         | 2T <sub>OSC</sub> - 20          |     | ns        |

- 1. 16 MHz.

- 2. Specifications for PSEN# are identical to those for RD#.

- 3. In the formula, M = Number of wait states (0 or 1) for ALE.

- 4. In the formula, N=Number of wait states (0, 1, 2, or 3) for RD#/PSEN#/WR#.

- 5. "Typical" specifications are untested and not guaranteed.

# SYSTEM BUS TIMINGS

Figure 6. External Read Data Bus Cycle in Nonpage Mode

Figure 7. External Instruction Bus Cycle in Nonpage Mode

Figure 8. External Write Data Bus Cycle in Nonpage Mode

Figure 9. External Read Data Bus Cycle in Page Mode

Figure 10. External Write Data Bus Cycle in Page Mode

Figure 11. External Instruction Bus Cycle in Page Mode

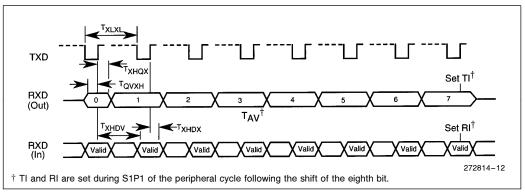

# AC Characteristics—Serial Port, Shift Register Mode

Table 10. Serial Port Timing Shift Register Mode

| Symbol            | Parameter                                | Min                      | Max                      | Units |

|-------------------|------------------------------------------|--------------------------|--------------------------|-------|

| T <sub>XLXL</sub> | Serial Port Clock Cycle Time             | 12T <sub>OSC</sub>       |                          | ns    |

| T <sub>QVSH</sub> | Output Data Setup to Clock Rising Edge   | 10T <sub>OSC</sub> - 133 |                          | ns    |

| T <sub>XHQX</sub> | Output Data Hold after Clock Rising Edge | 2T <sub>OSC</sub> - 117  |                          | ns    |

| T <sub>XHDX</sub> | Input Data Hold after Clock Rising Edge  | 0                        |                          | ns    |

| T <sub>XHDV</sub> | Clock Rising Edge to Input Data Valid    |                          | 10T <sub>OSC</sub> - 133 | ns    |

Figure 12. Serial Port Waveform —Shift Register Mode

# **External Clock Drive**

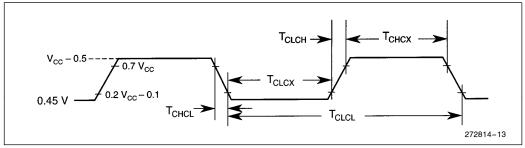

**Table 11. External Clock Drive**

| Symbol              | Parameter                                | Min | Max | Units |

|---------------------|------------------------------------------|-----|-----|-------|

| 1/T <sub>CLCL</sub> | Oscillator Frequency (F <sub>OSC</sub> ) |     | 16  | MHz   |

| T <sub>CHCX</sub>   | High Time                                | 20  |     | ns    |

| T <sub>CLCX</sub>   | Low Time                                 | 20  |     | ns    |

| T <sub>CLCH</sub>   | Rise Time                                |     | 10  | ns    |

| T <sub>CHCL</sub>   | Fall Time                                |     | 10  | ns    |

Figure 13. External Clock Drive Waveforms

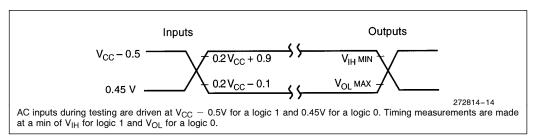

Figure 14. AC Testing Input, Output Waveforms

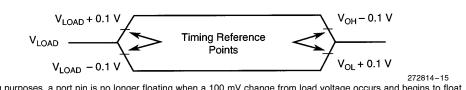

For timing purposes, a port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loading  $V_{OH}/V_{OL}$  level occurs with  $I_{OL}/I_{OH}=\pm20$  mA.

Figure 15. Float Waveforms

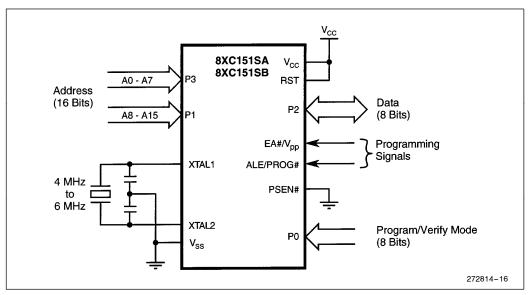

Figure 16. Setup for Programming and Verifying Nonvolatile Memory

# PROGRAMMING AND VERIFYING NONVOLATILE MEMORY

The 87C151SA/SB has several areas of nonvolatile memory that can be programmed and/or verified: on-chip code memory (8/16 Kbytes), lock bits (3 bits), encryption array (128 bytes), and signature bytes (3 bytes).

Figure 16 shows the setup for programming and/or verifying the nonvolatile memory. Table 11 lists the programming and verification operations and indicates which operations apply to the different versions of the 87C151SA/SB. It also specifies the signals on the programming input (PROG#) and the ports. The ROM/OTPROM mode (port 0) specifies the operation (program or verify) and the base address of the memory area. The addresses (ports 1 and 3) are relative to the base address. (On-chip memory for a 16-Kbyte ROM/OTPROM device is located at address range 0000H–3FFFH. The other areas of the ROM/OTPROM are outside the memory address space and are accessible only during programming and verification.)

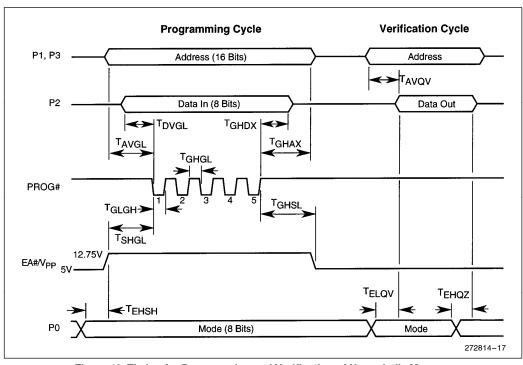

Information in Figures 17 and 18 define the configuration bits. Figure 19 shows the waveforms for the programming and verification cycles, and Table 12 lists the timing specifications. The signature bytes of the 83C151SA/SB ROM versions and the 87C151SA/SB OTPROM versions are factory programmed. Table 13 lists the addresses and the contents of the signature bytes.

Factory-programmed ROM and OTPROM versions of 8XC151SA/SB use configuration byte information supplied in a separate hexadecimal disk file. 8XC151SA/SB devices without internal ROM/OTPROM arrays fetch configuration byte information from external application memory based on an internal address range of FFF9:8H.

#### NOTE:

The V<sub>PP</sub> source in Figure 16 must be well regulated and free of glitches. The voltage on the V<sub>PP</sub> pin must not exceed the specified maximum, even under transient conditions.

Table 12. Programming and Verification Modes Mode

| Mode                           | 8XC151SA/SB |       | PROG#     | P0  | P2   | Addresses<br>P1 (high), P3 (low)      | Notes |

|--------------------------------|-------------|-------|-----------|-----|------|---------------------------------------|-------|

|                                | X = 7       | X = 3 |           |     |      | (9), ()                               |       |

| Program On-Chip Code<br>Memory | Υ           |       | 5 Pulses  | 68H | Data | 0000H-3FFFH (16K)<br>0000H-1FFFH (8K) | 1     |

| Verify On-Chip Code<br>Memory  | Υ           | Υ     | High      | 28H | Data | 0000H-3FFFH (16K)<br>0000H-1FFFH (8K) |       |

| Program Configuration<br>Bytes |             |       |           |     |      |                                       | 2     |

| Verify Configuration<br>Bytes  |             |       |           |     |      |                                       | 2     |

| Program Lock Bits              | Υ           |       | 25 Pulses | 6BH | XX   | 0001H-0003H                           | 1, 3  |

| Verify Lock Bits               | Υ           | Υ     | High      | 2BH | Data | 0000H                                 | 4     |

| Program Encryption<br>Array    | Y           |       | 25 Pulses | 6CH | Data | 0000H-007FH                           | 1     |

| Verify Signature Bytes         | Υ           | Υ     | High      | 29H | Data | 0030H, 0031H, 0060H                   |       |

- 1. The PROG# pulse waveform is shown in Figure 19.

- 2. Factory-programmed ROM and OTPROM versions of 8XC151SA/SB use configuration byte information supplied in a separate hexadecimal disk file. 8XC151SA/SB devices without internal ROM/OTPROM arrays fetch configuration byte information from external application memory based on an internal address range of FFF9:8H.

- 3. When programming the lock bits, the data bits on port 2 are don't care. Identify the lock bits with the address as follows: LB3 0003H, LB2 0002H, LB1 0001H.

- 4. The three lock bits are verified in a single operation. The states of the lock bits appear simultaneously at port 2 as follows: LB3 P2.3, LB2 P2.2, LB1 P2.1, High = programmed.

| UCONFIG0 |   |       |       |       |   | Addres | ss FFF8H |   |  |

|----------|---|-------|-------|-------|---|--------|----------|---|--|

|          | 7 |       |       |       |   |        |          | 0 |  |

|          | _ | WSA1# | WSA0# | XALE# | _ | _      | PAGE#    | _ |  |

| Bit<br>Number | Bit<br>Mnemonic | Function                                                                                                                                                                                                                                                                                                                                                                                                               |       |                      |  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------|--|

| 7             | _               | Reserved                                                                                                                                                                                                                                                                                                                                                                                                               |       |                      |  |

| 6:5           | WSA1#           | Wait State Select for external code                                                                                                                                                                                                                                                                                                                                                                                    |       |                      |  |

|               | WSA0#           | WSA1#                                                                                                                                                                                                                                                                                                                                                                                                                  | WSA0# | Description          |  |

|               | (see Note)      | 1                                                                                                                                                                                                                                                                                                                                                                                                                      | 1     | No wait states       |  |

|               |                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                      | 0     | Insert 1 wait state  |  |

|               |                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                      | 1     | Insert 2 wait states |  |

|               |                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                      | 0     | Insert 3 wait states |  |

| 4             | XALE#           | Extend Ale:  If this bit is set, the time of the ALE pulse is T <sub>OSC</sub> . Clearing this bit extends the time of the ALE pulse from T <sub>OSC</sub> to 3T <sub>OSC</sub> , which adds one external wait state.  Page Mode Select:  Clear this bit for page-mode (A15:8/D7:0 on P2, and A7:0 on P0). Set this bit for nonpage-mode (A15:8 on P2, and A7:0/D7:0 on P0 (compatible with MCS 51 microcontrollers)). |       |                      |  |

| 1             | PAGE#           |                                                                                                                                                                                                                                                                                                                                                                                                                        |       |                      |  |

#### NOTE

Factory-programmed ROM and OTPROM versions of 8XC151SA/SB use configuration byte information supplied in a separate hexadecimal disk file. 8XC151SA/SB devices without internal ROM/OTPROM arrays fetch configuration byte information from external application memory based on an internal address range of FFF9:8H.

Figure 17. Configuration Byte 0

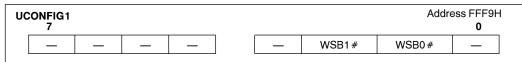

| Bit<br>Number | Bit<br>Mnemonic | Function                                       |                        |                        |

|---------------|-----------------|------------------------------------------------|------------------------|------------------------|

| 7:5           | _               | Reserved; set these bits when writing to UCONF |                        |                        |

| 2:1           | WSB1#,<br>WSB0# | Wait State<br>WSB1#                            | es for extern<br>WSB0# | al data<br>Description |

|               |                 | 1                                              | 1                      | No wait states         |

|               |                 | 1                                              | 0                      | Insert 1 wait state    |

|               |                 | 0                                              | 1                      | Insert 2 wait states   |

|               |                 | 0                                              | 0                      | Insert 3 wait states   |

#### NOTE:

Factory-programmed ROM and OTPROM versions of 8XC151SA/SB use configuration byte information supplied in a separate hexadecimal disk file. 8XC151SA/SB devices without internal ROM/OTPROM arrays fetch configuration byte information from external application memory based on an internal address range of FFF9:8H.

Figure 18. Configuration Byte 1

Figure 19. Timing for Programming and Verification of Nonvolatile Memory

Table 13. Nonvolatile Memory Programming and Verification Characteristics at  $T_A=21-27^{\circ}C,\,V_{CC}=5V,\,\text{and}\,\,V_{SS}=0V$

| Symbol            | Definition                         | Min                | Max                | Units      |

|-------------------|------------------------------------|--------------------|--------------------|------------|

| V <sub>PP</sub>   | Programming Supply Voltage         | 12.5               | 13.5               | D.C. Volts |

| I <sub>PP</sub>   | Programming Supply Current         |                    | 75                 | mA         |

| Fosc              | Oscillator Frequency               | 4.0                | 6.0                | MHz        |

| T <sub>AVGL</sub> | Address Setup to PROG # Low        | 48T <sub>OSC</sub> |                    |            |

| T <sub>GHAX</sub> | Address Hold after PROG#           | 48T <sub>OSC</sub> |                    |            |

| T <sub>DVGL</sub> | Data Setup to PROG # Low           | 48T <sub>OSC</sub> |                    |            |

| T <sub>GHDX</sub> | Data Hold after PROG#              | 48T <sub>OSC</sub> |                    |            |

| T <sub>EHSH</sub> | ENABLE High to V <sub>PP</sub>     | 48T <sub>OSC</sub> |                    |            |

| T <sub>SHGL</sub> | V <sub>PP</sub> Setup to PROG# Low | 10                 |                    | μs         |

| T <sub>GHSL</sub> | V <sub>PP</sub> Hold after PROG#   | 10                 |                    | μs         |

| T <sub>GLGH</sub> | PROG# Width                        | 90                 | 110                | μs         |

| T <sub>AVQV</sub> | Address to Data Valid              |                    | 48T <sub>OSC</sub> |            |

| T <sub>ELQV</sub> | ENABLE Low to Data Valid           |                    | 48To <sub>SC</sub> |            |

| T <sub>EHQZ</sub> | Data Float after ENABLE            | 0                  | 48T <sub>OSC</sub> |            |

| T <sub>GHGL</sub> | PROG# High to PROG# Low            | 10                 |                    | μs         |

#### NOTE:

Notation for timing parameters:

$A = Address \qquad D = Data \qquad \qquad E = Enable \qquad G = PROG\# \qquad \qquad H = High \qquad L = Low$

$Q = Data \ out \qquad S = Supply \ (V_{PP}) \qquad V = Valid \qquad \quad X = No \ Longer \ Valid \qquad \quad Z = Floating$

#### Table 14. Contents of the Signature Bytes

| ADDRESS | CONTENTS | DEVICE TYPE                    |  |  |

|---------|----------|--------------------------------|--|--|

| 30H     | 89H      | Indicates Intel Devices        |  |  |

| 31H     | 48H      | Indicates MCS 151 core product |  |  |

| 60H     | 7BH      | Indicates 83C151SB device      |  |  |

| 60H     | FBH      | Indicates 87C151SB device      |  |  |

| 60H     | 7AH      | Indicates 83C151SA device      |  |  |

| 60H     | FAH      | Indicates 87C151SA device      |  |  |