TUSB7320, TUSB7340 SLLSE76Q - MARCH 2011 - REVISED MARCH 2024

# TUSB73x0 USB 3.0 xHCl Host Controller

#### 1 Features

- USB 3.0-Compliant xHCI host controller

- PCle x1 Gen2 interface

- Four downstream ports

- Two or four downstream ports

- Each downstream port

- May be independently enabled or disabled

- Has adjustments for transmit swing, deemphasis, and equalization settings

- May be marked as removable or nonremovable

- Has independent power control and overcurrent detection

- Requires no external flash for default configuration

- Optional serial EEPROM for custom configuration

- Internal spread spectrum generation

- Low-cost crystal or oscillator support

- Best-in-class adaptive receiver equalizer design

## 2 Applications

- Rack server, microserver, and tower server

- High performance computing

- Storage area network (SAN) and host bus adapter (HBA) card

- Desktop PC or motherboard

## 3 Description

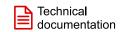

The TUSB7320 supports up to two downstream ports. The TUSB7340 is a USB 3.0-compliant xHCl host controller that supports up to four downstream ports. Both parts are available in a pin-compatible 100-pin RKM package. For the remainder of this document, the name TUSB73x0 is used to reference both the TUSB7320 and the TUSB7340.

The TUSB73x0 interfaces to the host system through a PCle x1 Gen 2 interface and provides SuperSpeed, high-speed, full-speed, or low-speed connections on the downstream USB ports.

#### **Device Information**

| PART NUMBER <sup>(1)</sup> | USB PORT COUNT | PACKAGE              |

|----------------------------|----------------|----------------------|

| TUSB7320                   | 2-port         | (WQFN-MR, 100)       |

| TUSB7340                   | 4-port         | (VVQI-IV-IVIIX, 100) |

For all available packages, see the orderable addendum at the end of the data sheet.

**Typical Application**

# **Table of Contents**

| 1 Features                               | 1  | 7.2 Typical Application                             | 24    |

|------------------------------------------|----|-----------------------------------------------------|-------|

| 2 Applications                           | 1  | 7.3 Power Supply Recommendations                    | 31    |

| 3 Description                            | 1  | 7.4 Layout                                          | 32    |

| 4 Pin Configuration and Functions        |    | 8 Register Maps                                     |       |

| 5 Specifications                         |    | 8.1 Classic PCI Configuration Space                 | 35    |

| 5.1 Absolute Maximum Ratings             | 9  | 8.2 PCI Express Extended Configuration Space        | 75    |

| 5.2 ESD Ratings                          | 9  | 8.3 xHCl Memory Mapped Register Space               | 84    |

| 5.3 Recommended Operating Conditions     | 9  | 8.4 MSI-X Memory Mapped Register Space              | 108   |

| 5.4 Thermal Information                  | 10 | 8.5 The MSI-X Table and PBA in Memory Mapped        |       |

| 5.5 3.3-V I/O Electrical Characteristics | 10 | Register Space                                      | 109   |

| 5.6 Input Clock Specification            | 10 | 9 Device and Documentation Support                  | 111   |

| 5.7 Input Clock 1.8-V DC Characteristics | 12 | 9.1 Device Support                                  | 111   |

| 5.8 Crystal Specification                | 12 | 9.2 Documentation Support                           | 111   |

| 5.9 TUSB7320 Power Consumption           | 12 | 9.3 Receiving Notification of Documentation Updates | s 111 |

| 5.10 TUSB7340 Power Consumption          | 13 | 9.4 Support Resources                               | 112   |

| 6 Detailed Description                   | 14 | 9.5 Trademarks                                      | 112   |

| 6.1 Overview                             | 14 | 9.6 Electrostatic Discharge Caution                 | 112   |

| 6.2 Functional Block Diagram             | 14 | 9.7 Glossary                                        |       |

| 6.3 Feature Description                  | 15 | 10 Revision History                                 | 112   |

| 6.4 Programming                          | 18 | 11 Mechanical, Packaging, and Orderable             |       |

| 7 Application and Implementation         | 23 | Information                                         | 113   |

| 7.1 Application Information              |    |                                                     |       |

## 4 Pin Configuration and Functions

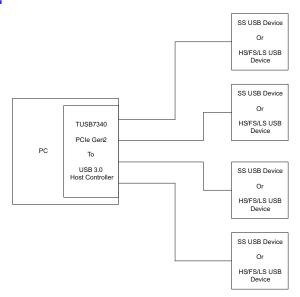

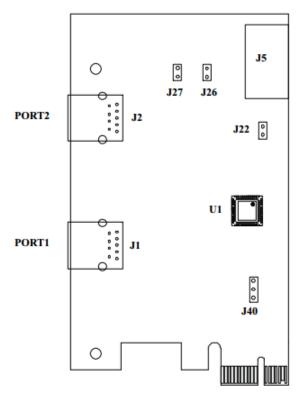

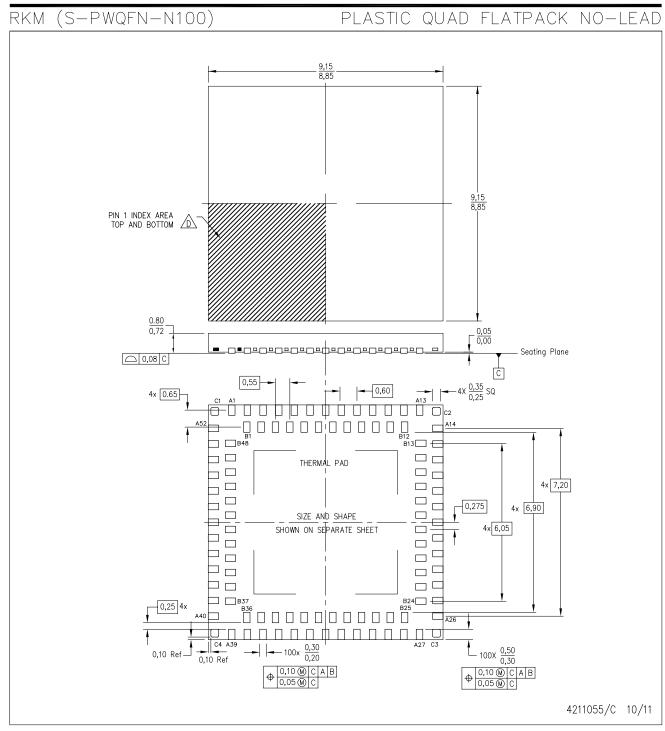

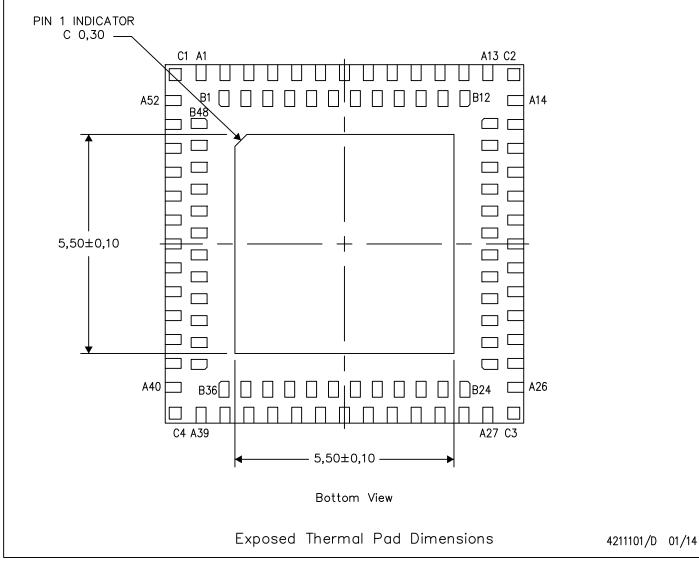

Figure 4-1. RKM Package, 100-Pin WQFN-MR Exposed Thermal Pad TUSB7320 (Top View)

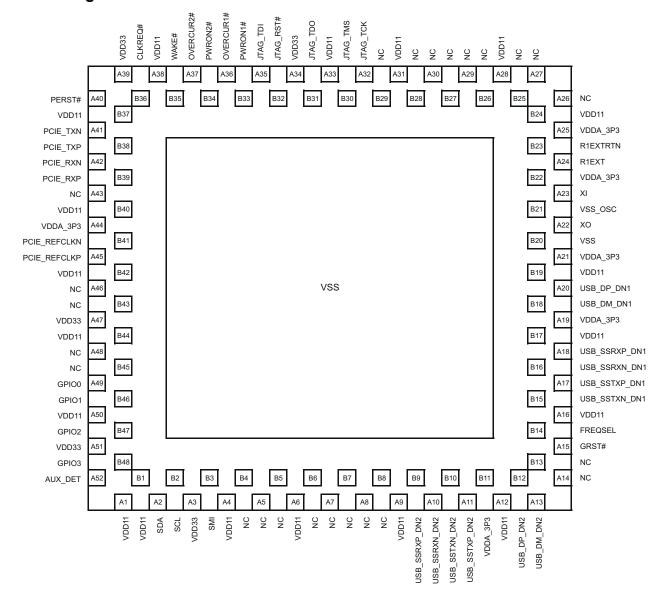

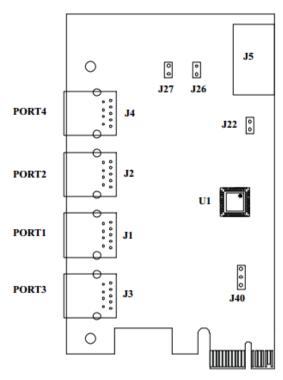

Figure 4-2. RKM Package, 100-Pin WQFN-MR Exposed Thermal Pad TUSB7340 (Top View)

The following tables give a description of the terminals. These terminals are grouped in tables by functionality. Each table includes the terminal name, terminal number, I/O type, and terminal description.

| TYPE   | DESCRIPTION               |

|--------|---------------------------|

| 1      | Input                     |

| 0      | Output                    |

| I/O    | Input/Output              |

| PD, PU | Internal pull-down/pullup |

| S      | Strapping pin             |

| Р      | Power supply              |

| G      | Ground                    |

Submit Document Feedback

Copyright © 2024 Texas Instruments Incorporated

Table 4-1. Clock and Reset Signals

|                        |           | I        | able 4- | 1. Clock and Reset Signals                                                                                                                                                                                                                                                                                                                                                               |

|------------------------|-----------|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | PIN       |          | TYPE    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                              |

| NAME                   | TUSB7320  | TUSB7340 |         |                                                                                                                                                                                                                                                                                                                                                                                          |

| CLOCK AND RESE         | T SIGNALS |          |         |                                                                                                                                                                                                                                                                                                                                                                                          |

| GRST#                  | A15       | A15      | IPU     | Global power reset. This reset brings all of the TUSB73x0 internal registers to their default states. When GRST# is asserted, the device is completely nonfunctional. GRST# should be asserted until all power rails are valid at the device. If a 24 MHz or 48 MHz reference clock is used instead of a crystal, GRST# must remain asserted until the 24 MHz or 48 MHz clock is stable. |

| ΧI                     | A23       | A23      | I       | Crystal input. This terminal is the crystal input for the internal oscillator. The input may alternately be driven by the output of an external oscillator. When using a crystal a 2-M $\Omega$ feedback resistor is required between XI and XO.                                                                                                                                         |

| XO                     | A22       | A22      | 0       | Crystal output. This terminal is crystal output for the internal oscillator. If XI is driven by an external oscillator this pin may be left unconnected. When using a crystal a 2-M $\Omega$ feedback resistor is required between XI and XO.                                                                                                                                            |

| FREQSEL                | B14       | B14      | I       | Frequency select. This terminal indicates the oscillator input frequency and is used to configure the correct PLL multiplier. This pin should be set low for normal operation.                                                                                                                                                                                                           |

| PCIE_REFCLKP           | A45       | A45      | I       | PCI Express Reference Clock. PCIE_REFCLKP and PCIE_REFCLKN comprise the differential input pair for the 100-MHz system reference clock.                                                                                                                                                                                                                                                  |

| PCIE_REFCLKN           | B41       | B41      | I       |                                                                                                                                                                                                                                                                                                                                                                                          |

| PERST#                 | A40       | A40      | I       | PCI Express Reset Input. The PERST# signal is used to signal when the system power is stable. The PERST# signal is also used to generate an internal power on reset                                                                                                                                                                                                                      |

| PCI EXPRESS<br>SIGNALS |           |          |         |                                                                                                                                                                                                                                                                                                                                                                                          |

| PCIE_TXP               | B38       | B38      | 0       | PCI Express transmitter differential pair (positive).                                                                                                                                                                                                                                                                                                                                    |

| PCIE_TXN               | A41       | A41      | 0       | PCI Express transmitter differential pair (negative).                                                                                                                                                                                                                                                                                                                                    |

| PCIE_RXP               | B39       | B39      | I       | PCI Express receiver differential pair (positive).                                                                                                                                                                                                                                                                                                                                       |

| PCIE_RXN               | A42       | A42      | I       | PCI Express receiver differential pair (negative).                                                                                                                                                                                                                                                                                                                                       |

| WAKE#                  | B35       | B35      | 0       | Wake. Wake is an active low signal that is driven low to reactivate the PCI Express link hierarchy's main power rails and reference clocks. Note: WAKE# is not a failsafe I/O and should not be connected to a 3.3-V auxiliary supply while VDD33 is not present.                                                                                                                        |

| CLKREQ#                | B36       | B36      | 0       | PCI Express REFCLK Request signal. Note: CLKREQ# is not a failsafe I/O and should not be connected to a 3.3-V auxiliary supply while VDD33 is not present.                                                                                                                                                                                                                               |

| USB DOWNSTREA          | M SIGNALS | •        |         |                                                                                                                                                                                                                                                                                                                                                                                          |

| USB_SSTXP_DN1          | A17       | A17      | 0       | USB SuperSpeed transmitter differential pair (positive). Note: When routing, it is permissible to swap the positive and negative signals in Port 1 SSTX differential pair.                                                                                                                                                                                                               |

| USB_SSTXN_DN1          | B15       | B15      | 0       | USB SuperSpeed transmitter differential pair (negative). Note: When routing, it is permissible to swap the positive and negative signals in Port 1 SSTX differential pair.                                                                                                                                                                                                               |

| USB_SSRXP_DN1          | A18       | A18      | I       | USB SuperSpeed receiver differential pair (positive). Note: When routing, it is permissible to swap the positive and negative signals in Port 1 SSRX differential pair.                                                                                                                                                                                                                  |

| USB_SSRXN_DN1          | B16       | B16      | I       | USB SuperSpeed receiver differential pair (negative). Note: When routing, it is permissible to swap the positive and negative signals in Port 1 SSRX differential pair.                                                                                                                                                                                                                  |

| USB_DP_DN1             | A20       | A20      | I/O     | USB High-speed differential transceiver (positive).                                                                                                                                                                                                                                                                                                                                      |

| USB_DM_DN1             | B18       | B18      | I/O     | USB High-speed differential transceiver (negative).                                                                                                                                                                                                                                                                                                                                      |

| PWRON1#                | B33       | B33      | O PD    | USB DS Port 1 Power On Control for Downstream Power. The terminal is used to control the downstream power switch. If the PWRON_POLARITY bit is set to 1, this pin is active high and the internal pull-down is disabled. This pin may be a low impedance when power rails are removed.                                                                                                   |

| OVERCUR1#              | A36       | A36      | I PU    | USB DS Port 1 Overcurrent Detection. 0: overcurrent detected; 1: overcurrent not detected                                                                                                                                                                                                                                                                                                |

## **Table 4-1. Clock and Reset Signals (continued)**

|               | PIN      |          |      | Description                                                                                                                                                                                                                                                                                 |  |  |

|---------------|----------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME          | TUSB7320 | TUSB7340 | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                 |  |  |

| USB_SSTXP_DN2 | A11      | A11      | 0    | USB SuperSpeed transmitter differential pair (positive). Note: When routing, it is permissible to swap the positive and negative signals in Port 2 SSTX differential pair.                                                                                                                  |  |  |

| USB_SSTXN_DN2 | B10      | B10      | 0    | USB SuperSpeed transmitter differential pair (negative). Note: When routing, it is permissible to swap the positive and negative signals in Port 2 SSTX differential pair.                                                                                                                  |  |  |

| USB_SSRXP_DN2 | В9       | В9       | I    | USB SuperSpeed receiver differential pair (positive). Note: When routing, it is permissible to swap the positive and negative signals in Port 2 SSRX differential pair.                                                                                                                     |  |  |

| USB_SSRXN_DN2 | A10      | A10      | I    | USB SuperSpeed receiver differential pair (negative). Note: When routing, it is permissible to swap the positive and negative signals in Port 2 SSRX differential pair.                                                                                                                     |  |  |

| USB_DP_DN2    | B12      | B12      | I/O  | USB High-speed differential transceiver (positive).                                                                                                                                                                                                                                         |  |  |

| USB_DM_DN2    | A13      | A13      | I/O  | USB High-speed differential transceiver (negative).                                                                                                                                                                                                                                         |  |  |

| PWRON2#       | B34      | B34      | O PD | USB DS Port 2 Power On Control for Downstream Power. The terminal is used for control of the downstream power switch. If the PWRON_POLARITY bit is set to 1, this pin is active high and the internal pull-down is disabled. This pin may be at low impedance when power rails are removed. |  |  |

| OVERCUR2#     | A37      | A37      | I PU | USB DS Port 2 Overcurrent Detection. 0: overcurrent detected; 1: overcurrent not detected                                                                                                                                                                                                   |  |  |

| USB_SSTXP_DN3 | _        | B28      | 0    | permissible to swap the positive and negative signals in Port 3 SSTX different pair.                                                                                                                                                                                                        |  |  |

| USB_SSTXN_DN3 | _        | A30      | 0    | O USB SuperSpeed transmitter differential pair (negative). Note: When routing permissible to swap the positive and negative signals in Port 3 SSTX differe pair.                                                                                                                            |  |  |

| USB_SSRXP_DN3 | _        | B27      | I    | USB SuperSpeed receiver differential pair (positive). Note: When routing, it is permissible to swap the positive and negative signals in Port 3 SSRX differential pair.                                                                                                                     |  |  |

| USB_SSRXN_DN3 | _        | A29      | I    | USB SuperSpeed receiver differential pair (negative). Note: When routing, it is permissible to swap the positive and negative signals in Port 3 SSRX differential pair.                                                                                                                     |  |  |

| USB_DP_DN3    | _        | B25      | I/O  | USB High-speed differential transceiver (positive).                                                                                                                                                                                                                                         |  |  |

| USB_DM_DN3    | _        | A27      | I/O  | USB High-speed differential transceiver (negative).                                                                                                                                                                                                                                         |  |  |

| PWRON3#       | _        | A46      | O PD | USB DS Port 3 Power On Control for Downstream Power. The terminal is used for control of the downstream power switch. If the PWRON_POLARITY bit is set to 1, this pin is active high and the internal pull-down is disabled. This pin may be at low impedance when power rails are removed. |  |  |

| OVERCUR3#     | _        | B43      | I PU | USB DS Port 3 Overcurrent Detection. 0: overcurrent detected; 1: overcurrent not detected                                                                                                                                                                                                   |  |  |

| USB_SSTXP_DN4 | _        | В7       | 0    | USB SuperSpeed transmitter differential pair (positive). Note: When routing, it is permissible to swap the positive and negative signals in Port 4 SSTX differential pair.                                                                                                                  |  |  |

| USB_SSTXN_DN4 | _        | A8       | 0    | USB SuperSpeed transmitter differential pair (negative). Note: When routing, it is permissible to swap the positive and negative signals in Port 4 SSTX differential pair.                                                                                                                  |  |  |

| USB_SSRXP_DN4 | _        | В6       | I    | USB SuperSpeed receiver differential pair (positive). Note: When routing, it is permissible to swap the positive and negative signals in Port 4 SSRX differential pair.                                                                                                                     |  |  |

| USB_SSRXN_DN4 | _        | A7       | I    | USB SuperSpeed receiver differential pair (negative). Note: When routing, it is permissible to swap the positive and negative signals in Port 4 SSRX differential pair.                                                                                                                     |  |  |

| USB_DP_DN4    | _        | B5       | I/O  | USB High-speed differential transceiver (positive).                                                                                                                                                                                                                                         |  |  |

| USB_DM_DN4    | _        | A5       | I/O  | USB High-speed differential transceiver (negative).                                                                                                                                                                                                                                         |  |  |

Table 4-1. Clock and Reset Signals (continued)

|                | PIN                                                                                                                                          |                                                |        | ck and Reset Signals (continued)                                                                                                                                                                                                                                                            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME           | TUSB7320                                                                                                                                     | TUSB7340                                       | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                 |

| PWRON4#        | _                                                                                                                                            | A48                                            | O PD   | USB DS Port 4 Power On Control for Downstream Power. The terminal is used for control of the downstream power switch. If the PWRON_POLARITY bit is set to 1, this pin is active high and the internal pull-down is disabled. This pin may be at low impedance when power rails are removed. |

| OVERCUR4#      | _                                                                                                                                            | B45                                            | IPU    | USB DS Port 4 Overcurrent Detection. 0: overcurrent detected; 1: overcurrent not detected                                                                                                                                                                                                   |

| I2C SIGNALS    |                                                                                                                                              |                                                |        |                                                                                                                                                                                                                                                                                             |

| SCL            | B2                                                                                                                                           | B2                                             | I/O    | I2C Clock – If no I2C device is present, pull this line down to disable.                                                                                                                                                                                                                    |

| SDA            | A2                                                                                                                                           | A2                                             | I/O    | I2C Data – If no I2C device is present, pull this line down to disable.                                                                                                                                                                                                                     |

| TEST AND MISCE | LLANEOUS SI                                                                                                                                  | GNALS                                          |        |                                                                                                                                                                                                                                                                                             |

| JTAG_TCK       | A32                                                                                                                                          | A32                                            | I PD   | JTAG test clock                                                                                                                                                                                                                                                                             |

| JTAG_TDI       | A35                                                                                                                                          | A35                                            | I PU   | JTAG test data in                                                                                                                                                                                                                                                                           |

| JTAG_TDO       | B31                                                                                                                                          | B31                                            | O PD   | JTAG test data out                                                                                                                                                                                                                                                                          |

| JTAG_TMS       | B30                                                                                                                                          | B30                                            | I PU   | JTAG test mode select                                                                                                                                                                                                                                                                       |

| JTAG_RST#      | B32                                                                                                                                          | B32                                            | I PD   | JTAG reset. Should be pulled low for normal operation.                                                                                                                                                                                                                                      |

| GPIO0          | A49                                                                                                                                          | A49                                            | I/O PU | General purpose I/O                                                                                                                                                                                                                                                                         |

| GPIO1          | B46                                                                                                                                          | B46                                            | I/O PU |                                                                                                                                                                                                                                                                                             |

| GPIO2          | B47                                                                                                                                          | B47                                            | I/O PU |                                                                                                                                                                                                                                                                                             |

| GPIO3          | B48                                                                                                                                          | B48                                            | I/O PU |                                                                                                                                                                                                                                                                                             |

| SMI            | В3                                                                                                                                           | В3                                             | 0      | System management interrupt Note: This pin is active high and should not be pulled up/down.                                                                                                                                                                                                 |

| R1EXT          | A24                                                                                                                                          | A24                                            | OI     | High precision external resistor used for calibration. A resister value of 9.09 K $\Omega$ ±1% accuracy is connected between the terminals R1EXT and R1EXTRTN.                                                                                                                              |

| R1EXTRTN       | B23                                                                                                                                          | B23                                            | OI     |                                                                                                                                                                                                                                                                                             |

| AUX_DET        | A52                                                                                                                                          | A52                                            | I      | Auxiliary power detect. This pin indicates if the TUSB73X0 is enabled for wakeup from D3cold. Note: If this feature is implemented, AUX_DET must be pulled to VDD33 to prevent leakage.                                                                                                     |

| NC             | B4, A5, B5,<br>B6, A7, B7,<br>A8, B8, B13,<br>A14, B25,<br>A26, B26,<br>A27, B27,<br>B28, A29,<br>B29, A30,<br>A43, B43,<br>B45, A46,<br>A48 | A14, B8,<br>B13, A26,<br>B29, A43              | I/O    | Pins are not connected internally. Note: TUSB7320 pins B4 and B26 may be connected to VDDA_3P3 to support a dual-layout option with the TUSB7340.                                                                                                                                           |

| POWER SIGNALS  | 3                                                                                                                                            |                                                | ,      |                                                                                                                                                                                                                                                                                             |

| VDD33          | A3, A34,<br>A39, A47,<br>A51                                                                                                                 | A3, A34,<br>A39, A47,<br>A51                   | PWR    | 3.3-V I/O power rail                                                                                                                                                                                                                                                                        |

| VDDA_3P3       | B11, A19,<br>A21, A25,<br>B22, A44                                                                                                           | B4, B11,<br>A19, A21,<br>A25, B22,<br>B26, A44 | PWR    | 3.3-V analog power rail                                                                                                                                                                                                                                                                     |

## **Table 4-1. Clock and Reset Signals (continued)**

|         | PIN                                                                                                              |                                                                                                                  | TYPE | DESCRIPTION                                                                                                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | TUSB7320                                                                                                         | TUSB7340                                                                                                         | IIFE | DESCRIPTION                                                                                                                                                                                                            |

| VDD11   | A1, B1, A4,<br>A6, A9, A12,<br>A16, B17,<br>B19, B24,<br>A28, A33,<br>A31, A38,<br>B37, B40,<br>B42, B44,<br>A50 | A1, B1, A4,<br>A6, A9, A12,<br>A16, B17,<br>B19, B24,<br>A28, A33,<br>A31, A38,<br>B37, B40,<br>B42, B44,<br>A50 | PWR  | 1.1-V core power rail                                                                                                                                                                                                  |

| VSS     | B20, A53                                                                                                         | B20, A53                                                                                                         | PWR  | Ground. The ground pad is labeled A53 for schematic purposes.                                                                                                                                                          |

| VSS_NC  | C1, C2, C3,<br>C4                                                                                                | C1, C2, C3,<br>C4                                                                                                | PWR  | The corner pins, which are for mechanical stability of the package, are connected to ground internally. These pins may be connected to VSS or left unconnected.                                                        |

| VSS_OSC | B21                                                                                                              | B21                                                                                                              | PWR  | Oscillator return. If using a crystal, the load capacitors should use this signal as the return path and it should not be connected to the PCB ground. If using an oscillator, this should be connected to PCB Ground. |

## **5 Specifications**

See the PCIe and USB specifications referred to in the *Related Documentation* for the electrical characteristics of those interfaces.

## 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                     |                                   | MIN  | MAX         | UNIT |

|------------------|---------------------|-----------------------------------|------|-------------|------|

|                  |                     | VDD33                             | -0.5 | 3.6         | V    |

|                  | Supply voltage      | VDDA_3P3                          | -0.5 | 3.6         | V    |

|                  |                     | VDD11                             | -0.3 | 1.4         | V    |

| .,               | Input voltage       | PCI Express (RX)                  | 0    | 1.2         | V    |

|                  |                     | PCI Express REFCLK (single-ended) | -0.5 | VDD33 + 0.5 | V    |

| V <sub>I</sub>   |                     | REFCLK (differential)             | -0.3 | 1.15        | V    |

|                  |                     | Miscellaneous 3.3 V IO            | -0.5 | VDD33 + 0.5 | V    |

| ,                | 0 1 1 1             | PCI Express (TX)                  | 0.8  | 1.2         | V    |

| V <sub>O</sub>   | Output voltage      | Miscellaneous 3.3 V IO            | -0.5 | VDD33 + 0.5 | V    |

| T <sub>stg</sub> | Storage temperature | ,                                 | -65  | 150         | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 5.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±1500 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                      |                          | MIN   | NOM | MAX  | UNIT    |  |

|----------------|--------------------------------------|--------------------------|-------|-----|------|---------|--|

|                |                                      | VDD33                    | 3     | 3.3 | 3.6  | V       |  |

|                | Supply voltage range                 | VDDA_3P3                 | 3     | 3.3 | 3.6  | V       |  |

|                |                                      | VDD11 <sup>(1)</sup> (2) | 1.045 | 1.1 | 1.21 | V       |  |

| T <sub>A</sub> | Operating free-air temperature range |                          | 0     |     | 70   | °C      |  |

| 'A             | Operating free-all temperature range | Industrial version       | -40   |     | 85   |         |  |

| т              | Operating junction temperature range |                          | 0     |     | 105  | -l °C ∣ |  |

| TJ             | Operating junction temperature range | Industrial version       | -40   |     | 105  |         |  |

- (1) A 1.05-V supply may be used as long as the minimum supply conditions are met.

- (2) 1.1 V -5% / +10% supply is recommended.

#### **5.4 Thermal Information**

|                        |                                              | TUSB7320, TUSB7340 |      |

|------------------------|----------------------------------------------|--------------------|------|

|                        | THERMAL METRIC(1)                            | RKM (WQFN-MR)      | UNIT |

|                        |                                              | 100 PINS           |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 25.6               | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 9.5                | °C/W |

| R <sub>0JB</sub>       | Junction-to-board thermal resistance         | 15.2               | °C/W |

| Ψлт                    | Junction-to-top characterization parameter   | 0.1                | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 7.5                | °C/W |

| R <sub>0JC(bot)</sub>  | Junction-to-case (bottom) thermal resistance | 0.4                | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

#### 5.5 3.3-V I/O Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

| PARA             | METER                                                                                    | OPERATION | TEST CONDITIONS             | MIN | MAX        | UNIT |

|------------------|------------------------------------------------------------------------------------------|-----------|-----------------------------|-----|------------|------|

| V <sub>IH</sub>  | High-level input voltage <sup>(1)</sup>                                                  | VDD33     |                             | 2   | VDD33      | V    |

| V                | Low-level input voltage <sup>(1)</sup>                                                   | VDD33     |                             | 0   | 0.8        | V    |

| V <sub>IL</sub>  | Low-level input voitage                                                                  | VDD33     | JTAG pins only              | 0   | 0.55       | v    |

| VI               | Input voltage                                                                            |           |                             | 0   | VDD33      | V    |

| Vo               | Output voltage <sup>(2)</sup>                                                            |           |                             | 0   | VDD33      | V    |

| t <sub>t</sub>   | Input transition time ( $t_{rise}$ and $t_{fall}$ )                                      |           |                             | 0   | 25         | ns   |

| $V_{hys}$        | Input hysteresis <sup>(3)</sup>                                                          |           |                             |     | 0.13 VDD33 | V    |

| V <sub>OH</sub>  | High-level output voltage                                                                | VDD33     | I <sub>OH</sub> = −4 mA     | 2.4 |            | V    |

| V <sub>OL</sub>  | Low-level output voltage                                                                 | VDD33     | I <sub>OL</sub> = 4 mA      |     | 0.4        | V    |

| I <sub>OZ</sub>  | High-impedance, output current <sup>(2)</sup>                                            | VDD33     | V <sub>I</sub> = 0 to VDD33 |     | ±20        | μΑ   |

| I <sub>OZP</sub> | High-impedance, output current with internal pullup or pull-down resistor <sup>(4)</sup> | VDD33     | V <sub>I</sub> = 0 to VDD33 |     | ±225       | μА   |

| I <sub>I</sub>   | Input current <sup>(5)</sup>                                                             | VDD33     | V <sub>I</sub> = 0 to VDD33 |     | ±15        | μA   |

- (1) Applies to external inputs and bidirectional buffers.

- Applies to external outputs and bidirectional buffers. (2)

- (3) Applies to PERST, GRST, and PME.

- Applies to GRST (pullup) and most GPIO (pullup).

- Applies to external input buffers.

## 5.6 Input Clock Specification

See External Clock

| SOS External Glock.                                                    |                            |     |     |      |      |  |

|------------------------------------------------------------------------|----------------------------|-----|-----|------|------|--|

| PARAMETER                                                              | TEST CONDITIONS            | MIN | TYP | MAX  | UNIT |  |

| Frequency Tolerance                                                    | Operational<br>Temperature |     |     | ±50  | ppm  |  |

| Frequency Stability                                                    | 1 year aging               |     |     | ±100 | ppm  |  |

| Rise / Fall Time                                                       | 20% - 80%                  |     |     | 6    | ns   |  |

| Reference Clock R <sub>J</sub> with JTF (1 sigma) <sup>(1)</sup> (2)   |                            |     | 0.8 |      | ps   |  |

| Reference Clock T <sub>J</sub> with JTF (total p-p) <sup>(2) (3)</sup> |                            |     | 25  |      | ps   |  |

| Reference Clock Jitter (absolute p-p) <sup>(4)</sup>                   |                            |     | 50  |      | ps   |  |

- Sigma value assuming Gaussian distribution. (1)

- (2) After application of JTF.

- Calculated as 14.1 x R<sub>J</sub>+D<sub>J</sub>

(4) Absolute phase jitter (p-p)

# 5.7 Input Clock 1.8-V DC Characteristics

See External Clock.

| PARAMETER       | TEST CONDITION                                                                                             | MIN                    | TYP | MAX                   | UNIT |  |

|-----------------|------------------------------------------------------------------------------------------------------------|------------------------|-----|-----------------------|------|--|

| V <sub>IH</sub> | High-level input voltage                                                                                   | 0.65 V <sub>DDS</sub>  |     |                       | V    |  |

| V <sub>IL</sub> | Low-level input voltage                                                                                    |                        |     | 0.35 V <sub>DDS</sub> | V    |  |

| V               | I <sub>O</sub> = -2 mA, V <sub>DDS</sub> = 1.62 to 1.98 V,<br>driver enabled, pullup or pull-down disabled | V <sub>DDS</sub> -0.45 |     |                       |      |  |

| V <sub>OH</sub> | I <sub>O</sub> = -2 mA, V <sub>DDS</sub> = 1.4 to 1.6 V,<br>driver enabled, pullup or pull-down disabled   | 0.75 V <sub>DDS</sub>  |     |                       | V    |  |

| V               | I <sub>O</sub> = 2 mA, driver enabled, V <sub>DDS</sub> = 1.62 to 1.98 V, pullup or pull-down disabled     |                        |     | 0.45                  | V    |  |

| V <sub>OL</sub> | I <sub>O</sub> = 2 mA, V <sub>DDS</sub> = 1.4 to 1.6 V,<br>driver enabled, pullup or pull-down disabled    |                        |     | 0.25 V <sub>DDS</sub> | V    |  |

# 5.8 Crystal Specification

See External Crystal.

| PARAMETER           | TEST CONDITIONS         | MIN | TYP | MAX  | UNIT |

|---------------------|-------------------------|-----|-----|------|------|

| Frequency Tolerance | Operational Temperature |     | '   | ±50  | ppm  |

| Frequency Stability | 1 year aging            |     | '   | ±100 | ppm  |

| Load Capacitance    |                         | 12  |     | 24   | pF   |

| ESR                 |                         |     |     | 50   | Ω    |

# 5.9 TUSB7320 Power Consumption

|                                            | VCore<br>1.05 V |        | V I/O<br>3.3 V |        | TOTAL   |

|--------------------------------------------|-----------------|--------|----------------|--------|---------|

|                                            | mA              | mW     | mA             | mW     | mW      |

| ACTIVE STATES                              | •               |        |                |        |         |

| 2 SuperSpeed devices active <sup>(1)</sup> | 594             | 623.70 | 115            | 379.50 | 1003.20 |

| 1 SuperSpeed device active <sup>(1)</sup>  | 410             | 430.50 | 115            | 379.50 | 810.00  |

| POWER-MANAGEMENT STATES                    |                 |        |                |        |         |

| System on – device idle <sup>(2)</sup>     | 55              | 57.75  | 4              | 13.20  | 70.95   |

| System suspend                             | 55              | 57.75  | 4              | 13.20  | 70.95   |

| System hibernate                           | 55              | 57.75  | 4              | 13.20  | 70.95   |

<sup>(1)</sup> Device active indicates that connected devices are actively transferring data.

(2) No downstream devices are connected.

# 5.10 TUSB7340 Power Consumption

|                                            | =        | VCore<br>1.05 V |     | V I/O<br>3.3 V |         |

|--------------------------------------------|----------|-----------------|-----|----------------|---------|

|                                            | mA       | mW              | mA  | mW             | mW      |

| ACTIVE STATES                              |          |                 |     |                |         |

| 4 SuperSpeed devices active <sup>(1)</sup> | 880      | 924.00          | 115 | 379.50         | 1303.50 |

| 3 SuperSpeed devices active <sup>(1)</sup> | 740      | 777.00          | 115 | 379.50         | 1156.50 |

| 2 SuperSpeed devices active <sup>(1)</sup> | 597      | 626.85          | 115 | 379.50         | 1006.35 |

| 1 SuperSpeed devices active <sup>(1)</sup> | 420      | 441.00          | 115 | 379.50         | 820.50  |

| POWER-MANAGEMENT STATES                    | <u>'</u> |                 |     |                |         |

| System on – device idle <sup>(2)</sup>     | 63       | 66.15           | 4   | 13.20          | 79.35   |

| System suspend                             | 63       | 66.15           | 4   | 13.20          | 79.35   |

| System hibernate                           | 63       | 66.15           | 4   | 13.20          | 79.35   |

Device active indicates that connected devices are actively transferring data. (1)

<sup>(2)</sup> No downstream devices are connected.

## **6 Detailed Description**

## 6.1 Overview

The TUSB73x0 interfaces to the host system through a PCIe x1 Gen 2 interface and provides SuperSpeed, high-speed, full-speed, or low-speed connections on the downstream USB ports.

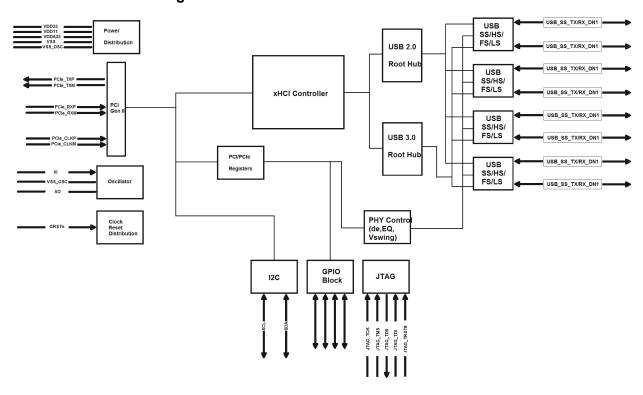

## **6.2 Functional Block Diagram**

Copyright © 2024 Texas Instruments Incorporated Product Folder Links: TUSB7320 TUSB7340

## **6.3 Feature Description**

#### 6.3.1 PHY Control

## 6.3.1.1 Output Voltage Swing Control

The output swing of each transmitter can be independently set to one of a number of settings through the SWING bits in the *De-Emphasis and Swing Control Register* section.

Reducing the output amplitude decreases the current drawn in direct proportion to the reduction in swing, thereby saving power.

**Table 6-1. Differential Output Swing**

| SWING VALUE | AC-COUPLED AMPLITUDE |

|-------------|----------------------|

| 0000        | 2.7                  |

| 0001        | 147                  |

| 0010        | 222                  |

| 0011        | 298                  |

| 0100        | 373                  |

| 0101        | 449                  |

| 0110        | 525                  |

| 0111        | 600                  |

| 1000        | 702                  |

| 1001        | 777                  |

| 1010        | 853                  |

| 1011        | 928                  |

| 1100        | 1050                 |

| 1101        | 1082                 |

| 1110        | 1164                 |

| 1111        | 1253                 |

#### 6.3.1.1.1 De-Emphasis Control

De-emphasis provides a means to compensate for high-frequency attenuation in the attached media. De-emphasis causes the output amplitude to be smaller for bits which are not preceded by a transition than for bits which are. Fifteen different de-emphasis settings are provided through the PORTx\_DE bits in *De-Emphasis and Swing Control Register*.

Table 6-2. Differential Output De-Emphasis

| VALUE | AMPLITUDE REDUCTION |        |  |

|-------|---------------------|--------|--|

|       | %                   | dB     |  |

| 0000  | 0                   | 0      |  |

| 0001  | 5.33                | -0.48  |  |

| 0010  | 9.52                | -0.87  |  |

| 0011  | 13.8                | -1.29  |  |

| 0100  | 18.1                | -1.73  |  |

| 0101  | 22.5                | -2.21  |  |

| 0110  | 27.0                | -2.73  |  |

| 0111  | 31.4                | -3.28  |  |

| 1000  | 36.2                | -3.9   |  |

| 1001  | 40.8                | -4.55  |  |

| 1010  | 45.4                | -5.26  |  |

| 1011  | 50.2                | -6.05  |  |

| 1100  | 55.0                | -6.93  |  |

| 1101  | 59.7                | -7.90  |  |

| 1110  | 64.5                | -8.99  |  |

| 1111  | 69.3                | -10.27 |  |

#### 6.3.1.2 Adaptive Equalizer

All receive channels in this macro family incorporate an adaptive equalizer, which can compensate for channel insertion loss by attenuating the low frequency components with respect to the high frequency components of the signal, thereby reducing inter-symbol interference.

The equalizer can be configured through the Portx\_EQ bits of the *Equalizer Control Register*. Table 6-3 summarizes the options, which are:

- No adaptive equalization. The equalizer provides a flat response at the maximum gain. This setting may

be appropriate if jitter at the receiver occurs predominantly as a result of crosstalk rather than frequency

dependent loss.

- Fully adaptive equalization. Both the low frequency gain and zero position of the equalizer are determined

algorithmically by analyzing the data patterns and transition positions in the received data. FTC refers to

the algorithm that controls the zero position. In the FTC normal mode, the zero is decreased in frequency

when more equalization is needed; in the FTC reversed mode, the zero is increased in frequency when more

equalization is needed. The fully adaptive with FTC reversed setting should be used for most applications.

- Hold. The equalizer state is held at its current gain level and zero point.

- *Initialize*. The equalizer is initialized to a mid-point gain level, with the zero set to a frequency appropriate for the receiver data rate.

- Partially adaptive equalization. The low frequency gain of the equalizer is determined algorithmically by analyzing the data patterns and transition positions in the received data. The zero position is fixed in one of eight zero positions. For any given application, the optimal setting is a function of the loss characteristics of the channel and the spectral density of the signal as well as the data rate, which means it is not possible to identify the best setting by data rate alone, although generally speaking, the lower the line rate, the lower the zero frequency that will be required.

When enabled, the receiver equalization logic analyzes data patterns and transition times to determine whether the low frequency gain of the equalizer should be increased or decreased. For the fully adaptive setting (**EQ** = 0001), if the low frequency gain reaches the minimum value, the zero frequency is then reduced. Likewise, if it reaches the maximum value, the zero frequency is then increased.

The decision logic is implemented as a voting algorithm with a relatively long analysis interval. The slow time constant that results reduces the probability of incorrect decisions but allows the equalizer to compensate for the relatively stable response of the channel.

Table 6-3. Receiver Equalizer Configuration

| AMPLITUDE REDUCTION |                     |                |  |  |

|---------------------|---------------------|----------------|--|--|

| EQ VALUE            | LOW-FREQUENCY GAIN  | ZERO FREQUENCY |  |  |

| 0000                | Maximum             | -              |  |  |

| 0001                | Fully Adaptive      | e, FTC Normal  |  |  |

| 0010                | Fully Adaptive,     | FTC Reversed   |  |  |

| 0011                | H                   | old            |  |  |

| 0100                |                     |                |  |  |

| 0101                | [:te                |                |  |  |

| 0110                |                     | alize          |  |  |

| 0111                |                     |                |  |  |

| 1000                |                     | 365 MHz        |  |  |

| 1001                |                     | 275 MHz        |  |  |

| 1010                |                     | 195 MHz        |  |  |

| 1011                | Dortically Adoptive | 140 MHz        |  |  |

| 1100                | Partially Adaptive  | 105 MHz        |  |  |

| 1101                |                     | 75 MHz         |  |  |

| 1110                | 55 MHz              |                |  |  |

| 1111                |                     | 50 MHz         |  |  |

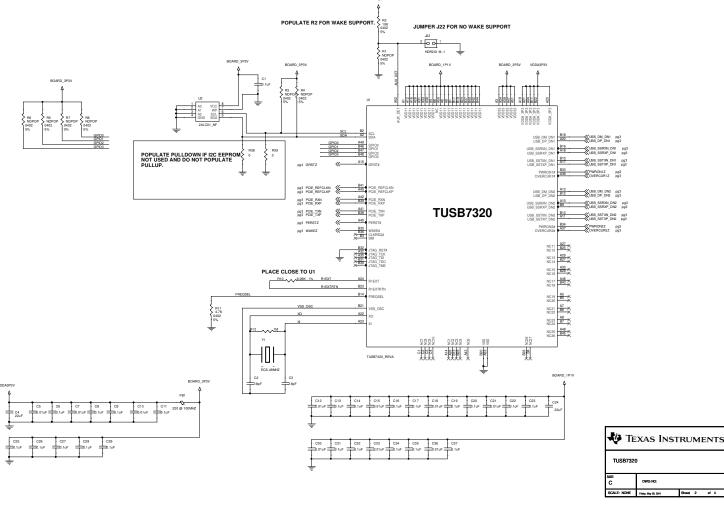

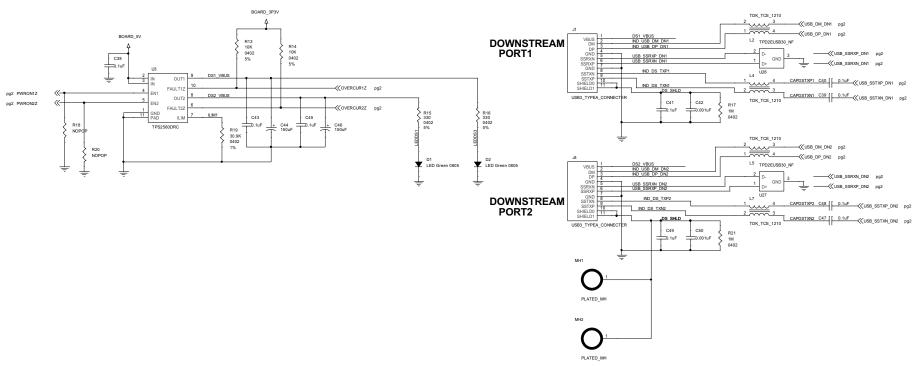

#### 6.3.2 Input Clock

#### 6.3.2.1 Clock Source Requirements

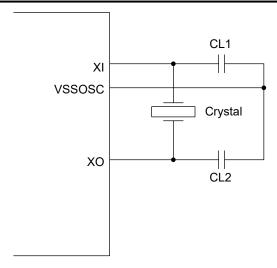

The TUSB73x0 supports an external oscillator source or a crystal unit. The frequency of the clock source may be 24 MHz or 48 MHz. If a clock is provided to XI instead of a crystal, XO is left open and VSSOSC should be connected to the PCB ground plane. Otherwise, if a crystal is used, the connection needs to follow the guidelines below.

Because XI and XO are coupled to other leads and supplies on the PCB, it is important to keep them as short as possible and away from any switching leads. It is also recommended to minimize the capacitance between XI and XO. This can be accomplished by connecting the VSSOSC lead to the two external capacitors CL1 and CL2 and shielding them with the clean ground lines. The VSSOSC should not be connected to PCB ground when using a crystal.

Load capacitance ( $C_{load}$ ) of the crystal varying with the crystal vendors is the total capacitance value of the entire oscillation circuit system as seen from the crystal. It includes two external capacitors CL1 and CL2.

Figure 6-1. Oscillation Circuit

#### 6.3.2.2 External Clock

When using an external clock source, the reference clock should have a ±100 PPM or better frequency stability and have less than 50-ps absolute peak to peak jitter or less than 25-ps peak to peak jitter after applying the USB 3.0 jitter transfer function. XI should be tied to the clock source and XO should be left floating. The input clock must be 1.8-V LVCMOS; this input is not 3.3-V tolerant.

#### 6.3.2.3 External Crystal

An external 2-M $\Omega$  feedback resistor is required between XI and XO when using a crystal. See *Crystal Specification* for additional crystal specifications.

#### 6.4 Programming

#### 6.4.1 Two-Wire Serial-Bus Interface

The host controller provides a two-wire serial-bus interface to load subsystem identification information and specific register defaults from an external EEPROM. The serial-bus interface signals include SDA and SCL. The use of an external EEPROM is optional. The TUSB73x0 will function with the default settings. For motherboard down applications, BIOS can be used to set all of the options available on the TUSB73x0.

On a PCIe Add-in Card, an EEPROM is only needed if any of the following is true:

- Mark one or more USB ports as non-removable.

- · Disable one or more USB ports.

- Set a PCle Subsystem ID and Subsystem Vendor ID.

- Change the default de-emphasis/swing/equalizer settings of the SuperSpeed USB ports.

- Change the default L0s and L1 latency values for PCle.

- Change the default PWRON polarity to active high instead of active low.

#### 6.4.1.1 Serial-Bus Interface Implementation

To enable the serial-bus interface, a pullup resistor must be implemented on the SCL signal. At the rising edge of PERST# or GRST#, whichever occurs later in time, the SCL terminal is checked for a pullup resistor. If one is detected, then bit 3 (SBDETECT) in *Serial Bus Control and Status Register*) is set. Software may disable the serial-bus interface at any time by writing a 0b to the SBDETECT bit. If no external EEPROM is required, then the serial-bus interface is permanently disabled by attaching a pull-down resistor to the SCL signal.

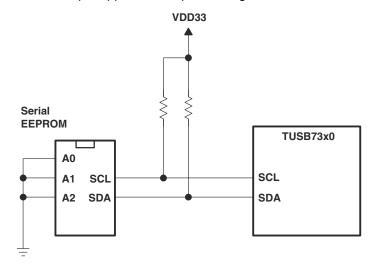

The host controller implements a two-terminal serial interface with one clock signal (SCL) and one data signal (SDA). The SCL signal is an unidirectional output from the host controller and the SDA signal is bidirectional. Both are open-drain signals and require pullup resistors. The host controller is a bus controller device and drives SCL at approximately 60 kHz during data transfers and places SCL in a high-impedance state (0 frequency) during bus idle states. The serial EEPROM is a bus target device and must acknowledge a target address equal to A0h. Figure 6-2 illustrates an example application implementing the two-wire serial bus.

Figure 6-2. Serial EEPROM Application

#### 6.4.1.2 Serial-Bus Interface Protocol

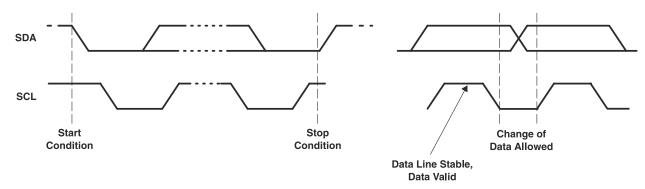

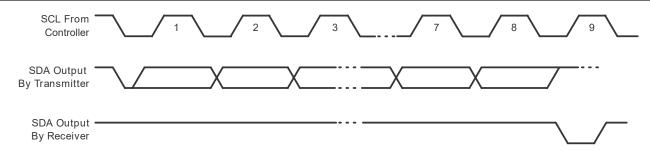

All data transfers are initiated by the serial-bus controller. The beginning of a data transfer is indicated by a start condition, which is signaled when the SDA line transitions to the low state while SCL is in the high state, as illustrated in Figure 6-3. The end of a requested data transfer is indicated by a stop condition, which is signaled by a low-to-high transition of SDA while SCL is in the high state, as shown in Figure 6-3. Data on SDA must remain stable during the high state of the SCL signal, as changes on the SDA signal during the high state of SCL are interpreted as control signals, that is, a start or stop condition.

Figure 6-3. Serial-Bus Start and Stop Conditions and Bit Transfers

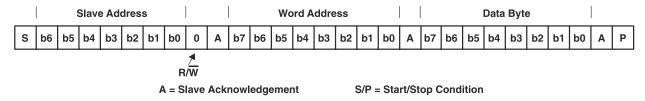

Data is transferred serially in 8-bit bytes. During a data transfer operation, the exact number of bytes that are transmitted is unlimited. However, each byte must be followed by an acknowledge bit to continue the data transfer operation. An acknowledge (ACK) is indicated by the data byte receiver pulling the SDA signal low, so that it remains low during the high state of the SCL signal. Figure 6-4 illustrates the acknowledge protocol.

Figure 6-4. Serial-Bus Protocol Acknowledge

The host controller performs three basic serial-bus operations: single byte reads, single byte writes, and multibyte reads. The single byte operations occur under software control. The multibyte read operations are performed by the serial EEPROM initialization circuitry immediately after a PCI Express reset. See TUSB7340 Power Consumption, Serial-Bus EEPROM Application, for details on how the host controller automatically loads the subsystem identification and other register defaults from the serial-bus EEPROM.

Figure 6-5 illustrates a single byte write. The host controller issues a start condition and sends the 7-bit target device address and the R/W command bit is equal to 0b. A 0b in the R/W command bit indicates that the data transfer is a write. The target device acknowledges if it recognizes the target address. If no acknowledgment is received by the host controller, then bit 1 (SB ERR) is set in the serial-bus control and status register (PCI offset BCh, see Serial Bus Control and Status Register). Next, the EEPROM word address is sent by the host controller, and another target acknowledgment is expected. Then the host controller delivers the data byte MSB first and expects a final acknowledgment before issuing the stop condition.

Figure 6-5. Serial-Bus Protocol – Byte Write

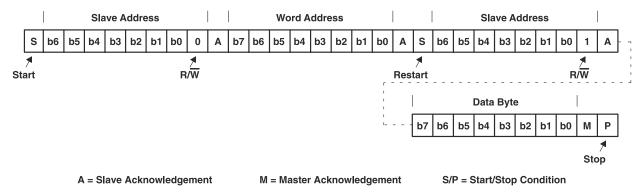

Figure 6-6 illustrates a single byte read. The host controller issues a start condition and sends the 7-bit target device address and the R/W command bit is equal to 0b (write). The target device acknowledges if it recognizes the target address. Next, the EEPROM word address is sent by the host controller, and another target acknowledgment is expected. Then, the host controller issues a restart condition followed by the 7-bit target address and the R/W command bit is equal to 1b (read). Once again, the target device responds with an acknowledge. Next, the target device sends the 8-bit data byte, MSB first. Because this is a 1-byte read, the host controller responds with no acknowledge (logic high) indicating the last data byte. Finally, the host controller issues a stop condition.

Figure 6-6. Serial-Bus Protocol – Byte Read

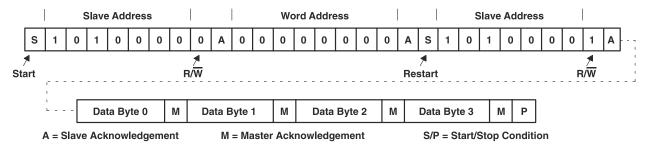

Figure 6-7 illustrates the serial interface protocol during a multibyte serial EEPROM download. The serial-bus protocol starts exactly the same as a 1-byte read. The only difference is that multiple data bytes are transferred. The number of transferred data bytes is controlled by the host controller. After each data byte, the host controller issues acknowledge (logic low) if more data bytes are requested. The transfer ends after a host controller no acknowledge (logic high) followed by a stop condition.

Figure 6-7. Serial-Bus Protocol – Multibyte Read

Bit 7 (PROT\_SEL) in the serial-bus control and status register changes the serial-bus protocol. Each of the three previous serial-bus protocol figures illustrates the PROT\_SEL bit default (logic low). When this control bit is asserted, the word address and corresponding acknowledge are removed from the serial-bus protocol. This feature allows the system designer a second serial-bus protocol option when selecting external EEPROM devices.

#### 6.4.1.3 Serial-Bus EEPROM Application

A serial EEPROM interface is implemented to pre-load several registers. The registers and corresponding bits that are loaded through the EEPROM are provided in Table 6-4.

Table 6-4. EEPROM Register Loading Map

| SERIAL EEPROM WORD ADDRESS BYTE DESCRIPTION |                                                |  |  |  |

|---------------------------------------------|------------------------------------------------|--|--|--|

| 00h                                         | TUSB73X0 Function Indicator (00h)              |  |  |  |

| 01h                                         | Number of Bytes (19h)                          |  |  |  |

| 02h                                         | PCI D0h, Subsystem Vendor ID, Byte 0           |  |  |  |

| 03h                                         | PCI D1h, Subsystem Vendor ID, Byte 1           |  |  |  |

| 04h                                         | PCI D2h, Subsystem ID, Byte 0                  |  |  |  |

| 05h                                         | PCI D3h, Subsystem ID, Byte 1                  |  |  |  |

| 06h                                         | PCI D4h, General Control 0, Byte 0             |  |  |  |

| 07h                                         | PCI D5h, General Control 0, Byte 1             |  |  |  |

| 08h                                         | PCI D8h, General Control 1, Byte 0             |  |  |  |

| 09h                                         | PCI DCh, General Control 2, Byte 0             |  |  |  |

| 0Ah                                         | PCI E0h, USB Control, Byte 0                   |  |  |  |

| 0Bh                                         | PCI E1h, USB Control, Byte 1                   |  |  |  |

| 0Ch                                         | PCI E2h, USB Control, Byte 2                   |  |  |  |

| 0Dh                                         | PCI E3h, USB Control, Byte 3                   |  |  |  |

| 0Eh                                         | PCI E4h, De-emphasis and Swing Control, Byte 0 |  |  |  |

| 0Fh                                         | PCI E5h, De-emphasis and Swing Control, Byte 1 |  |  |  |

| 10h                                         | PCI E6h, De-emphasis and Swing Control, Byte 2 |  |  |  |

| 11h                                         | PCI E7h, De-emphasis and Swing Control, Byte 3 |  |  |  |

| 12h                                         | PCI E8h, Equalizer Control, Byte 0             |  |  |  |

| 13h                                         | PCI E9h, Equalizer Control, Byte 1             |  |  |  |

| 14h                                         | PCI EAh, Equalizer Control, Byte 2             |  |  |  |

| 15h                                         | PCI EBh, Equalizer Control, Byte 3             |  |  |  |

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

Table 6-4. EEPROM Register Loading Map (continued)

| OFFICE FERROW WORD ARRESTO | DYTE DECODIDION                                      |

|----------------------------|------------------------------------------------------|

| SERIAL EEPROM WORD ADDRESS | BYTE DESCRIPTION                                     |

| 16h                        | PCI ECh, Custom PHY Transmit/Receive Control, Byte 0 |

| 17h                        | PCI EDh, Custom PHY Transmit/Receive Control, Byte 1 |

| 18h                        | PCI EEh, Custom PHY Transmit/Receive Control, Byte 2 |

| 19h                        | PCI EFh, Custom PHY Transmit/Receive Control, Byte 3 |

| 1Ah                        | PCI 61h, Frame Length Adjustment Register            |

| 1Bh                        | End of List Indicator (80h)                          |

This format must be explicitly followed for the host controller to correctly load initialization values from a serial EEPROM. All byte locations must be considered when programming the EEPROM.

The serial EEPROM is addressed by the host controller at target address 1010 000b. This target address is internally hardwired and cannot be changed by the system designer. Therefore, all three hardware address bits for the EEPROM are tied to VSS to achieve this address. The serial EEPROM in the sample application circuit (Figure 6-2) assumes the 1010b high-address nibble. The lower three address bits are terminal inputs to the chip, and the sample application shows these terminal inputs tied to VSS.

During an EEPROM download operation, bit 4 (ROMBUSY) in the serial-bus control and status register is asserted. After the download is finished, bit 0 (ROM\_ERR) in the serial-bus control and status register may be monitored to verify a successful download.

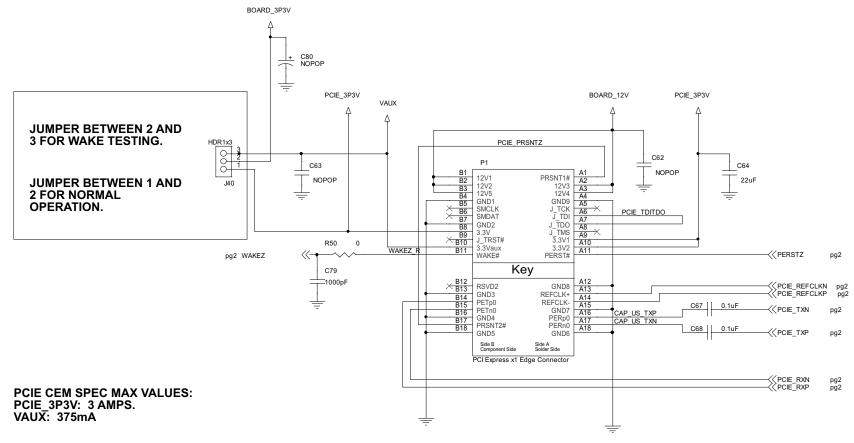

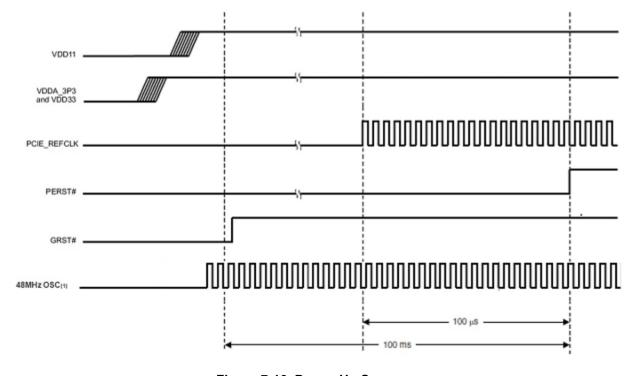

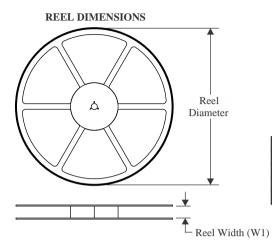

#### 6.4.2 System Management Interrupt