## ispGAL™22V10AV/B/C Device Datasheet

June 2010

# **All Devices Discontinued!**

Product Change Notification (PCN) #09-10 has been issued to discontinue all devices in this data sheet.

The original datasheet pages have not been modified and do not reflect those changes. Please refer to the table below for reference PCN and current product status.

| Product Line   | Ordering Part Number | Product Status | Reference PCN      |  |  |

|----------------|----------------------|----------------|--------------------|--|--|

|                | ispGAL22V10AV-23LS   |                |                    |  |  |

|                | ispGAL22V10AV-23LSN  |                |                    |  |  |

|                | ispGAL22V10AV-5LS    |                |                    |  |  |

|                | ispGAL22V10AV-5LSN   |                |                    |  |  |

|                | ispGAL22V10AV-75LS   |                |                    |  |  |

|                | ispGAL22V10AV-75LSN  |                |                    |  |  |

|                | ispGAL22V10AV-5LSI   | Discontinued   | PCN#09-10          |  |  |

| ispGAL22V10AV  | ispGAL22V10AV-5LSNI  | Discontinued   | <u>1 011#05-10</u> |  |  |

|                | ispGAL22V10AV-75LSI  |                |                    |  |  |

|                | ispGAL22V10AV-75LSNI |                |                    |  |  |

|                | ispGAL22V10AV-28LJ   |                |                    |  |  |

|                | ispGAL22V10AV-5LJ    |                |                    |  |  |

|                | ispGAL22V10AV-75LJ   |                |                    |  |  |

|                | ispGAL22V10AV-5LJI   |                |                    |  |  |

|                | ispGAL22V10AV-75LJI  |                |                    |  |  |

|                | ispGAL22V10AB-23LS   |                |                    |  |  |

|                | ispGAL22V10AB-5LS    |                |                    |  |  |

|                | ispGAL22V10AB-75LS   |                |                    |  |  |

|                | ispGAL22V10AB-5LSI   |                |                    |  |  |

| ispGAL22V10AB  | ispGAL22V10AB-75LSI  | Discontinued   | PCN#09-10          |  |  |

| 15pGALZZV 10AD | ispGAL22V10AB-28LJ   | Discontinued   | <u>FCN#09-10</u>   |  |  |

|                | ispGAL22V10AB-5LJ    |                |                    |  |  |

|                | ispGAL22V10AB-75LJ   |                |                    |  |  |

|                | ispGAL22V10AB-5LJI   |                |                    |  |  |

|                | ispGAL22V10AB-75LJI  |                |                    |  |  |

| Product Line   | Ordering Part Number | Product Status | Reference PCN    |

|----------------|----------------------|----------------|------------------|

|                | ispGAL22V10AC-23LS   |                |                  |

|                | ispGAL22V10AC-5LS    |                |                  |

|                | ispGAL22V10AC-75LS   |                |                  |

|                | ispGAL22V10AC-5LSI   |                |                  |

| ispGAL22V10AC  | ispGAL22V10AC-75LSI  | Discontinued   | PCN#09-10        |

| ISPGALZZV IVAC | ispGAL22V10AC-28LJ   | Discontinued   | <u>FCN#09-10</u> |

|                | ispGAL22V10AC-5LJ    |                |                  |

|                | ispGAL22V10AC-75LJ   |                |                  |

|                | ispGAL22V10AC-5LJI   |                |                  |

|                | ispGAL22V10AC-75LJI  |                |                  |

# ispGAL22V10AV/B/C

In-System Programmable Low Voltage E<sup>2</sup>CMOS® PLD Generic Array Logic

December 2008 Data Sheet

#### **Features**

#### ■ High Performance

- t<sub>PD</sub> = 2.3ns propagation delay

- f<sub>MAX</sub> = 455 MHz maximum operating frequency

- t<sub>CO</sub> = 2ns maximum from clock input to data output

- t<sub>SU</sub> = 1.3 ns clock set-up time

#### Low Power

- 1.8V core E<sup>2</sup>CMOS<sup>®</sup> technology

- Typical standby power <300µW (ispGAL22V10AC)

- CMOS design techniques provide low static and dynamic power

#### ■ Space-Saving Packaging

Available in 32-pin QFNS (Quad Flat-pack, No lead, Saw-singulated) package 5mm x 5mm body size<sup>1</sup>

#### ■ Easy System Integration

- Operation with 3.3V (ispGAL22V10AV), 2.5V (ispGAL22V10AB) or 1.8V (ispGAL22V10AC) supplies

- Operation with 3.3V, 2.5V or 1.8V LVCMOS I/O

- 5V tolerant I/O for LVCMOS 3.3 interface

- · Hot-socketing

- Open-drain capability

- · Input pull-up, pull-down or bus-keeper

- Lead-free package option

- Programmable output slew rate

- 3.3V PCI compatible

#### **■ In-System Programmable**

- IEEE 1149.1 boundary scan testable

- 3.3V/2.5V/1.8V in-system programmable (ISP™) using IEEE 1532 compliant interface

#### ■ E<sup>2</sup> CELL TECHNOLOGY

- In-system programmable logic

- 100% tested/100% yields

- High speed electrical erasure (<50ms)</li>

#### **■** Applications Include

- DMA control

- · State machine control

- · High speed graphics processing

- · Software-driven hardware configuration

#### Boundary Scan USERCODE Register

Supports electronic signature

1. Use 32-pin QFNS package for all new designs. Refer to PCN #13A-08 for 32-pin QFN package discontinuance.

#### Introduction

The ispGAL22V10A is manufactured using Lattice Semiconductor's advanced E²CMOS process, which combines CMOS with Electrically Erasable (E²) floating gate technology. With an advanced E² low-power cell and full CMOS logic approach, the ispGAL22V10A family offers fast pin-to-pin speeds, while simultaneously delivering low standby power without requiring any "turbo bits" or other traditional power management schemes. The ispGAL22V10A can interface with both 3.3V, 2.5V and 1.8V signal levels.

The ispGAL22V10A is functionally compatible with the ispGAL22LV10, GAL22LV10 and GAL22V10.

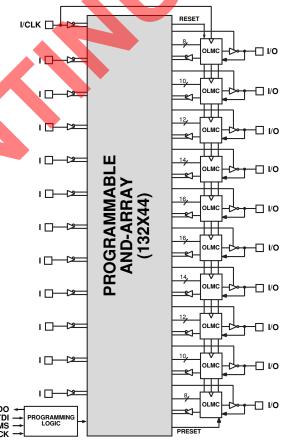

Figure 1. Functional Block Diagram

<sup>© 2008</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### ispGAL Architecture

#### **Output Logic Macrocell (OLMC)**

The ispGAL22V10A has a variable number of product terms per OLMC. Of the ten available OLMCs, two OLMCs have access to eight product terms (pins 17 and 27), two have ten product terms (pins 18 and 26), two have twelve product terms (pins 19 and 25), two have fourteen product terms (pins 20 and 24), and two OLMCs have sixteen product terms (pins 21 and 23). In addition to the product terms available for logic, each OLMC has an additional product-term dedicated to output enable control.

The output polarity of each OLMC can be individually programmed to be true or inverting, in either combinatorial or registered mode. This allows each output to be individually configured as either active high or active low.

The ispGAL22V10A has a product term for Asynchronous Reset (AR) and a product term for Synchronous Preset (SP). These two product terms are common to all registered OLMCs. The Asynchronous Reset sets all registers to zero any time this dedicated product term is asserted. The Synchronous Preset sets all registers to a logic one on the rising edge of the next clock pulse after this product term is asserted.

NOTE: The AR and SP product terms will force the Q output of the flip-flop into the same state regardless of the polarity of the output. Therefore, a reset operation, which sets the register output to a zero, may result in either a high or low at the output pin, depending on the pin polarity chosen.

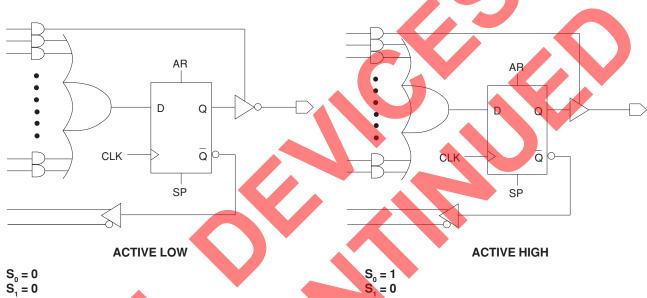

Figure 2. Output Logic Macrocell

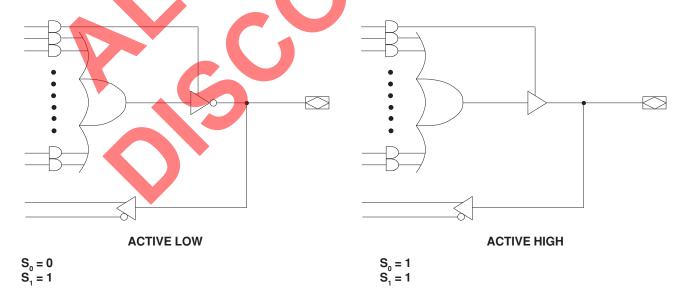

## **Output Logic Macrocell Configurations**

Each of the Macrocells of the ispGAL22V10A has two primary functional modes: registered, and combinatorial I/O. The modes and the output polarity are set by two bits (S0 and S1), which are normally controlled by the logic compiler. Each of these two primary modes, and the bit settings required to enable them, are described below and on the following page.

#### Registered

In registered mode the output pin associated with an individual OLMC is driven by the Q output of that OLMC's D-type flip-flop. Logic polarity of the output signal at the pin may be selected by specifying that the output buffer drive either true (active high) or inverted (active low). Output tri-state control is available as an individual product-term for each OLMC, and can therefore be defined by a logic equation. The D flip-flop's /Q output is fed back into the AND array, with both the true and complement of the feedback available as inputs to the AND array.

NOTE: In registered mode, the feedback is from the /Q output of the register, and not from the pin; therefore, a pin defined as registered is an output only, and cannot be used for dynamic I/O, as can the combinatorial pins.

#### Combinatorial I/O

In combinatorial mode the pin associated with an individual OLMC is driven by the output of the sum term gate. Logic polarity of the output signal at the pin may be selected by specifying that the output buffer drive either true (active high) or inverted (active low). Output tri-state control is available as an individual product-term for each output, and may be individually set by the compiler as either "on" (dedicated output), "off" (dedicated input), or "product-term driven" (dynamic I/O). Feedback into the AND array is from the pin side of the output enable buffer. Both polarities (true and inverted) of the pin are fed back into the AND array.

Figure 3. Registered Mode

Figure 4. Combinatorial Mode

2 (30) 0 20 24 28 12 16 32 36 40 JEDEC Fuse #0 ASYNCHRONOUS RESET (TO ALL REGISTERS) 8 OLMC S1, S0 = 5808, 580 > SR = 5830 OD = 5831 27 (26) OLMC \$0 = 5810, 5811 \$R = 5832 OD = 5833 10 26 (25) 3 (31) ->= OLMC 25 (24) S1, S0 = 5812, 5813 SR = 5834 OD = 5835 4 (32) OLMC S1, S0 = 5814, 5815 SR = 5836 OD = 5837 14 24 (23) 5 (1) →>= 23 (22) OLMC S0 = 5816, 5817 SR = 5838 OD = 5839 6 (2) →>= 21 (19) 16 OLMC S1, S0 = 5818, 5819 SR = 5840 OD = 5841 7 (3) 20 (18) 14 OLMC S1, S0 = 5820, 5821 SR = 5842 OD = 5843 9 (6) 12 OLMC 19 (17) S1, S0 = 5822, 5823 SR = 5844 OD = 5845 10 (7) 10 OLMC 18 (16) S1, S0 = 5824, 5825 SR = 5846 OD = 5847 11 (8) 8 OLMC 17 (15) S1, S0 = 5826, 582 SR = 5848 OD = 5849 12 (9) SYNCHRONOUS PRESET (TO ALL REGISTERS) 13 (10) 16 (14) JEDEC Fuse #131 S1, S0 = Arch Control Bits JEDEC Fuse #5807 SR = Slew Rate Bit OD = Open Drain Bit

Figure 5. Logic Diagram/JEDEC Fuse Map - PLCC & (QFN/QFNS) Package Pinout

### **Electronic Signature**

An electronic signature (ES) is provided in every ispGAL22V10A device. It contains 32 bits of reprogrammable memory that can contain user-defined data. Some uses include user ID codes, revision numbers, or inventory control. The signature data is always available to the user independent of the state of the security cell. IEEE 1149.1 and IEEE 1532 compliant USERCODE is supported.

## **Low Power and Power Management**

The ispGAL22V10A family is designed with high speed low power design techniques to offer both high speed and low power. With an advanced E<sup>2</sup> low power cell and no sense-amplifiers (full CMOS logic approach), the ispGAL22V10A family offers fast pin-to-pin speeds, while simultaneously delivering low standby power without requiring any "turbo bits" or other traditional power-management schemes.

## I/O Configuration

Each output supports a variety of output standards dependent on the  $V_{CCO}$ . Outputs can also be configured for open drain operation. Each input can be programmed to support a variety of standards, independent of the  $V_{CCO}$  supplied to its I/O. For 28 PLCC package the  $V_{CCO}$  and  $V_{CC}$  must be the same. The option to set the  $V_{CCO}$  independent of  $V_{CC}$  is available with the 32 QFN/QFNS package only. The I/O standards supported are:

- LVTTL

- LVCMOS 1.8

- LVCMOS 3.3

- 3.3V PCI Compatible

- LVCMOS 2.5

All of the I/Os and dedicated inputs have the capability to provide a bus-keeper latch, Pull-up Resistor or Pull-down Resistor. A fourth option is to provide none of these. The selection is done on a global basis. The default in both hardware and software is such that when the device is erased or if the user does not specify, the input structure is configured to be a Pull-up Resistor.

Each ispGAL22V10A device I/O has an individually programmable output slew rate control bit. Each output can be individually configured for fast slew or slow slew. The typical edge rate difference between fast and slow slew setting is 20%. For high-speed designs with long, unterminated traces, the slow-slew rate will introduce fewer reflections, less noise and keep ground bounce to a minimum. For designs with short traces or well terminated lines, the fast slew rate can be used to achieve the highest speed.

## IEEE 1149.1-Compliant Boundary Scan Testability

All ispGAL22V10A devices have boundary scan cells and are compliant to the IEEE 1149.1 standard. This allows functional testing of the circuit board on which the device is mounted through a serial scan path that can access all critical logic notes. Internal registers are linked internally, allowing test data to be shifted in and loaded directly onto test nodes, or test node data to be captured and shifted out for verification. In addition, these devices can be linked into a board-level serial scan path for more board-level testing. The test access port operates with an LVCMOS interface that corresponds to the power supply voltage.

## IEEE 1532-Compliant In-System Programming

Programming devices in-system provides a number of significant benefits including rapid prototyping, lower inventory levels, higher quality and the ability to make in-field modifications. All ispGAL22V10A devices provide In-System Programming (ISPTM) capability through the Boundary Scan Test Access Port. This capability has been implemented in a manner that ensures that the port remains complaint to the IEEE 1149.1 standard. By using IEEE 1149.1 as the communication interface through which ISP is achieved, users get the benefit of a standard, well-defined interface. All ispGAL22V10A devices are also compliant with the IEEE 1532 standard.

The ispGAL22V10A devices can be programmed across the commercial temperature and voltage range. The PC-based Lattice software facilitates in-system programming of ispGAL22V10A devices. The software takes the JEDEC file output produced by the design implementation software, along with information about the scan chain, and creates a set of vectors used to drive the scan chain. The software can use these vectors to drive a scan chain

via the parallel port of a PC. Alternatively, the software can output files in formats understood by common automated test equipment. This equipment can then be used to program ispGAL22V10A devices during the testing of a circuit board.

## **Security Bit**

A programmable security bit is provided on the ispGAL22V10A devices as a deterrent to unauthorized copying of the array configuration patterns. Once programmed, this bit defeats readback of the programmed pattern by a device programmer, securing proprietary designs from competitors. Programming and verification are also defeated by the security bit. The bit can only be reset by erasing the entire device.

## Hot Socketing

The ispGAL22V10A devices are well-suited for applications that require hot socketing. Hot socketing a device requires that the device, during power-up and down, tolerate active signals on the I/Os and inputs without being damaged. Additionally, it requires that the effects of I/O pin loading be minimal on active signals. The ispGAL22V10A devices provide this capability for input voltages in the range of 0V to 3.0V.

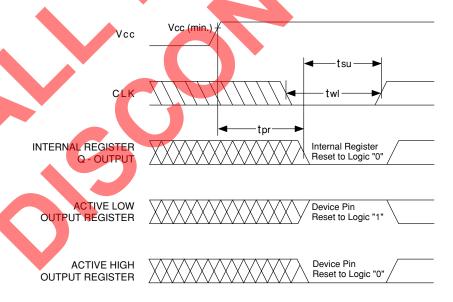

## **Power-up Reset**

Circuitry within the ispGAL22V10A provides a reset signal to all registers during power-up. All internal registers will have their Q outputs set low after a specified time (tpr, 1µs typical). As a result, the state on the registered output pins (if they are enabled) will be either high or low on power-up, depending on the programmed polarity of the output pins. This feature can greatly simplify state machine design by providing a known state on power-up. The timing diagram for power-up is shown above. Because of the asynchronous nature of system power-up, some conditions must be met to provide a valid power-up reset of the ispGAL22V10A. First, the Vcc rise must be monotonic. Second, the clock input must be at static TTL level as shown in the diagram during power up. The registers will reset within a maximum of tpr time. As in normal system operation, avoid clocking the device until all input and feedback path setup times have been met. The clock must also meet the minimum pulse width requirements.

Figure 6. Timing Diagram for Power-up

## **Absolute Maximum Ratings**<sup>1, 2, 3</sup>

|                                                    | ispGAL<br>22V10AC (1.8V) | ispGAL<br>22V10AB (2.5V) | ispGAL<br>22V10AV (3.3V) |

|----------------------------------------------------|--------------------------|--------------------------|--------------------------|

| Supply Voltage V <sub>CC</sub>                     | 0.5 to 2.5V              | -0.5 to 5.5V             | -0.5 to 5.5V             |

| Output Supply Voltage V <sub>CCO</sub>             | 0.5 to 4.5V              | -0.5 to 4.5V             | -0.5 to 4.5V             |

| Input or I/O Tristate Voltage Applied <sup>4</sup> | 0.5 to 5.5V              | -0.5 to 5.5V             | -0.5 to 5.5V             |

| Storage Temperature                                | 65 to 150°C              | -65 to 150°C             | -65 to 150°C             |

| Junction Temperature $(T_i)$ with Power Applied .  | 55 to 150°C              | -55 to 150°C             | -55 to 150°C             |

- 1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification

- 2. Compliance with Lattice Thermal Management document is required.

- 3. All voltages referenced to GND.

- 4. Undershoot of -2V and overshoot of (V<sub>IH</sub> (MAX) +2), up to a total pin voltage of 6.0V, is permitted for a duration of < 20ns.

## **Recommended Operating Conditions**

| Symbol          | Parameter                         | Min  | Max  | Units |

|-----------------|-----------------------------------|------|------|-------|

|                 | Supply Voltage for 1.8V Devices   | 1.65 | 1.95 | V     |

| V <sub>CC</sub> | Supply Voltage for 2.5V Devices   | 2.3  | 2.7  | V     |

| 100             | Supply Voltage for 3.3V Devices   | 3.0  | 3.6  | V     |

| т.              | Junction Temperature (Commercial) | 0    | 90   | С     |

| ¹ j             | Junction Temperature (Industrial) | -40  | 105  | С     |

## **Erase Reprogram Specifications**

|                       | Paramete | r |  | Min   | Max | Units  |

|-----------------------|----------|---|--|-------|-----|--------|

| Erase/Reprogram Cycle |          |   |  | 1,000 | _   | Cycles |

Note: Valid over commercial temperature range.

## Hot Socketing Characteristics 123

| Symbol          | Parameter                    | Condition                                                  | Min | Тур | Max | Units |

|-----------------|------------------------------|------------------------------------------------------------|-----|-----|-----|-------|

| I <sub>DK</sub> | Input or I/O Leakage Current | $0 \le V_{IN} \le 3.0 \text{V}, T_j = 105^{\circ}\text{C}$ | _   |     | ±50 | μΑ    |

<sup>1.</sup> Insensitive to sequence of  $V_{CC}$  and  $V_{CCO}$ . However, assumes monotonic rise/fall rates for  $V_{CC}$  and  $V_{CCO}$ , provided  $(V_{IN} - V_{CCO}) \le 3.0 \text{V}$ .

## I/O Recommended Operating Conditions

|            | V <sub>CCO</sub> (V) <sup>1</sup> |      |  |  |  |  |  |

|------------|-----------------------------------|------|--|--|--|--|--|

| Standard   | Min                               | Max  |  |  |  |  |  |

| LVTTL      | 3.0                               | 3.6  |  |  |  |  |  |

| LVCMOS 3.3 | 3.0                               | 3.6  |  |  |  |  |  |

| LVCMOS 2.5 | 2.3                               | 2.7  |  |  |  |  |  |

| LVCMOS 1.8 | 1.65                              | 1.95 |  |  |  |  |  |

| PCI 3.3    | 3.0                               | 3.6  |  |  |  |  |  |

<sup>1.</sup> Typical values for  $V_{CCO}$  are the average of the Min and Max values.

<sup>2.</sup>  $0 \le V_{CC} \le V_{CC}$  (MAX),  $0 \le V_{CCO} \le V_{CCO}$  (MAX) 3.  $I_{DK}$  is additive to  $I_{PU}$ ,  $I_{PD}$  or  $I_{BH}$ . Device defaults to pull-up until fuse circuitry is active.

### **DC Electrical Characteristics**

#### **Over Recommended Operating Conditions**

| Symbol                                         | Parameter                           | Condition                                                                   | Min                   | Тур          | Max                   | Units |

|------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------|-----------------------|--------------|-----------------------|-------|

| I <sub>IL</sub> , I <sub>IH</sub> <sup>1</sup> | Input Leakage Current               | $0 < V_{IN} \le 3.6V, T_j = 105^{\circ}C$                                   | _                     | _            | 10                    | μA    |

| I <sub>IH</sub> <sup>2</sup>                   | Input High Leakage Current          | $3.6V < V_{IN} \le 5.5V, T_j = 105^{\circ}C$<br>$3.0V \le V_{CCO} \le 3.6V$ | _                     | _            | 20                    | μΑ    |

| los                                            | Output Short Circuit Current        | $V_{CC} = 3.3V, V_{OUT} = 0.5V, T_A = 25^{\circ}C$                          | _                     | _            | -80                   | mA    |

| I <sub>PU</sub>                                | I/O Weak Pull-up Resistor Current   | $0 \le V_{IN} \le 0.7V_{CCO}$                                               | 20                    |              | 150                   | μA    |

| I <sub>PD</sub>                                | I/O Weak Pull-down Resistor Current | $V_{IL} (MAX) \le V_{IN} \le V_{IH} (MAX)$                                  | 20                    | <del>-</del> | 150                   | μA    |

| I <sub>BHLS</sub>                              | Bus Hold Low Sustaining Current     | $V_{IN} = V_{IL} (MAX)$                                                     | 20                    | _            |                       | μA    |

| I <sub>BHHS</sub>                              | Bus Hold High Sustaining Current    | $V_{IN} = 0.7 V_{CCO}$                                                      | 20                    | _            | <                     | μA    |

| I <sub>BHLO</sub>                              | Bus Hold Low Overdrive Current      | $0V \le V_{IN} \le V_{IH} (MAX)$                                            | <b>\</b>              |              | 150                   | μA    |

| I <sub>BHHO</sub>                              | Bus Hold High Overdrive Current     | $0 \le V_{IN} \le V_{IH} (MAX)$                                             | _                     |              | 150                   | μΑ    |

| V <sub>BHT</sub>                               | Bus Hold Trip Points                | _                                                                           | V <sub>IL</sub> (MAX) |              | V <sub>IH</sub> (MIN) | V     |

| C <sub>1</sub>                                 | I/O Capacitance <sup>3</sup>        | V <sub>CCO</sub> = 3.3V, 2.5V, 1.8V                                         | _                     | 6            | V <del>-</del>        | pf    |

| 01                                             | 1/O Oapaolianoe                     | $V_{CC} = 1.8V$ , $V_{IO} = 0$ to $V_{IH}$ (MAX)                            |                       |              | _                     | Pi    |

| $C_2$                                          | Clock Capacitance <sup>3</sup>      | V <sub>CCO</sub> = 3.3V, 2.5V, 1.8V                                         | 7-                    | 8            | _                     | pf    |

| <u> </u>                                       | Clock Capacitation                  | $V_{CC} = 1.8V$ , $V_{IO} = 0$ to $V_{IH}$ (MAX)                            |                       |              |                       | Pi    |

<sup>1.</sup> Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tristated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

### **Supply Current**

#### **Over Recommended Operating Conditions**

| Symbol                          | Parameter                      | Condition              | Min | Тур | Max | Units |  |  |

|---------------------------------|--------------------------------|------------------------|-----|-----|-----|-------|--|--|

| ispGAL22V10AV/B/C               |                                |                        |     |     |     |       |  |  |

|                                 |                                | V <sub>CC</sub> = 3.3V | _   | 8   | 90  | mA    |  |  |

| I <sub>CC</sub> <sup>1, 2</sup> | Operating Power Supply Current | V <sub>CC</sub> = 2.5V | _   | 8   | 90  | mA    |  |  |

|                                 |                                | $V_{CC} = 1.8V$        | _   | 3   | 80  | mA    |  |  |

|                                 |                                | V <sub>CC</sub> = 3.3V | _   | 7   | _   | mA    |  |  |

| I <sub>CC</sub> <sup>3</sup>    | Standby Power Supply Current   | V <sub>CC</sub> = 2.5V | _   | 7   | _   | mA    |  |  |

|                                 |                                | V <sub>CC</sub> = 1.8V | _   | 150 | _   | μΑ    |  |  |

<sup>2. 5</sup> volt tolerant inputs and I/Os apply to  $V_{CCO}$  condition of 3.0V  $\leq V_{CCO} \leq$  3.6V.

<sup>3.</sup>  $T_A = 25^{\circ}C$ , frequency = 1.0MHz

T<sub>A</sub> = 25°C, frequency = 15MHz.

I<sub>CC</sub> varies with specific device configuration and operating frequency.

<sup>3.</sup>  $T_A = 25^{\circ}C$

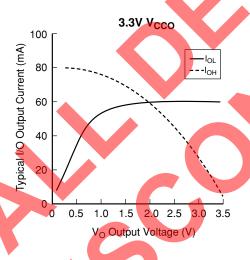

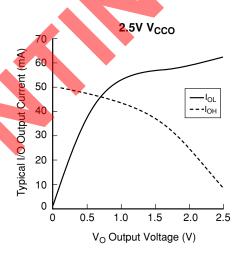

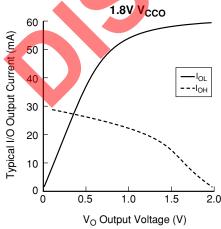

## I/O DC Electrical Characteristics<sup>1</sup>

**Over Recommended Operating Conditions**

|                              |         | V <sub>IL</sub>                     | V <sub>IH</sub>                     |         | V <sub>OL</sub>      | V <sub>OH</sub>         | l <sub>OL</sub> | I <sub>OH</sub> |

|------------------------------|---------|-------------------------------------|-------------------------------------|---------|----------------------|-------------------------|-----------------|-----------------|

| Standard                     | Min (V) | Max (V)                             | Min (V)                             | Max (V) | Max (V)              | Min (V)                 | (mA)            | (mA)            |

| LVTTL                        | -0.3    | 0.80                                | 2.0                                 | .0 5.5  |                      | V <sub>CCO</sub> - 0.40 | 8.0             | -4.0            |

| LVIIL                        | -0.5    | 0.00                                | 2.0                                 | 3.5     | 0.20                 | V <sub>CCO</sub> - 0.20 | 0.1             | -0.1            |

| LVCMOS 3.3                   | -0.3    | 0.80                                | 2.0                                 | 5.5     | 0.40                 | V <sub>CCO</sub> - 0.40 | 8.0             | -4.0            |

| LVOIVIOU 0.0                 | -0.5    | 0.00                                | 2.0                                 | 3.5     | 0.20                 | V <sub>CCO</sub> - 0.20 | 0.1             | -0.1            |

| LVCMOS 2.5                   | -0.3    | 0.70                                | 1.70                                | 3.6     | 0.40                 | V <sub>CCO</sub> - 0.40 | 8.0             | -4.0            |

| LVOWOO 2.5                   | -0.5    | 0.70                                | 1.70                                | 3.0     | 0.20                 | V <sub>CCO</sub> - 0.20 | 0.1             | -0.1            |

| LVCMOS 1.8                   | -0.3    | 0.63                                | 1.17                                | 3.6     | 0.40                 | V <sub>CCO</sub> - 0.45 | 2.0             | -2.0            |

| (ispGAL22V10AV/B)            | -0.5    | 0.00                                | 1.17                                | 0.0     | 0.20                 | V <sub>CCO</sub> - 0.20 | 0.1             | -0.1            |

| LVCMOS 1.8                   | -0.3    | 0.35 V <sub>CC</sub>                | 0.65 * V <sub>CC</sub>              | 3.6     | 0.40                 | V <sub>CCO</sub> - 0.45 | 2.0             | -2.0            |

| (ispGAL22V10AC)              | 0.0     | 0.00 100                            | 0.03 100                            | 0.0     | 0.20                 | V <sub>CCO</sub> - 0.20 | 0.1             | -0.1            |

| PCI 3.3<br>(ispGAL22V10AV/B) | -0.3    | 1.08                                | 1.5                                 | 5.5     | 0.1 V <sub>CC</sub>  | 0.9 V <sub>CCO</sub>    | 1.5             | -0.5            |

| PCI 3.3<br>(ispGAL22V10AC)   | -0.3    | 0.3 * 3.3 * (V <sub>CC</sub> / 1.8) | 0.5 * 3.3 * (V <sub>CC</sub> / 1.8) | 5.5     | 0.1 V <sub>CCO</sub> | 0.9 V <sub>CCO</sub>    | 1.5             | -0.5            |

<sup>1.</sup> For 28 PLCC package the I/O voltage and core voltage must be the same. The option to set the I/O voltage independent of the core voltage is available with the 32 QFN/QFNS package only.

## ispGAL22V10AV/B/C External Switching Characteristics<sup>1</sup>

### **Over Recommended Operating Conditions**

|                               |                                                                         | -2  | 23  | -2  | 28  | -          | 5            | -75 |          |       |

|-------------------------------|-------------------------------------------------------------------------|-----|-----|-----|-----|------------|--------------|-----|----------|-------|

| Param                         | Description                                                             | Min | Max | Min | Max | Min        | Max          | Min | Max      | Units |

|                               | 1 Output Switching Propagation Delay                                    | _   | 2.3 | _   | 2.8 | _          | _            | _   | _        | ns    |

| t <sub>PD</sub>               | 10 Output Switching Propagation Delay                                   | _   | 2.6 | _   | 3.0 | _          | 5.0          | _   | 7.5      |       |

| t <sub>CO</sub>               | Clock to Output Delay                                                   | _   | 2.0 | _   | 2.5 | _          | 3.5          | _   | 5.0      | ns    |

| t <sub>CF</sub> <sup>2</sup>  | Clock to Feedback Delay                                                 | _   | 1.9 | _   | 2.2 | <b>)</b> _ | 2.5          | _   | 2.5      | ns    |

| t <sub>SU</sub>               | Setup Time, Input or Feedback before CLK↑                               | 1.3 | _   | 2.0 |     | 3.5        | _            | 5.0 | _        | ns    |

| t <sub>H</sub>                | Hold Time, Input or Feedback after CLK↑                                 | 0   | _   | 0   |     | 0          | <del>-</del> | 0   | _        | ns    |

|                               | Maximum Clock Frequency with External Feedback, $[1/(t_{SU} + t_{CO})]$ | 303 | _ • | 222 |     | 143        | _            | 100 | -        | ns    |

| f <sub>MAX</sub> <sup>3</sup> | Maximum Clock Frequency with Internal Feedback, $[1/(t_{SU} + t_{CF})]$ | 312 |     | 238 | -   | 166        |              | 133 | 7        | ns    |

|                               | Maximum Clock Frequency with No Feedback                                | 455 | _   | 357 | _   | 200        |              | 166 | <u> </u> | ns    |

| t <sub>WH</sub> <sup>3</sup>  | Clock Pulse Duration, High                                              | 1.1 | -   | 1.4 | _   | 2.5        |              | 3.0 | _        | ns    |

| t <sub>WL</sub> <sup>3</sup>  | Clock Pulse Duration, Low                                               | 1.1 | _   | 1.4 | _   | 2.5        |              | 3.0 | _        | ns    |

| t <sub>EN</sub>               | Input or I/O to Output Enabled                                          | +   | 3.0 | _   | 3.5 | -          | 6.0          | _   | 7.5      | ns    |

| t <sub>DIS</sub>              | Input or I/O to Output Disabled                                         | 3   | 3.0 |     | 3.5 | 7          | 6.0          | _   | 7.5      | ns    |

| t <sub>AR</sub>               | Input or I/O to Asynch, Reset of Reg.                                   |     | 2.8 |     | 3.5 |            | 5.5          | _   | 9.0      | ns    |

| t <sub>ARW</sub>              | Asysnchronous Reset Pulse Duration                                      | 2.8 | _<  | 3.5 | _   | 5.5        | _            | 7.0 | _        | ns    |

| t <sub>ARR</sub>              | Asysnchronous Reset to CLK↑ Recovery Time                               | 2.5 | 7   | 3.0 | -   | 4.0        | _            | 5.0 | _        | ns    |

| t <sub>SPR</sub>              | Synchronous Preset to CLK↑ Recovery Time                                | 2.5 |     | 3.0 | _   | 4.0        | _            | 5.0 | _        | ns    |

<sup>1.</sup> Refer to Switching Test Conditions section.

Note: Maximum clock input rise and fall time between 10% to 90% of Vout = 2ns.

<sup>2.</sup> Calculated from fmax with internal feedback. Refer to fmax Descriptions section.

<sup>3.</sup> Refer to fmax Descriptions section. Characterized but not 100% tested.

## ispGAL22V10AV/B/C Timing Adders

### **Over Recommended Operating Conditions**

| Adder                          |                                            | -2   | 23   | -2   | 28   | -    | 5    | -7   | <b>'</b> 5 |       |

|--------------------------------|--------------------------------------------|------|------|------|------|------|------|------|------------|-------|

| Туре                           | Description                                | Min. | Max. | Min. | Max. | Min. | Max. | Min. | Max.       | Units |

| t <sub>IOI</sub> Input Adjuste | ers                                        |      |      |      |      |      |      | •    |            |       |

| LVTTL_in                       | Using LVTTL standard                       | _    | 0.6  | _    | 0.6  | _    | 0.6  | _    | 0.6        | ns    |

| LVCMOS33_in                    | Using LVCMOS 3.3 standard                  | _    | 0.6  | _    | 0.6  |      | 0.6  | _    | 0.6        | ns    |

| LVCMOS25_in                    | Using LVCMOS 2.5 standard                  | _    | 0.6  | _    | 0.6  |      | 0.6  | _    | 0.6        | ns    |

| LVCMOS18_in                    | Using LVCMOS 1.8 standard                  | _    | 0    | ~    | 0    | 4    | 0    | -/   | 0          | ns    |

| PCI_in                         | Using PCI compatible input                 | _    | 0.6  | -    | 0.6  |      | 0.6  | 1    | 0.6        | ns    |

| t <sub>IOO</sub> Output Adju   | sters                                      | •    |      |      | V    |      |      |      |            |       |

| LVTTL_out                      | Output configured as TTL buffer            |      | 0.2  | _    | 0.2  |      | 0.2  | 7    | 0.2        | ns    |

| LVCMOS33_out                   | Output configured as 3.3V buffer           |      | 0.2  |      | 0.2  | -(   | 0.2  |      | 0.2        | ns    |

| LVCMOS25_out                   | Output configured as 2.5V buffer           |      | 0.1  |      | 0.1  | _    | 0.1  | 7    | 0.1        | ns    |

| LVCMOS18_out                   | Output configured as 1.8V buffer           | +    | 0    | _    | 0    |      | 0    | _    | 0          | ns    |

| PCI_out                        | Output configured as PCI compatible buffer |      | 0.2  | _    | 0.2  | _    | 0.2  | _    | 0.2        | ns    |

| Slow Slew                      | Output configured for slow slew rate       |      | 1.0  |      | 1.0  |      | 1.0  | _    | 1.0        | ns    |

Note: Open drain timing is the same as corresponding LVCMOS timing.

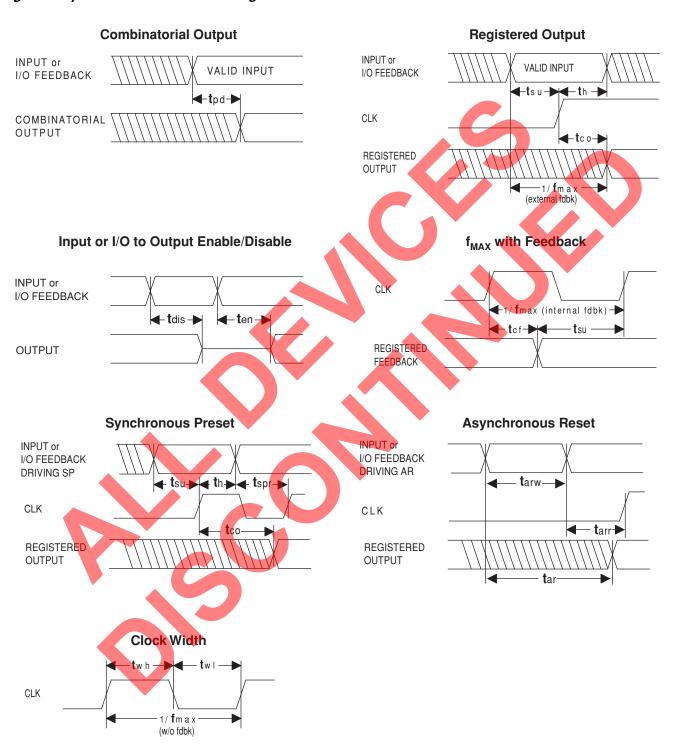

## **Switching Waveforms**

Figure 7. ispGAL22V10AV/B/C Switching Waveforms

## **f<sub>MAX</sub>** Descriptions

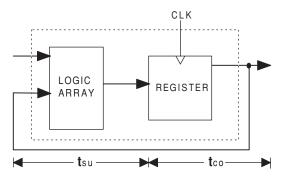

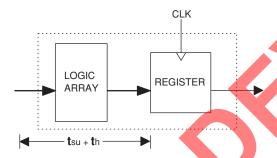

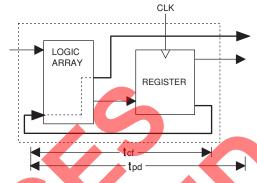

Figure 8. ispGAL22V10AV/B/C f<sub>MAX</sub> Descriptions

#### fmax with External Feedback 1/(tsu+tco)

Note: fmax with external feedback is calculated from measured tsu and tco.

#### fmax with No Feedback

Note: fmax with no feedback may be less than 1/twh + twl. This is to allow for a clock duty cycle of other than 50%.

#### fmax with Internal Feedback 1/(tsu+tcf)

Note: tof is a calculated value, derived by subtracting tsu from the period of imax w/internal feedback (tcf = 1/fmax - tsu). The value of tcf is used primarily when calculating the delay from clocking a register to a combinatorial output (through registered feedback), as shown above. For example, the timing from clock to a combinatorial output is equal to tcf + tpd.

## **Switching Test Conditions**

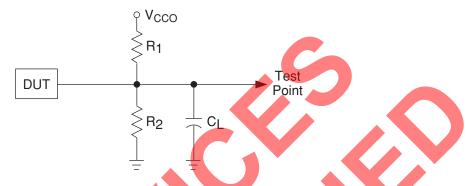

Figure 9 shows the output test load that is used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are shown in Table 1.

Figure 9. Output Test Load, LVTTL and LVCMOS Standards

Table 1. Test Fixture Required Components

| Test Condition               | I/O Standard   | R <sub>1</sub> | R <sub>2</sub> | C <sub>L</sub> <sup>1</sup> | Input<br>Timing Ref. <sup>2</sup> | Output<br>Timing Ref. | v <sub>cco</sub>    |

|------------------------------|----------------|----------------|----------------|-----------------------------|-----------------------------------|-----------------------|---------------------|

| LVCMOS I/O, (L -> H, H -> L) | LVCMOS 3.3     | 106Ω           | 106Ω           | 35pF                        | 1.5V                              | 1.5V                  | 3.0V                |

|                              | LVCMOS 2.5     |                |                |                             | 1.2V                              | V <sub>CCO</sub> /2   | 2.3V                |

|                              | LVCMOS 1.8     |                |                |                             | (V/B) 0.9V                        | V <sub>CCO</sub> /2   | (V/B) 1.65V         |

|                              |                |                |                |                             | (C) V <sub>CC</sub> /2            | V <sub>CCO</sub> /2   | (C) V <sub>CC</sub> |

| LVCMOS I/O (Z -> H)          |                | 106Ω           | 106Ω           | 35pF                        |                                   | Hi-Z + 0.3            | 3.0V                |

| LVCMOS I/O (Z -> L)          |                | 106Ω           | 106Ω           | 35pF                        |                                   | Hi-Z - 0.3            | 3.0V                |

| LVCMOS I/O (H -> Z)          |                | ∞              | 106Ω           | 5pF                         |                                   | V <sub>OH</sub> - 0.3 | 3.0V                |

| LVCMOS I/O (L -> Z)          | S I/O (L -> Z) |                | ∞              | 5pF                         |                                   | V <sub>OL</sub> + 0.3 | 3.0V                |

<sup>1.</sup> C<sub>1</sub> includes test fixtures and probe capacitance.

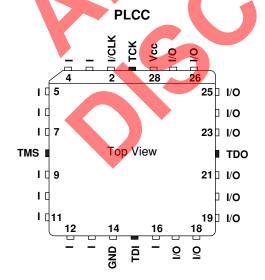

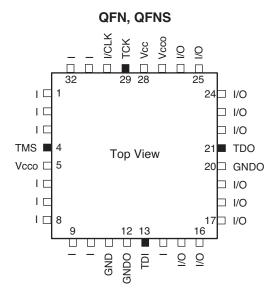

## **Pin Diagrams**

<sup>2.</sup> Input conditions.

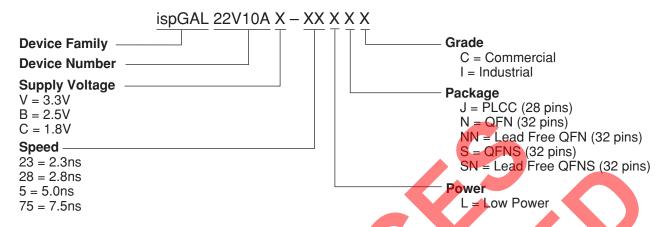

## **Part Number Description**

# Ordering Information

## **Conventional Packaging**

#### Commercial

| Part Number                     | Voltage | t <sub>PD</sub> | Power | Package | Pin Count | Grade |

|---------------------------------|---------|-----------------|-------|---------|-----------|-------|

| ispGAL22V10AV-23LS              | 3.3     | 2.3ns           | Low   | QFNS    | 32        | С     |

| ispGAL22V10AV-23LN <sup>1</sup> | 3.3     | 2.3ns           | Low   | QFN     | 32        | С     |

| ispGAL22V10AV-5LS               | 3.3     | 5.0ns           | Low   | QFNS    | 32        | С     |

| ispGAL22V10AV-5LN <sup>1</sup>  | 3.3     | 5.0ns           | Low   | QFN     | 32        | С     |

| ispGAL22V10AV-75LS              | 3.3     | 7.5ns           | Low   | QFNS    | 32        | С     |

| ispGAL22V10AV-75LN <sup>1</sup> | 3.3     | 7.5ns           | Low   | QFN     | 32        | С     |

| ispGAL22V10AV-28LJ              | 3.3     | 2.8ns           | Low   | PLCC    | 28        | С     |

| ispGAL22V10AV-5LJ               | 3.3     | 5.0ns           | Low   | PLCC    | 28        | С     |

| ispGAL22V10AV-75LJ              | 3.3     | 7.5ns           | Low   | PLCC    | 28        | С     |

| ispGAL22V10AB-23LS              | 2.5     | 2.3ns           | Low   | QFNS    | 32        | С     |

| ispGAL22V10AB-23LN1             | 2.5     | 2.3ns           | Low   | QFN     | 32        | С     |

| ispGAL22V10AB-5LS               | 2.5     | 5.0ns           | Low   | QFNS    | 32        | С     |

| ispGAL22V10AB-5LN1              | 2.5     | 5.0ns           | Low   | QFN     | 32        | С     |

| ispGAL22V10AB-75LS              | 2.5     | 7.5ns           | Low   | QFNS    | 32        | С     |

| ispGAL22V10AB-75LN1             | 2.5     | 7.5ns           | Low   | QFN     | 32        | С     |

| ispGAL22V10AB-28LJ              | 2.5     | 2.8ns           | Low   | PLCC    | 28        | С     |

| ispGAL22V10AB-5LJ               | 2.5     | 5.0ns           | Low   | PLCC    | 28        | С     |

| ispGAL22V10AB-75LJ              | 2.5     | 7.5ns           | Low   | PLCC    | 28        | С     |

| ispGAL22V10AC-23LS              | 1.8     | 2.3ns           | Low   | QFNS    | 32        | С     |

| ispGAL22V10AC-23LN1             | 1.8     | 2.3ns           | Low   | QFN     | 32        | С     |

| ispGAL22V10AC-5LS               | 1.8     | 5.0ns           | Low   | QFNS    | 32        | С     |

| ispGAL22V10AC-5LN1              | 1.8     | 5.0ns           | Low   | QFN     | 32        | С     |

| ispGAL22V10AC-75LS              | 1.8     | 7.5ns           | Low   | QFNS    | 32        | С     |

| ispGAL22V10AC-75LN <sup>1</sup> | 1.8     | 7.5ns           | Low   | QFN     | 32        | С     |

| ispGAL22V10AC-28LJ              | 1.8     | 2.8ns           | Low   | PLCC    | 28        | С     |

| ispGAL22V10AC-5LJ               | 1.8     | 5.0ns           | Low   | PLCC    | 28        | С     |

| ispGAL22V10AC-75LJ              | 1.8     | 7.5ns           | Low   | PLCC    | 28        | С     |

<sup>1.</sup> Use QFNS package. QFN package devices have been discontinued via PCN #13A-08.

#### Industrial

| Part Number                      | Voltage | t <sub>PD</sub> | Power | Package | Pin Count | Grade |

|----------------------------------|---------|-----------------|-------|---------|-----------|-------|

| ispGAL22V10AV-5LSI               | 3.3     | 5.0ns           | Low   | QFNS    | 32        | I     |

| ispGAL22V10AV-5LNI <sup>1</sup>  | 3.3     | 5.0ns           | Low   | QFN     | 32        | I     |

| ispGAL22V10AV-75LSI              | 3.3     | 7.5ns           | Low   | QFNS    | 32        | I     |

| ispGAL22V10AV-75LNI <sup>1</sup> | 3.3     | 7.5ns           | Low   | QFN     | 32        | 1     |

| ispGAL22V10AV-5LJI               | 3.3     | 5.0ns           | Low   | PLCC    | 28        | I     |

| ispGAL22V10AV-75LJI              | 3.3     | 7.5ns           | Low   | PLCC    | 28        | I     |

| ispGAL22V10AB-5LSI               | 2.5     | 5.0ns           | Low   | QFNS    | 32        | 1     |

| ispGAL22V10AB-5LNI <sup>1</sup>  | 2.5     | 5.0ns           | Low   | QFN     | 32        | I     |

| ispGAL22V10AB-75LSI              | 2.5     | 7.5ns           | Low   | QFNS    | 32        |       |

| ispGAL22V10AB-75LNI <sup>1</sup> | 2.5     | 7.5ns           | Low   | QFN     | 32        | 1     |

| ispGAL22V10AB-5LJI               | 2.5     | 5.0ns           | Low   | PLCC    | 28        |       |

| ispGAL22V10AB-75LJI              | 2.5     | 7.5ns           | Low   | PLCC    | 28        |       |

| ispGAL22V10AC-5LSI               | 1.8     | 5.0ns           | Low   | QFNS    | 32        | I     |

| ispGAL22V10AC-5LNI <sup>1</sup>  | 1.8     | 5.0ns           | Low   | QFN     | 32        | I     |

| ispGAL22V10AC-75LSI              | 1.8     | 7.5ns           | Low   | QFNS    | 32        | I     |

| ispGAL22V10AC-75LNI <sup>1</sup> | 1.8     | 7.5ns           | Low   | QFN     | 32        | I     |

| ispGAL22V10AC-5LJI               | 1.8     | 5.0ns           | Low   | PLCC    | 28        | I     |

| ispGAL22V10AC-75LJI              | 1.8     | 7.5ns           | Low   | PLCC    | 28        | I     |

<sup>1.</sup> Use QFNS package. QFN package devices have been discontinued via PCN #13A-08.

### **Lead-Free Packaging**

#### Commercial

| Part Number                      | Voltage | t <sub>PD</sub> | Power | Package | Pin Count | Grade |

|----------------------------------|---------|-----------------|-------|---------|-----------|-------|

| ispGAL22V10AV-23LSN              | 3.3     | 2.3ns           | Low   | QFNS    | 32        | С     |

| ispGAL22V10AV-23LNN <sup>1</sup> | 3.3     | 2.3ns           | Low   | QFN     | 32        | С     |

| ispGAL22V10AV-5LSN               | 3.3     | 5.0ns           | Low   | QFNS    | 32        | С     |

| ispGAL22V10AV-5LNN <sup>1</sup>  | 3.3     | 5.0ns           | Low   | QFN     | 32        | С     |

| ispGAL22V10AV-75LSN              | 3.3     | 7.5ns           | Low   | QFNS    | 32        | С     |

| ispGAL22V10AV-75LNN1             | 3.3     | 7.5ns           | Low   | QFN     | 32        | С     |

<sup>1.</sup> Use QFNS package. QFN package devices have been discontinued via PCN #13A-08.

#### Industrial

| Part Number                       | Voltage | t <sub>PD</sub> | Power | Package | Pin Count | Grade |

|-----------------------------------|---------|-----------------|-------|---------|-----------|-------|

| ispGAL22V10AV-5LSNI               | 3.3     | 5.0ns           | Low   | QFNS    | 32        | I     |

| ispGAL22V10AV-5LNNI <sup>1</sup>  | 3.3     | 5.0ns           | Low   | QFN     | 32        | I     |

| ispGAL22V10AV-75LSNI              | 3.3     | 7.5ns           | Low   | QFNS    | 32        | I     |

| ispGAL22V10AV-75LNNI <sup>1</sup> | 3.3     | 7.5ns           | Low   | QFN     | 32        | I     |

<sup>1.</sup> Use QFNS package. QFN package devices have been discontinued via PCN #13A-08.

Note: For all but the slowest commercial speed grade, the speed grades on these devices are dual marked. For example, the commercial speed grade -5LJ is also marked with the industrial grade -7LJI. The commercial grade is always one speed grade faster than the associated dual mark industrial grade. The slowest commercial speed grade is marked as commercial grade only.

# **Revision History**

| Date          | Version | Change Summary                                                              |

|---------------|---------|-----------------------------------------------------------------------------|

| _             | _       | Previous Lattice releases.                                                  |

| December 2008 | 03.0    | Added 32-pin QFNS package Ordering Part Number information per PCN #13A-08. |

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Lattice:

ISPGAL22V10AC-23LNN