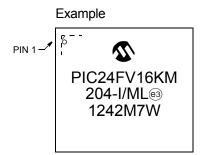

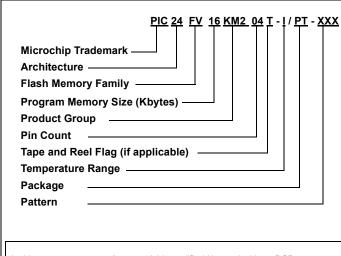

# General Purpose, 16-Bit Flash Microcontroller with XLP Technology Data Sheet

#### **Analog Peripheral Features**

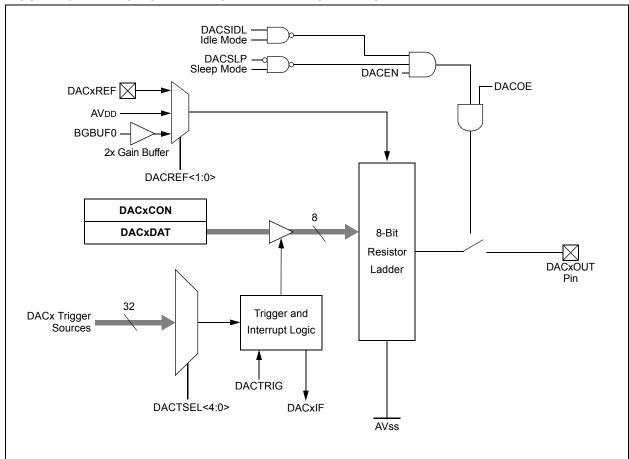

- Up to Two 8-Bit Digital-to-Analog Converters (DAC):

- Soft Reset disable function allows DAC to retain its output value through non-VDD Resets

- Support for Idle mode

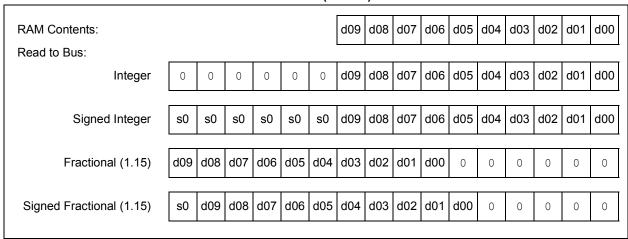

- Support for left and right-justified input data

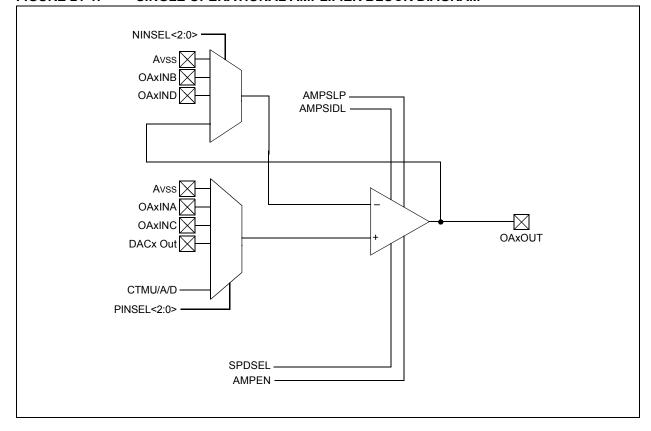

- · Two Operational Amplifiers (Op Amps):

- Differential inputs

- Selectable power/speed levels:

- Low power/low speed

- High power/high speed

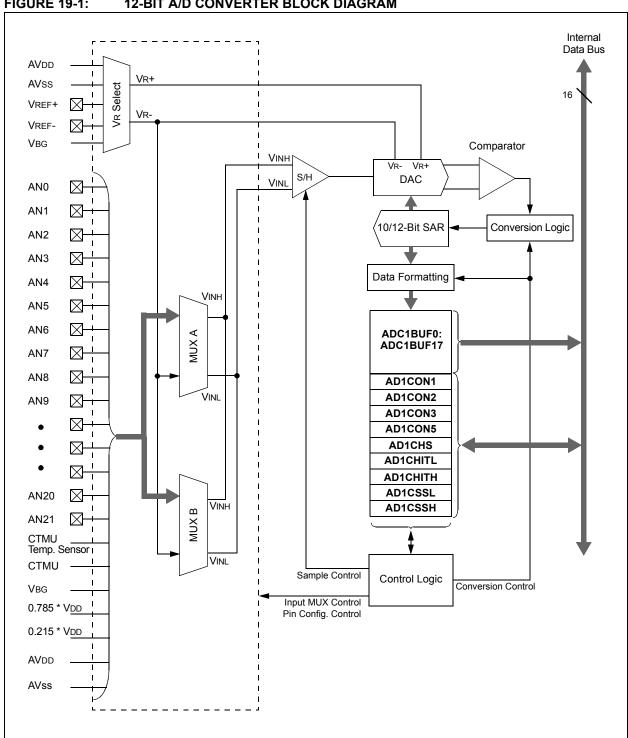

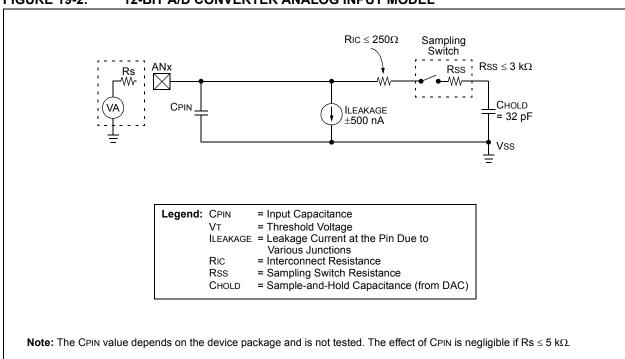

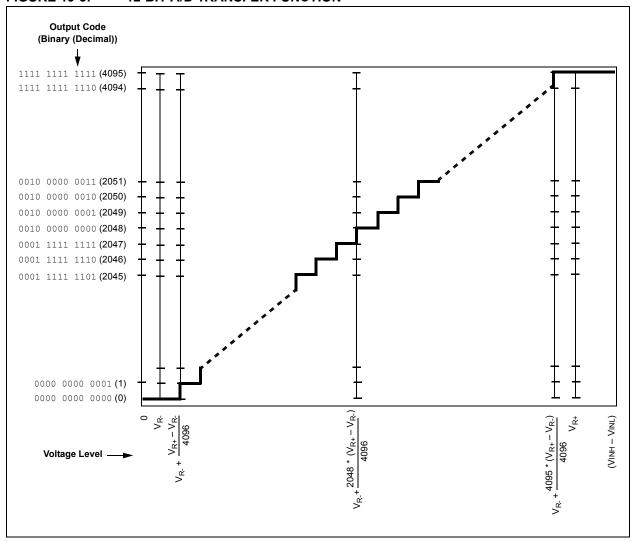

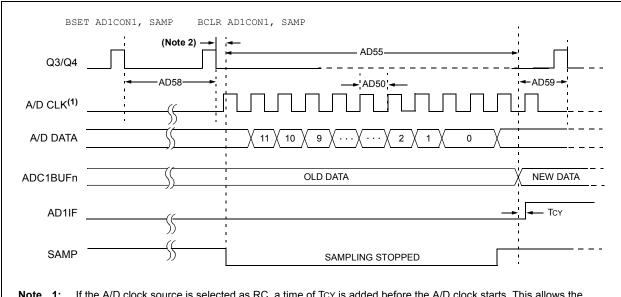

- Up to 22-Channel, 10/12-Bit Analog-to-Digital Converter:

- 100k samples/second at 12-bit conversion rate (single Sample-and-Hold)

- Auto-scan with Threshold Detect

- Can operate during Sleep

- Dedicated band gap reference and temperature sensor input

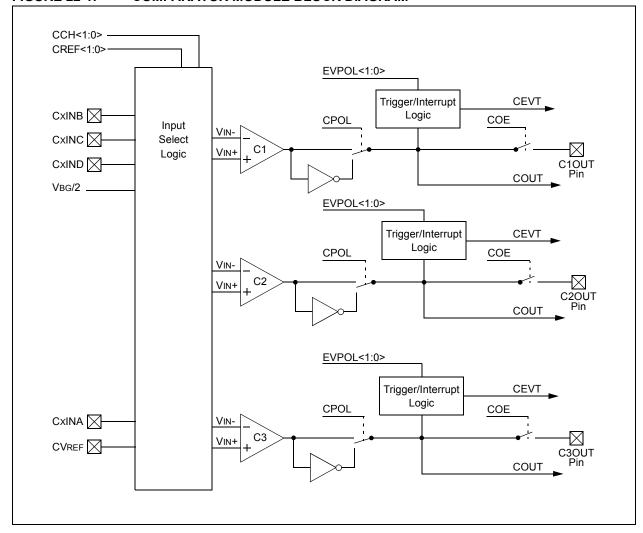

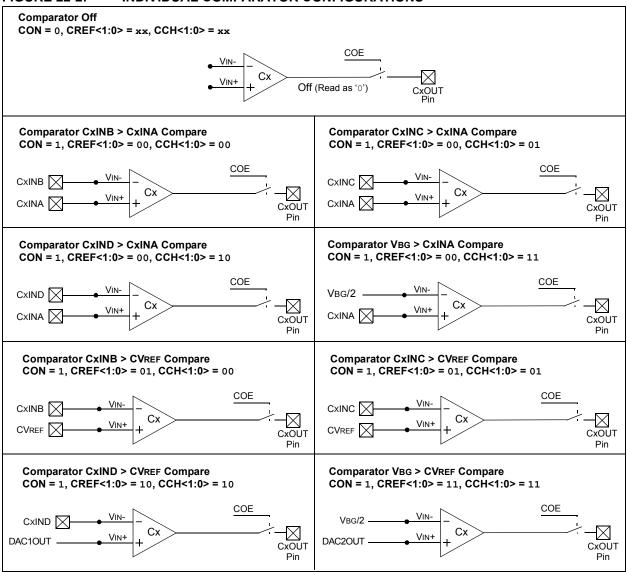

- · Up to Three Rail-to-Rail Analog Comparators:

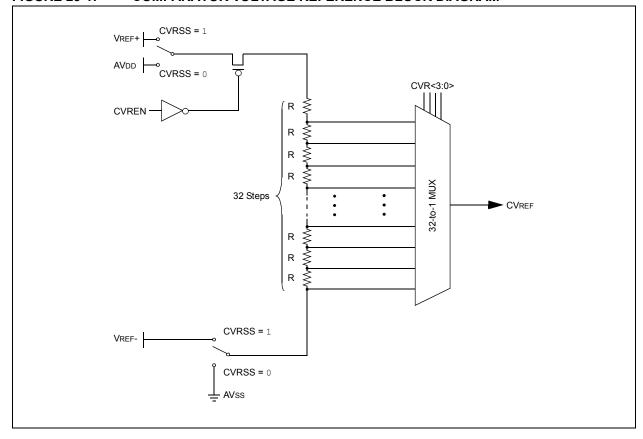

- Programmable reference voltage for comparators

- Band gap reference input

- Flexible input multiplexing

- Low-power or high-speed selection options

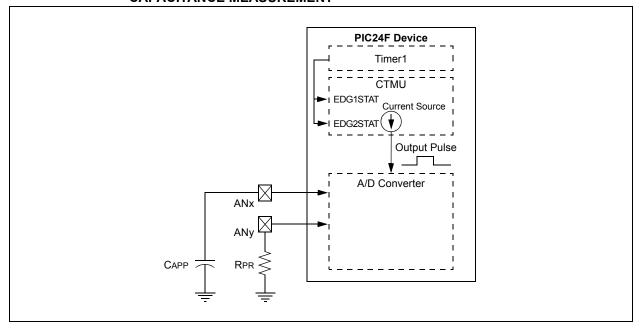

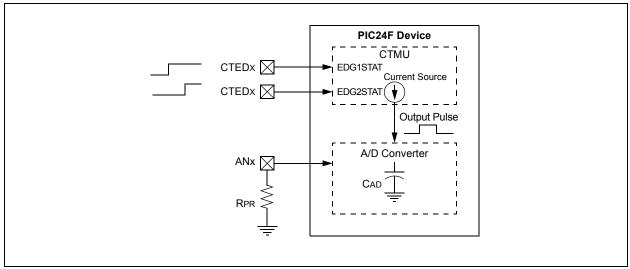

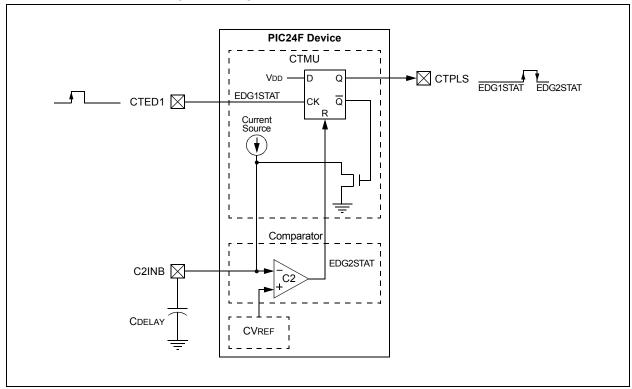

- · Charge Time Measurement Unit (CTMU):

- Capacitive measurement, up to 22 channels

- Time measurement down to 200 ps resolution

- Up to 16 external Trigger pairs

- Internal Temperature Sensor with Dedicated A/D Converter Input

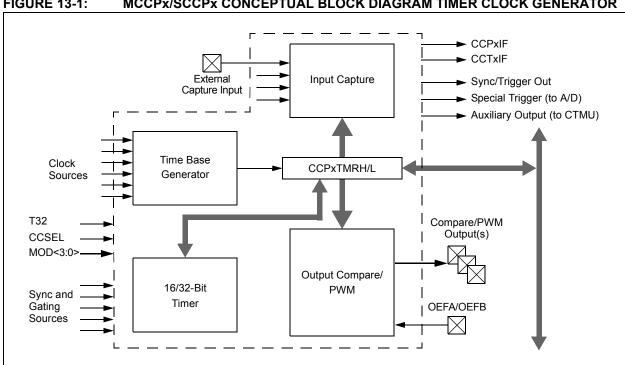

# Multiple/Single Capture Compare Peripheral (MCCP/SCCP) Features

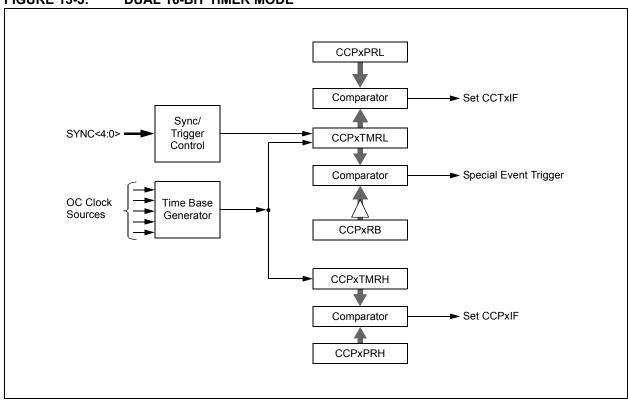

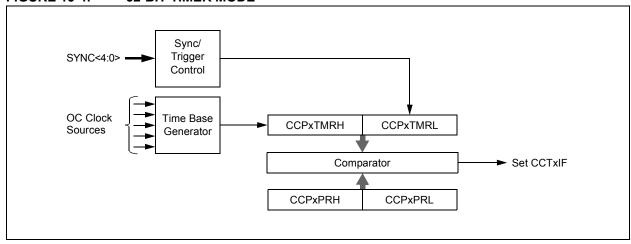

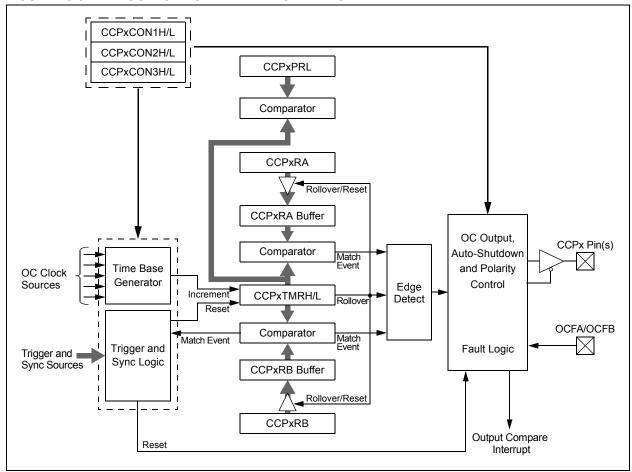

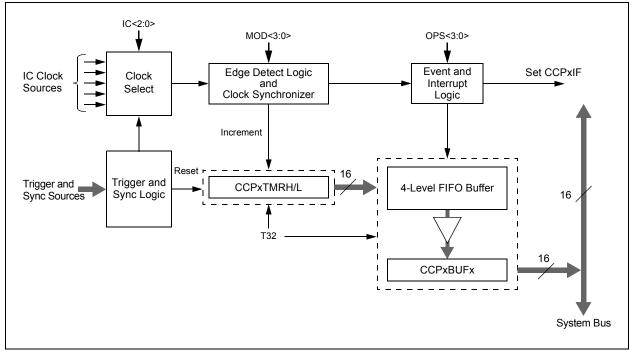

- · 16 or 32-Bit Time Base

- · 16 or 32-Bit Capture

- 4-Deep Capture Buffer

- 16 or 32-Bit Compare:

- Single Edge Compare modes

- Dual Edge Compare/PWM modes

- Center-Aligned Compare mode

- Variable Frequency Pulse mode

- Fully Asynchronous Operation, Available in Sleep modes

- · Single Output Steerable mode (MCCP only)

- Brush DC Forward and Reverse modes (MCCP only)

- Half-Bridge with Dead-Time Delay (MCCP only)

- · Push-Pull PWM mode (MCCP only)

- Auto-Shutdown with Programmable Source and Shutdown State

- · Programmable Output Polarity

|            | Memory Peripherals |                       |              |                 |                   |              |                  |      |      |                     |           |        |             |      |      |     |           |

|------------|--------------------|-----------------------|--------------|-----------------|-------------------|--------------|------------------|------|------|---------------------|-----------|--------|-------------|------|------|-----|-----------|

| Device     | Pins               | Flash Program (bytes) | SRAM (bytes) | EE Data (bytes) | Voltage Range (V) | 16-Bit Timer | 16-Bit MCCP/SCCP | MSSP | UART | 12-Bit A/D Channels | 8-Bit DAC | Op Amp | Comparators | СТМИ | RTCC | CLC | ICD BRKPT |

| 5V Devices |                    |                       |              |                 |                   |              |                  |      |      |                     |           |        |             |      |      |     |           |

| FV16KM204  | 44                 | 16K                   | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| FV16KM202  | 28                 | 16K                   | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| FV08KM204  | 44                 | 8K                    | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| FV08KM202  | 28                 | 8K                    | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| FV16KM104  | 44                 | 16K                   | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 22                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| FV16KM102  | 28                 | 16K                   | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| FV08KM102  | 28                 | 8K                    | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| FV08KM101  | 20                 | 8K                    | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 16                  | _         |        | 1           | Yes  |      | 1   | 3         |

|            |                    |                       |              |                 |                   | 3V           | Devic            | es   |      |                     |           |        |             |      |      |     |           |

| F16KM204   | 44                 | 16K                   | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| F16KM202   | 28                 | 16K                   | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| F08KM204   | 44                 | 8K                    | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| F08KM202   | 28                 | 8K                    | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| F16KM104   | 44                 | 16K                   | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 22                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| F16KM102   | 28                 | 16K                   | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| F08KM102   | 28                 | 8K                    | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| F08KM101   | 20                 | 8K                    | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 16                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

#### **Special Microcontroller Features**

- · Wide Operating Voltage Range Options:

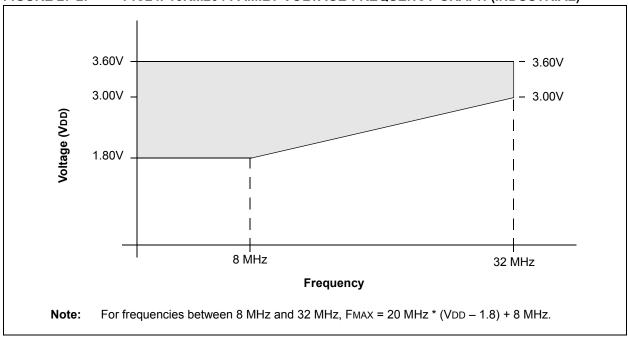

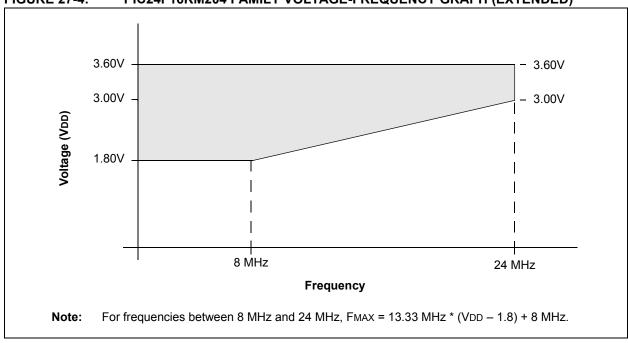

- 1.8V to 3.6V (PIC24F devices)

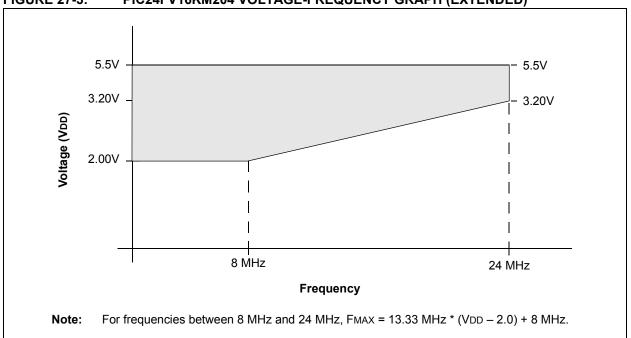

- 2.0V to 5.0V (PIC24FV devices)

- · Selectable Power Management modes:

- Idle: CPU shuts down, allowing for significant power reduction

- Sleep: CPU and peripherals shut down for substantial power reduction and fast wake-up

- Retention Sleep mode: PIC24FV devices can enter Sleep mode, employing the retention regulator, further reducing power consumption

- Doze: CPU can run at a lower frequency than peripherals, a user-programmable feature

- Alternate Clock modes allow on-the-fly switching to a lower clock speed for selective power reduction

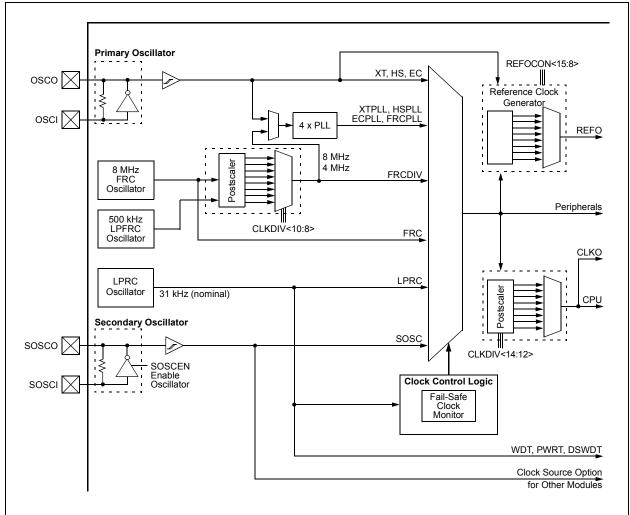

- · Fail-Safe Clock Monitor:

- Detects clock failure and switches to on-chip, low-power RC oscillator

- Ultra Low-Power Wake-up Pin Provides an External Trigger for Wake from Sleep

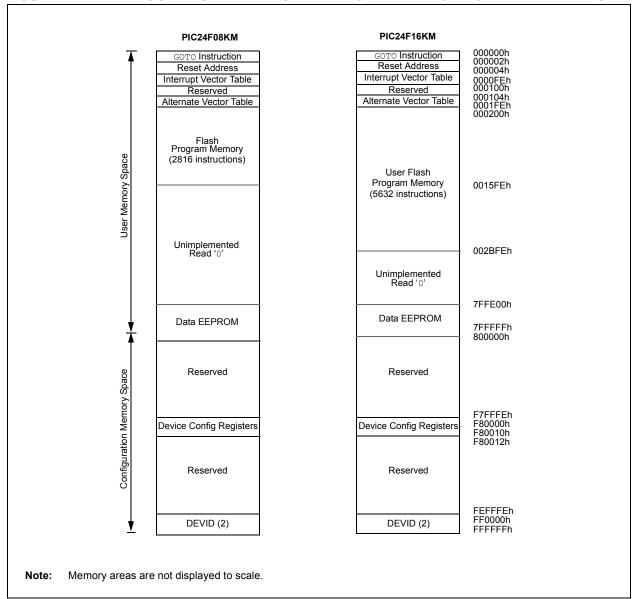

- 10,000 Erase/Write Cycle Endurance Flash Program Memory, Typical

- 100,000 Erase/Write Cycle Endurance Data EEPROM, Typical

- Flash and Data EEPROM Data Retention: 20 Years Minimum

- · Self-Programmable under Software Control

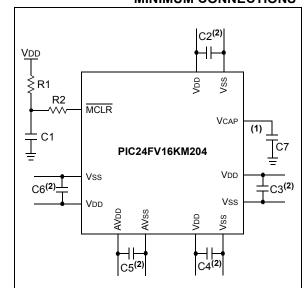

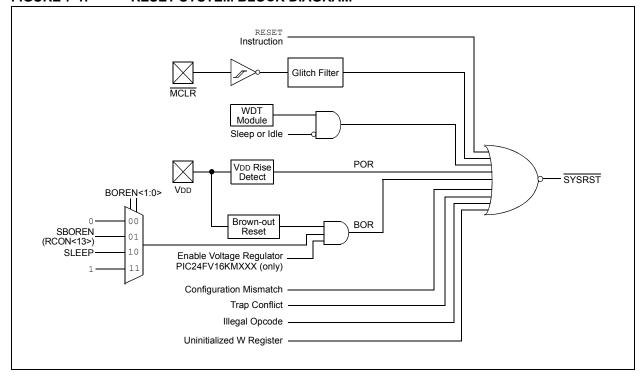

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

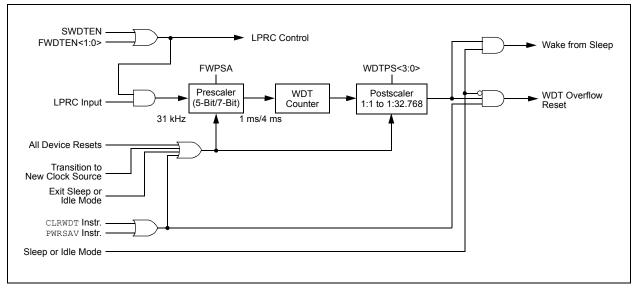

- Watchdog Timer (WDT) with its Own On-Chip RC Oscillator for Reliable Operation

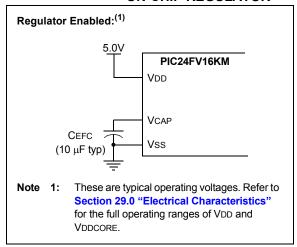

- · On-Chip Regulator for 5V Operation

- · Selectable Windowed WDT Feature

- · Selectable Oscillator Options including:

- 4x Phase Locked Loop (PLL)

- 8 MHz (FRC) Internal RC Oscillator:

- HS/EC, high-speed crystal/resonator oscillator or external clock

- In-Circuit Serial Programming™ (ICSP™) and In-Circuit Emulation (ICE) – via Two Pins

- · In-Circuit Debugging

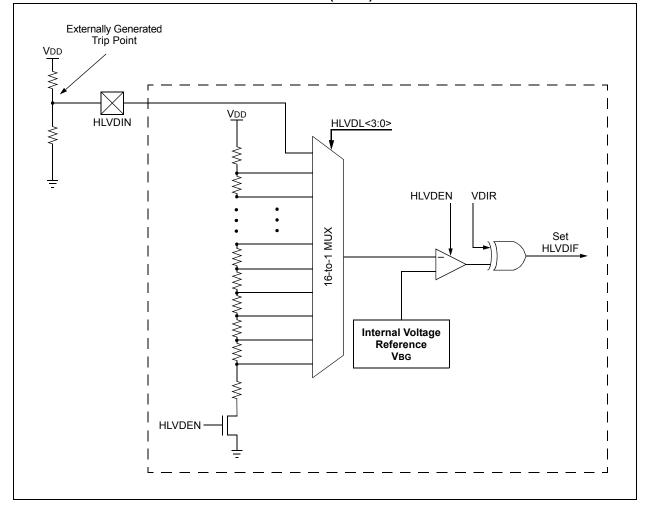

- Programmable High/Low-Voltage Detect (HLVD) module

- · Programmable Brown-out Reset (BOR):

- Software enable feature

- Configurable shutdown in Sleep

- Auto-configures power mode and sensitivity based on device operating speed

- LPBOR available for re-arming of the POR

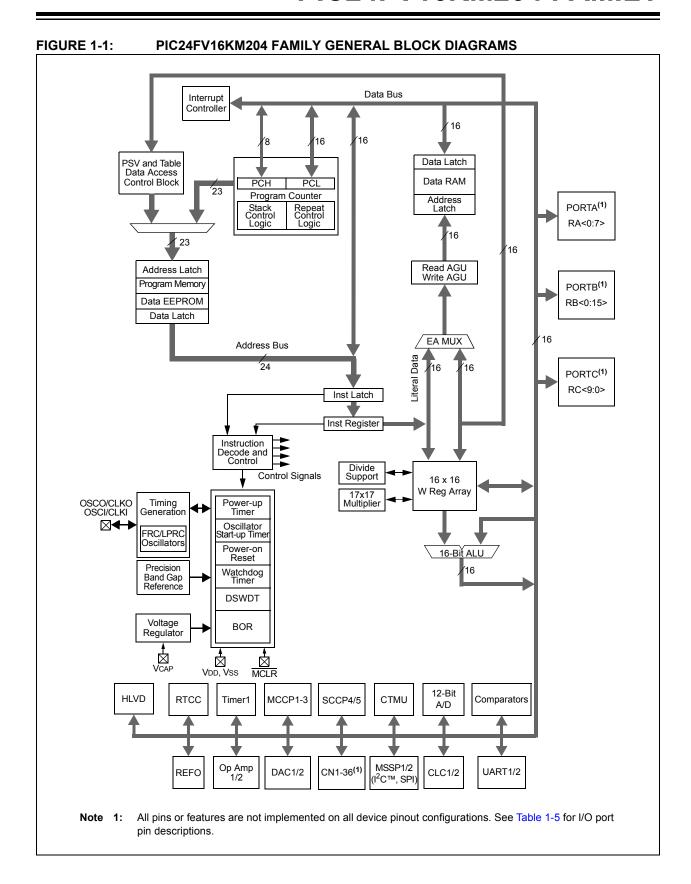

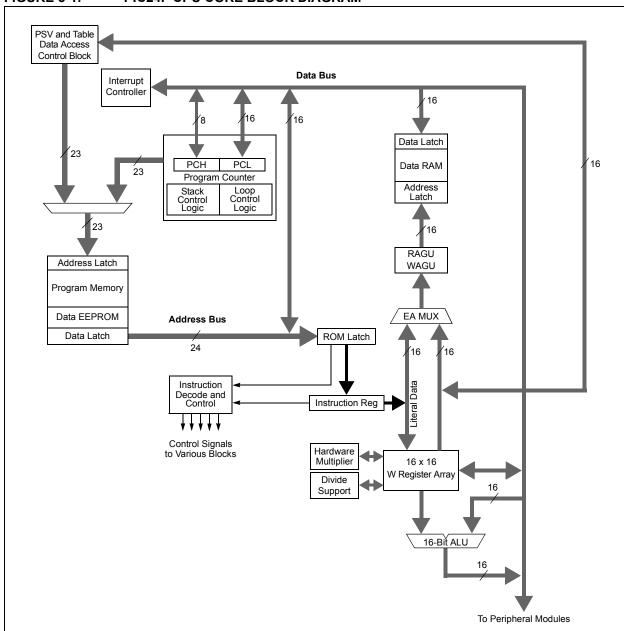

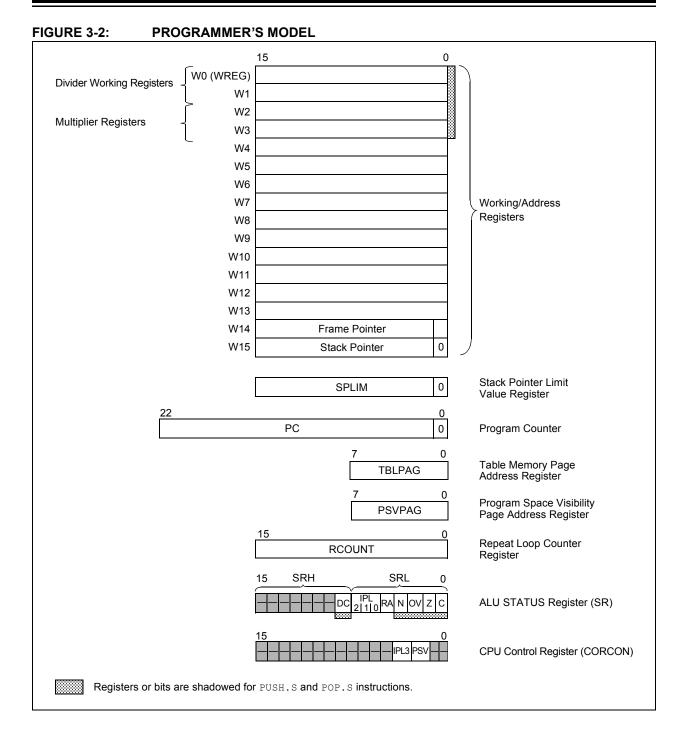

#### **High-Performance RISC CPU**

- · Modified Harvard Architecture

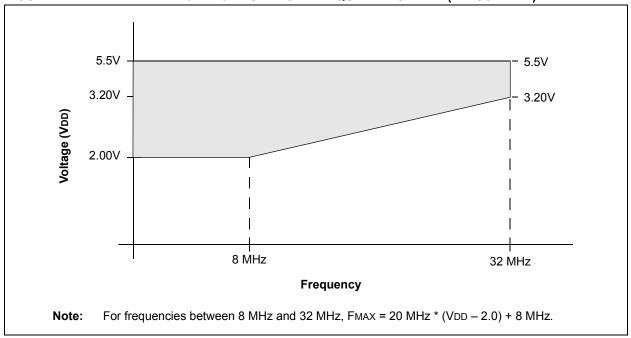

- · Operating Speed:

- DC 32 MHz clock input

- 16 MIPS at 32 MHz clock input

- · 8 MHz Internal Oscillator:

- 4x PLL option

- Multiple clock divide options

- Fast start-up

- 17-Bit x 17-Bit Single-Cycle Hardware Fractional/Integer Multiplier

- · 32-Bit by 16-Bit Hardware Divider

- 16 x 16-Bit Working Register Array

- · C Compiler Optimized Instruction Set Architecture

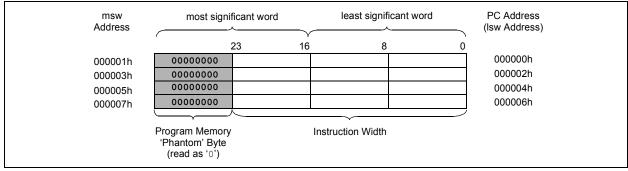

- · 24-Bit-Wide Instructions

- · 16-Bit-Wide Data Path

- Linear Program Memory Addressing, up to 6 Mbytes

- Linear Data Memory Addressing, up to 64 Kbytes

- Two Address Generation Units (AGUs) for Separate Read and Write Addressing of Data Memory

#### **Peripheral Features**

- · High-Current Sink/Source, 18 mA/18 mA All Ports

- Independent Ultra Low-Power, 32 kHz Timer Oscillator

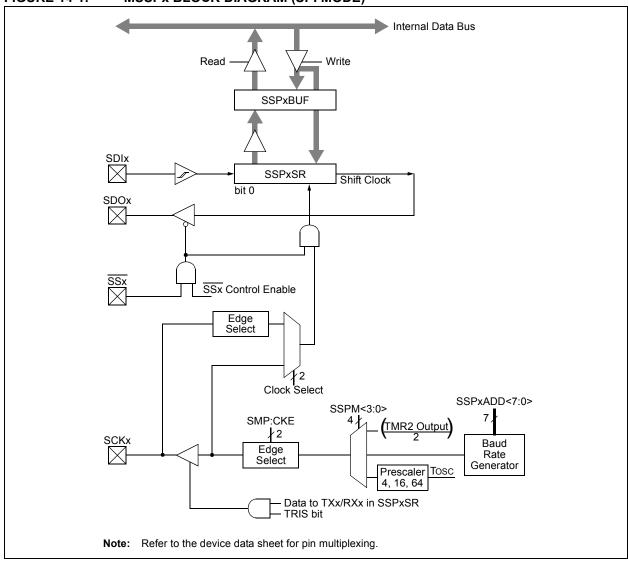

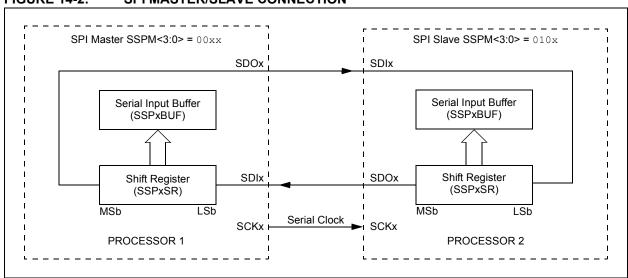

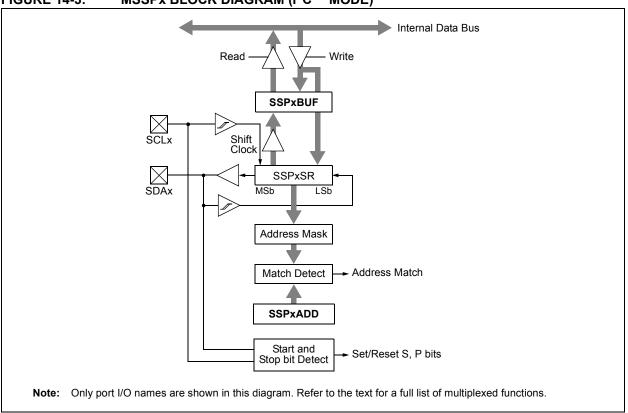

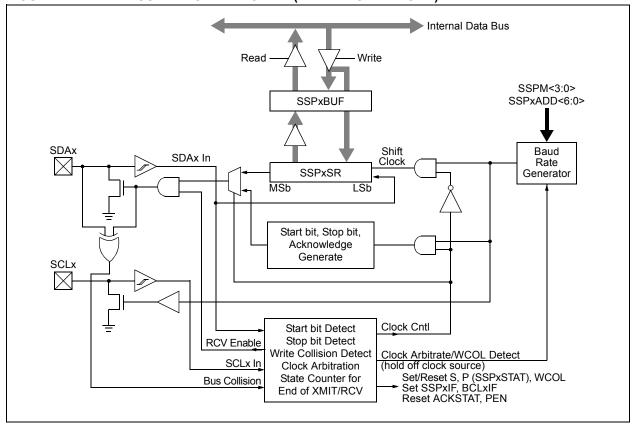

- Up to Two Master Synchronous Serial Ports (MSSPs) with SPI and I<sup>2</sup>C™ modes:

In SPI mode:

- User-configurable SCKx and SDOx pin outputs

- Daisy-chaining of SPI slave devices

In I<sup>2</sup>C mode:

- Serial clock synchronization (clock stretching)

- Bus collision detection and will arbitrate accordingly

- Support for 16-bit read/write interface

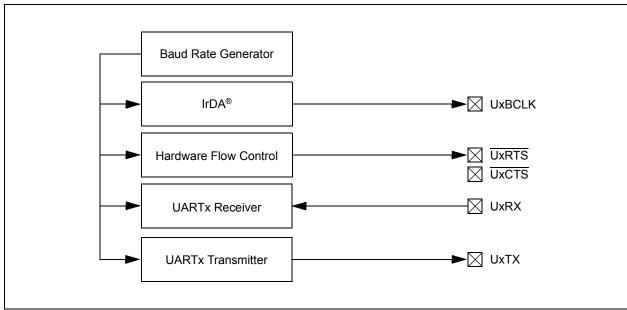

- Up to Two Enhanced Addressable UARTs:

- LIN/J2602 bus support (auto-wake-up, Auto-Baud Detect, Break character support)

- High and low speed (SCI)

- IrDA® mode (hardware encoder/decoder function)

- · Two External Interrupt Pins

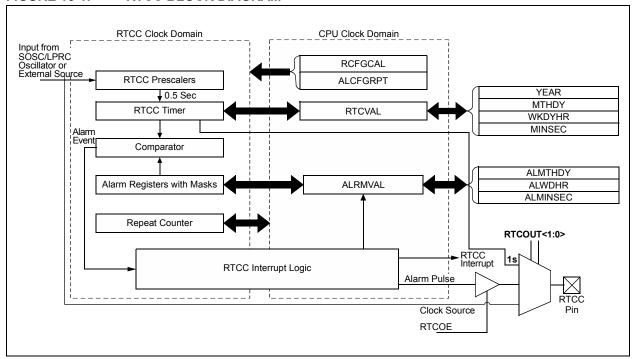

- Hardware Real-Time Clock and Calendar (RTCC)

- Configurable Reference Clock Output (REFO)

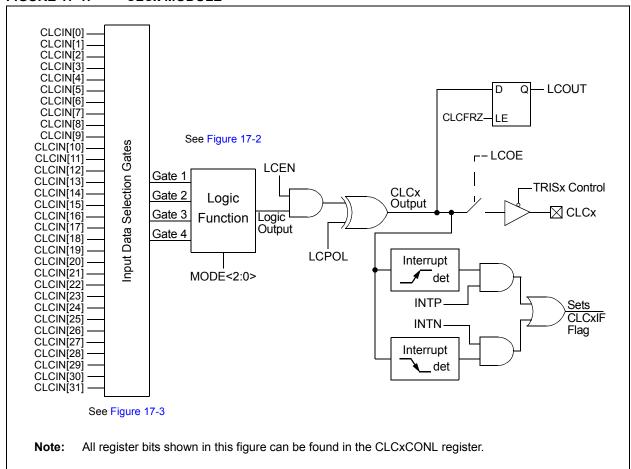

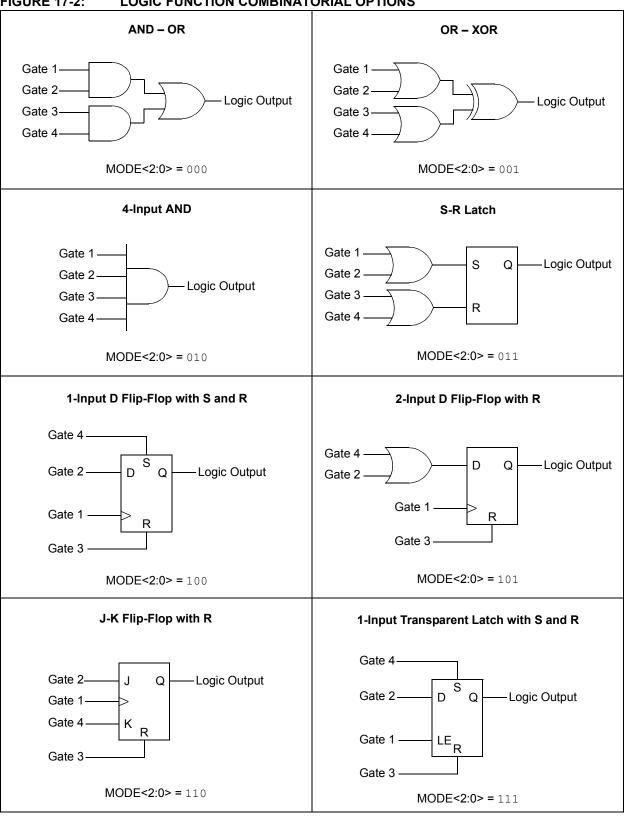

- Two Configurable Logic Cells (CLC)

- Up to Two Single Output Capture/Compare/PWM (SCCP) modules and up to Three Multiple Output Capture/Compare/PWM (MCCP) modules

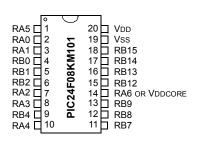

### **Pin Diagrams**

#### 20-Pin SPDIP/SSOP/SOIC

|     | Pin Features                                 |                                            |  |  |  |  |  |  |  |  |

|-----|----------------------------------------------|--------------------------------------------|--|--|--|--|--|--|--|--|

| Pin | PIC24F08KM101                                | PIC24FVKM08KM101                           |  |  |  |  |  |  |  |  |

| 1   | MCLR/Vpp/RA5                                 |                                            |  |  |  |  |  |  |  |  |

| 2   | PGC2/CVREF+/VREF+/AN0/CN2/RA0                |                                            |  |  |  |  |  |  |  |  |

| 3   | PGD2/CVREF-/VREF-/AN1/CN3/RA1                |                                            |  |  |  |  |  |  |  |  |

| 4   | PGD1/AN2/CTCMP/ULPWU/C1IND/OC2A/CN4/RB0      |                                            |  |  |  |  |  |  |  |  |

| 5   | PGC1/AN3/C1INC/CTED12/CN5/RB1                |                                            |  |  |  |  |  |  |  |  |

| 6   | AN4/U1RX/TCKIB/CTED13/CN6/RB2                |                                            |  |  |  |  |  |  |  |  |

| 7   | OSCI/CLKI/AN13/C1INB/CN30/RA2                |                                            |  |  |  |  |  |  |  |  |

| 8   | OSCO/CLKO/AN14/C1INA/CN29/RA3                |                                            |  |  |  |  |  |  |  |  |

| 9   | PGD3/SOSCI/AN15/CLCINA/CN1/RB4               |                                            |  |  |  |  |  |  |  |  |

| 10  | PGC3/SOSCO/SCLKI/AN16/PWRLCLK/CLCINB/CN0/RA4 |                                            |  |  |  |  |  |  |  |  |

| 11  | AN19/U1TX/CTED1/INT0/CN23/RB7                | AN19/U1TX/IC1/OC1A/CTED1/INT0/CN23/RB7     |  |  |  |  |  |  |  |  |

| 12  | AN20/SCL1/U1CTS/OC1B/CTED10/CN22/RB8         | ·                                          |  |  |  |  |  |  |  |  |

| 13  | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/CLC1O/CTED4  | /CN21/RB9                                  |  |  |  |  |  |  |  |  |

| 14  | IC1/OC1A/INT2/CN8/RA6                        | VCAP OR VDDCORE                            |  |  |  |  |  |  |  |  |

| 15  | AN12/HLVDIN/SCK1/OC1C/CTED2/CN14/RB12        | AN12/HLVDIN/SCK1/OC1C/CTED2/INT2/CN14/RB12 |  |  |  |  |  |  |  |  |

| 16  | AN11/SDO1/OCFB/OC1D/CTPLS/CN13/RB13          | ·                                          |  |  |  |  |  |  |  |  |

| 17  | CVREF/AN10/SDI1/C1OUT/OCFA/CTED5/INT1/CN12/R | B14                                        |  |  |  |  |  |  |  |  |

| 18  | AN9/REFO/SS1/TCKIA/CTED6/CN11/RB15           |                                            |  |  |  |  |  |  |  |  |

| 19  | Vss/AVss                                     |                                            |  |  |  |  |  |  |  |  |

| 20  | VDD/AVDD                                     |                                            |  |  |  |  |  |  |  |  |

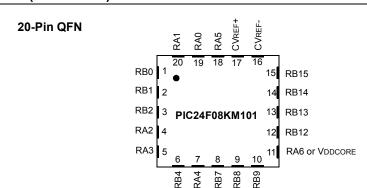

### Pin Diagrams (Continued)

| Pin | Pin Features                                                         |                                            |  |  |  |  |  |  |  |

|-----|----------------------------------------------------------------------|--------------------------------------------|--|--|--|--|--|--|--|

| Pin | PIC24F08KM101                                                        | PIC24FV08KM101                             |  |  |  |  |  |  |  |

| 1   | PGD1/AN2/CTCMP/ULPWU/C1IND/OC2A/CN4/RB0                              |                                            |  |  |  |  |  |  |  |

| 2   | PGC1/AN3/C1INC/CTED12/CN5/RB1                                        |                                            |  |  |  |  |  |  |  |

| 3   | AN4/U1RX/TCKIB/CTED13/CN6/RB2                                        |                                            |  |  |  |  |  |  |  |

| 4   | OSCI/CLKI/AN13/C1INB/CN30/RA2                                        |                                            |  |  |  |  |  |  |  |

| 5   | OSCO/CLKO/AN14/C1INA/CN29/RA3                                        |                                            |  |  |  |  |  |  |  |

| 6   | PGD3/SOSCI/AN15/CLCINA/CN1/RB4                                       |                                            |  |  |  |  |  |  |  |

| 7   | PGC3/SOSCO/SCLKI/AN16/PWRLCLK/CLCINB/CN0/RA4                         |                                            |  |  |  |  |  |  |  |

| 8   | AN19/U1TX/CTED1/INT0/CN23/RB7 AN19/U1TX/IC1/OC1A/CTED1/INT0/CN23/RB7 |                                            |  |  |  |  |  |  |  |

| 9   | AN20/SCL1/U1CTS/OC1B/CTED10/CN22/RB8                                 |                                            |  |  |  |  |  |  |  |

| 10  | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/CLC10/CTED4/CN21                     | I/RB9                                      |  |  |  |  |  |  |  |

| 11  | IC1/OC1A/INT2/CN8/RA6                                                | VCAP OR VDDCORE                            |  |  |  |  |  |  |  |

| 12  | AN12/HLVDIN/SCK1/OC1C/CTED2/CN14/RB12                                | AN12/HLVDIN/SCK1/OC1C/CTED2/INT2/CN14/RB12 |  |  |  |  |  |  |  |

| 13  | AN11/SDO1/OCFB/OC1D/CTPLS/CN13/RB13                                  |                                            |  |  |  |  |  |  |  |

| 14  | CVREF/AN10/SDI1/C1OUT/OCFA/CTED5/INT1/CN12/RB14                      |                                            |  |  |  |  |  |  |  |

| 15  | AN9/REFO/SS1/TCKIA/CTED6/CN11/RB15                                   |                                            |  |  |  |  |  |  |  |

| 16  | Vss/AVss                                                             |                                            |  |  |  |  |  |  |  |

| 17  | VDD/AVDD                                                             |                                            |  |  |  |  |  |  |  |

| 18  | MCLR/VPP/RA5                                                         | MCLR/VPP/RA5                               |  |  |  |  |  |  |  |

| 19  | PGC2/CVREF+ /VREF+/AN0/CN2/RA0                                       | PGC2/CVREF+ /VREF+/AN0/CN2/RA0             |  |  |  |  |  |  |  |

| 20  | PGD2/CVREF-/VREF-/AN1/CN3/RA1                                        | PGD2/CVRef-/VRef-/AN1/CN3/RA1              |  |  |  |  |  |  |  |

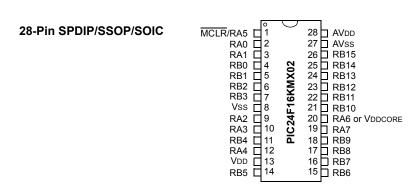

#### Pin Diagrams (Continued)

| 5.  | Pin Features                                                                                                                                                   |                                    |  |  |  |  |  |  |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|--|--|--|--|--|--|

| Pin | PIC24FXXKMX02                                                                                                                                                  | PIC24FVXXKMX02                     |  |  |  |  |  |  |  |  |  |

| 1   | MCLR/Vpp/RA5                                                                                                                                                   |                                    |  |  |  |  |  |  |  |  |  |

| 2   | CVREF+/VREF+/DAC1REF+/AN0/C3INC/CN2/RA0                                                                                                                        |                                    |  |  |  |  |  |  |  |  |  |

| 3   | CVREF-/VREF-/AN1/CN3/RA1 CVREF-/VREF-/AN1/RA1                                                                                                                  |                                    |  |  |  |  |  |  |  |  |  |

| 4   | PGD1/AN2/CTCMP/ULPWU/C1IND/C2INB/C3IND/U2TX/CN4/RE                                                                                                             | 30                                 |  |  |  |  |  |  |  |  |  |

| 5   | PGC1/OA1INA/OA2INA/AN3/C1INC/C2INA/U2RX/CTED12/CN5/                                                                                                            | RB1                                |  |  |  |  |  |  |  |  |  |

| 6   | OA1INB/OA2INB/AN4/C1INB/C2IND/SDA2/U1RX/TCKIB/CTED1                                                                                                            | 3/CN6/RB2                          |  |  |  |  |  |  |  |  |  |

| 7   | OA1OUT/AN5/C1INA/C2INC/SCL2/CN7/RB3                                                                                                                            |                                    |  |  |  |  |  |  |  |  |  |

| 8   | Vss                                                                                                                                                            |                                    |  |  |  |  |  |  |  |  |  |

| 9   | OSCI/CLKI/AN13/CN30/RA2                                                                                                                                        |                                    |  |  |  |  |  |  |  |  |  |

| 10  | OSCO/CLKO/AN14/CN29/RA3                                                                                                                                        |                                    |  |  |  |  |  |  |  |  |  |

| 11  | SOSCI/AN15/U2RTS/U2BCLK/CN1/RB4                                                                                                                                |                                    |  |  |  |  |  |  |  |  |  |

| 12  | SOSCO/SCLKI/AN16/PWRLCLK/U2CTS/CN0/RA4                                                                                                                         |                                    |  |  |  |  |  |  |  |  |  |

| 13  | VDD                                                                                                                                                            |                                    |  |  |  |  |  |  |  |  |  |

| 14  | PGD3/AN17/ASDA1/SCK2/IC4/OC1E/CLCINA/CN27/RB5                                                                                                                  |                                    |  |  |  |  |  |  |  |  |  |

| 15  | PGC3/AN18/ASCL1/SDO2/IC5/OC1F/CLCINB/CN24/RB6                                                                                                                  |                                    |  |  |  |  |  |  |  |  |  |

| 16  | AN19/U1TX/INT0/CN23/RB7                                                                                                                                        | AN19/U1TX/C2OUT/OC1A/INT0/CN23/RB7 |  |  |  |  |  |  |  |  |  |

| 17  | AN20/SCL1/U1CTS/C3OUT/OC1B/CTED10/CN22/RB8                                                                                                                     |                                    |  |  |  |  |  |  |  |  |  |

| 18  | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/OC4/CLC1O/CTED4/CN                                                                                                             | 21/RB9                             |  |  |  |  |  |  |  |  |  |

| 19  | SDI2/IC1/OC5/CLC2O/CTED3/CN9/RA7                                                                                                                               |                                    |  |  |  |  |  |  |  |  |  |

| 20  | C2OUT/OC1A/CTED1/INT2/CN8/RA6                                                                                                                                  | VCAP OR VDDCORE                    |  |  |  |  |  |  |  |  |  |

| 21  | PGD2/SDI1/OC3A/OC1C/CTED11/CN16/RB10                                                                                                                           |                                    |  |  |  |  |  |  |  |  |  |

| 22  | PGC2/SCK1/OC2A/CTED9/CN15/RB11                                                                                                                                 |                                    |  |  |  |  |  |  |  |  |  |

| 23  | DAC1OUT/AN12/HLVDIN/SS2/IC3/OC2B/CTED2/CN14/RB12  DAC1OUT/AN12/HLVDIN/SS2/IC3/OC2B/CTED2/INT2/CN14/RB12  DAC1OUT/AN12/HLVDIN/SS2/IC3/OC2B/CTED2/INT2/CN14/RB12 |                                    |  |  |  |  |  |  |  |  |  |

| 24  | OA1INC/OA2INC/AN11/SDO1/OCFB/OC3B/OC1D/CTPLS/CN13.                                                                                                             | /RB13                              |  |  |  |  |  |  |  |  |  |

| 25  | DAC2OUT/CVREF/OA1IND/OA2IND/AN10/C3INB/RTCC/C1OUT/                                                                                                             | OCFA/CTED5/INT1/CN12/RB14          |  |  |  |  |  |  |  |  |  |

| 26  | DAC2REF+/OA2OUT/AN9/C3INA/REFO/SS1/TCKIA/CTED6/CN                                                                                                              | 11/RB15                            |  |  |  |  |  |  |  |  |  |

| 27  | Vss/AVss                                                                                                                                                       |                                    |  |  |  |  |  |  |  |  |  |

| 28  | VDD/AVDD                                                                                                                                                       | VDD/AVDD                           |  |  |  |  |  |  |  |  |  |

Legend: Values in red indicate pin function differences between PIC24F(V)XXKM202 and PIC24F(V)XXKM102 devices.

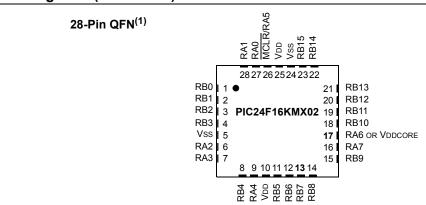

### Pin Diagrams (Continued)

| Pin - | PIC24FXXKMX02                                                               |                                                       |  |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|--|--|

| 1     |                                                                             |                                                       |  |  |  |  |  |  |

|       | PGD1/AN2/CTCMP/ULPWU/C1IND/C2INB/C3IND/U2TX/CN4/RB0                         |                                                       |  |  |  |  |  |  |

| 2     | PGC1/OA1INA/OA2INA/AN3/C1INC/C2INA/U2RX/CTED12/CN5                          | 5/RB1                                                 |  |  |  |  |  |  |

| 3     | OA1INB/OA2INB/AN4/C1INB/C2IND/SDA2/U1RX/TCKIB/CTED                          | 13/CN6/RB2                                            |  |  |  |  |  |  |

| 4     | OA1OUT/AN5/C1INA/C2INC/SCL2/CN7/RB3                                         |                                                       |  |  |  |  |  |  |

| 5     | Vss                                                                         |                                                       |  |  |  |  |  |  |

| 6     | OSCI/CLKI/AN13/CN30/RA2                                                     |                                                       |  |  |  |  |  |  |

| 7     | OSCO/CLKO/AN14/CN29/RA3                                                     |                                                       |  |  |  |  |  |  |

| 8     | SOSCI/AN15/U2RTS/U2BCLK/CN1/RB4                                             |                                                       |  |  |  |  |  |  |

| 9     | SOSCO/SCLKI/AN16/PWRLCLK/U2CTS/CN0/RA4                                      |                                                       |  |  |  |  |  |  |

| 10    | VDD                                                                         |                                                       |  |  |  |  |  |  |

| 11    | PGD3/AN17/ASDA1/SCK2/IC4/OC1E/CLCINA/CN27/RB5                               |                                                       |  |  |  |  |  |  |

| 12    | PGC3/AN18/ASCL1/SDO2/IC5/OC1F/CLCINB/CN24/RB6                               |                                                       |  |  |  |  |  |  |

| 13    | AN19/U1TX/INT0/CN23/RB7                                                     | AN19/U1TX/C2OUT/OC1A/INT0/CN23/RB7                    |  |  |  |  |  |  |

| 14    | AN20/SCL1/U1CTS/C3OUT/OC1B/CTED10/CN22/RB8                                  |                                                       |  |  |  |  |  |  |

| 15    | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/OC4/CLC1O/CTED4/Ct                          | N21/RB9                                               |  |  |  |  |  |  |

| 16    | SDI2/IC1/OC5/CLC2O/CTED3/CN9/RA7                                            |                                                       |  |  |  |  |  |  |

| 17    | C2OUT/OC1A/CTED1/INT2/CN8/RA6                                               | VDDCORE/VCAP                                          |  |  |  |  |  |  |

| 18    | PGD2/SDI1/OC3A/OC1C/CTED11/CN16/RB10                                        |                                                       |  |  |  |  |  |  |

| 19    | PGC2/SCK1/OC2A/CTED9/CN15/RB11                                              |                                                       |  |  |  |  |  |  |

| 20    | DAC1OUT/AN12/HLVDIN/SS2/IC3/OC2B/CTED2/CN14/RB12                            | DAC1OUT/AN12/HLVDIN/SS2/IC3/OC2B/CTED2/INT2/CN14/RB12 |  |  |  |  |  |  |

| 21    | OA1INC/OA2INC/AN11/SDO1/OCFB/OC3B/OC1D/CTPLS/CN13                           | 3/RB13                                                |  |  |  |  |  |  |

| 22    | DAC2OUT/CVREF/OA1IND/OA2IND/AN10/C3INB/RTCC/C1OUT/OCFA/CTED5/INT1/CN12/RB14 |                                                       |  |  |  |  |  |  |

| 23    | DAC2REF+/OA2OUT/AN9/C3INA/REFO/SS1/TCKIA/CTED6/CN11/RB15                    |                                                       |  |  |  |  |  |  |

| 24    | Vss                                                                         |                                                       |  |  |  |  |  |  |

| 25    | VDD                                                                         |                                                       |  |  |  |  |  |  |

| 26    | MCLR/VPP/RA5                                                                |                                                       |  |  |  |  |  |  |

| 27    | CVREF+/VREF+/DAC1REF+/AN0/C3INC/CN2/RA0                                     | CVREF+/VREF+/DAC1REF+/AN0/C3INC/CTED1/CN2/RA0         |  |  |  |  |  |  |

| 28    | CVREF-/VREF-/AN1/CN3/RA1                                                    | CVREF-/VREF-/AN1/CN3/RA1                              |  |  |  |  |  |  |

$\textbf{Legend:} \qquad \text{Values in } \\ \textbf{red} \\ \text{ indicate pin function differences between PIC24F(V)} \\ \textbf{XXKM202} \\ \text{ and PIC24F(V)} \\ \textbf{XXKM102} \\ \text{ devices.} \\ \\ \textbf{Volume for the pin function differences between PIC24F(V)} \\ \textbf{Volume for the pin function differences between PIC24F(V)} \\ \textbf{Volume for the pin function differences between PIC24F(V)} \\ \textbf{XXKM202} \\ \textbf{Available for the pin function differences between PIC24F(V)} \\ \textbf{XXKM202} \\ \textbf{Available for the pin function differences between PIC24F(V)} \\ \textbf{XXKM202} \\ \textbf{Available for the pin function differences between PIC24F(V)} \\ \textbf{XXKM202} \\ \textbf{Available for the pin function differences between PIC24F(V)} \\ \textbf{XXKM202} \\ \textbf{Available for the pin function differences between PIC24F(V)} \\ \textbf{XXKM202} \\ \textbf{Available for the pin function differences between PIC24F(V)} \\ \textbf{XXKM202} \\ \textbf{Available for the pin function differences between PIC24F(V)} \\ \textbf{XXKM202} \\ \textbf{Available for the pin function differences between PIC24F(V)} \\ \textbf{XXKM202} \\ \textbf{Available for the pin function differences} \\ \textbf{Available for the pin function difference$

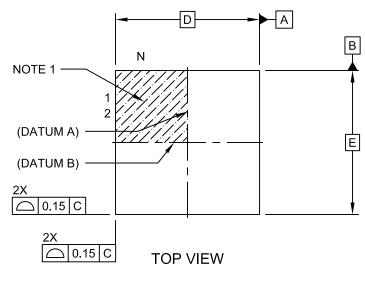

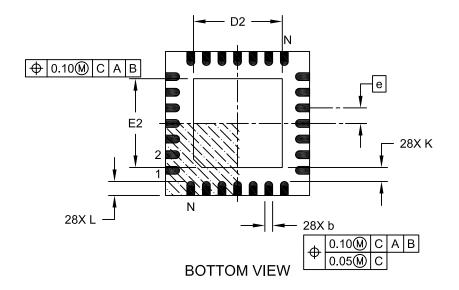

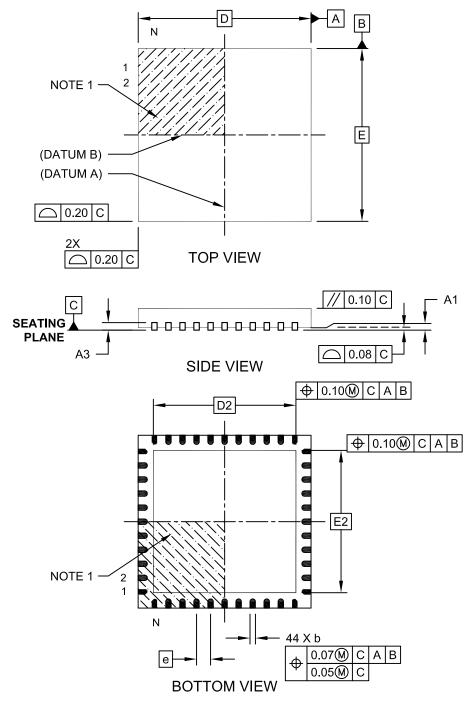

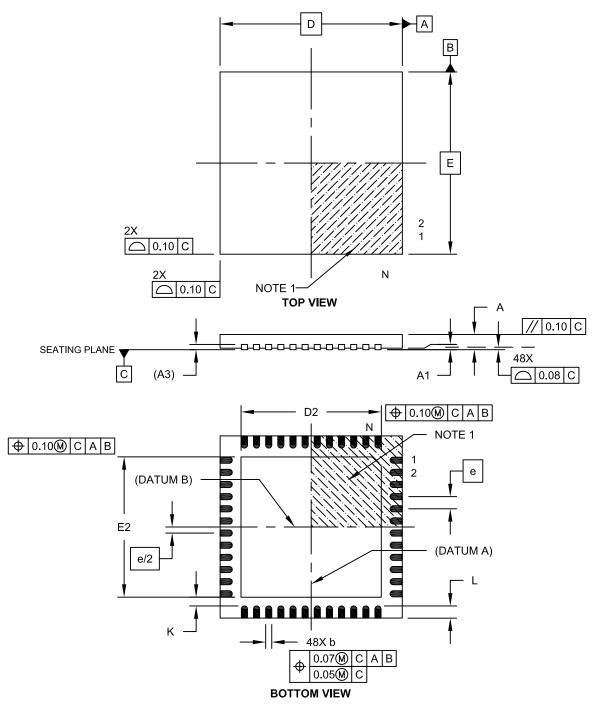

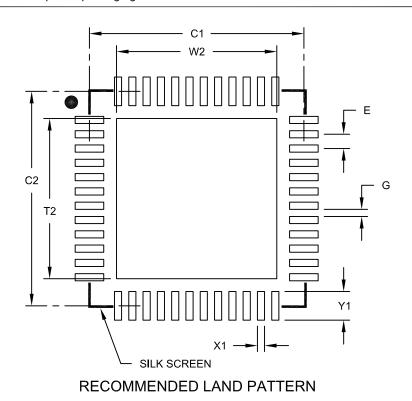

Note 1: Exposed pad on underside of device is connected to Vss.

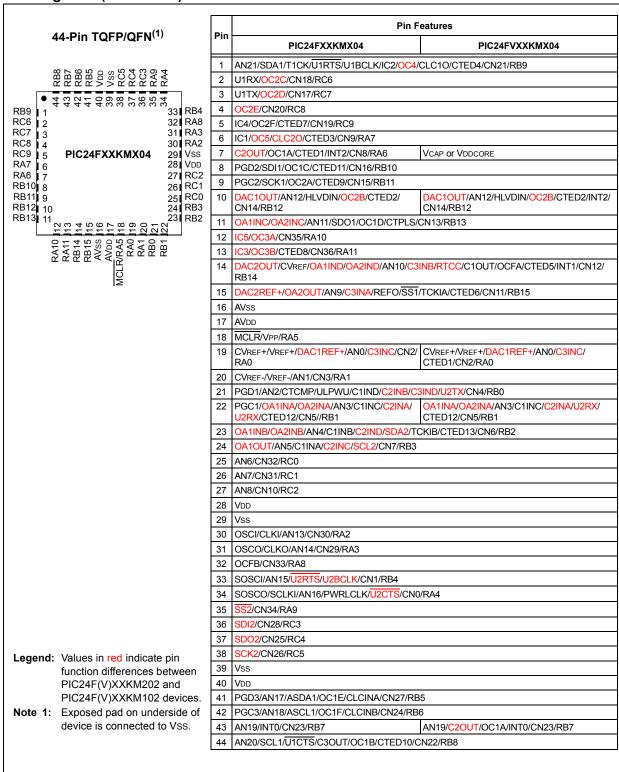

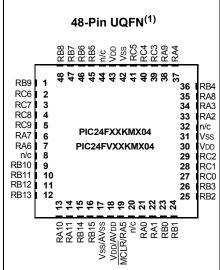

#### Pin Diagrams (Continued)

### **Pin Diagrams (Continued)**

| D:  | Pin Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                   |  |  |  |  |  |  |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Pin | PIC24FXXKMX04 PIC24FVXXKMX04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                   |  |  |  |  |  |  |  |  |  |

| 1   | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/OC4/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CLC1O/CTED4/CN21/RB9                              |  |  |  |  |  |  |  |  |  |

| 2   | U1RX/OC2C/CN18/RC6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                   |  |  |  |  |  |  |  |  |  |

| 3   | U1TX/OC2D/CN17/RC7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                   |  |  |  |  |  |  |  |  |  |

| 4   | OC2/CN20/RC8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                   |  |  |  |  |  |  |  |  |  |

| 5   | IC4/OC2F/CTED7/CN19/RC9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                   |  |  |  |  |  |  |  |  |  |

| 6   | IC1/OC5/CLC2O/CTED3/CN9/RA7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                   |  |  |  |  |  |  |  |  |  |

| 7   | VDDCORE or VCAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C2OUT/OC1A/CTED1/INT2/CN8/RA6                     |  |  |  |  |  |  |  |  |  |

| 8   | n/c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | n/c                                               |  |  |  |  |  |  |  |  |  |

| 9   | PGD2/SDI1/OC1C/CTED11/CN16/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                   |  |  |  |  |  |  |  |  |  |

| 10  | PGC2/SCK1/OC2A/CTED9/CN15/RB11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                   |  |  |  |  |  |  |  |  |  |

| 11  | DAC1OUT/AN12/HLVDIN/OC2B/CTED2/<br>CN14/RB12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DAC1OUT/AN12/HLVDIN/OC2B/CTED2/INT2/CN14/RB12     |  |  |  |  |  |  |  |  |  |

| 12  | OA1INC/OA2INC/AN11/SDO1/OC1D/CTPLS/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CN13/RB13                                         |  |  |  |  |  |  |  |  |  |

| 13  | IC5/OC3A/CN35/RA10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                   |  |  |  |  |  |  |  |  |  |

| 14  | IC3/OC3B/CTED8/CN36/RA11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                   |  |  |  |  |  |  |  |  |  |

| 15  | DAC2OUT/CVREF/OA1IND/OA2IND/AN10/C3INB/RTCC/C1OUT/OCFA/CTED5/INT1/CN12/RB14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                   |  |  |  |  |  |  |  |  |  |

| 16  | DAC2REF+/OA2OUT/AN9/C3INA/REFO/SS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | /TCKIA/CTED6/CN11/RB15                            |  |  |  |  |  |  |  |  |  |

| 17  | Vss/AVss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                   |  |  |  |  |  |  |  |  |  |

| 18  | VDD/AVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                   |  |  |  |  |  |  |  |  |  |

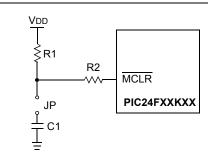

| 19  | MCLR/Vpp/RA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                   |  |  |  |  |  |  |  |  |  |