# LMP7312 Precision SPI-Programmable AFE with Differential/Single-Ended Input/Output

Check for Samples: LMP7312

### **FEATURES**

- Typical Values,  $T_A = 25^{\circ}C$ ,  $V^{+}=5V$ ,  $V^{-}=0V$ .

- Gain Bandwidth 1 MHz

- Input Voltage Range (G= 0.096 V/V) -15V to +15V

- Core Op-Amp Input Offset Voltage 100 µV

- Supply Current 2 mA (Max)

- Gain (Attenuation Mode) 0.096 V/V, 0.192 V/V0.384 V/V, 0.768 V/V

- Gain (Amplification Mode) 1 V/V, 2 V/V

- Gain Error 0.035% (Max)

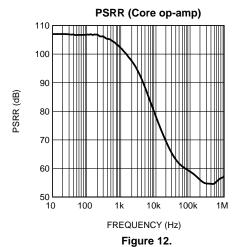

- Core Op-Amp PSRR 90 dB (Min)

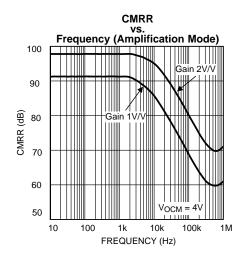

- CMRR 80 dB (min)

- Adjustable Output Common Mode 1V to 4V

- Temperature Range −40 to 125°C

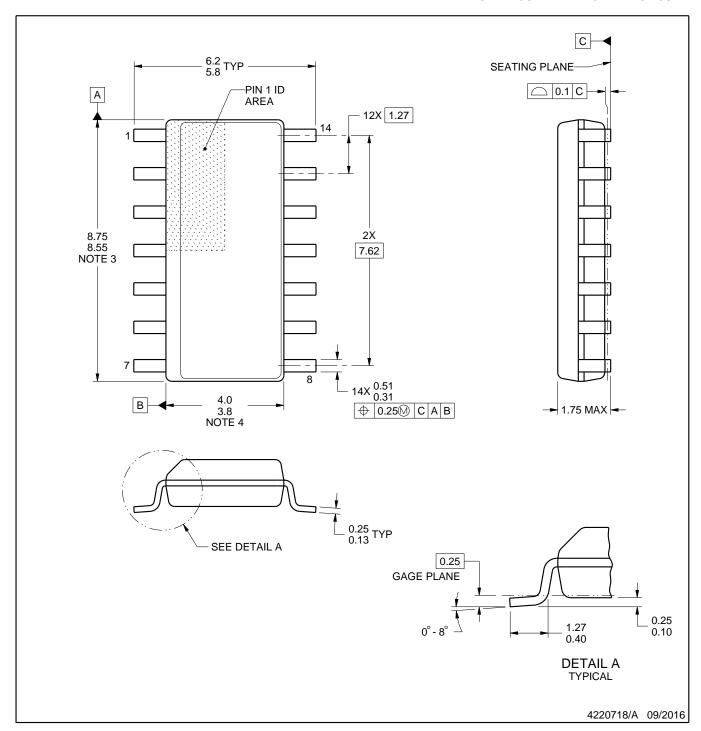

- Package 14-Pin SOIC

#### **APPLICATIONS**

- Signal Conditioning AFE

- ±10V; ±5V; 0-5V; 0-10V; 0-20mA; 4-20mA

- **Data Acquisition Systems**

- **Motor Control**

- **Instrument and Process Control**

- Remote Sensing

- **Programmable Automation Control**

#### DESCRIPTION

The LMP7312 is a digitally programmable variable gain amplifier/attenuator. Its wide input voltage range and superior precision make it a prime choice for applications requiring high accuracy such as data acquisition systems for IO modules in programmable logic control (PLC). The LMP7312 provides a differential output to maximize dynamic range and signal to noise ratio, thereby reducing the overall system error. It can also be configured to handle single ended input data converters by means of the V<sub>OCM</sub> pin (see Application Section for details). The inputs of LMP7312 can be configured in attenuation mode to handle large input signals of up to +/- 15V, as well as in amplification mode to handle current loops of 0-20mA and 4-20mA. The LMP7312 is equipped with a null switch to evaluate the offset of the internal amplifier. A ensured 0.035% maximum gain error (for all gains) and a maximum gain drift of 5ppm over the extended industrial temperature range (-40° to 125°C) make the LMP7312 very attractive for high precision systems even under harsh conditions. A low input offset voltage of 100µV and low voltage noise of 3µVpp give the LMP7312 a superior performance. The LMP7312 is fully specified from -40° to 125°C and is available in SOIC-14 package.

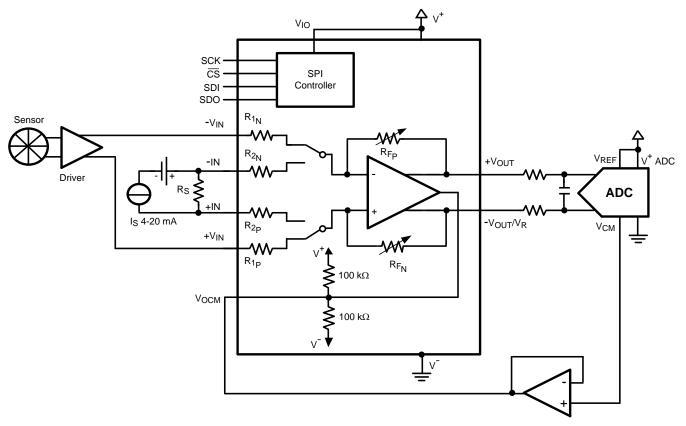

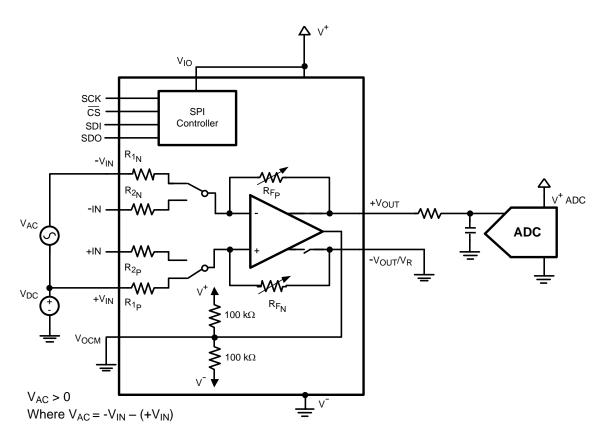

# **Typical Application**

LMP™ is a trademark of Texas Instruments Corporation.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## Absolute Maximum Ratings (1)(2)

| ESD Rating (3)                                                              |                |

|-----------------------------------------------------------------------------|----------------|

| Human Body Model                                                            | 2000V          |

| Machine Body Model                                                          | 150V           |

| Charge device Model                                                         | 1000V          |

| Analog Supply Voltage (V <sub>S</sub> = V <sup>+</sup> - V <sup>-</sup> )   | 6V             |

| Digital Supply Voltage (V <sub>DIO</sub> =V <sub>IO</sub> -V <sup>-</sup> ) | 6V             |

| Attenuation pins -V <sub>IN</sub> , +V <sub>IN</sub> referred to V          | ±17.5V         |

| Amplification pins -IN, +IN referred to V                                   | ±10V           |

| Voltage at all other pins referred to V                                     | 6V             |

| Storage Temperature Range                                                   | -65°C to 150°C |

| For soldering specification: http://www.ti.com/lit/SNOA549                  |                |

| Junction Temperature                                                        | 150°C          |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but for which specific performance is not ensured. For ensured specifications and the test conditions, see Electrical Characteristics.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (3) Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC). Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

## Operating Ratings (1)

| - p                                                                                               |                 |

|---------------------------------------------------------------------------------------------------|-----------------|

| Analog Supply Voltage $(V_S = V^+ - V^-)$ , $V^-=0V$                                              | 4.5V to 5.5V    |

| Digital Supply Voltage (V <sub>DIO</sub> = V <sub>IO</sub> - V <sup>-</sup> ), V <sup>-</sup> =0V | 2.7V to 5.5V    |

| Attenuation pins -V <sub>IN</sub> , +V <sub>IN</sub> referred to V <sup>-</sup>                   | -15V to 15V     |

| Amplification pins -IN, +IN referred to V                                                         | -2.35V to 7.35V |

| Temperature Range (2)                                                                             | -40°C to 125°C  |

| Package Thermal Resistance (2)                                                                    | ·               |

| SOIC-14                                                                                           | 145°C/W         |

|                                                                                                   |                 |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but for which specific performance is not ensured. For ensured specifications and the test conditions, see Electrical Characteristics.

- (2) The maximum power dissipation is a function of TJ(max), θJA. The maximum allowable power dissipation at any ambient temperature is: PD(max) = (TJ(max) TA)/ θJA. All numbers apply for packages soldered directly onto a PC Board.

### 5V Electrical Characteristics (1)

Unless otherwise specified, all limits ensured for  $T_A = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V_{IO} = 5V$ ,  $V^- = 0V$ , G = 0.192 V/V,  $V_{CM\_ATT} = (+V_{IN} + (-V_{IN}))/2$ ,  $V_{CM\_AMP} = (+IN + (-IN))/2$ . Differential output configuration. SE = Single Ended Output, DE = Differential Output. **Boldface** limits apply at the temperature extremes.

| Symbol | Parameter                           | Conditions                                                                                                         | Min <sup>(2)</sup>  | Typ <sup>(3)</sup> | Max <sup>(2)</sup> | Units |

|--------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------|--------------------|--------------------|-------|

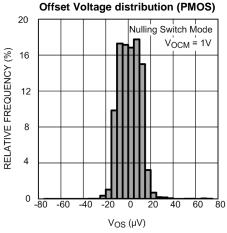

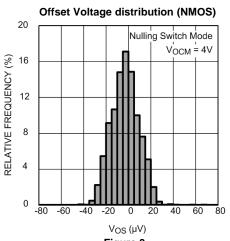

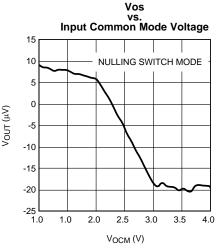

| Vos    | Core op-amp Input<br>Offset Voltage | Nulling Switch Mode, DE, V <sub>OCM</sub> = 1V;<br>Nulling switch Mode, SE, -V <sub>OUT</sub> /V <sub>R</sub> = 1V | −100<br><b>−250</b> |                    | 100<br><b>250</b>  | \/    |

|        |                                     | Nulling Switch Mode, DE, V <sub>OCM</sub> = 4V;<br>Nulling Switch Mode, SE, -V <sub>OUT</sub> /V <sub>R</sub> = 4V | −100<br><b>−250</b> |                    | 100<br><b>250</b>  | μV    |

- (1) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. No ensured specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where T<sub>J</sub> > T<sub>A</sub>.

- (2) All limits are specified by testing, design, or statistical analysis.

- (3) Typical values represent the most likely parametric norm at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

# 5V Electrical Characteristics (1) (continued)

Unless otherwise specified, all limits ensured for  $T_A = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V_{IO} = 5V$ ,  $V^- = 0V$ , G = 0.192 V/V,  $V_{CM\_ATT} = (+V_{IN} + (-V_{IN}))/2$ ,  $V_{CM\_AMP} = (+IN + (-IN))/2$ . Differential output configuration. SE = Single Ended Output, DE = Differential Output. **Boldface** limits apply at the temperature extremes.

| Symbol                                  | Parameter                                         | Conditions                                                                                                         | Min <sup>(2)</sup>       | Typ <sup>(3)</sup> | Max <sup>(2)</sup>    | Units            |

|-----------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------|-----------------------|------------------|

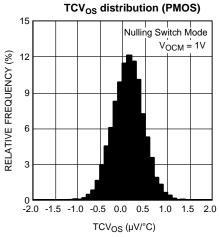

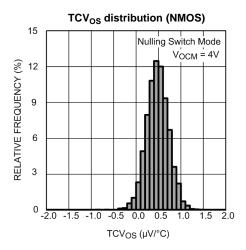

| TCV <sub>OS</sub>                       | Core op-amp Input<br>Offset Voltage (4)           | Nulling Switch Mode, DE, V <sub>OCM</sub> = 1V;<br>Nulling Switch Mode, SE, -V <sub>OUT</sub> /V <sub>R</sub> = 1V | -3                       | ±1.5               | 3                     | \//00            |

|                                         |                                                   | Nulling Switch Mode, DE, V <sub>OCM</sub> = 4V;<br>Nulling Switch Mode, SE, -V <sub>OUT</sub> /V <sub>R</sub> = 4V | -3                       | ±1.5               | 3                     | μV/°C            |

| Av                                      | Gain Error                                        | All gains, $R_L = 10 \text{ k}\Omega$ , $C_L = 50 \text{pF}$ , SE / DE                                             | -0.035<br>- <b>0.045</b> |                    | 0.035<br><b>0.045</b> | %                |

|                                         | Gain Drift                                        | SE / DE                                                                                                            | -5                       | ±1                 | 5                     | ppm/°C           |

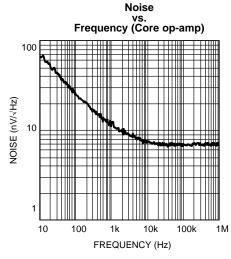

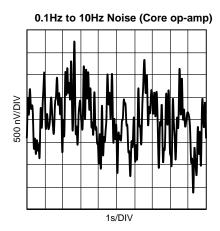

| e <sub>n</sub>                          | Core op-amp Voltage<br>Noise Density              | RTI, Nulling Switch Mode, f = 10 kHz                                                                               |                          | 7.25               |                       | nV/√Hz           |

|                                         | Core op-amp Peak to<br>Peak Voltage Noise         | RTI, Nulling Switch Mode, f= 0.1Hz to 10Hz                                                                         |                          | 3                  |                       | μV <sub>PP</sub> |

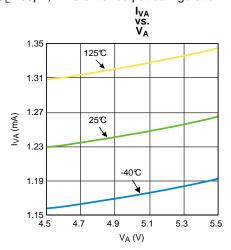

| $I_{VA}$                                | Analog Supply Current                             | $+V_{IN} = -V_{IN} = V_{OCM}$                                                                                      |                          |                    | 2                     | mA               |

| I <sub>VIO</sub>                        | Digital Supply Current                            | Without any load connected to SDO pin                                                                              |                          |                    | 120                   | μΑ               |

| R <sub>IN_CM</sub>                      | CM Input Resistance                               | G= 0.192 V/V                                                                                                       |                          | 62.08              |                       | kΩ               |

|                                         |                                                   | G= 1 V/V                                                                                                           |                          | 40                 |                       |                  |

| R <sub>IN_DIFF</sub> Differential Input |                                                   | G= 0.192 V/V                                                                                                       |                          | 248.3              |                       | kΩ               |

| _                                       | Resistance                                        | G= 1 V/V                                                                                                           |                          | 160                |                       |                  |

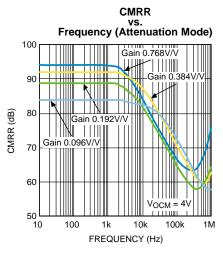

|                                         | DC Common Mode<br>Rejection Ratio                 | G= 0.096V/V, -15V < V <sub>CM ATT</sub> < 15V, SE / DE                                                             |                          |                    |                       |                  |

|                                         |                                                   | G= 0.192V/V, -11.4V < V <sub>CM ATT</sub> < 15V, SE / DE                                                           |                          |                    |                       | dB               |

|                                         |                                                   | G= 0.384V/V, -6V < V <sub>CM ATT</sub> < 11V, SE / DE                                                              | 80                       |                    |                       |                  |

| CMRR                                    |                                                   | G= 0.768V/V, -3V < V <sub>CM ATT</sub> < 8V, SE / DE                                                               | 77                       |                    |                       |                  |

|                                         |                                                   | G= 1V/V, -2.3V < V <sub>CM AMP</sub> < 7.3V, SE / DE                                                               |                          |                    |                       |                  |

|                                         |                                                   | G= 2V/V, -1.15V < V <sub>CM_AMP</sub> < 6.15V, SE / DE.                                                            |                          |                    |                       |                  |

| PSRR                                    | Core op-amp DC<br>Power Supply Rejection<br>Ratio | Nulling Switch Mode, 4.5V <v<sup>+ &lt;5.5V</v<sup>                                                                | 90                       |                    |                       | dB               |

| V <sub>OCM_OS</sub>                     | V <sub>OCM</sub> Output Offset (5)                | V <sub>OCM</sub> = 2.5 V                                                                                           | -20                      |                    | 20                    | mV               |

| V <sub>OUT</sub>                        | Positive Output Voltage<br>Swing                  | $R_L = 10 \text{ k}\Omega, C_L = 50 \text{ pF},$<br>+ $V_{IN} = 15V, -V_{IN} = -15V$                               |                          |                    | V+-0.2                |                  |

|                                         | Negative Output<br>Voltage Swing                  | $R_L = 10 \text{ k}\Omega, C_L = 50 \text{ pF},$<br>+ $V_{IN}$ = -15 $V$ , - $V_{IN}$ = 15 $V$                     | V <sup>-</sup> +0.2      |                    |                       | V                |

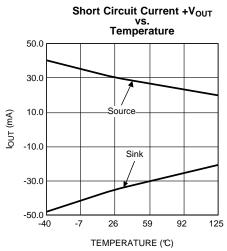

| I <sub>OUT</sub>                        | Short circuit current                             | $+V_{IN}=-V_{IN}=2.5V$ , $+V_{OUT}$ , $-V_{OUT}/V_R$ connected individually to either $V^+$ or $V^-$               | 10                       |                    |                       | mA               |

|                                         | Current limitation                                | Internal current limiter                                                                                           |                          |                    | 55                    |                  |

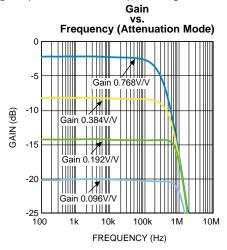

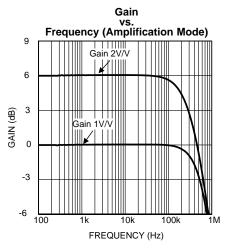

|                                         |                                                   | Attenuation Mode, G = 0.096 V/V, $R_L$ =10 k $\Omega$ , $C_L$ = 50 pF                                              |                          | 1.2                |                       | MHz              |

|                                         |                                                   | Attenuation Mode, G = 0.192 V/V, $R_L$ = 10 k $\Omega$ , $C_L$ = 50 pF                                             |                          | 1.0                |                       | IVII IZ          |

| GBW                                     | Bandwidth                                         | Attenuation Mode, G = 0.384 V/V, $R_L$ = 10 k $\Omega$ , $C_L$ = 50 pF                                             |                          | 560                |                       | kHz              |

|                                         | Ballawiani                                        | Attenuation Mode, G = 0.768 V/V, $R_L$ = 10 k $\Omega$ , $C_L$ = 50 pF                                             |                          | 310                |                       | NI IZ            |

|                                         |                                                   | Amplification Mode, G = 1 V/V, $R_L$ = 10 k $\Omega$ , $C_L$ = 50 pF                                               |                          | 530                |                       | kHz              |

|                                         |                                                   | Amplification Mode, G = 2 V/V, $R_L$ = 10 k $\Omega$ , $C_L$ = 50 pF                                               |                          | 280                |                       | NIIZ             |

<sup>(4)</sup> Offset voltage temperature drift is determined by dividing the change in V<sub>OS</sub> at the temperature extremes by the total temperature change.

Submit Documentation Feedback

Copyright © 2010-2013, Texas Instruments Incorporated

$V_{OCM\_OS}$  is the difference between the Output Common mode voltage  $(+V_{OUT}+(-V_{OUT}/V_R))/2$  and the Voltage on the  $V_{OCM}$  pin. (5)

# 5V Electrical Characteristics (1) (continued)

Unless otherwise specified, all limits ensured for  $T_A = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V_{IO} = 5V$ ,  $V^- = 0V$ , G = 0.192 V/V,  $V_{CM\_ATT} = (+V_{IN}) + (-V_{IN})/2$ ,  $V_{CM\_AMP} = (+IN + (-IN))/2$ . Differential output configuration. SE = Single Ended Output, DE = Differential Output. **Boldface** limits apply at the temperature extremes.

| Symbol | Parameter                            | Conditions                                                | Min <sup>(2)</sup> | Typ <sup>(3)</sup> | Max (2) | Units  |

|--------|--------------------------------------|-----------------------------------------------------------|--------------------|--------------------|---------|--------|

| SR     | Slew Rate                            | $R_{L} = 10 \text{ k}\Omega, C_{L} = 50 \text{ pF}$       |                    | 1.4                |         | V/µsec |

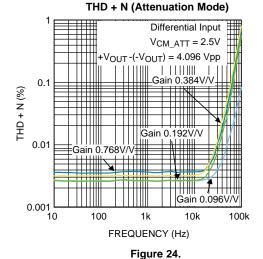

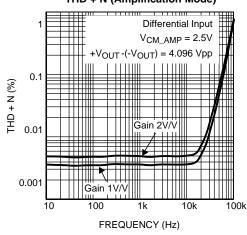

| THD+N  | Total Harmonic<br>Distorsion + Noise | Vout = 4.096 Vpp, f = 1KHz,<br>$R_L = 10 \text{ k}\Omega$ |                    | 0.0026             |         | %      |

<sup>(6)</sup> The number specified is the average of rising and falling slew rates and is measured at 90% to 10%.

# Electrical Characteristics (Serial Interface) (1)

Unless otherwise specified. All limits ensured for  $T_A = 25$  °C,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $2.7V < V_{IO} < 5.5V$

| Symbol                         | Parameter                                                        | Conditions               | Min <sup>(2)</sup>   | Typ <sup>(3)</sup> | Max <sup>(2)</sup> | Units |

|--------------------------------|------------------------------------------------------------------|--------------------------|----------------------|--------------------|--------------------|-------|

| VIL                            | Input Logic Low Threshold                                        |                          |                      |                    | 0.8                | V     |

| VIH                            | Input Logic High Threshold (SDO pin)                             |                          | 2                    |                    |                    | V     |

| VOL                            | Output logic Low Threshold (SDO pin)                             | I <sub>SDO</sub> = 100μA |                      |                    | 0.2                |       |

|                                |                                                                  | I <sub>SDO</sub> = 2mA   |                      |                    | 0.4                | V     |

| VOH Output I                   | Output logic High Threshold                                      | I <sub>SDO</sub> = 100μA | V <sub>IO</sub> -0.2 |                    |                    | V     |

|                                |                                                                  | I <sub>SDO</sub> = 2mA   | V <sub>IO</sub> -0.6 |                    |                    | V     |

| t <sub>1</sub>                 | High Period, SCK                                                 | (4)                      | 100                  |                    |                    | ns    |

| t <sub>2</sub>                 | Low Period, SCK                                                  | (4)                      | 100                  |                    |                    | ns    |

| t <sub>3</sub>                 | Set Up Time, CS to SCK                                           | (4)                      | 50                   |                    |                    | ns    |

| t <sub>4</sub>                 | Set Up Time, SDI to SCK                                          | (4)                      | 30                   |                    |                    | ns    |

| t <sub>5</sub>                 | Hold Time, SCK to SDI                                            | (4)                      | 10                   |                    |                    | ns    |

| t <sub>6</sub>                 | Prop. Delay, SCK to SDO                                          | (4)                      |                      |                    | 60                 | ns    |

| t <sub>7</sub>                 | Hold Time, SCK Transition to $\overline{\text{CS}}$ Rising Edge  | (4)                      | 50                   |                    |                    | ns    |

| t <sub>8</sub>                 | CS Inactive                                                      | (4)                      | 100                  |                    |                    | ns    |

| t <sub>9</sub>                 | Hold Time, SCK Transition to $\overline{\text{CS}}$ Falling Edge | (4)                      | 10                   |                    |                    | ns    |

| t <sub>R</sub> /t <sub>F</sub> | Signal Rise and Fall Times                                       | (4)                      | 1.5                  |                    | 5                  | ns    |

- (1) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. No ensured specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where T<sub>J</sub> > T<sub>A</sub>.

- (2) All limits are specified by testing, design, or statistical analysis.

- (3) Typical values represent the most likely parametric norm at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

- (4) Load for these tests is shown in Test Circuit Diagram.

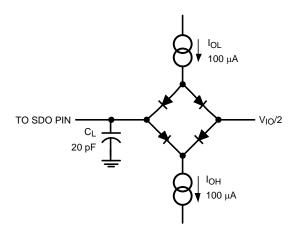

#### **TEST CIRCUIT DIAGRAM**

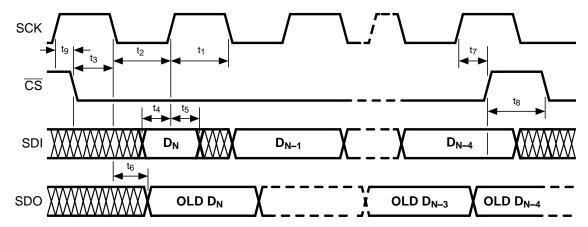

## **Timing Diagram**

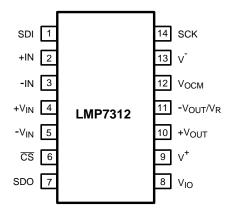

## **Connection Diagram**

Figure 1. 14-Pin SOIC-Top View

## **PIN DESCRIPTIONS**

| Pin | Name                              | Description                                                                                  |

|-----|-----------------------------------|----------------------------------------------------------------------------------------------|

| 1   | SDI                               | SPI data IN                                                                                  |

| 2   | +IN                               | Non-inverting input of Amplification pair                                                    |

| 3   | -IN                               | Inverting input of Amplification pair                                                        |

| 4   | +V <sub>IN</sub>                  | Non-inverting input of Attenuation pair                                                      |

| 5   | -V <sub>IN</sub>                  | Inverting input of Attenuation pair                                                          |

| 6   | CS                                | SPI chip select                                                                              |

| 7   | SDO                               | SPI data OUT                                                                                 |

| 8   | V <sub>IO</sub>                   | SPI supply voltage                                                                           |

| 9   | V <sup>+</sup>                    | Positive supply voltage                                                                      |

| 10  | +V <sub>OUT</sub>                 | Non-inverting output                                                                         |

| 11  | -V <sub>OUT</sub> /V <sub>R</sub> | Inverting output in differential output mode, reference input in single-ended operation mode |

| 12  | V <sub>OCM</sub>                  | Output common mode voltage in DE                                                             |

| 13  | V-                                | Negative supply voltage, reference for both Analog and Digital supplies                      |

| 14  | SCK                               | SPI Clock                                                                                    |

## **Typical Performance Characteristics**

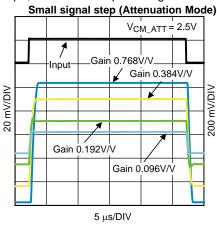

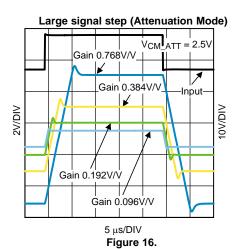

Unless otherwise specified,  $T_A = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V_{IO} = 5V$ ,  $V^- = 0V$ ,  $V_{CM\_ATT} = (+V_{IN} + (-V_{IN}))/2$ ,  $V_{CM\_AMP} = (+IN + (-IN))/2$ .  $R_L = 10k\Omega$ ,  $C_L = 50pF$ , Differential output configuration.

Figure 2.

Figure 4.

Figure 6.

Figure 3.

Figure 5.

Figure 7.

Unless otherwise specified,  $T_A = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V_{IO} = 5V$ ,  $V^- = 0V$ ,  $V_{CM\_ATT} = (+V_{IN} + (-V_{IN}))/2$ ,  $V_{CM\_AMP} = (+IN + (-IN))/2$ .  $R_L = 10k\Omega$ ,  $C_L = 50pF$ , Differential output configuration.

Figure 8.

Figure 10.

Figure 9.

Figure 11.

Figure 13.

Copyright © 2010–2013, Texas Instruments Incorporated

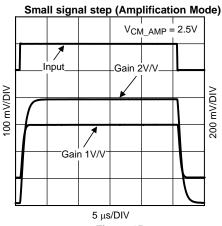

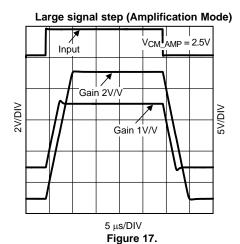

Unless otherwise specified,  $T_A = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V_{IO} = 5V$ ,  $V^- = 0V$ ,  $V_{CM\_ATT} = (+V_{IN} + (-V_{IN}))/2$ ,  $V_{CM\_AMP} = (+IN + (-IN))/2$ .  $R_L = 10k\Omega$ ,  $C_L = 50pF$ , Differential output configuration.

Gain 0.384V/V

Input Gain 0.192V/V

Gain 0.096V/V

Op

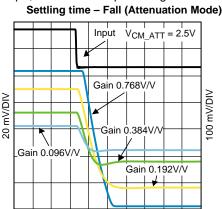

Settling time - Rise (Attenuation Mode)

$V_{CM\_ATT} = 2.5V$

500 ns/DIV Figure 18.

Gain 0.768V/V

Figure 15.

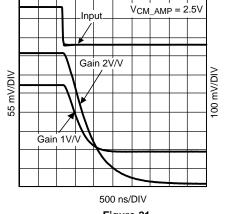

Settling time – Rise (Amplification Mode)

V<sub>CM\_AMP</sub> = 2.5V

Input

Gain 2V/V

Gain 1V/V

500 ns/DIV

Figure 19.

Unless otherwise specified,  $T_A = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V_{IO} = 5V$ ,  $V^- = 0V$ ,  $V_{CM\_ATT} = (+V_{IN} + (-V_{IN}))/2$ ,  $V_{CM\_AMP} = (+IN + (-IN))/2$ .  $R_L = 10k\Omega$ ,  $C_L = 50pF$ , Differential output configuration.

Figure 20.

500 ns/DIV

Settling time - Fall (Amplification Mode)

Figure 21.

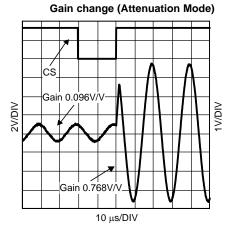

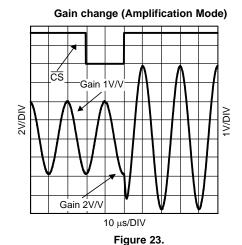

Figure 22.

THD + N (Amplification Mode)

Figure 25.

Copyright © 2010–2013, Texas Instruments Incorporated

Unless otherwise specified,  $T_A = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V_{IO} = 5V$ ,  $V^- = 0V$ ,  $V_{CM\_ATT} = (+V_{IN} + (-V_{IN}))/2$ ,  $V_{CM\_AMP} = (+IN + (-IN))/2$ .  $R_L = (+V_{IN} + (-V_{IN}))/2$  $10k\Omega$ ,  $C_L = 50pF$ , Differential output configuration.

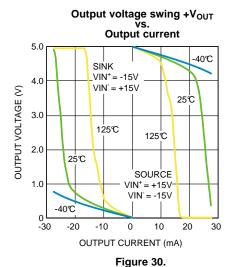

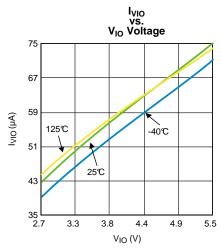

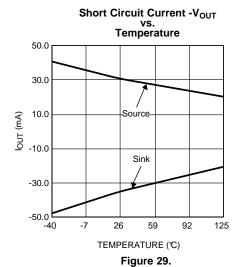

Figure 26.

Figure 28.

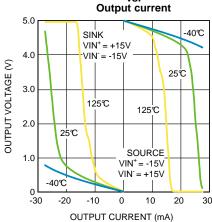

Figure 27.

Output voltage swing -V<sub>OUT</sub>

Figure 31.

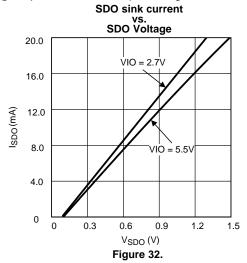

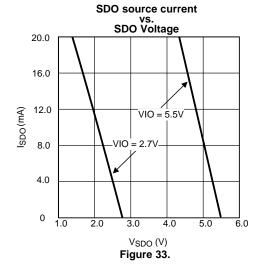

Unless otherwise specified,  $T_A = 25$ °C,  $V^+ = 5V$ ,  $V_{IO} = 5V$ ,  $V^- = 0V$ ,  $V_{CM\_ATT} = (+V_{IN} + (-V_{IN}))/2$ ,  $V_{CM\_AMP} = (+IN + (-IN))/2$ .  $R_L = 10k\Omega$ ,  $C_L = 50pF$ , Differential output configuration.

#### APPLICATION SECTION

#### **GENERAL DESCRIPTION**

The LMP7312 is a single supply programmable gain difference amplifier with two input pairs: Attenuation pair ( $V_{IN}$ ,  $+V_{IN}$ ) and Amplification pair (-IN, +IN). The output can be configured in both single-ended and differential modes with the output common mode voltage set by the user. The input selection, the gains and the mode of operation of the LMP7312 are controlled through a 4- wire SPI interface (SCK,  $\overline{CS}$ , SDI, SDO). These features combined make the LMP7312 a very easy interface between the analog high voltage industrial buses and the low voltage digital converters.

#### **OUTPUT MODE CONFIGURATION**

The LMP7312 is able to work in both single ended and differential output mode. The selection of the mode is made through the  $V_{OCM}$  (output common mode voltage) pin.

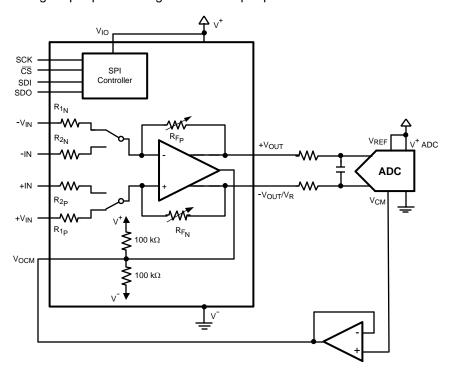

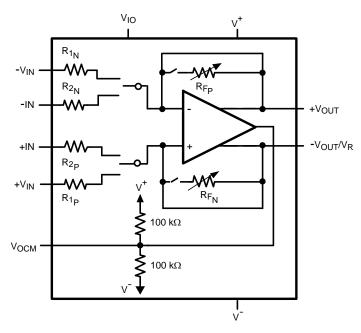

### **Differential Output**

This mode of operation is enabled when the output common mode voltage pin ( $V_{OCM}$ ) is connected to a voltage higher than 1V, for instance the common mode voltage supplied by an ADC, (Figure 34) or a voltage reference. If the  $V_{OCM}$  pin is floating an internal voltage divider biases it at the half supply voltage. In this configuration the output signals are set on the  $V_{OCM}$  voltage level.

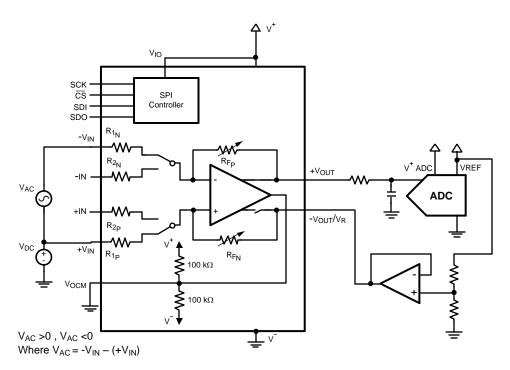

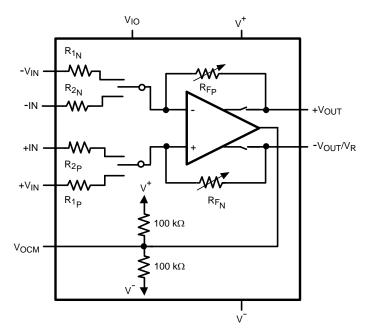

#### **Single-Ended Output**

This mode of operation is enabled when the  $V_{OCM}$  pin is tied to a voltage less than 0.5 V, for example to ground. In this mode of operation the LMP7312 behaves as a difference amplifier, where the  $+V_{OUT}$  pin is the single-ended output while the  $-V_{OUT}/V_R$  is the reference voltage.

- 1. In the case of bipolar input signal the non inverting output will be connected to an external reference through a buffer (Figure 35).

- 2. In the case of unipolar input signal the non inverting output will be connected to ground (Figure 36).

In both cases the inverting output pin is configured as an input pin.

Figure 34. Differential ADC Interfacing with V<sub>CM</sub> provided by the ADC

Figure 35. Bipolar Input Signal to Single-Ended ADC Interface

Figure 36. Unipolar Input Signal to Single-Ended ADC Interface

Copyright © 2010-2013, Texas Instruments Incorporated

#### INPUT VOLTAGE RANGE

The LMP7312 has an internal OpAmp with rail-to-rail input voltage range capability. The requirement to stay within the V-and V+ rail at the OpAmp input translates in an Input Voltage Range specification as explained in this application section.

#### **Differential Output**

Considering a single positive supply (V<sup>-</sup>= GND, V<sup>+</sup> = V<sub>S</sub>) the Input Common mode voltage,  $V_{CM\_ATT}$  = (+V<sub>IN</sub> + (-V<sub>IN</sub>))/2 for the Attenuation inputs and  $V_{CM\_AMP}$  = (+I<sub>IN</sub> + (-I<sub>IN</sub>))/2 for the Amplification inputs, has to stay between the MIN and MAX values determined by these formulas:

$$CM_{MAX} = V_S + 1/K_V^*(V_S - V_{OCM})$$

$CM_{MIN} = -1/K_V^*V_{OCM}$

K<sub>V</sub> is a function of the Gain according to the table below:

| Gain  | 0.096 V/V | 0.192 V/V | 0.384 V/V | 0.768 V/V | 1 V/V | 2 V/V |

|-------|-----------|-----------|-----------|-----------|-------|-------|

| $K_V$ | 0.12      | 0.218     | 0.414     | 0.806     | 1.065 | 2.096 |

Regardless to the values derived by the formula, the voltage on each input pin must never exceed the specified Absolute Maximum Ratings.

Below are some typical values:

Table 1. Differential Input, Differential Output,  $V_S = 5V$ ,  $V_{OCM} = 2.5V$

|           | V <sub>CM_ATT</sub>  |                      | V <sub>CM_</sub> | AMP    |

|-----------|----------------------|----------------------|------------------|--------|

| Gain      | Min                  | Max                  | Min              | Max    |

| 0.096 V/V | -15 V <sup>(1)</sup> | +15 V <sup>(1)</sup> | 1                |        |

| 0.192 V/V | -11.5 V              | +15 V                |                  |        |

| 0.384 V/V | -6 V                 | +11 V                |                  |        |

| 0.768 V/V | -3.1 V               | +8.1 V               |                  |        |

| 1 V/V     |                      |                      | -2.3 V           | +7.3 V |

| 2 V/V     |                      |                      | -1.2 V           | +6.2 V |

<sup>(1)</sup> Limited by the operating ratings on input pins

In the case of a single ended input referred to ground ( $-V_{IN} = GND$ , -IN = GND) the table below summarizes the voltage range allowed on the  $+VI_{N}$  and  $+I_{IN}$  inputs.

Table 2. Single Ended Input, Differential Output,  $V_S = 5V$ ,  $V_{OCM} = 2.5V$ ,  $-V_{IN} = GND$ ,  $-I_{IN} = GND$

|           | +V <sub>IN</sub>     |                      | +                     | IN                    |

|-----------|----------------------|----------------------|-----------------------|-----------------------|

| Gain      | Min                  | Max                  | Min                   | Max                   |

| 0.096 V/V | -15 V <sup>(1)</sup> | +15 V <sup>(1)</sup> |                       |                       |

| 0.192 V/V | -15 V <sup>(1)</sup> | +15 V <sup>(1)</sup> |                       |                       |

| 0.384 V/V | -12 V <sup>(2)</sup> | +12 V <sup>(2)</sup> |                       |                       |

| 0.768 V/V | -6 V <sup>(2)</sup>  | +6 V <sup>(2)</sup>  |                       |                       |

| 1 V/V     |                      |                      | -4.6 V <sup>(2)</sup> | +4.6 V <sup>(2)</sup> |

| 2 V/V     |                      |                      | -2.3 V <sup>(2)</sup> | +2.3 V <sup>(2)</sup> |

(1) Limited by the operating ratings on input pins.

(2) Limited by the output voltage swing (0.2V to  $V_S$ -0.2V on both +  $V_{OUT}$  and - $V_{OUT}$ )

#### **Single Ended Output**

In this mode the LMP7312 behaves as a Difference Amplifier, with  $-V_{OUT}/V_R$  being the reference output voltage when a zero volt differential input signal is applied. The voltages at the OpAmp inputs are determined by  $+V_{IN}$  and  $-V_{OUT}/V_R$  voltages. The voltage range of  $+V_{IN}$  and  $+I_{IN}$  inputs is as follows:

$$V_{MAX} = V_{S} + 1/K_{V} * (V_{S} - (-V_{OUT}/V_{R}))$$

$$V_{MIN} = -1/K_V * (-V_{OUT}/V_R)$$

Regardless of the values derived by the formula, the voltage on each input pin must never exceed the specified Absolute Maximum Ratings.

Below are some typical values:

Table 3. Differential Input, Single Ended Output,  $V_S = 5V$ ,  $V_{OCM} = GND$ , and  $-V_{OUT}/V_R = 2.5V$

|           | +V <sub>IN</sub>       |                      | +11    | N      |

|-----------|------------------------|----------------------|--------|--------|

| Gain      | Min                    | Max                  | Min    | Max    |

| 0.096 V/V | -15 V <sup>(1)</sup>   | +15 V <sup>(1)</sup> | 1      |        |

| 0.192 V/V | -11.5 V <sup>(1)</sup> | +15 V                |        |        |

| 0.384 V/V | -6 V                   | +11 V                |        |        |

| 0.768 V/V | -3.1 V                 | +8.1 V               |        |        |

| 1 V/V     |                        |                      | -2.3 V | +7.3 V |

| 2 V/V     |                        |                      | -1.2 V | +6.2 V |

<sup>(1)</sup> Limited by the operating ratings on input pins

In the case of a single ended input referred to ground ( $-V_{IN} = GND$ ), -IN = GND) this table summarize the voltage ranges allowed on the  $+V_{IN}$  and  $+I_{IN}$  inputs.

Table 4. Single Ended Input, Single Ended Output,  $V_S = 5V$ ,  $V_{OCM} = GND$ ,  $-V_{OUT}/V_R = 2.5V$ ,  $-V_{IN} = GND$ ,  $-I_{IN} = GND$

|           | +V <sub>IN</sub>     |                      | +I <sub>IN</sub>      |                       |  |

|-----------|----------------------|----------------------|-----------------------|-----------------------|--|

| Gain      | Min                  | Max                  | Min                   | Max                   |  |

| 0.096 V/V | -15 V <sup>(1)</sup> | +15 V <sup>(1)</sup> |                       |                       |  |

| 0.192 V/V | -11.5 V              | +12 V <sup>(2)</sup> |                       |                       |  |

| 0.384 V/V | -6 V <sup>(2)</sup>  | +6 V <sup>(2)</sup>  |                       |                       |  |

| 0.768 V/V | -3 V**               | +3 V <sup>(2)</sup>  |                       |                       |  |

| 1 V/V     |                      |                      | -2.3 V <sup>(2)</sup> | +2.3 V <sup>(2)</sup> |  |

| 2 V/V     |                      |                      | -1.1 V <sup>(2)</sup> | +1.1 V <sup>(2)</sup> |  |

<sup>(1)</sup> Limited by the operating ratings on input pins.

### SERIAL INTERFACE CONTROL OPERATION

The serial interface control of the LMP7312 can be supplied with a voltage between 2.7V and 5.5V through the  $V_{IO}$  pin for compatibility with different logic families present in the market.

The LMP7312 Attenuation, Amplification, Null switch and HiZ modes are controlled by a register. Data to be written into the control register is first loaded into the LMP7312 via the serial interface. The serial interface employs a 5-bit shift register. Data is loaded through the serial data input, SDI. Data passing through the shift register is obtained through the serial data output, SDO. The serial clock, SCK controls the serial loading process. All five data bits are required to correctly program the device. The falling edge of  $\overline{CS}$  enables the shift register to receive data. The SCK signal must be high during the falling edge of  $\overline{CS}$ . Each data bit is clocked into the shift register on the rising edge of SCK. Data is transferred from the shift register to the holding register on the rising edge of  $\overline{CS}$ . Operation is shown in the Timing Diagram.

<sup>(2)</sup> Limited by the output voltage swing (0.2V to V<sub>S</sub>-0.2V on +V<sub>OUT</sub>)

### **SPI Registers**

| MSB    |        |       |         | LSB  |

|--------|--------|-------|---------|------|

| Gain_1 | Gain_0 | EN_CL | Null_SW | Hi_Z |

### Gain\_0, Gain\_1 bit: Gain Values

Different gains are available in Attenuation Mode or Amplification Mode according to the following Gain Table.

| Gain_1 | Gain_0 | EN_CL | Gain Value (V/V) |

|--------|--------|-------|------------------|

| 0      | 0      | 0     | 0.096            |

| 0      | 1      | 0     | 0.192            |

| 1      | 0      | 0     | 0.384            |

| 1      | 1      | 0     | 0.768            |

| 1      | 0      | 1     | 1                |

| 1      | 1      | 1     | 2                |

### EN\_CL bit: Enable Amplification Mode

This register selects which input pair is processed.

| EN_CL | Mode               | Description                                                               |  |  |  |  |

|-------|--------------------|---------------------------------------------------------------------------|--|--|--|--|

| 0     | Attenuation Mode   | ±V <sub>IN</sub> inputs are processed through the 104.16k input resistors |  |  |  |  |

| 1     | Amplification Mode | ±IN inputs are processed through the 40k input resistors                  |  |  |  |  |

### NULL\_SW bit: Input Offset Nulling Switch Mode

This register selects a mode in which the amplifier is not processing any input but it is configured in unity gain to allow system level amplifier offset calibration. The Nulling Switch mode is available in both single ended and fully differential output mode. The LMP7312 in Nulling Switch and fully differential mode has he following configuration.

| NULL_SW | Mode                  | Description                                                                                       |

|---------|-----------------------|---------------------------------------------------------------------------------------------------|

| 0       | Normal Operation Mode | $\pm V_{\text{IN}}$ and $\pm \text{IN}$ inputs are processed depending on EN_CL register setting. |

| 1       | Nulling Switch Mode   | Enables to evaluate the offset of the internal amplifier for system level calibration             |

Figure 37. LMP7312 in Nulling Switch Mode

In this condition at the Output pins is possible to measure the input voltage offset of the op-amp:

| Output Mode  | +V <sub>OUT</sub>                       | -V <sub>OUT</sub> /V <sub>R</sub>       |  |  |

|--------------|-----------------------------------------|-----------------------------------------|--|--|

| Differential | V <sub>CM_out</sub> +V <sub>OS</sub> /2 | V <sub>CM_out</sub> -V <sub>OS</sub> /2 |  |  |

| Single-Ended | $V_R + V_{OS}$                          | $V_R$                                   |  |  |

## Hi\_Z bit:High Impedance

In this mode both outputs  $+V_{OUT}$  and  $-V_{OUT}/V_R$  of the LMP7312 are in tri-state Figure 38.

| HI_Z | Mode                  | Description                                                                       |

|------|-----------------------|-----------------------------------------------------------------------------------|

| 0    | Normal Operation Mode | The LMP7312 is configured according to value of the other 4 bits of the register. |

| 1    | High Impedance Mode   | The LMP7312 output is in high impedance                                           |

Figure 38. LMP7312 in High Impedance Mode

In each case the SPI registers require 5 bits. The table below is a summary of all allowed configurations.

| MSB    |        |       |         | LSB  |                  |                       |

|--------|--------|-------|---------|------|------------------|-----------------------|

| Gain_1 | Gain_0 | EN_CL | Null_SW | Hi_Z | Gain Value (V/V) | Mode of Operation     |

| 0      | 0      | 0     | 0       | 0    | 0.096            | Attenuation Mode      |

| 0      | 1      | 0     | 0       | 0    | 0.192            | Attenuation Mode      |

| 1      | 0      | 0     | 0       | 0    | 0.384            | Attenuation Mode      |

| 1      | 1      | 0     | 0       | 0    | 0.768            | Attenuation Mode      |

| 1      | 0      | 1     | 0       | 0    | 1                | Amplification Mode    |

| 1      | 1      | 1     | 0       | 0    | 2                | Amplification Mode    |

| Х      | х      | х     | х       | 1    | _                | High Impedance Output |

| Х      | х      | х     | 1       | 0    | 1                | Null Switch Mode      |

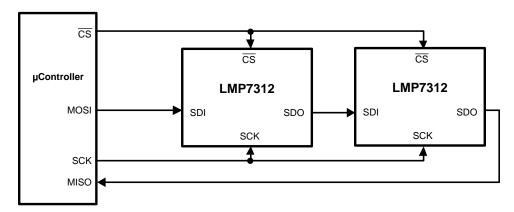

#### **Daisy Chain**

The LMP7312 supports daisy chaining of the serial data stream between multiple chips. To use this feature serial data is clocked into the first chip SDI pin, and the next chip SDI pin is connected to the SDO pin of the first chip. Both chips may share a chip select signal, or the second chip can be enabled separately. When the chip select pin goes low on both chips and 5 bits have been clocked into the first chip the next 5 clock cycle begins moving new configuration data into the second chip. With a full 10 clock cycles both chips have valid data and the chip select pin of both chips should be brought high to prevent the data from overshooting.

Figure 39. Daisy Chain

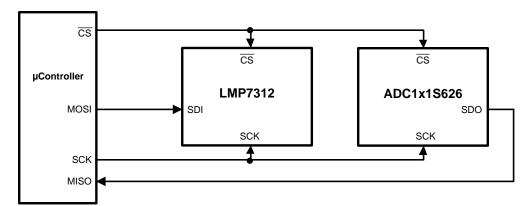

#### Shared 4-wire SPI with ADC

The LMP7312 is a good choice when interfacing to differential analog to digital converters ADC141S626 and ADC161S626 of PowerWise® Family. Its SPI interface has been designed to enable sharing CSB with the ADC. LMP7312 register access happens only when CSB is asserted low while SCK is high. However, the ADC starts conversion under any of the following conditions:

- 1. CSB goes low while SCK is high

- 2. CSB goes low while SCK is low

- 3. CSB and SCK both going low

Therefore, if a system uses timing condition #2 above, LMP7312 and ADC1x1S626 can share CSB and SCK as shown in Figure 40. The only side-effect would be that writing to LMP7312 triggers an ADC conversion, but then the result can be ignored. At other times, the LMP7312 is not affected by the CSB assertions used to initiate normal ADC conversions.

Figure 40. 4-wire SPI with ADC interface

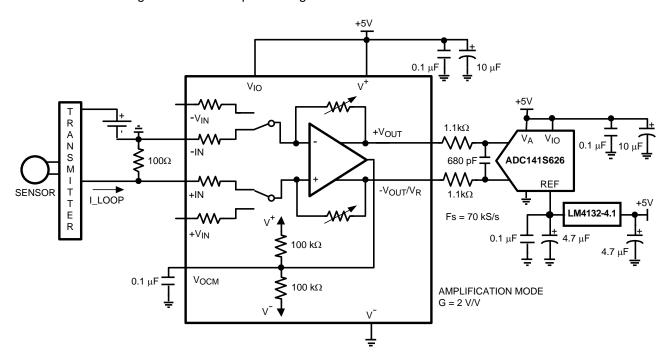

### LMP7312 IN 4-20mA CURRENT LOOP APPLICATION

The 4-20mA current loop shown in Figure 41 is a common method of transmitting sensor information in many industrial process-monitoring applications. Transmitting sensor information via a current loop is particularly useful when the information has to be sent to a remote location over long distances (1000 feet, or more). The loop's operation is straightforward: a sensor's output voltage is first converted to a proportional current, with 4mA normally representing the sensor's zero-level output, and 20mA representing the sensor's full-scale output. Then, a receiver at the remote end converts the 4-20mA current back into a voltage which in turn can be further processed by a computer or display module. A typical 4-20mA current-loop circuit is made up of four individual elements: a sensor/transducer; a voltage-to-current converter (commonly referred to as a transmitter and/or signal conditioner); a loop power supply; and a receiver/monitor. In loop powered applications, all four elements

Product Folder Links: LMP7312

are connected in a closed, series circuit, loop configuration (Figure 41). Sensors provide an output voltage whose value represents the physical parameter being measured. The transmitter amplifies and conditions the sensor's output, and then converts this voltage to a proportional 4-20mA dc-current that circulates within the closed series-loop. The loop power-supply generally provides all operating power to the transmitter and receiver, and any other loop components that require a well-regulated dc voltage. In loop-powered applications, the power supply's internal elements also furnish a path for closing the series loop. The receiver/monitor normally a subsection of a panel meter or data acquisition system, converts the 4-20mA current back into a voltage which can be further processed and/or displayed. The high DC performance of the LMP7312 makes this difference amplifier an ideal choice for use in current loop AFE receiver. The LMP7312 has a low input offset voltage and low input offset voltage drift when configured in amplification mode. In the circuit shown in Figure 41 the LMP7312 is in amplification mode with a gain of 2V/V and differential output in order to well match the input stage of the ADC141S626 (SAR ADC with differential input). The shunt resistor is 100ohm in order to have a max voltage drop of 2V when 20mA flows in the loop. The first order filter between the LMP7312 and the ADC141S626 reduces the noise bandwidth and allows handling input signal up to 2kHz. That frequency has been calculated taking in account the roll off of the filter and ensuring a gain error less than 1LSB of the ADC141S626. In order to utilize the maximum number of bits of the ADC141S626 in this configuration, a 4.1V reference voltage is used. With this system, the current of the 4-20mA loop is accurately gained to the full scale of the ADC and then digitized for further processing.

Figure 41. LMP7312 in 4-20mA Current Loop application

#### LAYOUT CONSIDERATIONS

### Power supply bypassing

In order to preserve the gain accuracy of the LMP7312, power supply stability requires particular attention. The LMP7312 ensures minimum PSRR of 90dB (or 31.62  $\mu$ V/V). However, the dynamic range, the gain accuracy and the inherent low-noise of the amplifier can be compromised by introducing and amplifying power supply noise. To decouple the LMP7312 from supply line AC noise, a 0.1  $\mu$ F ceramic capacitor should be located on the supply line, close to the LMP7312. Adding a 10  $\mu$ F tantalum capacitor in parallel with the 0.1  $\mu$ F ceramic capacitor will reduce the noise introduced to the LMP7312 even further by providing an AC path to ground for most frequency ranges.

#### **APPENDIX**

#### Offset Voltage and Offset Voltage Drift calculation

Listed in the table below are the calculated values for Offset Voltage and Offset Voltage Drift based on the max specifications of these parameters for the core op-amp (for all gain configurations).

| Parameter                                      | Unit  | Value |       |       |       |      |      |

|------------------------------------------------|-------|-------|-------|-------|-------|------|------|

| Gain                                           | V/V   | 0.096 | 0.192 | 0.384 | 0.768 | 1    | 2    |

| Total Offset Input Referred (MAX)              | μV    | ±1141 | ±620  | ±360  | ±230  | ±200 | ±150 |

| Total Offset Output Referred (MAX)             | μV    | ±109  | ±119  | ±138  | ±176  | ±200 | ±300 |

| TCV <sub>OS</sub> Input Referred @ 25°C (MAX)  | μV/°C | ±32.3 | ±18.6 | ±10.8 | ±6.9  | ±6   | ±4.5 |

| TCV <sub>OS</sub> Output Referred @ 25°C (MAX) | μV/°C | ±3.3  | ±3.6  | ±4.1  | ±5.3  | ±6   | ±9   |

#### Noise calculation

Listed in the table below are the calculated values for Voltage Noise based on the spectral density of the core op-amp at 10kHz (for all gain configurations).

| Parameter                      | Unit               | Value |       |       |       |    |    |

|--------------------------------|--------------------|-------|-------|-------|-------|----|----|

| Gain                           | V/V                | 0.096 | 0.192 | 0.384 | 0.768 | 1  | 2  |

| Total Noise Referred to Input  | nV/√ <del>Hz</del> | 211   | 150   | 112   | 89    | 53 | 46 |

| Total Noise Referred to Output | nV/√ <del>Hz</del> | 20    | 29    | 43    | 68    | 53 | 92 |

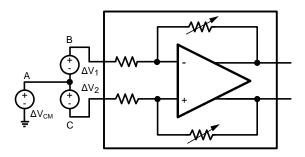

### Input resistance calculation

The common mode input resistance is the resistance seen from node "A" when  $\Delta V1 = \Delta V2 = 0$  and a common mode voltage  $\Delta VCM$  is applied to both inputs of the LMP7312. The differential input resistance is the resistance seen from the nodes "B" and "C" when  $\Delta VCM=0$  and a differential voltage  $\Delta V1 = \Delta V2 = V/2$  is applied to the inputs of the LMP7312.

Figure 42. Circuit for Input Resistance calculation

| Mode of Operation  |                         | Unit | Gains  |               |        |        |  |

|--------------------|-------------------------|------|--------|---------------|--------|--------|--|

| Attenuation Mode   |                         |      | 0.096  | 0.192         | 0.384  | 0.768  |  |

|                    | Common Mode Resistance  | kΩ   | 57.08  | 62.08         | 72.08  | 92.08  |  |

|                    | Differential Resistance | kΩ   | 228.30 | 248.30        | 288.30 | 368.30 |  |

| Amplification Mode |                         |      |        | 1             |        | 2      |  |

|                    | Common Mode Resistance  | kΩ   | 40     | 40.0<br>160.0 |        | 0.0    |  |

|                    | Differential Resistance | kΩ   | 16     |               |        | 0.0    |  |

### SNOSB32B -MARCH 2010-REVISED MARCH 2013

## **REVISION HISTORY**

| Cł | anges from Revision A (March 2013) to Revision B   | Pa | ge |

|----|----------------------------------------------------|----|----|

| •  | Changed layout of National Data Sheet to TI format |    | 23 |

www.ti.com 23-May-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|----------------|-----------------------|----------|-------------------------------|----------------------------|--------------|------------------|

| LMP7312MA/NOPB        | Active | Production    | SOIC (D)   14  | 55   TUBE             | Yes      | (4)<br>SN                     | (5)<br>Level-1-260C-UNLIM  | -40 to 125   | LMP7312<br>MA    |

| LMP7312MA/NOPB.A      | Active | Production    | SOIC (D)   14  | 55   TUBE             | Yes      | SN                            | Level-1-260C-UNLIM         | -40 to 125   | LMP7312<br>MA    |

| LMP7312MAX/NOPB       | Active | Production    | SOIC (D)   14  | 2500   LARGE T&R      | Yes      | SN                            | Level-1-260C-UNLIM         | -40 to 125   | LMP7312<br>MA    |

| LMP7312MAX/NOPB.A     | Active | Production    | SOIC (D)   14  | 2500   LARGE T&R      | Yes      | SN                            | Level-1-260C-UNLIM         | -40 to 125   | LMP7312<br>MA    |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 23-May-2025

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

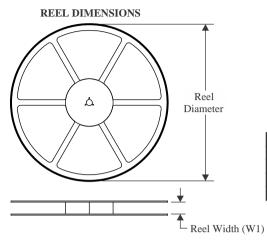

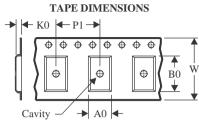

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

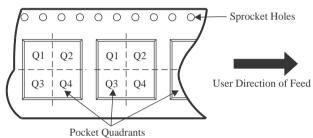

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          |      | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LMP7312MAX/NOPB | SOIC | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.35       | 2.3        | 8.0        | 16.0      | Q1               |

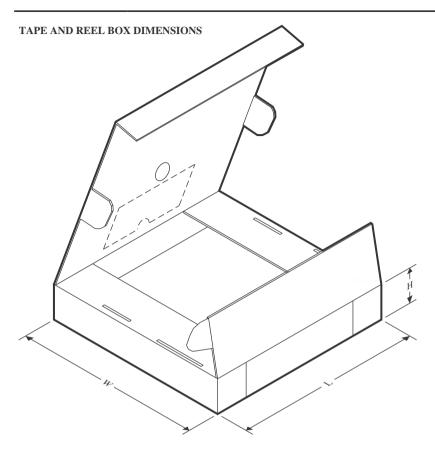

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

### \*All dimensions are nominal

|   | Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ı | LMP7312MAX/NOPB | SOIC         | D               | 14   | 2500 | 356.0       | 356.0      | 35.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

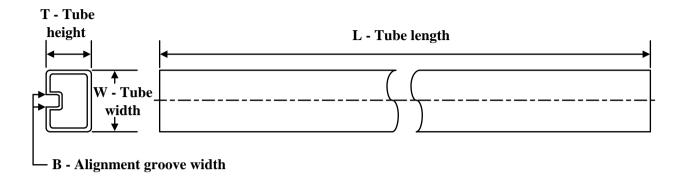

### **TUBE**

### \*All dimensions are nominal

| Device           | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|------------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| LMP7312MA/NOPB   | D            | SOIC         | 14   | 55  | 495    | 8      | 4064   | 3.05   |

| LMP7312MA/NOPB.A | D            | SOIC         | 14   | 55  | 495    | 8      | 4064   | 3.05   |

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES:

- 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm, per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.43 mm, per side.

- 5. Reference JEDEC registration MS-012, variation AB.

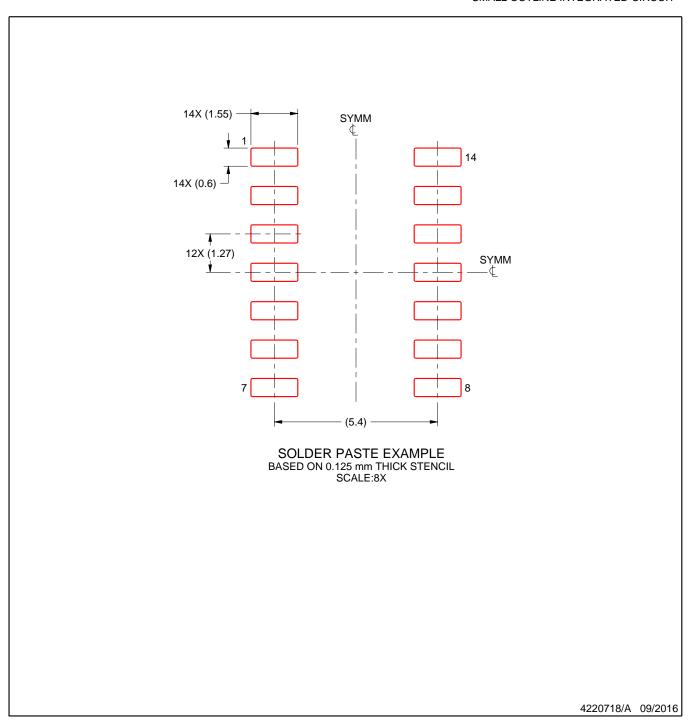

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated