# **SIEMENS**

#### Fault Tolerant Differential CAN Transceiver

**TLE 6252 G**

#### **Target Data**

#### **Features**

- Data transmission rate up to 125 kBaud

- Very low current consumption in stand-by and sleep mode

- Optimized EMI behavior due to limited and symmetric dynamic slopes of CANL and CANH signals

- Switches to single-wire mode during bus line failure events

- Supports one-wire transmission mode with ground offset voltages up to 1.5 V

- Preventation from bus occupation in case of CAN controller failure

- Fully-integrated receiver filters

- Short-circuit detection to battery and ground in 12 V powered systems

- Thermal protection

- Bus line error protection against transients in automotive environment

|   | Туре       | Ordering Code | Package          |  |  |

|---|------------|---------------|------------------|--|--|

| ▼ | TLE 6252 G | Q67006-A9337  | P-DSO-14-2 (SMD) |  |  |

▼ New type

#### **Functional Description**

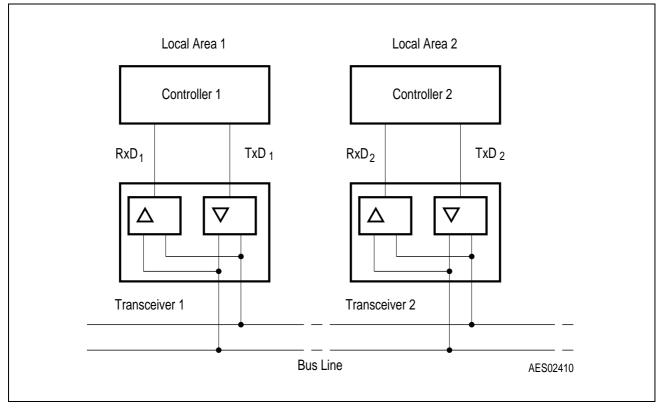

The CAN Transceiver works as the interface between the CAN protocol controller and the physical differential CAN bus. **Figure 1** shows the principle configuration of a CAN network.

The TLE 6252 is optimized for low-speed data transmission (up to 125 kBaud) in automotive and industrial applications.

In normal operation mode a differential signal is transmitted/received. When bus wiring failures are detected the device automatically switches in single-wire mode to maintain communication.

While no data is transferred, the power consumption can be minimized by multiple low power modes.

Figure 1 CAN Network Example

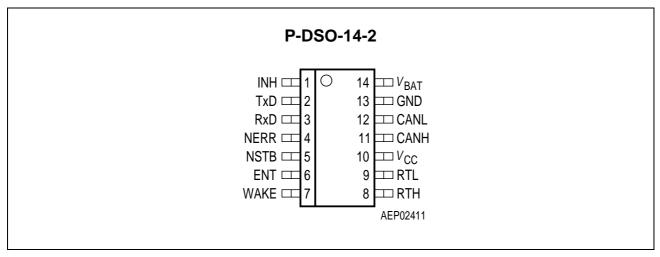

## **Pin Configuration**

(top view)

Figure 2

**Table 1** Pin Definitions and Functions

| Pin No. | Symbol       | Function                                                                                                                                                                             |

|---------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | INH          | Inhibit output; For controlling an external 5 V regulator                                                                                                                            |

| 2       | TxD          | Transmit data input; LOW: bus is dominant, HIGH: bus is recessive                                                                                                                    |

| 3       | RxD          | Receive data output;<br>LOW: bus is dominant                                                                                                                                         |

| 4       | NERR         | Error flag output;                                                                                                                                                                   |

|         |              | LOW: bus error                                                                                                                                                                       |

| 5       | NSTB         | Not stand-by input;                                                                                                                                                                  |

|         |              | Digital control signal for low power modes                                                                                                                                           |

| 6       | ENT          | Enable transfer input; Digital control signal for low power modes                                                                                                                    |

| 7       | WAKE         | $\begin{tabular}{ll} \textbf{Wake-up input;} \\ \textbf{If level of $V_{\text{WAKE}}$ changes the device initials a wake-up from sleep mode by switching INH HIGH} \\ \end{tabular}$ |

| 8       | RTH          | Termination resistor output; For CANH line, controlled by internal failure management                                                                                                |

| 9       | RTL          | Termination resistor output; For CANL line, controlled by internal failure and mode management                                                                                       |

| 10      | $V_{\sf CC}$ | Supply voltage;<br>+ 5 V                                                                                                                                                             |

| 11      | CANH         | Bus line H; HIGH: dominant state, external pull-down for termination                                                                                                                 |

| 12      | CANL         | Bus line L; LOW: dominant state, external pull-up for termination                                                                                                                    |

| 13      | GND          | Ground                                                                                                                                                                               |

| 14      | $V_{BAT}$    | Battery voltage;<br>+ 12 V                                                                                                                                                           |

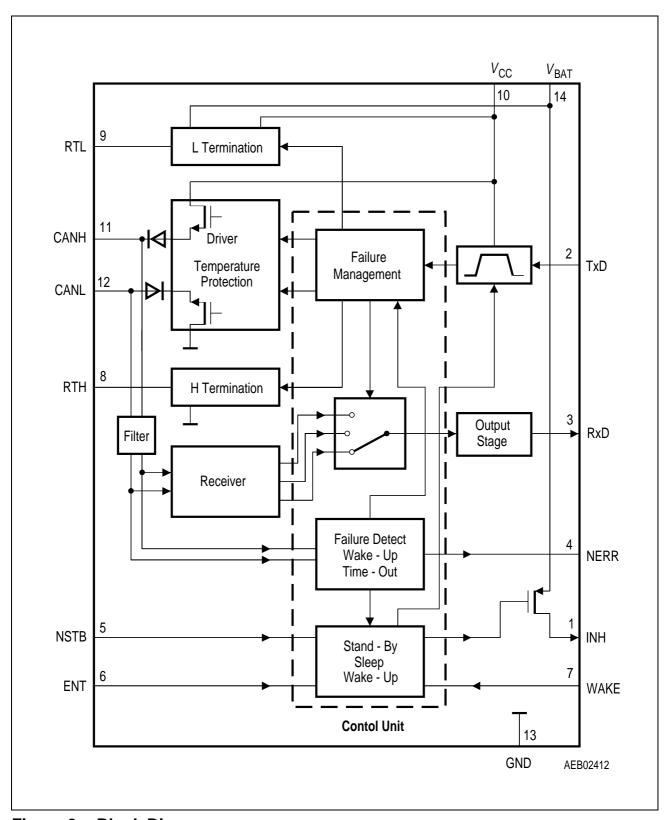

## **Functional Block Diagram**

Figure 3 Block Diagram

#### **General Operation Modes**

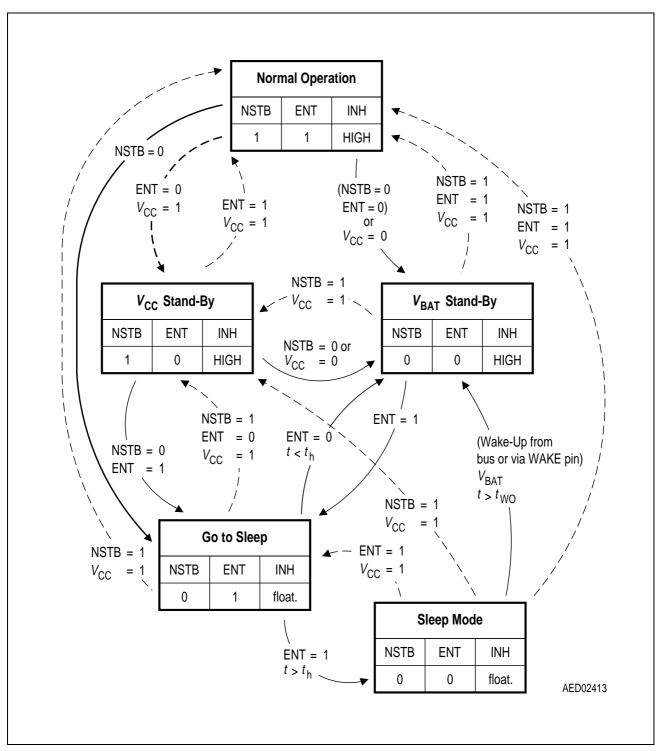

In addition to the normal operation mode, the CAN transceiver offers three multiple low power operation modes to save power when there is no bus achieved: sleep mode,  $V_{\rm Bat}$  stand-by mode and  $V_{\rm CC}$  stand-by mode (see **Table 2** and **Figure 4**). Via the control inputs NSTB and ENT the operation modes are selected by the CAN controller.

In sleep operation mode the lowest power consumption is achieved. To deactivate the external voltage regulator for 5 V supply, the INH output is switched to high impedance in this mode. Also CANL is pulled-up to the battery voltage via the RTL output and the pull-up paths at input pins TxD and RxD are disabled from the internal supply.

On a wake-up request either by bus line activities or by the input WAKE, the transceiver automatically switches on the voltage regulator (5 V supply). The WAKE input reacts to rising and falling edges. As soon as  $V_{\rm CC}$  is provided, the wake-up request can be read on both the NERR and RxD outputs, upon which the microcontroller can activate the normal operation mode by setting the control inputs NSTB and ENT high.

In  $V_{\rm CC}$ -stand-by mode the wake up request is only reported at the RxD-output. The NERR output in this mode is set low when the supply voltage at pin  $V_{\rm bat}$  was below the battery voltage threshold of 1 V.

When entering the normal mode the  $V_{\rm bat}$ -Flag is reseted and the NERR becomes high again.

In addition the  $V_{\rm bat}$ -Flag is set at a first connection of the device to battery voltage. This feature is usefull e.g. when changing the ECU and therefore a presetting routine of the microcontroller has to be started.

If either of the supply voltage drop below the specified limits, the transceiver automatically goes to a stand-by mode.

Table 2 Truth Table of the CAN Transceiver

| NSTB | ENT | Mode                           | INH       | NERR RxD                                     |                                             | RTL                            |

|------|-----|--------------------------------|-----------|----------------------------------------------|---------------------------------------------|--------------------------------|

| 0    | 0   | $V_{\rm BAT}$ stand-by $^{1)}$ | $V_{bat}$ | active LOW walk $V_{\mathrm{CC}}$ is present | switched to $V_{\mathrm{BAT}}$              |                                |

| 0    | 0   | sleep mode <sup>2)</sup>       | floating  |                                              |                                             | switched to $V_{\mathrm{BAT}}$ |

| 0    | 1   | go to sleep command            | floating  |                                              |                                             | switched to $V_{\mathrm{BAT}}$ |

| 1    | 0   | $V_{ m CC}$ stand-by $^{3)}$   | $V_{bat}$ | active LOW $V_{\mathrm{BAT}}$ power-on flag  | active LOW<br>wake-up<br>interrupt          | switched to $V_{\rm CC}$       |

| 1    | 1   | normal mode                    | $V_{bat}$ | active LOW<br>error flag                     | HIGH = receive; LOW = dominant receive data | switched to $V_{\rm CC}$       |

<sup>1)</sup> Wake-up interrupts are released when entering normal operation mode.

<sup>&</sup>lt;sup>2)</sup> If go to sleep command was used before. ENT may turn LOW as  $V_{\rm CC}$  drops, without affecting internal functions.

$<sup>^{\</sup>rm 3)}$   $\ V_{\rm BAT}$  power-on flag will be reseted when entering normal operation mode.

Figure 4 State Diagram

The transceiver will stay in a present operating mode until a suitable condition disposes a state change. If not otherwise defined all conditions are AND-combined. The signals  $V_{\rm CC}$  and  $V_{\rm BAT}$  show if the supply is available (e.g.  $V_{\rm CC}$  = 1 :  $V_{\rm CC}$  voltage is present). If at minimum one supply voltage is switched on, the start-up procedure begins (not figured). After a delay time the device changes to normal operating or stand-by mode.

#### **Bus Failure Management**

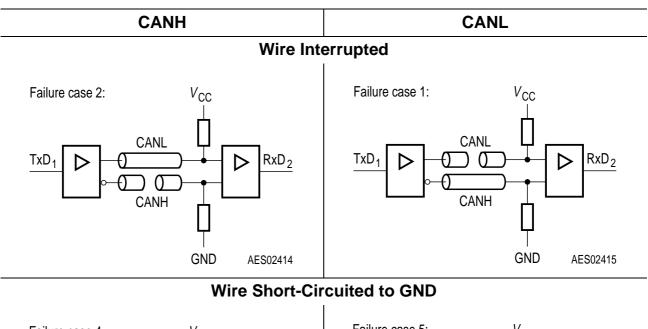

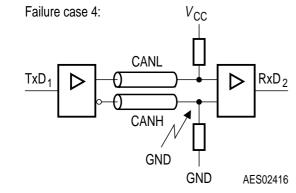

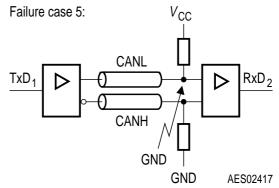

The TLE 6252 detects the bus failures as described in the following (**Table 3**, failures listed according to ISO 11519-2) and automatically switches to a dedicated CANH or CANL single wire mode to maintain data transmission if necessary. Therefore, it is equipped with one differential receiver and 4 single ended comparators, two for each bus line. To avoid false triggering by external RF influences the single wire modes are activated after a certain delay time. As soon as the bus failure disappears the transceiver switches back to differential mode after another time delay. Bus failures are indicated in the normal operation mode by setting the NERR output to LOW.

To reduce EMI the dynamic slopes of the CANL and CANH signals are both limited and symmetric. This allows the use of an unshielded twisted or parallel pair of wires for the bus. During single-wire transmission the EMI performance of the system is degraded from the differential mode.

The differential receiver threshold is set to -2.8 V. This ensures correct reception in the normal operation mode as well as in the failure cases 1, 2 and 4 with a noise margin as high as possible. For these failures, further failure management is not necessary. Detection of the failure cases 1, 2 and 4 is only possible when the bus is dominant. Nevertheless, they are reported on the NERR output until transmission of the next CAN word on the bus begins.

When one of the bus failures 3, 5, 6, 6a and 7 is detected, the defective bus wire is disabled by switching off the affected bus termination and the respective output stage. A wake-up from sleep mode via the bus is possible either via a dominant CANH or CANL line. This ensures that a wake-up is possible even if one of the failures 1 to 7 occurs.

In case the transmission data input, TxD from the CAN controller is permanently dominant, both, the CANH and CANL transmitting stage, are deactivated after a delay time. This is necessary to prevent blocking the bus by a defective protocol unit. The transmit time out error is flagged on NERR.

Table 3 Specified Wiring Failure Cases on the Bus Line 1) (according to ISO 11519-2)

Table 3 Specified Wiring Failure Cases on the Bus Line (cont'd) 1) (according to ISO 11519-2)

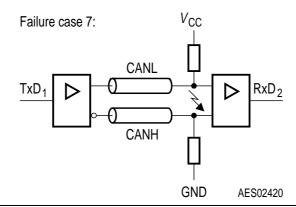

CANH **CANL Wire Short-Circuited to Battery** Failure case 6:  $V_{CANH} > 7.2 \text{ V}$ Failure case 3:  $V_{CANL} > 7.2 \text{ V}$ Failure case 6a:  $1.8 \text{ V} < V_{\text{CANH}} < 7.2 \text{ V}$  (no ISO failure) Failure case 3a:  $1.8 \text{ V} < V_{\text{CANL}} < 7.2 \text{ V}$  (no ISO failure) **CANL** CANL  $RxD_2$  $RxD_2$ TxD. **CANH CANH**  $V_{\mathsf{BAT}}$ **GND** AES02418 AES02419 GND

**CANL Mutually Short-Circuited to CANH**

The images represent a communication between two participants of the network (see **Figure 1**). The controller of the local area 1 transmits data (T×D<sub>1</sub>) to the receiver of the local area 2 (R×D<sub>2</sub>). When a single failure of cases 1 to 7 occurs, the error handling enables communication through appreciated reactions.

#### **Circuit Protection**

A current limiting circuit protects the CAN transceiver output stages from damage by short-circuit to positive and negative battery voltages.

The CANH and CANL pins are protected against electrical transients which may occur in the severe conditions of automotive environments.

The transmitter output stage generates the majority of the power dissipation. Therefore it is disabled if the junction temperature exceeds the maximum value. This effectively reduces power dissipation, and hence will lead to a lower chip temperature, while other parts of the IC can remain operating.

#### **Absolute Maximum Ratings**

| Parameter                                     | Symbol       | Lim          | it Values             | Unit | Notes |

|-----------------------------------------------|--------------|--------------|-----------------------|------|-------|

|                                               |              | min.         | max.                  |      |       |

| Input voltage at $V_{BAT}$                    | $V_{BAT}$    | - 0.3        | 40                    | V    | _     |

| Logic supply voltage $V_{\rm CC}$             | $V_{\sf CC}$ | - 0.3        | 6                     | V    | _     |

| Input voltage at TxD, RxD, NERR, NSTD and ENT | $V_{IN}$     | - 0.3        | V <sub>CC</sub> + 0.3 | V    | _     |

| Input voltage at CANH and CANL                | $V_{BUS}$    | <b>- 10</b>  | 27                    | V    | _     |

| Input voltage at CANH and CANL                | $V_{BUS}$    | - 40         | 40                    | V    | 1)    |

| Transient voltage at CANH and CANL            | $V_{BUS}$    | <b>– 150</b> | 100                   | V    | 2)    |

| Input voltage at WAKE                         | $V_{IN}$     | _            | $V_{\rm BAT} + 0.3$   | V    | _     |

| Input current at WAKE                         | $I_{IN}$     | <b>– 15</b>  | _                     | mA   | 3)    |

| Input voltage at INH, RTH and RTL             | $V_{IN}$     | - 0.3        | $V_{\rm BAT}$ + 0.3   | V    | _     |

| Termination resistances at RTL and RTH        | $R_{RTL/H}$  | 500          | 16000                 | Ω    | _     |

| Junction temperature                          | $T_{j}$      | - 40         | 150                   | °C   | _     |

| Storage temperature                           | $T_{ m stg}$ | - 55         | 155                   | °C   | _     |

| Electrostatic discharge voltage at any pin    | $V_{esd}$    | - 4000       | 4000                  | V    | 4)    |

<sup>&</sup>lt;sup>1)</sup>  $V_{CC} = 0$  to 5.5 V;  $V_{RAT} > 0$  V; t < 0.1 ms; load dump

Note: Maximum ratings are absolute ratings; exceeding one of these values may cause irreversible damage to the integrated circuit.

<sup>2)</sup> See ISO 7637

<sup>3)</sup> Negative currents flowing out of the IC.

Human body model: equivalent to discharging a 100 pF capacitor through a 1.5 k $\Omega$  resistor.

## **Operating Range**

| Parameter             | Symbol       | Lir  | mit Values | Unit | Notes |

|-----------------------|--------------|------|------------|------|-------|

|                       |              | min. | max.       |      |       |

| Logic input voltage   | $V_{\sf CC}$ | 4.75 | 5.25       | V    | _     |

| Battery input voltage | $V_{BAT}$    | 6    | 27         | V    | _     |

| Junction temperature  | $T_{i}$      | - 40 | 150        | °C   | _     |

#### **Thermal Resistance**

| Junction ambient | $R_{thja}$ | _ | 120 | K/W | _ |

|------------------|------------|---|-----|-----|---|

#### **Static Characteristics**

4.75 V  $\leq$   $V_{\rm CC} \leq$  5.25 V;  $V_{\rm NSTB} = V_{\rm CC}$ ; 6 V  $\leq$   $V_{\rm BAT} \leq$  27 V; - 40  $\leq$   $T_{\rm j} \leq$  + 125 °C (unless otherwise specified). All voltages are defined with respect to ground. Positive current flowing into the IC.

| Parameter | Symbol | Limit Values |      | Unit | Notes |  |

|-----------|--------|--------------|------|------|-------|--|

|           |        | min.         | typ. | max. |       |  |

## Supplies $V_{\rm CC},\,V_{\rm BAT}$

| Supply current                                          | $I_{\rm CC}$                 | _ | 3.5 | 10  | mA | recessive;                                                          |

|---------------------------------------------------------|------------------------------|---|-----|-----|----|---------------------------------------------------------------------|

|                                                         |                              | _ | 6   | 20  | mA | dominant;<br>TxD = 0 V; no load;<br>normal operating<br>mode        |

| Supply current $(V_{CC} \text{ stand-by})$              | $I_{\rm CC}$ + $I_{\rm BAT}$ | _ | 120 | 500 | μΑ | $V_{\rm CC}$ = 5 V;<br>$V_{\rm BAT}$ = 12 V;                        |

| Supply current $(V_{\mathrm{BAT}} \ \mathrm{stand-by})$ | $I_{BAT}$ + $I_{CC}$         | _ | 55  | 100 | μΑ | T <sub>A</sub> < 90 °C                                              |

| Supply current (sleep operation mode)                   | $I_{BAT}$                    | _ | 15  | 30  | μΑ | $V_{\rm CC}$ = 0 V;<br>$V_{\rm BAT}$ = 12 V;<br>$T_{\rm A}$ < 90 °C |

| Battery voltage for setting power-on flag               | $V_{BAT}$                    | _ | _   | 1.0 | V  | $V_{ m CC}$ stand-by mode                                           |

| Battery voltage low time for setting power-on flag      | t <sub>pw(on)</sub>          | _ | 200 | _   | μs | $V_{ m CC}$ stand-by mode                                           |

|                                                         |                              |   |     |     |    |                                                                     |

## Receiver Output R×D and Error Detection Output NERR

| HIGH level output voltage (pin NERR) | $V_{OH}$ | V <sub>CC</sub> – 0.9 | _ | $V_{\sf CC}$ | V | $I_0 = -100  \mu A$      |

|--------------------------------------|----------|-----------------------|---|--------------|---|--------------------------|

| HIGH level output voltage (pin RxD)  | $V_{OH}$ | V <sub>CC</sub> – 0.9 | _ | $V_{\sf CC}$ | V | $I_0 = -250  \mu A$      |

| LOW level output voltage             | $V_{OL}$ | 0                     | _ | 0.9          | V | $I_0 = -1.25 \text{ mA}$ |

4.75 V  $\leq$   $V_{\rm CC} \leq$  5.25 V;  $V_{\rm NSTB} = V_{\rm CC}$ ; 6 V  $\leq$   $V_{\rm BAT} \leq$  27 V; - 40  $\leq$   $T_{\rm j} \leq$  + 125 °C (unless otherwise specified). All voltages are defined with respect to ground. Positive current flowing into the IC.

| Parameter | Symbol | Limit Values |      | Unit | Notes |  |

|-----------|--------|--------------|------|------|-------|--|

|           |        | min.         | typ. | max. |       |  |

#### Transmission Input T×D, Not Stand-By NSTB and Enable Transfer ENT

| HIGH level input voltage threshold               | $V_{IH}$     | $V_{\rm CC}$ | _     | V <sub>CC</sub> + 0.3 | V  | 500 mV hysteresis           |

|--------------------------------------------------|--------------|--------------|-------|-----------------------|----|-----------------------------|

| LOW level input voltage threshold                | $V_{IL}$     | - 0.3        | _     | $0.3 	imes V_{ m CC}$ | V  | 500 mV hysteresis           |

| HIGH level input current (pins NSTB and ENT)     | $I_{IH}$     | _            | 9     | 20                    | μΑ | <i>V</i> <sub>i</sub> = 4 V |

| LOW level input current (pins NSTB and ENT)      | $I_{IL}$     | 0            | 1     | _                     | μΑ | <i>V</i> <sub>i</sub> = 1 V |

| HIGH level input current (pin TxD)               | $I_{IH}$     | - 200        | - 50  | - 25                  | μΑ | <i>V</i> <sub>i</sub> = 4 V |

| LOW level input current (pin TxD)                | $I_{IL}$     | - 800        | - 200 | - 100                 | μΑ | <i>V</i> <sub>i</sub> = 1 V |

| Forced battery voltage stand-by mode (fail safe) | $V_{\sf CC}$ | 2.75         | _     | 4.5                   | V  | _                           |

| Minimum hold time for Go-To-Sleep command        | $t_{hSLP}$   | 4            | 22    | 38                    | μs | _                           |

## Wake-up Input WAKE

| Input current             | $I_{IL}$     | - 3 | -2  | <b>–</b> 1 | μΑ | _                   |

|---------------------------|--------------|-----|-----|------------|----|---------------------|

| Wake-up threshold voltage | $V_{WK(th)}$ | 2.0 | 3.0 | 4.0        | V  | $V_{NSTB} = 0 \; V$ |

4.75 V  $\leq$   $V_{\rm CC} \leq$  5.25 V;  $V_{\rm NSTB} = V_{\rm CC}$ ; 6 V  $\leq$   $V_{\rm BAT} \leq$  27 V; - 40  $\leq$   $T_{\rm j} \leq$  + 125 °C (unless otherwise specified). All voltages are defined with respect to ground. Positive current flowing into the IC.

| Parameter | Symbol | Li   | mit Valu | ies  | Unit | Notes |

|-----------|--------|------|----------|------|------|-------|

|           |        | min. | typ.     | max. |      |       |

#### **Inhibit Output INH**

| HIGH level voltage drop            | $\Delta V_{H}$ | _          | 0.5 | 0.8 | V  | $I_{\text{INH}} = -0.18 \text{ mA};$                       |

|------------------------------------|----------------|------------|-----|-----|----|------------------------------------------------------------|

| $\Delta V_{H} = V_{BAT} - V_{INH}$ |                |            |     |     |    |                                                            |

| Leakage current                    | $I_{LI}$       | <b>-</b> 5 | _   | 5.0 | μΑ | sleep operation mode; $V_{\mathrm{INH}} = 0 \; \mathrm{V}$ |

#### **Bus Lines CANL, CANH**

| Differential receiver recessive-to-dominant threshold voltage | $V_{ m dRxD(rd)}$ | - 2.8                 | - 2.5  | - 2.2        | V  | V <sub>CC</sub> = 5.0 V                                   |

|---------------------------------------------------------------|-------------------|-----------------------|--------|--------------|----|-----------------------------------------------------------|

| Differential receiver dominant-to-recessive threshold voltage | $V_{dRxD(dr)}$    | - 3.17                | - 2.87 | - 2.58       | V  | V <sub>CC</sub> = 5.0 V                                   |

| CANH recessive output voltage                                 | $V_{CANHr}$       | 0.1                   | 0.2    | 0.3          | V  | $TxD = V_{CC};$ $R_{RTH} < 4 \text{ k}\Omega$             |

| CANL recessive output voltage                                 | $V_{CANLr}$       | V <sub>CC</sub> – 0.2 | _      | _            | V  | $TxD = V_{CC};$<br>$R_{RTL} < 4 \text{ k}\Omega$          |

| CANH dominant output voltage                                  | $V_{CANHd}$       | V <sub>CC</sub> – 1.4 | _      | $V_{\sf CC}$ | V  | TxD = 0 V;<br>normal mode;<br>$I_{CANH} = -40 \text{ mA}$ |

| CANL dominant output voltage                                  | $V_{CANLd}$       | _                     | 1.1    | 1.4          | V  | TxD = 0 V;<br>normal mode;<br>$I_{CANL} = 40 \text{ mA}$  |

| CANH output current                                           | $I_{CANH}$        | - 130                 | - 90   | - 50         | mA | $V_{\text{CANH}} = 0 \text{ V};$<br>TxD = 0 V             |

|                                                               |                   | _                     | 0      | _            | μΑ | sleep operation mode; $V_{\rm CANH}$ = 12 V               |

4.75 V  $\leq$   $V_{\rm CC} \leq$  5.25 V;  $V_{\rm NSTB} = V_{\rm CC}$ ; 6 V  $\leq$   $V_{\rm BAT} \leq$  27 V; - 40  $\leq$   $T_{\rm j} \leq$  + 125 °C (unless otherwise specified). All voltages are defined with respect to ground. Positive current flowing into the IC.

| Parameter                                                                                  | Symbol            | Li                     | mit Val              | ues                  | Unit | Notes                                                                                                                                                              |

|--------------------------------------------------------------------------------------------|-------------------|------------------------|----------------------|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                            |                   | min.                   | typ.                 | max.                 |      |                                                                                                                                                                    |

| CANL output current                                                                        | $I_{CANL}$        | - 50                   | 90                   | 130                  | mA   | $V_{\text{CANL}} = 5 \text{ V};$<br>TxD = 0 V                                                                                                                      |

|                                                                                            |                   | _                      | 0                    | -                    | μΑ   | sleep operation mode; $V_{\rm CANL} = 0 \; \rm V;$ $V_{\rm BAT} = 12 \; \rm V$                                                                                     |

| Voltage detection<br>threshold for short-circuit<br>to battery voltage on<br>CANH and CANL | $V_{ m det(th)}$  | 6.5                    | 7.3                  | 8.0                  | V    | normal operation mode                                                                                                                                              |

| Voltage detection<br>threshold for short-circuit<br>to battery voltage on<br>CANH          | $V_{ m det(th)}$  | V <sub>BAT</sub> – 2.5 | V <sub>BAT</sub> – 2 | V <sub>BAT</sub> – 1 | V    | stand-by/<br>sleep operation<br>mode                                                                                                                               |

| CANH wake-up voltage threshold                                                             | $V_{WAKEH}$       | 1.2                    | 1.9                  | 2.7                  | V    | _                                                                                                                                                                  |

| CANL wake-up voltage threshold                                                             | $V_{WAKEL}$       | 2.4                    | 3.1                  | 3.8                  | V    | -                                                                                                                                                                  |

| Wake-up voltage threshold difference                                                       | $\Delta V_{WAKE}$ | 0.2                    | _                    | _                    | V    | $\Delta V_{\rm SLP} = V_{\rm SLPL} - \\ V_{\rm SLPH}$                                                                                                              |

| CANH single-ended receiver threshold                                                       | $V_{CANH}$        | 1.5                    | 1.9                  | 2.3                  | V    | failure cases 3, 5 and 7                                                                                                                                           |

| CANL single-ended receiver threshold                                                       | $V_{CANL}$        | 2.8                    | 3.1                  | 3.8                  | V    | failure case 6 and<br>6a                                                                                                                                           |

| CANH leakage current                                                                       | $I_{CANHI}$       | _                      | 0                    | 5                    | μΑ   | $V_{\rm CC} = 0 \text{ V},$<br>$V_{\rm bat} = 0 \text{ V},$<br>$V_{\rm CANL} = 13.5 \text{ V},$<br>$R_{\rm RTL} = 100 \Omega,$<br>$T_{\rm j} < 85 ^{\circ}{\rm C}$ |

4.75 V  $\leq$   $V_{\rm CC} \leq$  5.25 V;  $V_{\rm NSTB} = V_{\rm CC}$ ; 6 V  $\leq$   $V_{\rm BAT} \leq$  27 V; - 40  $\leq$   $T_{\rm j} \leq$  + 125 °C (unless otherwise specified). All voltages are defined with respect to ground. Positive current flowing into the IC.

| Parameter            | Symbol      | Limit Values |      |      | Unit | Notes                                                                                                                                                                                            |

|----------------------|-------------|--------------|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |             | min.         | typ. | max. |      |                                                                                                                                                                                                  |

| CANL leakage current | $I_{CANLI}$ | _            | 0    | 5    | μΑ   | $\begin{split} V_{\text{CC}} &= 0 \text{ V,} \\ V_{\text{bat}} &= 0 \text{ V,} \\ V_{\text{CANH}} &= 5 \text{ V,} \\ R_{\text{RTH}} &= 100 \Omega, \\ T_{\text{j}} &< 85 \text{ °C} \end{split}$ |

## **Termination Outputs RTL, RTH**

| RTL to $V_{\rm CC}$ switch-on resistance | $R_{RTL}$   | _                     | 43                    | 95  | Ω  | $I_{\rm o}$ = $-$ 10 mA;<br>normal operating<br>mode                                                                          |

|------------------------------------------|-------------|-----------------------|-----------------------|-----|----|-------------------------------------------------------------------------------------------------------------------------------|

| RTL output voltage                       | $V_{oRTL}$  | V <sub>CC</sub> – 1.0 | V <sub>CC</sub> – 0.7 | _   | V  | $ I_{\rm o} $ < 1 mA; $V_{\rm CC}$ stand-by mode                                                                              |

| RTL to BAT switch series resistance      | $R_{oRTL}$  | 10                    | 16                    | 35  | kΩ | $V_{\mathrm{BAT}}$ stand-by or sleep operation mode                                                                           |

| RTH to ground switch-on resistance       | $R_{RTH}$   | _                     | 43                    | 95  | Ω  | $I_{\rm o}$ = 10 mA; normal operating mode                                                                                    |

| RTH output voltage                       | $V_{oRTH}$  | _                     | 0.7                   | 1.0 | V  | I <sub>o</sub> = 1 mA;<br>low power mode                                                                                      |

| RTH pull-down current                    | $I_{RTHpd}$ | _                     | 75                    | _   | μΑ | normal operating<br>mode, failure<br>cases 6 and 6a                                                                           |

| RTL pull-up current                      | $I_{RTLpu}$ | _                     | <b>- 75</b>           | _   | μΑ | normal operating<br>mode, failure<br>cases 3, 3a, 5 and 7                                                                     |

| RTH leakage current                      | $I_{RTHI}$  | _                     | 0                     | 5   | μΑ | $V_{\rm CC}$ = 0 V,<br>$V_{\rm bat}$ = 0 V,<br>$V_{\rm CANH}$ = 5 V,<br>$R_{\rm RTH}$ = 100 $\Omega$ ,<br>$T_{\rm j}$ < 85 °C |

4.75 V  $\leq$   $V_{\rm CC} \leq$  5.25 V;  $V_{\rm NSTB} = V_{\rm CC}$ ; 6 V  $\leq$   $V_{\rm BAT} \leq$  27 V; - 40  $\leq$   $T_{\rm j} \leq$  + 125 °C (unless otherwise specified). All voltages are defined with respect to ground. Positive current flowing into the IC.

| Parameter           | Symbol     | Limit Values |      |      | Unit | Notes                                                                                                                                                              |

|---------------------|------------|--------------|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |            | min.         | typ. | max. |      |                                                                                                                                                                    |

| RTL leakage current | $I_{RTLI}$ | _            | 0    | 5    | μΑ   | $V_{\rm CC} = 0 \text{ V},$<br>$V_{\rm bat} = 0 \text{ V},$<br>$V_{\rm CANL} = 13.5 \text{ V},$<br>$R_{\rm RTL} = 100 \Omega,$<br>$T_{\rm j} < 85 ^{\circ}{\rm C}$ |

#### **Thermal Shutdown**

| Shutdown junction | $T_{iSH}$ | 150 | _ | _ | °С | _ |

|-------------------|-----------|-----|---|---|----|---|

| temperature       | JOH       |     |   |   |    |   |

## **Dynamic Characteristics**

$V_{\rm CC}$  = 4.75 V to 5.25 V;  $V_{\rm NSTB}$  =  $V_{\rm CC}$ ;  $V_{\rm BAT}$  = 6 V to 27 V;  $T_{\rm A}$  = - 40 to + 125 °C (unless otherwise specified). All voltages are defined with respect to ground. Positive current flows into the IC.

| Parameter                                                      | Symbol               | Limit Values |      |      | Unit | Notes                                                                |

|----------------------------------------------------------------|----------------------|--------------|------|------|------|----------------------------------------------------------------------|

|                                                                |                      | min.         | typ. | max. |      |                                                                      |

| CANH and CANL bus output transition time recessive-to-dominant | $t_{\sf rd}$         | 0.6          | 1.4  | 2.0  | μs   | 10% to 90%;<br>$C_1 = 10 \text{ nF};$<br>$C_2 = 0; R_1 = 100 \Omega$ |

| CANH and CANL bus output transition time dominant-to-recessive | t <sub>dr</sub>      | 0.7          | 1.0  | 1.3  | μs   | 10% to 90%;<br>$C_1 = 1 \text{ nF}; C_2 = 0;$<br>$R_1 = 100 \Omega$  |

| Minimum dominant time for wake-up on CANL or CANH              | t <sub>wu(min)</sub> | 8            | 22   | 38   | μs   | stand-by modes $V_{\rm BAT}$ = 12 V                                  |

| Minimum WAKE Low time for wake-up                              | t <sub>WK(min)</sub> | 20           | 36   | 60   | μs   | Low power modes $V_{\rm BAT}$ = 12 V                                 |

| Failure cases 3 and 6 detection time                           | $t_{fail}$           | 30           | 55   | 80   | μs   | normal operating mode                                                |

| Failure case 6a detection time                                 |                      | 2            | 4.8  | 8    | ms   | normal operating mode                                                |

| Failure cases 5, 6, 6a and 7 recovery time                     |                      | 30           | 55   | 80   | μs   | normal operating mode                                                |

| Failure cases 3 recovery time                                  |                      | 150          | 450  | 750  | μs   | normal operating mode                                                |

| Failure cases 5 and 7 detection time                           |                      | 0.75         | 1.8  | 4.0  | ms   | normal operating mode                                                |

| Failure cases 5, 6, 6a and 7 detection time                    |                      | 0.8          | 3.6  | 8.0  | ms   | stand-by modes; $V_{\rm BAT}$ = 12 V                                 |

| Failure cases 5, 6, 6a and 7 recovery time                     |                      | _            | 2    | _    | μs   | stand-by modes; $V_{\rm BAT}$ = 12 V                                 |

## **Dynamic Characteristics** (cont'd)

$V_{\rm CC}$  = 4.75 V to 5.25 V;  $V_{\rm NSTB}$  =  $V_{\rm CC}$ ;  $V_{\rm BAT}$  = 6 V to 27 V;  $T_{\rm A}$  = - 40 to + 125 °C (unless otherwise specified). All voltages are defined with respect to ground. Positive current flows into the IC.

| Parameter                                                | Symbol      | Li   | Limit Values |      |    | Notes                                                                                                          |

|----------------------------------------------------------|-------------|------|--------------|------|----|----------------------------------------------------------------------------------------------------------------|

|                                                          |             | min. | typ.         | max. |    |                                                                                                                |

| Propagation delay TxD-to-RxD LOW (recessive to dominant) | $t_{PD(L)}$ | _    | 0.8          | 1.5  | μs | $C_1$ = 100 pF;<br>$C_2$ = 0; $R_1$ = 100 $\Omega$ ;<br>no failures and bus<br>failure cases 1, 2,<br>3a and 4 |

|                                                          |             | _    | 0.8          | 1.5  | μs | $C_1$ = $C_2$ = 3.3 nF;<br>$R_1$ = 100 $\Omega$ ; no bus<br>failure and failure<br>cases 1, 2, 3a and          |

|                                                          |             | _    | 1.2          | 1.8  | μs | $C_1$ 100 pF; $C_2$ = 0; $R_1$ = 100 $\Omega$ ; bus failure cases 3, 5, 6, 6a and 7                            |

|                                                          |             | _    | 1.2          | 1.8  | μs | $C_1 = C_2 = 3.3 \text{ nF};$<br>$R_1 = 100 \Omega$ ; bus<br>failure cases 3, 5,<br>6, 6a and 7                |

## **Dynamic Characteristics** (cont'd)

$V_{\rm CC}$  = 4.75 V to 5.25 V;  $V_{\rm NSTB}$  =  $V_{\rm CC}$ ;  $V_{\rm BAT}$  = 6 V to 27 V;  $T_{\rm A}$  = - 40 to + 125 °C (unless otherwise specified). All voltages are defined with respect to ground. Positive current flows into the IC.

| Parameter                                                                                                                             | Symbol              | Li   | mit Val | ues  | Unit | Notes                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|---------|------|------|---------------------------------------------------------------------------------------------------------------|

|                                                                                                                                       |                     | min. | typ.    | max. |      |                                                                                                               |

| Propagation delay TxD-to-RxD HIGH (dominanat to recessive)                                                                            | t <sub>PD(H)</sub>  | _    | 1.5     | 2.0  | μs   | $C_1$ = 100 pF;<br>$C_2$ = 0; $R_1$ =100 $\Omega$ ;<br>no failures and bus<br>failure cases 1, 2,<br>3a and 4 |

|                                                                                                                                       |                     | _    | 2.5     | 3.0  | μs   | $C_1 = C_2 = 3.3 \text{ nF};$<br>$R_1 = 100 \Omega;$ no bus<br>failure and failure<br>cases 1, 2, 3a and<br>4 |

|                                                                                                                                       |                     | _    | 1.0     | 1.5  | μs   | $C_1$ 100 pF; $C_2$ = 0; $R_1$ = 100 $\Omega$ ; bus failure cases 3, 5, 6, 6a and 7                           |

|                                                                                                                                       |                     | _    | 1.4     | 2.1  | μs   | $C_1 = C_2 = 3.3 \text{ nF};$<br>$R_1 = 100 \Omega;$ bus<br>failure cases 3, 5,<br>6, 6a and 7                |

| Minimum hold time to go sleep command                                                                                                 | t <sub>h(min)</sub> | 4    | 22      | 38   | μs   | _                                                                                                             |

| Edge-count difference<br>(falling edge) between<br>CANH and CANL for<br>failure cases 1, 2, 3a and 4<br>detection NERR becomes<br>LOW | n <sub>e</sub>      | -    | 4       | _    | _    | normal operating mode                                                                                         |

| Edge-count difference<br>(rising edge) between<br>CANH and CANL for<br>failure cases 1, 2, 3a and 4<br>recovery                       |                     | _    | 2       | _    | _    |                                                                                                               |

| TxD permanent dominant disable time                                                                                                   | $t_{TxD}$           | 1    | 2.5     | 4    | ms   | normal mode                                                                                                   |

#### **Test and Application**

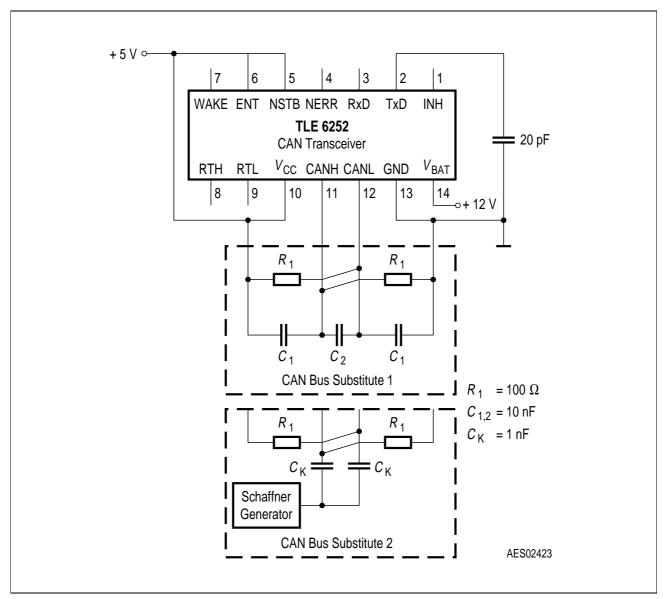

Figure 5 Test Circuits

For isolated testing the CAN Bus Substitute 1 is connected to the CAN Transceiver (see **Figure 5**). The capacitors  $C_{1-3}$  simulate the cable. Allowed minimum values of the termination resistors  $R_{\rm RTH}$  and  $R_{\rm RTL}$  are 500  $\Omega$ . Electromagnetic interference on the bus lines is simulated by switching to CAN Bus Substitute 2. The waves of the applied transients will be in accordance with ISO 7637 part 1, test 1, test pulses 1, 2, 3a and 3b.

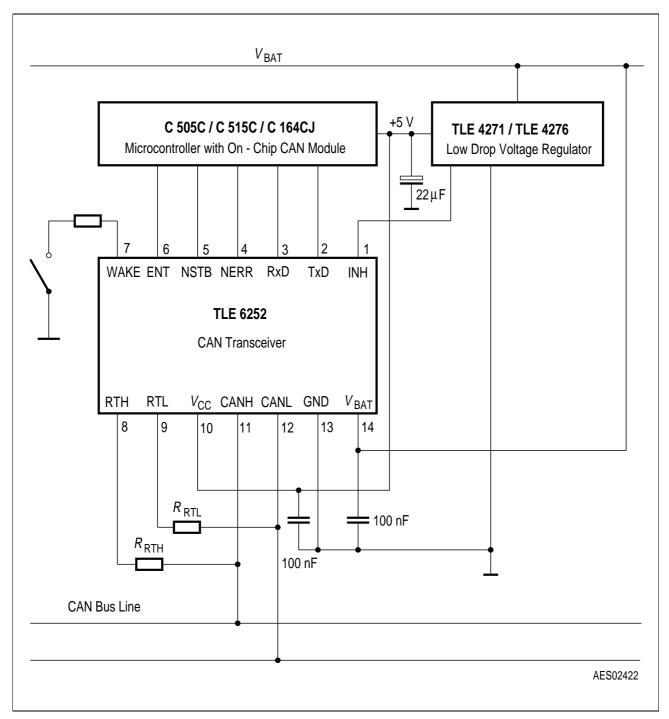

Figure 6 Application of the TLE 6252 G

SIEMENS TLE 6252 G

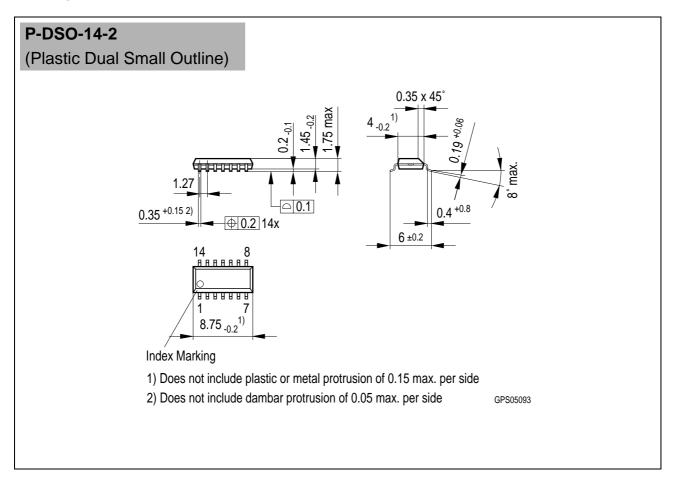

#### **Package Outlines**

#### **Sorts of Packing**

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".

SMD = Surface Mounted Device

Dimensions in mm