# Single-Phase High-Performance Wide-Span Energy Metering IC

#### DATASHEET

## **FEATURES**

## **Metering Features**

- Metering features fully in compliance with the requirements of IEC62052-11, IEC62053-21 and IEC62053-23; applicable in class 1 or class 2 single-phase watthour meter or class 2 single-phase var-hour meter.

- Accuracy of 0.1% for active energy and 0.2% for reactive energy over a dynamic range of 5000:1.

- Temperature coefficient is 15 ppm/ <sup>°</sup>C (typical) for on-chip reference voltage

- Single-point calibration over a dynamic range of 5000:1 for active energy; no calibration needed for reactive energy.

- Energy Meter Constant doubling at low current to save verification time.

- Electrical parameters measurement: less than  $\pm 0.5\%$  fiducial error for Vrms, Irms, mean active/ reactive/ apparent power, frequency, power factor and phase angle.

- Forward/ reverse active/ reactive energy with independent energy registers. Active/ reactive energy can be output by pulse or read through energy registers to adapt to different applications.

- Programmable startup and no-load power threshold.

- Dedicated ADC and different gains for L line and N line current sampling circuits.

Current sampled over shunt resistor or current transformer (CT); voltage sampled over resistor divider network or potential transformer (PT).

- Programmable L line and N line metering modes: anti-tampering mode (larger power), L line mode (fixed L line), L+N mode (applicable for single-phase three-wire system) and flexible mode (configure through register).

- Programmable L line and N line power difference threshold in anti-tampering mode.

#### Other Features

- 3.3V single power supply. Operating voltage range: 2.8~3.6V. Metering accuracy guaranteed within 3.0V~3.6V. 5V compatible for digital input.

- · Built-in hysteresis for power-on reset.

- Selectable UART interface and SPI interface (four-wire SPI interface or simplified three-wire SPI interface with fixed 24 cycles for all registers operation).

- Parameter diagnosis function and programmable interrupt output of the IRQ interrupt signal and the WarnOut signal.

- Programmable voltage sag detection and zero-crossing output.

- · Channel input range

- Voltage channel (when gain is '1'): 120μVrms~600mVrms.

- L line current channel (when gain is '24'): 5μVrms~25mVrms.

- N line current channel (when gain is '1'): 120μVrms~600mVrms.

- Programmable L line current gain: 1, 4, 8, 16, 24; Programmable N line gain: 1, 2, 4.

- Support L line and N line offset compensation.

- CF1 and CF2 output active and reactive energy pulses respectively which can be used for calibration or energy accumulation.

- Crystal oscillator frequency: 8.192 MHz.

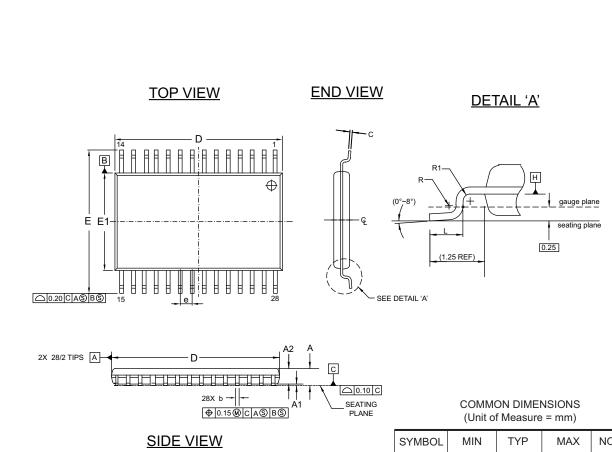

- · Green SSOP28 package.

- Operating temperature: -40  $^{\circ}$ C ~ +85  $^{\circ}$ C .

## **APPLICATION**

The M90E26 is used for active and reactive energy metering for single-phase two-wire (1P2W), single-phase three-wire (1P3W) or anti-tampering energy meters. With the measurement function, the M90E26 can also be used in power instruments which need to measure voltage, current, etc.

## **DESCRIPTION**

The M90E26 is a high-performance wide-span energy metering chip. The ADC and DSP technology ensure the chip's long-term stability over variations in grid and ambient environmental conditions.

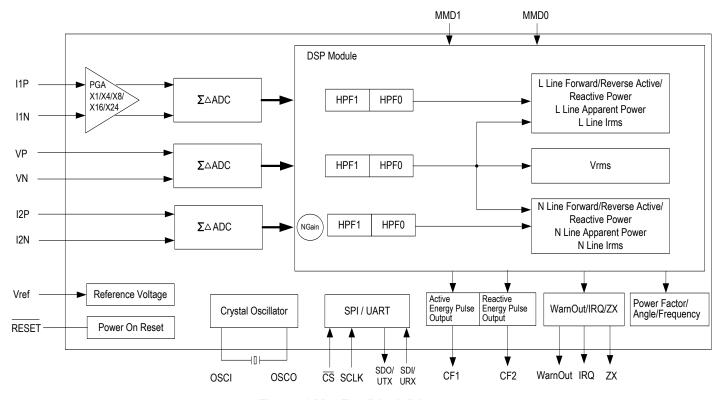

## **BLOCK DIAGRAM**

Figure-1 M90E26 Block Diagram

# **Table of Contents**

|   | eatures                                                              |    |

|---|----------------------------------------------------------------------|----|

| A | pplication                                                           | 2  |

| D | escription                                                           | 2  |

| В | lock Diagram                                                         | 2  |

| 1 | Pin Assignment                                                       | 7  |

|   | Pin Description                                                      |    |

| 3 | Functional Description                                               | 10 |

|   | 3.1 Dynamic Metering Range                                           |    |

|   | 3.2 Startup and No-Load Power                                        |    |

|   | 3.3 Energy Registers                                                 |    |

|   | 3.4 N Line Metering and Anti-Tampering                               |    |

|   | 3.4.1 Metering Mode and L/N Line Current Sampling Gain Configuration |    |

|   | 3.4.2 Anti-Tampering Mode                                            |    |

|   | 3.5 Measurement and Zero-Crossing                                    |    |

|   | 3.5.1 Measurement                                                    |    |

|   | 3.5.2 Zero-Crossing                                                  | 13 |

|   | 3.6 Calibration                                                      | 14 |

|   | 3.7 Reset                                                            | 14 |

| 4 | Interface                                                            | 15 |

|   | 4.1 SPI Interface                                                    |    |

|   | 4.1.1 Four-Wire Mode                                                 |    |

|   | 4.1.2 Three-Wire Mode                                                | 16 |

|   | 4.1.3 Timeout and Protection                                         | 17 |

|   | 4.2 UART Interface                                                   |    |

|   | 4.2.1 Byte Level Timing                                              |    |

|   | 4.2.2 Write Transaction                                              |    |

|   | 4.2.3 Read transaction                                               |    |

|   |                                                                      |    |

|   | 4.3 WarnOut Pin for Fatal Error Warning                              |    |

|   |                                                                      |    |

| 5 | Register                                                             |    |

|   | 5.1 Register List                                                    |    |

|   | 5.2 Status and Special Register                                      |    |

|   | 5.3 Metering/ Measurement Calibration and Configuration              |    |

|   | 5.3.1 Metering Calibration and Configuration Register                |    |

|   | 5.3.2 Measurement Calibration Register                               |    |

|   | 5.4 Energy Register                                                  |    |

|   | 3.3 IVIEASULETTIETIL REUISIEL                                        |    |

| 6 | Electrical Specification     | . 51 |

|---|------------------------------|------|

|   | 6.1 Electrical Specification |      |

|   | 6.2 SPI Interface Timing     |      |

|   | 6.3 Power On Reset Timing    |      |

|   | 6.4 Zero-Crossing Timing     |      |

|   | 6.5 Voltage Sag Timing       |      |

|   | 6.6 Pulse Output             |      |

|   | 6.7 Absolute Maximum Rating  |      |

|   | rdering Information          |      |

|   | ackaging Drawings            |      |

|   | evision History              |      |

|   |                              |      |

# **List of Tables**

| Table-1  | Pin Description                                       | 8  |

|----------|-------------------------------------------------------|----|

| Table-2  | Active Energy Metering Error                          | 10 |

| Table-3  | Reactive Energy Metering Error                        | 10 |

| Table-4  | Threshold Configuration for Startup and No-Load Power | 10 |

| Table-5  | Energy Registers                                      | 11 |

| Table-6  | Metering Mode                                         |    |

| Table-7  | The Measurement Format                                |    |

| Table-8  | Read / Write Result in Four-Wire Mode                 | 17 |

| Table-9  | Read / Write Result in Three-Wire Mode                | 17 |

| Table-10 | Register List                                         | 21 |

|          | SPI Timing Specification                              |    |

|          | Power On Reset Specification                          |    |

| Table-13 | Zero-Crossing Specification                           | 55 |

| Table-14 | Voltage Sag Specification                             | 56 |

# List of Figures

| . 2 |

|-----|

| . 7 |

| 15  |

| 15  |

| 16  |

| 16  |

| 18  |

| 18  |

| 19  |

| 53  |

| 53  |

| 54  |

| 55  |

| 55  |

| 56  |

|     |

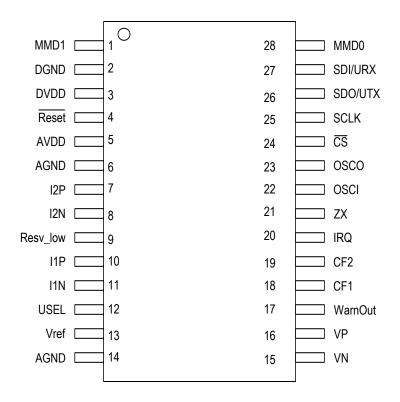

#### 1 **PIN ASSIGNMENT**

Figure-2 Pin Assignment (Top View)

# 2 PIN DESCRIPTION

**Table-1 Pin Description**

| Name       | Pin No.  | I/O note 1 | Туре   | Description                                                                                                                                                                                                                                                                                                       |  |

|------------|----------|------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Reset      | 4        | I          | LVTTL  | Reset: Reset Pin (active low) This pin should connect to ground through a 0.1μF filter capacitor. In application it can also directly connect to one output pin from microcontrolle (MCU).                                                                                                                        |  |

| DVDD       | 3        | I          | Power  | DVDD: Digital Power Supply This pin provides power supply to the digital part. It should be decoupled with a $10\mu F$ electrolytic capacitor and a $0.1\mu F$ capacitor.                                                                                                                                         |  |

| DGND       | 2        | I          | Power  | DGND: Digital Ground                                                                                                                                                                                                                                                                                              |  |

| AVDD       | 5        | I          | Power  | AVDD: Analog Power Supply This pin provides power supply to the analog part. It should be decoupled with a 0.1μF capacitor.                                                                                                                                                                                       |  |

| Vref       | 13       | 0          | Analog | Vref: Output Pin for Reference Voltage This pin should be decoupled with a 1μF capacitor and a 1nF capacitor.                                                                                                                                                                                                     |  |

| AGND       | 6, 14    | I          | Power  | AGND: Analog Ground                                                                                                                                                                                                                                                                                               |  |

| I1P<br>I1N | 10<br>11 | I          | Analog | I1P: Positive Input for L Line Current I1N: Negative Input for L Line Current These pins are differential inputs for L line current. Input range is 5μVrms~25mVrms when gain is '24'.                                                                                                                             |  |

| 12P<br>12N | 7<br>8   | I          | Analog | I2P: Positive Input for N Line Current I2N: Negative Input for N Line Current These pins are differential inputs for N line current. Input range is 120μVrms~600mVrms when gain is '1'.                                                                                                                           |  |

| VP<br>VN   | 16<br>15 | I          | Analog | VP: Positive Input for Voltage VN: Negative Input for Voltage These pins are differential inputs for voltage. Input range is 120μVrms~600mVrms.                                                                                                                                                                   |  |

| USEL       | 12       | I          | LVTTL  | USEL: UART/SPI Interface Selection High: UART interface Low: SPI interface  Note: This pin should not change after reset.                                                                                                                                                                                         |  |

| CS         | 24       | ı          | LVTTL  | CS: Chip Select (Active Low) of SPI In 4-wire SPI mode, this pin must be driven from high to low for each read/ write operation, and maintain low for the entire operation. In 3-wire SPI mode, this pin must be low all the time. Refer to section 4.1.  In UART interface, this pin should be connected to VDD. |  |

| SCLK       | 25       | I          | LVTTL  | SCLK: Serial Clock of SPI This pin is used as the clock for the SPI interface. Data on SDI is shifted into the chip on the rising edge of SCLK while data on SDO is shifted out of the chip on the falling edge of SCLK.  In UART interface, this pin should be connected to ground.                              |  |

Table-1 Pin Description (Continued)

| Name         | Pin No.  | I/O note 1 | Туре  | Description                                                                                                                                                                                                                                    |

|--------------|----------|------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |          |            |       | SDO: Serial Data Output of SPI This pin is used as the data output for the SPI interface. Data on this pin is shifted out of the chip on the falling edge of SCLK.                                                                             |

| SDO/UTX      | 26       | OZ         | LVTTL | UTX: UART Data Transmit This pin is used to transmit data for the UART interface. This pin needs to be pulled up to VDD by a $10k\Omega$ resistor."                                                                                            |

|              |          |            |       | Note: UART and SPI interface is selected by the USEL pin.                                                                                                                                                                                      |

|              |          |            |       | SDI: Serial Data Input of SPI This pin is used as the data input for the SPI interface. Address and data on this pin is shifted into the chip on the rising edge of SCLK.                                                                      |

| SDI/URX      | 27       | ı          | LVTTL | URX: UART Data Receive This pin is used to receive data for the UART interface.                                                                                                                                                                |

|              |          |            |       | Note: UART and SPI interface is selected by the USEL pin.                                                                                                                                                                                      |

| MMD1<br>MMD0 | 1<br>28  | I          | LVTTL | MMD1/0: Metering Mode Configuration  00: anti-tampering mode (larger power);  01: L line mode (fixed L line);  10: L+N mode (applicable for single-phase three-wire system);  11: flexible mode (line specified by the LNSel bit (MMode, 2BH)) |

| OSCI         | 22       | I          | LVTTL | OSCI: External Crystal Input An 8.192 MHz crystal is connected between OSCI and OSCO. In application, this pin should be connected to ground through a 12pF capacitor.                                                                         |

| OSCO         | 23       | 0          | LVTTL | OSCO: External Crystal Output An 8.192 MHz crystal is connected between OSCI and OSCO. In application, this pin should be connected to ground through a 12pF capacitor.                                                                        |

| CF1<br>CF2   | 18<br>19 | 0          | LVTTL | CF1: Active Energy Pulse Output CF2: Reactive Energy Pulse Output These pins output active/reactive energy pulses.                                                                                                                             |

| ZX           | 21       | 0          | LVTTL | ZX: Voltage Zero-Crossing Output This pin is asserted when voltage crosses zero. Zero-crossing mode can be configured to positive zero-crossing, negative zero-crossing or all zero-crossing by the Zxcon[1:0] bits (MMode, 2BH).              |

| IRQ          | 20       | 0          | LVTTL | IRQ: Interrupt Output This pin is asserted when one or more events in the SysStatus register (01H) occur. It is deasserted when there is no bit set in the SysStatus register (01H).                                                           |

| WarnOut      | 17       | 0          | LVTTL | WarnOut: Fatal Error Warning This pin is asserted when there is metering parameter calibration error or voltage sag. Refer to section 4.3.                                                                                                     |

| Resv_Low     | 9        | I          | LVTTL | Reserved For normal operation, these pins should be connected to ground.                                                                                                                                                                       |

# 3 FUNCTIONAL DESCRIPTION

#### 3.1 DYNAMIC METERING RANGE

Accuracy is 0.1% for active energy metering and 0.2% for reactive energy metering over a dynamic range of 5000:1 (typical). Refer to Table-2 and Table-3.

**Table-2 Active Energy Metering Error**

| Current                                                                                         | Power Factor     | Error(%) |  |

|-------------------------------------------------------------------------------------------------|------------------|----------|--|

| 20mA ≤ I < 50mA                                                                                 | 1.0              | ±0.2     |  |

| 50mA ≤ I ≤ 100A                                                                                 | 1.0              | ±0.1     |  |

| 50mA ≤ I < 100mA                                                                                | 0.5 (Inductive)  | ±0.2     |  |

| 100mA ≤ I ≤ 100A                                                                                | 0.8 (Capacitive) | ±0.1     |  |

| Note: Shunt resistor is 250 $\mu\Omega$ or CT ratio is 1000:1 and load resistor is 6 $\Omega$ . |                  |          |  |

**Table-3 Reactive Energy Metering Error**

| Current                                                                                        | sinφ (Inductive or Capacitive) | Error(%) |  |

|------------------------------------------------------------------------------------------------|--------------------------------|----------|--|

| 20mA ≤ I < 50mA                                                                                | 1.0                            | ±0.4     |  |

| 50mA ≤ I ≤ 100A                                                                                | 1.0                            | ±0.2     |  |

| 50mA ≤ I < 100mA                                                                               | 0.5                            | ±0.4     |  |

| 100mA ≤ I ≤ 100A                                                                               | 0.5                            | ±0.2     |  |

| Note: Shunt resistor is 250 $\mu\Omega$ or CT ratio is 1000:1 and load resistor is $6\Omega$ . |                                |          |  |

## 3.2 STARTUP AND NO-LOAD POWER

Startup and no-load power thresholds are programmable, both for active and reactive power. The related registers are listed in Table-4.

Table-4 Threshold Configuration for Startup and No-Load Power

| Threshold                            | Register      |

|--------------------------------------|---------------|

| Threshold for Active Startup Power   | PStartTh, 27H |

| Threshold for Active No-load Power   | PNoITh, 28H   |

| Threshold for Reactive Startup Power | QStartTh, 29H |

| Threshold for Reactive No-load Power | QNolTh, 2AH   |

The M90E26 will start within 1.2 times of the theoretical startup time of the configured startup power, if startup power is less than the corresponding power of 20mA when power factor or  $\sin\phi$  is 1.0.

The M90E26 has no-load status bits, the Pnoload/Qnoload bit (EnStatus, 46H). The M90E26 will not output any active pulse (CF1) in active no-load state. The M90E26 will not output any reactive pulse (CF2) in reactive no-load state.

## 3.3 ENERGY REGISTERS

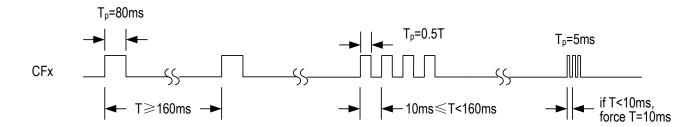

The M90E26 provides energy pulse output CFx (CF1/CF2) which is proportionate to active/reactive energy. Energy is usually accumulated by adding the CFx pulses in system applications. Alternatively, the M90E26 provides energy registers. There are forward (inductive), reverse (capacitive) and absolute energy registers for both active and reactive energy. Refer to Table-5.

**Table-5 Energy Registers**

| Energy                               | Register      |

|--------------------------------------|---------------|

| Forward Active Energy                | APenergy, 40H |

| Reverse Active Energy                | ANenergy, 41H |

| Absolute Active Energy               | ATenergy, 42H |

| Forward (Inductive) Reactive Energy  | RPenergy, 43H |

| Reverse (Capacitive) Reactive Energy | RNenergy, 44H |

| Absolute Reactive Energy             | RTenergy, 45H |

Each energy register is cleared after read. The resolution of energy registers is 0.1CF, i.e. one LSB represents 0.1 energy pulse.

## 3.4 N LINE METERING AND ANTI-TAMPERING

#### 3.4.1 METERING MODE AND L/N LINE CURRENT SAMPLING GAIN CONFIGURATION

The M90E26 has two current sampling circuits with N line metering and anti-tampering functions. The MMD1 and MMD0 pins are used to configure the metering mode. Refer to Table-6.

#### **Table-6 Metering Mode**

| MMD1                           | MD1 MMD0 Metering Mode                   |                                                              | CFx (CF1 or CF2) Output                                        |  |

|--------------------------------|------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------|--|

| 0                              | U IU IANTI-TAMBERING WORE (Jarger bower) |                                                              | CFx represents the larger energy line. Refer to section 3.4.2. |  |

| 0 1 L Line Mode (fixed L line) |                                          | L Line Mode (fixed L line)                                   | CFx represents L line energy all the time.                     |  |

| 1                              | 0                                        | L+N Mode (applicable for single-phase three-wire system)     | energy                                                         |  |

| 1                              | 1                                        | Flexible Mode (line specified by the LNSel bit (MMode, 2BH)) | CFx represents energy of the specified line.                   |  |

The M90E26 has two current sampling circuits with different gain configurations. L line gain can be 1, 4, 8, 16 and 24, and N line gain can be 1, 2 and 4. The configuration is made by the MMode register (2BH). Generally L line can be sampled over shunt resistor or CT. N line can be sampled over CT for isolation consideration. Note that Rogowski coil is not supported.

#### 3.4.2 ANTI-TAMPERING MODE

#### Threshold

In anti-tampering mode, the power difference threshold between L line and N line can be: 1%, 2%,... 12%, 12.5%, 6.25%, 3.125% and 1.5625%, altogether 16 choices. The configuration is made by the Pthresh[3:0] bits (MMode, 2BH) and the default value is 3.125%. The threshold is applicable for active energy. The metering line of the reactive energy follows that of the active energy.

#### Compare Method

In anti-tampering mode, the compare method is as follows:

If current metering line is L line and

N line is switched as the metering line, otherwise L line keeps as the metering line.

If current metering line is N line and

L line is switched as the metering line, otherwise N line keeps as the metering line.

This method can achieve hysteresis around the threshold automatically. L line is employed after reset by default.

#### Special Treatment at Low Power

When power is low, general factors such as the quantization error or calibration difference between L line and N line might cause the power difference to be exceeded. To ensure L line and N line to start up normally, special treatment as follows is adopted:

The line with higher power is selected as the metering line when both L line and N line power are lower than 8 times of the startup power but higher than the startup power.

### 3.5 MEASUREMENT AND ZERO-CROSSING

#### 3.5.1 MEASUREMENT

The M90E26 has the following measurements:

- · voltage rms

- current rms (L line/N line)

- mean active power (L line/N line)

- mean reactive power (L line/N line)

- voltage frequency

- power factor (L line/N line)

- phase angle between voltage and current (L line/N line)

- mean apparent power (L line/N line)

The above measurements are all calculated with fiducial error except for frequency. The frequency accuracy is 0.01Hz, and the other measurement accuracy is 0.5%. Fiducial error is calculated as follow:

$$Fiducial\_E \, rror = \frac{U_{mea} - U_{real}}{U_{rv}} * 100\%$$

Where  $U_{mea}$  is the measured voltage,  $U_{real}$  is the actual voltage and  $U_{FV}$  is the fiducial value.

**Table-7 The Measurement Format**

| Measurement                              | Fiducial Value (FV)     | M90E26 Defined Format | Range                      | Comment                         |

|------------------------------------------|-------------------------|-----------------------|----------------------------|---------------------------------|

| Voltage rms                              | Un                      | XXX.XX                | 0~655.35V                  |                                 |

| Current rms <sup>note 1, note 2</sup>    | lmax<br>as 4lb          | XX.XXX                | 0~65.535A                  |                                 |

| Active/ Reactive Power <sup>note 1</sup> | maximum power as Un*4lb | XX.XXX                | -32.768~+32.767<br>kW/kvar | Complement, MSB as the sign bit |

| Apparent Power <sup>note 1</sup>         | Un*4lb                  | XX.XXX                | 0~+32.767 kVA              | Complement, MSB always '0'      |

| Frequency                                | fn                      | XX.XX                 | 45.00~65.00 Hz             |                                 |

| Power Factor <sup>note 3</sup>           | 1.000                   | X.XXX                 | -1.000~+1.000              | Signed, MSB as the sign bit     |

| Phase Angle <sup>note 4</sup>            | 180°                    | XXX.X                 | -180°~+180°                | Signed, MSB as the sign bit     |

**Note 1:** All registers are of 16 bits. For cases when the current and active/reactive/apparent power goes beyond the above range, it is suggested to be handled by microcontroller (MCU) in application. For example, register value can be calibrated to 1/2 of the actual value during calibration, then multiply 2 in application. Note that if the actual current is twice of that of the M90E26, the actual active/reactive/apparent power is also twice of that of the M90E26.

**Note 2:** The accuracy is not guaranteed when the current is lower than 15mA. Note that the tolerance is 25 mA at I<sub>FV</sub> of 5A and fiducial accuracy of 0.5%.

Note 3: Power factor is obtained by active power dividing apparent power

**Note 4:** Phase angle is obtained when voltage/current crosses zero at the frequency of 256kHz. Precision is not guaranteed at small current.

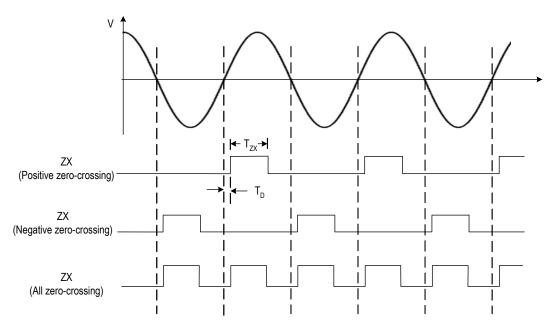

#### 3.5.2 ZERO-CROSSING

The ZX pin is asserted when the sampling voltage crosses zero. Zero-crossing mode can be configured to positive zero-crossing, negative zero-crossing and all zero-crossing by the Zxcon[1:0] bits (MMode, 2BH). Refer to section 6.4.

The zero-crossing signal can facilitate operations such as relay operation and power line carrier transmission in typical smart meter applications.

#### 3.6 CALIBRATION

Calibration includes metering and measurement calibration.

## **Metering Calibration**

The M90E26 design methodology guarantees the accuracy over the entire dynamic range, after metering calibration at one specific current, i.e. the basic current of I<sub>b</sub>.

The calibration procedure includes the following steps:

- 1. Calibrate gain at unity power factor;

- 2. Calibrate phase angle compensation at 0.5 inductive power factor.

Generally, line current sampling is susceptible to the circuits around the sensor when shunt resistor is employed as the current sensor in L line. For example, the transformer in the energy meter's power supply may conduct interference to the shunt resistor. Such interference will cause perceptible metering error, especially at low current conditions. The total interfere is at a statistically constant level. In this case, the M90E26 provides the power offset compensation feature to improve metering performance.

L line and N line need to be calibrated sequentially. Reactive energy does not need to be calibrated after active energy calibration completed.

#### Measurement Calibration

Measurement calibration includes gain calibration for voltage rms and current rms.

Considering the possible nonlinearity around zero caused by external components, the M90E26 also provides offset compensation for voltage rms, current rms, mean active power and mean reactive power.

The M90E26 design methodology guarantees automatic calibration for frequency, phase angle and power factor measurement.

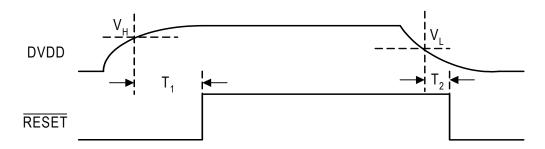

#### 3.7 RESET

The M90E26 has an on-chip power supply monitor circuit with built-in hysteresis. The M90E26 only works within the voltage range.

The M90E26 has three means of reset: power-on reset, hardware reset and software reset. All registers resume to their default value after reset.

Power-on Reset: Power-on reset is initiated during power-up. Refer to section 6.3.

Hardware Reset: Hardware Reset is initiated when the reset pin is pulled low. The width of the reset signal should be over 200µs.

Software Reset: Software Reset is initiated when '789AH' is written to the software reset register (SoftReset, 00H).

### 4 INTERFACE

The M90E26 supports both Serial Peripheral Interface (SPI) and UART interface. The selection is made by the USEL pin. When the USEL pin is low, SPI interface is selected. When the USEL pin is high, UART interface is selected. Note that the USEL pin should not change after reset.

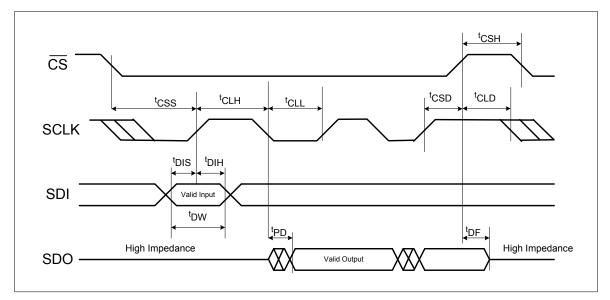

#### 4.1 SPI INTERFACE

SPI is a full-duplex, synchronous channel. There are two SPI modes: four-wire mode and three-wire mode. In four-wire mode, four pins are used:  $\overline{CS}$ , SCLK, SDI and SDO. In three-wire mode, three pins are used: SCLK, SDI and SDO. Data on SDI is shifted into the chip on the rising edge of SCLK while data on SDO is shifted out of the chip on the falling edge of SCLK. The LastData register (06H) stores the 16-bit data that is just read or written.

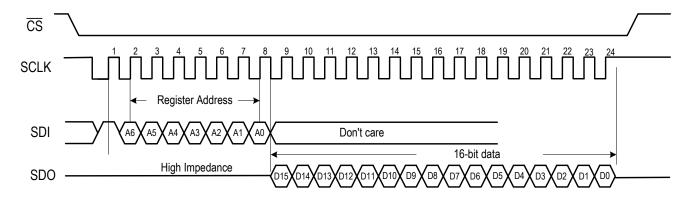

#### 4.1.1 FOUR-WIRE MODE

In four-wire mode, the  $\overline{\text{CS}}$  pin must be driven low for the entire read or write operation. The first bit on SDI defines the access type and the lower 7-bit is decoded as address.

#### Read Sequence

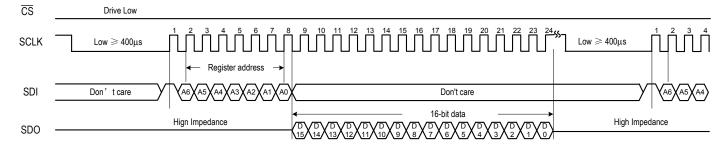

As shown in Figure-3, a read operation is initiated by a high on SDI followed by a 7-bit register address. A 16-bit data in this register is then shifted out of the chip on SDO. A complete read operation contains 24 cycles.

Figure-3 Read Sequence in Four-Wire Mode

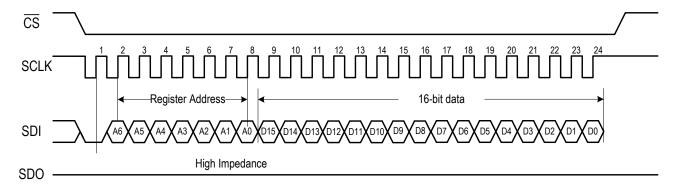

#### Write Sequence

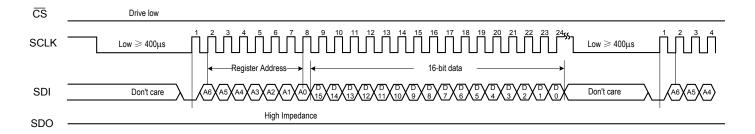

As shown in Figure-4, a write operation is initiated by a low on SDI followed by a 7-bit register address. A 16-bit data is then shifted into the chip on SDI. A complete write operation contains 24 cycles.

Figure-4 Write Sequence in Four-Wire Mode

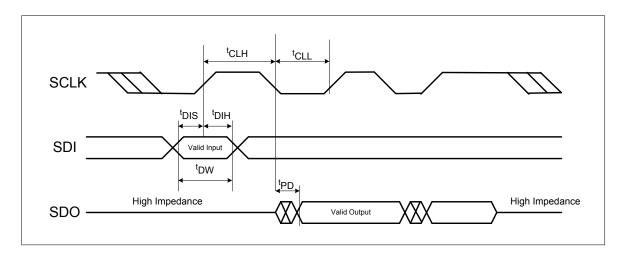

#### 4.1.2 THREE-WIRE MODE

In three-wire mode,  $\overline{\text{CS}}$  is always at low level. When there is no operation, SCLK keeps at high level. The start of a read or write operation is triggered if SCLK is consistently low for at least 400 $\mu$ s. The subsequent read or write operation is similar to that in four-wire mode. Refer to Figure-5 and Figure-6.

Figure-5 Read Sequence in Three-Wire Mode

Figure-6 Write Sequence in Three-Wire Mode

#### 4.1.3 TIMEOUT AND PROTECTION

Timeout occurs if SCLK does not toggle for 6ms in both four-wire and three-wire modes. When timeout, the read or write operation is aborted.

If there are more than 24 SCLK cycles when  $\overline{\text{CS}}$  is driven low in four-wire mode or between two starts in three-wire mode, writing operation is prohibited while normal reading operation can be completed by taking the first 24 SCLK cycles as the valid ones. However, the reading result might not be the intended one.

A read access to an invalid address returns all zero. A write access to an invalid address is discarded.

Table-8 and Table-9 list the read or write result in different conditions.

Table-8 Read / Write Result in Four-Wire Mode

|           | Condition |                               | Result               |                             |  |

|-----------|-----------|-------------------------------|----------------------|-----------------------------|--|

| Operation | Timeout   | SCLK Cycles <sup>note 1</sup> | Read/Write<br>Status | LastData<br>Register Update |  |

|           | note 2    | >=24                          | Normal Read          | Yes                         |  |

| Read      | note 2    | <24                           | Partial Read         | No                          |  |

|           | No        | =24                           | Normal Write         | Yes                         |  |

|           | No        | !=24                          | No Write             | No                          |  |

| Write     | Yes       | -                             | No Write             | No                          |  |

**Note 1:** The number of SCLK cycles when  $\overline{CS}$  is driven low or the number of SCLK cycles before timeout if any.

Note 2: '-' stands for Don't Care.

Table-9 Read / Write Result in Three-Wire Mode

|           | Condition                |                               | Result            |                             |  |  |

|-----------|--------------------------|-------------------------------|-------------------|-----------------------------|--|--|

| Operation | Timeout                  | SCLK Cycles <sup>note 1</sup> | Read/Write Status | LastData<br>Register Update |  |  |

|           | No                       | >=24 <sup>note 2</sup>        | Normal Read       | Yes                         |  |  |

|           | Timeout after 24 cycles  | >24                           | Normal Read       | Yes                         |  |  |

|           | Timeout before 24 cycles | _note 3                       | Partial Read      | No                          |  |  |

| Read      | Timeout at 24 cycles     | =24                           | Normal Read       | Yes                         |  |  |

|           | No                       | =24                           | Normal Write      | Yes                         |  |  |

|           | No                       | !=24                          | No Write          | No                          |  |  |

| Write     | Yes                      | -                             | No Write          | No                          |  |  |

**Note 1:** The number of SCLK cycles between 2 starts or the number of SCLK cycles before timeout if any.

**Note 2:** There is no such case of less than 24 SCLK cycles when there is no timeout in three-wire mode, because the first few SCLK cycles in the next operation is counted into this operation. In this case, data is corrupted.

Note 3: '-' stands for Don't Care.

#### 4.2 UART INTERFACE

The UART interface is of 8-bit data only, with no parity checking features.

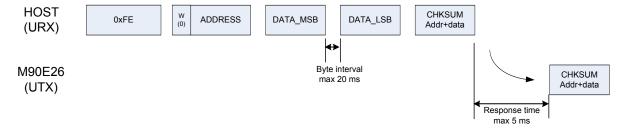

A read/write transaction is composed of 6 bytes' transfer, starting always from the host transmitting the first byte 'FEH'. The second byte is referenced as RW\_ADDRESS, which has a R/W bit (bit7) and 7 address bits (bit6-0).

Upon receiving commands from the host, the M90E26 will send data and/or checksum bytes back to the host within 5ms if the checksum is confirmed to be correct. Interval between successive UART bytes from the M90E26 is 5 bits maximum.

The M90E26 will time out the current transaction if the host byte interval (idling time between two successive bytes) is greater than 20ms. Once transaction timeout or checksum failure, the M90E26 will abort the current transaction and wait for the starting byte 'FEH' of the new transaction and ignore other data that received. The host needs to have a timeout scheme to detect transaction failure. In addition, host needs to wait at least 20ms to start a new transaction to allow the M90E26 to recover from a failure condition.

UART baud rate is determined by the host, and it can be auto-detected by the M90E26. The baud rates supported are 2400 and 9600. The first byte (FEH) is used in detecting the baud-rate. The baud-rate of a transaction shall be kept unchanged. For a new transaction, host may change the baud rate. However, it is suggested that boad rate remain the same in application.

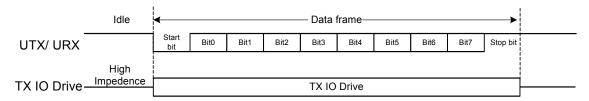

The 8-bit data in TX/RX pin is shifted in a LSB (bit0) first manner.

#### 4.2.1 BYTE LEVEL TIMING

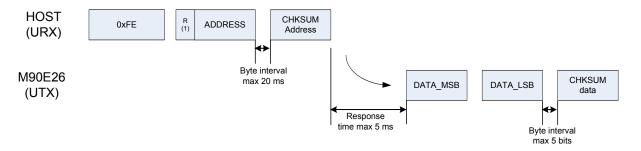

The timing for each byte is as shown in Figure-7.

Note: The UTX pin will be in high impedance state when not transmitting

Figure-7 UART Byte Level Timing

#### 4.2.2 WRITE TRANSACTION

A complete write transaction is composed of six bytes, five from the host and one from the M90E26 as shown in Figure-8.

Figure-8 Write Transaction

#### 4.2.3 READ TRANSACTION

A complete read transaction is composed of six bytes, three from the host and three from the M90E26 as shown in Figure-9.

Figure-9 Read Transaction

#### 4.2.4 CHECKSUM

Checksum is done by adding the bytes as unsigned numbers, dropping the overflow bits, and taking the result as the checksum.

Checksum is calculated with address, data or address+data, depending on the transaction type:

#### Write Transaction:

Host Checksum = RW\_Address+DATA\_MSB+DATA\_LSB M90E26 Checksum = RW\_Address+DATA\_MSB+DATA\_LSB

# Read Transaction:

Host Checksum = RW\_Address M90E26 Checksum = DATA\_MSB + DATA\_LSB

#### 4.3 WARNOUT PIN FOR FATAL ERROR WARNING

Fatal error warning is raised through the WarnOut pin in two cases: checksum calibration error and voltage sag.

#### Calibration Error

The M90E26 performs diagnosis on a regular basis for important parameters such as calibration parameters and metering configuration. When checksum is not correct, the CalErr[1:0] bits (SysStatus, 01H) are set, and both the WarnOut pin and the IRQ pin are asserted. When checksum is not correct, the metering part does not work to prevent a large number of pulses during power-on or any abnormal situation upon incorrect parameters.

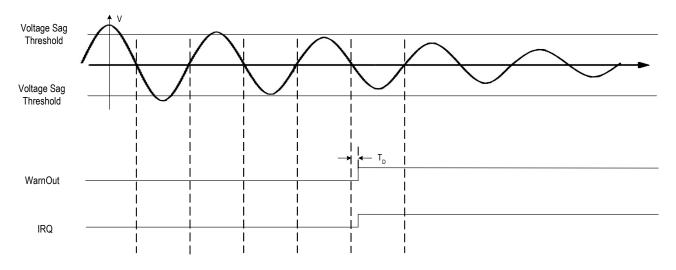

#### Voltage Sag

Voltage sag is detected when voltage is continuously below the voltage sag threshold for one cycle which starts from any zero-crossing point. Voltage threshold is configured by the SagTh register (03H). Refer to section 6.5.

When voltage sag occurs, the SagWarn bit (SysStatus, 01H) is set and the WarnOut pin is asserted if the FuncEn register (02H) enables voltage sag warning through the WarnOut pin. This function helps reduce power-down detection circuit in system design. In addition, the method of judging voltage sag by detecting AC side voltage eliminates the influence of large capacitor in traditional rectifier circuit, and can detect voltage sag earlier.

#### 4.4 LOW COST IMPLEMENTATION IN ISOLATION WITH MCU

The following functions can be achieved at low cost when the M90E26 is isolated from the MCU:

SPI/UART: MCU can perform read and write operations through low speed optocoupler (e.g. PS2501) when the M90E26 is isolated from the MCU. For the SPI interface, it can be either of 3-wire or 4-wire.

Energy Pulses CFx: Energy can be accumulated by reading values in corresponding energy registers. CFx can also connect to the optocoupler and the energy pulse light can be turned on by CFx.

Fatal Error WarnOut: Fatal error can be acquired by reading the CalErr[1:0] bits (SysStatus, 01H).

IRQ: IRQ interrupt can be acquired by reading the SysStatus register (01H).

Reset: The M90E26 is reset when '789AH' is written to the software reset register (SoftReset, 00H).

# 5 REGISTER

# 5.1 REGISTER LIST

Table-10 Register List

| Register<br>Address | Register Name | Read/Write<br>Type     | Functional Description                | Page |

|---------------------|---------------|------------------------|---------------------------------------|------|

| •                   |               | Status and S           | pecial Register                       | •    |

| 00H                 | SoftReset     | W                      | Software Reset                        | P 22 |

| 01H                 | SysStatus     | R/C                    | System Status                         | P 23 |

| 02H                 | FuncEn        | R/W                    | Function Enable                       | P 24 |

| 03H                 | SagTh         | R/W                    | Voltage Sag Threshold                 | P 24 |

| 04H                 | SmallPMod     | R/W                    | Small-Power Mode                      | P 25 |

| 06H                 | LastData      | R                      | Last Read/Write SPI/UART Value        | P 25 |

| <u>'</u>            | Me            | etering Calibration an | nd Configuration Register             | l .  |

| H80                 | LSB           | R/W                    | RMS/Power 16-bit LSB                  | P 26 |

| 20H                 | CalStart      | R/W                    | Calibration Start Command             | P 26 |

| 21H                 | PLconstH      | R/W                    | High Word of PL_Constant              | P 27 |

| 22H                 | PLconstL      | R/W                    | Low Word of PL_Constant               | P 27 |

| 23H                 | Lgain         | R/W                    | L Line Calibration Gain               | P 28 |

| 24H                 | Lphi          | R/W                    | L Line Calibration Angle              | P 28 |

| 25H                 | Ngain         | R/W                    | N Line Calibration Gain               | P 28 |

| 26H                 | Nphi          | R/W                    | N Line Calibration Angle              | P 29 |

| 27H                 | PStartTh      | R/W                    | Active Startup Power Threshold        | P 29 |

| 28H                 | PNolTh        | R/W                    | Active No-Load Power Threshold        | P 29 |

| 29H                 | QStartTh      | R/W                    | Reactive Startup Power Threshold      | P 30 |

| 2AH                 | QNolTh        | R/W                    | Reactive No-Load Power Threshold      | P 30 |

| 2BH                 | MMode         | R/W                    | Metering Mode Configuration           | P 31 |

| 2CH                 | CS1           | R/W                    | Checksum 1                            | P 33 |

| <u> </u>            |               | Measurement Ca         | alibration Register                   | L    |

| 30H                 | AdjStart      | R/W                    | Measurement Calibration Start Command | P 34 |

| 31H                 | Ugain         | R/W                    | Voltage rms Gain                      | P 34 |

| 32H                 | IgainL        | R/W                    | L Line Current rms Gain               | P 35 |

| 33H                 | IgainN        | R/W                    | N Line Current rms Gain               | P 35 |

| 34H                 | Uoffset       | R/W                    | Voltage Offset                        | P 35 |

| 35H                 | loffsetL      | R/W                    | L Line Current Offset                 | P 36 |

| 36H                 | IoffsetN      | R/W                    | N Line Current Offset                 | P 36 |

| 37H                 | PoffsetL      | R/W                    | L Line Active Power Offset            | P 36 |

| 38H                 | QoffsetL      | R/W                    | L Line Reactive Power Offset          | P 37 |

| 39H                 | PoffsetN      | R/W                    | N Line Active Power Offset            | P 37 |

| 3AH                 | QoffsetN      | R/W                    | N Line Reactive Power Offset          | P 37 |

| 3BH                 | CS2           | R/W                    | Checksum 2                            | P 38 |

|                     |               | Energy                 | Register                              | ı    |

| 40H                 | APenergy      | R/C                    | Forward Active Energy                 | P 39 |

| 41H                 | ANenergy      | R/C                    | Reverse Active Energy                 | P 40 |

| 42H                 | ATenergy      | R/C                    | Absolute Active Energy                | P 40 |

| 43H                 | RPenergy      | R/C                    | Forward (Inductive) Reactive Energy   | P 41 |

Table-10 Register List (Continued)

| Register<br>Address | Register Name | Read/Write<br>Type | Functional Description                         | Page |

|---------------------|---------------|--------------------|------------------------------------------------|------|

| 44H                 | RNenergy      | R/C                | Reverse (Capacitive) Reactive Energy           | P 41 |

| 45H                 | RTenergy      | R/C                | Absolute Reactive Energy                       | P 42 |

| 46H                 | EnStatus      | R                  | Metering Status                                | P 43 |

| 1                   |               | Measure            | ment Register                                  | 1    |

| 48H                 | Irms          | R                  | L Line Current rms                             | P 44 |

| 49H Urms            |               | R                  | Voltage rms                                    | P 44 |

| 4AH                 | Pmean         | R                  | L Line Mean Active Power                       | P 45 |

| 4BH                 | Qmean         | R                  | L Line Mean Reactive Power                     | P 45 |

| 4CH                 | Freq          | R                  | Voltage Frequency                              | P 46 |

| 4DH                 | PowerF        | R                  | L Line Power Factor                            | P 46 |

| 4EH                 | Pangle        | R                  | Phase Angle between Voltage and L Line Current | P 47 |

| 4FH                 | Smean         | R                  | L Line Mean Apparent Power                     | P 47 |

| 68H                 | Irms2         | R                  | N Line Current rms                             | P 48 |

| 6AH                 | Pmean2        | R                  | N Line Mean Active Power                       | P 48 |

| 6BH                 | Qmean2        | R                  | N Line Mean Reactive Power                     | P 49 |

| 6DH                 | PowerF2       | R                  | N Line Power Factor                            | P 49 |

| 6EH                 | Pangle2       | R                  | Phase Angle between Voltage and N Line Current | P 50 |

| 6FH                 | Smean2        | R                  | N Line Mean Apparent Power                     | P 50 |

# 5.2 STATUS AND SPECIAL REGISTER

#### SoftReset Software Reset

Address: 00H Type: Write Default Value: 0000H 15 14 13 12 10 9 8 11 SoftReset15 SoftReset14 SoftReset13 SoftReset12 SoftReset11 SoftReset10 SoftReset9 SoftReset8 3 2 6 5 4 1 0 SoftReset7 SoftReset6 SoftReset5 SoftReset4 SoftReset3 SoftReset2 SoftReset1 SoftReset0 Bit Description Name 15 - 0 SoftReset[15:0] Software reset register. The M90E26 resets if only 789AH is written to this register.

# SysStatus System Status

| Address: 01F<br>Type: Read/C<br>Default Value                                                                                                                                                                                                         | Clear       |                                                                                                                                                          |                                                                                                                                                                                                                                   |                      |        |                  |   |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------|------------------|---|--|--|

| 15                                                                                                                                                                                                                                                    | 14          | 13                                                                                                                                                       | 12                                                                                                                                                                                                                                | 11                   | 10     | 9                | 8 |  |  |

| CalErr1                                                                                                                                                                                                                                               | CalErr      | 0 AdjErr1                                                                                                                                                | AdjErr0                                                                                                                                                                                                                           | -                    | -      | -                | - |  |  |

| 7                                                                                                                                                                                                                                                     | 6           | 5                                                                                                                                                        | 4                                                                                                                                                                                                                                 | 3                    | 2      | 1                | 0 |  |  |

| LNchang                                                                                                                                                                                                                                               | e RevQch    | ng RevPchg                                                                                                                                               | -                                                                                                                                                                                                                                 | -                    | -      | SagWarn          | - |  |  |

| Bit                                                                                                                                                                                                                                                   | Name        |                                                                                                                                                          |                                                                                                                                                                                                                                   | Descri               | iption |                  | _ |  |  |

| 15 - 14                                                                                                                                                                                                                                               | CalErr[1:0] | These bits indicate CS1 checksum status. 00: CS1 checksum correct (default) 11: CS1 checksum error. At the same time, the WarnOut pin is asserted.       |                                                                                                                                                                                                                                   |                      |        |                  |   |  |  |

| 13 - 12                                                                                                                                                                                                                                               | AdjErr[1:0] | These bits indicate 00: CS2 checksum 11: CS2 checksum                                                                                                    | correct (default)                                                                                                                                                                                                                 | tatus.               |        |                  |   |  |  |

| 11 - 8                                                                                                                                                                                                                                                | -           | Reserved.                                                                                                                                                |                                                                                                                                                                                                                                   |                      |        |                  |   |  |  |

| 7                                                                                                                                                                                                                                                     | LNchange    | This bit indicates whether there is any change of the metering line (L line and N line).  0: metering line no change (default)  1: metering line changed |                                                                                                                                                                                                                                   |                      |        |                  |   |  |  |

| 6                                                                                                                                                                                                                                                     | RevQchq     | This bit indicates w<br>0: direction of react<br>1: direction of react<br>This status is enab                                                            | ive energy no cha<br>ive energy chang                                                                                                                                                                                             | ange (default)<br>ed |        | active energy.   |   |  |  |

| 5                                                                                                                                                                                                                                                     | RevPchg     | 0: direction of active 1: direction of active                                                                                                            | his bit indicates whether there is any change with the direction of active energy.  : direction of active energy no change (default)  : direction of active energy changed his status is enabled by the RevPEn bit (FuncEn, 02H). |                      |        |                  |   |  |  |

| 4 - 2                                                                                                                                                                                                                                                 | -           | Reserved.                                                                                                                                                |                                                                                                                                                                                                                                   |                      |        |                  |   |  |  |

| This bit indicates the voltage sag status. 0: no voltage sag (default) 1: voltage sag Voltage sag is enabled by the SagEn bit (FuncEn, 02H). Voltage sag status can also be reported by the WarnOut pin. It is enabled by the SagWo bit(FuncEn, 02H). |             |                                                                                                                                                          |                                                                                                                                                                                                                                   |                      |        | agWo bit(FuncEn, |   |  |  |

| 0                                                                                                                                                                                                                                                     | -           | Reserved.                                                                                                                                                |                                                                                                                                                                                                                                   |                      |        |                  |   |  |  |

|                                                                                                                                                                                                                                                       |             | •                                                                                                                                                        |                                                                                                                                                                                                                                   |                      |        |                  |   |  |  |

**Note:** Any of the above events will prompt the IRQ pin to be asserted, which can be supplied to external MCU as an interrupt.

# FuncEn Function Enable

| Address: 02H<br>Type: Read/W<br>Default Value: | /rite                |                                                                                                                           |                  |                    |                   |                 |   |  |  |  |

|------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|-------------------|-----------------|---|--|--|--|

| 15                                             | 14                   | 13                                                                                                                        | 12               | 11                 | 10                | 9               | 8 |  |  |  |

| -                                              | -                    | -                                                                                                                         | -                | -                  | -                 | -               | - |  |  |  |

| 7                                              | 6                    | 5                                                                                                                         | 4                | 3                  | 2                 | 1               | 0 |  |  |  |

| -                                              | -                    | SagEn                                                                                                                     | SagWo            | RevQEn             | RevPEn            | -               | - |  |  |  |

| Bit                                            | Bit Name Description |                                                                                                                           |                  |                    |                   |                 |   |  |  |  |

| 15 - 6                                         | -                    | Reserved.                                                                                                                 |                  |                    | -                 |                 |   |  |  |  |

| 5                                              | SagEn                | This bit determines v<br>0: disable (default)<br>1: enable                                                                | vhether to enabl | e the voltage sag  | interrupt.        |                 |   |  |  |  |

| 4                                              | SagWo                | This bit determines v<br>0: disable (default)<br>1: enable                                                                | vhether to enabl | e voltage sag to l | be reported by th | ne WarnOut pin. |   |  |  |  |

| 3                                              | RevQEn               | This bit determines whether to enable the direction change interrupt of reactive energy.  0: disable  1: enable (default) |                  |                    |                   |                 |   |  |  |  |

| 2                                              | RevPEn               | This bit determines v<br>0: disable<br>1: enable (default)                                                                |                  |                    |                   |                 |   |  |  |  |

| 1 - 0                                          | -                    | Reserved.                                                                                                                 |                  |                    |                   |                 |   |  |  |  |

# SagTh Voltage Sag Threshold

| voitage Sa                                    | ,           |                    |                                                                                                                                                                                                                             |         |         |        |        |  |

|-----------------------------------------------|-------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|--------|--------|--|

| Address: 03ł<br>Type: Read/\<br>Default Value | Vrite       |                    |                                                                                                                                                                                                                             |         |         |        |        |  |

| 15                                            | 14          | 13                 | 12                                                                                                                                                                                                                          | 11      | 10      | 9      | 8      |  |

| SagTh1                                        | 5 SagTh1    | 4 SagTh13          | SagTh12                                                                                                                                                                                                                     | SagTh11 | SagTh10 | SagTh9 | SagTh8 |  |

| 7                                             | 6           | 5                  | 4                                                                                                                                                                                                                           | 3       | 2       | 1      | 0      |  |

| SagTh                                         | 7 SagTh     | 6 SagTh5           | SagTh4                                                                                                                                                                                                                      | SagTh3  | SagTh2  | SagTh1 | SagTh0 |  |

| '-                                            |             |                    |                                                                                                                                                                                                                             |         |         |        |        |  |

| Bit                                           | Name        |                    |                                                                                                                                                                                                                             | Descri  | ption   |        |        |  |

| 15 - 0                                        | SagTh[15:0] | The power-on value | Voltage sag threshold configuration. Data format is XXX.XX. Unit is V. The power-on value of SagTh is 1D6AH, which is calculated by 22000*sqrt(2)*0.78/(4*Ugai For details, please refer to related application note 46102. |         |         |        |        |  |

# Small-Power Mode

| Ac | dress: 0          | 4H      |            |                               |                                                      |                                                               |              |                   |            |                      |  |

|----|-------------------|---------|------------|-------------------------------|------------------------------------------------------|---------------------------------------------------------------|--------------|-------------------|------------|----------------------|--|

| _  | pe: Read          |         |            |                               |                                                      |                                                               |              |                   |            |                      |  |

| De | fault Val         | ue: 000 | )0H        |                               |                                                      |                                                               |              |                   |            |                      |  |

|    | 15                |         | 14         |                               | 13                                                   | 12                                                            | 11           | 10                | 9          | 8                    |  |

|    | SmallPl           | Mod1    | SmallPMo   | od1                           | SmallPMod1                                           | SmallPMod1                                                    | SmallPMod1   | SmallPMod1        |            |                      |  |

|    | 5                 |         | 4          |                               | 3                                                    | 2                                                             | 1            | 0                 | SmallPMod9 | SmallPMod8           |  |

|    | 7                 |         | 6          |                               | 5                                                    | 4                                                             | 3            | 2                 | 1          | 0                    |  |

|    | SmallP            | Mod7    | SmallPMo   | od6                           | SmallPMod5                                           | SmallPMod4                                                    | SmallPMod3   | SmallPMod2        | SmallPMod1 | SmallPMod0           |  |

|    | Bit               | N       | lame       |                               | Description                                          |                                                               |              |                   |            |                      |  |

|    | 15 - 0 SmallPMod[ |         | PMod[15:0] | A987<br>powe<br>powe<br>Other | r in small-powe<br>r in normal mod<br>s: Normal mode | mode. The relati<br>r mode and norn<br>le = power in sm<br>e. | nal mode is: | *Igain*Ugain /(10 |            | line active/reactive |  |

# LastData Last Read/Write SPI/UART Value

| Ty | ddress: 0<br>/pe: Rea<br>efault Va | d     | 00H        |                                 |                     |                    |                   |                  |                      |  |

|----|------------------------------------|-------|------------|---------------------------------|---------------------|--------------------|-------------------|------------------|----------------------|--|

|    | 15 14                              |       | 13         | 12                              | 11                  | 10                 | 9                 | 8                |                      |  |

|    | LastData15 Last                    |       | LastData   | 14 LastData1                    | 3 LastData12        | LastData11         | LastData10        | LastData9        | LastData8            |  |

|    | 7                                  |       | 6          | 5                               | 4                   | 3                  | 2                 | 1                | 0                    |  |

|    | LastData7                          |       | LastData   | 6 LastData5                     | LastData4           | LastData3          | LastData2         | LastData1        | LastData0            |  |

|    |                                    |       |            |                                 |                     |                    |                   |                  |                      |  |

|    | Bit Name                           |       |            | Description                     |                     |                    |                   |                  |                      |  |

|    | 15 - 0                             | LastD | )ata[15:0] | This register stor and Table-9. | es the data that is | ust read or writte | en through the SI | PI/UART interfac | ce. Refer to Table-8 |  |

# 5.3 METERING/ MEASUREMENT CALIBRATION AND CONFIGURATION

## 5.3.1 METERING CALIBRATION AND CONFIGURATION REGISTER

## LSB RMS/Power 16-bit LSB

| Ту | ldress: 08H<br>pe: Read<br>efault Value:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                                                                                               |       |       |       |      |      |  |  |