#### Automotive 4-channel valve driver

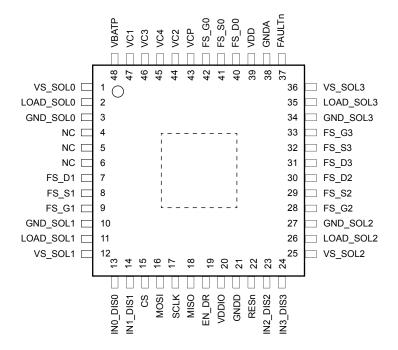

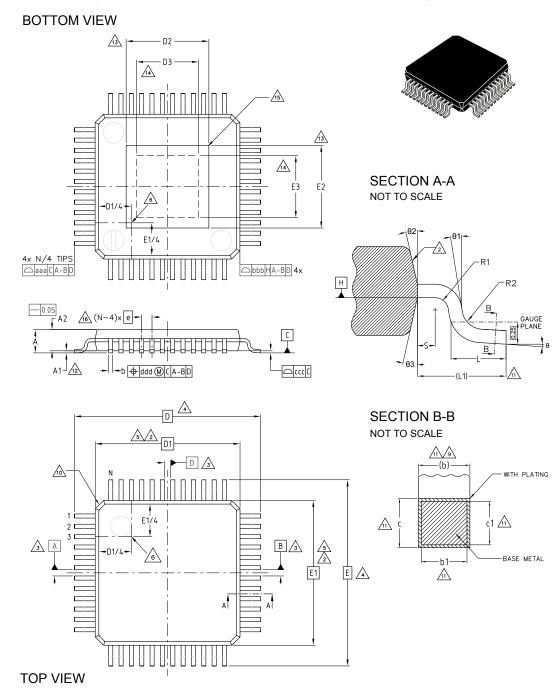

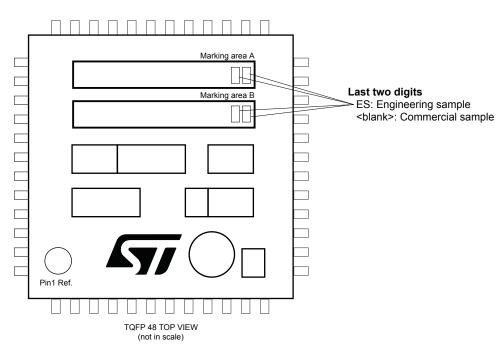

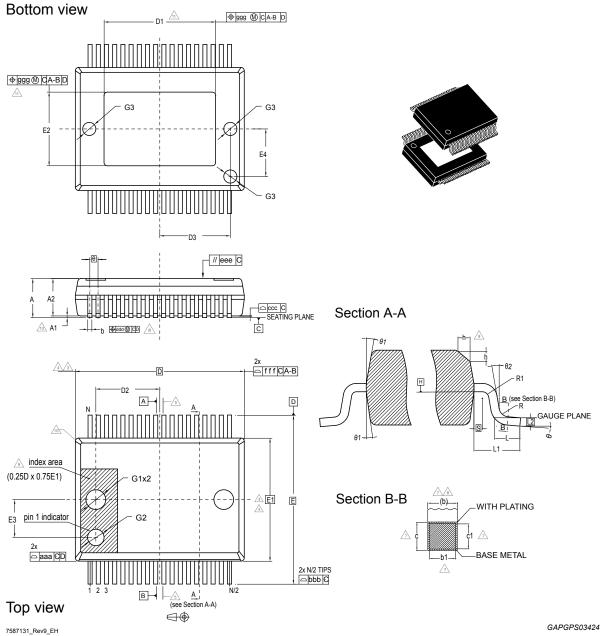

TQFP48 exposed pad down (7x7x1 mm)

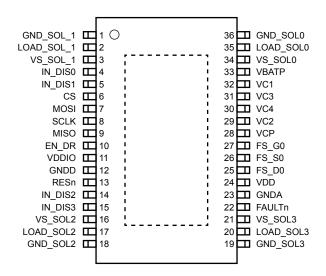

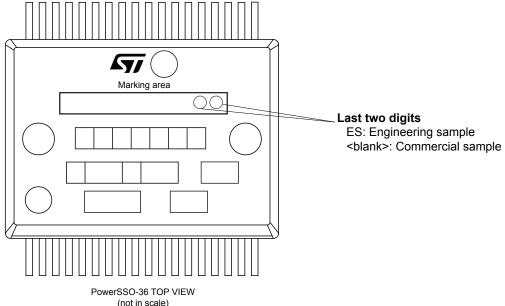

PowerSSO36 exposed pad down

# Product status link L9305

| Product summary |               |  |  |  |  |

|-----------------|---------------|--|--|--|--|

| Order code      | L9305EP       |  |  |  |  |

| Package         | PowerSSO36    |  |  |  |  |

| Packing         | Tube          |  |  |  |  |

| Order code      | L9305EP-TR    |  |  |  |  |

| Package         | PowerSSO36    |  |  |  |  |

| Packing         | Tape and reel |  |  |  |  |

| Order code      | L9305QFP      |  |  |  |  |

| Package         | TQFP48        |  |  |  |  |

| Packing         | Tray          |  |  |  |  |

| Order code      | L9305QFP-TR   |  |  |  |  |

| Package         | TQFP48        |  |  |  |  |

| Packing         | Tape and reel |  |  |  |  |

#### **Features**

- 4-channel independent LSD/HSD current controlled drivers

- Integrated current sense path

- Current accuracy (in normal range)

- ± 5 mA in 0 to 0.5 A range

- ± 1% in 0.5 A to 1.5 A range

- Current accuracy (in extended range)

- ± 15 mA in 0 to 0.3 A range

- ± 5% in 0.3 A to 0.5 A range

- ± 4% in 0.5 A to 2 A range

- Max driver  $R_{DSON}\,375~m\Omega$  @ 175  $^{\circ}C$

- 13-bit current set-point resolution

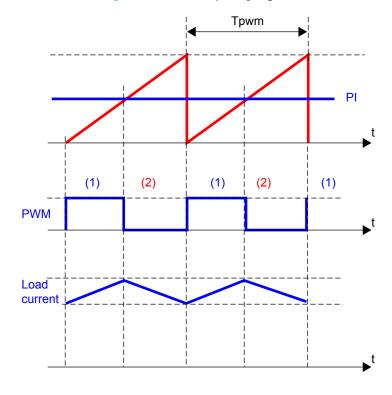

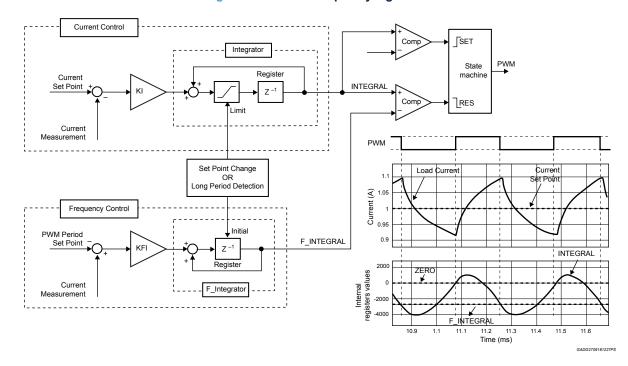

- Variable and fixed frequency current control

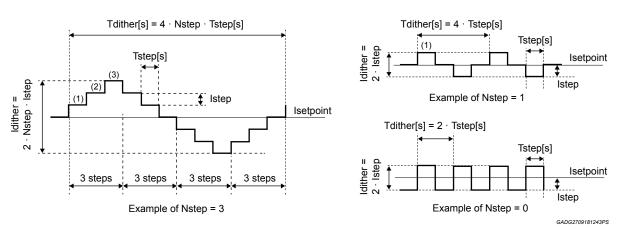

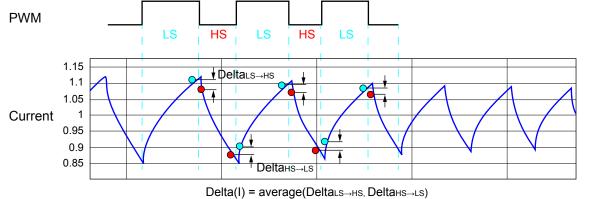

- Programmable dither function

- Selectable driver slew rate control

- Safety features

- High side fail safe ENABLE switch pre-driver with VDS monitoring

- Redundant safe enable path

- Advanced diagnosis and monitoring using BIST

- Temperature sensor and monitoring

- Redundant current sensing for all channels

- Calibration & configuration memory including CRC

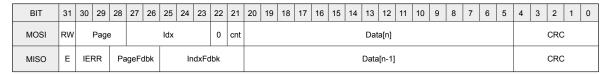

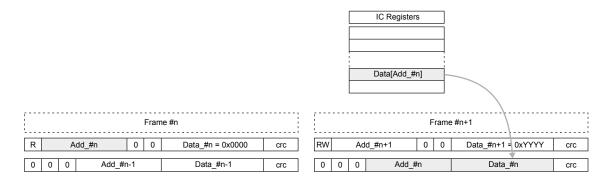

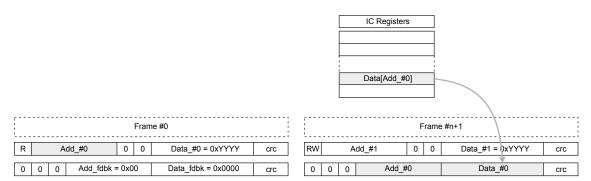

- Secure serial communications using address feedback, 5-bit CRC, frame counter & long/short frame detection

- Register verification

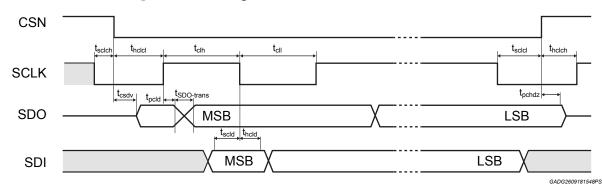

- 32-bit SPI communications with 5-bit CRC message verification

- Package options: PWSSO36, TQFP48

- Full ISO26262 compliant, ASIL-D systems ready

## **Description**

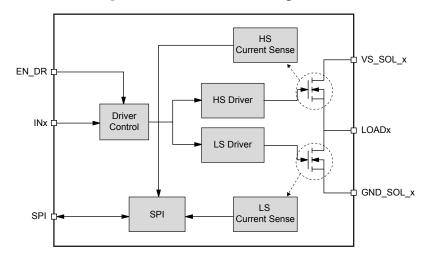

The L9305 is a configurable, monolithic solenoid driver IC designed for the control of linear solenoids for automatic transmission, electronic stability control, and active suspension applications. The four channels can be configured as either low side or high side drivers in any combination. The device includes the power transistor, recirculation transistor and current sensing for both the power and recirculation transistor. This architecture quarantees redundancy of the current measurement for each channel.

The regulated current is programmable in the range of 0-1.5 A (normal range), with a resolution of 0.25 mA, or 0-2 A (extended range), with a resolution of 0.33 mA. The user can superimpose configurable dither modulation over the set point current.

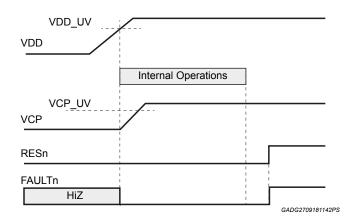

A 32-bit CRC protected SPI interface is used for configuration and control of all channels and provides status feedback of all diagnostic functions. An active low reset input, RESN, is used to disable all channels and resets internal registers to their default values. A safe enable path is provided through the EN\_DR pin and the integrated Fail Safe Pre-driver. An isolated redundant safety switch-off path ensures that critical internal faults disable the fail safe pre-driver. An active high enable pin, EN\_DR, is used to enable or disable the operation of all channels. When the EN\_DR pin is low, all channels are disabled. A fault output pin is provided and can be used to generate an external interrupt to the microcontroller whenever a fault is detected. The user can map specific faults to the FAULTn pin based on their specific system requirements.

DS12774 - Rev 10 page 2/107

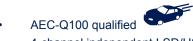

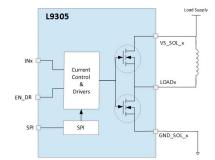

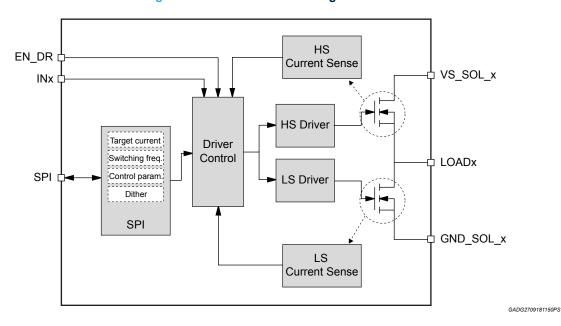

# **Block diagram**

Figure 1. Block diagram L9305

GADG2609181252PS

DS12774 - Rev 10 page 3/107

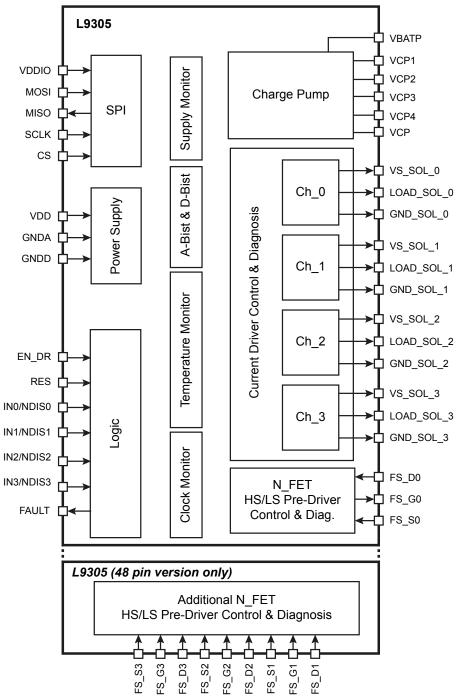

Figure 2. PWSSO36 application schematic

DS12774 - Rev 10 page 4/107

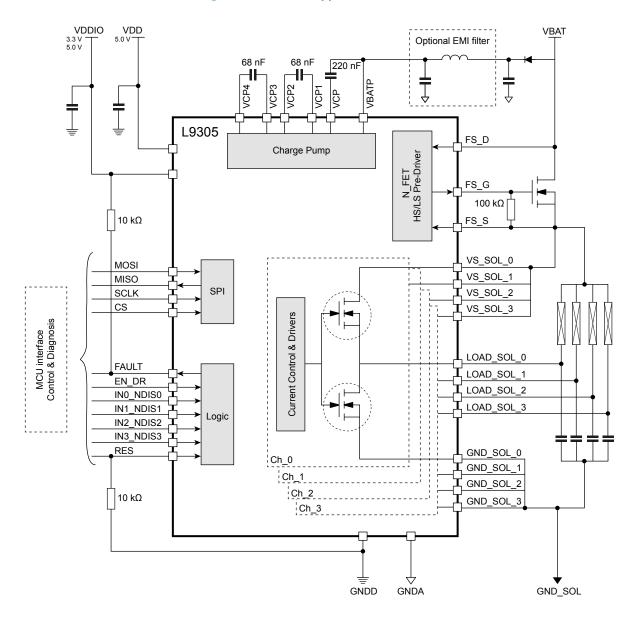

Figure 3. TQFP48 application schematic

DS12774 - Rev 10 page 5/107

# 2 Pins description

Figure 4. PowerSSO-36 pinout diagram

Figure 5. TQFP48 pinout diagram

DS12774 - Rev 10 page 6/107

Table 1. PowerSSO-36 and TQFP48 pins list

| 1 10 GND_SOL1 Channel 1 Ground: Ground connection for channel 1 power stage.  2 11 LOAD_SOL1 Channel 1 Output  3 12 VS_SOL1 Channel 1 Output  4 13 IN_DIS0 Parallel Input Channel 0: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode  5 14 IN_DIS1 Parallel Input Channel 0: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode  5 SPI Chip Select Input: SPI communication protocol Chip Select from MCU to the device. Digital logic level: 5.0V or 3.3V  7 16 MOSI SPI Chip Select Input: SPI communication protocol input from MCU to the device. Digital logic level: 5.0V or 3.3V  8 SPI Data Input: SPI communication protocol clock from MCU to the device. Digital logic level: 5.0V or 3.3V  9 18 MISO SPI Clock Input: SPI communication protocol clock from MCU to the device. Digital logic level: 5.0V or 3.3V  10 19 EN_DR Enable Driver:  10 SPI Data Output: SPI communication protocol output to MCU from the device. Digital logic level: 5.0V or 3.3V  11 20 VDDIO ID Spipit: To be connected to 5.0V or 3.3V  12 21 GNDD Digital Ground: Ground for digital circuits  13 22 RESIN Reset: when HIGH, device out of reset, when LOW, device in reset state  14 23 IN_DIS2 Parallel Input Channel 2: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode  15 24 IN_DIS3 Channel 2: Ground: Ground on the control from external MCU when in SW Mode; Disable channel command when in SW mode  16 25 VS_SOL2 Channel 2: Ground: Ground connection for channel 2 power stage.  17 26 LOAD_SOL2 Channel 3: Ground: Ground connection for channel 2 power stage.  18 27 GND_SOL3 Channel 3: Ground: Ground connection for channel 2 power stage.  19 34 GND_SOL3 Channel 3: Ground: Ground connection for channel 2 power stage.  20 35 LOAD_SOL3 Channel 3: Ground: Ground connection for channel 2 power stage.  21 36 VS_SOL3 Channel 3: Ground: Ground connection for channel 2 power stage.  22 37 FAULTIN Fault when LOW, Fault present, when HIGH, no | Pin number<br>PowerSSO-36 | Pin number<br>TQFP48 | Symbol    | Function                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------|-----------|---------------------------------------------------------------------------------------------|

| 12 VS_SOL1 13 IN_DISO 14 IS_DISO 15 Parallel Input Channel 0: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode 15 I4 IN_DISI 18 Parallel Input Channel 1: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode 16 I5 CS SPI Chip Select Input: SPI communication protocol Chip Select from MCU to the device. Digital logic level: 5.0V or 3.3V 16 MOSI SPI Data Input: SPI communication protocol input from MCU to the device. Digital logic level: 5.0V or 3.3V 17 SCLK SPI Clock Input: SPI communication protocol input from MCU to the device. Digital logic level: 5.0V or 3.3V 18 If SPI Data Input: SPI communication protocol input from MCU to the device. Digital logic level: 5.0V or 3.3V 19 I8 MISO SPI Data Output: SPI communication protocol output to MCU from the device. Digital logic level: 5.0V or 3.3V 10 I9 EN_DR Enable Driver: 111 20 VDDIO IO Supply: To be connected to 5.0V or 3.3V 112 21 GNDD Digital Ground: Ground for digital circuits 113 22 RESN Reset: when HIGH, device out of reset, when LOW, device in reset state Parallel Input Channel 2: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode 15 24 IN_DIS3 in SW Mode; Disable channel command when in SW mode 16 25 VS SOL2 Channel 2: Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode 17 26 LOAD_SOL2 Channel 2 Ground: Ground connection for channel 2 power stage. 18 27 GND_SOL3 Channel 3 Ground: Ground connection for channel 3 power stage. 19 34 GND_SOL3 Channel 3 Ground: Ground connection for channel 3 power stage. 20 35 LOAD_SOL3 Channel 3 Ground: Ground connection for channel 3 power stage. 21 37 FAULTN Fault: when LOW, Fault present, when HIGH, no fault present 22 37 FAULTN Fault: when LOW, Fault present, when HIGH, no fault present 23 38 GNDA Analog Ground: Ground connected to external FET Drain used as FS. VDS monitor 24 49 FS_DO Fail Safe Drain: to be connected to external FET Drain used as FS. | 1                         | 10                   | GND_SOL1  | Channel 1 Ground: Ground connection for channel 1 power stage.                              |

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2                         | 11                   | LOAD_SOL1 | Channel 1 Output                                                                            |

| 1 IN_DISU 2 IN_DISU 2 IN_DISU 3 IN_DISU 3 IN_DISU 3 IN_DISU 3 IN_DISU 4 IN_DISU 4 IN_DISU 5 IN_DISU 5 IN_DISU 6 IN_DISU 6 IN_DISU 6 IN_DISU 7 IS IN_DISU 7 IS IN_DISU 8 IN_DISU  | 3                         | 12                   | VS_SOL1   | , , ,                                                                                       |

| in SW Mode; Disable channel command when in SW mode  SPI Chip Select Input: SPI communication protocol Chip Select from MCU to the device. Digital logic level: 5.0V or 3.3V  SPI Data Input: SPI communication protocol Chip Select from MCU to the device. Digital logic level: 5.0V or 3.3V  SPI Clock Input: SPI communication protocol clock from MCU to the device. Digital logic level: 5.0V or 3.3V  SPI Data Output: SPI communication protocol clock from MCU to the device. Digital logic level: 5.0V or 3.3V  SPI Data Output: SPI communication protocol output to MCU from the device. Digital logic level: 5.0V or 3.3V  SPI Data Output: SPI communication protocol output to MCU from the device. Digital logic level: 5.0V or 3.3V  SPI Data Output: SPI communication protocol output to MCU from the device. Digital logic level: 5.0V or 3.3V  SPI Data Output: SPI communication protocol output to MCU from the device. Digital logic level: 5.0V or 3.3V  Digital logic level: 5.0V or 3.3V  SPI Data Output: SPI communication protocol output to MCU from the device. Digital logic level: 5.0V or 3.3V  SPI Data Output: SPI communication protocol output to MCU of the device. Digital logic level: 5.0V or 3.3V  Digital Spital output: SPI communication protocol output to MCU from the device. Digital logic level: 5.0V or 3.3V  SPI Data Output: SPI communication protocol loutput to MCU from the device. Digital logic level: 5.0V or 3.3V  SPI Data Output: SPI communication protocol loutput for Institute output in SPI device. Digital logic level: 5.0V or 3.3V  SPI Data Output: SPI communication protocol loutput for Institute output in SPI device. Digital logic level: 5.0V or 3.3V  SPI Data Output: SPI communication protocol loutput for Institute output in SPI device out of reserve protection diode  SPI Data Output: SPI communication protocol loutput for Institute output in SPI device out of SPI self-self-self-self-self-self-self-self-                                                                                                                     | 4                         | 13                   | IN_DIS0   |                                                                                             |

| MCU to the device. Digital logic level: 5.0V or 3.3V  7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5                         | 14                   | IN_DIS1   |                                                                                             |

| 8 17 SCLK SPI Clock Input: SPI communication protocol clock from MCU to the device. Digital logic level: 5.0V or 3.3V  9 18 MISO SPI Clock Input: SPI communication protocol clock from MCU to the device. Digital logic level: 5.0V or 3.3V  10 19 EN_DR Enable Driver:  11 20 VDDIO IO Supply: To be connected to 5.0V or 3.3V  12 21 GNDD Digital Ground: Ground for digital circuits  13 22 RESN Reset: when HIGH, device out of reset, when LOW, device in reset state  14 23 IN_DIS2 Input Channel 2: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode  15 VS_SOL2 Parallel Input Channel 3: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode  16 25 VS_SOL2 Channel 2 Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode  17 26 LOAD_SOL2 Channel 2 Output  18 27 GND_SOL2 Channel 2 Ground: Ground connection for channel 2 power stage.  19 34 GND_SOL3 Channel 3 Ground: Ground connection for channel 3 power stage.  20 35 LOAD_SOL3 Channel 3 Output  21 36 VS_SOL3 Channel 3 Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode  22 37 FAULTN Fault: when LOW, Fault present, when HIGH, no fault present  23 38 GNDA Analog Ground: Ground connection for channel 3 power stage.  24 39 VDD Supply Voltage: Supply Voltage: Connect to S.0V supply voltage  25 40 FS_DO Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor  26 41 FS_SO Fail Safe Source: to be connected to external FET Source used as FS. VDS monitor  27 42 FS_GO Fail Safe Gate: Gate command for external FET Drain used as FS. VDS Charge Pump Voltage: Connected to Protected Battery Voltage through External Capacitor                                                                                                                                                                                                                                                                                                                | 6                         | 15                   | CS        |                                                                                             |

| 9 18 MISO SPI Data Output: SPI communication protocol output to MCU from the device. Digital logic level: 5.0V or 3.3V  10 19 EN_DR Enable Driver: 11 20 VDDIO IO Supply: To be connected to 5.0V or 3.3V  12 21 GNDD Digital Ground: Ground for digital circuits 13 22 RESn Reset: when HIGH, device out of reset, when LOW, device in reset state 14 23 IN_DIS2 Parallel Input Channel 2: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode 15 24 IN_DIS3 Parallel Input Channel 3: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode 16 25 VS_SOL2 Channel 2 Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode 17 26 LOAD_SOL2 Channel 2 Ground: Ground connection for channel 2 power stage. 19 34 GND_SOL3 Channel 3 Ground: Ground connection for channel 3 power stage. 20 35 LOAD_SOL3 Channel 3 Ground: Ground connection for channel 3 power stage. 21 36 VS_SOL3 Channel 3 Output 21 36 VS_SOL3 Channel 3 Output 22 37 FAULTn Fault: When LOW, Fault present, when HIGH, no fault present 23 38 GNDA Analog Ground: Ground for analog circuits 24 39 VDD Supply Voltage: Supply for circuits. Connect to 5.0V supply voltage 25 40 FS_D0 Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor 26 41 FS_S0 Fail Safe Source: to be connected to external FET Drain used as FS. VDS monitor 27 42 FS_G0 Fail Safe Gate: Gate command for external FET Drain used as FS. Charnel 2 Channel 2 Channel 3 Channel 3 Channel 5 Channel 5 Channel 5 Channel 5 Channel 5 Channel 5 Channel 6 Channel 7 | 7                         | 16                   | MOSI      |                                                                                             |

| device. Digital logic level: 5.0V or 3.3V  10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8                         | 17                   | SCLK      |                                                                                             |

| 11 20 VDDIO IO Supply: To be connected to 5.0V or 3.3V  12 21 GNDD Digital Ground: Ground for digital circuits  13 22 RESn Reset: when HIGH, device out of reset, when LOW, device in reset state  14 23 IN_DIS2 Parallel Input Channel 2: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode  15 24 IN_DIS3 Parallel Input Channel 3: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode  16 25 VS_SOL2 Channel 2 Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode  17 26 LOAD_SOL2 Channel 2 Output  18 27 GND_SOL2 Channel 2 Ground: Ground connection for channel 2 power stage.  19 34 GND_SOL3 Channel 3 Ground: Ground connection for channel 3 power stage.  20 35 LOAD_SOL3 Channel 3 Output  21 36 VS_SOL3 Channel 3 Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode  22 37 FAULTn Fault: when LOW, Fault present, when HIGH, no fault present  23 38 GNDA Analog Ground: Ground for analog circuits  24 39 VDD Supply Voltage: Supply for circuits. Connect to 5.0V supply voltage  25 40 FS_D0 Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor  26 41 FS_S0 Fail Safe Source: to be connected to external FET Drain used as FS. VDS monitor  27 42 FS_G0 Fail Safe Gate: Gate command for external FET Drain used as FS.  28 43 VCP Charge Pump Voltage: Connected to Protected Battery Voltage through External Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9                         | 18                   | MISO      |                                                                                             |

| 12 21 GNDD Digital Ground: Ground for digital circuits  13 22 RESN Reset: when HIGH, device out of reset, when LOW, device in reset state  14 23 IN_DIS2 Parallel Input Channel 2: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode  15 24 IN_DIS3 Parallel Input Channel 3: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode  16 25 VS_SOL2 Channel 2 Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode  17 26 LOAD_SOL2 Channel 2 Output  18 27 GND_SOL2 Channel 2 Ground: Ground connection for channel 2 power stage.  19 34 GND_SOL3 Channel 3 Ground: Ground connection for channel 3 power stage.  20 35 LOAD_SOL3 Channel 3 Output  21 36 VS_SOL3 Channel 3 Output  22 37 FAULTN Fault: when LOW, Fault present, when HIGH, no fault present  23 38 GNDA Analog Ground: Ground for analog circuits  24 39 VDD Supply Voltage: Supply for circuits. Connect to 5.0V supply voltage  25 40 FS_D0 Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor  26 41 FS_S0 Fail Safe Source: to be connected to external FET Drain used as FS. VDS monitor  27 42 FS_G0 Fail Safe Gate: Gate command for external FET Drain used as FS. Charge Pump Voltage: Connected to Protected Battery Voltage through External Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10                        | 19                   | EN_DR     | Enable Driver:                                                                              |

| 13 22 RESn Reset: when HIGH, device out of reset, when LOW, device in reset state  14 23 IN_DIS2 Parallel Input Channel 2: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode  15 24 IN_DIS3 Parallel Input Channel 3: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode  16 25 VS_SOL2 Channel 2 Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode  17 26 LOAD_SOL2 Channel 2 Output  18 27 GND_SOL2 Channel 2 Ground: Ground connection for channel 2 power stage.  19 34 GND_SOL3 Channel 3 Ground: Ground connection for channel 3 power stage.  20 35 LOAD_SOL3 Channel 3 Output  21 36 VS_SOL3 Channel 3 Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode  22 37 FAULTn Fault: when LOW, Fault present, when HIGH, no fault present  23 38 GNDA Analog Ground: Ground for analog circuits  24 39 VDD Supply Voltage: Supply for circuits. Connect to 5.0V supply voltage  25 40 FS_DO Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor  26 41 FS_SO Fail Safe Gate: Gate command for external FET Drain used as FS. VDS monitor  27 42 FS_GO Fail Safe Gate: Gate command for external FET Drain used as FS. VDS monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11                        | 20                   | VDDIO     | IO Supply: To be connected to 5.0V or 3.3V                                                  |

| 14 23 IN_DIS2 Parallel Input Channel 2: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode  15 24 IN_DIS3 Parallel Input Channel 3: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode  16 25 VS_SOL2 Channel 2 Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode  17 26 LOAD_SOL2 Channel 2 Output  18 27 GND_SOL2 Channel 2 Ground: Ground connection for channel 2 power stage.  19 34 GND_SOL3 Channel 3 Ground: Ground connection for channel 3 power stage.  20 35 LOAD_SOL3 Channel 3 Output  21 36 VS_SOL3 Channel 3 Output  22 37 FAULTn Fault: when LOW, Fault present, when HIGH, no fault present  23 38 GNDA Analog Ground: Ground for analog circuits  24 39 VDD Supply Voltage: Supply for circuits. Connect to 5.0V supply voltage  25 40 FS_D0 Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor  26 41 FS_S0 Fail Safe Gate: Gate command for external FET Drain used as FS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12                        | 21                   | GNDD      | Digital Ground: Ground for digital circuits                                                 |

| IN_DIS2 in SW Mode; Disable channel command when in SW mode  15 24 IN_DIS3 Parallel Input Channel 3: Input for direct control from external MCU when in SW Mode; Disable channel command when in SW mode  16 25 VS_SOL2 Channel 2 Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode  17 26 LOAD_SOL2 Channel 2 Output  18 27 GND_SOL2 Channel 2 Ground: Ground connection for channel 2 power stage.  19 34 GND_SOL3 Channel 3 Ground: Ground connection for channel 3 power stage.  20 35 LOAD_SOL3 Channel 3 Output  21 36 VS_SOL3 Channel 3 Output  22 37 FAULTn Fault: when LOW, Fault present, when HIGH, no fault present  23 38 GNDA Analog Ground: Ground for analog circuits  24 39 VDD Supply Voltage: Supply for circuits. Connect to 5.0V supply voltage  25 40 FS_DO Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor  27 42 FS_GO Fail Safe Gate: Gate command for external FET Drain used as FS  28 43 VCP Charge Pump Voltage: Connected to Protected Battery Voltage through External Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13                        | 22                   | RESn      | Reset: when HIGH, device out of reset, when LOW, device in reset state                      |

| in SW Mode; Disable channel command when in SW mode  16 25 VS_SOL2 Channel 2 Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode  17 26 LOAD_SOL2 Channel 2 Output  18 27 GND_SOL2 Channel 2 Ground: Ground connection for channel 2 power stage.  19 34 GND_SOL3 Channel 3 Ground: Ground connection for channel 3 power stage.  20 35 LOAD_SOL3 Channel 3 Output  21 36 VS_SOL3 Channel 3 Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode  22 37 FAULTn Fault: when LOW, Fault present, when HIGH, no fault present  23 38 GNDA Analog Ground: Ground for analog circuits  24 39 VDD Supply Voltage: Supply for circuits. Connect to 5.0V supply voltage  25 40 FS_D0 Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor  26 41 FS_S0 Fail Safe Source: to be connected to external FET Drain used as FS. VDS monitor  27 42 FS_G0 Fail Safe Gate: Gate command for external FET Drain used as FS  Charge Pump Voltage: Connected to Protected Battery Voltage through External Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14                        | 23                   | IN_DIS2   |                                                                                             |

| reverse protection diode  17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15                        | 24                   | IN_DIS3   |                                                                                             |

| 18 27 GND_SOL2 Channel 2 Ground: Ground connection for channel 2 power stage.  19 34 GND_SOL3 Channel 3 Ground: Ground connection for channel 3 power stage.  20 35 LOAD_SOL3 Channel 3 Output  21 36 VS_SOL3 Channel 3 Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode  22 37 FAULTn Fault: when LOW, Fault present, when HIGH, no fault present  23 38 GNDA Analog Ground: Ground for analog circuits  24 39 VDD Supply Voltage: Supply for circuits. Connect to 5.0V supply voltage  25 40 FS_DO Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor  26 41 FS_SO Fail Safe Source: to be connected to external FET Drain used as FS.  27 42 FS_GO Fail Safe Gate: Gate command for external FET Drain used as FS  28 43 VCP Charge Pump Voltage: Connected to Protected Battery Voltage through External Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16                        | 25                   | VS_SOL2   | Channel 2 Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode |

| 19 34 GND_SOL3 Channel 3 Ground: Ground connection for channel 3 power stage. 20 35 LOAD_SOL3 Channel 3 Output  21 36 VS_SOL3 Channel 3 Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode  22 37 FAULTn Fault: when LOW, Fault present, when HIGH, no fault present  23 38 GNDA Analog Ground: Ground for analog circuits  24 39 VDD Supply Voltage: Supply for circuits. Connect to 5.0V supply voltage  25 40 FS_D0 Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor  26 41 FS_S0 Fail Safe Source: to be connected to external FET Source used as FS. VDS monitor  27 42 FS_G0 Fail Safe Gate: Gate command for external FET Drain used as FS  28 43 VCP Charge Pump Voltage: Connected to Protected Battery Voltage through External Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17                        | 26                   | LOAD_SOL2 | Channel 2 Output                                                                            |

| 20 35 LOAD_SOL3 Channel 3 Output  21 36 VS_SOL3 Channel 3 Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode  22 37 FAULTn Fault: when LOW, Fault present, when HIGH, no fault present  23 38 GNDA Analog Ground: Ground for analog circuits  24 39 VDD Supply Voltage: Supply for circuits. Connect to 5.0V supply voltage  25 40 FS_D0 Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor  26 41 FS_S0 Fail Safe Source: to be connected to external FET Source used as FS. VDS monitor  27 42 FS_G0 Fail Safe Gate: Gate command for external FET Drain used as FS  28 43 VCP Charge Pump Voltage: Connected to Protected Battery Voltage through External Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18                        | 27                   | GND_SOL2  | Channel 2 Ground: Ground connection for channel 2 power stage.                              |

| 21 36 VS_SOL3 Channel 3 Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode  22 37 FAULTn Fault: when LOW, Fault present, when HIGH, no fault present  23 38 GNDA Analog Ground: Ground for analog circuits  24 39 VDD Supply Voltage: Supply for circuits. Connect to 5.0V supply voltage  25 40 FS_D0 Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor  26 41 FS_S0 Fail Safe Source: to be connected to external FET Source used as FS. VDS monitor  27 42 FS_G0 Fail Safe Gate: Gate command for external FET Drain used as FS  28 43 VCP Charge Pump Voltage: Connected to Protected Battery Voltage through External Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19                        | 34                   | GND_SOL3  | Channel 3 Ground: Ground connection for channel 3 power stage.                              |

| reverse protection diode  22 37 FAULTn Fault: when LOW, Fault present, when HIGH, no fault present  23 38 GNDA Analog Ground: Ground for analog circuits  24 39 VDD Supply Voltage: Supply for circuits. Connect to 5.0V supply voltage  25 40 FS_D0 Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor  26 41 FS_S0 Fail Safe Source: to be connected to external FET Source used as FS. VDS monitor  27 42 FS_G0 Fail Safe Gate: Gate command for external FET Drain used as FS  28 43 VCP Charge Pump Voltage: Connected to Protected Battery Voltage through External Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20                        | 35                   | LOAD_SOL3 | Channel 3 Output                                                                            |

| 23 38 GNDA Analog Ground: Ground for analog circuits  24 39 VDD Supply Voltage: Supply for circuits. Connect to 5.0V supply voltage  25 40 FS_D0 Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor  26 41 FS_S0 Fail Safe Source: to be connected to external FET Source used as FS. VDS monitor  27 42 FS_G0 Fail Safe Gate: Gate command for external FET Drain used as FS  28 43 VCP Charge Pump Voltage: Connected to Protected Battery Voltage through External Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21                        | 36                   | VS_SOL3   | , , , ,                                                                                     |

| 24 39 VDD Supply Voltage: Supply for circuits. Connect to 5.0V supply voltage  25 40 FS_D0 Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor  26 41 FS_S0 Fail Safe Source: to be connected to external FET Source used as FS. VDS monitor  27 42 FS_G0 Fail Safe Gate: Gate command for external FET Drain used as FS  28 43 VCP Charge Pump Voltage: Connected to Protected Battery Voltage through External Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22                        | 37                   | FAULTn    | Fault: when LOW, Fault present, when HIGH, no fault present                                 |

| FS_D0 Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor  FS_S0 Fail Safe Source: to be connected to external FET Source used as FS. VDS monitor  FS_S0 Fail Safe Source: to be connected to external FET Source used as FS. VDS monitor  FS_G0 Fail Safe Gate: Gate command for external FET Drain used as FS  VCP Charge Pump Voltage: Connected to Protected Battery Voltage through External Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23                        | 38                   | GNDA      | Analog Ground: Ground for analog circuits                                                   |

| 26 41 FS_D0 monitor  26 41 FS_S0 Fail Safe Source: to be connected to external FET Source used as FS. VDS monitor  27 42 FS_G0 Fail Safe Gate: Gate command for external FET Drain used as FS  28 43 VCP Charge Pump Voltage: Connected to Protected Battery Voltage through External Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24                        | 39                   | VDD       | Supply Voltage: Supply for circuits. Connect to 5.0V supply voltage                         |

| VDS monitor  27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25                        | 40                   | FS_D0     |                                                                                             |

| 28 43 VCP Charge Pump Voltage: Connected to Protected Battery Voltage through External Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 26                        | 41                   | FS_S0     |                                                                                             |

| External Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27                        | 42                   | FS_G0     | Fail Safe Gate: Gate command for external FET Drain used as FS                              |

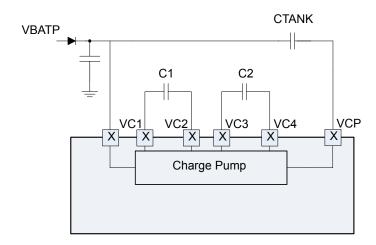

| 99 J. 14 NOS OL B. 5 . 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28                        | 43                   | VCP       |                                                                                             |

| 29 44 VC2 Charge Pump: External Capacitor connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29                        | 44                   | VC2       | Charge Pump: External Capacitor connection                                                  |

| 30 45 VC4 Charge Pump: External Capacitor connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30                        | 45                   | VC4       | Charge Pump: External Capacitor connection                                                  |

| 31 46 VC3 Charge Pump: External Capacitor connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31                        | 46                   | VC3       | Charge Pump: External Capacitor connection                                                  |

DS12774 - Rev 10 page 7/107

| Pin number<br>PowerSSO-36 | Pin number<br>TQFP48 | Symbol    | Function                                                                                                 |

|---------------------------|----------------------|-----------|----------------------------------------------------------------------------------------------------------|

| 32                        | 47                   | VC1       | Charge Pump: External Capacitor connection                                                               |

| 33                        | 48                   | VBATP     | Supply Voltage: Connected to Protected Battery Voltage (reverse protection diode and filter against EMC) |

| 34                        | 1                    | VS_SOL0   | Channel 0 Supply Voltage: Connect to Switched Battery Voltage with reverse protection diode              |

| 35                        | 2                    | LOAD_SOL0 | Channel 0 Output                                                                                         |

| 36                        | 3                    | GND_SOL0  | Channel 0 Ground: Ground connection for channel 0 power stage.                                           |

| _                         | _                    | _         | Available on TQFP-48 version only                                                                        |

| _                         | 9                    | FS_G_1    | Fail Safe Gate: Gate command for external FET Drain used as FS                                           |

| _                         | 8                    | FS_S_1    | Fail Safe Source: to be connected to external FET Source used as FS. VDS monitor                         |

| _                         | 7                    | FS_D_1    | Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor                           |

| _                         | 6                    | NC        | Not Used: To be connected to GND.                                                                        |

| _                         | 5                    | NC        | Not Used: To be connected to GND.                                                                        |

| _                         | 4                    | NC        | Not Used: To be connected to GND.                                                                        |

| _                         | 28                   | FS_G2     | Fail Safe Gate: Gate command for external FET Drain used as FS                                           |

| _                         | 29                   | FS_S2     | Fail Safe Source: to be connected to external FET Source used as FS. VDS monitor                         |

| _                         | 30                   | FS_D2     | Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor                           |

| _                         | 31                   | FS_D3     | Fail Safe Drain: to be connected to external FET Drain used as FS. VDS monitor                           |

| _                         | 32                   | FS_S3     | Fail Safe Source: to be connected to external FET Source used as FS. VDS monitor                         |

| _                         | 33                   | FS_G_3    | Fail Safe Gate: Gate command for external FET Drain used as FS                                           |

DS12774 - Rev 10 page 8/107

## 3 Product Characteristics

## 3.1 Absolute maximum ratings

This part may be irreparably damaged if taken outside the values specified in the next table. Operation above the absolute maximum ratings may also cause a decrease in reliability. The operating junction temperature range is from -40 °C to +175 °C. The maximum junction temperature must not be exceeded. All voltages are with respect to analog ground pin GNDA.

Pin name Туре **Test condition** Min Typ Max Unit | Pin type **VBATP** Global -0.3 40 S VCP Note: VCP-VBATP<13V, VBATP-VCP<0.3V -0.3 50 V S Local VC1, VC3 Note: VCx-VBATP<0.3V -0.3 40 V  $\cap$ Local VC2, VC4 Local Note: VCx-VBATP<13V VBATP-VCx<0.3V -0.3 50 ٧ 0 VS\_SOLx Global -0.3 40(1) ٧ S LOAD\_SOLx Global -0.3 40(1) ٧ 0 GND\_SOLx Local -0.3 0.3 V 1 VDD Local -0.3 19 ٧ S \_ S **VDDIO** Local -0.3 19 ٧ V S **GNDD** Local -0.3 0.3 FS D0 Global -0.3 40 ٧ ī Internally shorted to FS\_S0 (off phase) Note: Local -2<sup>(2)</sup> 0 FS\_G0 50 ٧ FS G0-FS S0<13V Note: FS\_S0-FS\_G0<0.3V FS\_S0 Global -2 50 ٧ 0 CS, SCLK, MOSI, EN\_DR, RESn, Local -0.3 19 ī

-0.3

19

٧

0

Table 2. Absolute maximum ratings

Local

INx\_DISx MISO, FAULTn

## 3.2 Latchup trials

Latch-up tests performed according to JEDEC 78 class 2 Level A

DS12774 - Rev 10 page 9/107