◇PRODUCT **◇PART NUMBER ♦DESCRIPTION**

64 x 16 bit Electrically Erasable Programmable Rom

BR9010/F/FV/RFV/RFVM-W

The BR9010-W series are serial EEPROMs that can be connected directly to a serial port and can be erased and written electrically. Writing and reading is perfomed in word units, using four types of operation commands. Communication occurs through CS, SK, DI, and DO pins, WC pin control is used to initiate a write disabled state, enabling these EEPROMs to be used as one-time ROMs. During writing, operation is checked via the internal status check.

**APPLICATION** General Purpose **♦FEATURES**

• 64words x 16 bit organization 1kbit serial EEPROM

· Single power supply

Serial data I/O

Self-timed programming cycle with auto-erase

·Low supply current

Active (5V); 2mA (max.)

Standby (5V); 3uA (max.) (CMQS INPUT)

•Noise filter on the SK pin

\*Write protection when the supply is low

Space Saving DIP8/SOP8/SSOP8/MSOP8pin Packages

·High reliability CMOS process

·100,000 erase/write cycles endurance

Provide 10 years of data retention

•Easy connection to serial port

"FFFFh" stored in all address on shipped

#### ♦ ABSOLUTE MAXIMUM RATINGS(Ta=25°C)

| Parameter             | Symbol | Rating -0. 3~7. 0               |                                          | Unit          |

|-----------------------|--------|---------------------------------|------------------------------------------|---------------|

| Supply Voltage        | VCC    |                                 |                                          | $\overline{}$ |

| Power dissipation     | Pd     | DIP8<br>SOP8<br>SSOPB8<br>MSOP8 | 800(%1)<br>450(%2)<br>300(%3)<br>310(%4) | mW            |

| Storage Temperature   | Tstg   | -65~125                         |                                          | °C            |

| Operating Temperature | Topr   | -40~85                          |                                          | ొ             |

| Terminal Voltage      |        | -0. 3~Vcc+0. 3                  |                                          | V             |

Degradation is done at 8.0mW/°C for operation above Ta=25°C Degradation is done at 4.5mW/°C for operation above Ta=25°C Degradation is done at 3.0mW/°C for operation above Ta=25°C

Degradation is done at 3.1mW/°C for operation above Ta=25°C

# **♦ RECOMMENDED OPERATING CONDITION**

| Parameter      | neter Symbol Rating |                  | Unit |

|----------------|---------------------|------------------|------|

| Supply Voltage | V00                 | 2. 7~5. 5(WRITE) |      |

|                | VCC -               | 2. 7~5. 5(READ)  |      |

| Input Voltage  | Vin                 | o ~ vcc          | 1    |

# *<del>OELECTRICAL CHARACTERISTICS </u>*</del>

Unless otherwise specified(Ta=-40~85°C, VCC=2. 7~5. 5V)

| Offices Outletwise spe | ecified(Ta=-40~85°C, VCC=2. 7~ |             |         | <del>:</del> |      |                                | Test    |

|------------------------|--------------------------------|-------------|---------|--------------|------|--------------------------------|---------|

| Parameter              | Symbol                         |             |         | Max.         | Unit | Condition                      | Circuit |

| Input Low Voltage 1    | VIL1                           | _           | -       | 0.3x<br>VCC  | V    | DI Pin                         |         |

| Input High Voltage 1   | VIH1                           | 0.7x<br>VCC |         | _            | V    | DI Pin                         |         |

| Input Low Voltage 2    | VIL2                           | _           |         | 0.2x<br>VCC  | V    | CS, SK, WC Pin                 |         |

| Input High Voltage 2   | VIH2                           | 0.8x<br>VCC | _       |              | ٧    | CS, SK, WC Pin                 |         |

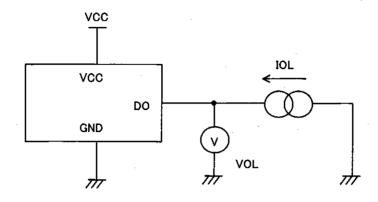

| Output Low Voltage     | VOL                            | 0           | _       | 0.4          | V    | IOL=2.1mA                      | Fig4    |

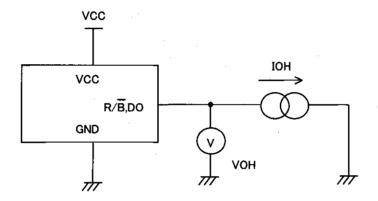

| Output High Voltage    | ∨он                            | VCC-<br>0.4 |         | vcc          | V    | IOH=-0.4mA                     | Fig5    |

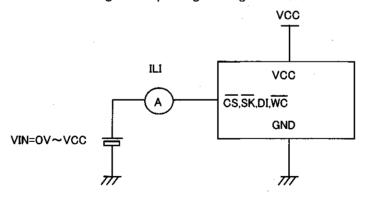

| Input Leakage Current  | ILI                            | -1          | _       | 1            | μА   | VIN=0V~VCC                     | Fig6    |

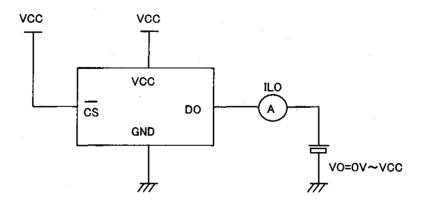

| Output Leakage Current | ILO                            | -1          | ·<br> - | . 1          | μΑ   | VOUT=0V~VCC,CS =VCC            | Fìg.−7  |

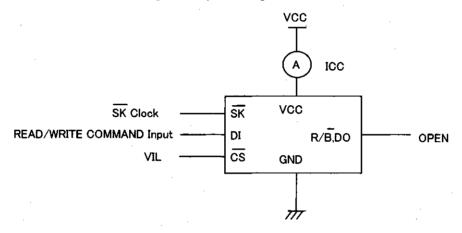

|                        | ICC1                           | _           | _       | 2            | mA   | fSK=2MHz,tE/W=10ms (WRITE)     | Fig8    |

| Operating Current      | ICC2                           | _           | _       | 1            | mA   | fSK=2MHz (READ)                | Fig8    |

| Standby Current        | ISB                            | _           | _       | 3            | μΑ   | CS,SK,DI,WC=VCC<br>DO,R/B=OPEN | Fig9    |

| Clock Frequency        | fSK                            | _           |         | 2            | MHz  |                                |         |

Unless otherwise specified (Ta=-40~85°C, VCC=2. 7~3. 3V)

| Parameter              | Symbol | Limit          |              |             | Unit | Condition                      | Test    |

|------------------------|--------|----------------|--------------|-------------|------|--------------------------------|---------|

|                        |        | Min.           | Тур.         | Max.        | ļ    |                                | Circuit |

| Input Low Voltage 1    | VIL1   | -<br>-         |              | 0.3x<br>VCC | V    | DI Pin                         |         |

| Input High Voltage 1   | VIH1   | 0.7x<br>VCC    | ` <u> </u>   | <b>–</b>    | ٧    | DI Pin                         |         |

| Input Low Voltage 2    | VIL2   | -              |              | 0.2x<br>VCC | V    | CS, SK, WC Pin                 |         |

| Input High Voltage 2   | VIH2   | 0.8x<br>VCC    |              | _           | V    | CS, SK, WC Pin                 |         |

| Output Low Voltage     | VOL    | 0              | _            | 0.4         | V    | IOL=100uA                      | Fig4    |

| Output High Voltage    | VOH    | VCC-<br>0.4    | -            | VCC         | ٧    | IOH=-100uA                     | Fig5    |

| Input Leakage Current  | ILI    | -1             | <del>_</del> | 1           | μА   | VIN=0~VCC                      | Fig6    |

| Output Leakage Current | ILO    | -1             |              | 1           | μΑ   | VOUT=0~VCC,CS=VCC              | Fig7    |

| Operating Current      | ICC1   | _              | _            | 1.5         | mA   | fSK =2MHz,tE/W=10ms (WRITE)    | Fig.~8  |

| Operating Ourrent      | ICC2   | <del>-</del> . | <del>-</del> | 0.5         | mA   | fSK =2MHz (READ)               | Fig8    |

| Standby Current        | ISB    | _              | _            | 2           | μА   | CS,SK,DI,WC=VCC<br>DO,R/B=OPEN | Fig9    |

| Clock Frequency        | fSK    |                | _            | 2           | MHz  |                                |         |

OThis product is not designed for protection against radioactive rays.

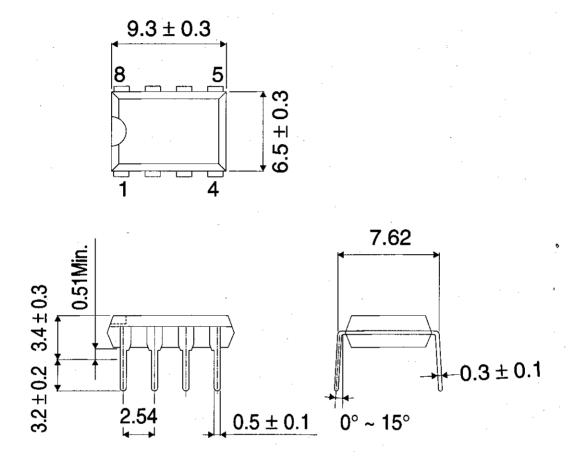

Fig.1-1 Outline Dimensions DIP8(BR9010-W)

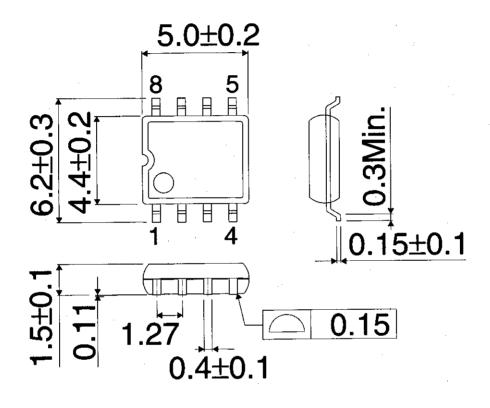

Fig.1-2 Outline Dimensions SOP8(BR9010F-W)

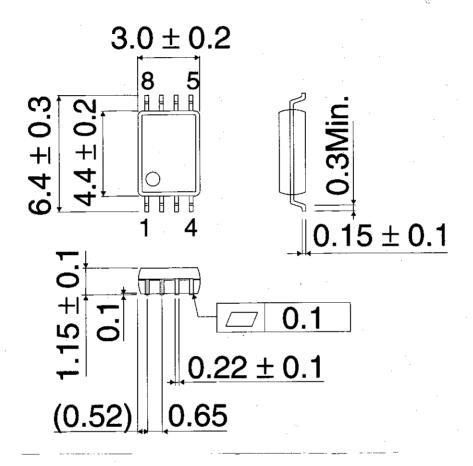

Fig.1-3 Outline Dimensions SSOPB8(BR9010RFV-W)

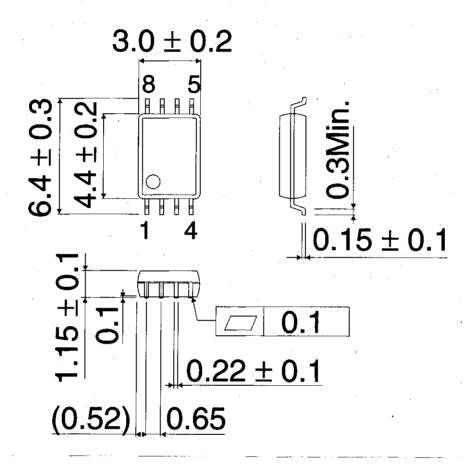

Fig.1-4 Outline Dimensions SSOPB8(BR9010FV-W)

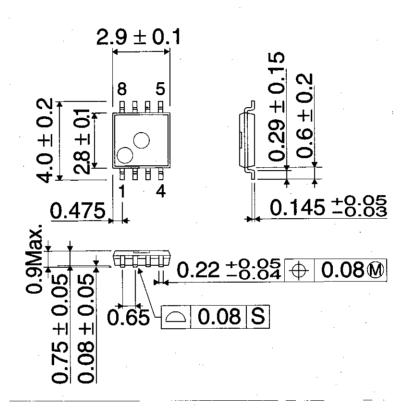

Fig.1-5 Outline Dimensions MSOP8(BR9010RFVM-W)

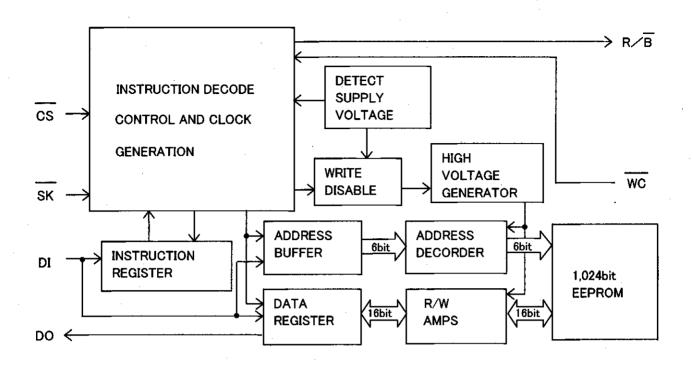

Fig.-2 Block Diagram

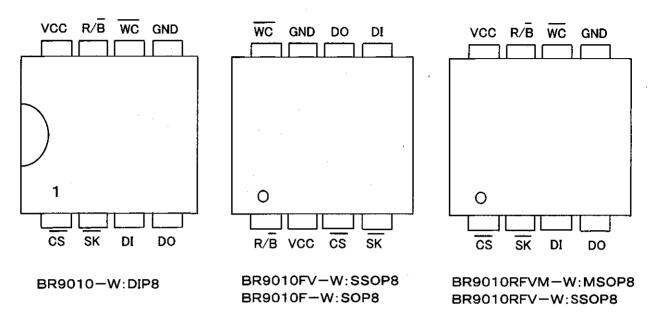

# **♦PIN CONFIGURATIONS**

Fig.-3 Pin Configurations

# **♦TERMINAL FUNCTION**

| Terminal | IN/OUT | Function                             |

|----------|--------|--------------------------------------|

| Vcc      | _      | Power Supply                         |

| GND      | _      | Ground (0V)                          |

| cs       | INPUT  | Chip Select Input                    |

| SK       | INPUT  | Serial Data Clock Input              |

| DI       | INPUT  | Serial Data Input (Op code, address) |

| DO       | OUTPUT | Serial Data Output                   |

| wc       | INPUT  | Write Control Input                  |

| R/B      | OUTPUT | READY/BUSY Status Output             |

Set Output Pin to Low

Fig.-4 Output Low voltage test circuit

Set Output Pin to High

Fig.-5 Output High voltage test circuit

Fig.-6 Input leakage current test circuit

Fig.-7 Output leakage current test circuit

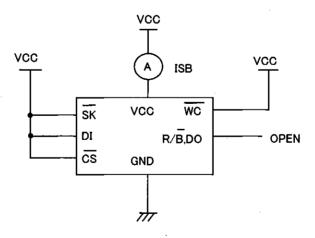

Fig.-8 Operating Current test circuit

Fig.-9 Standby current test circuit

# **♦INSTRUCTION CODE**

| Instruction        | Start Bit | Op Code | Address               | Data                            |  |  |

|--------------------|-----------|---------|-----------------------|---------------------------------|--|--|

| READ               | 1010      | 1000    | A0 A1 A2 A3 A4 A5 0 0 | D0 D1 - D14 D15<br>(READ DATA)  |  |  |

| WRITE              | 1010      | 0100    | A0 A1 A2 A3 A4 A5 0 0 | D0 D1 - D14 D15<br>(WRITE DATA) |  |  |

| Write Enable(WEN)  | 1010      | 0011    | * * * * * * *         |                                 |  |  |

| Write Disable(WDS) | 1010      | 0000    | * * * * * * * *       |                                 |  |  |

Address and data must be transferred from LSB.

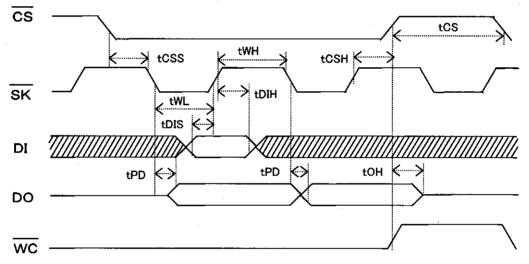

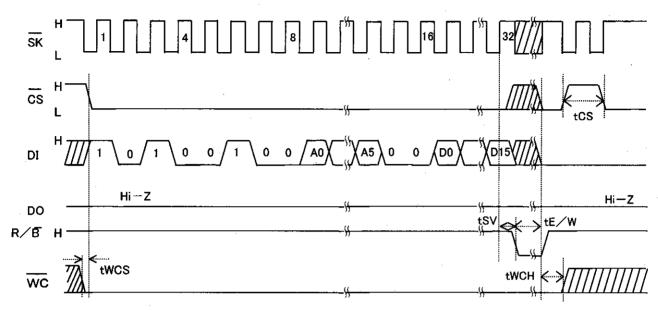

#### **SYNCHRONOUS DATA INPUT OUTPUT TIMING**

Fig.-10 Synchronous data input output timing

Olnput Data is clocked into the DI pin on the rising edge of the clock SK.

- OOutput data is clocked out on the falling edge of the SK clock.

- OThe WC pin does not have any affect on the READ, WEN and WDS operations.

- OBetween instructions, CS must be brought High for greater than the minimum of tCS. If CS is maintained Low, the next instruction isn't detected.

<sup>&</sup>quot;\*" Means either VIH or VIL

# ♦AC OPERATION CHARACTERISTICS(Ta=-40~85°C, VCC=2. 7~5. 5V)

| Parameter                              | Symbol | Min. | Тур. | Max.     | Unit |

|----------------------------------------|--------|------|------|----------|------|

| Chip Select Setup Time                 | tCSS   | 100  |      | _        | ns   |

| Chip Select Hold Time                  | tCSH   | 100  |      | _        | ns   |

| Data In Setup Time                     | tDIS   | 100  | 1    | •        | ns   |

| Data In Hold Time                      | tDIH   | 100  | 1    | <b>–</b> | ns   |

| Delay to Output High                   | tPD1   | 1 -  | 1    | 150      | ns   |

| Delay to Output Low                    | tPD0   | .    | I    | 150      | ns   |

| Self-Timed Program Cycle               | tE/W   | I    | 1    | 10       | ms   |

| Minimum Chip Select High Time          | tCS    | 250  | 1    | ı        | ns   |

| Data Output Disable Time (From CS)     | tOH    | 0    | .1   | 150      | ns   |

| Clock High Time                        | tWH    | 230  | 1    | 1        | ns   |

| Clock Low Time                         | tWL    | 230  | I    | <b>l</b> | ns   |

| Write Control Setup Time               | tWCS   | 0    | _    | _        | ns   |

| Write Control Hold Time                | tWCH   | 0    | _    | -        | ns   |

| Clock High to Output READY/BUSY Status | tSV    | -    | _    | 150      | ns   |

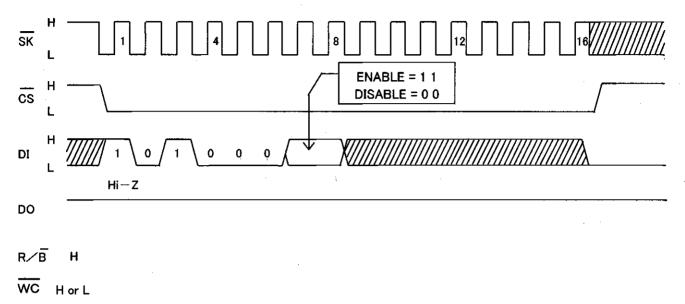

#### **♦TIMING CHART**

#### 1. WRITE Enable/Disable

Fig.-11 WRITE Enable and Disable Cycle Timing

- OWhen power is first applied, the device has been held in a reset status, with respect to the write enable, in the same way the write disable (WDS) instruction is executed. Before the write instruction is executed, the device must be received the write enable (WEN) instruction. Once the device is done, the device remains programmable until the write disable (WDS) instruction is executed or the supply is removed from the device.

- OIt is unnecessary to add the clock after 16th clock. If the device is recieved the clock, the device ignores the clock.

- OAs both of the enable and disable instructions don't depend on the status of the WC pin, the state of WC isn't cared during the instruction.

- OThe instruction is recognized after the rising edge of 8th clock for the address following 8clocks for the opcode, but the specified address isn't cared during the instructions.

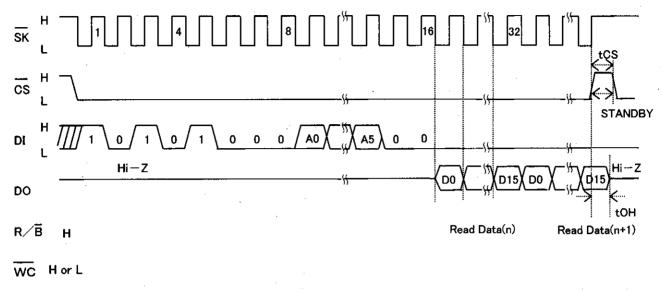

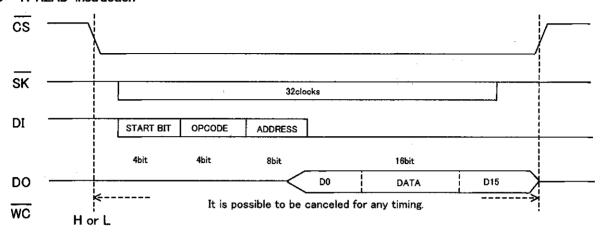

#### 2. READ INSTRUCTION

Fig.-12 READ Cycle Timing

OOn the falling edge of 16th clock, the data stored in the specified address (n) is clocked out of the DO pin.

The output DO is toggled after the internal propagation tPD0 or tPD1 on the falling edge of SK. During tPD0 or tPD1, the data is the previous data or unstable, and to take in the data, tPD is needed. (Refer to Fig.-10 Synchronous data input output timing.)

OThe data stored in the next address is clocked out of the device on the falling edge of 32nd clock. The data stored in the upper address every 16 clocks is output sequentially by the continual SK input. Also the read operation is reset by CS High.

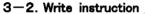

#### 3. WRITE INSTRUCTION

Fig.-13 WRITE Cycle Timing

ODuring the write instruction, CS must be brought Low. However once the write operation started, CS may be either High or Low. But in the case of connecting the WC pin to the CS pin, CS and WC must be brought Low during programming cycle. (If the WC pin is brought High during the write cycle, the write operation is halted. In that case, the data of the specified address is not guaranteed. It is necessary to rewrite it.)

OAfter the R/B pin changed Busy to Ready, once CS is brought High, then CS keep Low, which means the status of being able to accept an instruction. The device can take in the input from SK and DI, but in the case of keeping CS Low without being brought High once, the input is canceled until being CS High once.

OAt the rising edge of 32nd clock, the R/B pin will be driven Low after the specified time delay(tSV). ODuring programming, R/B is tied to Low by the device (On the rising edge of SK taken in the last data (D15), internal timer starts and automatically finished after the data of memory cell is written spending tE/W. SK could be either High or Low at the time.

OAfter input write instruction, also the DO pin will be able to show the status of R/B, in the case that CS is falling from High to Low while SK is tied to Low. (Refer to READY/BUSY STATUS in the next page.)

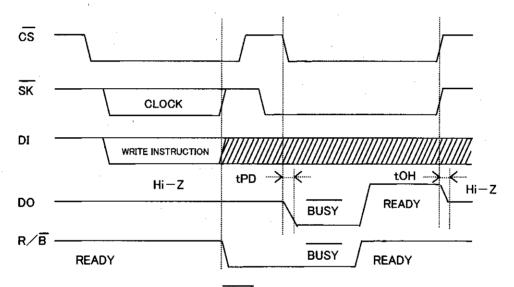

# ♦ READY/BUSY STATUS (on the R/B pin, the DO pin)

•The DO pin outputs the READY/BUSY status of the internal part, which shows whether the device is ready to receive the next instruction or not. (High or Low)

After the write instruction is completed, if CS is brought from high to low while SK is Low, the DO pin outputs the internal status.(The R/B pin may be no connection.)

When written to the memory cell, R/B status is output after tSV spent from the rising edge of 32th clock on SK.

R/B =Low : under writing

After spending tE/W operating the internal timer, the device automatically

finishes writing.

During tE/W, the memory array is accessed and any instruction is not received.

$R/\overline{B} = High : ready$

Auto programming has been completed. The device is ready to receive the next Instruction.

Fig.-14 READY/BUSY Status Output timing

About the direct connection between the DI and DO pins

The device can be used with the DI pin connected to the DO pin directly.

But when the READY/BUSY status is output, be careful about the bus conflict on the port of the controller.

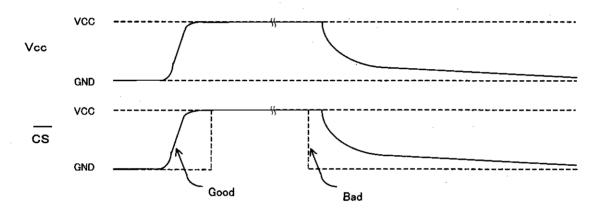

# ●ATTENTION TO USE 1. Power ON/OFF

- •The CS is brought High during power-up and power-down.

- •This device is in active state while CS is Low.

- •The extraordinary function or data collapse may occur in that condition because of noise etc., if power-up and power-down is done with CS brought Low.

In order to prevent above errors from happening, keep CS High during power-up and power-down.

(Good example) CS is brought High during power-up and power-down.

Please take more than 10ms between power-up and power-off, or the internal circuit is not always reset.

(Bad example ) CS is brought Low during power-up and power-down.

The  $\overline{\text{CS}}$  pin is always Low in this case, the noise may force the device to make malfunction or inadvertent write.

※ It sometimes occurs in the case that the CS pin is Hi-Z.

# 2. NOISE REJECTION

# 2-1 SK NOISE

If SK line has a lot of noise for rising time of SK, the device may recognize the noise as a clock and then clock will be shifted.

# 2-2 WC NOISE

If WC line has noise during write cycle(tE/W), there may be a chance to deny the programming.

# 2-3 VCC NOISE

It recommended that capacitor is put between VCC and GND to prevent these case, since it is possible to occur malfunction by the effect of noise or surge on power line.

# 3. INSTRUCTION MODE CANCEL

#### 3-1. READ instruction

How to cancel: CS is brought High.

How to cancel

a : CS is brought High to cancel the instruction, and WC may be either High or Low.

b: In case that WC is brought High for a moment, or CS is brought High, the write instruction is canceled, the data of the specified address is not changed.

c : When WC is brought High, or the device is powered down (But the latter way is not recommended), the instruction is canceled but the specified data is not guaranteed. Send the instruction again.

d: When  $\overline{CS}$  is brought High during R/B High, the device is reset and ready to receive a next instruction.

NOTE: The document may be strategic technical data subject to COCOM regulations.