Distributed by:

JAMECO

ELECTRONICS

## www.Jameco.com + 1-800-831-4242

The content and copyrights of the attached material are the property of its owner.

Jameco Part Number 1726831

# Dual, Matched Precision Operational Amplifier

### **FEATURES**

- Guaranteed low offset voltage

LT1002A 60μV max

LT1002 100μV max

- Guaranteed offset voltage match

LT1002A 40μV max

LT1002 80μV max

- Guaranteed low drift

LT1002A 0.9 $\mu$ V/°C max LT1002 1.3 $\mu$ V/°C max

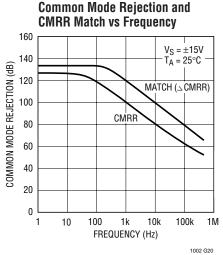

Guaranteed CMRR

LT1002A 110dB min LT1002 110dB min

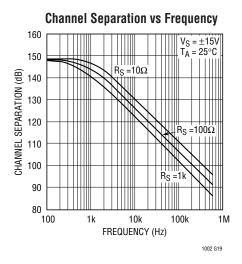

Guaranteed channel separation

LT1002A 132dB min LT1002 130dB min

- Guaranteed matching characteristics

- Low noise 0.35µV<sub>P-P</sub>

### **APPLICATIONS**

- Thermocouple Amplifiers

- Strain Gauge Amplifiers

- Low level signal processing

- Medical instrumentation

- Precision dual limit threshold detection

- Instrumentation amplifiers

7, LTC and LT are registered trademarks of Linear Technology Corporation

## DESCRIPTION

The LT®1002 dual, matched precision operational amplifiers combine excellent individual amplifier performance with tight matching and temperature tracking between amplifiers.

In the design, processing, and testing of the device, particular attention has been paid to the optimization of the entire distribution of several key parameters and their matching. Consequently, the specifications of even the low cost commercial grade (LT1002C) have been spectacularly improved compared to presently available devices.

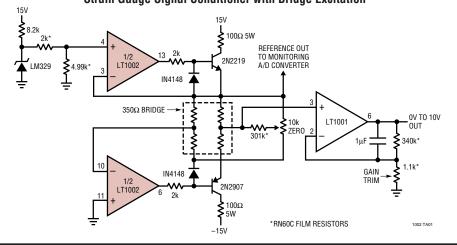

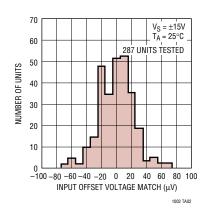

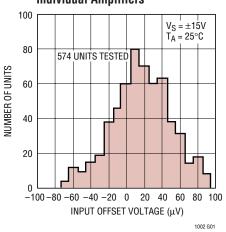

Essentially, the input offset voltage of all units is less than  $80\mu V$ , and matching between amplifiers is consistently beter than  $60\mu V$  (see distribution plot below). Input bias and offset currents, channel separation, common mode and power suply rejections of the LT1002C are all specified at levels which were previsouly attainable only on very expensive, selected grades of other dual devices. Power dissipation is nearly halved compared to the most popular precision duals, without adversely affecting noise or speed performance. A by-product of lower dissipation is decreased warm-up drift. For even better performance in a single precision op amp, refer to the LT1001 data sheet. A bridge signal conditioning application is shown below. This circuit illustrates the requirement for both excellent matching and individual amplifier specifications.

## TYPICAL APPLICATION

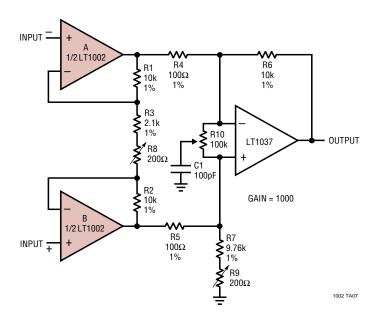

#### Strain Gauge Signal Conditioner with Bridge Excitation

#### Distribution of Offset Voltage Match

## **ABSOLUTE MAXIMUM RATINGS**

| (Note 1)                               |                  |

|----------------------------------------|------------------|

| Supply Voltage (Note 7)                | ±22V             |

| Differential Input Voltage             | ±30V             |

| Input Voltage Equal to Supply Voltage  |                  |

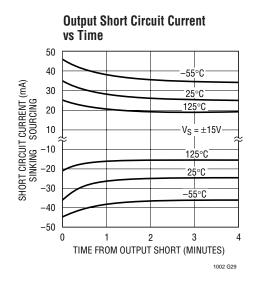

| Output Short Circuit Duration          | Indefinite       |

| Operating Temperature Range            |                  |

| LT1002AM/LT1002M (OBSOLETE).           | .−55°C to 125°C  |

| LT1002AC/LT1002C                       | 0°C to 70°C      |

| Storage Temperature Range              |                  |

| All Grades                             | . −65°C to 150°C |

| Lead Temperature (Soldering, 10 sec.). | 300°C            |

|                                        |                  |

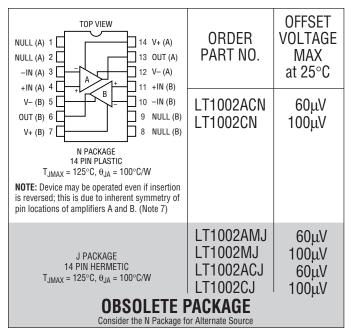

## PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

## **ELECTRICAL CHARACTERISTICS, INDIVIDUAL AMPLIFIERS**

$V_S=\pm 15 V,~T_A=25^{\circ}C,~unless~otherwise~noted$

| 0)/11001                            |                                             |                                                                          |            | 2AM/LT1      |              |            | 002C         |              |                   |

|-------------------------------------|---------------------------------------------|--------------------------------------------------------------------------|------------|--------------|--------------|------------|--------------|--------------|-------------------|

| SYMBOL                              | PARAMETER                                   | CONDITIONS                                                               | MIN        | TYP          | MAX          | MIN        | TYP          | MAX          | UNITS             |

| $V_{OS}$                            | Input Offset Voltage                        | (Note 2)                                                                 |            | 20           | 60           |            | 25           | 100          | μV                |

| $\frac{\Delta V_{OS}}{\Delta Time}$ | Long Term Input Offset Voltage<br>Stability | (Notes 3 and 4)                                                          |            | 0.3          | 1.5          |            | 0.4          | 2.0          | μV/month          |

| I <sub>0S</sub>                     | Input Offset Current                        |                                                                          |            | 0.3          | 2.8          |            | 0.4          | 4.2          | nA                |

| $I_{B}$                             | Input Bias Current                          |                                                                          |            | ±0.6         | ±3.0         |            | ±0.7         | ±4.5         | nA                |

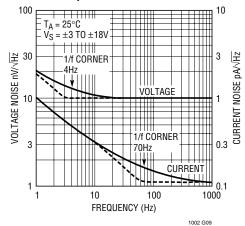

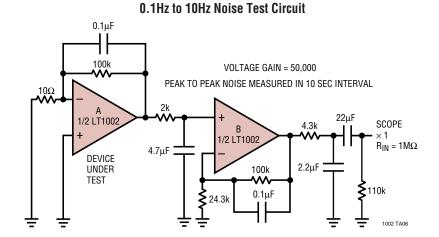

| $\overline{\overline{e}_n}$         | Input Noise Voltage                         | 0.1Hz to 10Hz (Note 3)                                                   |            | 0.35         | 0.7          |            | 0.38         | 0.75         | μV <sub>p-p</sub> |

| e <sub>n</sub>                      | Input Noise Voltage Density                 | f <sub>0</sub> = 10Hz (Note 6)<br>f <sub>0</sub> = 1000Hz (Note 3)       |            | 10.3<br>9.6  | 20.0<br>11.5 |            | 10.5<br>9.8  | 20.0<br>12.0 | nV√Hz             |

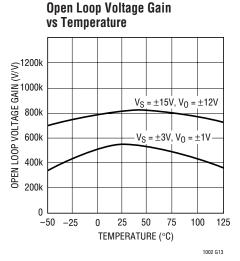

| A <sub>VOL</sub>                    | Large Signal Voltage Gain                   | $R_L \ge 2k\Omega, V_0 = \pm 12V$<br>$R_L \ge 1k\Omega, V_0 = \pm 10V$   | 400<br>250 | 800<br>500   |              | 350<br>220 | 800<br>500   |              | V/mV              |

| CMRR                                | Common Mode Rejection Ratio                 | $V_{CM} = \pm 13V$                                                       | 110        | 126          |              | 110        | 126          |              | dB                |

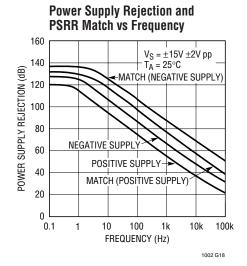

| PSRR                                | Power Supply Rejection Ratio                | $V_S = \pm 3V \text{ to } \pm 18V$                                       | 108        | 123          |              | 105        | 123          |              | dB                |

| R <sub>in</sub>                     | Input Resistance Differential Mode          | (Note 5)                                                                 | 20         | 100          |              | 13         | 80           |              | MΩ                |

|                                     | Input Voltage Range                         |                                                                          | ±13        | ±14          |              | ±13        | ±14          |              | V                 |

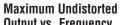

| V <sub>OUT</sub>                    | Maximum Output Voltage Swing                | $\begin{aligned} R_L &\geq 2k\Omega \\ R_L &\geq 1k\Omega \end{aligned}$ | ±13<br>±12 | ±14<br>±13.5 |              | ±13<br>±12 | ±14<br>±13.5 |              | V                 |

| SR                                  | Slew Rate                                   | $R_L \ge 2k\Omega$ (Note 5)                                              | 0.1        | 0.25         |              | 0.1        | 0.25         |              | V/µs              |

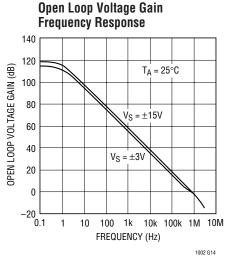

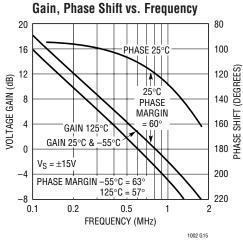

| GBW                                 | Gain Bandwidth Product                      | (Note 5)                                                                 | 0.4        | 0.8          |              | 0.4        | 0.8          |              | MHz               |

| $\overline{P_d}$                    | Power Dissipation per amplifier             | No load<br>No load, $V_S = \pm 3V$                                       |            | 46<br>4      | 75<br>7      |            | 48<br>4      | 85<br>8      | mW                |

# **ELECTRICAL CHARACTERISTICS, INDIVIDUAL AMPLIFIERS**

The ullet denotes the specifications which apply over the temperature range  $-55^{\circ}C \leq T_A \leq 125^{\circ}C$ ,  $V_S = \pm 15V$ ,unless otherwise noted.

|                               |                                    |                                      |   | ı     | LT1002A | M    |       | LT1002N | /I   |       |

|-------------------------------|------------------------------------|--------------------------------------|---|-------|---------|------|-------|---------|------|-------|

| SYMBOL                        | PARAMETER                          | CONDITIONS                           |   | MIN   | TYP     | MAX  | MIN   | TYP     | MAX  | UNITS |

| $V_{OS}$                      | Input Offset Voltage               | (Note 2)                             | • |       | 30      | 150  |       | 45      | 230  | μV    |

| $\Delta V_{OS}$ $\Delta Temp$ | Average Input Offset Voltage Drift |                                      | • |       | 0.2     | 0.9  |       | 0.3     | 1.3  | μV/°C |

| I <sub>OS</sub>               | Input Offset Current               |                                      | • |       | 0.8     | 5.6  |       | 1.2     | 8.5  | nA    |

| I <sub>B</sub>                | Input Bias Current                 |                                      | • |       | ±1.0    | ±6.0 |       | ±1.5    | ±9.0 | nA    |

| A <sub>VOL</sub>              | Large Signal Voltage Gain          | $R_L \ge 2k\Omega$ , $V_0 = \pm 10V$ | • | 300   | 700     |      | 200   | 700     |      | V/mV  |

| CMRR                          | Common Mode Rejection Ratio        | $V_{CM} = \pm 13V$                   | • | 106   | 122     |      | 104   | 120     |      | dB    |

| PSRR                          | Power Supply Rejection Ratio       | $V_S = \pm 3V \text{ to } \pm 18V$   | • | 102   | 117     |      | 96    | 117     |      | dB    |

|                               | Input Voltage Range                |                                      | • | ±13   | ±14     |      | ±13   | ±14     |      | V     |

| V <sub>OUT</sub>              | Output Voltage Swing               | $R_L \ge 2k\Omega$                   | • | ±12.5 | ±13.5   |      | ±12.0 | ±13.5   |      | V     |

| $\overline{P_d}$              | Power Dissipation per amplifier    | No load                              | • |       | 55      | 90   |       | 60      | 100  | mW    |

The ullet denotes the specifications which apply over the temperature range  $0^{\circ}C \leq T_A \leq 70^{\circ}C$ ,  $V_S = \pm 15V$ , unless otherwise noted.

| SYMBOL                            | PARAMETER                          | CONDITIONS                           |   | MIN    | .T1002A( | MAX  | MIN    | LT1002C<br>TYP | MAX  | UNITS |

|-----------------------------------|------------------------------------|--------------------------------------|---|--------|----------|------|--------|----------------|------|-------|

| STWIDUL                           |                                    |                                      |   | IVIIIV |          |      | IVIIIV |                |      | UNITS |

| $V_{OS}$                          | Input Offset Voltage               | (Note 2)                             | • |        | 20       | 100  |        | 30             | 160  | μV    |

| $\Delta V_{OS} \over \Delta Temp$ | Average Input Offset Voltage Drift |                                      | • |        | 0.2      | 0.9  |        | 0.3            | 1.3  | μV/°C |

| I <sub>OS</sub>                   | Input Offset Current               |                                      | • |        | 0.5      | 4.2  |        | 0.6            | 5.7  | nA    |

| I <sub>B</sub>                    | Input Bias Current                 |                                      | • |        | ±0.7     | ±4.5 |        | ±1.0           | ±6.0 | nA    |

| A <sub>VOL</sub>                  | Large Signal Voltage Gain          | $R_L \ge 2k\Omega$ , $V_0 = \pm 10V$ | • | 350    | 750      |      | 250    | 750            |      | V/mV  |

| CMRR                              | Common Mode Rejection Ratio        | $V_{CM} = \pm 13V$                   | • | 108    | 124      |      | 106    | 123            |      | dB    |

| PSRR                              | Power Supply Rejection Ratio       | $V_S = \pm 3V \text{ to } \pm 18V$   | • | 105    | 120      |      | 100    | 120            |      | dB    |

|                                   | Input Voltage Range                |                                      | • | ±13    | ±14      |      | ±13    | ±14            |      | V     |

| V <sub>OUT</sub>                  | Output Voltage Swing               | $R_L \ge 2k\Omega$                   | • | ±12.5  | ±13.8    |      | ±12.5  | ±13.8          |      | V     |

| $P_d$                             | Power Dissipation per amplifier    | No Load                              | • |        | 50       | 85   |        | 55             | 90   | mW    |

## **MATCHING CHARACTERISTICS**

$V_S = \pm 15V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

|                              |                                       |                                      | LT  | 1002AM | /AC  | L   |      |      |       |

|------------------------------|---------------------------------------|--------------------------------------|-----|--------|------|-----|------|------|-------|

| SYMBOL                       | PARAMETER                             | CONDITIONS                           | MIN | TYP    | MAX  | MIN | TYP  | MAX  | UNITS |

|                              | Input Offset Voltage Match            |                                      | _   | 15     | 40   | _   | 25   | 80   | μV    |

| I <sub>B</sub> <sup>+</sup>  | Average Non-Inverting Bias<br>Current |                                      | _   | ±0.6   | ±3.5 | _   | ±0.7 | ±4.8 | nA    |

| I <sub>OS</sub> +            | Non-Inverting Offset Current          |                                      | -   | 0.6    | 3.5  | -   | 0.7  | 6.0  | nA    |

| I <sub>OS</sub> <sup>-</sup> | Inverting Offset Current              |                                      | -   | 0.6    | 3.5  | -   | 0.7  | 6.0  | nA    |

| ∆CMRR                        | Common Mode Rejection Ratio<br>Match  | V <sub>CM</sub> = ±13V               | 110 | 132    | _    | 108 | 132  | _    | dB    |

| ∆PSRR                        | Power Supply Rejection Ratio<br>Match | $V_{S} = \pm 3V \text{ to } \pm 18V$ | 108 | 130    | _    | 102 | 128  | _    | dB    |

|                              | Channel Seperation                    | f ≤ 10Hz (Note 5)                    | 132 | 148    | _    | 130 | 146  | _    | dB    |

### **MATCHING CHARACTERISTICS**

The ullet denotes the specifications which apply over the temperature range  $-55^{\circ}C \le T_A \le 125^{\circ}C$ ,  $V_S = \pm 15V$ , unless otherwise noted.

|                              |                                       |                                      |   | L   | T1002A | M    |     | LT1002 | VI    |       |

|------------------------------|---------------------------------------|--------------------------------------|---|-----|--------|------|-----|--------|-------|-------|

| SYMBOL                       | PARAMETER                             | CONDITIONS                           |   | MIN | TYP    | MAX  | MIN | TYP    | MAX   | UNITS |

|                              | Input Offset Voltage Match            |                                      | • | _   | 50     | 140  | _   | 60     | 230   | μV    |

|                              | Input Offset Voltage Tracking         |                                      | • | _   | 0.3    | 1.0  | -   | 0.4    | 1.5   | μV/°C |

| I <sub>B</sub> <sup>+</sup>  | Average Non-Inverting Bias<br>Current |                                      | • | _   | ±1.5   | ±6.0 | _   | ±1.8   | ±10.0 | nA    |

| I <sub>OS</sub> <sup>+</sup> | Non-Inverting Offset Current          |                                      | • | _   | 1.5    | 6.5  | _   | 1.8    | 12.0  | nA    |

| I <sub>0S</sub> <sup>-</sup> | Inverting Offset Current              |                                      | • | _   | 1.5    | 6.5  | -   | 1.8    | 12.0  | nA    |

| ΔCMRR                        | Common Mode Rejection Ratio<br>Match  | V <sub>CM</sub> = ±13V               | • | 106 | 126    |      | 102 | 124    | _     | dB    |

| ΔPSRR                        | Power Supply Rejection Ratio<br>Match | $V_{S} = \pm 3V \text{ to } \pm 18V$ | • | 102 | 122    |      | 94  | 120    | _     | dB    |

#### The ullet denotes the specifications which apply over the temperature range $0^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq 70^{\circ}\text{C}$ , $\text{V}_{\text{S}} = \pm 15\text{V}$ , unless otherwise noted.

|                              |                                       |                                      | L | T1002A | С    |      |     |      |      |       |

|------------------------------|---------------------------------------|--------------------------------------|---|--------|------|------|-----|------|------|-------|

| SYMBOL                       | PARAMETER                             | CONDITIONS                           |   | MIN    | TYP  | MAX  | MIN | TYP  | MAX  | UNITS |

|                              | Input Offset Voltage Match            |                                      | • | _      | 30   | 85   | _   | 45   | 150  | μV    |

|                              | Input Offset Voltage Tracking         |                                      | • | _      | 0.3  | 1.0  | _   | 0.4  | 1.5  | μV/°C |

| I <sub>B</sub> +             | Average Non-Inverting Bias<br>Current |                                      | • | _      | ±1.0 | ±4.5 | _   | ±1.2 | ±7.0 | nA    |

| I <sub>OS</sub> <sup>+</sup> | Non-Inverting Offset Current          |                                      | • | _      | 1.0  | 5.0  | _   | 1.2  | 8.5  | nA    |

| I <sub>0S</sub> <sup>-</sup> | Inverting Offset Current              |                                      | • | _      | 1.0  | 5.0  | _   | 1.2  | 8.5  | nA    |

| ΔCMRR                        | Common Mode Rejection Ratio<br>Match  | V <sub>CM</sub> = ±13V               | • | 108    | 130  | _    | 105 | 128  | _    | dB    |

| ΔPSRR                        | Power Supply Rejection Ratio<br>Match | $V_{S} = \pm 3V \text{ to } \pm 18V$ | • | 105    | 126  | -    | 98  | 124  | _    | dB    |

For MIL-STD components, please refer to LTC 883C data sheet for test listing and parameters.

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** Offset voltage measured with high speed test equipment, approximately 1second after power is applied.

Note 3: This parameter is tested on a sample basis only.

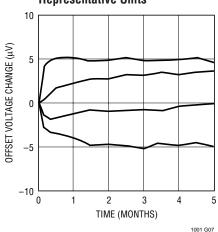

**Note 4:** Long Term Input Offset Voltage Stability refers to the averaged trend line of  $V_{OS}$  versus Time over extended periods after the first 30 days

of operation. Excluding the initial hour of operation, changes in  $V_{OS}$  during the first 30 operating days are typically  $2.5\mu V$ .

Note 5: Parameter is guaranteed by design.

**Note 6:** 10Hz noise voltage density is sample tested on every lot. Devices 100% tested at 10Hz are available on request.

**Note 7:** The V+ supply terminals are completely independent and may be powered by separate supplies if desired (this approach, however, would sacrifice the advantages of the power supply rejection ratio matching). The V- supply terminals are both connected to the common substrate and must be tied to the same voltage. Both V- pins should be used.

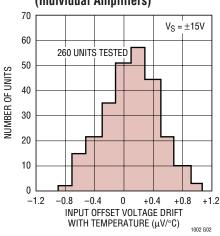

#### Distribution of Offset Voltage Drift with Temperature (Individual Amplifiers)

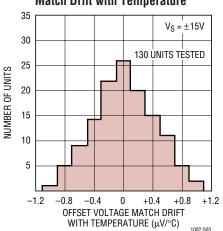

#### Distribution of Offset Voltage Match Drift with Temperature

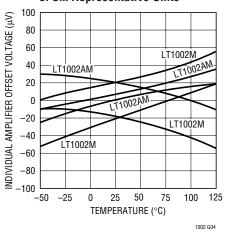

# Offset Voltage Drift with Temperature of Six Representative Units

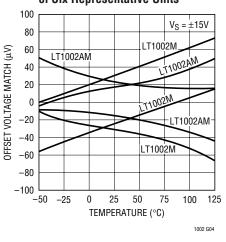

# Offset Voltage Tracking with Temperature of Six Representative Units

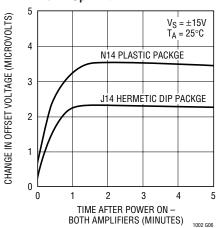

Warm-Up Drift

#### Long Term Stability of Four Representative Units

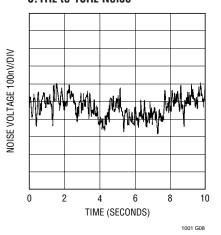

0.1Hz to 10Hz Noise

#### Noise Spectrum

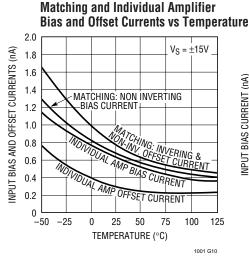

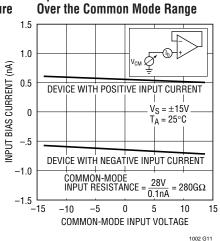

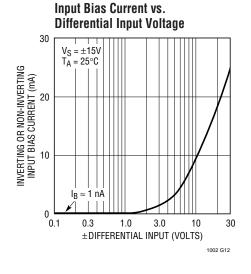

**Input Bias Current**

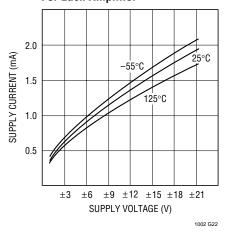

# Supply Current vs. Supply Voltage For Each Amplifier

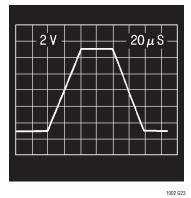

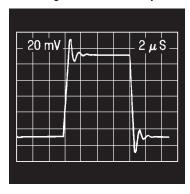

#### **Small Signal Transient Response**

$A_V=+1,\,C_L=50pF$

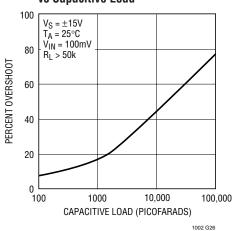

# Voltage Follower Overshoot vs Capacitive Load

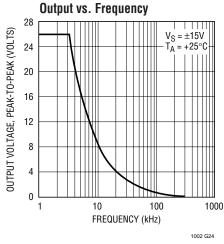

#### **Small Signal Transient Response**

A<sub>V</sub> = +1, C<sub>L</sub> = 1000pF 1002 G27

### APPLICATIONS INFORMATION

The LT1002 dual amplifier may be inserted directly into OP-10, OP207, OP227 sockets with or without removal of external nulling potentiometers.

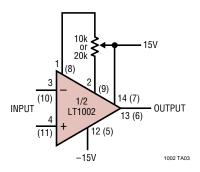

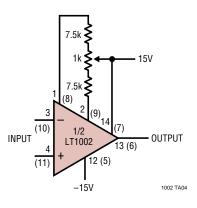

Offset Voltage Adjustment The input offset voltage of the LT1002, and its drift with temperature, are permanently trimmed at wafer testing to a low level. However, if further adjustment of  $V_{OS}$  is necessary, nulling with a 10k or 20k potentiometer will not degrade drift with temperature. Trimming to a value other than zero creates a drift of  $(V_{OS}/300)\mu V/^{\circ}C$ , e.g. if  $V_{OS}$  is adjusted to  $300\mu V$ , the change in drift will be  $1\mu V/^{\circ}C$ . The adjustment range with a 10k or 20k pot is approximately  $\pm 2.5 mV$ . If less adjustment range is needed, the sensitivity and resolution of the nulling can be improved by using a smaller pot in conjunction with fixed resistors. The example has an approximate null range of  $\pm 100\mu V$ .

In matching applications, both amplifiers can be trimmed to zero, or the offset of one amplifier can be trimmed to match the offset of the other. Offset adjustment, however, slightly degrades the gain, common-mode and power-supply rejection match between the two op amps. Fortu-

nately, the guaranteed offset voltage match of the LT1002 is very low, in most applications offset adjustment will be unnecessary.

#### **Standard Adjustment**

**Improved Sensitivity Adjustment**

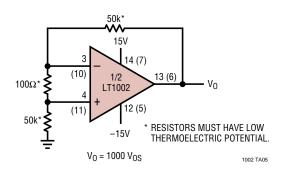

# Test Circuit for Offset Voltage and its Drift with Temperature

This circuit is also used as burn-in configuration for the LT1002, with supply voltages increased to  $\pm 20V$ .

Unless proper care is exercised, thermocouple effects, caused by temperature gradients across dissimilar metals at the contacts to the input terminals, can exceed the inherent drift of the amplifier. Air currents should be minimized, package leads should be short, the two input leads should be as close together as possible and maintained at the same temperature.

## **Channel Separation**

This parameter is defined as the ratio of the change in input offset voltage of one amplifier to the change in output voltage of the other amplifier causing the offset change.

At low frequencies the LT1002's channel separation is an almost unmeasurable 148dB. As frequency increases, pin to pin capacitance of the package, between the output of one amplifier and the inputs of the other, becomes dominant. Since these pins are non-adjacent, the capacitance is only 0.02pF. To maintain the LT1002's excellent channel separation at higher frequencies, the socket and PC board capacitances should be minimized.

The device under test should be warmed up for three minutes and shielded from air currents. Turn the device 180° to measure the noise of side B.

#### **Power supplies**

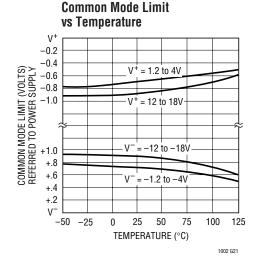

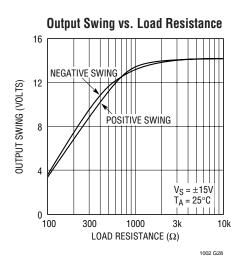

The LT1002 is specified over a wide range of power supply voltages from  $\pm 3V$  to  $\pm 18V$ . Operation with lower supplies is possible, down to  $\pm 1.2V$  (two Ni-Cad batteries). However, with  $\pm 1.2V$  supplies, the device is stable only in closed loop gains of +2 or higher (or inverting gain of one or higher).

The V+ supply terminals are completely independent and may be powered by separate supplies if desired (this approach, however, would sacrifice the advantages of the power supply rejection ratio matching). The V- supply terminals are both connected to the common substrate and must be tied to the same voltage. Both V- pins should be used.

Advantages of Matched Dual Op Amps In many applications the performance of a system depends on the matching between two operational amplifiers rather than the individual characteristics of the two op amps. Two or three op amp instrumentation amplifiers, tracking voltage references and low drift active filters are some of the circuits requiring matching between two op amps.

The well-known triple op amp configuration illustrates these concepts. Output offset is a function of the difference between the offsets of the two halves of the LT1002. This error cancellation principle holds for a considerable number of input referred parameters in addition to offset voltage and its drift with temperature. Input bias current will be the average of the two non-inverting input currents ( $I_{B}^{+}$ ). The difference between these two currents ( $I_{OS}^{+}$ ) is the offset current of the instrumentation amplifier. The difference between the inverting input currents ( $I_{OS}^{-}$ ) will cause errors flowing through R1, R2, and R3. Commonmode and power supply rejections will be dependent only on the match between the two amplifiers (assuming perfect resistor matching).

The concepts of common mode and power supply rejection ratio match ( $\Delta$ CMRR and  $\Delta$ PSRR) are best demonstrated with a numerical example:

Assume CMRR<sub>A</sub> =  $+1.0\mu$ V/V or 120dB, and CMRR<sub>B</sub> =  $+0.75\mu$ V/V or 122.5dB, then  $\Delta$ CMRR =  $0.25\mu$ V/V or 132dB; if CMRR<sub>B</sub> =  $-0.75\mu$ V/V which is still 122.5dB, then  $\Delta$ CMRR =  $1.75\mu$ V/V or 115dB.

Clearly, the LT1002, by specifying and guaranteeing all of these matching parameters, can significantly improve the performance of matching dependent circuits.

Three Op Amp Instrumentation Amplifier

Trim R8 for gain

Trim R9 for DC common mode rejection

Trim R10 for AC common mode rejection

Typical performance of the instrumentation amplifier:

Input offset voltage =  $25\mu V$ Input bias current = 0.7nAInput resistance =  $200~G\Omega$ Input offset current = 0.6nAInput noise =  $0.5\mu V$  p-p Power bandwidth ( $V_0 = \pm 10V$ ) = 80kHz

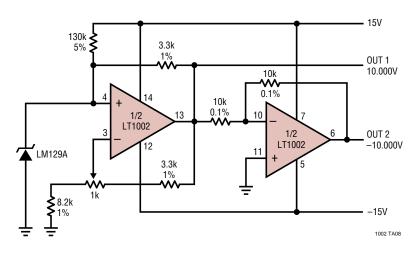

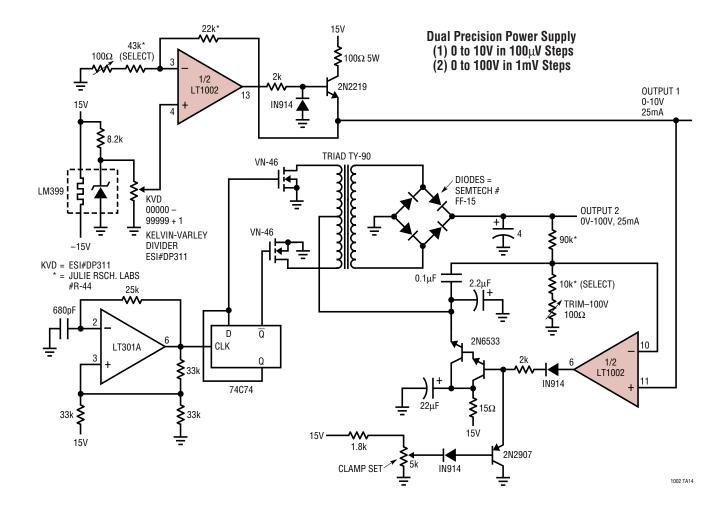

#### Precision ±10V Reference

The LT1002 contributes less than 5% of the total drift with temperature, noise and long term drift of the reference.

The accuracy of the -10V output is limited by the matching of the two 10k resistors.

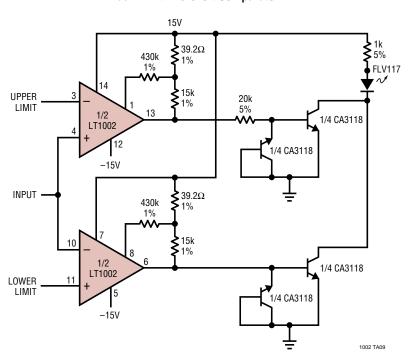

#### **Dual Limit Microvolt Comparator**

When the upper or lower limit is exceeded the LED lights up. Positive feedback to one of the nulling terminals creates 5 to  $20\mu V$  of hysteresis on both amplifiers. This

feedback changes the offset voltage of the LT1002 by less than  $5\mu V$ . Therefore, the basic accuracy of the comparator is limited only by the low offset voltage of the LT1002.

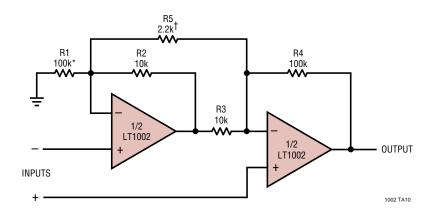

#### Two Op Amp Instrumentation Amplifier

- \* TRIM FOR COMMON-MODE REJECTION

- † TRIM FOR GAIN

$$GAIN = \frac{R4}{R3} \left[ 1 + \frac{1}{2} \left( \frac{R2}{R1} + \frac{R3}{R4} \right) + \frac{R2 + R3}{R5} \right] \approx 100$$

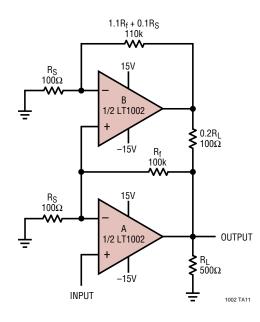

#### Precision Amplifier Drives 500 $\Omega$ Load to $\pm 10V$

This application utilizes the guaranteed 10mA load driving capability of the LT1002. The offset voltage of amplifier A is the offset of the configuration. Amplifier B provides the additional 10mA load current. When load resistor  $R_{\rm L}$  is

removed, amplifier A sinks this current without affecting accuracy. In the gain of 1000 configuration shown, approximately 0.3% gain accuracy can be realized.

LINEAR

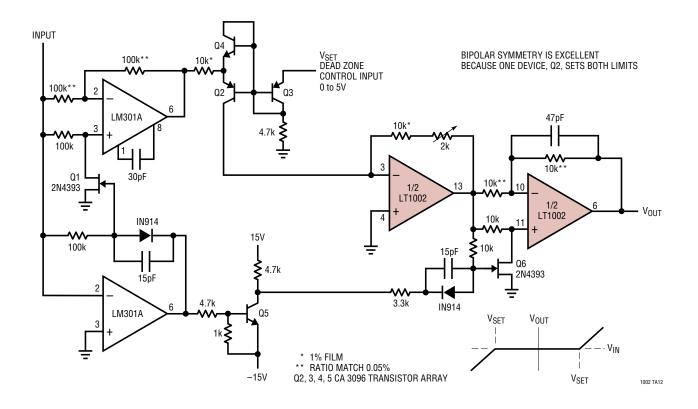

#### **Dead Zone Generator**

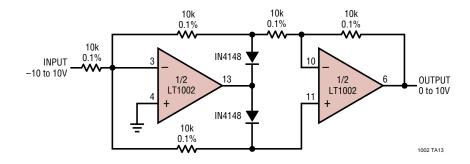

#### **Precision Absolute Value Circuit**

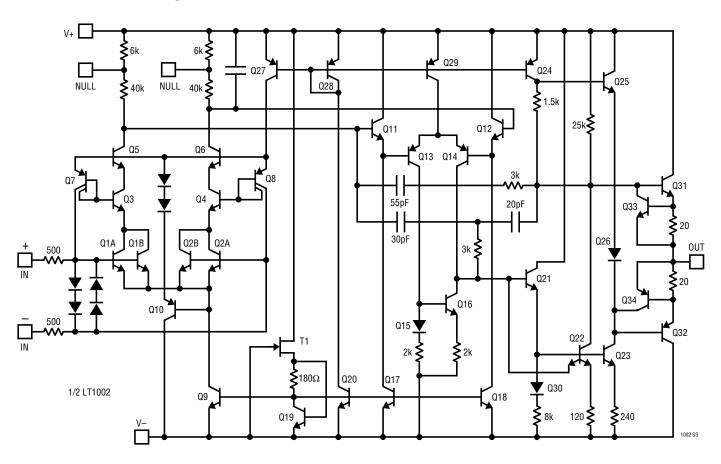

## **SCHEMATIC DIAGRAM**

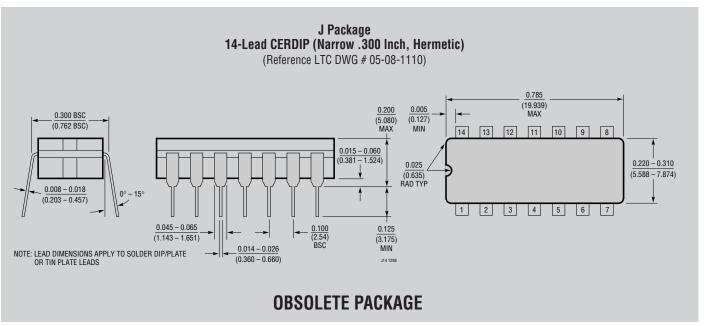

## PACKAGE DESCRIPTION

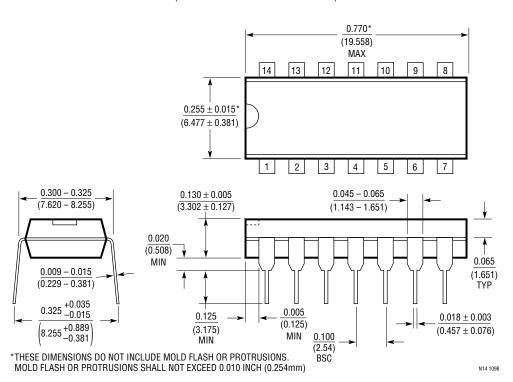

## PACKAGE DESCRIPTION

#### N Package 14-Lead PDIP (Narrow .300 Inch)

(Reference LTC DWG # 05-08-1510)

## **RELATED PARTS**

| PART NUMBER   | DESCRIPTION                                         | COMMENTS                                            |

|---------------|-----------------------------------------------------|-----------------------------------------------------|

| LT1001        | Single LT1002                                       | 60μV V <sub>OS</sub> , 1μV/°C Precision Op Amp      |

| LT1884/LT1885 | Dual/Quad Precision Op Amp with Rail-to-Rail Output | 50μV Max V <sub>OS</sub> , 400pA Max I <sub>B</sub> |