# ISSI<sup>®</sup>

## 262,144 x 8 CMOS FLASH MEMORY

## PRELIMINARY SEPTEMBER 1995

## **FEATURES**

- High performance

- 70 ns maximum access time

- CMOS low power consumption

- 30 mA maximum active current

- 100 µA maximum standby current

- Compatible with JEDEC-standard byte-wide pinouts

- 32-pin DIP

- 32-pin PLCC

- 32-pin TSOP

- Program and erase voltage 12.0V ± 5%

- Maximum latch-up immunity through advanced CMOS process

- · Flash electrical bulk chip-erase

- One second typical chip-erase

- · Fast-pulse programming algorithm

- 10 μs (typical) byte-program

- 4 second chip-program

- Command register architecture for microprocessor/microcontroller compatible write interface

- On-chip address and data latches for programming

- Advanced CMOS flash memory technology

- Low cost single transistor memory cell

- · Integrated program/erase stop timer

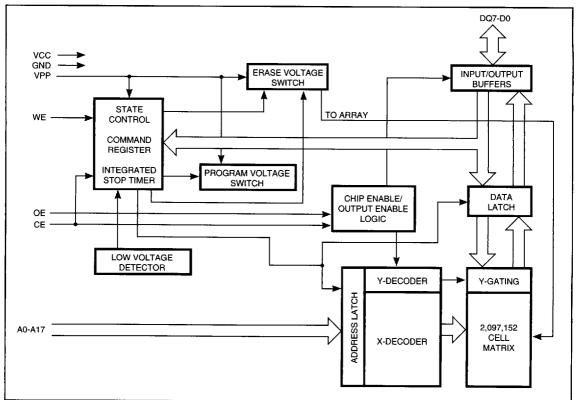

## **BLOCK DIAGRAM**

This document contains preliminary data. ISSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any errors which may appear in this publication. © Copyright 1995, Integrated Silicon Solution, Inc.

### DESCRIPTION

The ISSI IS28F020 is a high-speed, low-power,262,144 bytes of eight bits CMOS flash memory. It offers the most cost-effective and reliable alternative for read/write nonvolatile RAM.

The IS28F020 adds electrical chip-erasure and reprogramming to familiar EPROM technology. Memory contents can be rewritten in a test socket; PROM-programmer socket; onboard during subassembly test; in-system during final test; and in-system after-sale. Finally, the highest degree of latch-up protection is achieved with special layout. Prevention of latch-up is provided for stresses up to 100 mA on address and data pins from -1V to Vcc + 1V.

The IS28F020 is available in 32-pin DIP, 32-lead PLCC and 32-pin TSOP packages. Pin assignments conform to JEDEC standards for byte-wide EPROMS.

## PIN DESCRIPTIONS

| A0-A17  | Address Inputs         |  |  |  |

|---------|------------------------|--|--|--|

| DQ0-DQ7 | Data Inputs/Outputs    |  |  |  |

| CE (E)  | Chip Enable Input      |  |  |  |

| ŌĒ (G)  | Output Enable Input    |  |  |  |

| WE (W)  | Write Enable Input     |  |  |  |

| Vcc     | Power Supply Voltage   |  |  |  |

| VPP     | Program Supply Voltage |  |  |  |

| GND     | Ground                 |  |  |  |

| NC      | No Internal Connection |  |  |  |

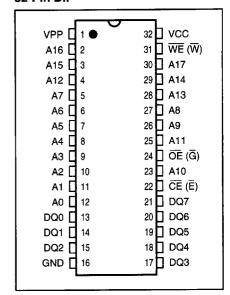

## PIN CONFIGURATIONS 32-Pin DIP

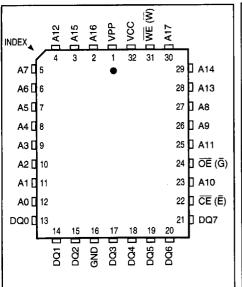

## 32-Pin PLCC

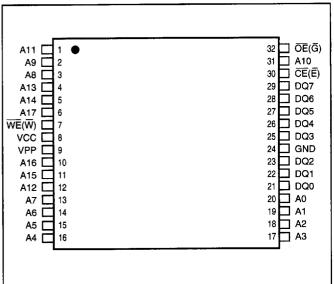

### 32-Pin TSOP

## PRINCIPLES OF OPERATION

ISSI's IS28F020 flash memory augments EPROM functionality with in-circuit electrical erasure and reprogramming. The IS28F020 uses a command register to manage this functionality. The command register allows for 100% TTL-level control inputs and fixed power supply levels during erasure and programming, while maintaining maximum EPROM compatibility.

With the Vpp pin at a low voltage level, the IS28F020 is a read-only memory. With the Vpp pin at a high voltage level, the same EPROM read, standby, and output disable operations are available along with enabling erasure and programming operations. All functions associated with altering memory contents—ISSI identifier, erase, erase verify, program, and program verify—are accessed via the command register.

Command codes are written to the command register using standard microprocessor write timings. Contents of the command register serve as instruction codes input to an internal state-machine which controls the erase and programming circuitry. With the appropriate command codes written to the register, standard microprocessor read timings may output array data, access the ISSI identifier codes, or output data for erase and program verification. Table 2 defines these IS28F020 command codes.

## **Integrated Stop Timer**

The program or erase time durations are normally terminated by associated program or erase verify commands. An integrated stop timer provides simplified timing control over these operations; thus eliminating the need for maximum program/erase timing specifications. Programming and erase pulse durations are minimums only. When the stop timer terminates a program or erase operation, the device enters an inactive state and remains inactive until receiving the appropriate verify or reset command.

#### Write Protection

The IS28F020 uses a two-step program/erase write sequence to the command register which provides additional software write protections. The command register is active when VPP = VPPH. When VPP = VPPH, the contents of the command register default to 00H, making the IS28F020 a read-only memory. The system designer may choose to make the VPP power-supply switchable or to "hardwire" VPP = VPPH. The IS28F020 is designed to accommodate either design practice, and to encourage optimization of the processor-memory interface.

### BUS OPERATIONS

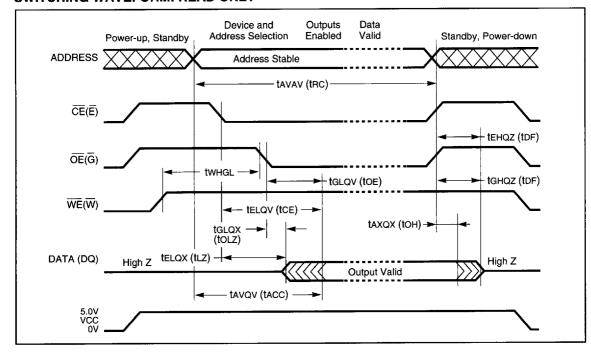

#### Read

The IS28F020 has  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  control signals. To obtain data at the output, both control signals must be brought low. Chip-Enable ( $\overline{\text{CE}}$ ) is used for device selection. Ouput-Enable ( $\overline{\text{OE}}$ ) is used to gate data from the output pins, when the device is selected by asserting  $\overline{\text{CE}}$  LOW. Refer to AC read timing waveforms.

When VPP is HIGH (VPPH), the read operation can be used to access array data, to output the ISSI identifier codes, and to access data for program/erase verification. When VPP is LOW (VPPL), the read operation can only access the array data.

## **Output Disable**

When  $\overline{OE}$  is HIGH (ViH), device output is disabled. The output pins are placed in a high-impedance state.

## Standby

When  $\overline{CE}$  is HIGH, the standby operation disables most of the IS28F020's circuitry and substantially reduces device power consumption. The outputs are placed in a high-impedance state, independent of the Output Enable signal. If the IS28F020 is deselected during erasure, programming, or program/erase verification, the device draws active current until the operation is terminated.

#### **ISSI Identifier Operation**

The ISSI identifier operation outputs the manufacturer code (D5H) and device code (B4H). Programming equipment automatically matches the device with its proper erase and programming algorithms.

With  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  both LOW, raising A9 to high voltage, V<sub>ID</sub> activates the ISSI identifier operation. Data read from locations 0000H and 0001H represent the manufacturer's code and the device code, respectively.

The manufacturer code and device code can also be read via the command register, for example, when the IS28F020 is erased and reprogrammed in the target system. Following a write of 90H to the command register, a read from address location 0000H outputs the manufacturer code (D5H). A read from address 0001H outputs the device code (B4H).

TABLE 1. IS28F020 BUS OPERATIONS(1)

|            |                        |                |    |                            | Pins |    |    |             |

|------------|------------------------|----------------|----|----------------------------|------|----|----|-------------|

|            | Operation              | $V_{PP^{(2)}}$ | A0 | A9                         | CE   | OE | WE | DQ0-DQ7     |

| READ-ONLY  | Read                   | VPPL           | Α0 | A9                         | L    | L  | Н  | Data Out    |

|            | Output Disable         | VPPL           | Х  | Х                          | L    | Н  | Н  | Tri-State   |

|            | Standby                | VPPL           | Х  | Х                          | Н    | Х  | X  | Tri-State   |

|            | ISSI Identifier Mfr    | VPPL           | L  | $V_{ID^{(3)}}$             | Ĺ    | L  | Н  | Data = D5H  |

|            | ISSI Identifier Device | VPPL           | Н  | <b>V</b> ID <sup>(3)</sup> | L    | L  | Н  | Data = B4H  |

| READ/WRITE | Read                   | VPPH           | A0 | A9                         | L    | L  | Н  | Data Out(4) |

|            | Output Disable         | VPPH           | X  | Х                          | L    | Н  | Н  | Tri-State   |

|            | Standby                | Vppн           | Х  | Х                          | Н    | Х  | Х  | Tri-State   |

|            | Write                  | Vpph           | A0 | <b>A</b> 9                 | L    | Н  | L  | Data In(5)  |

### NOTES:

- 1. L = VIL; H = VIH; X = Don't Care

- 2. Refer to DC Characteristics.

- 3. VID is the ISSI identifier high voltage. Refer to DC Characteristics.

- 4. Read operations with VPP=VPPH may access array data or the ISSI identifier codes.

- 5. Refer to Table 2 for valid Data-In during a write operation.

## **TABLE 2. COMMAND DEFINITIONS**

|                                         | Bus<br>Cycles | F            | irstBusCycl | e                   | Se                       | condBusCy              | cle        |

|-----------------------------------------|---------------|--------------|-------------|---------------------|--------------------------|------------------------|------------|

| Command                                 | Req'd         | Operation(1) | Address(2)  | Data <sup>(2)</sup> | Operation <sup>(1)</sup> | Address <sup>(2)</sup> | Data(2     |

| Read Memory                             | 1             | Write        | Х           | 00H                 |                          |                        |            |

| Read ISSI Identifier<br>Codes (Mrf/Dev) | 3             | Write        | Х           | 90H                 | Read                     | 0000H<br>0001H         | D5H<br>B4H |

| Setup Erase/Erase                       | 2             | Write        | Χ           | 20H                 | Write                    | Х                      | 20H        |

| Erase Verify                            | 2             | Write        | EA          | A0H                 | Read                     | Х                      | EVD        |

| Setup Program/Program                   | 2             | Write        | Х           | 40H                 | Write                    | PA                     | PD         |

| Program Verify                          | 2             | Write        | Х           | C0H                 | Read                     | Х                      | PVD        |

| Reset                                   | 2             | Write        | Х           | FFH                 | Write                    | Х                      | FFH        |

#### NOTES:

- 1. Bus operations are defined in Table 1.

- 2. EA = Address of memory location to be read during erase verify.

- PA = Address of memory location to be programmed.

- EVD = Data read from location EA during erase verify.

- PD = Data to be programmed at location PA. Data is latched on the rising edge of Write-Enable.

- PVD = Data read from location PA during program verify. PA is latched on the program command.

## 6

#### Write

With the VPP pin at high voltage level, device erasure and programming are accomplished via the command register. The contents of the command register serve as input to the internal state-machine. The state-machine outputs dictate the function of the device.

The command register itself does not occupy an addressable memory location. The register is a latch used to store the command, along with address and data information needed to execute the command.

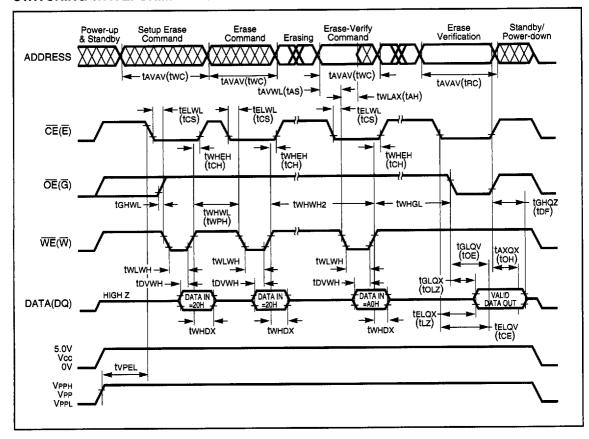

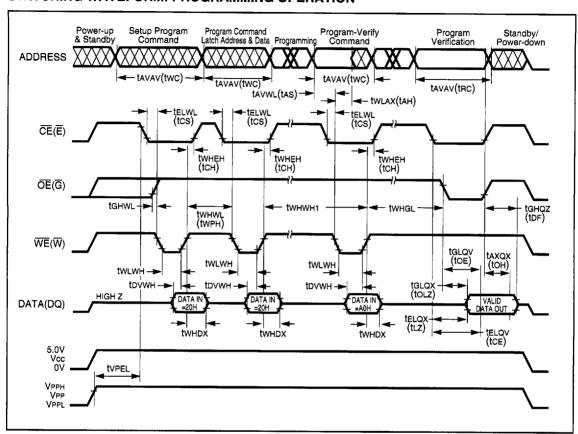

The command register is written by bringing low (VIL), while is LOW. Addresses are latched on the falling edge of while data is latched on the rising edge of the pulse. Standard microprocessor write timings are used. Refer to AC Write Characteristics and the Erase/Programming Waveforms for specific timing parameters.

### **COMMAND DEFINITIONS**

With the VPP pin at the low voltage level, the contents of the command register default to 00H, enabling read-only operations. With the VPP pin at high voltage, enabling read/write operations. Device operations are selected by writing specific command codes to the command register. Table 2 defines these IS28F020 register commands.

#### Read Command (00H)

While VPP = VPPH, for erasure and programming, memory contents can be accessed via the read command. The read operation is initiated by writing 00H to the command register. Standard microprocessor read cycles retrieve array data. The device remains enabled for reads until the command register contents are altered.

Upon VPP power-up, the default value of the command register is 00H. This default value ensures that no spurious alteration of memory contents occurs during the VPP power transition. Where the VPP supply is hard-wired to the IS28F020, the device powers-up and remains enabled for reads until the command-register content is changed. Refer to the AC Read Characteristics and Waveforms for specific timing parameters.

## ISSI Identifier Command (90H)

The ISSI's IS28F020 flash memory is intended for use in applications where the local CPU alters memory contents. As such, manufacturer- and device-codes must be accessible while the device resides in the target system.

The IS28F020 contains an ISSI identifier operation to supplement traditional PROM-programming methods. This operation is initiated by writing 90H to the command register. Following the command write, a read cycle from address 0000H retrieves the manufacturer code of D5H. A read cycle from address 0001H returns the device code of B4H. To terminate the operation, it is necessary to write another valid command to the register.

## Setup Erase/Erase Commands (20H/20H)

Two-step sequence of setup erase operation followed by erase operation ensures that the memory content is not accidentally erased.

The setup erase operation is initiated by writing 20H to the command register. Setup erase is a command-only operation that instructs the device for electrical erasure of all bytes in the array.

The erase command (20H) must again be written to the register. The erase command erases all bytes of the array in parallel. The erase operation begins with the rising edge of the Write-Enable pulse and terminates with the rising edge of the next Write-Enable pulse (i.e., Erase-Verify Command). Refer to AC Erase Characteristics and Waveforms for specific timing parameters.

## **Erase-Verify Command (A0H)**

After each erase operation, all bytes must be verified. The erase-verify operation is initiated by writing A0H into the command register prior to each byte verification to latch its address. The address for the byte to be verified must be ready as it is latched on the falling edge of the Write-Enable control signal. The IS28F020 applies an internally-generated margin voltage to the addressed byte. Reading FFH from the addressed byte indicates that all bits in the byte are erased. The process continues for each byte in the array until a byte does not return data FFH , or the last address is accessed.

In the case where the data read is not FFH, user should perform another erase operation. (Refer to Setup Erase/Erase). Then verification can resume from the address of the last verified byte. Once all bytes in the array have been verified, the erase step is complete. The device can be reprogrammed. At this point, the verify operation is terminated by writing a valid command (e.g., Program Setup) to the command register. Figure 2, the Fast-Erase algorithm, illustrates how commands and bus operations are combined to perform electrical erasure of the IS28F020. Refer to AC Erase Characteristics and Waveforms for specific timing parameters.

## Setup Program/Program Commands (40H)

The setup program operation is initiated by writing 40H to the command register. It is a command-only operation that instructs the device for byte programming. Once the setup program operation is performed, the next Write-Enable pulse causes a transition to an active programming operation. Addresses are internally latched on the falling edge of the Write-Enable pulse. Data is internally latched on the rising edge of Write-Enable pulse. The rising edge of Write-Enable also begins the programming operation. The IS28F020 is programmed on a byte-by-byte basis. Byte programming may occur sequentially or at random. The programming operation terminates with the next rising edge of Write-Enable that used to write the program-verify command. Refer to AC Programming Characteristics and Waveforms for specific timing parameters.

## **Program-Verify Command (C0H)**

Following each programming operation, the byte just programmed must be verified.

The program-verify operation is initiated by writing C0H to the command register. It instructs the device for verification of the byte last programmed. The IS28F020 applies an internally-generated margin voltage to the byte. A standard microprocessor read cycle may output the data. If a comparison between the programmed byte and the true data is successful, programming then proceeds to the next desired byte location. Figure 1, the IS28F020 Fast-Pulse programming algorithm, illustrates how commands are combined with bus operations to perform byte programming. Refer to AC Programming Characteristics and Waveforms for specific timing parameters.

### Reset Command (FFH)

A reset command is used to abort the erase- or programcommand sequences safely. Following either setup erase operation or setup program operation with two consecutive writes of FFH will safely abort the operation. Memory contents will not be altered. A valid command must then be written to place the device in the desired state.

## **ERASE/PROGRAM CYCLING**

The IS28F020 is programmed and erased using ISSI's Fast-Pulse programming and Fast-Erase algorithms. The algorithmic approach uses a series of pulses, along with byte verification, to completely and reliably erase and program the device.

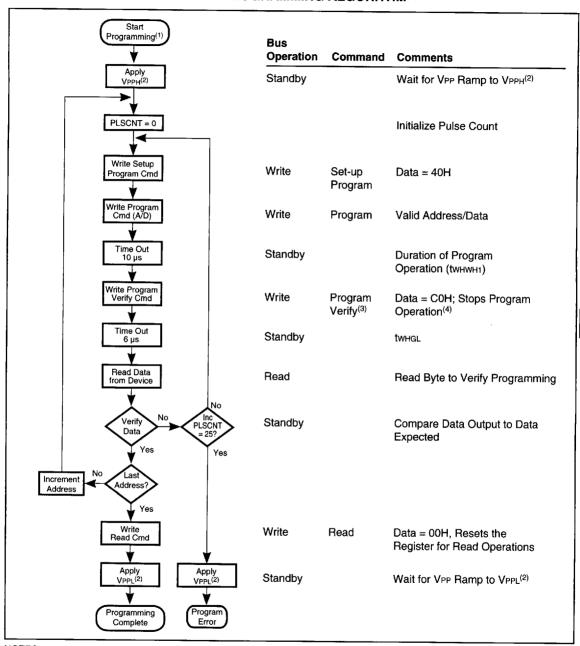

## **FAST-PULSE PROGRAMMING ALGORITHM**

The IS28F020 is programmed on a byte-by-byte basis using 10 µs duration programming pulse in accordance with ISSI's Fast-Pulse programming algorithm. Each operation is followed by a byte verification to determine when the addressed byte has been successfully programmed. The algorithm allows for up to 25 programming operations per byte, although most bytes verify on the first or second operation. The entire sequence of programming and byte verification is performed with VPP at high voltage. Figure 1 illustrates the Fast-Pulse Programming algorithm.

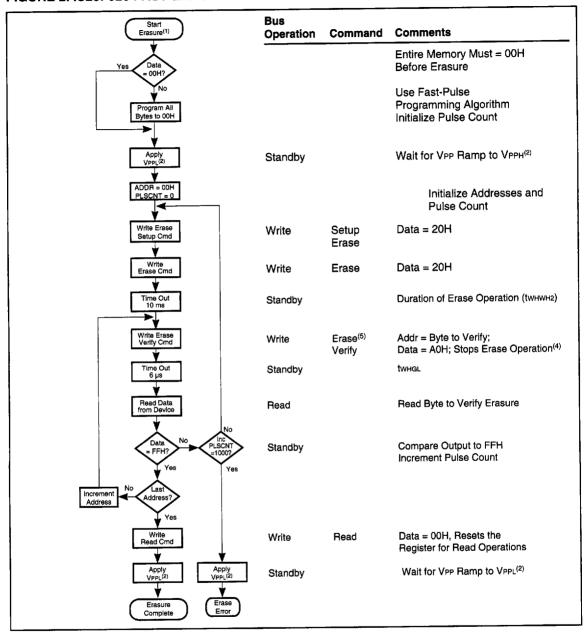

## **FAST-ERASE ALGORITHM**

The erase operation erases all bytes of the array in parallel. The entire device is bulk erased using 10 ms duration erase pulse in accordance with ISSI's Fast-Erase algorithm. The Fast-Erase algorithm yields fast and reliable electrical erasure of memory contents. The algorithm employs a Fowler-Nordheim tunneling to simultaneously remove charge from all bits in the array.

Erasure begins with a read of memory contents. The IS28F020 is erased when shipped from the factory. Reading FFH data from the device would immediately be followed by device programming.

For devices being erased and reprogrammed, uniform and reliable erasure is ensured by first programming all bits in the device to their charged state (Data=00H). This is accomplished, using the Fast-Pulse Programming algorithm, in approximately two seconds.

Erase execution then continues with an initial erase operation. Erase verification (Data=FFH) begins at address 0000H and continues through the array to the last address, or until data other than FFH is encountered. With each erase operation, an increasing number of bytes verify to the erased state. Erase efficiency may be improved by storing the address of the last byte verified in a register. Following the next erase operation, verification starts at that stored address location. Erasure typically occurs in one second. Figure 2 illustrates the Fast-Erase algorithm.

## FIGURE 1. IS28F020 FAST-PULSE PROGRAMMING ALGORITHM(1)

## NOTES:

- 1. The algorithm MUST BE FOLLOWED to ensure proper and reliable operation of the device.

- 2. See DC Characteristics for the value of VPPH and VPPL.

- Program Verify is only performed after byte programming. A final read/compare may be performed (optional) after the register is written with the Read command.

- 4. Refer to principles of operation.

## FIGURE 2. IS28F020 FAST-ERASE ALGORITHM(1)

#### NOTES:

- 1. The algorithm MUST BE FOLLOWED to ensure proper and reliable operation of the device.

- 2. See DC Characteristics for the value of VPPH and VPPL.

- 3. Program Verify is only performed after byte programming. A final read/compare may be performed (optional) after the register is written with the Read command.

- 4. Refer to principles of operation.

- 5. Erase Verify is performed only after chip-erasure. A final read/compare may be performed (optional) after the register is written with the Read command.

## **ABSOLUTE MAXIMUM RATINGS(1)**

| Symbol | Parameter                            | Value                     | Unit |  |

|--------|--------------------------------------|---------------------------|------|--|

| VTERM  | Terminal Voltage with Respect to GND |                           |      |  |

|        | During Erase/Program                 | $-2.0$ to $+14.0^{(2.3)}$ | V    |  |

|        | Any Pin                              | $-2.0$ to $+7.0^{(3)}$    | V    |  |

|        | A9                                   | $-2.0$ to $+13.5^{(2.3)}$ | V    |  |

|        | Vcc                                  | $-2.0$ to $+7.0^{(2)}$    | V    |  |

| TA     | Commercial Operating Temperature     |                           |      |  |

|        | During Read                          | 0 to +70                  | °C   |  |

|        | During Read                          | 0 to +70                  | °C   |  |

| TA     | Industrial Operating Temperature     |                           |      |  |

|        | During Read                          | -40 to +85                | °C   |  |

|        | During Read                          | -40 to +85                | °C   |  |

| TBIAS  | Temperature Under Bias               | -10 to +80                | °C   |  |

| Tstg   | Storage Temperature                  | -65 to +125               | °C   |  |

#### Notes:

- Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the

device. This is a stress rating only and functional operation of the device at these or any other conditions above

those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum

rating conditions for extended periods may affect reliability.

- Minimum DC input voltage is -0.5V. During transitions, inputs may undershoot to -2.0V for periods less than 10 ns. Maximum DC voltage on output pins is Vcc + 0.5V, which may overshoot to Vcc + 2.0V for periods less than 10 ns.

- 3. Maximum DC voltage on A9 or VPP may overshoot to +14.0V for periods less than 20 ns.

- 4. No more than one output shorted at one time. Duration of short shall not exceed one second.

## **OPERATING RANGE**

| Range         | Ambient Temperature | Vcc      |

|---------------|---------------------|----------|

| Commercial    | 0°C to +70°C        | 5V ± 10% |

| Industrial(1) | -40°C to +85°C      | 5V ± 10% |

### Note:

Operating ranges define those limits between which the functionally of the device is guaranteed.

## **CAPACITANCE**

| Symbol | Parameter          | Conditions | Тур. | Max. | Unit |

|--------|--------------------|------------|------|------|------|

| CIN    | Input Capacitance  | Vin = 0V   | _    | 6    | pF   |

| Соит   | Output Capacitance | Vout = 0V  | _    | 12   | pF   |

## DC CHARACTERISTICS: TTL/NMOS COMPATIBLE

| Symbol | Parameter Description              | Test Conditions                                                 |              | Min.        | Max.       | Unit       |

|--------|------------------------------------|-----------------------------------------------------------------|--------------|-------------|------------|------------|

| lu     | Input Leakage Current              | Vcc = Vcc Max.,<br>Vin = Vcc or GND                             |              | _           | ±1.0       | μА         |

| lLO    | Output Leakage Current             | Vcc = Vcc Max.,<br>Vout = Vcc or GND                            |              | <del></del> | ±10        | μ <b>A</b> |

| Iccs   | Vcc Standby Current                | Vcc = Vcc Max., CE = Vін                                        |              |             | 1.0        | mΑ         |

| loc1   | Vcc Active Read Current            | Vcc = Vcc Max., CE = Vi∟, OE :<br>lout = 0 mA, at 6 MHz         | = ViH        | _           | 30         | mA         |

| lcc2   | Vcc Programming Current            | CE = Vı∟<br>Programming in Process                              | Com.<br>Ind. |             | 10<br>30   | mA         |

| lcc3   | Vcc Erase Current                  | CE = VIL<br>Erasure in Process                                  | Com.<br>Ind. | _           | 15<br>30   | mA         |

| Icc4   | Vcc Program Verify Current         | VPP = VPPH<br>Program Verify in Process                         | Com.<br>Ind. | _           | 15<br>30   | mA         |

| lcc5   | Vcc Erase Verify Current           | VPP = VPPH<br>Erase Verify in Process                           | Com.<br>Ind. | _           | 15<br>30   | mA         |

| IPPS   | VPP Leakage Current                | VPP ≤ VCC                                                       |              | · —         | ±10        | μΑ         |

| ÎPP1   | VPP Read Current                   | VPP > VCC<br>VPP ≤ VCC                                          |              | _           | 200<br>±10 | μΑ         |

| IPP2   | VPP Programming Current            | Vpp = Vppн<br>Programming in Process                            |              | _           | 30         | mA         |

| IPP3   | VPP Erase Current                  | V <sub>PP</sub> = V <sub>PPH</sub><br>Erasure in Process        |              | _           | 30         | mA         |

| IPP4   | VPP Program Verify Current         | V <sub>PP</sub> = V <sub>PPH</sub><br>Program Verify in Process |              | _           | 5.0        | mA         |

| IPP5   | VPP Erase Verify Current           | V <sub>PP</sub> = V <sub>PPH</sub><br>Erase Verify in Process   |              | _           | 5.0        | mA         |

| VIL    | Input Low Voltage                  |                                                                 |              | -0.5        | 0.8        | V          |

| Vін    | Input High Voltage                 |                                                                 |              | 2.0         | Vcc + 0.5  | V          |

| Vol    | Output Low Voltage                 | lot = 5.8 mA, Vcc = Vcc Min.                                    |              |             | 0.45       | ٧          |

| Von1   | Output High Voltage                | IOH = -2.5  mA, $VCC = VCC  Min$ .                              |              | 2.4         |            | ٧          |

| VID    | A9 Auto Select Voltage             | A9 = Vid                                                        |              | 11.5        | 13.0       | V          |

| lib    | A9 Auto Select Current             | A9 = Vid Max., Vcc = Vcc Max.                                   |              |             | 200        | μΑ         |

| VPPL   | VPP During Read-Only<br>Operations | Note: Erase/Program are inhibited when VPP = VPPL               |              | 0.0         | Vcc + 2.0  | V          |

| VPPH   | VPP During Read/Write Operations   |                                                                 |              | 11.4        | 12.6       | ٧          |

| VLKO   | Vcc Erase/Write Lock Voltage       |                                                                 |              | 2.5         |            | ٧          |

## DC CHARACTERISTICS: CMOS COMPATIBLE

| Symbol | Parameter Description              | Test Conditions                                        | - <u>-</u>   | Min.     | Max.      | Unit |

|--------|------------------------------------|--------------------------------------------------------|--------------|----------|-----------|------|

| lu     | Input Leakage Current              | Vcc = Vcc Max.,<br>Vin = Vcc or GND                    |              | _        | ±1.0      | μΑ   |

| ILO    | Output Leakage Current             | Vcc = Vcc Max.,<br>Vout = Vcc or GND                   |              | _        | ±10       | μΑ   |

| lccs   | Vcc Standby Current                | Vcc = Vcc Max., CE = Vcc ± 0.                          | 2V           | _        | 100       | μΑ   |

| lcc1   | Vcc Active Read Current            | Vcc = Vcc Max., CE = Vil., OE<br>lout = 0 mA, at 6 MHz | = ViH        |          | 30        | mA   |

| lcc2   | Vcc Programming Current            | CE = VIL<br>Programming in Process                     | Com.<br>Ind. | _        | 15<br>30  | mA   |

| lcc3   | Vcc Erase Current                  | CE = V <sub>IL</sub><br>Erasure in Process             | Com.<br>Ind. | _        | 15<br>30  | mA   |

| lcc4   | Vcc Program Verify Current         | Vpp = Vppн<br>Program Verify in Process                | Com.<br>Ind. | _        | 15<br>30  | mA   |

| lcc5   | Vcc Erase Verify Current           | VPP = VPPH<br>Erase Verify in Process                  | Com.<br>Ind. | _        | 15<br>30  | mA   |

| IPPS   | VPP Leakage Current                | VPP ≤ VCC                                              |              | _        | ±10       | μΑ   |

| IPP1   | VPP Read Current                   | VPP > VCC                                              |              | _        | 200       | μA   |

| IPP2   | VPP Programming Current            | VPP = VPPH Programming in Process                      |              | ****     | 30        | mA   |

| IPP3   | VPP Erase Current                  | VPP = VPPH<br>Erasure in Process                       |              | _        | 30        | mA   |

| IPP4   | VPP Program Verify Current         | Vpp = Vppн<br>Program Verify in Process                |              | _        | 5.0       | mA   |

| İPP5   | VPP Erase Verify Current           | VPP = VPPH Erase Verify in Process                     |              |          | 5.0       | mA   |

| Vil    | Input Low Voltage                  |                                                        |              | -0.5     | 0.8       | ٧    |

| ViH    | Input High Voltage                 |                                                        |              | 0.7Vcc   | Vcc + 0.5 | ٧    |

| Vol    | Output Low Voltage                 | IoL = 5.8 mA, Vcc = Vcc Min.                           |              | _        | 0.45      | ٧    |

| Voн1   | Output High Voltage                | Ioн = -2.5 mA, Vcc = Vcc Min.                          |              | 0.85 x V | :c —      | ٧    |

| Voн1   | Output High Voltage                | loн = −100 μA, Vcc = Vcc Min.                          |              | Vcc - 0. | 4 —       | ٧    |

| VID    | A9 Auto Select Voltage             | A9 = VID                                               |              | 11.5     | 13.0      | ٧    |

| ID     | A9 Auto Select Current             | A9 = Vid Max., Vcc = Vcc Max.                          |              |          | 200       | μА   |

| VPPL   | VPP During Read-Only<br>Operations | Note: Erase/Program are inhibited when VPP = VPPL      |              | 0.0      | Vcc + 2.0 | ٧    |

| VPPH   | VPP During Read/Write Operations   |                                                        |              | 11.4     | 12.6      | ٧    |

| VLKO   | Vcc Erase/Write Lock Voltage       |                                                        |              | 2.5      | _         | ٧    |

## SWITCHING CHARACTERISTICS(1): READ ONLY (Over Operating Range)

| JEDEC         | Std.   |                                                    | -7   | 70   | -(   | 90   | -1   | 20   |      |

|---------------|--------|----------------------------------------------------|------|------|------|------|------|------|------|

| Symbol        | Symbol | Parameter                                          | Min. | Max. | Min. | Max. | Min. | Max. | Unit |

| tavav         | trc    | Read Cycle Time                                    | 70   | _    | 90   | _    | 120  |      | ns   |

| telov         | tce    | Chip Enable Access Time                            | _    | 70   | _    | 90   | _    | 120  | ns   |

| tavqv         | tacc   | Address Access Time                                | _    | 70   | _    | 90   | _    | 120  | ns   |

| tglav         | toe    | Output Enable Access Time                          | _    | 28   |      | 35   | _    | 50   | ns   |

| telox         | tız    | Chip Enable to Output in Low Z                     | 0    | _    | 0    | _    | 0    | _    | ns   |

| <b>t</b> EHQZ | tor    | Chip Disable to Output in High Z                   | _    | 35   |      | 45   | _    | 50   | ns   |

| tglax         | toLz   | Output Enable to Output in Low Z                   | 0    | _    | 0    | _    | 0    | _    | ns   |

| tghoz         | tor    | Output Disable to Output in High Z                 | _    | 30   | _    | 30   | -    | - 30 | ns   |

| taxqx         | tон    | Output Hold from First of Address, CE or OE Change | 0    | _    | 0    | _    | 0    | _    | ns   |

| twhgL         |        | Write Recovery Time before Read                    | 6    |      | 6    |      | 6    | _    | μs   |

#### Notes:

## **SWITCHING WAVEFORM: READ ONLY**

Output load: 1 TTL Gate and C<sub>L</sub> = 30 pF, input Rise and Fall times: ≤ 10 ns, input pulse levels: 0 to 3 V, timing measurement reference level: Inputs: 1.5V

Outputs: 1.5V

## 6

## SWITCHING CHARACTERISTICS: WRITE/ERASE PROGRAM(1) (Over Operating Range)

| JEDEC  | Std.        |                                      | -    | 70   | .(   | 90   | -1   | 20   |      |

|--------|-------------|--------------------------------------|------|------|------|------|------|------|------|

| Symbol | Symbol      | Parameter                            | Min. | Max. | Min. | Max. | Min. | Max. | Unit |

| tavav  | twc         | Write Cycle Time                     | 70   | _    | 90   | _    | 120  | _    | ns   |

| tavwl  | tas         | Addess Setup Time                    | 0    | _    | 0    | _    | 0    | _    | ns   |

| twlax  | tah         | Address Hold Time                    | 40   | _    | 40   | _    | 40   |      | ns   |

| tovwh  | tos         | Data Setup Time                      | 40   | _    | 40   | _    | 40   |      | ns   |

| twnox  | tон         | Data Hold Time                       | 10   | _    | 10   | _    | 10   |      | ns   |

| twngl  | twn         | Write Recovery Time before Read      | 6    | _    | 6    |      | 6    |      | μs   |

| tghwl  |             | Read Recovery Time before Write      | 0    | _    | 0    | _    | 0    | _    | μs   |

| termr  | tcs         | Chip Enable Setup Time before Write  | 15   | _    | 15   |      | 15   | _    | ns   |

| twhen  | <b>t</b> CH | Chip Enable Hold Time                | 0    | _    | 0    | _    | 0    |      | ns   |

| twlwh  | twp         | Write Pulse Width                    | 40   |      | 40   | _    | 60   | _    | ns   |

| twhwL  | twpH        | Write Pulse Width HIGH               | 20   |      | 20   | _    | 20   | _    | ns   |

| twnw+1 |             | Duration of Programming Operation(2) | 10   |      | 10   | _    | 10   |      | μs   |

| twhwh2 |             | Duration of Erase Operation(2)       | 9.5  | _    | 9.5  | _    | 9.5  | _    | ms   |

| tvpel  |             | VPP Setup Time to Chip Enable LOW    | 1.0  |      | 1.0  | _    | 1.0  | _    | μs   |

### Notes:

Read timing characteristics during read/write operations are the same as during read-only operations. Refer to AC Characteristics for Read Only operations.

<sup>2.</sup> The integrated stop timer terminates the programming/erase operations, thereby eliminating the need for a maximum specification.

## **SWITCHING WAVEFORM: ERASE OPERATION**

## SWITCHING WAVEFORM: PROGRAMMING OPERATION

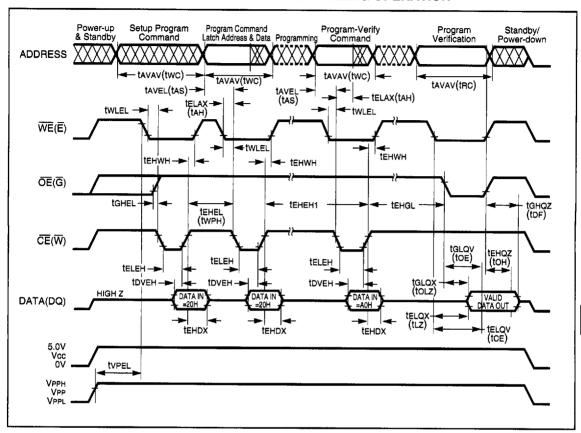

## SWITCHING CHARACTERISTICS: ALTERNATIVE CE-CONTROLLED WRITES(1) (Over Operating Range)

| JEDEC Std.    |             |                                            | -70  |      | -90  |      | -120 |      |      |  |

|---------------|-------------|--------------------------------------------|------|------|------|------|------|------|------|--|

| Symbol        | Symbol      | Parameter                                  | Min. | Max. | Min. | Max. | Min. | Max. | Unit |  |

| tavav         | twc         | Write Cycle Time                           | 70   | _    | 90   | _    | 120  | -    | ns   |  |

| tavel         | tas         | Addess Setup Time                          | 0    | _    | 0    | _    | 0    |      | ns   |  |

| <b>t</b> ELAX | <b>t</b> ah | Address Hold Time                          | 50   |      | 50   | _    | 55   | _    | ns   |  |

| toven         | tos         | Data Setup Time                            | 40   | _    | 40   | _    | 45   | _    | ns   |  |

| tendx         | tон         | Data Hold Time                             | 10   | _    | 10   | _    | 10   | _    | ns   |  |

| tengl         | twn         | Write Recovery Time before Read            | 6    | _    | 6    | _    | 6    | _    | μs   |  |

| tghel         |             | Read Recovery Time before Write            | 0    | _    | 0    | _    | 0    |      | μs   |  |

| twler         |             | Write Enable Setup Time before Chip Enable | 0    |      | 0    | _    | 0    | _    | ns   |  |

| tehwh         |             | Write Enable Hold Time                     | 0    | _    | 0    | -    | 0    | _    | ns   |  |

| teleh         | twp         | Write Pulse Width                          | 50   |      | 50   | _    | 70   | _    | ns   |  |

| tehel         | twpH        | Write Pulse Width HIGH                     | 20   | _    | 20   | _    | 20   | _    | ns   |  |

| tenen1        |             | Duration of Programming Operation(2)       | 10   | _    | 10   | _    | 10   | -    | μs   |  |

| tehen2        |             | Duration of Erase Operation(2)             | 9.5  | _    | 9.5  | _    | 9.5  | _    | ms   |  |

| tvpel         |             | VPP Setup Time to Chip Enable LOW          | 1.0  | _    | 1.0  |      | 1.0  |      | μs   |  |

#### Notes:

2. The integrated stop timer terminates the programming/erase operations, thereby eliminating the need for a maximum specification.

Chip Enable Controlled Writes: Write operations are driven by the valid combination of Chip Enable and Write Enable. In system

where Chip Enable defines the write pulse width all setup, hold and inactive Write Enable times should be measured relative to the

Chip Enable waveform.

## **ALTERNATIVE SWITCHING WAVEFORM: PROGRAMMING OPERATION**

## Notes:

1. Alternative CE-Controlled Write Timings also apply to Erase Operations.

## **ORDERING INFORMATION**

Commerical Range: 0°C to +70°C

| Speed (ns) | Order Part No. | Package                            |

|------------|----------------|------------------------------------|

| 70         | IS28F020-70W   | 600-mil Plastic DIP                |

| 70         | IS28F020-70PL  | PLCC - Plastic Leaded Chip Carrier |

| 70         | IS28F020-70T   | TSOP                               |

| 90         | IS28F020-90W   | 600-mil Plastic DIP                |

| 90         | IS28F020-90PL  | PLCC – Plastic Leaded Chip Carrier |

| 90         | IS28F020-90T   | TSOP                               |

| 120        | IS28F020-120W  | 600-mil Plastic DIP                |

| 120        | IS28F020-120PL | PLCC - Plastic Leaded Chip Carrier |

| 120        | IS28F020-120T  | TSOP                               |

## **ORDERING INFORMATION**

Industrial Range: -40°C to +85°C

| Speed (ns) | Order Part No.  | Package                            |

|------------|-----------------|------------------------------------|

| 70         | IS28F020-70WI   | 600-mil Plastic DIP                |

| 70         | IS28F020-70PLI  | PLCC – Plastic Leaded Chip Carrier |

| 70         | IS28F020-70TI   | TSOP                               |

| 90         | IS28F020-90WI   | 600-mil Plastic DIP                |

| 90         | IS28F020-90PLI  | PLCC – Plastic Leaded Chip Carrier |

| 90         | IS28F020-90TI   | TSOP                               |

| 120        | IS28F020-120WI  | 600-mil Plastic DIP                |

| 120        | IS28F020-120PLI | PLCC – Plastic Leaded Chip Carrier |

| 120        | IS28F020-120TI  | TSOP                               |