# AN2104NFHQ

## Digital Pre-Processing IC

### ■ Overview

The AN2104NFHQ is a digital pre-processing IC for CCD cameras. It is a single chip IC including a 10-bit A/D converter as well as CDS and AGC circuits. The CDS circuit achieves high-speed sampling at rates up to 25 MHz, and thus the AN2104NFHQ can support advanced CCD cameras developing in higher density pixels and image quality, such as XGA or SXGA resolutions. The AGC and OB circuits can be adjusted with 9-bit and 8-bit serial data respectively through on-chip D/A converter.

### ■ Features

- Low power (114 mW typ. at 3 V supply voltage)

- High-speed sample-and-hold circuit operates up to 25 MHz.

- The AGC can be adjusted over 0.5 dB to 36 dB range.

- The OB circuit is adjustable over a  $\{V_{RB} \text{ to } V_{RB} + (V_{RT} - V_{RB})/4\}$  range.

- On-chip A/D converter reference voltage supply circuit ( $V_{RT}$  and  $V_{RB}$ )

- On-chip 10-bit A/D converter (maximum conversion speed: 25 MSPS)

- Built-in 3-channel 8-bit D/A converter for adjustments and mode settings.

### ■ Applications

- Digital still cameras

- Video cameras

- PC input cameras

- Surveillance cameras

- Board cameras

- Cameras that use CCDs and digital signal processing.

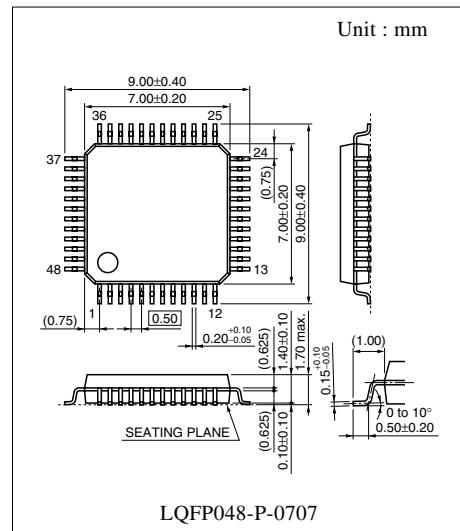

LQFP048-P-0707

Note) The package of this product will be changed to lead-free type (LQF048-P-0707A). See the new package dimensions section later of this datasheet.

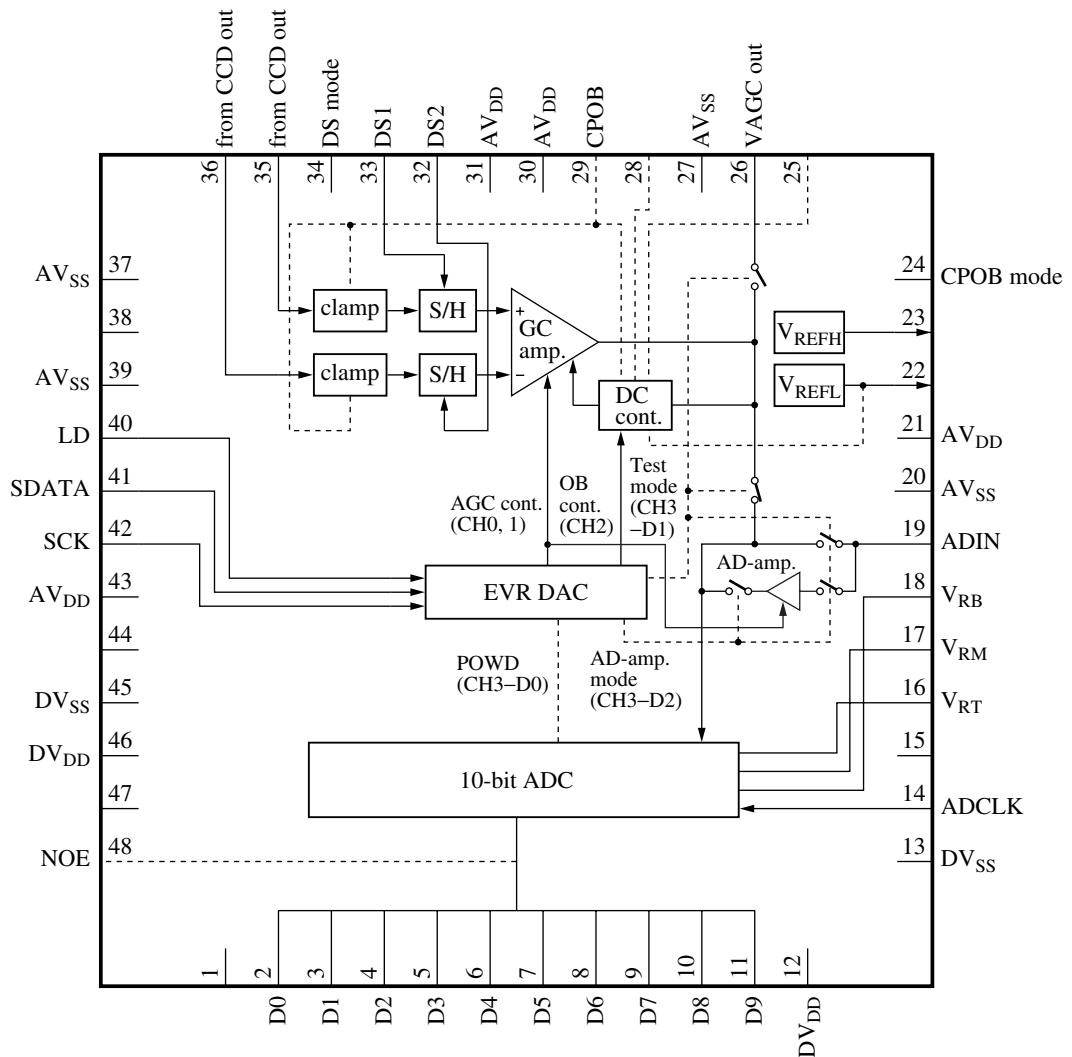

## ■ Block Diagram

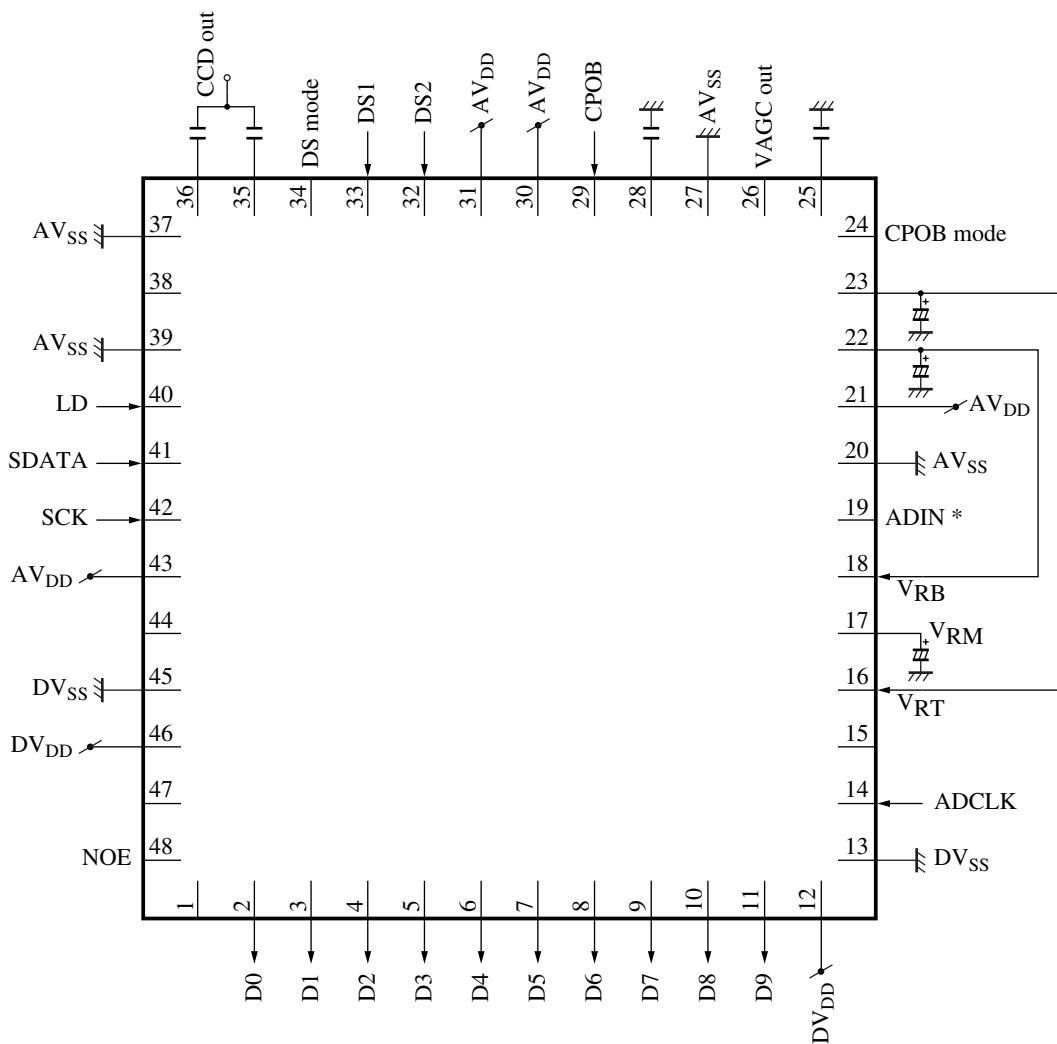

## ■ Pin Descriptions

| Pin No. | Description                                                | Pin No. | Description                                       |

|---------|------------------------------------------------------------|---------|---------------------------------------------------|

| 1       | Unused (Must be connected to ground.)                      | 25      | Output OB level stabilization                     |

| 2       | A/D converter output D0                                    | 26      | AGC output in test mode                           |

| 3       | A/D converter output D1                                    | 27      | Analog system ground 2                            |

| 4       | A/D converter output D2                                    | 28      | Input DC level stabilization                      |

| 5       | A/D converter output D3                                    | 29      | CPOB pulse input                                  |

| 6       | A/D converter output D4                                    | 30      | Analog system power supply 2                      |

| 7       | A/D converter output D5                                    | 31      | Analog system power supply 3                      |

| 8       | A/D converter output D6                                    | 32      | DS2 pulse input                                   |

| 9       | A/D converter output D7                                    | 33      | DS1 pulse input                                   |

| 10      | A/D converter output D8                                    | 34      | DS1 and DS2 pulse. Active high/active low setting |

| 11      | A/D converter output D9                                    | 35      | CCD output signal input 1                         |

| 12      | Digital system power supply 1                              | 36      | CCD output signal input 2                         |

| 13      | Digital system ground 1                                    | 37      | Analog system ground 3                            |

| 14      | A/D converter clock input                                  | 38      | Unused (Must be connected to ground.)             |

| 15      | Unused (Must be connected to ground.)                      | 39      | Analog system ground 4                            |

| 16      | A/D converter reference supply $V_{RT}$ input              | 40      | Load pulse input                                  |

| 17      | A/D converter reference supply $V_{RM}$                    | 41      | Serial data input                                 |

| 18      | A/D converter reference supply $V_{RB}$ input              | 42      | Serial clock input                                |

| 19      | AGC input in test mode                                     | 43      | Analog system power supply 4                      |

| 20      | Analog system ground 1                                     | 44      | Unused (Must be connected to ground.)             |

| 21      | Analog system power supply 1                               | 45      | Digital system ground 2                           |

| 22      | Reference voltage supply $V_{REFL}$ output (1.1 V typical) | 46      | Digital system power supply 2                     |

| 23      | Reference voltage supply $V_{REFH}$ output (2.5 V typical) | 47      | Unused (Must be connected to ground.)             |

| 24      | CPOB pulse. Active high/active low setting                 | 48      | A/D converter output enable setting               |

## ■ Absolute Maximum Ratings

| Parameter                           | Symbol    | Rating       | Unit |

|-------------------------------------|-----------|--------------|------|

| Supply voltage                      | $V_{DD}$  | –0.3 to +4.6 | V    |

| Supply current                      | $I_{DD}$  | —            | mA   |

| Power dissipation <sup>*2</sup>     | $P_D$     | 226          | mW   |

| Operating temperature <sup>*1</sup> | $T_{opr}$ | –20 to +75   | °C   |

| Storage temperature <sup>*1</sup>   | $T_{stg}$ | –55 to +125  | °C   |

Notes: <sup>\*1</sup> : Except for the operating temperature and storage temperature, all items are measured at  $T_a = 25$  °C.

<sup>\*2</sup> : The power dissipation is for the package at  $T_a = 75$  °C in free air.

## ■ Recommended Operating Range

| Parameter      | Symbol          | Range             | Unit |

|----------------|-----------------|-------------------|------|

| Supply voltage | V <sub>CC</sub> | 2.7 to 3.0 to 3.6 | V    |

■ Electrical Characteristics at AV<sub>DD</sub> = DV<sub>DD</sub> = 3.0 V, T<sub>a</sub> = 25 °C

| Parameter                                                | Symbol            | Conditions                                                                          | Min             | Typ  | Max             | Unit    |

|----------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------|-----------------|------|-----------------|---------|

| Supply current (in CDS mode)                             | I <sub>DD1</sub>  | AV <sub>DD</sub> = DV <sub>DD</sub> = 3.0 V, f <sub>CLK</sub> = 25 MHz              | —               | 38   | 51              | mA      |

| Supply current (in AD amplifier mode)                    | I <sub>DD2</sub>  | AV <sub>DD</sub> = DV <sub>DD</sub> = 3.0 V, f <sub>CLK</sub> = 25 MHz              | —               | 24   | 39              | mA      |

| Low power mode supply current                            | I <sub>POWD</sub> | f <sub>CLK</sub> = 25 MHz                                                           | —               | 5.0  | 16              | mA      |

| Reference voltage (1)                                    | V <sub>REFH</sub> | AV <sub>DD</sub> = DV <sub>DD</sub> = 3.0 V                                         | 2.3             | 2.5  | 2.7             | V       |

| Reference voltage (2)                                    | V <sub>REFL</sub> | AV <sub>DD</sub> = DV <sub>DD</sub> = 3.0 V                                         | 0.8             | 1.0  | 1.2             | V       |

| CPOB pulse input voltage high level                      | CPOB <sub>H</sub> | —                                                                                   | 2.4             | —    | V <sub>DD</sub> | V       |

| CPOB pulse input voltage low level                       | CPOB <sub>L</sub> | —                                                                                   | V <sub>SS</sub> | —    | 0.8             | V       |

| DS1 pulse input voltage high level                       | DS1 <sub>H</sub>  | —                                                                                   | 2.4             | —    | V <sub>DD</sub> | V       |

| DS1 pulse input voltage low level                        | DS1 <sub>L</sub>  | —                                                                                   | V <sub>SS</sub> | —    | 0.8             | V       |

| DS2 pulse input voltage high level                       | DS2 <sub>H</sub>  | —                                                                                   | 2.4             | —    | V <sub>DD</sub> | V       |

| DS2 pulse input voltage low level                        | DS2 <sub>L</sub>  | —                                                                                   | V <sub>SS</sub> | —    | 0.8             | V       |

| AGC frequency characteristics                            | G <sub>fA</sub>   | 10 MHz, with upper blanking, sine wave, 300 mV[p-p]                                 | -2.9            | -0.4 | 2.1             | dB      |

| AGC input dynamic range                                  | G <sub>AG3</sub>  | With upper BLK, sine wave, 600 mV[p-p]                                              | -1.8            | 0    | 1.8             | dB      |

| Minimum AGC gain                                         | G <sub>AG4</sub>  | With upper BLK, sine wave, 300 mV[p-p]                                              | -2.0            | 0.5  | 3.0             | dB      |

| Maximum AGC gain                                         | G <sub>AG5</sub>  | With upper BLK, sine wave, 20 mV[p-p]                                               | 32.0            | 36.0 | 40.0            | dB      |

| AGC output dynamic range                                 | V <sub>AG6</sub>  | With upper BLK, sine wave, 50 mV[p-p]                                               | 1350            | 1700 | —               | mV[p-p] |

| AGC output DC (1)                                        | V <sub>OFF1</sub> | CH2 = 00, the difference with respect to V <sub>REF</sub>                           | -70             | 0    | 70              | mV      |

| AGC output DC (2)                                        | V <sub>OFF2</sub> | CH2 = FF, the difference with respect to (V <sub>REFH</sub> - V <sub>REFL</sub> )/4 | -70             | 0    | 70              | mV      |

| CDS sampling capability                                  | G <sub>CDS</sub>  | DS1 = DS2 = 25 MHz<br>CDS input: 300 mV[p-p]                                        | -2.0            | 0    | 2.0             | dB      |

| Reference resistor (V <sub>RB</sub> to V <sub>RT</sub> ) | R <sub>REF</sub>  | —                                                                                   | 278             | 570  | 950             | Ω       |

| AD-amplifier maximum gain                                | G <sub>AA1</sub>  | 3.58 MHz sine wave, 300 mV[p-p]                                                     | 5.0             | —    | —               | dB      |

| AD-amplifier minimum gain                                | G <sub>AA2</sub>  | 3.58 MHz sine wave, 300 mV[p-p]                                                     | —               | —    | -2.0            | dB      |

■ Electrical Characteristics (continued) at  $AV_{DD} = DV_{DD} = 3.0\text{ V}$ ,  $T_a = 25\text{ }^\circ\text{C}$

| Parameter                         | Symbol     | Conditions                                             | Min      | Typ       | Max       | Unit          |

|-----------------------------------|------------|--------------------------------------------------------|----------|-----------|-----------|---------------|

| Digital input current (high)      | $I_{DINH}$ | CLK and POWD pins<br>Pin19 = $0.8 \times V_{DD}$       | —        | —         | 45        | $\mu\text{A}$ |

| Digital input current (low)       | $I_{DINL}$ | CLK and POWD pins<br>Pin19 = $0.2 \times V_{DD}$       | —        | —         | 45        | $\mu\text{A}$ |

| Analog input current (high)       | $I_{AIH}$  | Pin19 = 3.0 V                                          | —        | —         | 200       | $\mu\text{A}$ |

| Analog input current (low)        | $I_{AIL}$  | Pin19 = 0.5 V                                          | -200     | —         | —         | $\mu\text{A}$ |

| High-level digital input current  | $V_{IH}$   | —                                                      | 2.4      | —         | $V_{DD}$  | V             |

| Low-level digital input current   | $V_{IL}$   | —                                                      | $V_{SS}$ | —         | 0.8       | V             |

| High-level digital output current | $I_{OH}$   | $V_{OH} = 0.8 \times V_{DD}$                           | —        | —         | -1.5      | mA            |

| Low-level digital output current  | $I_{OL}$   | $V_{OL} = -0.2 \times V_{DD}$                          | 1.5      | —         | —         | mA            |

| Differential linearity error      | $E_D$      | —                                                      | —        | $\pm 0.5$ | $\pm 1.0$ | LSB           |

| Dynamic linearity error           | $DE_L$     | $f_{CLK} = 25\text{ MHz}$ , $f_{IN} = 12.5\text{ MHz}$ | —        | —         | $\pm 13$  | LSB           |

| Quantization noise <sup>*1</sup>  | S/N        | $f_{CLK} = 20\text{ MHz}$ , $f_{IN} = 3.58\text{ MHz}$ | 42       | 47        | —         | dB            |

Note: \*1. Including the total harmonic distortion.

- Design Reference Data

Note: The characteristics shown below are design reference values, and are not guaranteed.

| Parameter                    | Symbol      | Conditions                         | Min  | Typ  | Max  | Unit |

|------------------------------|-------------|------------------------------------|------|------|------|------|

| Maximum conversion rate      | $F_{CMAX}$  | —                                  | 25   | —    | —    | MSPS |

| Reference voltage difference | $V_{DELTA}$ | $AV_{DD} = DV_{DD} = 3.0\text{ V}$ | 1.38 | 1.48 | 1.58 | V    |

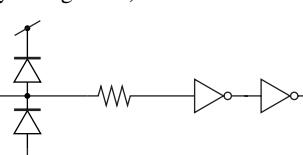

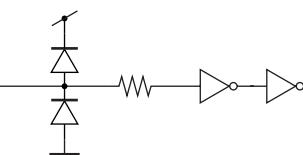

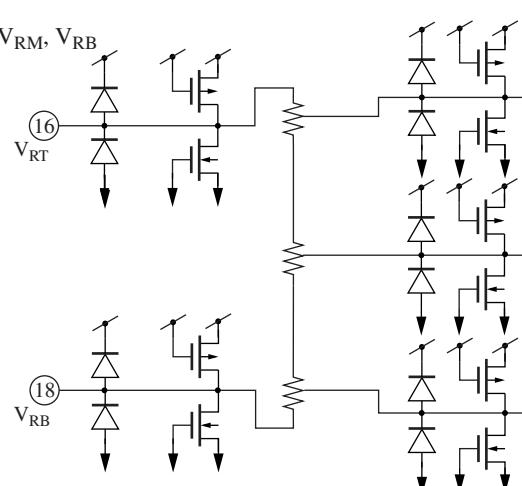

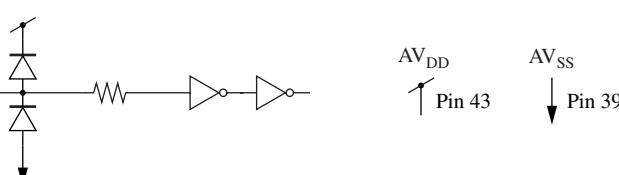

## ■ Terminal Equivalent Circuits

| Pin No.        | Equivalent circuit                                                                                                                         |                                                                                                                                       |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1              | Pin 1, 44, 47<br>N.C. (Ground to analog system ground)                                                                                     | <br>DV <sub>DD</sub> Pin 12 DV <sub>SS</sub> Pin 13  |

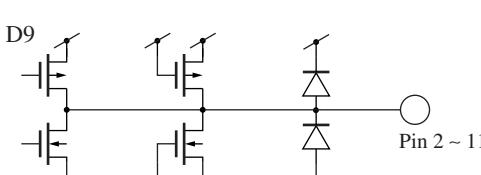

| 2 to 11        | D0 to D9                                                                                                                                   | <br>DV <sub>DD</sub> Pin 12 DV <sub>SS</sub> Pin 13  |

| 12<br>13       | Pin 12 : DV <sub>DD</sub><br>Pin 13 : DV <sub>SS</sub>                                                                                     |                                                      |

| 14<br>15       | Pin 14 : ADCLK<br>Pin 15 : N.C. (Ground to analog system ground)                                                                           | <br>DV <sub>DD</sub> Pin 12 DV <sub>SS</sub> Pin 13 |

| 16<br>17<br>18 | V <sub>RT</sub> , V <sub>RM</sub> , V <sub>RB</sub><br> | AV <sub>DD</sub> Pin 21 AV <sub>SS</sub> Pin 20                                                                                       |

## ■ Terminal Equivalent Circuits (continued)

| Pin No. | Equivalent circuit                                                                                                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 19      | <p>ADIN</p> <p>ADIN (19)</p> <p>AV<sub>DD</sub> Pin 21</p> <p>AV<sub>SS</sub> Pin 20</p>                                                     |

| 20      | Pin 20 : AV <sub>SS</sub>                                                                                                                    |

| 21      | Pin 21 : AV <sub>DD</sub>                                                                                                                    |

| 22      | <p>Pin 22 : V<sub>REFL</sub><br/>Pin 23 : V<sub>REFH</sub></p> <p>Pin 22, 23</p> <p>AV<sub>DD</sub> Pin 30</p> <p>AV<sub>SS</sub> Pin 27</p> |

| 24      | <p>CPOB mode</p> <p>AV<sub>DD</sub> Pin 30</p> <p>AV<sub>SS</sub> Pin 27</p>                                                                 |

| 25      | <p>VOBDAT</p> <p>Pin 25, 28</p> <p>AV<sub>DD</sub> Pin 30</p> <p>AV<sub>SS</sub> Pin 27</p>                                                  |

| 26      | <p>V<sub>AGC</sub> out</p> <p>Pin 26</p> <p>AV<sub>DD</sub> Pin 30</p> <p>AV<sub>SS</sub> Pin 27</p>                                         |

## ■ Terminal Equivalent Circuits (continued)

| Pin No. | Equivalent circuit                              |

|---------|-------------------------------------------------|

| 27      | Analog ground                                   |

| 28      | VCLIPDAT<br>See pin 25                          |

| 29      | CPOB<br>                                        |

| 30      | AV <sub>DD</sub> (analog system power supply 2) |

| 31      | AV <sub>DD</sub> (analog system power supply 3) |

| 32      | Pin 32 : DS2<br>Pin 33 : DS1<br>                |

| 33      |                                                 |

| 34      | DS mode<br>                                     |

| 35      | Pin 35 : SIGIN1<br>Pin 36 : SIGIN2<br>          |

| 36      |                                                 |

| 37      | Analog ground3                                  |

| 38      | Unused (Must be connected to ground.)<br>       |

| 39      | Analog ground 4                                 |

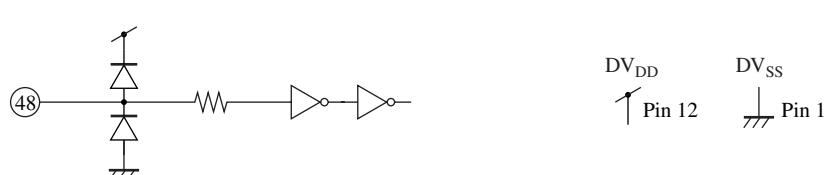

## ■ Terminal Equivalent Circuits (continued)

| Pin No.        | Equivalent circuit                                              |                                                                                    |

|----------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------|

| 40<br>41<br>42 | Pin 40 : LD<br>Pin 41 : SDATA<br>Pin 42 : SCK<br>Pin 40, 41, 42 |  |

| 43             | Analog system power supply 4                                    |                                                                                    |

| 44             | Unused (Must be connected to ground.)                           |                                                                                    |

| 45             | Digital system ground 2                                         |                                                                                    |

| 46             | Digital system power supply 2                                   |                                                                                    |

| 47             | Unused (Must be connected to ground.)                           |                                                                                    |

| 48             | NOE                                                             |  |

## ■ Application Circuit Example

Note \*: When the AD amplifier is used, signals should be input to pin 19 through a capacitor. (Assumed chrominance signal may be input.)

## ■ Usage Notes

The unused pins (pins 1, 15, 38, 44, and 47) are connected internally to the circuit shown in the "Pin Equivalent Circuits" table. Therefore, these pins must be held fixed at either V<sub>SS</sub> or V<sub>DD</sub>.

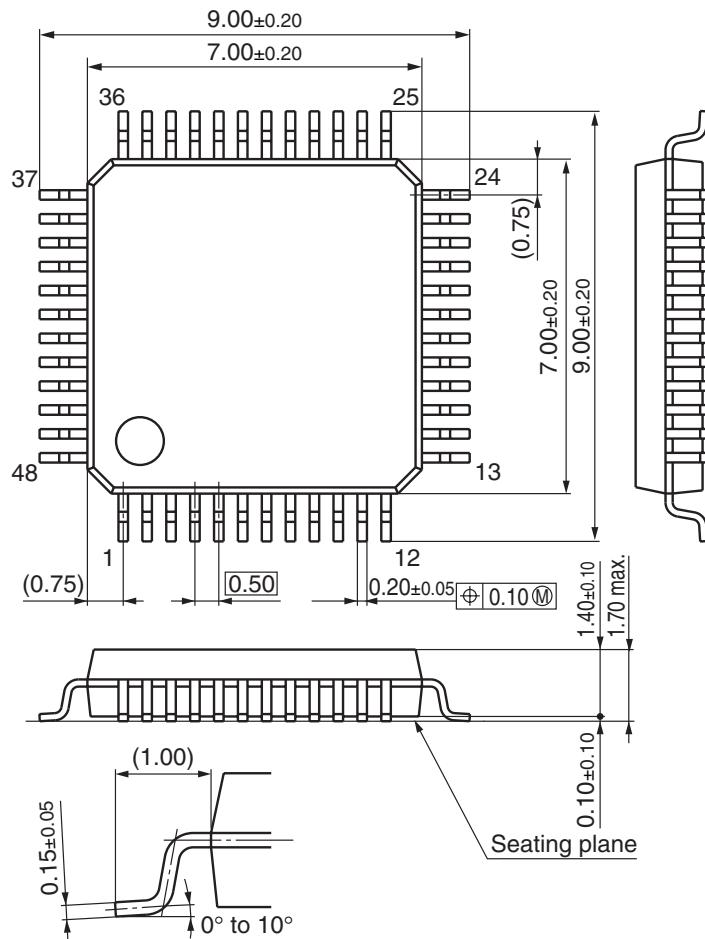

## ■ New Package Dimensions (Unit: mm)

- LQFP048-P-0707A (Lead-free package)

**Request for your special attention and precautions in using the technical information and semiconductors described in this material**

- (1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this material and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan.

- (2) The technical information described in this material is limited to showing representative characteristics and applied circuit examples of the products. It does not constitute the warranting of industrial property, the granting of relative rights, or the granting of any license.

- (3) The products described in this material are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (4) The products and product specifications described in this material are subject to change without notice for reasons of modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the guaranteed values, in particular those of maximum rating, the range of operating power supply voltage and heat radiation characteristics. Otherwise, we will not be liable for any defect which may arise later in your equipment.

Even when the products are used within the guaranteed values, redundant design is recommended, so that such equipment may not violate relevant laws or regulations because of the function of our products.

- (6) When using products for which dry packing is required, observe the conditions (including shelf life and after-unpacking standby time) agreed upon when specification sheets are individually exchanged.

- (7) No part of this material may be reprinted or reproduced by any means without written permission from our company.

**Please read the following notes before using the datasheets**

- A. These materials are intended as a reference to assist customers with the selection of Panasonic semiconductor products best suited to their applications.

Due to modification or other reasons, any information contained in this material, such as available product types, technical data, and so on, is subject to change without notice.

Customers are advised to contact our semiconductor sales office and obtain the latest information before starting precise technical research and/or purchasing activities.

- B. Panasonic is endeavoring to continually improve the quality and reliability of these materials but there is always the possibility that further rectifications will be required in the future. Therefore, Panasonic will not assume any liability for any damages arising from any errors etc. that may appear in this material.

- C. These materials are solely intended for a customer's individual use.

Therefore, without the prior written approval of Panasonic, any other use such as reproducing, selling, or distributing this material to a third party, via the Internet or in any other way, is prohibited.