## NTE797 Integrated Circuit TV Chroma Processor

## Features:

- Phase-Locked Subcarrier Regeneration Utilizes Sample-And-Hold Techniques

- Automatic Chrominance Control (ACC)/Killer Detector Employs Sample-And-Hold Techniques

- Supplementary ACC with an Overload Detector to Prevent Oversaturation of this Picture Tube

- Sinusoidal Subcarrier Output

- Keyed Chroma Output

- Emitter-Follower Buffered Outputs for Low Output Impedance

- Linear DC Saturation Control

| Absolute Maximum Ratings: (T <sub>A</sub> = +25°C unless otherwise specified)                      |

|----------------------------------------------------------------------------------------------------|

| Device Dissipation ( $T_A \le +55^{\circ}C$ )                                                      |

| Derate Linearly Above $T_A = +55^{\circ}C$ 7.9mW/°C                                                |

| DC Supply Voltage (Across Pin5 and Pin12, Note 1) $\Delta$                                         |

| DC Current:                                                                                        |

| Into Pin12 38mA                                                                                    |

| Into Pin14                                                                                         |

| DC Voltage (Pin9)                                                                                  |

| Negative Rating                                                                                    |

| Positive Rating                                                                                    |

| Operating Ambient Temperature Range, T <sub>A</sub>                                                |

| Storage Temperature range, T <sub>stq</sub> 65° to +150°C                                          |

| Lead Temperature (During Soldering, 1/32 in (0.79mm) from case, 10sec max.), T <sub>L</sub> +265°C |

Note 1. This rating does not apply when using the internal zener reference in conjunction with an external pass transistor.

<u>Electrical Characteristics</u>:  $(T_A = +25^{\circ}C)$ , chroma control at maximum position for all characteristics test except for chroma output test. For this test, control should be set at minimum position.)

| Characteristic                   | Test<br>Measurement<br>& Symbol | Switch<br>S1 | Pos.<br>S2 | Chroma<br>Input<br>TP1 | Min  | Тур  | Max  | Unit       |  |

|----------------------------------|---------------------------------|--------------|------------|------------------------|------|------|------|------------|--|

| Static Characteristics           |                                 |              |            |                        |      |      |      |            |  |

| Voltage Regulator                | V <sub>12</sub>                 | 2            | 2          | 0                      | 10.1 | 11.2 | 12.1 | V          |  |

| Supply Current                   |                                 |              |            |                        |      |      |      |            |  |

| Dynamic Characteristics (Note 2) |                                 |              |            |                        |      |      |      |            |  |

| Pull-In Range (Note 3)           | V <sub>8</sub>                  | Note 3       | 2          | 0.5V <sub>p-p</sub>    | ±250 | _    | _    | Hz         |  |

| Oscillator Output                | V <sub>8</sub>                  | 2            | 2          | 0                      | 0.6  | 1.0  | _    | $V_{p-p}$  |  |

| 100% Chroma Output               | V <sub>15</sub>                 | 1            | 2          | 0.5V <sub>p-p</sub>    | 1.4  | 2.7  | _    | $V_{p-p}$  |  |

| Overload Detector                | V <sub>15</sub>                 | 1            | 1          | 0.5V <sub>p-p</sub>    | 0.4  | _    | 0.7  | $V_{p-p}$  |  |

| Minimum Chroma Output            | V <sub>15</sub>                 | 1            | 2          | 0.5V <sub>p-p</sub>    | _    | _    | 20   | $mV_{p-p}$ |  |

| 200% Chroma Output               | V <sub>15</sub>                 | 1            | 2          | 1V <sub>p-p</sub>      | 70   | 100  | 140  | % of 100%  |  |

| 20% Chroma Output                | V <sub>15</sub>                 | 1            | 2          | 0.1V <sub>p-p</sub>    | 40   | _    | 105  | reading    |  |

| Kill Level                       | V <sub>TP1</sub>                | 1            | 2          | vary                   | 5    | _    | 60   | $mV_{p-p}$ |  |

- Note 2. Except for pull-in range testing, tune oscillator trimmer capacitor for free-running frequency of 3.579545 MHz ± 10Hz.

- Note 3. Set Switch 1 to Position 2, detune oscillator ±250Hz, set Switch to Position 1, and check for oscillator pull–in.

## **Circuit Description:**

The chroma input is applied to Pin1 through the desired band-shaping network. A 2,450-ohm resistor should be placed in series with Pin1 to minimize oscillator pickup in the first chroma amplifier. This amplifier supplies signals to the second chroma amplifier and to the ACC and AFPC detectors. The first chroma amplifier is gain-controlled by the ACC amplifier. A horizontal keying pulse is applied to Pin9. This pulse must be present to ensure proper operation of the oscillator circuit. The subcarrier burst is sampled during the keying interval in the AFPC detector. The error voltage, produced at Pin2 and proportional to the burst phase, is compared to the guiescent bias voltage at Pin3 by the sampleand-hold circuitry. This "compared" voltage controls the phase-shifting network in the phase-locked loop. The operation of the AFPC loop is independent of any external adjustments or voltages except for an initial capacitor adjustment to set the free-running frequency. The regenerated oscillator signal at Pin8 is applied internally to the AFPC and ACC detectors through +45 - and -45 -degree phaseshifter networks to establish the proper phase relationship for these detectors. The ACC detectors, which also samples the burst during the keying interval, produces a correction voltage proportional to the burst amplitude. The correction voltage is compared to the guiescent bias level using sampleand-hold circuitry similar to that used in the AFPC portion of the circuit. The "compared" voltage is applied internally to the ACC amplifier and killer amplifier. Because the amplifier gains and killer threhold are determined by the ratios of the internal resistors, these functions are independent of external voltages or controls.

The attenuated chroma signal is fed to the second chroma amplifier, where the burst is removed by keyer action. The killer amplifier, the chroma gain control, and the overload detector control the action of the second chroma amplifier, whose gain is proportional to the DC voltage at Pin16. The overload detector (Pin13) receives a sample of the chroma output (Pin15) and detects the peak of the signal. The detected voltage is stored in an external capacitor connected to Pin16. This stored voltage on Pin16 affects the gain of the second chroma in the same manner as the chroma gain control.

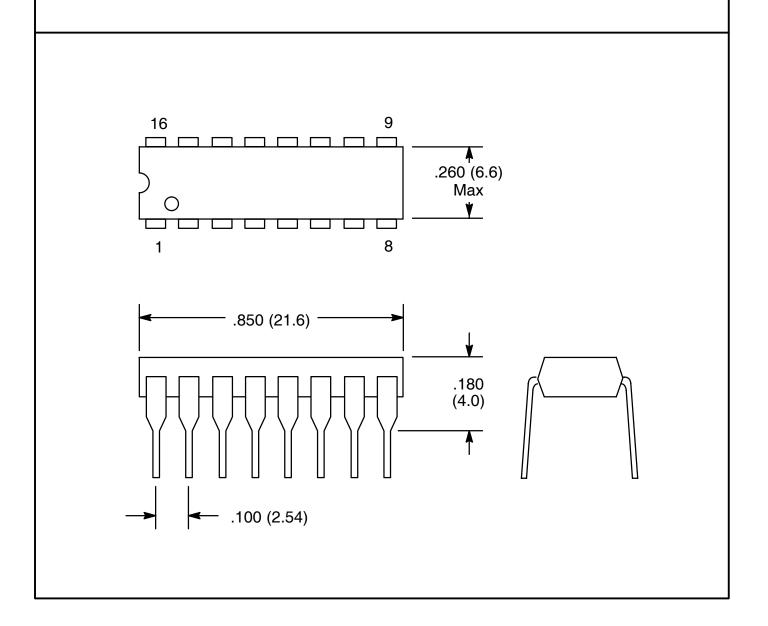

## **Pin Connection Diagram** Chroma Input 16 Chroma Gain Control 15 Chroma Output AF PC Filter Network 2 Bypass 3 Zener Reference RF Bypass Overload Det GND **12** V<sub>CC</sub> Crystal Filter 6 11 ACC Filter Network Crystal Filter 7 10 ACC Filter Network Carrier Output 8 9 Horiz Keying Input