- Single +5-V Supply

- Fully Static Operation (No Clocks, No Refresh)

- JEDEC Standard Pinout

- 24-Pin 600 Mil (15.2 mm) Package Configuration

- Plug-in Compatible with 16K 5 V EPROMs

- 8-Bit Output for Use in Microprocessor-Based Systems

- G Eliminates Need for External Bus Buffers

- All Inputs and Outputs Fully TTL Compatible

- Fanout to Series 74, Series 74S or Series 74LS TTL Loads

- N-Channel Silicon-Gate Technology

- Power Dissipation Under 385 mW Max

- Guaranteed dc Noise Immunity of 400 mV with Standard TTL Loads

- 4 Performance Ranges:

#### ACCESS TIME (MAX)

| TMS4016-12 | 120 ns |

|------------|--------|

| TMS4016-15 | 150 ns |

| TMS4016-20 | 200 ns |

| TMS4016-25 | 250 ns |

| TMS40 | 1 | 6  |   |   |   | NL | PACKAGE |  |

|-------|---|----|---|---|---|----|---------|--|

|       |   | íΤ | n | D | ١ | ΛE | A/\     |  |

|   | •    | 1.  | 1 100 | _ |                         |

|---|------|-----|-------|---|-------------------------|

|   | A7[  | יו  | U24   | ш | VCC                     |

|   | A6[  | 2   | 23    | ᄓ | A8                      |

|   | A5[  | 3   | 22    | ₽ | A9                      |

|   | A4[  | 4   | 21    | □ | $\overline{\mathbf{w}}$ |

|   | A3[  | 5   | 20    |   | G                       |

|   | A2[  | 6   | 19    | D | A10                     |

|   | A1[  | 7   | 18    | ᄓ | s                       |

|   | AO[  | В   | 17    |   | DQ8                     |

|   | DQ1[ | 9   | 16    |   | DQ7                     |

| 1 | DQ2[ | 10  | 15    |   | DQ6                     |

|   | DQ3[ | 111 | 14    |   | DQ5                     |

|   | Vss[ | 112 | 13    | h | DQ4                     |

| PIN NOM   | ENCLATURE        |

|-----------|------------------|

| A0 - A10  | Addresses        |

| DQ1 - DQ8 | Data In/Data Out |

| G         | Output Enable    |

| <u>ই</u>  | Chip Select      |

| Vcc       | + 5-V Supply     |

| VSS       | Ground           |

| W         | Write Enable     |

### description

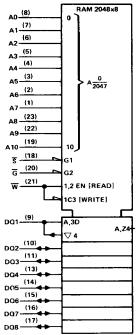

The TMS4016 static random-access memory is organized as 2048 words of 8 bits each. Fabricated using proven N-channel, silicon-gate MOS technology, the TMS4016 operates at high speeds and draws less power per bit than 4K static RAMs. It is fully compatible with Series 74, 74S, or 74LS TTL. Its static design means that no refresh clocking circuitry is needed and timing requirements are simplified. Access time is equal to cycle time. A chip select control is provided for controlling the flow of data-in and data-out and an output enable function is included in order to eliminate the need for external bus buffers.

Of special importance is that the TMS4016 static RAM has the same standardized pinout as TI's compatible EPROM family. This, along with other compatible features, makes the TMS4016 plug-in compatible with the TMS2516 (or other 16K 5 V EPROMs). Minimal, if any modifications are needed. This allows the microprocessor system designer complete flexibility in partitioning his memory board between read/write and non-volatile storage.

The TMS4016 is offered in the plastic (NL suffix) 24-pin dual-in-line package designed for insertion in mounting hole rows on 600-mil (15.2 mm) centers. It is guaranteed for operation from 0 °C to 70 °C.

Copyright © 1983 by Texas Instruments Incorporated

Texas Instruments

POST OFFICE BOX 225012 . DALLAS, TEXAS 75265

8-13

184

#### addresses (A0 - A10)

The eleven address inputs select one of the 2048 8-bit words in the RAM. The address-inputs must be stable for the duration of a write cycle. The address inputs can be driven directly from standard Series 54/74 TTL with no external pull-up resistors.

### output enable (G)

The output enable terminal, which can be driven directly from standard TTL circuits, affects only the data-out terminals. When output enable is at a logic high level, the output terminals are disabled to the high-impedance state. Output enable provides greater output control flexibility, simplifying data bus design.

#### chip select (S)

The chip-select terminal, which can be driven directly from standard TTL circuits, affects the data-in/data-out terminals. When chip select and output enable are at a logic low level, the D/Q terminals are enabled. When chip select is high, the D/Q terminals are in the floating or high-impedance state and the input is inhibited.

#### write enable (W)

The read or write mode is selected through the write enable terminal. A logic high selects the read mode; a logic low selects the write mode.  $\overline{W}$  must be high when changing addresses to prevent erroneously writing data into a memory location. The  $\overline{W}$  input can be driven directly from standard TTL circuits.

#### data-in/data-out (DQ1 - DQ8)

Data can be written into a selected device when the write enable input is low. The D/Q terminal can be driven directly from standard TTL circuits. The three-state output buffer provides direct TTL compatibility with a fan-out of one Series 74 TTL gate, one Series 74S TTL gate, or five Series 74LS TTL gates. The D/Q terminals are in the high impedance state when chip select  $(\overline{S})$  is high, output enable  $(\overline{G})$  is high, or whenever a write operation is being performed. Data-out is the same polarity as data-in.

8

# logic symbol†

#### **FUNCTION TABLE**

| ₩ | ŝ | G | DQ1-DQ8     | MODE            |

|---|---|---|-------------|-----------------|

| L | L | X | VALID DATA  | WRITE           |

| Н | Ļ | L | DATA OUTPUT | READ            |

| × | н | х | HI-Z        | DEVICE DISABLED |

| н | L | Н | HI∙Z        | OUTPUT DISABLED |

<sup>†</sup> This symbol is in accordance with IEEE Std 91/ANSI Y32.14 and recent decisions by IEEE and IEC. See explanation on page 10-1.

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage, VCC (see Note 1)       | 5 V to 7 V |

|----------------------------------------|------------|

| Input voltage (any input) (see Note 1) | 1 V to 7 V |

| Continuous power dissipation           | 1 W        |

| Operating free-air temperature range   | C to 70°C  |

| Storage temperature range 55 °C        | to 150°C   |

<sup>†</sup> Stresses beyond those listed under "'Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: Voltage values are with respect to the VSS terminal.

#### recommended operating conditions

| PARAMETER                                 | MIN | NOM | MAX | UNIT |

|-------------------------------------------|-----|-----|-----|------|

| Supply voltage, VCC                       | 4.5 | 5   | 5.5 | ٧    |

| Supply voltage, VSS                       |     | 0   |     | V    |

| High-level input voltage, VIH             | 2   |     | 5.5 | V    |

| Low-level input voltage, VIL (see Note 2) | -1  |     | 0.8 | V    |

| Operating free-air temperature, TA        | 0   |     | 70  | °C   |

NOTE 2: The algebraic convention, where the more negative (less positive) limit is designated as minimum, is used in this data sheet for logic voltage levels only.

Texas Instruments

POST OFFICE BOX 225012 • DALLAS, TEXAS 75265

8-15

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                | PARAMETER                | TEST CONDI                         | TIONS                    | MIN TYP     | MAX | UNIT         |

|----------------|--------------------------|------------------------------------|--------------------------|-------------|-----|--------------|

| VOH            | High level voltage       | I <sub>OH</sub> = −1 mA,           | V <sub>CC</sub> = 4.5 V  | 2.4         | WAX | +            |

| VOL            | Low level voltage        | I <sub>OL</sub> = 2.1 mA,          | V <sub>CC</sub> =4.5 V   | - Z.4       |     | V            |

| l <sub>l</sub> | Input current            | V <sub>I</sub> =0 V to 5.5 V       | VCC -4.5 V               | <del></del> | 0.4 | V            |

| loz            | Off-state output current | S or G at 2 V or W at 0.8 \        | 7,                       |             | 10  | μΑ           |

| -02            |                          | V <sub>O</sub> =0 V to 5.5 V       |                          | ĺ           | 10  | μΑ           |

| lcc            | Supply current from VCC  | I <sub>O</sub> = 0 mA,             | V <sub>CC</sub> = 5.5 V, |             |     | <del> </del> |

|                |                          | T <sub>A</sub> = 0 °C (worst case) |                          | 40          | 70  | mA           |

| C <sub>i</sub> | Input capacitance        | $V_I = 0 V$ ,                      | f=1 MHz                  |             | 8   | pF           |

| Co             | Output capacitance       | V <sub>O</sub> = 0 V,              | f = 1 MHz                |             | 12  | pF           |

<sup>†</sup>All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25 \,^{\circ}\text{C}$ .

# timing requirements over recommended supply voltage range and operating free-air temperature range

|                     | PARAMETER              | TMS4016-12 | TMS4     | TMS4016-15 |     | TMS4016-20 |     | TMS4016-25 |              |

|---------------------|------------------------|------------|----------|------------|-----|------------|-----|------------|--------------|

|                     |                        | MIN MAX    | MIN      | MAX        | MIN | MAX        | MIN | MAX        | UNIT         |

| tc(rd)              | Read cycle time        | 120        | 150      |            | 200 |            | 250 | WAA        | <del> </del> |

| tc(wr)              | Write cycle time       | 120        | 150      |            | 200 |            |     |            | ns           |

| tw(W)               | Write pulse width      | 60         | 80       |            |     |            | 250 |            | ns           |

| t <sub>su(A)</sub>  | Address setup time     | 20         | +        |            | 100 |            | 120 |            | ns           |

| t <sub>su</sub> (S) | Chip select setup time |            | 20       |            | 20  |            | 20  |            | ns           |

|                     |                        | 60         | 80       |            | 100 |            | 120 |            | ns           |

| tsu(D)              | Data setup time        | 50         | 60       |            | 80  |            | 100 |            | ns           |

| <sup>t</sup> h(A)   | Address hold time      | 0          | 0        |            | 0   |            |     |            |              |

| h(D)                | Data hold time         |            | <u> </u> |            |     | _          | 0   |            | ns           |

| 11(0)               | Total Hold talle       | 5          | 10       |            | 10  |            | 10  |            | ns           |

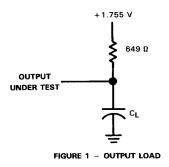

# switching characteristics over recommended voltage range, $T_A = 0^{\circ}C$ to $70^{\circ}C$ with output loading of Figure 1 (see notes 3 and 4)

|                     | PARAMETER                                    | TMS4016-12 | TMS40                                            | TMS4016-15 |      | TMS4016-20 |     | 016-25 |      |

|---------------------|----------------------------------------------|------------|--------------------------------------------------|------------|------|------------|-----|--------|------|

|                     |                                              | MIN MAX    | MIN                                              | MAX        | MIN  | MAX        | MIN | MAX    | UNIT |

| <sup>t</sup> a(A)   | Access time from address                     | 120        |                                                  | 150        |      | 200        |     | 250    |      |

| ta(S)               | Access time from chip select low             | 60         |                                                  | 75         |      | 100        |     | 120    | ns   |

| ta(G)               | Access time from output enable low           | 50         |                                                  | 60         |      | 80         |     | 100    | ns   |

| tv(A)               | Output data valid after address change       | 10         | 15                                               |            | 15   | - 30       | 15  | - 100  | ns   |

| tdis(S)             | Output disable time after chip select high   | 40         | <del>                                     </del> | 50         | - 13 | 60         | 15  |        | ns   |

| tdis(G)             | Output disable time after output enable high | 40         | +                                                | 50         |      | 60         |     | 80     | ns   |

| <sup>‡</sup> dis(W) | Output disable time after write enable low   | 50         | <del> </del>                                     | 60         |      |            |     | 80     | ns   |

| ten(S)              | Output enable time after chip select low     | 5          | 5                                                | - 60       | 10   | 60         |     | 80     | ns   |

| ten(G)              | Output enable time after output enable low   | 5          | 5                                                |            |      |            | 10  |        | ns   |

| ten(W)              | Output enable time after write enable high   | 5          |                                                  |            | 10   |            | 10  |        | ns   |

|                     |                                              | 5          | 5                                                |            | 10   | - 1        | 10  |        | ns   |

NOTES: 3.  $C_L = 100 \text{ pF}$  for all measurements except  $t_{dis(W)}$  and  $t_{en(W)}$ .

C<sub>L</sub> = 5 pF for t<sub>dis(W)</sub> and t<sub>en(W)</sub>.

4. t<sub>dis</sub> and t<sub>en</sub> parameters are sampled and not 100% tested.

184

POST OFFICE BOX 225012 . DALLAS, TEXAS 75265

8-16

**Static RAM and Memory Support Devices**

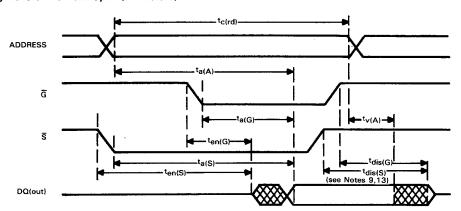

#### PARAMETER MEASUREMENT INFORMATION

timing waveform of read cycle (see note 5)

184

All timing reference points are 0.8 V and 2.0 V on inputs and 0.6 V and 2.2 V on outputs (90% points). Input rise and fall times equal 10 ns. NOTE 5: W is high for Read Cycle.

TEXAS

INSTRUMENTS

POST OFFICE BOX 225012 • DALLAS, TEXAS 75265

8-17

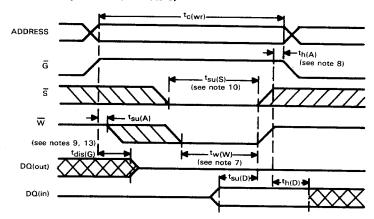

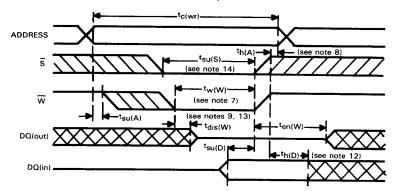

## timing waveform of write cycle no. 1 (see note 6)

timing waveform of write cycle no. 2 (see notes 6 and 11)

All timing reference points are 0.8 V and 2.0 V on inputs and 0.6 V and 2.2 V on outputs (90% points). Input rise and fall times equal 10 nanoseconds.

- NOTES: 6. W must be high during all address transitions.

- 7. A write occurs during the overlap of a low  $\overline{S}$  and a low  $\overline{W}$ . 8.  $t_{h(A)}$  is measured from the earlier of  $\overline{S}$  or  $\overline{W}$  going high to the end of the write cycle.

- 9. During this period, I/O pins are in the output state so that the input signals of opposite phase to the outputs must not be applied.

- 10. If the \$\overline{\Sigma}\$ low transition occurs simultaneously with the \$\overline{\W}\$ low transitions or after the \$\overline{\W}\$ transition, output remains in a high impedance state. 11.  $\vec{G}$  is continuously low  $(\vec{G} = V_{\parallel L})$ .

12. If  $\vec{S}$  is low during this period, I/O pins are in the output state. Data input signals of opposite phase to the outputs must not be applied.

- 13. Transition is measured ±200 mV from steady-state voltage.

- 14. If the S low transition occurs before the W low transition, then the data input signals of opposite phase to the outputs must not be applied for the duration of  $t_{\mbox{\scriptsize dis}(\mbox{\scriptsize W})}$  after the  $\overline{\mbox{\scriptsize W}}$  low transition.

Texas Instruments reserves the right to make changes at any time in order to improve design and to supply the best product possible.

184

8-18

POST OFFICE BOX 225012 . DALLAS, TEXAS 75265