# AN5095K

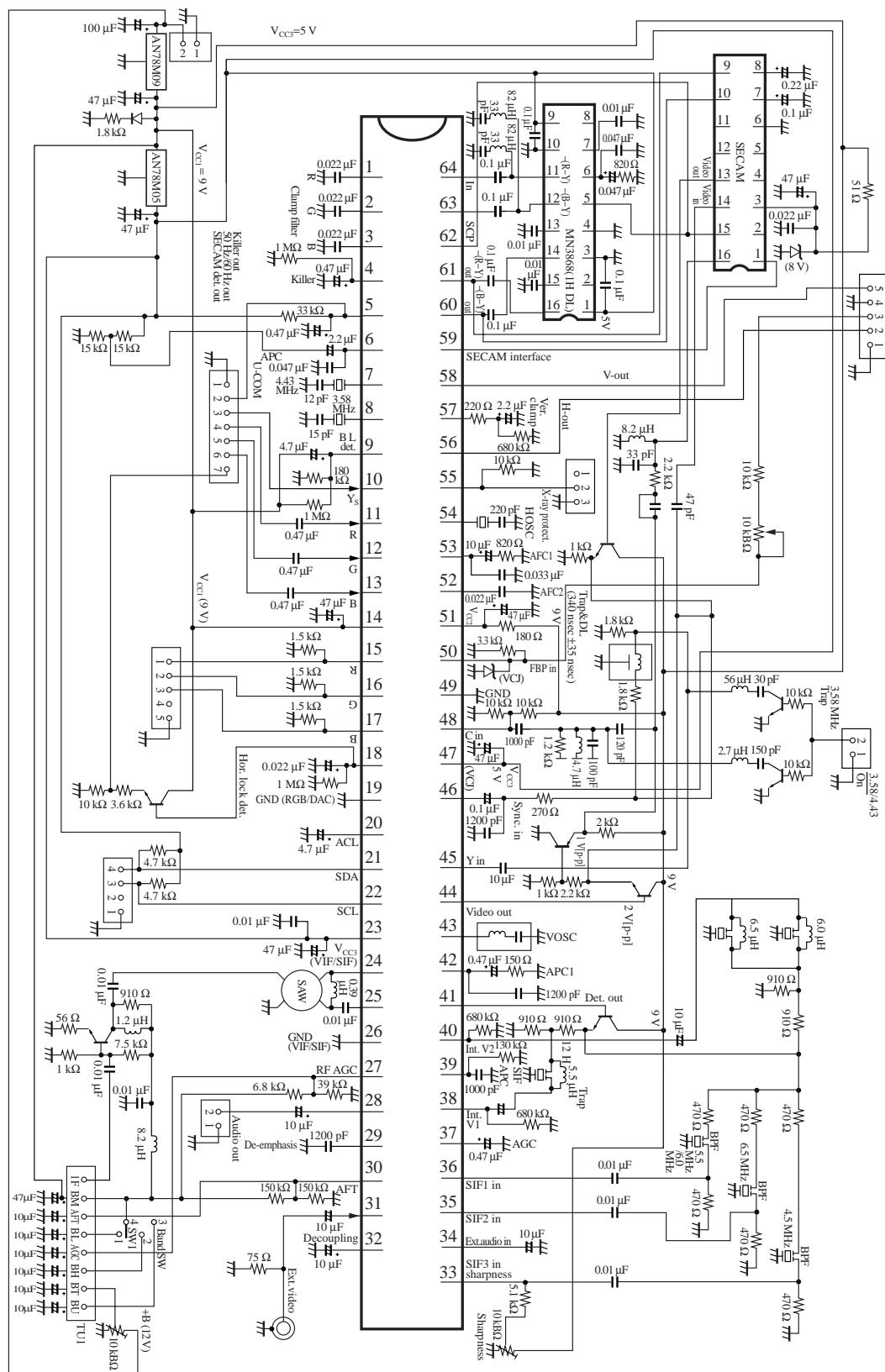

Single chip IC with I<sup>2</sup>C bus interface for PAL/NTSC color TV system

## ■ Overview

The AN5095K is an IC in which PAL/NTSC color television signal processing circuits are integrated into a single chip. Also, since the I<sup>2</sup>C bus interface is built in the IC, the rationalization of set production line can be realized.

## ■ Features

- Built- in video IF circuit, sound IF circuit, video signal processing circuit, color signal processing circuit, sync. signal processing circuit

- Suitable for PAL/NTSC/AV-NTSC/M-NTSC systems

- 6 dB improved sound S/N (compared with the AN5195K-B/-C)

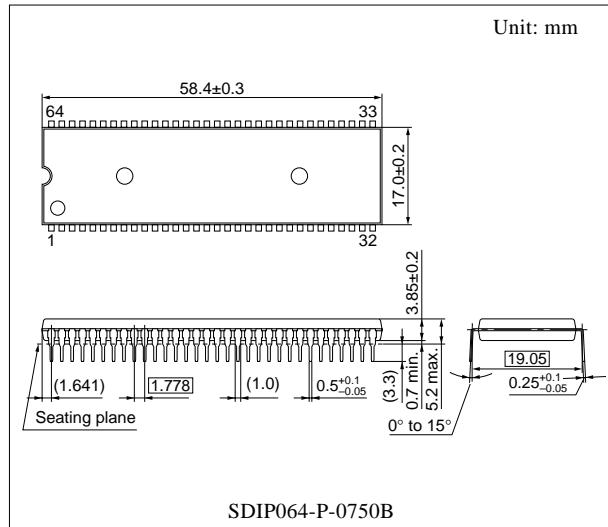

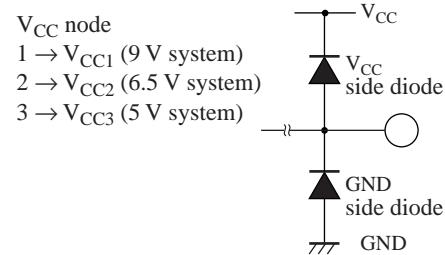

- Package: 64-SDIP, supply voltage: 5 V, 9 V

## ■ Applications

- Television and televideo

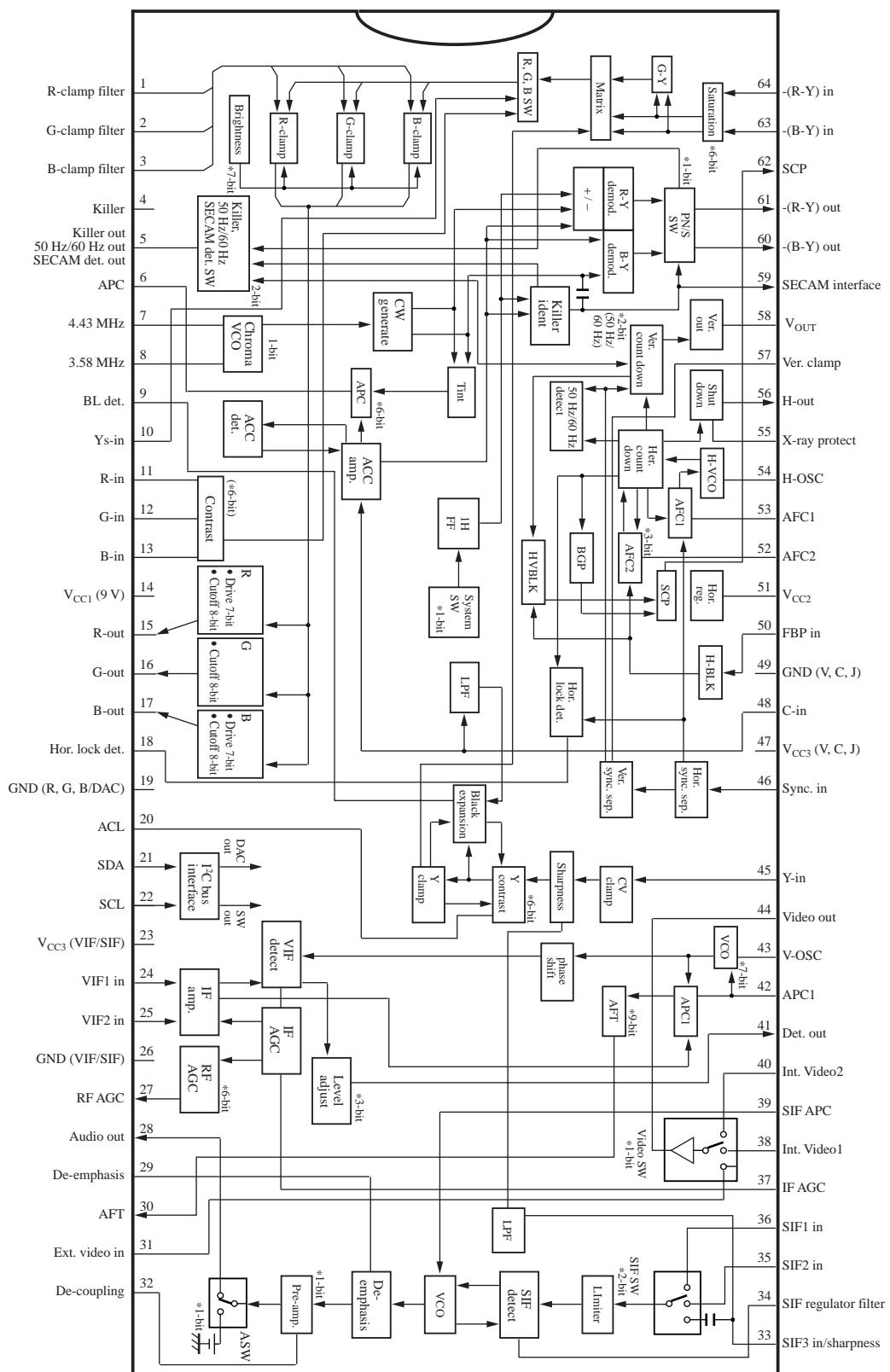

## ■ Block Diagram

## ■ Pin Descriptions

| Pin No. | Description                                 | Pin No. | Description                              |

|---------|---------------------------------------------|---------|------------------------------------------|

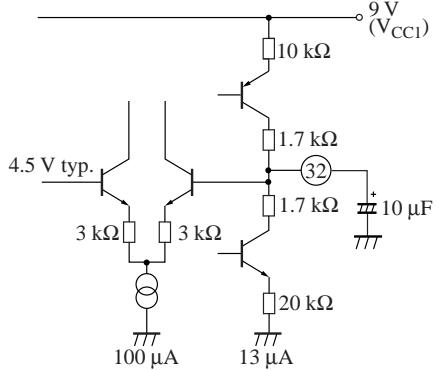

| 1       | (R) clamp                                   | 33      | SIF3 input/sharpness                     |

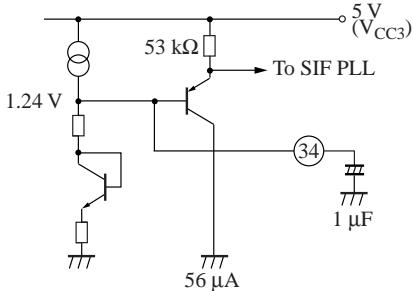

| 2       | (G) clamp                                   | 34      | SIF regulator filter                     |

| 3       | (B) clamp                                   | 35      | SIF2 input                               |

| 4       | Killer filter                               | 36      | SIF1 input                               |

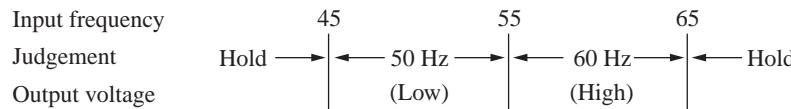

| 5       | Killer out, 50 Hz/60 Hz out, SECAM det. out | 37      | IF AGC filter                            |

| 6       | Chroma APC filter                           | 38      | Internal videol input                    |

| 7       | Chroma VCO (4.43 MHz)                       | 39      | SIF APC filter                           |

| 8       | Chroma VCO (3.58 MHz)                       | 40      | Internal video2 input                    |

| 9       | Black level det./Blank off SW               | 41      | VIF detect output                        |

| 10      | Y <sub>S</sub> input (fast blanking)        | 42      | VIF APC 1 filter                         |

| 11      | External R-input                            | 43      | VIF VCO (f <sub>P</sub> /2)              |

| 12      | External G-input                            | 44      | Video output                             |

| 13      | External B-input                            | 45      | Y-input                                  |

| 14      | V <sub>CC1</sub>                            | 46      | H, V sync. input                         |

| 15      | R-output                                    | 47      | V <sub>CC3-2</sub> (chroma/jungle/DAC)   |

| 16      | G-output                                    | 48      | Chroma input/black expansion start       |

| 17      | B-output                                    | 49      | GND (video/chroma/jungle)                |

| 18      | Hor.lock detect                             | 50      | FBP input                                |

| 19      | GND (R, G, B/I <sup>2</sup> C/DAC)          | 51      | V <sub>CC2</sub> (hor. stability supply) |

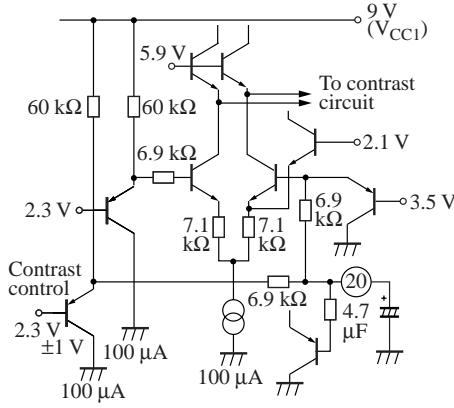

| 20      | ACL                                         | 52      | AFC2 filter                              |

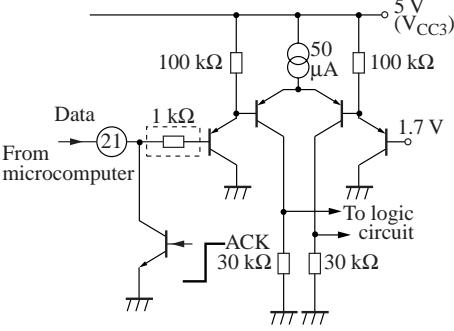

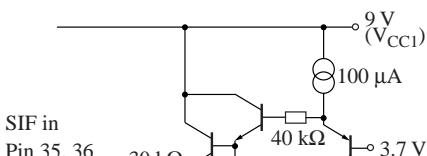

| 21      | SDA                                         | 53      | AFC1 filter                              |

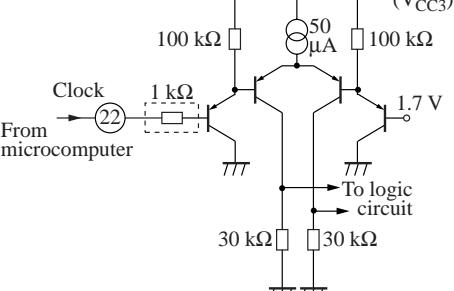

| 22      | SCL                                         | 54      | Hor. VCO (32 f <sub>H</sub> )            |

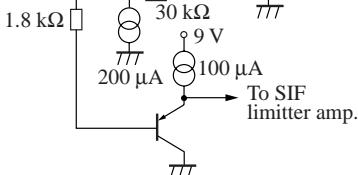

| 23      | V <sub>CC3-1</sub> (VIF/SIF)                | 55      | X-ray protection input                   |

| 24      | VIF1 input                                  | 56      | Hor. pulse output                        |

| 25      | VIF2 input                                  | 57      | Ver. sync. clamp                         |

| 26      | GND (VIF/SIF)                               | 58      | Ver. pulse output                        |

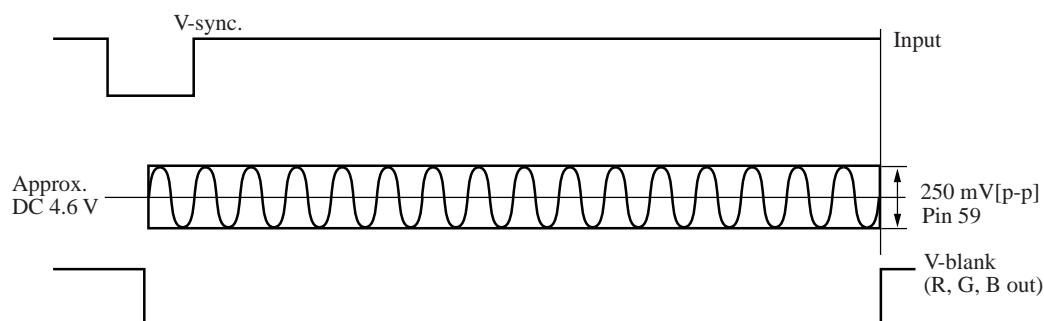

| 27      | RF AGC output                               | 59      | SECAM interface                          |

| 28      | Audio output                                | 60      | -(B-Y) output                            |

| 29      | De-emphasis                                 | 61      | -(R-Y) output                            |

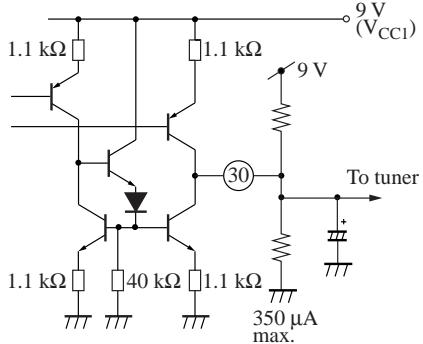

| 30      | AFT output                                  | 62      | Sandcastle pulse output                  |

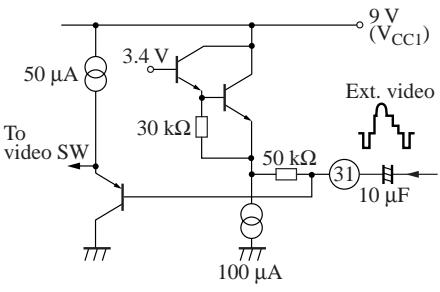

| 31      | External video input                        | 63      | -(B-Y) input                             |

| 32      | DC De-coupling filter                       | 64      | -(R-Y) input                             |

### ■ Absolute Maximum Ratings

| Parameter                        | Symbol    | Rating             | Unit |

|----------------------------------|-----------|--------------------|------|

| Supply voltage                   | $V_{CC}$  | $V_{CC1}$ (14)     | 10.5 |

|                                  |           | $V_{CC3}$ (23, 47) | 6.0  |

| Supply current                   | $I_{CC}$  | $I_{14}$           | 67   |

|                                  |           | $I_{23+47}$        | 126  |

|                                  |           | $I_{51}$           | 27   |

| Power dissipation *2             | $P_D$     | 1 480              | mW   |

| Operating ambient temperature *1 | $T_{opr}$ | -20 to +70         | °C   |

| Storage temperature *1           | $T_{stg}$ | -55 to +150        | °C   |

Note) \*1: Except for the operating ambient temperature, and storage temperature, all ratings are for  $T_a = 25^\circ\text{C}$ .

\*2: The power dissipation shown is for the IC package in free air at  $T_a = 70^\circ\text{C}$ .

### ■ Recommended Operating Range

| Parameter        | Symbol    | Range         | Unit |

|------------------|-----------|---------------|------|

| Supply voltage   | $V_{CC1}$ | 8.1 to 9.9    | V    |

|                  | $V_{CC3}$ | 4.5 to 5.5    |      |

| Terminal voltage | $V_5$     | 0 to 6        | V    |

|                  | $V_{10}$  | 0 to 6        |      |

|                  | $V_{11}$  | 0 to 6        |      |

|                  | $V_{12}$  | 0 to 6        |      |

|                  | $V_{13}$  | 0 to 6        |      |

|                  | $V_{21}$  | 0 to 6        |      |

|                  | $V_{22}$  | 0 to 6        |      |

|                  | $V_{27}$  | 0 to 10.5     |      |

|                  | $V_{30}$  | 0 to 10.5     |      |

|                  | $V_{48}$  | 0 to $V_{14}$ |      |

|                  | $V_{50}$  | 0 to $V_{47}$ |      |

|                  | $V_{55}$  | 0 to 2        |      |

|                  | $V_{59}$  | 0 to $V_{14}$ |      |

| Supply current   | $I_{51}$  | 10 to 25      | mA   |

| Circuit current  | $I_{15}$  | -3.2 to +0.6  | mA   |

|                  | $I_{16}$  | -3.2 to +0.6  |      |

|                  | $I_{17}$  | -3.2 to +0.6  |      |

|                  | $I_{41}$  | -0.8 to +0.8  |      |

|                  | $I_{44}$  | -1.1 to +0.4  |      |

|                  | $I_{46}$  | -0.8 to +0.1  |      |

## ■ Recommended Operating Range (continued)

| Parameter       | Symbol   | Range        | Unit |

|-----------------|----------|--------------|------|

| Circuit current | $I_{56}$ | –6.4 to +0.1 | mA   |

|                 | $I_{58}$ | –0.8 to +0.1 |      |

|                 | $I_{59}$ | –0.3 to +0.1 |      |

Note) Do not apply external currents or voltages to any pins not specifically mentioned.

For circuit currents, '+' denotes current flowing into the IC, and '-' denotes current flowing out of the IC.

■ Electrical Characteristics at  $T_a = 25^\circ\text{C}$

| Parameter                          | Symbol   | Conditions                                                                  | Min | Typ | Max | Unit     |

|------------------------------------|----------|-----------------------------------------------------------------------------|-----|-----|-----|----------|

| <b>Power Supply</b>                |          |                                                                             |     |     |     |          |

| Supply current 1                   | $I_{14}$ | Current at $V_{14} = 9\text{ V}$                                            | 39  | 48  | 57  | mA       |

| Supply current 2                   | $I_{23}$ | Current at $V_{23} = 5\text{ V}$                                            | 7   | 10  | 13  | mA       |

| Supply current 3                   | $I_{47}$ | Current at $V_{47} = 5\text{ V}$                                            | 49  | 63  | 77  | mA       |

| Stabilized supply voltage          | $V_{51}$ | Voltage at $I_{51} = 15\text{ mA}$                                          | 5.8 | 6.5 | 7.2 | V        |

| Stabilized supply current          | $I_{51}$ | Current at $V_{51} = 5\text{ V}$                                            | 2   | 5   | 7   | mA       |

| Stabilized supply input resistance | $R_{51}$ | DC measurement, slant between at $I_{51} = 10\text{ mA}$ and $25\text{ mA}$ | 1   | 5   | 10  | $\Omega$ |

VIF circuit   Typical input;  $f_p = 38.9\text{ MHz}$ ,  $V_{IN} = 90\text{ dB}\mu$ , DAC data are typical

|                                                 |                   |                                                                                                     |      |      |      |                |

|-------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------|------|------|------|----------------|

| Video detection output (typ.)                   | $V_{PO}$          | Modulation $m = 87.5\%$ , data $0B = 44$                                                            | 1.7  | 2.1  | 2.5  | V[p-p]         |

| Video detection output (max.)                   | $V_{POmax}$       | $0B = 74$                                                                                           | 1.9  | 2.6  | 3.3  | V[p-p]         |

| Video detection output (min.)                   | $V_{POmin}$       | $0B = 04$                                                                                           | 1.1  | 1.6  | 2.1  | V[p-p]         |

| Video detection output-frequency characteristic | $f_{PC}$          | Frequency which becomes –3 dB for 1 MHz output                                                      | 5.5  | 8    | 12   | MHz            |

| Synchronous peak value voltage                  | $V_{SP}$          | Synchronized peak value voltage at V[p-0] measurement                                               | 1.6  | 2.0  | 2.4  | V              |

| APC high-level pull-in range                    | $f_{PPH}$         | High-pass side pull-in range (difference from $f_p = 38.9\text{ MHz}$ )                             | 1.0  | 2.0  | —    | MHz            |

| APC low-level pull-in range                     | $f_{PPL}$         | Low-pass side pull-in range (difference from $f_p = 38.9\text{ MHz}$ )                              | —    | –2.0 | –1.0 | MHz            |

| RF AGC delay point adjustable range *1          | $\Delta V_{RFDP}$ | Delay point in which data are $0A = 00$ to $3F$ (input at $V_{27} = \text{approx. } 6.5\text{ V}$ ) | 75   | —    | 95   | $\text{dB}\mu$ |

| VCO free-running frequency                      | $\Delta f_p$      | Dispersion without $V_{IN}$ $V_{37}$ (IF AGC) = 0 V (measurement of the difference from 38.9 MHz)   | –1.2 | 0    | 1.2  | MHz            |

| RF AGC maximum sink current                     | $I_{RFmax}$       | Max. current IC can sink when pin 27 is low                                                         | 1.5  | 3.0  | —    | mA             |

| RF AGC minimum sink current                     | $I_{RFmin}$       | IC leak current at which pin 27 is high                                                             | –50  | 0    | 50   | $\mu\text{A}$  |

Note) \*1 to \*9: Refer to "Explanation of test methods".

■ Electrical Characteristics at  $T_a = 25^\circ\text{C}$  (continued)

| Parameter                                                                                                            | Symbol              | Conditions                                                                 | Min  | Typ  | Max  | Unit             |

|----------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------|------|------|------|------------------|

| VIF circuit (continued) Typical input; $f_p = 38.9 \text{ MHz}$ , $V_{IN} = 90 \text{ dB}\mu$ , DAC data are typical |                     |                                                                            |      |      |      |                  |

| AFT discrimination sensitivity <sup>*2</sup>                                                                         | $\mu_{AFT}$         | $\Delta f = \pm 25 \text{ kHz}$                                            | 40   | 57   | 75   | $\text{mV/kHz}$  |

| AFT center voltage                                                                                                   | $V_{AFT}$           | $V_{30}$ at $V_{IN}$ without input                                         | 4.0  | 4.5  | 5.0  | $\text{V}$       |

| AFT maximum output voltage                                                                                           | $V_{AFT\text{max}}$ | $V_{30}$ at $f = f_p - 500 \text{ kHz}$                                    | 7.8  | 8.1  | 8.7  | $\text{V}$       |

| AFT minimum output voltage                                                                                           | $V_{AFT\text{min}}$ | $V_{30}$ at $f = f_p + 500 \text{ kHz}$                                    | 0.3  | 0.8  | 1.0  | $\text{V}$       |

| Detection output resistance                                                                                          | $R_{O41}$           | DC measurement,<br>$I_O = -0.4 \text{ V to } -1.0 \text{ mA}$              | 70   | 120  | 170  | $\Omega$         |

| SIF circuit Typical input; $f_S = 6.0 \text{ MHz}$ , $f_M = 400 \text{ Hz}$ , $V_{IN} = 90 \text{ dB}\mu$            |                     |                                                                            |      |      |      |                  |

| Audio detection output (PAL, SIF1)                                                                                   | $V_{SOP36}$         | $\Delta f = \pm 50 \text{ kHz}$<br>0B-D3 = 0                               | 0.90 | 1.15 | 1.40 | $\text{V[rms]}$  |

| Audio detection output (PAL, SIF2)                                                                                   | $V_{SOP35}$         | $\Delta f = \pm 50 \text{ kHz}$<br>0B-D3 = 0                               | 0.90 | 1.15 | 1.40 | $\text{V[rms]}$  |

| Audio detection output (PAL, SIF3)                                                                                   | $V_{SOP33}$         | $\Delta f = \pm 50 \text{ kHz}$<br>0B-D3 = 0                               | 0.90 | 1.15 | 1.40 | $\text{V[rms]}$  |

| Audio detection output NTSC/PAL                                                                                      | $R_{SN/P}$          | $\Delta f = \pm 25 \text{ kHz}$<br>0B-D3 = 1, ratio to PAL ( $V_{SOP36}$ ) | -2.5 | -0.5 | 1.5  | $\text{dB}$      |

| Audio detection output linearity                                                                                     | $\Delta V_{SOP}$    | $f_S = 5.5 \text{ MHz and } 6.0 \text{ MHz}$<br>ratio to 6.5 MHz           | -3   | 0    | 3    | $\text{dB}$      |

| SIF pull-in range NTSC (4.5 MHz)                                                                                     | $f_{SNH}$<br>(4.5M) | Pull-in range of high-pass side                                            | 4.8  | 5.0  | —    | $\text{MHz}$     |

| SIF pull-in range NTSC (4.5 MHz)                                                                                     | $f_{SNL}$<br>(4.5M) | Pull-in range of low-pass side                                             | —    | 4.0  | 4.2  | $\text{MHz}$     |

| SIF pull-in range PAL (5.5 MHz)                                                                                      | $f_{SPH}$<br>(5.5M) | Pull-in range of high-pass side                                            | 5.8  | 6.0  | —    | $\text{MHz}$     |

| SIF pull-in range PAL (5.5 MHz)                                                                                      | $f_{SPL}$<br>(5.5M) | Pull-in range of low-pass side                                             | —    | 5.0  | 5.2  | $\text{MHz}$     |

| SIF pull-in range PAL (6.0 MHz)                                                                                      | $f_{SPH}$<br>(6.0M) | Pull-in range of high-pass side                                            | 6.3  | 6.5  | —    | $\text{MHz}$     |

| SIF pull-in range PAL (6.0 MHz)                                                                                      | $f_{SPL}$<br>(6.0M) | Pull-in range of low-pass side                                             | —    | 5.5  | 5.7  | $\text{MHz}$     |

| SIF pull-in range PAL (6.5 MHz)                                                                                      | $f_{SPH}$<br>(6.5M) | Pull-in range of high-pass side                                            | 6.8  | 7.0  | —    | $\text{MHz}$     |

| SIF pull-in range PAL (6.5 MHz)                                                                                      | $f_{SPL}$<br>(6.5M) | Pull-in range of low-pass side                                             | —    | 6.0  | 6.2  | $\text{MHz}$     |

| De-emphasis terminal output resistance (PAL)                                                                         | $R_{29P}$           | Impedance of pin 29 at PAL                                                 | 32   | 40   | 48   | $\text{k}\Omega$ |

| De-emphasis terminal output resistance (NTSC)                                                                        | $R_{29N}$           | Impedance of pin 29 at NTSC                                                | 48   | 60   | 72   | $\text{k}\Omega$ |

Note) \*1 to \*9: Refer to "Explanation of test methods".

■ Electrical Characteristics at  $T_a = 25^\circ\text{C}$  (continued)

| Parameter                                                                                                                 | Symbol           | Conditions                                                                                               | Min  | Typ  | Max  | Unit             |

|---------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------|------|------|------|------------------|

| AV SW circuit                                                                                                             |                  |                                                                                                          |      |      |      |                  |

| Video SW voltage gain                                                                                                     | $G_{VSW}$        | $f = 1 \text{ MHz}, V_{IN} = 1 \text{ V[p-p]}$                                                           | 5.7  | 6.7  | 7.7  | dB               |

| Video SW-frequency characteristic                                                                                         | $f_{VSW}$        | Frequency to become $-3 \text{ dB}$ from $f = 1 \text{ MHz}, V_{IN} = 0.714 \text{ V[0-p]}$              | 8    | 10   | —    | MHz              |

| Video SW external input terminal voltage                                                                                  | $V_{31}$         | DC measurement                                                                                           | 1.7  | 2.0  | 2.3  | V                |

| Video SW external output DC voltage                                                                                       | $V_{44E}$        | DC measurement,<br>03-D7 = 1, 0B-D7 = 1                                                                  | 4.2  | 4.8  | 5.4  | V                |

| Video SW external input resistance                                                                                        | $R_{I31}$        | DC measurement                                                                                           | 44   | 56   | 68   | $\text{k}\Omega$ |

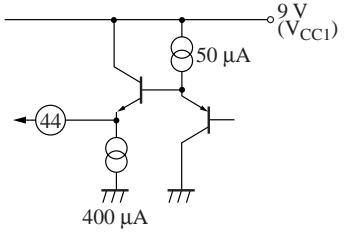

| Video SW output resistance                                                                                                | $R_{O44}$        | DC measurement,<br>$I_O = -0.6 \text{ mA}$ to $-1.0 \text{ mA}$                                          | 110  | 150  | 190  | $\Omega$         |

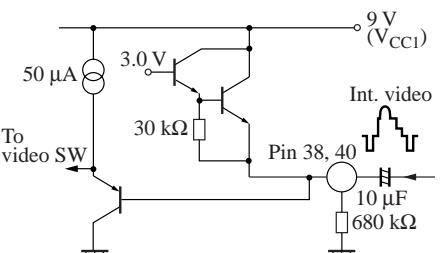

| Video SW internal clamp terminal voltage                                                                                  | $V_{38,40}$      | DC measurement,<br>$I_{IN} = -1.0 \text{ mA}$                                                            | 1.4  | 1.7  | 2.0  | V                |

| Video SW internal output DC voltage                                                                                       | $V_{44I}$        | DC measurement                                                                                           | 3.7  | 4.3  | 4.9  | V                |

| Audio SW voltage gain                                                                                                     | $G_{ASW}$        | Data 03-D7 = 1, 0B-D7 = 1,<br>(input from outside) $f = 400 \text{ Hz}$ ,<br>$V_{IN} = 1 \text{ V[p-p]}$ | -1   | 0    | 1    | dB               |

| Audio SW output DC voltage                                                                                                | $V_{28}$         | DC measurement                                                                                           | 3.7  | 4.2  | 4.7  | V                |

| Audio SW output resistance                                                                                                | $R_{O28}$        | DC measurement                                                                                           | 350  | 450  | 550  | $\Omega$         |

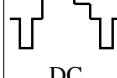

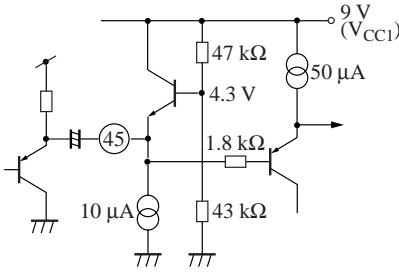

| Video signal processing circuit Typical input; $0.6 \text{ V[p-p]}$ ( $V_{BW} = 0.42 \text{ V[p-p]}$ stair-step) at G-out |                  |                                                                                                          |      |      |      |                  |

| Video output (typ.)                                                                                                       | $V_{YO}$         | Data 03 = 20 (typ.) (contrast)                                                                           | 2.0  | 2.5  | 3.0  | V[0-p]           |

| Video output (max.)                                                                                                       | $V_{Y0max}$      | Data 03 = 3F (max.)                                                                                      | 4.1  | 5.0  | 5.9  | V[0-p]           |

| Video output (min.)                                                                                                       | $V_{Y0min}$      | Data 03 = 00 (min.)                                                                                      | 0.15 | 0.50 | 1.00 | V[0-p]           |

| Contrast variable range                                                                                                   | $Y_{Cmax/min}$   | $03 = 3F$<br>$03 = 00$                                                                                   | 15   | 20   | 25   | dB               |

| Video frequency characteristic                                                                                            | $f_{YC}$         | Pin 33 = 5 V (sharpness), frequency to become $-3 \text{ dB}$ from $f = 0.2 \text{ MHz}$                 | 5.5  | 6.0  | —    | MHz              |

| Picture quality variable range                                                                                            | $Y_{Smax/min}$   | $\frac{V_{33} = 7V}{V_{33} = 5V} \quad f = 3.8 \text{ MHz}$                                              | 9    | 13   | 17   | dB               |

| Pedestal level (typ.)                                                                                                     | $V_{PED}$        | Data 02 = 40 (typ.) (brightness)                                                                         | 2.0  | 2.5  | 3.0  | V                |

| Pedestal variable width                                                                                                   | $\Delta V_{PED}$ | Difference between data 02 = 00 and 7F                                                                   | 2.15 | 2.75 | 3.35 | V                |

| Brightness control sensitivity                                                                                            | $\Delta V_{BRT}$ | Average amount of change per 1-step between data 02 = 30 and 50                                          | 14   | 20   | 26   | mV/Step          |

| Video input clamp voltage                                                                                                 | $V_{YCLP}$       | Pin 45 clamp voltage                                                                                     | 3.2  | 3.7  | 4.2  | V                |

| ACL sensitivity                                                                                                           | ACL              | Amount of change of Y-out, when $V_{20} = 3.0 \text{ V} \rightarrow 3.5 \text{ V}$                       | 2.7  | 3.2  | 3.7  | V/V              |

| Blanking level                                                                                                            | $V_{YBL}$        | Blanking pulse DC voltage                                                                                | —    | 1.0  | 1.5  | V                |

■ Electrical Characteristics at  $T_a = 25^\circ\text{C}$  (continued)

| Parameter                                     | Symbol            | Conditions                                                                     | Min  | Typ  | Max  | Unit          |

|-----------------------------------------------|-------------------|--------------------------------------------------------------------------------|------|------|------|---------------|

| Video signal processing circuit (continued)   |                   | Typical input; 0.6 V[p-p] ( $V_{BW} = 0.42$ V[p-p] stair-step) at G-out        |      |      |      |               |

| Service SW * threshold voltage                | $V_{STH}$         | Voltage at which vertical output stops when pin 20 (ACL) voltage is decreased  | —    | —    | 0.3  | V             |

| DC restoration ratio                          | $T_{DC}$          | APL10% to 90%<br>$T_{DC} = \frac{\Delta AC - \Delta DC}{\Delta AC} \times 100$ | 90   | 100  | 110  | %             |

| Video input clamp current                     | $I_{YCLP}$        | DC measurement; Sink current inside of IC                                      | 6    | 11   | 16   | $\mu\text{A}$ |

| Pedestal difference voltage                   | $\Delta V_{IPL}$  | Pedestal difference voltage of R, G, B-out                                     | -0.2 | 0    | 0.2  | V             |

| Brightness voltage tracking                   | $\Delta T_{BL}$   | Ratio of R, G, B-out fluctuation level for data 02 (bright) = 20 to 60         | 0.9  | 1.0  | 1.1  | Time          |

| Video voltage gain relative ratio             | $\Delta G_{YC}$   | Output ratio of R, B-out against G-out                                         | 0.8  | 1.0  | 1.2  | Time          |

| Video voltage gain tracking                   | $\Delta T_{CONT}$ | Ratio of gain of R, G, B-out for data 03 (contrast) = 10 to 30                 | 0.9  | 1.0  | 1.1  | Time/ Time    |

| Color signal processing circuit               |                   | Burst 150 mV[p-p] (PAL), reference is B-out                                    |      |      |      |               |

| Color-difference output (typ.)                | $V_{CO}$          | Input; Color bar<br>Data 00 = 20 (typ.), 03 = 20 (typ.)                        | 2.9  | 3.7  | 4.5  | V[p-p]        |

| Color-difference output (max.)                | $V_{COmax}$       | Data 03 = 3F, amplitude of one side<br>03 = 20                                 | 2.6  | 3.3  | —    | V[0-p]        |

| Color-difference output (min.)                | $V_{COmin}$       | Data 00 = 00, 03 = 20                                                          | —    | —    | 100  | mV[p-p]       |

| Contrast adjustable range                     | $C_{Cmax/min}$    | $\frac{03 = 3F}{03 = 00} \quad 00 = 20$                                        | 15   | 20   | 25   | dB            |

| ACC characteristic 1                          | ACC1              | Burst 150 mV[p-p] → 300 mV[p-p]                                                | 0.9  | 1.0  | 1.2  | Time          |

| ACC characteristic 2                          | ACC2              | Burst 150 mV[p-p] → 30 mV[p-p]                                                 | 0.8  | 1.0  | 1.2  | Time          |

| NTSC tint center                              | $\Delta\theta_C$  | The difference from data 01 = 20 at which tint is adjusted to center           | -7   | 0    | 7    | Step          |

| NTSC tint adjustable range 1                  | $\Delta\theta_1$  | Input; Rainbow data 01 = 3F                                                    | 30   | 50   | 65   | deg           |

| NTSC tint adjustable range 2                  | $\Delta\theta_2$  | Input; Rainbow data 01 = 00                                                    | -65  | -50  | -30  | deg           |

| Color-difference output ratio (R)             | R/B               | Input; Rainbow for both PAL/NTSC                                               | 0.46 | 0.56 | 0.66 | Time          |

| Color-difference output ratio (G)             | G/B               | Input; Rainbow for both PAL/NTSC                                               | 0.28 | 0.34 | 0.40 | Time          |

| Color-difference output angle (R)             | $\angle R$        | Input; Rainbow for both PAL/NTSC                                               | 78   | 90   | 102  | deg           |

| Color-difference output angle (G)             | $\angle G$        | Input; Rainbow for both PAL/NTSC                                               | 224  | 236  | 248  | deg           |

| PAL color killer tolerance                    | $V_{KILLP}$       | 0 dB = 150 mV[p-p]                                                             | -57  | -44  | -34  | dB            |

| NTSC color killer tolerance                   | $V_{KILLN}$       | 0 dB = 150 mV[p-p]                                                             | -57  | -44  | -34  | dB            |

| APC high-lebel pull-in range                  | $f_{CPH}$         | Both PAL/NTSC                                                                  | 450  | 700  | —    | Hz            |

| APC low-lebel pull-in range                   | $f_{CPL}$         | Both PAL/NTSC                                                                  | —    | -700 | -450 | Hz            |

| Color killer detection output voltage (color) | $V_{KC}$          | $V_5$ , killer out at which chroma input data 0A-D6 = 0, 0A-D7 = 1             | 4.5  | 5.0  | —    | V             |

Note) \*: Since pin 20 is also used partly as service SW when used as ACL, a sufficient care must be taken so as not to become  $V_{20} < 0.9$  V in carrying out set design.

■ Electrical Characteristics at  $T_a = 25^\circ\text{C}$  (continued)

| Parameter                                                                               | Symbol             | Conditions                                                                 | Min  | Typ  | Max  | Unit    |

|-----------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------|------|------|------|---------|

| Color signal processing circuit (continued) Burst 150 mV[p-p] (PAL), reference is B-out |                    |                                                                            |      |      |      |         |

| Color killer detection output voltage (B & W)                                           | $V_{KBW}$          | $V_5$ , killer out at which chroma input data 0A-D6 = 0, 0A-D7 = 1         | 0    | 0.1  | 0.5  | V       |

| Demodulation output -(B-Y)                                                              | $V_{DB}$           | Input; Color bar measured at pin 60 for both PAL/NTSC                      | 555  | 695  | 835  | mV[p-p] |

| Demodulation output -(R-Y)                                                              | $V_{DR}$           | Input; Color bar measured at pin 61 for both PAL/NTSC                      | 430  | 540  | 650  | mV[p-p] |

| Demodulation output angle $\angle(B-Y)$                                                 | $\angle R_{DB}$    | B-Y axis out of phase                                                      | -6   | 0    | 6    | deg     |

| Demodulation output angle $\angle(R-Y)$                                                 | $\angle R_{DR}$    | B-Y axis phase difference                                                  | 84   | 90   | 96   | deg     |

| CW output level (4.43 MHz) <sup>*3</sup>                                                | $V_{CWP}$          | AC component, when VCO is set at 4.43 MHz                                  | 250  | 350  | 450  | mV[p-p] |

| CW output level (3.58 MHz) <sup>*3</sup>                                                | $V_{CWN}$          | AC component, when VCO is set at 3.58 MHz                                  | —    | —    | 50   | mV[p-p] |

| CW output level period (SECAM) <sup>*3</sup>                                            | $t_{CW}$           | Period in which CW is outputted at SECAM, PAL                              | 1.31 | 1.41 | 1.51 | ms      |

| SECAM judgment current                                                                  | $I_{SECAM}$        | The minimum value to take out current from pin 59 to discriminate as SECAM | 50   | 100  | 150  | μA      |

| SECAM judgment output                                                                   | $V_{SE}$           | $V_5$ , det. out, when SECAM signal input data 0A-D6 = 1, 0A-D7 = 0, SECAM | 4.5  | 5.0  | —    | V       |

| PAL/NTSC DC level                                                                       | $V_{59PN}$         | $V_{59}$ DC level at PAL/NTSC                                              | 0.8  | 1.3  | 1.65 | V       |

| SECAM DC level                                                                          | $V_{59S}$          | $V_{59}$ DC level at SECAM                                                 | 4.1  | 4.6  | 5.1  | V       |

| RGB processing circuit DAC data are typicals                                            |                    |                                                                            |      |      |      |         |

| Drive adjusting range                                                                   | $G_{DV}$           | AC change amount for R, B-out between drive adjustment max. and min.       | 5    | 6    | 7    | dB      |

| Offset adjusting range                                                                  | $V_{CUT-OFF}$      | DC change amount for R, G, B-out between offset adjustment max. and min.   | 2.2  | 2.5  | 2.8  | V       |

| $Y_S$ threshold voltage                                                                 | $V_{YSON}$         | Minimum DC voltage at which $Y_S$ turns on                                 | 1.0  | —    | —    | V       |

| $Y_S$ threshold voltage                                                                 | $V_{YSOF}$         | Maximum DC voltage at which $Y_S$ turns off                                | —    | —    | 0.4  | V       |

| External R, G, B pedestal difference voltage                                            | $\Delta V_{EPL}$   | $Y_S = 1$ V is applied                                                     | -200 | 0    | 200  | mV      |

| Internal and external pedestal difference voltage                                       | $\Delta V_{PL/IE}$ | Internal part — external part                                              | -200 | 0    | 200  | mV      |

| External R, G, B output voltage                                                         | $V_{ERGB}$         | Input 0.7 V[p-p], contrast 03 = 20 (typ.)                                  | 1.8  | 2.2  | 2.7  | V[p-p]  |

| External R, G, B output difference voltage                                              | $\Delta V_{ERGB}$  | Input 0.7 V[p-p], contrast 03 = 20 (typ.)                                  | 0.8  | 1.0  | 1.2  | Time    |

| External R, G, B contrast variable range                                                | $EC_{max/min}$     | $03 = 3F$<br>$03 = 00$                                                     | 12   | 17   | 22   | dB      |

Note) \*1 to \*9: Refer to "Explanation of test methods".

■ Electrical Characteristics at  $T_a = 25^\circ\text{C}$  (continued)

| Parameter                                                | Symbol          | Conditions                                                                                       | Min       | Typ       | Max   | Unit          |

|----------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------|-----------|-----------|-------|---------------|

| RGB processing circuit (continued) DAC data are typicals |                 |                                                                                                  |           |           |       |               |

| External R, G, B frequency characteristic                | $f_{RGBC}$      | Input 0.2 V[p-p]                                                                                 | 8         | 10        | —     | MHz           |

| Internal and external R, G, B output voltage ratio       | $V_{E/I}$       | External part 0.7 V[p-p]/internal part 0.6 V[p-p] input, contrast 03 = 20 (typ.)                 | 0.78      | 0.92      | 1.06  | Time          |

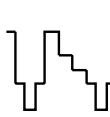

| Synchronizing signal processing circuit                  |                 |                                                                                                  |           |           |       |               |

| Horizontal free run frequency                            | $f_{HO}$        | Without sync. signal input                                                                       | 15.33     | 15.63     | 15.93 | kHz           |

| Horizontal output pulse duty cycle                       | $\tau_{HO}$     | Upward pulse duty cycle                                                                          | 31        | 37        | 43    | %             |

| Horizontal pull-in range                                 | $f_{HP}$        | Difference from $f_H = 15.625$ kHz                                                               | $\pm 500$ | $\pm 650$ | —     | Hz            |

| PAL horizontal free run frequency                        | $f_{VO-P}$      | Data 01-D7 = 1, 02-D7 = 0, forced 50 Hz mode, without sync. signal input                         | 48        | 50        | 52    | Hz            |

| NTSC vertical free run frequency                         | $f_{VO-N}$      | Data 01-D7 = 1, 02-D7 = 1, forced 60 Hz mode, without sync. signal input                         | 58        | 60        | 62    | Hz            |

| Vertical output pulse width                              | $\tau_{VO}$     | For both PAL/NTSC                                                                                | 9         | 10        | 11    | 1/fH          |

| PAL vertical pull-in range                               | $f_{VPP}$       | $f_H = 15.625$ kHz, forced 50 Hz mode                                                            | 46        | —         | 54    | Hz            |

| NTSC vertical pull-in range                              | $f_{VPN}$       | $f_H = 15.75$ kHz, forced 60 Hz mode                                                             | 56        | —         | 64    | Hz            |

| Horizontal high-level output voltage                     | $V_{56H}$       | High-level DC voltage                                                                            | 2.8       | 3.1       | 3.4   | V             |

| Horizontal low-level output voltage                      | $V_{56L}$       | Low-level DC voltage                                                                             | —         | —         | 0.3   | V             |

| Vertical high-level output voltage                       | $V_{58H}$       | High-level DC voltage                                                                            | 3.9       | 4.2       | 4.5   | V             |

| Vertical low-level output voltage                        | $V_{58L}$       | Low-level DC voltage                                                                             | —         | —         | 0.3   | V             |

| Screen center variable range                             | $\Delta T_{HC}$ | Change amount of phase difference between sync. and H-out of data 0B = 40 to 47                  | 2.6       | 3.2       | 4.4   | $\mu\text{s}$ |

| Overvoltage protection operation voltage                 | $V_{X-RAY}$     | The pin 55 minimum voltage at which H-out does not appear any longer                             | 0.60      | 0.68      | 0.76  | V             |

| Vertical frequency discrimination (50)                   | $f_{50}$        | Vertical frequency at which $V_5$ becomes low (< 0.5 V)                                          | 47        | —         | 55    | Hz            |

| Vertical frequency discrimination (60)                   | $f_{60}$        | Vertical frequency at which $V_5$ becomes high (> 4.5 V)                                         | 57        | —         | 63    | Hz            |

| Synchronous signal clamp voltage                         | $V_{46}$        | $V_{46}$ clamp voltage                                                                           | 1.1       | 1.4       | 1.7   | V             |

| Horizontal output start voltage                          | $V_{fHS}$       | The minimum $V_{50}$ at $f_0 > 10$ kHz and horizontal oscillation output is higher than 1 V[p-p] | 3.4       | 4.2       | 5.0   | V             |

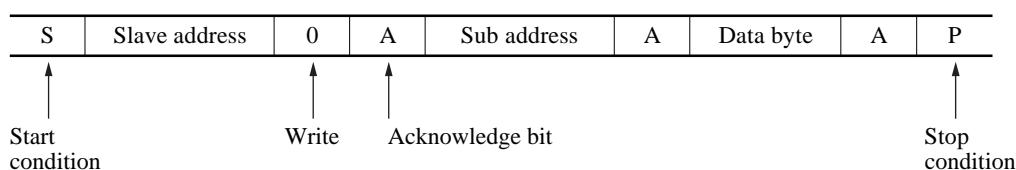

| $\text{I}^2\text{C}$ interface                           |                 |                                                                                                  |           |           |       |               |

| Sink current when ACK                                    | $I_{ACK}$       | The maximum value of pin 21 sink current at ACK                                                  | 1.5       | 2.0       | 5.0   | mA            |

| SCL, SDA signal high level input                         | $V_{IHI}$       |                                                                                                  | 3.1       | —         | —     | V             |

| SCL, SDA signal low level input                          | $V_{ILO}$       |                                                                                                  | —         | —         | 0.9   | V             |

| Allowable maximum input frequency                        | $f_{I_{max}}$   |                                                                                                  | —         | —         | 100   | kbit/s        |

## ■ Electrical Characteristics at $T_a = 25^\circ\text{C}$ (continued)

- Design reference data

Note) The characteristics listed below are theoretical values based on the IC design and are not guaranteed.

| Parameter                                              | Symbol                                                                | Conditions                                                                                                  | Min | Typ | Max      | Unit             |

|--------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|-----|----------|------------------|

| VIF circuit                                            | Typical input; $f_p = 38.9 \text{ MHz}$ , $V_{IN} = 90 \text{ dB}\mu$ |                                                                                                             |     |     |          |                  |

| Input sensitivity                                      | $V_{PS}$                                                              | Input level at which $V_{POI}$ becomes $-3 \text{ dB}$                                                      | —   | 45  | —        | $\text{dB}\mu$   |

| Maximum allowable input                                | $V_{Pmax}$                                                            | Input level at which $V_{POI}$ becomes $+1 \text{ dB}$                                                      | —   | 110 | —        | $\text{dB}\mu$   |

| SN ratio                                               | $SN_p$                                                                |                                                                                                             | 50  | —   | —        | $\text{dB}$      |

| Differential gain                                      | $DG_p$                                                                |                                                                                                             | —   | —   | 5        | %                |

| Differential phase                                     | $DP_p$                                                                |                                                                                                             | —   | —   | 5        | deg              |

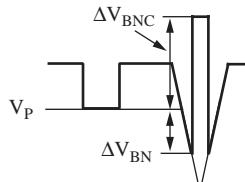

| Black-noise detection level <sup>*4</sup>              | $\Delta V_{BN}$                                                       | Difference from sync. peak value                                                                            | —   | -45 | —        | IRE              |

| Black-noise clamp level <sup>*4</sup>                  | $\Delta V_{BNC}$                                                      | Difference from sync. peak value                                                                            | —   | 45  | —        | IRE              |

| RF-AGC operation sensitivity                           | $G_{RF}$                                                              | Input level difference, when $V_{27} = 1 \text{ V}$ goes to $7 \text{ V}$                                   | 0.5 | —   | 3.0      | $\text{dB}$      |

| VCO switch-on drift                                    | $\Delta f_{PD}$                                                       | Frequency drift from 5 sec. to 5 min. after SW-on                                                           | —   | —   | 200      | $\text{kHz}$     |

| Inter modulation <sup>*5</sup>                         | IM                                                                    | $V_{fC} - V_{fP} = -2 \text{ dB}$ , $V_{fS} - V_{fP} = -12 \text{ dB}$                                      | 46  | —   | —        | $\text{dB}$      |

| RF-AGC adjustment sensitivity                          | $S_{RF}$                                                              | Output voltage in data 1-step, average change amount of $V_{27}$                                            | 1   | —   | 4        | $\text{V/step}$  |

| AFT offset adjustment sensitivity                      | $S_{AFT}$                                                             | Output voltage in data 1-step, average change amount of $V_{30}$                                            | 0.1 | —   | 0.3      | $\text{V/step}$  |

| Video detection output fluctuation with $V_{CC}$       | $\Delta V_{P/V}$                                                      | $V_{CC} = \pm 10\%$                                                                                         | —   | —   | $\pm 15$ | %                |

| Video detection output-temperature characteristics     | $\Delta V_{P/T}$                                                      | $T_a = -20^\circ\text{C}$ to $+70^\circ\text{C}$                                                            | —   | —   | $\pm 10$ | %                |

| Input resistance (pin 24, pin 25)                      | $R_{I24,25}$                                                          | $f = 38.9 \text{ MHz}$                                                                                      | —   | 1.2 | —        | $\text{k}\Omega$ |

| Input capacitance (pin 24, pin 25)                     | $C_{I24,25}$                                                          | $f = 38.9 \text{ MHz}$                                                                                      | —   | 4.0 | —        | $\text{pF}$      |

| Sound-IF output level                                  | $V_{SIF}$                                                             | $f_S = 38.9 \text{ MHz} - 6.0 \text{ MHz}$ , P/S = 20 dB                                                    | 90  | —   | 110      | $\text{dB}\mu$   |

| VCO control sensitivity                                | $\beta_p$                                                             | $\Delta V_{42} = \pm 0.1 \text{ V}$                                                                         | 2.0 | —   | 3.5      | $\text{kHz/mV}$  |

| VCO adjustment range                                   | $f_{VCO}$                                                             | Free-running frequency change width at data $0C = 00$ to $7F$                                               | 3   | —   | 5        | $\text{MHz}$     |

| RF-AGC delay point-temperature characteristics         | $\Delta V_{DP/T}$                                                     | $T_a = -20^\circ\text{C}$ to $+70^\circ\text{C}$                                                            | —   | —   | 5        | $\text{dB}$      |

| VCO free-running frequency-temperature characteristics | $\Delta f_{P/T}$                                                      | $T_a = -20^\circ\text{C}$ to $+70^\circ\text{C}$                                                            | —   | 300 | —        | $\text{kHz}$     |

| AFT center frequency-temperature characteristics       | $\Delta f_{AFT/T}$                                                    | Input frequency at which AFT output voltage becomes 4.5 V, $T_a = -20^\circ\text{C}$ to $+70^\circ\text{C}$ | —   | 300 | —        | $\text{kHz}$     |

| External mode output DC voltage                        | $V_{41EXT}$                                                           | Output DC voltage at AV-SW outside mode                                                                     | 0.5 | 1.0 | 1.8      | $\text{V}$       |

Note) \*1 to \*9: Refer to "Explanation of test methods".

■ Electrical Characteristics at  $T_a = 25^\circ\text{C}$  (continued)

## • Design reference data (continued)

Note) The characteristics listed below are theoretical values based on the IC design and are not guaranteed.

| Parameter                                                                                                                        | Symbol           | Conditions                                                                                                                                                       | Min  | Typ  | Max      | Unit             |

|----------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|------------------|

| <b>SIF circuit</b> Typical input; $f_S = 6.0 \text{ MHz}$ , $f_M = 400 \text{ Hz}$ , $V_{IN} = 90 \text{ dB}\mu$                 |                  |                                                                                                                                                                  |      |      |          |                  |

| Input limiting level                                                                                                             | $V_{LIM}$        | Input level, when $V_{SOP}$ becomes $-3 \text{ dB}$                                                                                                              | —    | —    | 50       | $\text{dB}\mu$   |

| AM rejection ratio                                                                                                               | AMR              | AM = 30%                                                                                                                                                         | 55   | —    | —        | $\text{dB}$      |

| Total harmonic distortion                                                                                                        | THD              | $\Delta f = \pm 50 \text{ kHz}$                                                                                                                                  | —    | —    | 1.0      | %                |

| SN ratio                                                                                                                         | $SN_A$           | $\Delta f = \pm 50 \text{ kHz}$ , $f_M = 400 \text{ Hz}$ , on/off                                                                                                | 55   | —    | —        | $\text{dB}$      |

| Audio output fluctuation with $V_{CC}$                                                                                           | $\Delta V_{S/V}$ | $V_{CC} = \pm 10\%$                                                                                                                                              | —    | —    | $\pm 10$ | %                |

| Audio output - temperature characteristics                                                                                       | $\Delta V_{S/T}$ | $T_a = -20^\circ\text{C}$ to $+70^\circ\text{C}$                                                                                                                 | —    | —    | $\pm 10$ | %                |

| SIF input resistance                                                                                                             | $R_{I35}$        | DC measurement                                                                                                                                                   | —    | 31.5 | —        | $\text{k}\Omega$ |

| SIF input resistance                                                                                                             | $R_{I36}$        | DC measurement                                                                                                                                                   | —    | 31.5 | —        | $\text{k}\Omega$ |

| <b>AV-SW circuit</b>                                                                                                             |                  |                                                                                                                                                                  |      |      |          |                  |

| Video-SW crosstalk (inside $\rightarrow$ inside)                                                                                 | $C_{TVII}$       | $f = 1 \text{ MHz}$ , $V_{IN} = 1 \text{ V[p-p]}$ , inside $\rightarrow$ inside                                                                                  | —    | —    | -55      | $\text{dB}$      |

| Video-SW crosstalk (outside $\rightarrow$ inside)                                                                                | $C_{TVEI}$       | $f = 1 \text{ MHz}$ , $V_{IN} = 1 \text{ V[p-p]}$ , inside $\rightarrow$ outside, outside $\rightarrow$ inside                                                   | —    | —    | -55      | $\text{dB}$      |

| Audio-SW crosstalk (inside $\rightarrow$ inside)                                                                                 | $C_{TAII}$       | $f_S = 6.5 \text{ MHz}$ , $f_M = 400 \text{ Hz}$ , $V_{IN} = 1 \text{ V[p-p]}$ , $f_S = 6.5 \text{ MHz}$ , $f_M = 1.0 \text{ kHz}$ , $V_{IN} = 1 \text{ V[p-p]}$ | —    | —    | -60      | $\text{dB}$      |

| <b>Video signal processing circuit</b> Typical input; $0.6 \text{ V[p-p]}$ ( $V_{BW} = 0.42 \text{ V[p-p]}$ stair-step) at G-out |                  |                                                                                                                                                                  |      |      |          |                  |

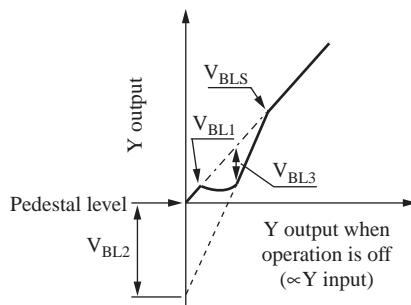

| Black level expansion 1 <sup>*6</sup>                                                                                            | $V_{BL1}$        | Input: All black, difference between pin 9 = 9 V and open (with RC)                                                                                              | -100 | 0    | 100      | $\text{mV}$      |

| Black level expansion 2 <sup>*6</sup>                                                                                            | $V_{BL2}$        | Input: All black, difference between pin 9 = 3 V and 9 V                                                                                                         | 400  | 700  | 1000     | $\text{mV}$      |

| Black level expansion 3 <sup>*6</sup>                                                                                            | $V_{BL3}$        | Input: Approx. 20 IRE, voltage difference between pin 9 = open and 9 V at 03 (contrast) = 3F (max.)                                                              | 100  | 300  | 500      | $\text{mV}$      |

| Contrast change by sharpness                                                                                                     | $\Delta V_{CS}$  | Y-out output difference at sharpness between max. and min.                                                                                                       | -300 | 0    | 300      | $\text{mV}$      |

| Brightness change by sharpness                                                                                                   | $\Delta V_{BS}$  | Pedestal level DC difference at sharpness between max. and min.                                                                                                  | -250 | 0    | 250      | $\text{mV}$      |

| Input dynamic change                                                                                                             | $V_{Imax}$       | 03 (contrast) = 20 (typ.)                                                                                                                                        | —    | —    | 1.6      | $\text{V[p-p]}$  |

| Y-signal SN-ratio                                                                                                                | $SN_Y$           | 03 (contrast) = 3F (max.)                                                                                                                                        | 53   | —    | —        | $\text{dB}$      |

| Black level expansion start point <sup>*6</sup>                                                                                  | $V_{BLS}$        | Start point at $V_{48} = 4.5 \text{ V}$                                                                                                                          | 37   | 42   | 47       | IRE              |

| Video output fluctuation with $V_{CC}$                                                                                           | $\Delta V_{Y/V}$ | $V_{CC1} = 9 \text{ V}$ (allowance: $\pm 10\%$ )                                                                                                                 | —    | —    | $\pm 15$ | %                |

| Video output - temperature characteristics                                                                                       | $\Delta V_{Y/T}$ | $T_a = -20^\circ\text{C}$ to $+70^\circ\text{C}$                                                                                                                 | —    | —    | $\pm 10$ | %                |

| ACL start point                                                                                                                  | $V_{ACL}$        | $V_{20}$ at which the output amplitude becomes 90% when ACL terminal ( $V_{20}$ ) is decreased from 5 V                                                          | 3.4  | 3.7  | 4.0      | $\text{V}$       |

Note) \*1 to \*9: Refer to "Explanation of test methods".

■ Electrical Characteristics at  $T_a = 25^\circ\text{C}$  (continued)

## • Design reference data (continued)

Note) The characteristics listed below are theoretical values based on the IC design and are not guaranteed.

| Parameter                                                | Symbol                              | Conditions                                                                                          | Min       | Typ       | Max       | Unit                          |

|----------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------|-----------|-----------|-----------|-------------------------------|

| Color signal processing circuit                          |                                     |                                                                                                     |           |           |           |                               |

| Demodulation output residual carrier                     | $V_{\text{CAR1}}$                   | $2f_{\text{SC}}$ level of pin 60 and pin 61                                                         | —         | —         | 30        | mV                            |

| Color-difference output residual carrier                 | $V_{\text{CAR2}}$                   | $2f_{\text{SC}}$ level of pin 15, pin 16 and pin 17                                                 | —         | —         | 50        | mV                            |

| VCO free-running frequency (PAL)                         | $f_{\text{CP}}$                     | Difference from $f = 4.433619$ MHz                                                                  | -300      | —         | 300       | Hz                            |

| VCO free-running frequency (NTSC)                        | $f_{\text{CN}}$                     | Difference from $f = 3.579545$ MHz                                                                  | -300      | —         | 300       | Hz                            |

| $f_{\text{CO}}$ fluctuation with $V_{\text{CC}}$         | $\Delta f_{\text{C}}/V_{\text{CC}}$ | $V_{\text{CC1}} = 9$ V (allowance: $\pm 10\%$ ),<br>$V_{\text{CC3}} = 5$ V (allowance: $\pm 10\%$ ) | -300      | —         | 300       | Hz                            |

| Static phase error (PAL)                                 | $\Delta\theta_{\text{P}}$           | Tint gap at $\Delta f_{\text{C}} = -300$ Hz to $+300$ Hz change                                     | —         | —         | 5         | deg/<br>100 Hz                |

| Static phase error (NTSC)                                | $\Delta\theta_{\text{N}}$           | Tint gap at $\Delta f_{\text{C}} = -300$ Hz to $+300$ Hz change                                     | —         | —         | 5         | deg/<br>100 Hz                |

| PAL/NTSC ratio                                           | $R_{\text{P/N}}$                    | Output amplitude ratio between PAL and NTSC                                                         | 0.7       | 1.0       | 1.3       | Time                          |

| Line crawling                                            | $\Delta V_{\text{PAL}}$             | Pin 61: Output amplitude difference per 1H at -(R-Y) terminal                                       | —         | —         | 50        | mV                            |

| Color-difference output bandwidth                        | $f_{\text{CC}}$                     | Band to become $-3$ dB                                                                              | 1.0       | —         | —         | MHz                           |

| Color-difference output fluctuation with $V_{\text{CC}}$ | $\Delta V_{\text{C/V}}$             | $V_{\text{CC1}} = 9$ V (allowance: $\pm 10\%$ ),<br>$V_{\text{CC3}} = 5$ V (allowance: $\pm 10\%$ ) | —         | —         | $\pm 15$  | %                             |

| Color-difference output - temperature characteristics    | $\Delta V_{\text{CT}}$              | $T_a = -20^\circ\text{C}$ to $70^\circ\text{C}$                                                     | —         | —         | $\pm 15$  | %                             |

| PAL/NTSC output impedance                                | $R_{\text{O60,61PN}}$               | DC measurement                                                                                      | 400       | 510       | 620       | $\Omega$                      |

| SECAM output impedance                                   | $R_{\text{O60,61S}}$                | DC measurement                                                                                      | 100       | —         | —         | $\text{k}\Omega$              |

| Color, black & white DC difference voltage               | $\Delta V_{\text{CBW}}$             | Pedestal voltage difference between with and without burst signal                                   | -60       | 0         | 60        | mV                            |

| (C-Y)/Y ratio *7                                         | $R_{\text{C/Y}}$                    | Color bar input, B-out contrast typ.<br>color data 00 = 30                                          | 0.9       | 1.2       | 1.5       | $V[0\text{-p}]/V[0\text{-p}]$ |

| RGB processing circuit                                   |                                     |                                                                                                     |           |           |           |                               |

| $Y_S$ change-over speed                                  | $f_{\text{YS}}$                     | $f_{\text{YS}}$ , when $Y_S$ input is 3 V[0-p] and output level is $-3$ dB                          | 7         | —         | —         | MHz                           |

| Outside R, G, B input dynamic range                      | $V_{\text{DEXT}}$                   | Contrast max. data 03 = 3F                                                                          | 1.0       | —         | —         | V[p-p]                        |

| Inside and outside crosstalk                             | $CT_{\text{RGB}}$                   | Leakage at $f = 1$ MHz, 1 V[p-p],<br>$Y_S = 5$ V                                                    | —         | —         | -50       | dB                            |

| Synchronizing signal processing circuit                  |                                     |                                                                                                     |           |           |           |                               |

| Lock detection output voltage                            | $V_{\text{LD}}$                     | $V_{18}$ at horizontal AFC lock                                                                     | 5.7       | 6.3       | 6.9       | V                             |

| Lock detection charge and discharge current              | $I_{\text{LD}}$                     | DC measurement                                                                                      | $\pm 0.6$ | $\pm 0.8$ | $\pm 1.1$ | mA                            |

Note) \*1 to \*9: Refer to "Explanation of test methods".

■ Electrical Characteristics at  $T_a = 25^\circ\text{C}$  (continued)

## • Design reference data (continued)

Note) The characteristics listed below are theoretical values based on the IC design and are not guaranteed.

| Parameter                                           | Symbol     | Conditions                                                            | Min  | Typ  | Max  | Unit                      |

|-----------------------------------------------------|------------|-----------------------------------------------------------------------|------|------|------|---------------------------|

| Synchronizing signal processing circuit (continued) |            |                                                                       |      |      |      |                           |

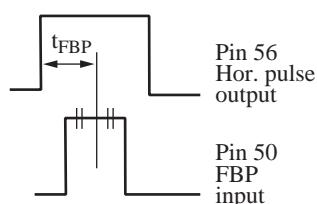

| FBR (R, G, B) slice level                           | $V_{FBP}$  | Pin 50 minimum voltage at which blanking is applied to R, G, B output | 0.4  | 0.75 | 1.1  | V                         |

| FBP (AFC2) slice level                              | $V_{FBPH}$ | Pin 50 minimum voltage in which AFC2 operates                         | 1.5  | 1.9  | 2.3  | V                         |

| Horizontal AFC $\mu$                                | $\mu_H$    | DC measurement                                                        | 30   | 37   | 44   | $\mu\text{A}/\mu\text{s}$ |

| Horizontal VCO $\beta$                              | $\beta_H$  | $\beta$ curve slant near $f = 15.75 \text{ kHz}$                      | 1.4  | 1.9  | 2.4  | $\text{Hz}/\text{mV}$     |

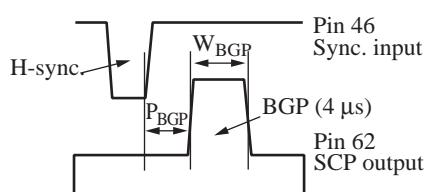

| Burst gate pulse position *8                        | $P_{BGP}$  | Delay from H sync. rise for both PAL/NTSC                             | 0.2  | 0.4  | 0.6  | $\mu\text{s}$             |

| PAL burst gate pulse width *8                       | $W_{BGPP}$ |                                                                       | 3.4  | 4.0  | 4.6  | $\mu\text{s}$             |

| NTSC burst gate pulse width *8                      | $W_{BGPN}$ |                                                                       | 2.5  | 3.0  | 3.5  | $\mu\text{s}$             |

| Burst gate pulse output voltage                     | $V_{BGP}$  | Pin 62 DC voltage during BGP period                                   | 4.5  | 4.7  | 4.9  | V                         |

| H blanking pulse output voltage                     | $V_{HBLK}$ | Pin 62 DC voltage during H blanking pulse period                      | 2.1  | 2.4  | 2.7  | V                         |

| V blanking pulse output voltage                     | $V_{VBLK}$ | Pin 62 DC voltage during V blanking pulse period                      | 2.1  | 2.4  | 2.7  | V                         |

| PAL V blanking pulse width                          | $W_{VP}$   | Pulse width at $f = 15.625 \text{ kHz}$                               | 1.31 | 1.41 | 1.51 | ms                        |

| NTSC V blanking pulse width                         | $W_{VN}$   | Pulse width at $f = 15.73 \text{ kHz}$                                | 1.01 | 1.11 | 1.21 | ms                        |

| FBP allowable range *9                              | $T_{FBP}$  | Time from H-out rise to FBP center                                    | 12   | —    | 19   | $\mu\text{s}$             |

| FBP maximum allowable input voltage                 | $V_{AFBP}$ |                                                                       | 2.5  | —    | 5.0  | V                         |

I<sup>2</sup>C interface

|                             |               |  |      |   |      |               |

|-----------------------------|---------------|--|------|---|------|---------------|

| Bus free before start       | $t_{BUF}$     |  | 4.0  | — | —    | $\mu\text{s}$ |

| Start condition set-up time | $t_{SU, STA}$ |  | 4.0  | — | —    | $\mu\text{s}$ |

| Start condition hold time   | $t_{HD, STA}$ |  | 4.0  | — | —    | $\mu\text{s}$ |

| Low period SCL, SDA         | $t_{LOW}$     |  | 4.0  | — | —    | $\mu\text{s}$ |

| High period SCL             | $t_{HIGH}$    |  | 4.0  | — | —    | $\mu\text{s}$ |

| Rise time SCL, SDA          | $t_r$         |  | —    | — | 1.0  | $\mu\text{s}$ |

| Fall time SCL, SDA          | $t_f$         |  | —    | — | 0.35 | $\mu\text{s}$ |

| Data set-up time (write)    | $t_{SU, DAT}$ |  | 0.25 | — | —    | $\mu\text{s}$ |

| Data hold time (write)      | $t_{HD, DAT}$ |  | 0    | — | —    | $\mu\text{s}$ |

| Acknowledge set-up time     | $t_{SU, ACK}$ |  | —    | — | 3.5  | $\mu\text{s}$ |

| Acknowledge hold time       | $t_{HD, ACK}$ |  | 0    | — | —    | $\mu\text{s}$ |

| Stop condition set-up time  | $t_{SU, STO}$ |  | 4.0  | — | —    | $\mu\text{s}$ |

Note) \*1 to \*9: Refer to "Explanation of test methods".

## ■ Electrical Characteristics at $T_a = 25^\circ\text{C}$ (continued)

### • Design reference data (continued)

Note) The characteristics listed below are theoretical values based on the IC design and are not guaranteed.

| Parameter                    | Symbol              | Conditions                                                                          | Min | Typ | Max | Unit     |

|------------------------------|---------------------|-------------------------------------------------------------------------------------|-----|-----|-----|----------|

| <b>DAC</b>                   |                     |                                                                                     |     |     |     |          |

| 3-bit, 6-bit, 7-bit DAC DNLE | $L_{3,6,7}$         | $1\text{LSB} = \{\text{data (max.)} - \text{data (00)}\} / 7, 63, 127$              | 0.1 | 1.0 | 1.9 | LSB/Step |

| 8-bit DAC DNLE               | $L_8$               | $1\text{LSB} = \{\text{data (FF)} - \text{data (00)}\} / 255$<br>(7F → 80 excluded) | 0.1 | 1.0 | 1.9 | LSB/Step |

| 8-bit DAC DNLE (80)          | $L_{8-80}$          | $\text{LSB} = \{\text{data (FF)} - \text{data (00)}\} / 255$<br>(7F → 80)           | 0.1 | 1.0 | 2.9 | LSB/Step |

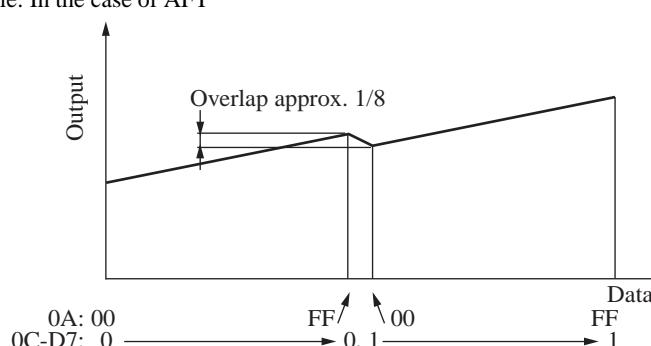

| AFT DAC overlap              | $\Delta\text{Step}$ | 8-bit of AFT double-stage changeover overlap                                        | 27  | 32  | 37  | Step     |

### • Explanation of test methods

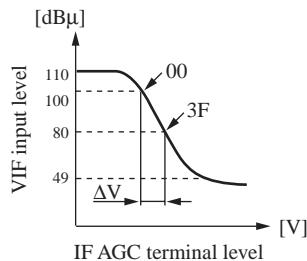

\*1: RF AGC delay point adjusting range:  $\Delta V_{\text{RFdp}}$

In the case of VIF gain reduction curve (figure 1), if the RF AGC delay point adjustment DAC (0 A) goes 00 to 3F, the internal comparison voltage changes by  $\Delta V$ , and the delay point adjustment range is determined.

Figure 1. Gain reduction curve

\*2: AFT discrimination sensitivity:  $\mu\text{AFT}$

Adjust DAC (0C-D7) and DAC (09) so that the AFT output voltage ( $V_{30}$ ) becomes approx. 4.5 V when  $f_p = 38.9\text{ MHz}$ .

Measure  $\Delta V_{30}$  when  $f_p = 38.9\text{ MHz} \pm 25\text{ kHz}$ .

\*3: Refer to "■ Technical Information 4. 7) PAL/NTSC, SECAM interface".

\*4: Black noise detection level:  $\Delta V_{\text{BN}}$

Black noise clamp level:  $\Delta V_{\text{BNC}}$

Figure 2. Black noise rejection characteristic

\*5: Inter modulation: IM

Apply the signal of  $f_p = 38.9\text{ MHz}$ ,  $90\text{ dBμ}$  and fix the voltage of pin 37 (IF AGC) under that condition.

$f_p = 38.9\text{ MHz}, 82\text{ dBμ}$

$f_p = 38.9\text{ MHz} - 4.43\text{ MHz}, 80\text{ dBμ}$

$f_p = 38.9\text{ MHz} - 6.0\text{ MHz}, 70\text{ dBμ}$

$$\text{IM} = 20\text{Log} \frac{\text{view component [rms]}}{\text{V}_{1.57\text{ MHz}} [\text{rms}]}$$

## ■ Electrical Characteristics at $T_a = 25^\circ\text{C}$ (continued)

### • Explanation of test methods (continued)

\*6: Black level extension:  $V_{BL}$

Figure 3. Black level expansion characteristics

In the black level extension characteristics (figure 3), when the voltage of pin 9 (black level detection filter) is  $V_{CC1} = 9\text{ V}$ , the operation of the black level extension circuit is turned off and the characteristic becomes as shown by the line  $---$ . Also, if the voltage of pin 9 is set at 3 V, the black level extension forcibly comes to start and the characteristic becomes as shown by the line  $-----$ . When pin 9 is set by only R, C filter, the black level extension characteristic as shown by the line  $—$  can be obtained.

$V_{BL3}$  shows an output level difference between the black extension is off and the normal operation when the video input level is constant in 20 IRE.

$V_{BL1}$  is a point where the black extension comes to start and can be adjusted by the DC voltage of pin 48 ( $C_{IN}$ ).

| $V_{48}$    | 2.5 V  | 4.5 V  | 6.5 V  |

|-------------|--------|--------|--------|

| Start point | 52 IRE | 42 IRE | 32 IRE |

\*7: (C-Y)/Y ratio: RC/Y