## 80C592/83C592/87C592

#### DESCRIPTION

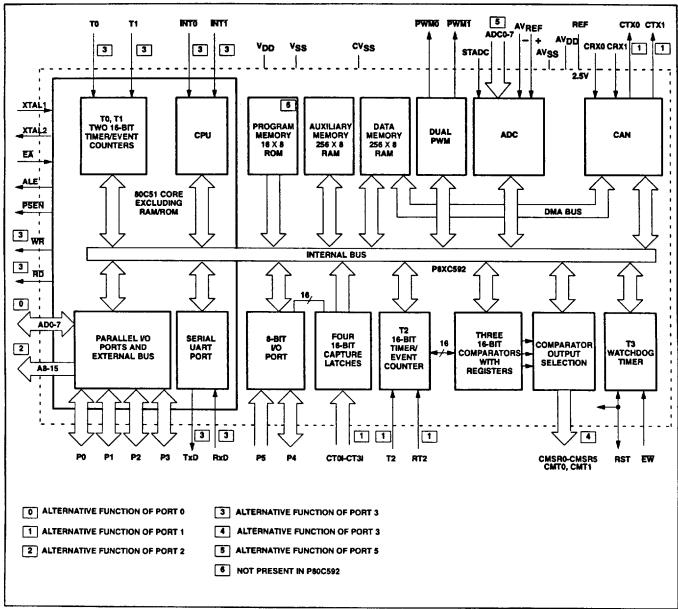

The 80C592/83C592/87C592 (hereafter referred to generically as the 8XC592) is a stand-alone high-performance microcontroller designed for use in automotive and general industrial applications. In addition to the 80C51 standard features, this device provides a number of dedicated hardware functions for these applications. Three versions of this derivative will be offered:

- 83C592 (ROM version)

- 80C592 (ROMless version)

- 87C592 (EPROM/OTP version)

It combines the functions of the existing 8XC552 and the Philips CAN-Controller PCA82C200 (CAN: Controller Area Network) with the following enhanced features:

- 16K byte Program Memory

- 2 x 256 byte Data Memory

- DMA between CAN Transmit/Receive buffer and internal RAM

The temperature range includes -40°C to +85°C as well as automotive temperature range -40°C to +125°C for the ROM and ROMless version with a maximum clock frequency of 16MHz. The 87C592 has a temperature range of -40°C to +85°C.

The main differences to the 8XC552 microcontroller are:

- a CAN-controller substitutes the I2C-serial interface

- 16K byte programmable ROM resp. EPROM instead of 8K byte

- additional 256 byte RAM.

The 8XC592 contains a 16k x 8 EPROM (87C592), ROM (83C592) program memory, a volatile 512 × 8 read/write data memory, a Controller Area Network (CAN) controller, six 8-bit I/O ports, one 8-bit input port, two 16-bit timer/event counters (identical to the timers of the 80C51), an additional 16-bit timer coupled to capture and compare latches, a 15-source, two-priority-level, nested interrupt structure, a 10-input ADC, a dual DAC pulse width modulated interface, two serial interfaces

(UART and CAN), a "watchdog" timer and on-chip oscillator and timing circuits. For systems that require extra capability, the 8XC592 memory can be expanded externally using standard TTL compatible memories and logic.

#### **FEATURES**

- 80C51 core architecture

- 16k × 8 EPROM (87C592)

- 16k × 8 ROM (83C592)

- ROMiess (80C592)

- 512 × 8 RAM, expandable externally to 64k bytes

- Two standard 16-bit timer/counters

- An additional 16-bit timer/counter coupled to four capture registers and three compare

- A 10-bit ADC with eight multiplexed analog inputs

- Two 8-bit resolution, pulse width modulation outputs

- 15 interrupt sources with 2 priority levels

- Five 8-bit I/O ports plus one 8-bit input port shared with analog inputs

- CAN controller with DMA transfer between internal data RAM and CAN registers

- Up to 1 Mbit/s CAN-Controller with bus failure management facility

- V<sub>DD</sub>/2 reference voltage

- Full-duplex UART compatible with the standard 80C51

- On-chip watchdog timer

- Extended temperature ranges (-40 to +125°C)

- OTP package available

- ROM code protection

#### PIN CONFIGURATION

| 1  | P5.0/ADC0       | 35 | V <sub>SS</sub>  |

|----|-----------------|----|------------------|

| 2  | V <sub>DD</sub> | 36 | P2.0/A08         |

| 3  | STADC           | 37 | P2.1/A09         |

| 4  | PWWO            | 38 | P2.2/A10         |

| 5  | PWM             | 38 | P2.3/A11         |

| 6  | EM              | 40 | P2.4/A12         |

| 7  | P4.0/CMSR0      | 41 | P2.5/A13         |

| 8  | P4.1/CMR\$1     | 42 | P2.6/A14         |

| 9  | P4.2CMSR2       | 43 | P2.7/A15         |

| 10 | P4.3/CMSR3      | 44 | PSEN             |

| 11 | P4.4/CMSR4      | 45 | ALE/PROG         |

| 12 | P4.5/CMSR5      | 46 | EAVPP            |

| 13 | P4.6/CMT0       | 47 | P0.7/AD7         |

| 14 | P4.7/CMT1       | 48 | P0.6/AD6         |

| 15 | RST             | 49 | P0.5/AD5         |

| 16 | P1.0/CT0I/INT2  | 50 | P0.4/AD4         |

| 17 | P1.1/CT1I/INT3  | 51 | P0.3/AD3         |

| 18 | P1.2/CT2I/INT4  | 52 | P0.2/AD2         |

| 19 | P1.3/CT3I/INT5  | 53 | P0.1/AD1         |

| 20 | P1.4/T2         | 54 | P0.0/AD0         |

| 21 | P1.5/RT2        | 55 | REF              |

| 22 | CVSS            | 56 | CRX1             |

| 23 | P1.6/CTX0       | 57 | CRX0             |

| 24 | P1.7/CTX1       | 58 | AVref-           |

| 25 | P3.0/RxD        | 59 | AVref+           |

| 26 | P3.1TxD         | 60 | AV <sub>SS</sub> |

| 27 | P3.2/INTO       | 61 | AVDD             |

| 28 | P3.3/INTT       | 62 | P5.7/ADC7        |

| 29 | P3.4/T0         | 63 | P5.6/ADC6        |

| 30 | P3.5/T1         | 64 | P5.5/ADC5        |

| 31 | P3.6/WR         | 65 | P5.4/ADC4        |

| 32 | P3.7/RD         | 66 | P5.3/ADC3        |

| 33 | XTAL2           | 67 | P5.2/ADC2        |

| 34 | XTAL1           | 68 | P5.1/ADC1        |

|    |                 |    |                  |

#### ORDERING INFORMATION

| ROMiess    | ROM        | EPROM      | TEMPERATURE RANGE °C AND PACKAGE                        | FREQUENCY<br>MHZ | DRAWING<br>NUMBER |  |

|------------|------------|------------|---------------------------------------------------------|------------------|-------------------|--|

| P80C592FFA | P83C592FFA | -          | -40 to +85, 68-Pin Plastic Leaded Chip Carrier          | 1.2 to 16        | 0398              |  |

| P80C592FHA | P83C592FHA | _          | -40 to +125, 68-Pin Plastic Leaded Chip Carrier         | 1.2 to 16        | 0398              |  |

| -          | -          | P87C592EFL | -40 to +85, 68-Pin Ceramic Leaded Chip Carrier w/Window | 3.5 to 16        | 1240              |  |

| _          | _          | P87C592EFA | -40 to +85, 68-Pin Plastic Leaded Chip Carrier          | 3.5 to 16        | 0398              |  |

# Single-chip 8-bit microcontroller with CAN controller

## 80C592/83C592/87C592

#### **BLOCK DIAGRAM**

NAPC/PHILIPS SEMICOND

## 80C592/83C592/87C592

### **PIN DESCRIPTION**

| MNEMONIC         | PIN NO.         | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|------------------|-----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| V <sub>DD</sub>  | 2               | ı    | Digital Power Supply: +5V power supply pin during normal operation, idle and power-down mode.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| STADC            | 3               | 1    | Start ADC Operation: Input starting analog to digital conversion (ADC operation can also be started by software). This pin must not float.                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| PWM0             | 4               | 0    | ulse Width Modulation: Output 0.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| PWM1             | 5               | 0    | Pulse Width Modulation: Output 1.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| EW               | 6               | 1    | <b>Enable Watchdog Timer:</b> Enable for T3 watchdog timer and disable power-down mode. This pin must not float.                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

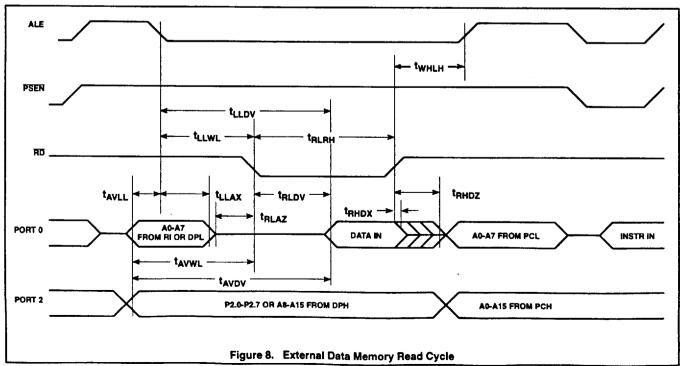

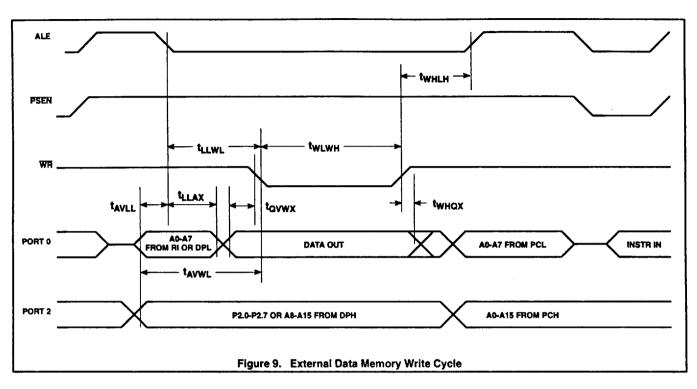

| P0.0-P0.7        | 54-47           | 1/0  | Port 0: Port 0 is an 8-bit open-drain bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application it uses strong internal pull-ups when emitting 1s. Port 0 is also used to input the code byte during programming and to output the code byte during verification. |  |  |  |  |

| P1.0-P1.7        | 16-21,<br>23-24 | 1/0  | Port 1: 8-bit I/O port. Alternate functions include:                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                  | 16-19           | !    | CT0I-CT3I (P1.0-P1.3): Capture timer input signals for timer T2.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                  | 16-19           | 1 !  | INT2-INT5 (P1.0-P1.3): External interrupts 2-5.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                  | 20<br>21        | ;    | T2 (P1.4): T2 event input. Rising edge triggered. RT2 (P1.5): T2 timer reset signal. Rising edge triggered.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| İ                | 23              | اة   | CTX0 (P1.6): CAN transmitter output 0.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                  | 24              | 0    | CTX1 (P1.7): CAN transmitter output 1.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                  | :               |      | Port 1 is also used to input the lower order address byte during EPROM programming and verification.  A0 is on P1.0, etc.                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| CV <sub>SS</sub> | 22              | 1    | CV <sub>SS</sub> : CAN transmitter driver ground.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| P2.0-P2.7        | 36-43           | 1/0  | Port 2: 8-bit quasi-bidirectional I/O port.  Alternate function: High-order address byte for external memory (A08-A15). Port 2 is also used to input the upper order address during EPROM programming and verification. A8 is on P2.0, A9 on P2.1, through A12 on P2.4.                                                                                                                                                                                         |  |  |  |  |

| P3.0-P3.7        | 25-32           | 1/0  | Port 3: 8-bit quasi-bidirectional I/O port. Alternate functions include:                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| }                | 25              | }    | RxD (P3.0): Serial input port.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|                  | 26              |      | TxD (P3.1): Serial output port.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                  | 27<br>28        |      | INTO (P3.2): External interrupt. INT1 (P3.3): External interrupt.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| ł                | 29              |      | TO (P3.4): Timer 0 external input.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                  | 30              | Į.   | T1 (P3.5): Timer 1 external input.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                  | 31              |      | WR (P3.6): External data memory write strobe.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                  | 32              |      | RD (P3.7): External data memory read strobe.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| P4.0-P4.7        | 7-14            | 1/0  | Port 4: 8-bit quasi-bidirectional I/O port. Alternate functions include:                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                  | 7-12            |      | CMSR0-CMSR5 (P4.0-P4.5): Timer T2 compare and set/reset outputs on a match with timer T2.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                  | 13, 14          | 0    | CMT0, CMT1 (P4.6, P4.7): Timer T2 compare and toggle outputs on a match with timer T2.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| P5.0-P5.7        | 68-62,<br>1     | 1    | Port 5: 8-bit input port. ADC0-ADC7 (P5.0-P5.7): Alternate function: Eight input channels to ADC.                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| RST              | 15              | 1/0  | <b>Reset:</b> Input to reset the 8XC592. It also provides a reset pulse as output when the watchdog timer overflows or after a CAN wakeup from power-down.                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| XTAL1            | 34              |      | Crystal Pin 1: Input to the inverting amplifier that forms the oscillator, and input to the internal clock generator. Receives the external clock signal when an external oscillator is used.                                                                                                                                                                                                                                                                   |  |  |  |  |

| XTAL2            | 33              | 0    | Crystal Pin 2: Output of the inverting amplifier that forms the oscillator. Left open-circuit when an external clock is used.                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Vss              | 35              | 1    | Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| PSEN             | 44              | 0    | Program Store Enable: Active-low read strobe to external program memory.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

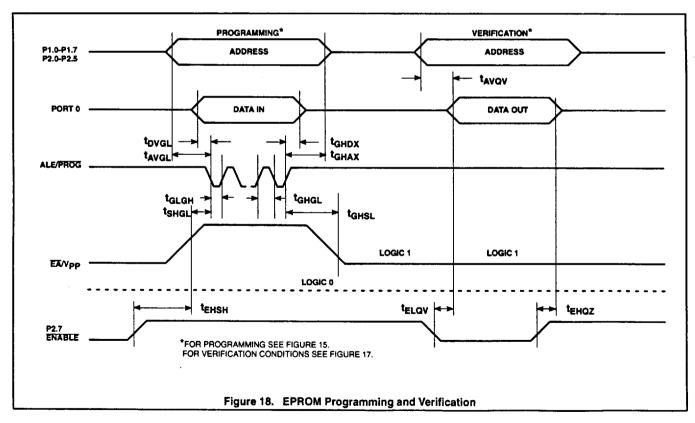

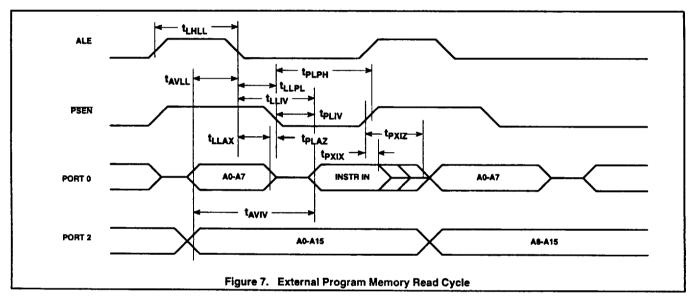

| ALE/PROG         | 45              | 0    | Address Latch Enable: Latches the low byte of the address during accesses to external memory. It is activated every six oscillator periods. During an external data memory access, one ALE pulse is skipped. ALE can drive up to eight LS TTL inputs and handles CMOS inputs without an external pull-up. This pin is also the program pulse input (PROG) during EPROM programming.                                                                             |  |  |  |  |

## 80C592/83C592/87C592

#### **PIN DESCRIPTION (Continued)**

| MNEMONIC            | PIN NO. | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EAV <sub>PP</sub>   | 46      | -    | External Access: When EA is held at TTL level high, during reset the CPU executes out of the internal program ROM provided the program counter is less than 16384. When EA is held at TTL low level, during reset the CPU executes out of external program memory. EA is not allowed to float. This pin also receives the 12.75V programming supply voltage (VPP) during EPROM programming. |

| REF                 | 55      | 0    | REF: AV <sub>DD</sub> /2 reference voltage output or input, depending on CAN control register bits. If the internal reference is used, then REF should be connected to AV <sub>SS</sub> through a 10nf (or greater) capacitor.                                                                                                                                                              |

| CRX1                | 56      | l t  | CRX1: CAN receiver input line 1.                                                                                                                                                                                                                                                                                                                                                            |

| CRX0                | 57      | 1    | CRX0: CAN receiver input line 0.                                                                                                                                                                                                                                                                                                                                                            |

| AV <sub>REF</sub> _ | 58      | 1    | Analog to Digital Conversion Reference Resistor: Low-end.                                                                                                                                                                                                                                                                                                                                   |

| AV <sub>REF+</sub>  | 59      | ı    | Analog to Digital Conversion Reference Resistor: High-end.                                                                                                                                                                                                                                                                                                                                  |

| AVSS                | 60      | ı    | Analog Ground (for ADC and CAN receiver)                                                                                                                                                                                                                                                                                                                                                    |

| AVDD                | 61      | 1    | Analog Power Supply (for ADC and CAN receiver)                                                                                                                                                                                                                                                                                                                                              |

NOTE:

The 8XC592 has the same operation as the 8XC552 for all features except the CAN interface and the AuxRAM. Please refer to the 8XC552 section in this data handbook for information on the PWM outputs, A/D converter, Timers 0, 1, or 2, the Watchdog Timer and the UART (SIO0).

#### **INTERNAL DATA MEMORY**

The internal Data Memory is divided into three physically separated parts: the 256 byte of Main RAM, the 256 byte of AuxRAM, and the 128 byte special function area, these can be addressed each in a different way.

- Main RAM 0 to 127 can be addressed directly and indirectly as in the 80C51.

Address pointers are R0 and R1 of the selected register bank.

- Main RAM 128 to 255 can only be addressed indirectly. Address pointers are R0 and R1 of the selected register bank.

- AuxRAM 0 to 255 is indirectly addressable in the same way as the external Data Memory with MOVX instructions. Address pointers are R0, R1 of the selected register

bank and the DPTR. An access to AuxRAM 0 to 255 will not affect the ports P0, P2, P3.6 and P3.7 during internal program execution.

An access to external Data Memory locations higher than 255 will be performed with the MOVX @DPTR instructions in the same way as in the 80C51 structure, so with P0 and P2 as data/address bus and P3.6 and P.37 as write and read strobe signals. Note that these external Data Memory locations cannot be accessed with R0 or R1 as address pointer.

To avoid "latch-up" effect at power-on, the voltage on any pin at any time must not be higher or lower than V<sub>DD</sub> + 0.5V or V<sub>SS</sub> - 0.5V, respectively.

Preliminary specification

# Single-chip 8-bit microcontroller with CAN controller

## 80C592/83C592/87C592

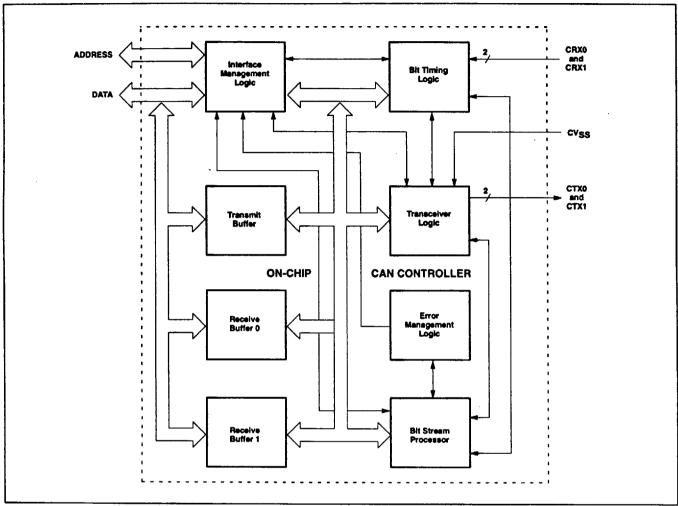

## **BLOCK DIAGRAM OF 8XC592 CAN CONTROLLER CIRCUITRY**

## 80C592/83C592/87C592

#### CAN FUNCTIONAL DESCRIPTION

#### SIO1, CAN (Controller Area Network)

CAN is the definition of a high performance communication protocol for serial data communication. The 8XC592 on-chip CAN Controller is a full implementation of the CAN-protocol. With the 8XC592, powerful local networks can be built, both for automotive and general industrial environments. This results in a strongly reduced wiring harness and enhanced diagnostic and supervisory capabilities.

#### **Features**

- Multi-master architecture

- Bus access priority determined by the message identifier

- 2032 message identifier

- Guaranteed latency time for high priority messages

- Powerful error handling capability

- Data length from 0 up to 8 bytes

- Multicast and broadcast message facility

- Non-destructive bit-wise arbitration

- Non-return-to-zero (NRZ) coding/decoding with bit stuffing

- Programmable transfer rate (up to 1 Mbit/s)

- Programmable output driver configuration

- Suitable for use in a wide range of networks, including the SAE's network classes A, B and C

- DMA providing high-speed on-chip data exchange

- Bus failure management facility

- AV<sub>DDD</sub> reference voltage

The CAN Controller meets the following automotive requirements:

- Short message length

- Guaranteed latency time\* for urgent messages

- Bus access priority, determined by the message identifier

- Powerful error handling capability

- Configuration flexibility to allow area network expansion.

#### NOTE:

The latency time defines the period between the initiation (Transmission Request) and the start of the transmission on the bus. The latency time strongly depends on a large variety of bus-related conditions. In the case of a message being transmitted on the bus and one distortion, the latency time can be up to 149 bit times (worst case). For more information, see the application note on bit timing.

#### CAN Functional Overview

The 8XC592 includes all hardware modules necessary to implement the transfer layer which represents the kernel of the CAN protocol. Refer to the block diagram (previous page) of the CAN controller portion of the

#### Interface Special Function Registers

The data transfer between the CPU and the CAN part of the 8XC592 is done via four

CANADR (DBH):

to point to a register of

the CAN-controller

CANDAT (DAH):

to read or write data

CANCON (D9H):

to read interrupt flags and to write commands

CANSTA (D8H):

to read status information and to write DMA pointer to the MAIN RAM

Additionally, the DMA-logic allows a highspeed data exchange between the CANcontroller and the MAIN RAM (see section "Handling of the CPU-CAN interface").

## Interface Management Logic

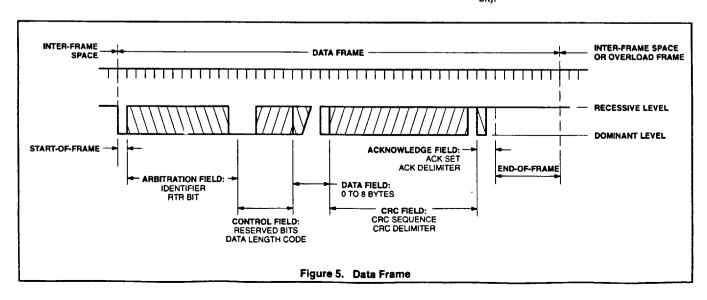

The IML interprets the commands from the CPU, controls the allocation of the message buffers Transmit Buffer (TBF), Receive Buffer 0 (RBF0), and Receive Buffer 1 (RBF1), and provides interrupts and status information to the CPU.

### Transmit Buffer (TBF)

The TBF is an interface between the CPU and the Bit Stream Processor (BSP) and is able to store a complete message. The buffer is written by the CPU and read by the BSP. The TBF is 10 bytes long to hold the Descriptor (2 bytes) and the Data-Field (up to 8 bytes) of the message.

## Receive Buffer (RBF0, RBF1)

The RBF is an interface between the BSP and the CPU and stores a message received from the busline. Once filled by BSP and allocated to the CPU by IML, the buffer cannot be used to store subsequently received messages until the CPU has (read and) released the buffer.

To reduce the requirements on the CPU, two receive buffers (RBF0, RBF1) are implemented. While one RBF is allocated to the CPU, the BSP may write to the other one. Both RBF0 and RBF1 are 10 bytes long to hold the Descriptor (2 bytes) and the Data-Fleid (up to 8 bytes) of the message.

#### **Bit Stream Processor (BSP)**

This is a sequencer controlling the data stream between transmit and receive buffers (parallel data) and the busline (serial data). The BSP contains the Acceptance Filter and also controls the TCL and the EML such that the processes of reception, arbitration, transmission, and error signaling are performed according to the protocol. The BSP provides signals to the IML indicating when a message has got acceptance, when a receive buffer contains a valid message, and also when the transmit butter is no longer required after a successful transmission.

### Bit Timing Logic (BTL)

This block monitors the busline using the (built-in) Input Comparator and handles the busline-related bit timing.

The BTL synchronizes on a "recessive" to "dominant" busline transition at the beginning of a message (hard synchronization) and resynchronizes on further transitions during the reception of a message (soft synchronization).

The BTL also provides programmable time segments to compensate for the propagation delay times and phase shifts (e.g., due to oscillator drifts) and to define the sampling time and the number of samples (one or three) to be taken within a bit time.

#### Transceiver Logic (TCL)

The TCL controls the transmit output driver.

### Error Management Logic (EML)

The EML is responsible for the error confinement of the transfer-layer modules. The EML gets error announcements from BSP and then informs the BSP, TCL, and IML about error statistics.

## 80C592/83C592/87C592

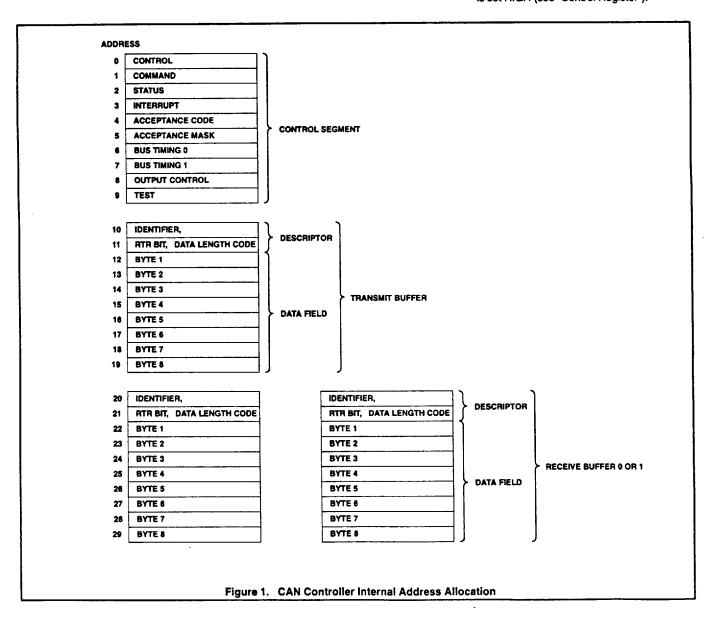

# CONTROL SEGMENT AND MESSAGE BUFFER DESCRIPTION

The CAN Controller appears to the CPU as an on chip memory mapped peripheral, guaranteeing the independent operation of both parts.

#### **Address Allocation**

The address area of the CAN Controller consists of the Control Segment and the

message buffers. The Control Segment is programmed during an initialization down-load in order to configure communication parameters (e.g., bit timing). The communication over the CAN-bus is also controlled via this segment by the CPU. A message which is to be transmitted, must be written to the Transmit Buffer. After a successful reception the CPU may read the message from the Receive Buffer and then release it for further use.

#### **Control Segment Layout**

The exchange of status, control and command signals between the CPU and the CAN Controller is performed in the control segment. The layout of this segment is shown in Figure 1. After an initial down-load, the contents of the registers Acceptance Code, Acceptance Mask, bus Timing 0 and 1 and Output Control should not be changed. These registers may only be accessed when the Reset Request bit in the Control Register is set HIGH (see "Control Register").

Preliminary specification

# Single-chip 8-bit microcontroller with CAN controller

## 80C592/83C592/87C592

Table 1. CAN Registers

| DESCRIPTION                 | ADDRESS | 7 (MSB)       | 6               | 5                   | 4                              | 3                                       | 2                               | 1                              | 0 (LSB)                               |

|-----------------------------|---------|---------------|-----------------|---------------------|--------------------------------|-----------------------------------------|---------------------------------|--------------------------------|---------------------------------------|

| Control Segment             |         |               |                 |                     |                                |                                         |                                 |                                |                                       |

| Control Register            | 0       | Test Mode     | Synch           | Reference<br>Active | Overrun<br>Interrupt<br>Enable | Error<br>Interrupt<br>Enable            | Transmit<br>Interrupt<br>Enable | Receive<br>Interrupt<br>Enable | Reset<br>Request                      |

| Command Register            | 1       | RX0<br>Active | RX1<br>Active   | Wake-Up<br>Mode     | Sieep                          | Clear<br>Overrun<br>Status              | Release<br>Receive<br>Buffer    | Abort<br>Trans-<br>mission     | Trans-<br>mission<br>Request          |

| Status Register             | 2       | Bus<br>Status | Error<br>Status | Transmit<br>Status  | Receive<br>Status              | Trans-<br>mission<br>Complete<br>Status | Transmit<br>Buffer<br>Access    | Data<br>Overrun                | Receive<br>Buffer<br>Status           |

| Interrupt Register          | 3       | reserved      | reserved        | reserved            | Wake-Up<br>Interrupt           | Overrun<br>Interrupt                    | Error<br>Interrupt              | Transmit<br>Interrupt          | Receive<br>Interrupt                  |

| Acceptance Code<br>Register | 4       | AC.7          | AC.6            | AC.5                | AC.4                           | AC.3                                    | AC.2                            | AC.1                           | AC.0                                  |

| Acceptance Mask<br>Register | 5       | AM.7          | AM.6            | AM.5                | AM.4                           | АМ.З                                    | AM.2                            | AM.1                           | AM.0                                  |

| Bus Timing Register 0       | 6       | SJW.1         | SJW.0           | BRP.5               | BRP.4                          | BRP.3                                   | BRP.2                           | BRP.1                          | BRP.0                                 |

| Bus Timing Register 1       | 7       | SAM           | TSEG2.2         | TSEG2.1             | TSEG2.0                        | TSEG1.3                                 | TSEG1.2                         | TSEG1.1                        | TSEG1.0                               |

| Output Control<br>Register  | 8       | OCTP1         | OCTN1           | OCPOL1              | ОСТР0                          | COTN0                                   | OCPOL0                          | OCMODE1                        | OCMODE0                               |

| Transmit Buffer             | -       |               |                 | •                   |                                |                                         |                                 | ·                              |                                       |

| Identifier                  | 10      | ID.10         | ID.9            | ID.8                | ID.7                           | ID.6                                    | ID.5                            | ID.4                           | ID.3                                  |

| RTR, Data Length<br>Code    | 11      | ID.2          | ID.1            | ID.0                | RTR                            | DLC.3                                   | DLC.2                           | DLC.1                          | DLC.0                                 |

| Bytes 1–8                   | 12–19   | Data          | Data            | Data                | Data                           | Data                                    | Data                            | Data                           | Data                                  |

| Receive Buffer 0/1          |         |               |                 | •                   | <u></u>                        | <u> </u>                                | · <del></del> -                 | <u></u>                        | · · · · · · · · · · · · · · · · · · · |

| Identifier                  | 20      | ID.10         | ID.9            | ID.8                | ID.7                           | ID.6                                    | ID.5                            | ID.4                           | ID.3                                  |

| RTR, Data Length<br>Code    | 21      | ID.2          | ID.1            | ID.0                | RTR                            | DLC.3                                   | DLC.2                           | DLC.1                          | DLC.0                                 |

| Bytes 1-8                   | 22-29   | Data          | Data            | Data                | Data                           | Data                                    | Data                            | Data                           | Data                                  |

Preliminary specification

## Single-chip 8-bit microcontroller with CAN controller

80C592/83C592/87C592

Control Register (CR)

The contents of the Control Register are used to change the behavior of the CAN Controller. Control bits may be set or reset by the CPU which uses the Control Register as a read/write memory.

Table 2 **Description of the Control Register Bits**

| CR   |        |                               | A              | DDRESS 0                                                                                                                                                                                                      |

|------|--------|-------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT  | SYMBOL | NAME                          | VALUE          | FUNCTION                                                                                                                                                                                                      |

| CR.0 | RR     | Reset Request <sup>1</sup>    | HIGH (present) | Detection of a Reset Request results in the CAN Controller aborting the current transmission/reception of a message entering the reset state.                                                                 |

|      |        |                               | LOW (absent)   | On the HIGH-to-LOW transition of the Reset Request bit, the CAN Controller returns to its normal operating state.                                                                                             |

| CR.1 | RIE    | Receive Interrupt Enable      | HIGH (enabled) | When a message has been received without errors, the CAN Controller transmits a Receive Interrupt signal to the CPU.                                                                                          |

|      |        |                               | LOW (disabled) | No transmission of the Receive Interrupt signal by the CAN Controller to the CPU.                                                                                                                             |

| CR.2 | TIE    | Transmit Interrupt Enable     | HIGH (enabled) | When a message has been successfully transmitted or the transmit buffer is accessible again, (e.g., after an Abort Transmission command) the CAN Controller transmits a Transmit Interrupt signal to the CPU. |

|      |        |                               | LOW (disabled) | No transmission of the Transmit Interrupt signal by the CAN Controller to the CPU.                                                                                                                            |

| CR.3 | EIE    | Error Interrupt Enable        | HIGH (enabled) | If the Error or Bus Status change (see status Register), the CPU receives an Error Interrupt signal.                                                                                                          |

|      |        |                               | LOW (disabled) | The CPU receives no Error Interrupt signal.                                                                                                                                                                   |

| CR.4 | OIE    | Overrun Interrupt Enable      | HIGH (enabled) | If the Data Overrun bit is set (see Status Register), the CPU receives an Overrun Interrupt signal.                                                                                                           |

| :    |        |                               | LOW (disabled) | The CPU receives no Overrun Interrupt signal from the CAN Controller.                                                                                                                                         |

| CR.5 | RA     | Reference Active <sup>2</sup> | HIGH (output)  | The pin REF is an AV <sub>DD/2</sub> reference output.                                                                                                                                                        |

|      |        |                               | LOW (input)    | A reference voltage may be input.                                                                                                                                                                             |

| CR.6 | s      | Synch <sup>2</sup>            | HIGH (2 edges) | Bus-line transitions from recessive-to-dominant and vice versa are used for resynchronization.                                                                                                                |

|      |        |                               | LOW (1 edge)   | Only transitions from recessive-to-dominant are used for resynchronization.                                                                                                                                   |

| CR.7 | _      | RESERVED                      |                |                                                                                                                                                                                                               |

#### NOTES:

- 1. During an exfernal reset (RST = HIGH) or when the Bus Status bit is set HIGH (Bus-Off), the IML forces the Reset Request HIGH (present). During an external reset the CPU cannot set the Reset Request bit LOW (absent). Therefore, after having set the Reset Request bit LOW (absent), the CPU must check this bit to ensure that the external reset pin is not being held HIGH (present). After the Reset Request bit is set LOW (absent) the CAN controller will wait for:

- one occurrence of the Bus-Free signal (11 recessive bits), if the preceding reset (Reset Request = HIGH) has been caused by an external reset or a CPU initiated reset.

- 128 occurrences of Bus-Free, if the preceding reset (Reset Request = H(GH) has been caused by a CAN Controller initiated Bus-Off, before re-entering the Bus-On mode.

- When Reset Request is set HIGH (present), for whatever reason, the control, command, status and interrupt bits are affected, see Table 3. Only, when Reset Request is set HIGH (present) the registers at addresses 4 to 8 are accessible.

- 2. A modification of the bits Reference Active and Synch is only possible with Reset Request = HIGH (present). It is allowed to set these bits while Reset Request is changed from HIGH to LOW. After an external reset (pin RST = HIGH) the Reference Active bit is set HIGH (output), the Synch bit is undefined.

## 80C592/83C592/87C592

Table 3. Effects of Setting the Reset Request Bit HIGH (present)

| TYPE      | BIT                                                                                                                                           | EFFECT                                                                                                                                                                 |  |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Control   | Reference Active                                                                                                                              | HIGH (output), only after an external reset                                                                                                                            |  |  |  |  |

| Command   | RX0 Active / RX1 Active<br>Sleep<br>Clear Overrun Status<br>Release Receive Buffer<br>Abort Transmission<br>Transmission Request              | HIGH (RX0=CRX0, RX1=CRX1), only after an external reset LOW (wake-up) HIGH (clear) HIGH (released) LOW (absent) LOW (absent)                                           |  |  |  |  |

| Status    | Bus Status Error Status Transmit Status Receive Status Transmission Complete Status Transmit Buffer Access Data Overrun Receive Buffer Status | LOW (Bus-On), only after an external reset LOW (no error), only after an external reset LOW (idle) LOW (idle) HIGH (complete) HIGH (released) LOW (absent) LOW (empty) |  |  |  |  |

| Interrupt | Overrun Interrupt<br>Transmit Interrupt<br>Receive Interrupt                                                                                  | LOW (reset) LOW (reset) LOW (reset)                                                                                                                                    |  |  |  |  |

#### Command Register (CMR)

A command bit initiates an action within the transfer layer of the CAN controller, the Command Register appears to the CPU as a read/write memory, except of the bits CMR.0 to CMR.3, which return HIGH if being read.

HPF D

■ 6623454 0045648 587 ■ ZIC3

■ ZTC ∃

Philips Semiconductors Microcontroller Products

Preliminary specification

# Single-chip 8-bit microcontroller with CAN controller

## 80C592/83C592/87C592

Table 4. Description of the Command Register Bits

| CMR   | ADDRESS 1 |                                     |                          |           |                                                                                                            |  |  |  |  |

|-------|-----------|-------------------------------------|--------------------------|-----------|------------------------------------------------------------------------------------------------------------|--|--|--|--|

| BIT   | SYMBOL    | NAME                                | VALUE                    |           | FUNCTION                                                                                                   |  |  |  |  |

| CMR.0 | TR        | Transmission Request <sup>1</sup>   | HIGH (pres               | sent)     | A message shall be transmitted.                                                                            |  |  |  |  |

|       |           |                                     | LOW (abse                | ent)      | No action.                                                                                                 |  |  |  |  |

| CMR.1 | AT        | Abort Transmission <sup>2</sup>     | HIGH (present)           |           | If not already in progress, a pending Transmission Request is cancelled.                                   |  |  |  |  |

|       |           |                                     | LOW (abse                | ent)      | No action.                                                                                                 |  |  |  |  |

| CMR.2 | RRB       | Release Receive Buffer <sup>3</sup> | HIGH (rele               | ased)     | The Receive Buffer attached to the CPU is released.                                                        |  |  |  |  |

|       |           |                                     | LOW (no a                | ction)    | No action.                                                                                                 |  |  |  |  |

| CMR.3 | cos       | Clear Overrun <sup>4</sup>          | HIGH (clea               | ır)       | The Data Overrun status bit is set to LOW (see Status Register)                                            |  |  |  |  |

|       |           |                                     | LOW (no a                | ction)    | No action.                                                                                                 |  |  |  |  |

| CMR.4 | SLP       | Sleep <sup>5</sup>                  | HIGH (slee               | p)        | The CAN Controller enters sleep mode if no CAN interrupt is pending and there is no bus activity.          |  |  |  |  |

|       |           |                                     | LOW (wake up)            |           | The CAN Controller functions normally.                                                                     |  |  |  |  |

| CMR.5 | WUM       | Wake-Up Mode <sup>6</sup>           | HIGH (sing               | le ended) | The difference of the RX signals to the internal reference voltage AV <sub>DD/2</sub> is used for wake up. |  |  |  |  |

|       | 1         |                                     | LOW (diffe               | rential)  | The differential signal between RX0 and RX1 is used for wake up.                                           |  |  |  |  |

| CMR.6 | RX1A      | RX1 Active <sup>7</sup>             | RX0 RX1<br>Active Active |           | See Figure 2.                                                                                              |  |  |  |  |

| CMR.7 | RX0A      | RX0 Active <sup>7</sup>             | 1 1                      |           | RX0 = CRX0, RX1 = CRX1                                                                                     |  |  |  |  |

|       |           |                                     | 1                        | 0         | $RX0 = CRX0, RX1 = AV_{DD/2}$                                                                              |  |  |  |  |

|       |           | ]                                   | 0                        | 1         | $RX0 = AV_{DD/2}, RX1 = CRX1$                                                                              |  |  |  |  |

|       | <u> </u>  |                                     | 0                        | 0         | No action.                                                                                                 |  |  |  |  |

#### NOTES:

If the Transmission Request bit was set HIGH in a previous command, it cannot be cancelled by setting the Transmission Request bit LOW

(absent). Cancellation of the requested transmission may be performed by setting the Abort Transmission bit HIGH (present).

2. The Abort Transmission bit is used when the CPU requires the suspension of the previously requested transmission, e.g., to transmit an urgent message. A transmission already in progress is not stopped. In order to see if the original message had been either transmitted successfully or aborted, the Transmission Complete Status bit should be checked. this should be done after the Transmit Buffer Access bit has been set HIGH (released) or a Transmit Interrupt has been generated (see Interrupt Register).

After reading the contents of the Receive Buffer (RBF0 or RBF1) the CPU must release this buffer by setting Release Receive Buffer bit HIGH (released). This may result in another message becoming immediately available.

4. This command bit is used to acknowledge the Data Overrun condition signaled by the Data Overrun status bit. It may be given or set at the

same time as a Release Receive Buffer command bit.

5. The CAN Controller will enter sleep mode, if the Sleep bit is set HIGH (sleep), there is no bus activity and no interrupt is pending. A CAN Controller will wake up after the Sleep bit is set LOW (wake up) or when there is bus activity. On wake up, a Wake-Up Interrupt (see Interrupt Register) is generated (see "Power Reduction Modes"). A CAN Controller which is sleeping and then awoken by bus activity will not be able

to receive this message until it detects a Bus-Free signal. The Sleep bit, if being read, reflects the status of the CAN Controller.

The Wake-Up Mode bit should be set at the same time as the Sleep bit. The differential wake up mode is useful if both bus wires are fully

functioning; it minimizes the probability of wake ups due to noise. The single ended wake up mode is recommended if a wake up must be possible even if one bus wire is already or may become disturbed (See Figure 2).

7. The RX0/RX1, Active bits, if being read, reflect the status of the respective switches (See Figure 2). It is recommended to change the switches only during the reset state (Reset Request is HIGH).

Preliminary specification

## Single-chip 8-bit microcontroller with CAN controller

Philips Semiconductors Microcontroller Products

## 80C592/83C592/87C592

Status Register (SR)

The contents of the Status Register reflects the status of the CAN Controller. The Status Register appears to the CPU as a read only memory.

**Description of the Status Register Bits** Table 5.

| SR   |        |                                          |                  | ADDRESS 2                                                                                                                          |  |  |  |  |

|------|--------|------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| BIT  | SYMBOL | NAME                                     | VALUE            | FUNCTION                                                                                                                           |  |  |  |  |

| SR.0 | RBS    | Receive Buffer Status <sup>1</sup>       | HIGH (full)      | This bit is set when a new message is available.                                                                                   |  |  |  |  |

|      |        |                                          | LOW (empty)      | No message has become available since the last Release Receive Buffer command bit was set.                                         |  |  |  |  |

| SR.1 | DO     | Data Overrun <sup>2</sup>                | HIGH (overrun)   | This bit is set HIGH (overrun) when both Receive Buffers are full and the first byte of another message should be stored.          |  |  |  |  |

|      |        |                                          | LOW (absent)     | No data overrun has occurred since the Clear Overrun command was given.                                                            |  |  |  |  |

| SR.2 | TBS    | Transmit Buffer Access <sup>3</sup>      | HIGH (released)  | The CPU may write a message into the TBF.                                                                                          |  |  |  |  |

|      |        |                                          | LOW (locked)     | The CPU cannot access the Transmit Buffer. A message is either waiting for transmission or is in the process of being transmitted. |  |  |  |  |

| SR.3 | TCS    | Transmit Complete<br>Status <sup>3</sup> | HIGH (complete)  | Last requested transmission has been successfully completed.                                                                       |  |  |  |  |

|      |        |                                          | LOW (incomplete) | Previously requested transmission is not yet completed.                                                                            |  |  |  |  |

| SR.4 | RS     | Receive Status <sup>4</sup>              | HIGH (receive)   | The CAN Controller is receiving a message.                                                                                         |  |  |  |  |

|      |        |                                          | LOW (idle)       | No message is received.                                                                                                            |  |  |  |  |

| SR.5 | TS     | Transmit Status <sup>4</sup>             | HIGH (transmit)  | The CAN Controller is transmitting a message.                                                                                      |  |  |  |  |

|      |        |                                          | LOW (idle)       | No message is transmitted.                                                                                                         |  |  |  |  |

| SR.6 | ES     | Error Status                             | HIGH (error)     | At least one of the Error Counters has reached the CPU Warning limit.                                                              |  |  |  |  |

|      |        |                                          | LOW (ok)         | Both Error Counters have not reached the warning limit.                                                                            |  |  |  |  |

| SR.7 | BS     | Bus Status <sup>5</sup>                  | HIGH (Bus-Off)   | The CAN Controller is not involved in bus activities.                                                                              |  |  |  |  |

|      |        |                                          | LOW (Bus-On)     | The CAN Controller is involved in bus activities.                                                                                  |  |  |  |  |

#### NOTES:

- If the command bit Release Receive Buffer is set HIGH (released) by the CPU, the Receive Buffer Status bit is set LOW (empty) by IML. When a new message is stored in any of the receive buffers, the Receive Buffer Status bit is set HIGH (full) again.

- 2. If Data Overrun = HIGH (overrun) is detected, the currently received message is dropped. A transmitted message, granted acceptance, is also stored in a Receive Buffer. This occurs because it is not known if the CAN Controller will lose arbitration and so become a receiver of the message. If no Receive Buffer is available, Data Overrun is signaled. However, this transmitted and accepted message does neither cause a Receive Interrupt nor set the Receive Buffer Status bit to HIGH (full). Also, a Data Overrun does not cause the transmission of an Overload Frame.

- 3. If the CPU tries to write to the Transmit Buffer when the Transmit Buffer Access bit is LOW (locked), the written bytes will not be accepted and will be lost without this being signaled. The Transmission Complete Status bit is set LOW (incomplete) whenever the Transmission Request bit is set HIGH (present). If an Abort Transmission command is issued, the Transmit Buffer will be released. If the message, which was requested and then aborted, was not transmitted, the Transmission Complete Status bit will remain LOW.

- 4. If both the Receive Status and Transmit Status bits are LOW (idle) the CAN-bus is idle.

- 5. When the Bus Status bit is set HIGH (Bus-Off), the CAN Controller will set the Reset Request bit HIGH (present). It will stay in this state until the CPU sets the Reset Request bit LOW (absent). Once this is completed, the CAN Controller will wait the minimum protocol-defined time (128 occurrences of the Bus-Free signal) before setting the Bus Status bit LOW (Bus-On), the Error Status bit LOW (ok), and resetting the Error Counters.

Preliminary specification

# Single-chip 8-bit microcontroller with CAN controller

80C592/83C592/87C592

### Interrupt Register (IR)

The Interrupt Register allows the identification of an interrupt source. When one or more bits of this register are set, a CAN interrupt (SIO1) will be indicated to the CPU. All bits are reset by the CAN Controller after this register is read by the CPU. This register appears to the CPU as a read only memory.

Table 6. Description of the Interrupt Register Bits

| IR   |        |                                |             | ADDRESS 3                                                                                                                                                                                       |

|------|--------|--------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT  | SYMBOL | NAME                           | VALUE       | FUNCTION                                                                                                                                                                                        |

| IR.0 | RI     | Receive Interrupt <sup>1</sup> | HIGH (set)  | This bit is set when a new message is available in the Receive Buffer and the Receive Interrupt Enable bit is HIGH (enabled).                                                                   |

|      |        |                                | LOW (reset) | Receive Interrupt bit is automatically reset by a read access of Interrupt Register by the CPU.                                                                                                 |

| IR.1 | TI     | Transmit Interrupt             | HIGH (set)  | This bit is set on a change of the Transmit Buffer Access from LOW to HIGH (released) and Transmit Interrupt Enable is HIGH (enabled).                                                          |

|      |        |                                | LOW (reset) | Transmit Interrupt bit will be reset after a read access of the Interrupt Register by the CPU.                                                                                                  |

| IR.2 | El     | Error Interrupt                | HIGH (set)  | This bit is set on a change of either the Error Status or Bus Status bits (see Status Register) if the Error Interrupt Enable is HIGH (enabled).                                                |

|      |        |                                | LOW (reset) | The Error Interrupt bit is reset by a read access of the Interrupt Register by the CPU.                                                                                                         |

| IR.3 | OI     | Overrun Interrupt <sup>2</sup> | HIGH (set)  | This bit is set HIGH, if both Receive Buffers contain a message and the first byte of another message should be stored (passed acceptance), and the Overrun Interrupt Enable is HIGH (enabled). |

|      |        |                                | LOW (reset) | Overrun Interrupt bit is reset by a read access of the Interrupt register by the CPU.                                                                                                           |

| IR.4 | WUI    | Wake-Up Interrupt              | HIGH (set)  | The Wake-Up Interrupt bit is set HIGH when the sleep mode is left (see Command Register).                                                                                                       |

|      |        |                                | LOW (reset) | Wake-Up Interrupt bit is reset by a read access of the Interrupt Register by the CPU.                                                                                                           |

| IR.5 | -      | RESERVED                       |             |                                                                                                                                                                                                 |

| IR.6 | -      | RESERVED                       |             |                                                                                                                                                                                                 |

| IR.7 | _      | RESERVED                       |             |                                                                                                                                                                                                 |

#### NOTES:

2. Overrun Interrupt bit (if enabled) and Data Overrun bit (see Command Register) are set at the same time.

<sup>1.</sup> Receive Interrupt bit (if enabled) and Receive Buffer Status bit (see Status Register) are set at the same time.

Preliminary specification

# Single-chip 8-bit microcontroller with CAN controller

## 80C592/83C592/87C592

#### Acceptance Code Register (ACR)

Philips Semiconductors Microcontroller Products

The Acceptance Code Register is part of the acceptance filter of the CAN Controller. This register can be accessed (read/write), if the Reset Request bit is set HIGH (present). When a message is received which passes the acceptance test and if there is an empty Receive Buffer, then the respective Descriptor and Data Field (see Figure 1) are sequentially stored in this empty buffer. In the case that there is no empty Receive buffer, the Data Overrun bit is set HIGH (overrun), see Status and Interrupt Register. When the complete message has been correctly received, the following occurs:

- The Receive Buffer Status bit is set HIGH (full)

- If the Receive Interrupt Enable bit is set HIGH (enabled), the receive Interrupt is set HIGH (set).

The Acceptance Code bits (AC.7–AC.0) and the eight most significant bits of the message's Identifier (ID.10–ID.3) must be equal to those bit positions which are marked relevant by the Acceptance Mask bits (AM.7–AM.0). If the following equation is satisfied, acceptance is given:

[(ID.10..ID.3) EQUAL (AC.7..AC.0)] or  $(AM.7..AM.0) = 1111 \ 1111_b$

#### **Acceptance Code Register Bits**

| ACR  | ADDI | ADDRESS 4 |      |      |      |      |      |  |  |  |  |

|------|------|-----------|------|------|------|------|------|--|--|--|--|

| 7    | 6    | 5         | 4    | 3    | 2    | 1    | 0    |  |  |  |  |

| AC.7 | AC.6 | AC.5      | AC.4 | AC.3 | AC.2 | AC.1 | AC.0 |  |  |  |  |

During transmission of a message which passes the acceptance test, the message is also written to its own Receive Buffer. If no Receive Buffer is available, Data Overrun is signaled because it is not known at the start of a message whether the CAN Controller will lose arbitration and so become a receiver of the message.

### Acceptance Mask Register (AMR)

The Acceptance Mask Register is part of the acceptance filter of the CAN Controller. This register can be accessed (read/write) if the Reset Request bit is set HIGH (present). The

Acceptance Mask Register qualifies which of the corresponding bits of the acceptance code are "relevant" or "don't care" for acceptance filtering.

#### **Acceptance Mask Register Bits**

| AMR  | ADDRESS 5 |      |      |      |      |      |      |  |  |  |

|------|-----------|------|------|------|------|------|------|--|--|--|

| 7    | 6         | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |

| AM.7 | AM.6      | AM.5 | AM.4 | AM.3 | AM.2 | AM.1 | AM.0 |  |  |  |

## Description of the Acceptance Mask Register Bits

| ACCEPTANCE<br>MASK BIT | VALUE                | COMMENTS                                                                    |

|------------------------|----------------------|-----------------------------------------------------------------------------|

| AM.7 to AM.0           | HIGH<br>(don't care) | This bit position is<br>"don't care" for the<br>acceptance of a<br>message. |

|                        | LOW<br>(relevant)    | This bit position is<br>"relevant" for<br>acceptance filtering.             |

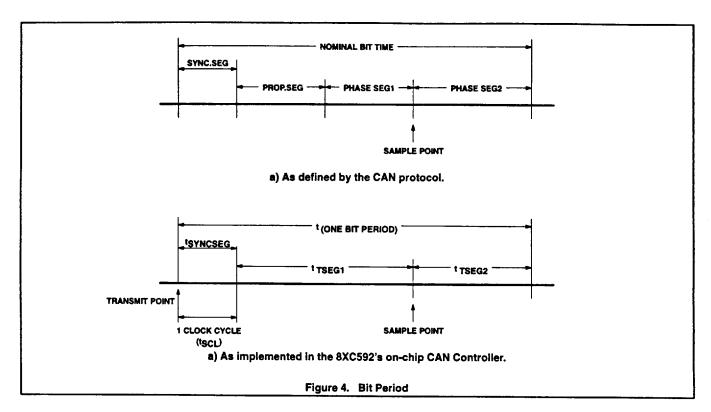

#### **Bus Timing Register 0 (BTR 0)**

The contents of Bus Timing Register 0 defines the values of the Baud Rate Prescaler (BRP) and the Synchronization Jump Width (SJW). This register can be accessed (read/write) if the Reset Request bit is set HIGH (present).

#### **Bus Timing Register 0 Bits**

| BTRO  | ADD   | RESS 6 |       |       |       |       |       |

|-------|-------|--------|-------|-------|-------|-------|-------|

| 7     | 6     | 5      | 4     | 3     | 2     | 1     | 0     |

| SJW.1 | SJW.0 | BRP.5  | BRP.4 | BRP.3 | BAP.2 | BRP.1 | BRP.0 |

#### **Baud Rate Prescaler (BRP)**

The period of the system clock t<sub>SCL</sub> is programmable and determines the individual bit timing. The system clock is calculated using the following equation:

t<sub>SCL</sub> = 2t<sub>CLK</sub> (32BRP.5 + 16BRP.4 + 8BRP.3 + 4BRP.2 + 2BRP.1 + BRP.0 +1)

$t_{CLK}$  = time period of the 8XC592 oscillator.

## Synchronization Jump Width (SJW)

To compensate for phase shifts between clock oscillators of different bus controllers, any bus controller must resynchronize on any relevant signal edge of the current

transmission. The synchronization jump width defines the maximum number of clock cycles a bit period may be shortened or lengthened by one resynchronization:

$t_{SJW} = t_{SCL} (2SJW.1 + SJW.0 + 1)$

### **Bus Timing Register 1 (BTR1)**

The contents of Bus Timing Register 1 defines the length of the bit period, the location of the sample point and the number of samples to be taken at each sample point. This register can be accessed (read/write) if the Reset Request bit is set HIGH (present).

#### **Bus Timing Register 1 Bits**

| BTR1 | ADDRESS | 7  |        |      |         |         |  |

|------|---------|----|--------|------|---------|---------|--|

| 7    | 6       |    |        | 5    |         | 4       |  |

| SAM  | TSEG2.2 | ?  | TSE    | G2.1 | TSEG2.0 |         |  |

|      | 3       |    | 2      | 1    | 0       |         |  |

|      | TSEG1.3 | TS | SEG1.2 | TSEG | 1.1     | TSEG1.0 |  |

#### Sampling (SAM)

| ВІТ | VALUE               | COMMENTS                 |

|-----|---------------------|--------------------------|

| SAM | HIGH<br>(3 samples) | 3 samples are taken.     |

|     | LOW<br>(1 sample)   | The bus is sampled once. |

SAM = LOW is recommended for high speed buses (SAE class C), while SAM = HIGH is recommended for slow/medium speed buses (class A and B) where filtering of spikes on the bus-line is beneficial (see "Bit Timing Restrictions").

## Time Segment 1 (TSEG1) and Time Segment 2 (TSEG2)

TSEG1 and TSEG2 determine the number of clock cycles per bit period and the location of the sample point:

$t_{TSEG1} = t_{SCL} (8TSEG1.3 + 4TSEG1.2 + 2TSEG.1 + TSEG1.0 + 1)$

$t_{TSEG2} = t_{SCL} (4TSEG2.2 + 2TSEG2.1 + TSEG2.0 + 1)$

For further information on bus timing see Bus Timing Register 0 and "Bus Timing/ Synchronization".

## 80C592/83C592/87C592

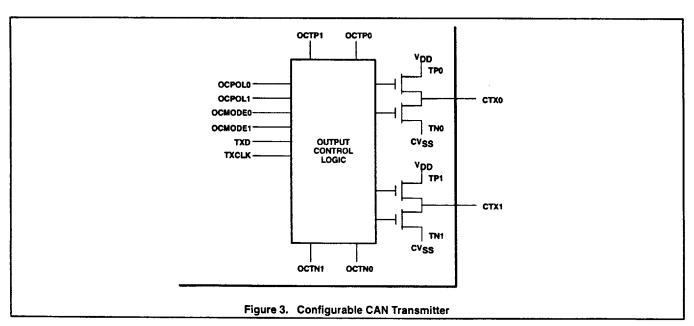

#### **Output Control Register (OCR)**

The Output Control Register allows, under software control, the set-up of different output driver configurations. This register can be accessed (read/write) if the Reset Request bit is set HIGH (present).

#### **Output Control Register Bits**

| OCR   | ADDRESS 8 |                    |     |      |   |        |  |  |

|-------|-----------|--------------------|-----|------|---|--------|--|--|

| 7     | 6         | 6 5 4 3            |     |      |   |        |  |  |

| OCTP1 | OCTN1     | OCPOL1 OCTP0 OCTN0 |     |      |   |        |  |  |

|       | 2         | 1                  |     |      | 0 |        |  |  |

|       | OCPOL     | )                  | ОСМ | DDE1 | 0 | CMODE0 |  |  |

If the CAN Controller is in the sleep mode (Sleep = HIGH) a recessive level is output on the CTX0 and CTX1 pins. If the CAN Controller is in the reset state (Reset Request = HIGH) the output drivers are floating.

#### **Normal Output Mode**

In Normal Output Mode the bit sequence (TXD) is sent via CTX0 and CTX1. The

voltage levels on the output driver pins CTX0 and CTX1 depend on both the driver characteristic programmed by OCTPx, OCTNx (float, pull-up, pull-down, push-pull) and the output polarity programmed by OCPOLx (see Figure 3).

#### **Clock Output Mode**

For the CTX0 pin this is the same as in Normal Output Mode. However, the data stream to CTX1 is replaced by the transmit clock (TXCLK). The rising edge of the transmit clock (non-inverted) marks the beginning of a bit period. The clock pulse width is t<sub>SCL</sub>.

#### **Bi-phase Output Mode**

In contrast to Normal Output Mode the bit representation is time variant and toggled. If the bus controllers are galvanically decoupled from the bus-line by a transformer, the bit stream is not allowed to contain a DC component. This is achieved by the following

scheme. During recessive bits all outputs are de-activated (floating). Dominant bits are sent alternatingly on CTX0 and CTX1, i.e., the first dominant bit is sent on CTX0, the second is sent on CTX1, and the third one is sent on CTX0 again, etc.

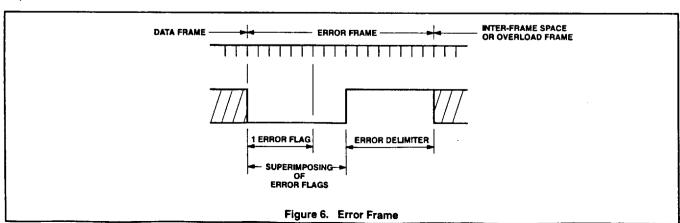

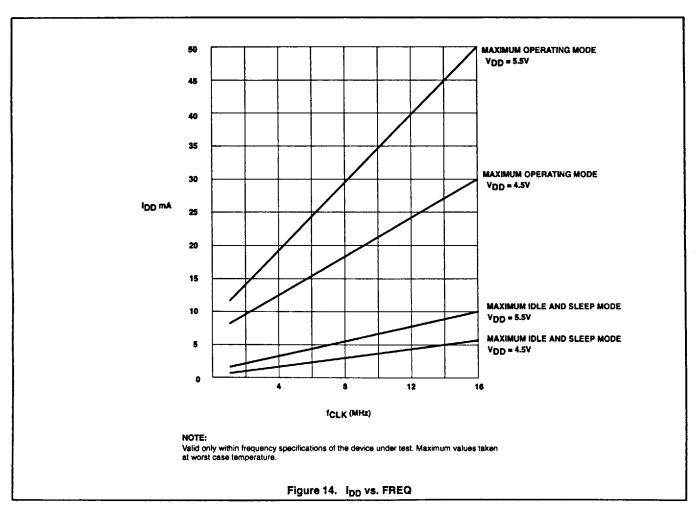

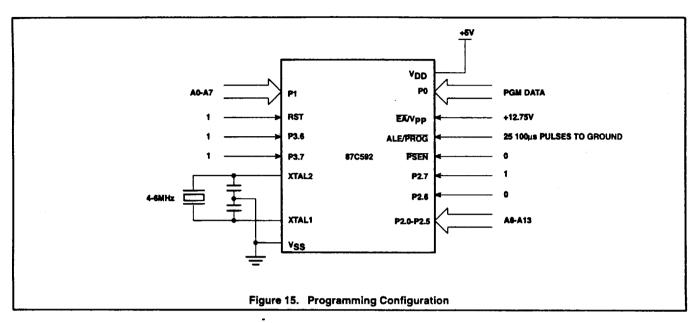

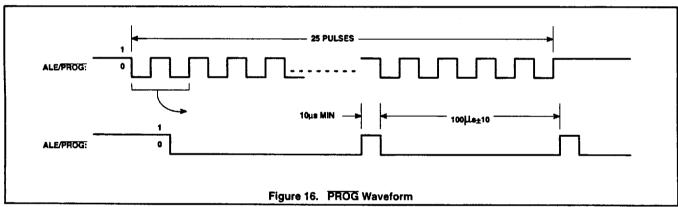

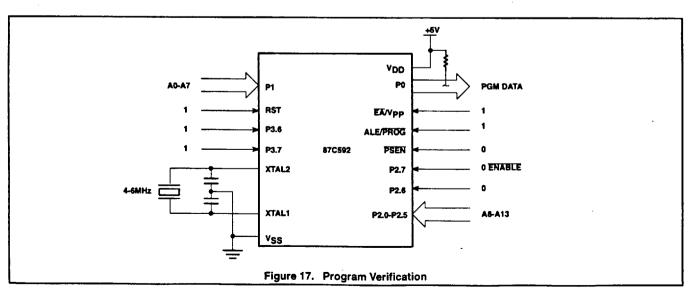

### **Test Output Mode**