DECEMBER 1979-- REVISED MAY 1982

- 1024 X 8 Organization

- All Inputs and Outputs Fully TTL Compatible

- Static Operation (No Clocks, No Refresh)

- Performance Ranges:

|              | Max Access | Min Cycle |

|--------------|------------|-----------|

| TMS 2708-35  | 350 ns     | 350 ns    |

| TMS 2708-45  | 450 ns     | 450 ns    |

| TMS 27L08-45 | 450 ns     | 450 ns    |

- 3-State Outputs for OR-Ties

- N-Channel Silicon-Gate Technology

- 8-Bit Output for Use in Microprocessor-Based Systems

- Low Power on TMS 27L08-45 . . . 245 mW (Typ)

- 10% Power Supply Tolerance (TMS 27L08-45 Only)

- Plug-Compatible Pin-Outs Allowing Interchangeability/Upgrade to 16K With Minimum Board Change

### description

The TMS 2708-35, TMS 2708-45, and TMS 27L08-45 JL are ultra-violet light-erasable, electrically programmable read only memories. They have 8,192 bits organized as 1024 words of 8-bit length. The devices are fabricated using N-channel silicon-gate technology for high speed and simple interface with MOS and bipolar circuits. All inputs (including program data inputs) can be driven by Series 74 TTL circuits without the use of external pull-up resistors. Each output can drive one Series 74 or 74LS TTL circuit without external resistors. The TMS 27L08 guarantees 200 mV dc noise immunity in the high state and 250 mV in the low state. The data outputs for the TMS 2708-35, TMS 2708-45, and TMS 27L08-45 are three-state for OR-tying multiple devices on a common bus.

These EPROMs are designed for high-density fixed-memory applications where fast turn arounds and/or program changes are required. They are supplied in a 24-pin dual-in-line ceramic cerdip (JL suffix) package designed for insertion in mounting-hole rows on 600-mil (15.2 mm) centers. They are designed for operation from 0°C to 70°C.

## operation (read mode)

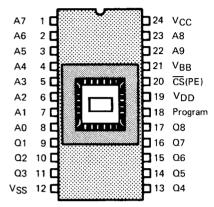

#### address (A0-A9)

The address-valid interval determines the device cycle time. The 10-bit positive-logic address is decoded on-chip to select one of the 1024 words of 8-bit length in the memory array. A0 is the least-significant bit and A9 is the most-significant bit of the word address.

#### chip select, program enable [CS (PE)]

When the chip select is low, all eight outputs are enabled and the eight-bit addressed word can be read. When the chip select is high, all eight outputs are in a high-impedance state.

#### data out (Q1-Q8)

The chip must be selected before the eight-bit output word can be read. Data will remain valid until the address is changed or the chip is deselected. When deselected, the three-state outputs are in a high-impedance state. The outputs will drive TTL circuits without external components.

#### program

The program pin must be held below VCC in the read mode.

### operation (program mode)

#### erase

Before programming, the TMS 2708-35, TMS 2708-45, or TMS 27L08-45 is erased by exposing the chip through the transparent lid to high-intensity ultraviolet light (wavelength 2537 angstroms). The recommended minimum exposure dose (= UV intensity × exposure time) is fifteen watt-seconds per square centimeter. Thus, a typical 12 milliwatt per square centimeter, filterless UV lamp will erase the device in a minimum of 21 minutes. The lamp should be located about 2.5 centimeters above the chip during erasure. After erasure, all bits are in the high state.

#### programming

Programming consists of successively depositing a small amount of charge to a selected memory cell that is to be changed from the erased high state to the low state. A low can be changed to a high only by erasure. Programming is normally accomplished on a PROM or EPROM Programmer, an example of which is TI's Universal PROM Programming Module in conjunction with the 990 prototyping system. Programming must be done at room temperature (25°C) only.

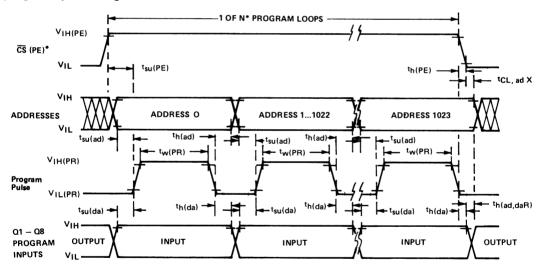

#### to start programming (see program cycle timing diagram)

First bring the  $\overline{CS}$  (PE) pin to +12 V to disable the outputs and convert them to inputs. This pin is held high for the duration of the programming sequence. The first word to be programmed is addressed (it is customary to begin with the "0" address) and the data to be stored is placed on the Q1-Q8 program inputs. Then a +25 V program pulse is applied to the program pin. After 0.1 to 1.0 milliseconds the program pin is brought back to 0 V. After at least one microsecond the word address is sequentially changed to the next location, the new data is set up and the program pulse is applied.

Programming continues in this manner until all words have been programmed. This constitutes one of N program loops. The entire sequence is then repeated N times with N x  $t_W(PR) \ge 100$  ms. Thus, if  $t_W(PR) = 1$  ms; then N = 100, the minimum number of program loops required to program the EPROM.

#### to stop programming

After cycling through the N program loops, the last program pulse is brought to 0 V, then Program Enable [CS (PE)] is brought to V<sub>|L</sub> which takes the device out of the program mode. The data supplied by the programmer must be removed before the address is changed since the program inputs are now data outputs and change of address could cause a voltage conflict on the output buffer. Q1-Q8 outputs are invalid up to 10 microseconds after the program enable pin is brought from V<sub>IH</sub>(PE) to V<sub>II</sub>.

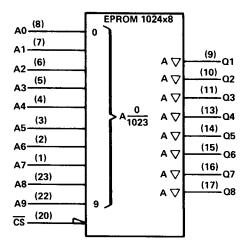

logic symbol<sup>†</sup>

<sup>†</sup> This symbol is in accordance with IEEE Std 91/ANSI Y32.14 and recent decisions by IEEE and IEC. See explanation on page 289.

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)\*

| Supply voltage, VCC (see Note 1)                | 15 V  |

|-------------------------------------------------|-------|

| Supply voltage, VDD (see Note 1)                |       |

| Supply voltage, VSS (see note 1)                | 15 V  |

| All input voltage (except program) (see Note 1) |       |

| Program input (see Note 1)                      | 35 V  |

| Output voltage (operating, with respect to VSS) | to 7V |

| Operating free-air temperature range            | 70°C  |

| Storage temperature range                       | 25 °C |

NOTE 1: Under absolute maximum ratings, voltage values are with respect to the most-negative supply voltage, VBB (substrate), unless otherwise noted.

Throughout the remainder of this data sheet, voltage values are with respect to VSS.

<sup>\*</sup> Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### recommended operating conditions

| PARAMETER                                                           | TMS270 | TMS2708-35, TMS2708-45 |                    |      | TMS27L08-45 |                    |      |

|---------------------------------------------------------------------|--------|------------------------|--------------------|------|-------------|--------------------|------|

| r ADAMETER                                                          | MIN    | NOM                    | MAX                | MIN  | NOM         | MAX                | UNIT |

| Supply voltage, VBB                                                 | -4.75  | -5                     | -5.25              | -4.5 | -5          | -5.5               | V    |

| Supply voltage, V <sub>CC</sub>                                     | 4.75   | 5                      | 5.25               | 4.5  | 5           | 5.5                | V    |

| Supply voltage, V <sub>DD</sub>                                     | 11.4   | 12                     | 12.6               | 10.8 | 12          | 13.2               | V    |

| Supply voltage, VSS                                                 |        | 0                      |                    |      | 0           |                    | V    |

| High-level input voltage, VIH                                       |        |                        | 14 . 4             |      |             |                    |      |

| (except program and program enable)                                 | 2.4    |                        | V <sub>CC</sub> +1 | 2.2  |             | V <sub>CC</sub> +1 | \ \  |

| High-level program enable input voltage, VIH(PE)                    | 11.4   | 12                     | 12.6               | 10.8 | 12          | 13.2               | V    |

| High-level program input voltage, VIH(PR)                           | 25     | 26                     | 27                 | 25   | 26          | 27                 | V    |

| Low-level input voltage, VIL (except program)                       | VSS    |                        | 0.65               | Vss  |             | 0.65               | V    |

| Low-level program input voltage, VIL(PR)                            | \/     |                        | •                  |      |             |                    | V    |

| Note: $V_{IL}(PR)$ max $\leq V_{IH}(PR) - 25 V$                     | VSS    |                        | •                  | VSS  |             | 1                  | V    |

| High-level program pulse input current (sink), I <sub>IH</sub> (PR) |        |                        | 40                 |      |             | 40                 | mA   |

| Low-level program pusle input current (source), I <sub>IL(PR)</sub> |        |                        | 3                  |      |             | 3                  | mA   |

| Operating free-air temperature, TA                                  | 0      |                        | 70                 | 0    |             | 70                 | °C   |

## electrical characteristics over full ranges of recommended operating conditions (unless otherwise noted)

| PARAMETER |                                     | TEST CONDITIONS                                   |     | TMS 2708-35,<br>TMS 2708-45 |      | TMS 27L08-45 |                  |      | UNIT |

|-----------|-------------------------------------|---------------------------------------------------|-----|-----------------------------|------|--------------|------------------|------|------|

|           |                                     |                                                   | MIN | MIN TYP <sup>†</sup>        |      | MIN          | TYP <sup>†</sup> | MAX  | 1    |

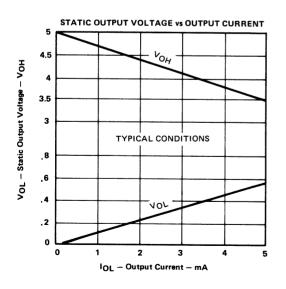

| Vон       | High-level output voltage           | $I_{OH} = -100 \mu A$                             | 3.7 |                             |      | 3.7          |                  |      | T    |

| *UH       | riigii-level output voltage         | I <sub>OH</sub> = -1 mA                           | 2.4 | 2.4                         |      | 2.4          |                  |      | \ \  |

| VOL       | Low-level output voltage            | IOL = 1.6 mA                                      |     |                             | 0.45 |              |                  | 0.40 | V    |

| lį        | Input current (leakage)             | V <sub>I</sub> = 0 V to 5.25 V                    |     | 1                           | 10   |              | 1                | 10   | μΑ   |

| ю         | Output current (leakage)            | CS(PE) = 5 V,<br>$V_O = 0.4 V \text{ to } 5.25 V$ |     | 1                           | 10   |              | 1                | 10   | μΑ   |

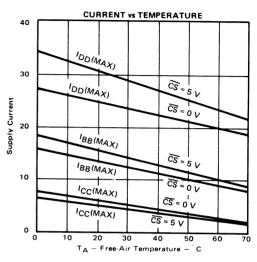

| IBB       | Supply current from VBB             | All inputs high,                                  |     | 30                          | 45   |              | 9                | 18   | mA   |

| lcc       | Supply current from VCC             | $\overline{CS}(PE) = 5 V,$                        |     | 6                           | 10   |              | .9               | 6    | mA   |

| lDD       | Supply current from V <sub>DD</sub> | T <sub>A</sub> = 0 °C<br>(worst case)             |     | 50                          | 65   |              | 20               | 34   | mA   |

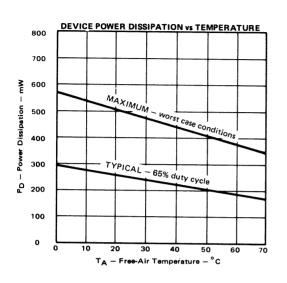

|           | T <sub>A</sub> = 70°C               |                                                   |     | 800                         |      |              | 350              |      |      |

| PD(AV)    | Power Dissipation                   | $T_A = 0$ °C $CS = 0V$                            |     |                             |      |              | 245              | 475  | mW   |

|           |                                     | $T_A = 0$ °C $CS = +5$ V                          |     |                             |      |              | 290              | 580  | 1    |

<sup>&</sup>lt;sup>†</sup>All typical values are at T<sub>A</sub> = 25 °C and nominal voltages.

## capacitance over recommended supply voltage range and operating free-air temperature range, $\mathbf{f} = \mathbf{1} \ \mathbf{MHz}$

|    | PARAMETER          | TYP† | MAX | UNIT |

|----|--------------------|------|-----|------|

| Ci | Input capacitance  | 4    | 6   | pF   |

| Co | Output capacitance | 8    | 12  | pF   |

†All typical values are at  $T_A = 25$ °C and nominal voltages.

## switching characteristics over recommended supply voltage range and operating free-air temperature range

|                    | PARAMETER                              | TEST CONDITIONS                           | TMS2 | 708-35 |     | 2708<br>27L08 | UNIT |

|--------------------|----------------------------------------|-------------------------------------------|------|--------|-----|---------------|------|

|                    |                                        |                                           | MIN  | MAX    | MIN | MAX           |      |

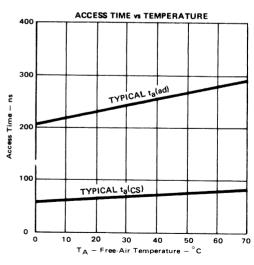

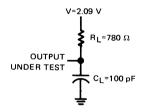

| ta(ad)             | Access time from address               |                                           |      | 300    |     | 450           | ns   |

| ta(CS)             | Access time from CS                    | C <sub>L</sub> = 100 pF                   |      | 120    |     | 120           | ns   |

| t <sub>V</sub> (A) | Output data valid after address change | 1 Series 74 TTL load                      | 0    |        | 0   |               | ns   |

| <sup>t</sup> dis   | Output disable time <sup>†</sup>       | $t_{f(CS)}$ , $t_{f(ad)} = 20 \text{ ns}$ | 0    | 120    | 0   | 120           | ns   |

| t <sub>c(rd)</sub> | Read cycle time                        |                                           | 300  |        | 450 |               | ns   |

<sup>†</sup> Value calculated from 0.5 volt delta to measured output level.

T<sub>A</sub> = 25 °C program characteristics over recommended supply voltage range

|                     | PARAMETER                                          | MIN  | MAX  | UNIT |

|---------------------|----------------------------------------------------|------|------|------|

| tw(PR)              | Pulse width, program pulse                         | 0.1  | 1    | ms   |

| tŢ                  | Transition times (except program pulse)            |      | 20   | ns   |

| tT(PR)              | Transition times, program pulse                    | 50   | 2000 | ns   |

| t <sub>su(ad)</sub> | Address setup time                                 | 10   |      | μS   |

| <sup>t</sup> su(da) | Data setup time                                    | 10   |      | μS   |

| t <sub>su(PE)</sub> | Program enable setup time                          | 10   |      | μS   |

| th(ad)              | Address hold time                                  | 1000 |      | ns   |

| th(ad,da R)         | Address hold time after program input data stopped | 0    |      | ns   |

| th(da)              | Data hold time                                     | 1000 |      | ns   |

| th(PE)              | Program enable hold time                           | 500  |      | ns   |

| <sup>t</sup> CL,adX | Delay time, CS(PE) low to address change           | 0    |      | ns   |

### PARAMETER MEASUREMENT INFORMATION

FIGURE 1 - TYPICAL OUTPUT LOAD CIRCUIT

## read cycle timing tc(rd) ADDRESSES ADDRESSES VALID ADDRESSES VALID ۷щ CS(PE) VIL ta(ad) ta(CS) + - t<sub>dis</sub> t<sub>V</sub>(A) → Vон Q1-Q8 VALID VALID VOL

### program cycle timing

\*CS (PE) is at +12 V through N program loops where N ≥ 100 ms/tw (PR).

NOTE: Q1-Q8 outputs are invalid up to 10 µsec after programming [CS(PE) goes low].

All timing reference points in this data sheet (inputs and outputs) are 90% points.

## **TYPICAL TMS 27L08-45 CHARACTERISTICS**