# 4th Generation USB 2.0 Flash Media Controller with Integrated Card Power FETs

# **Highlights**

- Complete System Solution for interfacing Smart-Media<sup>™</sup> (SM) or xD Picture Card<sup>™</sup> (xD)<sup>1</sup>, Memory Stick<sup>®</sup> (MS), High Speed Memory Stick (HSMS), Memory Stick PRO (MSPRO), MS Duo<sup>™</sup>, Secure Digital (SD), Mini-Secure Digital (Mini-SD), Trans-Flash (SD), MultiMediaCard<sup>™</sup> (MMC), Reduced Size MultiMediaCard (RS-MMC), NAND Flash, Compact Flash<sup>®</sup> (CF) and CF Ultra<sup>™</sup> I & II, and CF form-factor ATA hard drives to USB 2.0 bus

- Supports USB Bulk Only Mass Storage Compliant Bootable BIOS

- Support for simultaneous operation of all above devices. (only one at a time of each of the following groups supported: CF or ATA drive, SM or XD or NAND, SD or MMC)

- On-Chip 4-Bit High Speed Memory Stick and MS PRO Hardware Circuitry

- On-Chip firmware reads and writes High Speed Memory Stick and MS PRO

- 1-bit ECC correction performed in hardware for maximum efficiency

- Hardware support for SD Security Command Extensions

- On-chip power FETs for supplying flash media card power with minimum board components

- · USB Bus Power Certified

- 3.3 Volt I/O with 5V input tolerance on VBUS/ GPIO3

- Complete USB Specification 2.0 Compatibility for Bus Powered Operation

- Includes USB 2.0 Transceiver

- A Bi-directional Control and a Bi-directional Bulk Endpoint are provided.

- 8051 8 bit microprocessor

- Provides low speed control functions

- 30 Mhz execution speed at 4 cycles per instruction average

- 12K Bytes of internal SRAM for general purpose scratchpad

- 768 Bytes of internal SRAM for general purpose scratchpad or program execution while re-flashing external ROM

- · Double Buffered Bulk Endpoint

- Bi-directional 512 Byte Buffer for Bulk Endpoint

- 64 Byte RX Control Endpoint Buffer

- 64 Byte TX Control Endpoint Buffer

- Internal or External Program Memory Interface

- 64K Byte Internal Code Space or Optional 64K Byte External Code Space using Flash, SRAM or EPROM memory.

- On Board 24Mhz Crystal Driver Circuit

- Can be clocked by 48MHz external source

- On-Chip 1.8V Regulator for Low Power Core Operation

- Internal PLL for 480Mhz USB 2.0 Sampling, Configurable MCU clock

- Supports firmware upgrade via USB bus if "boot block" Flash program memory is used

- 15 GPIOs for special function use: LED indicators, button inputs, power control to memory devices, etc.

- Inputs capable of generating interrupts with either edge sensitivity

- Attribute bit controlled features:

- Activity LED polarity/operation/blink rate

- Full or Partial Card compliance checking

- Bus or Self Powered

- LUN configuration and assignment

- Write Protect Polarity

- SmartDetach Detach from USB when no Card Inserted for Notebook apps

- Cover Switch operation for xD compliance

- Inquiry Command operation

- SD Write Protect operation

- Older CF card support

- Force USB 1.1 reporting

- Internal or External Power FET operation

- Compatible with Microsoft WinXP, WinME, Win2K SP3, Apple OS10, Softconnex, and Linux Multi-LUN Mass Storage Class Drivers

- Win2K, Win98/98SE and Apple OS8.6 and OS9 Multi-LUN Mass Storage Class Drivers available from Microchip

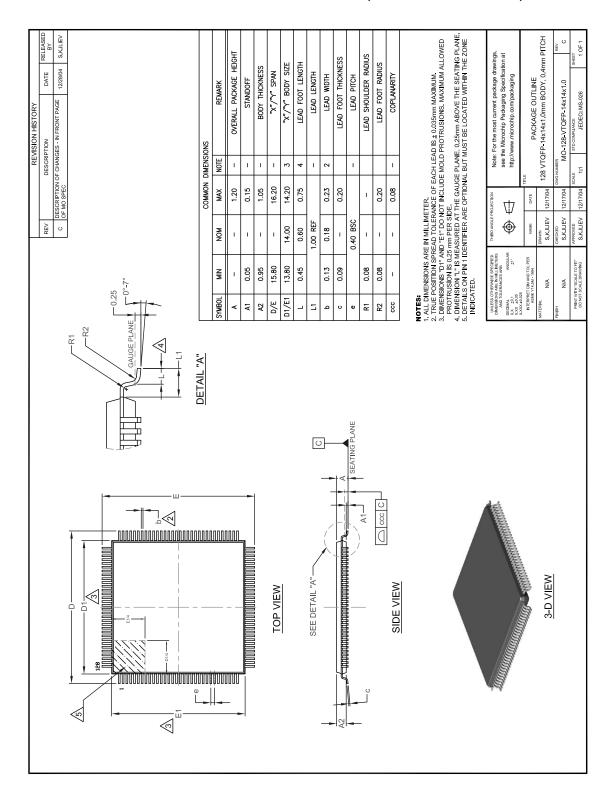

- 128-Pin VTQFP RoHS Compliant Package (14mm x 14mm footprint, 1.0mm height)

1.xD Picture Card not applicable to USB2227

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# **Table of Contents**

| 1.0 General Description                 | 4    |

|-----------------------------------------|------|

| 2.0 Pin Configuration                   | 5    |

| 3.0 Block Diagram                       | 6    |

| 4.0 Pin Descriptions                    |      |

| 5.0 DC Parameters                       |      |

| 5.0 Package Information                 |      |

| 7.0 GPIO Usage                          |      |

| Appendix A: Data Sheet Revision History |      |

| The Microchip Web Site                  | . 22 |

| Customer Change Notification Service    |      |

| Customer Support                        |      |

| Product Identification System           |      |

## 1.0 GENERAL DESCRIPTION

The USB2227/USB2228 is a USB 2.0 Bulk Only Mass Storage Class Peripheral Controller intended for supporting CompactFlash (CF and CF Ultra I/II) in True IDE Mode only, SmartMedia (SM) and XD cards, Memory Stick (MS), Memory Stick DUO (MSDUO) and Memory Stick Pro (MSPRO), Secure Digital (SD), and MultiMediaCard (MMC) flash memory devices. It provides a single chip solution for the most popular flash memory cards in the market.

The device consists of a USB 2.0 PHY and SIE, buffers, Fast 8051 microprocessor with expanded scratchpad, and program SRAM, and CF, MS, SM and SD controllers. The SD controller supports both SD and MMC devices. SM controller supports both SM and xD cards.

Provisions for external Flash Memory up to 64K bytes for program storage is provided.

12K bytes of scratchpad SRAM and 768 Bytes of program SRAM are also provided.

Fifteen GPIO pins are provided for indicators, external serial EEPROM for OEM id and system configuration information, and other special functions.

Internal power FETs are provided to directly supply power to the xD/SM, MMC/SD and MS/MSPro cards.

The internal ROM program is capable of implementing any combination of single or multi-LUN CF/SD/MMC/SM/MS reader functions with individual card power control and activity indication. Microchip also provides licenses\*\* for Win98 and Win2K drivers and setup utilities. Note: Please check with Microchip for precise features and capabilities for the current ROM code release.

## 1.1 Acronyms

SM: SmartMedia

**SMC:** SmartMedia Controller

FM: Flash Media

FMC: Flash Media Controller

CF: Compact Flash

CFC: CompactFlash Controller

SD: Secure Digital

**SDC:** Secure Digital Controller

MMC: MultiMediaCardMS: Memory Stick

MSC: Memory Stick Controller

TPC: Transport Protocol Code.

ECC: Error Checking and Correct

ECC: Error Checking and Correcting

CRC: Cyclic Redundancy Checking

## 2.0 PIN CONFIGURATION

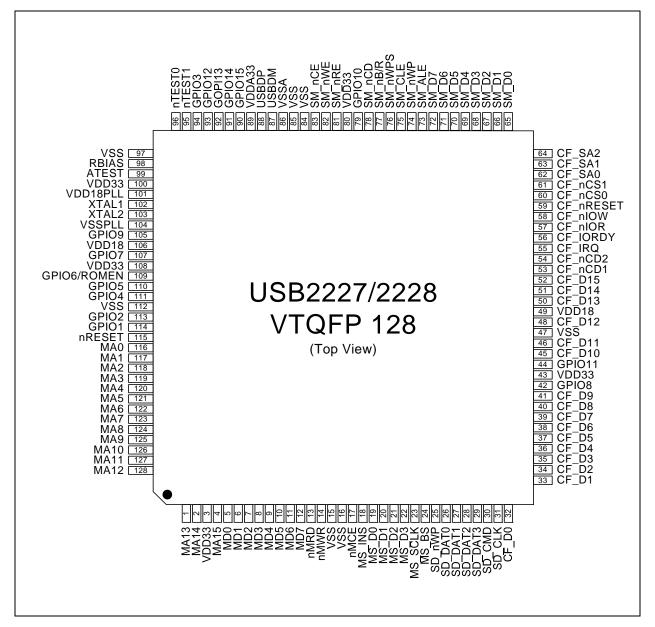

FIGURE 2-1: USB2227/USB2228 128-PIN VTQFP

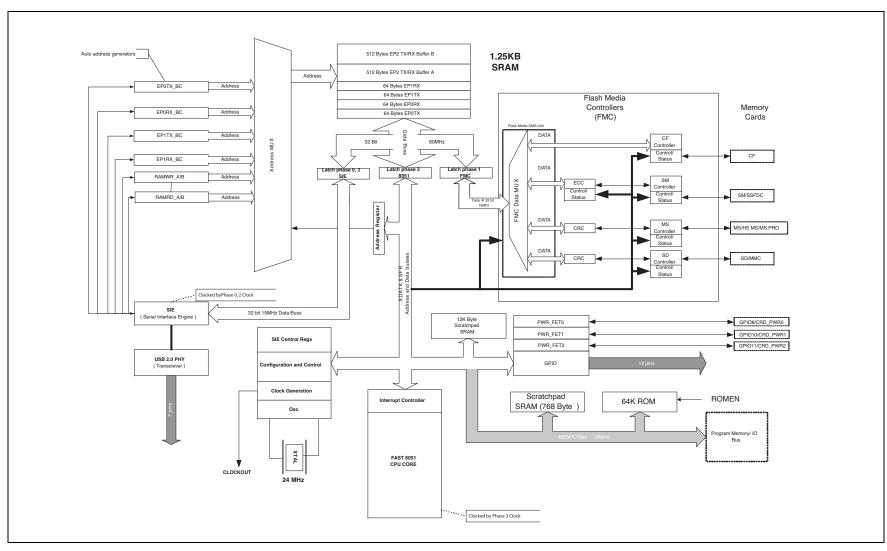

# 3.0 BLOCK DIAGRAM

# FIGURE 3-1: USB2227/USB2228 BLOCK DIAGRAM

## 4.0 PIN DESCRIPTIONS

This section provides a detailed description of each signal. The signals are arranged in functional groups according to their associated interface.

The "n" symbol in the signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "n" is not present before the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used exclusively. This is done to avoid confusion when working with a mixture of "active low" and "active high" signal. The term assert, or assertion indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term negate, or negation indicates that a signal is inactive.

# 4.1 PIN Descriptions

| Symbol     | 128-Pin<br>VTQFP | Buffer Type | Description                                                                                                                 |  |  |  |

|------------|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

|            |                  | CompactFlas | h (In True IDE Mode) Interface                                                                                              |  |  |  |

| CF_nCS1    | 61               | O8PU        | CF Chip Select 1:                                                                                                           |  |  |  |

|            |                  |             | This pin is the active low chip select 1 signal for the CF ATA device.                                                      |  |  |  |

| CF_nCS0    | 60               | O8PU        | CF Chip Select 0:                                                                                                           |  |  |  |

|            |                  |             | This pin is the active low chip select 0 signal for the task file registers of CF ATA device in the True IDE mode.          |  |  |  |

| CF_SA2     | 64               | O8          | CF Register Address 2:                                                                                                      |  |  |  |

|            |                  |             | This pin is the register select address bit 2 for the CF ATA device.                                                        |  |  |  |

| CF_SA1     | 63               | 08          | CF Register Address 1:                                                                                                      |  |  |  |

|            |                  |             | This pin is the register select address bit 1 for the CF ATA device.                                                        |  |  |  |

| CF_SA0     | 62               | 08          | CF Register Address 0:                                                                                                      |  |  |  |

|            |                  |             | This pin is the register select address bit 0 for the CF ATA device.                                                        |  |  |  |

| CF_IRQ     | 55               | IPD         | CF Interrupt:                                                                                                               |  |  |  |

|            |                  |             | This is the active high interrupt request signal from the CF device.                                                        |  |  |  |

| CF_D[15:8] | 52<br>51         | I/O8PD      | CF Data 15-8:                                                                                                               |  |  |  |

|            | 50<br>48         |             | The bi-directional data signals CF_D15-CF_D8 in True IDE mode data transfer.                                                |  |  |  |

|            | 46<br>45<br>41   |             | In the True IDE Mode, all of task file register operation occur on the CF_D[7:0], while the data transfer is on CF_D[15:0]. |  |  |  |

|            | 40               |             | The bi-directional data signal has an internal weak pull-down resistor.                                                     |  |  |  |

| CF_D[7:0]  | 39               | I/O8PD      | CF Data 7-0:                                                                                                                |  |  |  |

|            | 38<br>37         |             | The bi-directional data signals CF_D7-CF_D0 in the True IDE                                                                 |  |  |  |

|            | 36<br>35         |             | mode data transfer. In the True IDE Mode, all of task file register operation occur on                                      |  |  |  |

|            | 34               |             | the CF_D[7:0], while the data transfer is on CF_D[15:0].                                                                    |  |  |  |

|            | 33<br>32         |             | The bi-directional data signal has an internal weak pull-down resistor.                                                     |  |  |  |

| CF_IORDY   | 56               | IPU         | IO Ready:                                                                                                                   |  |  |  |

|            |                  |             | This pin is active high input signal.                                                                                       |  |  |  |

|            |                  |             | This pin has an internally controlled weak pull-up resistor.                                                                |  |  |  |

| Symbol    | 128-Pin<br>VTQFP     | Buffer Type | Description                                                                                                                                                                                      |  |  |  |

|-----------|----------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CF_nCD2   | 54                   | IPU         | CF Card Detection2:                                                                                                                                                                              |  |  |  |

|           |                      |             | This card detection pin is connected to the ground on the CF device, when the CF device is inserted.                                                                                             |  |  |  |

|           |                      |             | This pin has an internally controlled weak pull-up resistor.                                                                                                                                     |  |  |  |

| CF_nCD1   | 53                   | IPU         | CF Card Detection1:                                                                                                                                                                              |  |  |  |

|           |                      |             | This card detection pin is connected to ground on the CF device, when the CF device is inserted.                                                                                                 |  |  |  |

|           |                      |             | This pin has an internally controlled weak pull-up resistor.                                                                                                                                     |  |  |  |

| CF_nRESET | 59                   | 08          | CF Hardware Reset:                                                                                                                                                                               |  |  |  |

|           |                      |             | This pin is an active low hardware reset signal to CF device.                                                                                                                                    |  |  |  |

| CF_nIOR   | 57                   | 08          | CF IO Read:                                                                                                                                                                                      |  |  |  |

|           |                      |             | This pin is an active low read strobe signal for CF device.                                                                                                                                      |  |  |  |

| CF_nIOW   | 58                   | O8          | CF IO Write Strobe:                                                                                                                                                                              |  |  |  |

|           |                      |             | This pin is an active low write strobe signal for CF device.                                                                                                                                     |  |  |  |

|           |                      | Sr          | nartMedia Interface                                                                                                                                                                              |  |  |  |

| SM_nWP    | 74                   | O8PD        | SM Write Protect:                                                                                                                                                                                |  |  |  |

|           |                      |             | This pin is an active low write protect signal for the SM device.                                                                                                                                |  |  |  |

|           |                      |             | This pin has a weak pull-down resistor that is permanently enabled.                                                                                                                              |  |  |  |

| SM_ALE    | 73                   | O8PD        | SM Address Strobe:                                                                                                                                                                               |  |  |  |

|           |                      |             | This pin is an active high Address Latch Enable signal for the SM device.                                                                                                                        |  |  |  |

|           |                      |             | This pin has a weak pull-down resistor that is permanently enabled.                                                                                                                              |  |  |  |

| SM_CLE    | 75                   | O8PD        | SM Command Strobe:                                                                                                                                                                               |  |  |  |

|           |                      |             | This pin is an active high Command Latch Enable signal for the SM device.                                                                                                                        |  |  |  |

|           |                      |             | This pin has a weak pull-down resistor that is permanently enabled.                                                                                                                              |  |  |  |

| SM_D[7:0] | 72<br>71             | I/O8PD      | SM Data 7-0:                                                                                                                                                                                     |  |  |  |

|           | 70                   |             | These pins are the bi-directional data signal SM_D7-SM_D0.                                                                                                                                       |  |  |  |

|           | 69<br>68<br>67<br>66 |             | The bi-directional data signal has an internal weak pull-down resistor.                                                                                                                          |  |  |  |

| SM PDE    | 65                   | 08PU        | SM Read Enable:                                                                                                                                                                                  |  |  |  |

| SM_nRE    | 81                   | UOFU        |                                                                                                                                                                                                  |  |  |  |

|           |                      |             | This pin is an active low read strobe signal for SM device.                                                                                                                                      |  |  |  |

|           |                      |             | When using the internal FET, this pin has an internal weak pull-<br>up resistor that is tied to the output of the internal Power FET.                                                            |  |  |  |

|           |                      | 08          | If an external FET is used (Internal FET is disabled), then the internal pull-up is not available (external pull-ups must be used, and should be connected to the applicable Card Power Supply). |  |  |  |

| Symbol       | 128-Pin<br>VTQFP | Buffer Type | Description                                                                                                                                                                                      |  |  |  |

|--------------|------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SM_nWE       | 82               | O8PU        | SM Write Enable:                                                                                                                                                                                 |  |  |  |

|              |                  |             | This pin is an active low write strobe signal for SM device.                                                                                                                                     |  |  |  |

|              |                  |             | When using the internal FET, this pin has an internal weak pull-up resistor that is tied to the output of the internal Power FET.                                                                |  |  |  |

|              |                  | 08          | If an external FET is used (Internal FET is disabled), then the internal pull-up is not available (external pull-ups must be used, and should be connected to the applicable Card Power Supply). |  |  |  |

| SM_nWPS      | 76               | IPU         | SM Write Protect Switch:                                                                                                                                                                         |  |  |  |

|              |                  |             | A write-protect seal is detected, when this pin is low.                                                                                                                                          |  |  |  |

|              |                  |             | This pin has an internally controlled weak pull-up resistor.                                                                                                                                     |  |  |  |

| SM_nB/R      | 77               | I           | SM Busy or Data Ready:                                                                                                                                                                           |  |  |  |

|              |                  |             | This pin is connected to the BSY/RDY pin of the SM device.                                                                                                                                       |  |  |  |

|              |                  |             | An external pull-up resistor is required on this signal. The pull-up resistor must be pulled up to the same power source that powers the SM/NAND flash device.                                   |  |  |  |

| SM_nCE       | 83               | O8PU        | SM Chip Enable:                                                                                                                                                                                  |  |  |  |

|              |                  |             | This pin is the active low chip enable signal to the SM device.                                                                                                                                  |  |  |  |

|              |                  |             | When using the internal FET, this pin has an internal weak pull-up resistor that is tied to the output of the internal Power FET.                                                                |  |  |  |

|              |                  | 08          | If an external FET is used (Internal FET is disabled), then the internal pull-up is not available (external pull-ups must be used, and should be connected to the applicable Card Power Supply). |  |  |  |

| SM_nCD       | 78               | IPU         | SM Card Detection:                                                                                                                                                                               |  |  |  |

|              |                  |             | This is the card detection signal from SM device to indicate if the device is inserted.                                                                                                          |  |  |  |

|              |                  |             | This pin has an internally controlled weak pull-up resistor.                                                                                                                                     |  |  |  |

|              |                  | Ме          | mory Stick Interface                                                                                                                                                                             |  |  |  |

| MS_BS        | 24               | O8          | MS Bus State:                                                                                                                                                                                    |  |  |  |

|              |                  |             | This pin is connected to the BS pin of the MS device.                                                                                                                                            |  |  |  |

|              |                  |             | It is used to control the Bus States 0, 1, 2 and 3 (BS0, BS1, BS2 and BS3) of the MS device.                                                                                                     |  |  |  |

| MS_SDIO/MS_D | 19               | I/O8PD      | MS System Data In/Out:                                                                                                                                                                           |  |  |  |

| 0            |                  |             | This pin is a bi-directional data signal for the MS device.                                                                                                                                      |  |  |  |

|              |                  |             | Most significant bit (MSB) of each byte is transmitted first by either MSC or MS device.                                                                                                         |  |  |  |

|              |                  |             | The bi-directional data signal has an internal weak pull-down resistor.                                                                                                                          |  |  |  |

| MS_D1        | 20               | I/O8PD      | MS System Data In/Out:                                                                                                                                                                           |  |  |  |

|              |                  |             | This pin is a bi-directional data signal for the MS device.                                                                                                                                      |  |  |  |

|              |                  |             | This pin has internally controlled weak pull-up and pull-down resistors for various operational modes.                                                                                           |  |  |  |

| Symbol         | 128-Pin<br>VTQFP | Buffer Type | Description                                                                                                                         |  |  |  |

|----------------|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MS_D[3:2]      | 22               | I/O8PD      | MS System Data In/Out:                                                                                                              |  |  |  |

|                | 21               |             | This pin is a bi-directional data signal for the MS device.                                                                         |  |  |  |

|                |                  |             | The bi-directional data signal has an internal weak pull-down resistor.                                                             |  |  |  |

| MS_INS         | 18               | IPU         | MS Card Insertion:                                                                                                                  |  |  |  |

|                |                  |             | This pin is the card detection signal from the MS device to indicate, if the device is inserted.                                    |  |  |  |

|                |                  |             | This pin has an internally controlled weak pull-up resistor.                                                                        |  |  |  |

| MS_SCLK        | 23               | 08          | MS System CLK:                                                                                                                      |  |  |  |

|                |                  |             | This pin is an output clock signal to the MS device.                                                                                |  |  |  |

|                |                  |             | The clock frequency is software configurable.                                                                                       |  |  |  |

|                | T                | ı           | SD Interface                                                                                                                        |  |  |  |

| SD_DAT[3:0]    | 29<br>28         | I/O8PU      | SD Data 3-0:                                                                                                                        |  |  |  |

|                | 27               |             | These are bi-directional data signals.                                                                                              |  |  |  |

|                | 26               |             | These pins have internally controlled weak pull-up resistors.                                                                       |  |  |  |

| SD_CLK         | 31               | 08          | SD Clock:                                                                                                                           |  |  |  |

|                |                  |             | This is an output clock signal to SD/MMC device.                                                                                    |  |  |  |

|                |                  |             | The clock frequency is software configurable.                                                                                       |  |  |  |

| SD_CMD         | 30               | I/O8PU      | SD Command:                                                                                                                         |  |  |  |

|                |                  |             | This is a bi-directional signal that connects to the CMD signal of SD/MMC device.                                                   |  |  |  |

|                |                  |             | This pin has an internally controlled weak pull-up resistor.                                                                        |  |  |  |

| SD_nWP         | 25               | IPD         | SD Write Protected:                                                                                                                 |  |  |  |

|                |                  |             | This pin is an input signal with an internal weak pull-down.                                                                        |  |  |  |

|                |                  |             | This pin has an internally controlled weak pull-down resistor.                                                                      |  |  |  |

|                |                  |             | USB Interface                                                                                                                       |  |  |  |

| USBDM<br>USBDP | 87               | IO-U        | USB Bus Data:                                                                                                                       |  |  |  |

| USBDP          | 88               |             | These pins connect to the USB bus data signals.                                                                                     |  |  |  |

| RBIAS          | 98               | I           | USB Transceiver Bias:                                                                                                               |  |  |  |

|                |                  |             | A 12.0k $\Omega$ , $\pm$ 1.0% resistor is attached from VSSA to this pin, in order to set the transceiver's internal bias currents. |  |  |  |

| ATEST          | 99               | AIO         | Analog Test:                                                                                                                        |  |  |  |

|                |                  |             | This signal is used for testing the analog section of the chip and should be connected to VDDA33 for normal operation.              |  |  |  |

| VDD18PLL       | 101              |             | 1.8v Power for the PLL                                                                                                              |  |  |  |

| VSSPLL         | 104              |             | PLL Ground Reference:                                                                                                               |  |  |  |

|                |                  |             | Ground Reference for 1.8v PLL power                                                                                                 |  |  |  |

| VDDA33         | 89               |             | 3.3v Analog Power                                                                                                                   |  |  |  |

| VSSA           | 86               |             | Analog Ground Reference:                                                                                                            |  |  |  |

|                |                  |             | Analog Ground Reference for 3.3v Analog Power.                                                                                      |  |  |  |

| Symbol             | 128-Pin<br>VTQFP                                                             | Buffer Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|--------------------|------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| XTAL1/             | 102                                                                          | ICLKx       | Crystal Input/External Clock Input:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| CLKIN              |                                                                              |             | 24Mhz Crystal or external clock input. This pin can be connected to one terminal of the crystal or can be connected to an external 24Mhz clock when a crystal is not used.  Note: The MA[2:0] pins will be sampled while nRESET is asserted, and the value will be latched upon nRESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                    |                                                                              |             | negation. This will determine the clock source and value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| XTAL2              | 103                                                                          | OCLKx       | Crystal Output:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                    |                                                                              |             | 24Mhz Crystal This is the other terminal of the crystal, or left open when an external clock source is used to drive XTAL1/CLKIN. It may not be used to drive any external circuitry other than the crystal circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                    |                                                                              | Me          | emory I/O Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| MD[7:0]            | 12<br>11                                                                     | I/O8PU      | Memory Data Bus:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                    | 10<br>9<br>8                                                                 |             | When ROMEN bit of GPIO_IN1 register = 0, these signals are used to transfer data between the internal CPU and the external program memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | 7<br>6<br>5                                                                  |             | These pins have internally controlled weak pull-up resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| MA[15:3]           | 4                                                                            | O8          | Memory Address Bus:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                    | 2<br>1<br>128<br>127<br>126<br>125<br>124<br>123<br>122<br>121<br>120<br>119 |             | These signals address memory locations within the external memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| MA2/<br>SEL_CLKDRV | 118                                                                          | I/O8PD      | Memory Address Bus:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                    |                                                                              |             | MA2 Addresses memory locations within the external memory.  SEL_CLKDRV. During nRESET assertion, this pins will select the operating clock mode (crystal or externally driven clock source), and a weak pull-down resistor is enabled. When nRESET is negated, the value will be internally latched and this pin will revert to MA2 functionality, the internal pull-down will be disabled.  '0' = Crystal operation (24MHz only) '1' = Externally driven clock source (24MHz or 48MHz)  Note: If the latched value is '1', then the MA2 pin is tri-stated when the following conditions are true:  1. IDLE bit (PCON.0) is 1.  2. INT2 is negated  3. SLEEP bit of CLOCK_SEL is 1.  If the latched value is '0', then the MA2 pin will function identically to the MA[15:3] pins at all times (other than during nRESET |  |  |  |

| Symbol         | 128-Pin<br>VTQFP | Buffer Type | Description                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|----------------|------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MA[1:0]/CLK_SE | 117              | I/O8PD      | Memory Address Bus:                                                                                                                                                                                                                                                                                                                          |  |  |  |

| L[1:0]         | 116              |             | MA[1:0], These signals address memory locations within the external memory.                                                                                                                                                                                                                                                                  |  |  |  |

|                |                  |             | SEL[1:0]. During nRESET assertion, these pins will select the operating frequency of the external clock, and the corresponding weak pull-down resistors are enabled. When nRESET is negated, the value on these pins will be internal latched and these pins will revert to MA[1:0] functionality, the internal pull-downs will be disabled. |  |  |  |

|                |                  |             | SEL[1:0] = '00'. 24MHz<br>SEL[1:0] = '01'. RESERVED<br>SEL[1:0] = '10'. RESERVED<br>SEL[1:0] = '11'. 48MHz                                                                                                                                                                                                                                   |  |  |  |

|                |                  |             | <b>Note:</b> If the latched value is '1', then the corresponding MA pin is tri-stated when the following conditions are true:                                                                                                                                                                                                                |  |  |  |

|                |                  |             | 1. IDLE bit (PCON.0) is 1.                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                |                  |             | 2. INT2 is negated                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                |                  |             | 3. SLEEP bit of CLOCK_SEL is 1.                                                                                                                                                                                                                                                                                                              |  |  |  |

|                |                  |             | If the latched value is '0', then the corresponding MA pin will function identically to the MA[15:3] pins at all times (other than during nRESET assertion).                                                                                                                                                                                 |  |  |  |

| nMWR           | 14               | O8          | Memory Write Strobe:                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                |                  |             | Program Memory Write; active low                                                                                                                                                                                                                                                                                                             |  |  |  |

| nMRD           | 13               | O8          | Memory Read Strobe:                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                |                  |             | Program Memory Read; active low                                                                                                                                                                                                                                                                                                              |  |  |  |

| nMCE           | 17               | O8          | Memory Chip Enable:                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                |                  |             | Program Memory Chip Enable; active low.                                                                                                                                                                                                                                                                                                      |  |  |  |

|                |                  |             | This signal is asserted, when any of the following conditions are no longer met:  1. IDLE bit (PCON.0) is 1.                                                                                                                                                                                                                                 |  |  |  |

|                |                  |             | 2. INT2 is negated                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                |                  |             | 3. SLEEP bit of CLOCK_SEL is 1.                                                                                                                                                                                                                                                                                                              |  |  |  |

|                |                  |             | <b>Note:</b> This signal is held to a logic 'high' while nRESET is asserted.                                                                                                                                                                                                                                                                 |  |  |  |

|                |                  |             | MISC                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| GPIO1          | 114              | I/O8        | General Purpose I/O:                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                |                  |             | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                                                                                             |  |  |  |

| GPIO2          | 113              | I/O8        | General Purpose I/O:                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                |                  |             | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                                                                                             |  |  |  |

| GPIO3          | 94               | I/O8        | General Purpose I/O:                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                |                  |             | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                                                                                             |  |  |  |

| GPIO4          | 111              | I/O8        | General Purpose I/O:                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                |                  |             | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                                                                                             |  |  |  |

| Symbol      | 128-Pin<br>VTQFP | Buffer Type | Description                                                                                                                                                                                                                                                       |  |  |  |

|-------------|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| GPIO5       | 110              | I/O8        | General Purpose I/O:                                                                                                                                                                                                                                              |  |  |  |

|             |                  |             | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                  |  |  |  |

| GPIO6/      | 109              | IPU         | GPIO6, ROMEN:                                                                                                                                                                                                                                                     |  |  |  |

| ROMEN       |                  |             | This pin has an internal weak pull-up resistor that is enabled or disabled by the state of nRESET. The pull-up is enabled when nRESET is active. The pull-up is disabled, when the nRESET is inactive (some clock cycles later, after the rising edge of nRESET). |  |  |  |

|             |                  |             | The state of this pin is latched internally on the rising edge of nRESET to determine if internal or external program memory is used.                                                                                                                             |  |  |  |

|             |                  |             | The state latched is stored in ROMEN bit of GPIO_IN1 register.                                                                                                                                                                                                    |  |  |  |

|             |                  | I/O8        | After the rising edge of nRESET, this pin may be used as GPIO6 or RXD.                                                                                                                                                                                            |  |  |  |

|             |                  |             | When pulled low via an external weak pull-down resistor, an external program memory should be connected to the memory data bus. The USB2227/USB2228 uses this external bus for program execution.                                                                 |  |  |  |

|             |                  |             | When this pin is left unconnected or pulled high by a weak pull-up resistor, the USB2227/USB2228 uses the internal ROM for program execution.                                                                                                                     |  |  |  |

| GPIO7       | 107              | I/O8        | General Purpose I/O:                                                                                                                                                                                                                                              |  |  |  |

|             |                  |             | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                  |  |  |  |

| GPIO8/      | = = = :          |             | General Purpose I/O or Card Power:                                                                                                                                                                                                                                |  |  |  |

| CRD_PWR0    |                  |             | GPIO: This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                            |  |  |  |

|             |                  |             | CRD_PWR: Card Power drive of 3.3V @ 100mA.                                                                                                                                                                                                                        |  |  |  |

| GPIO9       | 105              | I/O8        | General Purpose I/O:                                                                                                                                                                                                                                              |  |  |  |

|             |                  |             | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                  |  |  |  |

| GPIO10/     | 79               | I/O8        | General Purpose I/O or Card Power:                                                                                                                                                                                                                                |  |  |  |

| CRD_PWR1    |                  |             | GPIO: These pins may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                          |  |  |  |

|             |                  |             | CRD_PWR: Card Power drive of 3.3V @ 100mA.                                                                                                                                                                                                                        |  |  |  |

| GPIO11/     | 44               | I/O8        | General Purpose I/O or Card Power:                                                                                                                                                                                                                                |  |  |  |

| CRD_PWR2    |                  |             | GPIO: This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                            |  |  |  |

|             |                  |             | CRD_PWR: Card Power drive of 3.3V @ 200mA.                                                                                                                                                                                                                        |  |  |  |

| GPIO[15:12] | 90               | I/O8        | General Purpose I/O:                                                                                                                                                                                                                                              |  |  |  |

|             | 91<br>92<br>93   |             | These pins may be used either as input, or output.                                                                                                                                                                                                                |  |  |  |

| nRESET      | 115              | IS          | RESET input:                                                                                                                                                                                                                                                      |  |  |  |

|             |                  |             | This active low signal is used by the system to reset the chip. The active low pulse should be at least $1\mu s$ wide.                                                                                                                                            |  |  |  |

| Symbol     | 128-Pin<br>VTQFP | Buffer Type  | Description                                                                                                                   |

|------------|------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------|

| nTEST[1:0] | 95               | I            | TEST input:                                                                                                                   |

|            | 96               |              | These signals are used for testing the chip. User should normally tie them high externally, if the test function is not used. |

|            |                  | Digital Powe | r, Grounds and no Connects                                                                                                    |

| VDD18      | 49               |              | 1.8v Digital Core Power:                                                                                                      |

|            | 106              |              | +1.8V Core power                                                                                                              |

|            |                  |              | All VDD18 pins must be connected together on the circuit board.                                                               |

| VDD33      | 3                |              | 3.3v Power & Voltage Regulator Input:                                                                                         |

|            | 43<br>80         |              | 3.3V Power & Regulator Input.                                                                                                 |

|            | 100<br>108       |              | Pins 100 & 108 supply 3.3V power to the internal 1.8V regulators.                                                             |

| VSS        | 15               |              | Ground:                                                                                                                       |

|            | 16<br>47<br>84   |              | Ground Reference                                                                                                              |

|            | 85<br>07         |              |                                                                                                                               |

|            | 97<br>112        |              |                                                                                                                               |

- **Note 1:** Hot-insertion capable card connectors are required for all flash media. It is required for SD connector to have Write Protect switch. This allows the chip to detect MMC card.

- 2: nMCE is normally asserted except when the 8051 is in standby mode.

- 3: VDD18 (Pin 106) and VDD18PLL (Pin 101) must have a 10uF +/-20% Low-ESR (equivalent series resistance) <0.1 ohm bypass capacitor to VSSA. These capacitors must be as close to these pins as possible.

# 4.2 Buffer Type Descriptions

TABLE 4-1: USB2227/USB2228 BUFFER TYPE DESCRIPTIONS

| Buffer | Description                                                                                 |

|--------|---------------------------------------------------------------------------------------------|

| I      | Input                                                                                       |

| IPU    | Input with internal weak pull-up resistor.                                                  |

| IPD    | Input with internal weak pull-down resistor.                                                |

| IS     | Input with Schmitt trigger                                                                  |

| I/O8   | Input/Output buffer with 8mA sink and 8mA source.                                           |

| I/O8PU | Input/Output buffer with 8mA sink and 8mA source, with an internal weak pull-up resistor.   |

| I/O8PD | Input/Output buffer with 8mA sink and 8mA source, with an internal weak pull-down resistor. |

| O8     | Output buffer with 8mA sink and 8mA source.                                                 |

| O8PU   | Output buffer with 8mA sink and 8mA source, with an internal weak pull-up resistor.         |

| O8PD   | Output buffer with 8mA sink and 8mA source, with an internal weak pull-down resistor.       |

| ICLKx  | XTAL clock input                                                                            |

| OCLKx  | XTAL clock output                                                                           |

| I/O-U  | Analog Input/Output Defined in USB specification                                            |

| AIO    | Analog Input/Output                                                                         |

# 5.0 DC PARAMETERS

# 5.1 Maximum Ratings

| Parameter                                 | Symbol                                   | MIN  | MAX                           | Units | Comments                                                                                                                                                                                                                                                                                           |

|-------------------------------------------|------------------------------------------|------|-------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Storage<br>Temperature                    | T <sub>A</sub>                           | -55  | 150                           | °C    |                                                                                                                                                                                                                                                                                                    |

| Lead<br>Temperature                       |                                          |      | 325                           | °C    | Soldering < 10 seconds                                                                                                                                                                                                                                                                             |