# Am9520/Am9521/AmZ8065

Burst Error Processor

# DISTINCTIVE CHARACTERISTICS

Provides for detection and correction of burst errors

Detects errors in serial data up to 585K bits long. Allows correction of error bursts of up to 12 bits.

High-Speed Operation

Effective data rates up to 20 Mbits/second for Am9520/ Am9521/AmZ8065 and 30 Mbits/second for -1 versions. Fast enough for high-performance hard and soft disk systems.

Selectable Industry-Standard Polynomials 35-bit and 32-bit polynomials on Am9521. Am9520/ Am28065 additionally has popular IBM 56-bit and 48-bit versions.

- Three correction algorithms provide flexibility

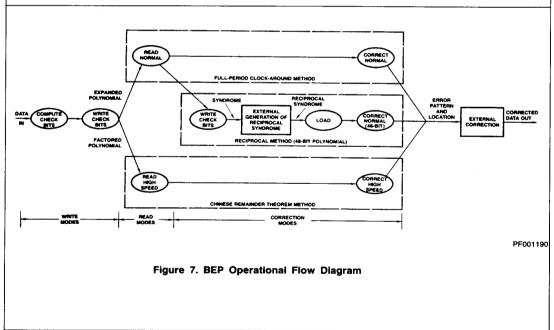

Iq j Full-period clock-around method for conforming to current practices. Chinese remainder theorem reduces correction time by orders of magnitude. Reciprocal polynomial makes correction possible with 48-bit code.

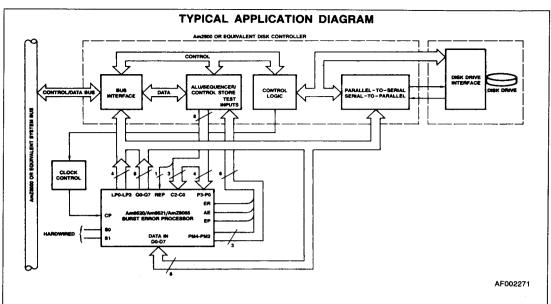

- Designed for use in both microprogrammed and microprocessor disk controller systems Device complements both AmZ8000 and Am2900 microprocessor families and can also be used with other microprocessors.

# GENERAL DESCRIPTION

The Burst Error Processor (BEP) provides for error detection and correction for high-performance disk systems and other systems in which high-speed serial data transfer takes place. As data density and transfer rates increase in both hard and floppy disks and other storage media, error detection and correction become increasingly important. The BEP is an LSI circuit that facilitates the most common error detection and correction schemes accommodating data streams of up to 585K bits at up to 20M bits/second effective data rate.

The BEP provides a choice of four standard polynomials, including the popular 56-bit and 48-bit versions, to satisfy a broad range of applications. The device divides the data stream by the selected polynomial using the rules of algebra in polynomial fields. The resulting remainder is the check word, which is then appended to the data for writing on the disk as a record. When the record is read back, the BEP computes the syndrome for data validation. If an error is detected, the location and pattern of this burst in the data stream is determined for corrections.

00617B

2-489

Refer to page 7-1 for Essential Information on Military Devices

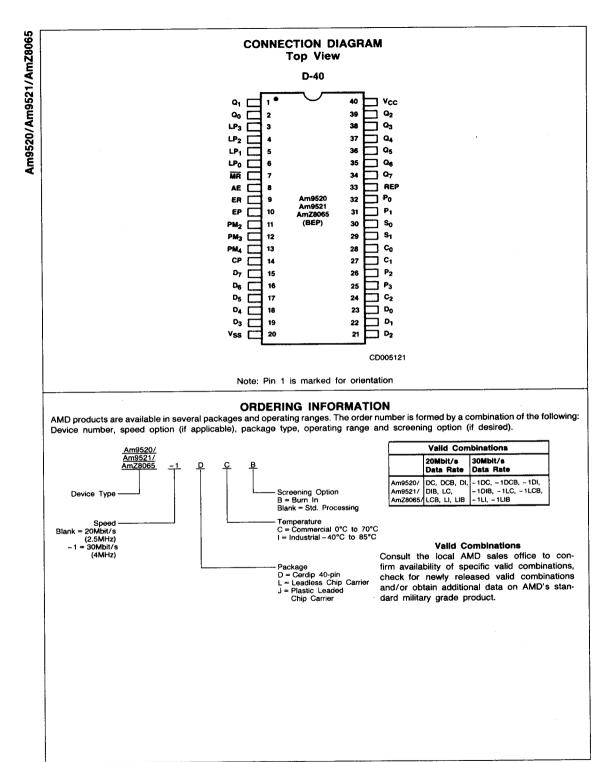

# PIN DESCRIPTION

| Pin No.                                                                                                                                                                                                                                                                                               | Name                             | 1/0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                            | Description                                                                                                                                                                                              |                                                                  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|

| 40                                                                                                                                                                                                                                                                                                    | Vcc                              |     | +5V Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                            |                                                                                                                                                                                                          |                                                                  |  |  |

| 20                                                                                                                                                                                                                                                                                                    | Vss                              |     | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                            |                                                                                                                                                                                                          |                                                                  |  |  |

| 30,29                                                                                                                                                                                                                                                                                                 | S <sub>0</sub> -S <sub>1</sub>   | ı   | Polynomial S<br>the Am9520                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | elect. Logic<br>. The follow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ving table s                                               | ese two inputs select one of the four sepecifies the polynomial select codes<br>DLYNOMIAL SELECT CODES                                                                                                   | tandard polynomials provided .                                   |  |  |

|                                                                                                                                                                                                                                                                                                       | }                                |     | S <sub>1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | S <sub>0</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                            | Polynomial                                                                                                                                                                                               | Number of<br>Check Bits                                          |  |  |

|                                                                                                                                                                                                                                                                                                       |                                  |     | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $(x^{12}+x^1)$                                             | • (X <sup>11</sup> + X <sup>7</sup> + X <sup>6</sup> + X+ 1) •<br><sup>1</sup> + X <sup>10</sup> + + X+ 1) •<br><sup>1</sup> + X <sup>7</sup> + X <sup>6</sup> + X <sup>5</sup> + X+ 1)                  | 56                                                               |  |  |

|                                                                                                                                                                                                                                                                                                       |                                  |     | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (X <sup>21</sup> +1)                                       | • (X <sup>11</sup> + X <sup>2</sup> + 1)                                                                                                                                                                 | 32                                                               |  |  |

|                                                                                                                                                                                                                                                                                                       |                                  |     | н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (X <sup>23</sup> + 1)<br>(X <sup>12</sup> + X <sup>1</sup> | •<br>1+ X <sup>8</sup> + X <sup>7</sup> + X <sup>3</sup> + X+ 1)                                                                                                                                         | 35                                                               |  |  |

|                                                                                                                                                                                                                                                                                                       |                                  |     | н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (X <sup>13</sup> + 1)<br>(X <sup>35</sup> + X <sup>2</sup> | •<br><sup>(3</sup> + X <sup>8</sup> + X <sup>2</sup> + 1)                                                                                                                                                | 48                                                               |  |  |

| 23,22<br>21,19<br>18,17<br>16,15                                                                                                                                                                                                                                                                      | D <sub>0</sub> -D <sub>7</sub>   | I   | most signification the LOW-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ant bit positi<br>to-HIGH tra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | on. HIGH or<br>nsition of th                               | d for entering information. D <sub>0</sub> is the let<br>n any input corresponds to 1, and LOW<br>e CP input. Any change on the D <sub>0</sub> -D <sub>7</sub> in<br>diagram for details on set-up and h | represents 0. Data entry occur<br>puts must take place only whe  |  |  |

| 28,27 24  Function Select. These three inputs specify the desired function according to the formula description of each function is found in later sections of this document. Any changement take place only when the CP input is HIGH. See Timing diagram for specifications.  FUNCTION SELECT CODES |                                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ny change on the Cn-Co input                               |                                                                                                                                                                                                          |                                                                  |  |  |

|                                                                                                                                                                                                                                                                                                       |                                  |     | C <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | C <sub>1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C <sub>0</sub>                                             | Function                                                                                                                                                                                                 | on .                                                             |  |  |

|                                                                                                                                                                                                                                                                                                       |                                  |     | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | L                                                          | Compute check bits                                                                                                                                                                                       |                                                                  |  |  |

|                                                                                                                                                                                                                                                                                                       |                                  |     | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Н                                                          | Write check bits                                                                                                                                                                                         |                                                                  |  |  |

|                                                                                                                                                                                                                                                                                                       |                                  |     | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | L                                                          | Read normal                                                                                                                                                                                              |                                                                  |  |  |

|                                                                                                                                                                                                                                                                                                       |                                  |     | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Н                                                          | Read high speed                                                                                                                                                                                          |                                                                  |  |  |

|                                                                                                                                                                                                                                                                                                       |                                  |     | н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | L                                                          | Load                                                                                                                                                                                                     |                                                                  |  |  |

|                                                                                                                                                                                                                                                                                                       | İ                                |     | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Н                                                          | Reserved                                                                                                                                                                                                 |                                                                  |  |  |

|                                                                                                                                                                                                                                                                                                       |                                  |     | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | L                                                          | Correct normal (Full period clock a                                                                                                                                                                      | around)                                                          |  |  |

|                                                                                                                                                                                                                                                                                                       |                                  |     | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | н                                                          | Correct high speed<br>(Chinese remainder theorem metho                                                                                                                                                   | od)                                                              |  |  |

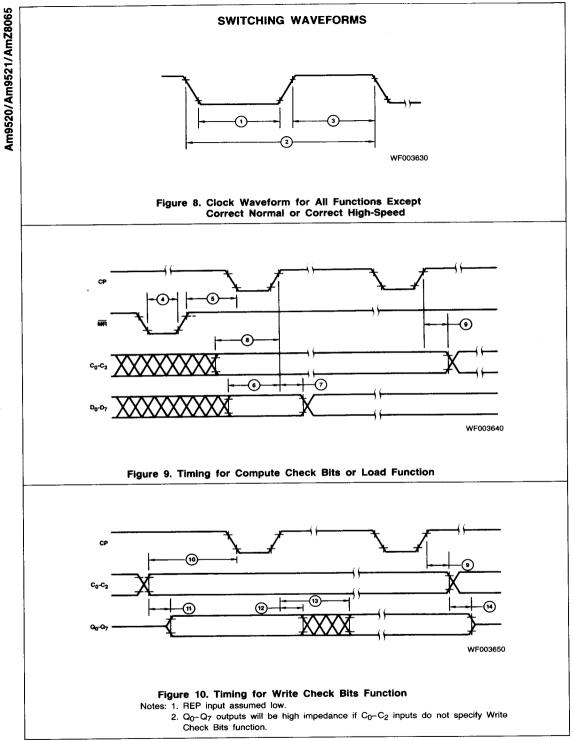

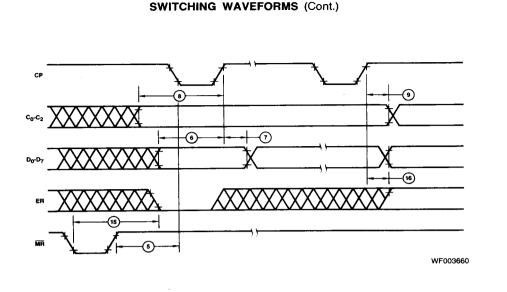

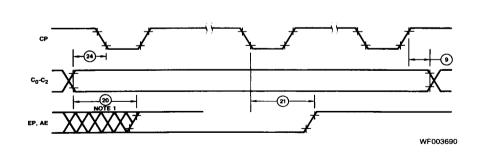

| 14                                                                                                                                                                                                                                                                                                    | СР                               | ı   | the CP input.<br>take place operations, if<br>note that re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Clock. Operations are controlled by this input. Outputs become valid after the LOW-to-HIGH transition on the CP input. The quiescent state of the CP input is HIGH. Any changes on the data and control inputs must take place only when the CP input is HIGH. See Timing diagrams for exact specifications. During operations, it may be required to stop the clock; the clock must be stopped in the HIGH state only. Also, note that requirements on the CP input during correction operations differ from those during other functions. See Timing diagram for details. |                                                            |                                                                                                                                                                                                          |                                                                  |  |  |

| 7                                                                                                                                                                                                                                                                                                     | MR                               | 1   | accomplish i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nitialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | before retu                                                | tializes the device. This input must rem<br>rining to the quiescent HIGH state. I<br>pute Check Bits, Read Normal, Read H                                                                                | n general, the devices requi                                     |  |  |

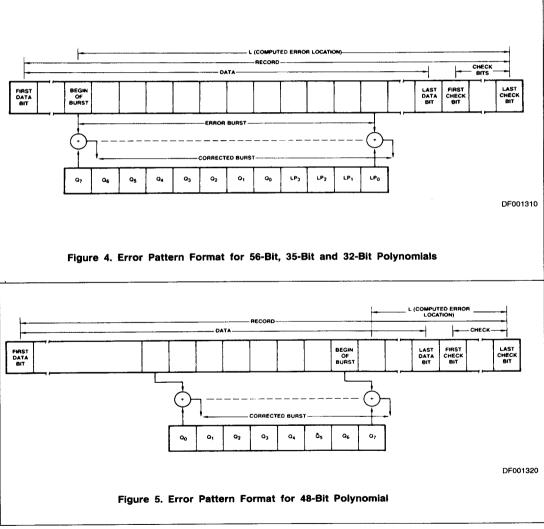

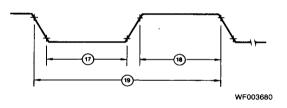

| 2,1,39<br>38,37<br>36,35<br>34                                                                                                                                                                                                                                                                        | Q <sub>0</sub> -Q <sub>7</sub>   | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                            | re made available on these eight outputs is the most significant. HIGH on these                                                                                                                          |                                                                  |  |  |

|                                                                                                                                                                                                                                                                                                       |                                  |     | a) The C <sub>0</sub> -<br>b) The RE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | C <sub>2</sub> inputs s<br>P input is I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | specify Writ                                               | the following conditions:  Check Bits Function.                                                                                                                                                          |                                                                  |  |  |

| 6,5                                                                                                                                                                                                                                                                                                   | I Pa I P-                        | +   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                            | are in a high-impedance state.  LP0-LP3 outputs together with the Q                                                                                                                                      | a-On outpute provide the 10 h                                    |  |  |

| 6,5<br>4,3                                                                                                                                                                                                                                                                                            | LP <sub>0</sub> -LP <sub>3</sub> |     | error pattern<br>represents 1<br>input is LOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | in which (<br>, and LOW<br>V, the LP <sub>0</sub> -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27 is the m<br>represents<br>LP3 outputs                   | ost significant bit and $LP_0$ is the leas 0. The REP input must be HIGH to reason are in the high-impedance state.                                                                                      | st significant bit position. HIG ad the error pattern. If the RE |  |  |

| 33                                                                                                                                                                                                                                                                                                    | REP                              | 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                            |                                                                                                                                                                                                          |                                                                  |  |  |

| 9                                                                                                                                                                                                                                                                                                     | ER                               | 0   | Read Error Pattern. A HIGH on this input activates the LP <sub>0</sub> -LP <sub>3</sub> and Q <sub>0</sub> -Q <sub>7</sub> outputs. This error pattern information is valid only after a HIGH is indicated on the EP output during correction operations. Error. HIGH on this output indicates that the BEP has detected an error. This output must be considered valid only after the last check byte during Read Normal or Read High Speed functions has been entered. The resulting syndrome is then contained in the register array. A non-zero syndrome indicates error; zero syndrome indicates no error. The ER output always reflects the state of this register array (zero or non- |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                            |                                                                                                                                                                                                          |                                                                  |  |  |

# Am9520/Am9521/AmZ8065

# PIN DESCRIPTION (Cont.)

| Pin No.  | Name                             | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|----------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10       | EP                               | 0   | Error Pattern. HIGH on this output indicates that the error pattern has been found during the correction process. When the last check byte was entered during a Read function, the resulting syndrome is contained in the register array. The error pattern information is buried in this syndrome. To extract the error pattern, the BEP is clocked while the appropriate (Correct Normal or Correct High Speed) code is applied to the Co-Co inputs until EP goes HIGH. The number of clocks required to find the error pattern is used to calucate where in the data stream the error has occurred.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          |                                  |     | The EP output will be LOW after initialization by the MR input. The EP output is valid only during the correction operations and must be ignored at all other times. See Correct Normal and Correct High Speed under Detailed Description for further details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11,12,13 | PM <sub>2</sub> -PM <sub>4</sub> | 0   | Pattern Match. When using the Chinese remainder theorem for error correction, information is loaded into several feedback shift registers simultaneously. The number of registers is equal to the number of factors of the polynomial. After a high speed operation, there are as many syndromes as there are factors. For correction, the register corresponding to the first factor must be shifted until the EP output indicates HIGH. Then each register corresponding to the remaining factors must be shifted until a match occurs in each register with the error pattern contained in the first register. HIGH on PM <sub>2</sub> , PM <sub>3</sub> or PM <sub>4</sub> outputs indicates that corresponding registers match. The PM <sub>2</sub> corresponds to the second factor, PM <sub>3</sub> corresponds to the third and PM <sub>4</sub> corresponds to the fourth factor. PM <sub>3</sub> corresponds to the third and PM <sub>4</sub> corresponds to the fourth factor. PM <sub>3</sub> corresponds to the fourth factor. If a polynomial has only two factors, then PM <sub>3</sub> and PM <sub>4</sub> outputs have no meaning. Indications on the PM <sub>2</sub> -PM <sub>4</sub> outputs must be considered valid only during high-speed correct function and should be ignored at all other times. |

| 6,5,4,3  | P <sub>0</sub> -P <sub>3</sub>   | ı   | Polynomial Shift Control. Correction procedure using the Chinese remainder theorem method requires tha each syndrome obtained from the High-Speed Read function be shifted individually. The Po-P3 inputs provide this capability: Po corresponds to the first factor, P1 corresponds to the second factor and so on HiGH on an input allows the corresponding register to shift and LOW causes it to hold. These inputs have an effect only during the Correct High-Speed function. Any change on these inputs must occur only when the CP input is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8        | AE                               | 0   | Alignment Exception. The devices use an 8-bit parallel mechanization of the feedback shift register configurations. Under certain conditions, the error pattern will not, therefore, automatically line up predetermined positions of the register array during the correction operations. HIGH on the AE output indicates that such a condition is detected. The Am9520 automatically switches into the one-bit shift mode. The number of clocks for which the AE output is HIGH is used in the error location calculation. See Detailed Description for further details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

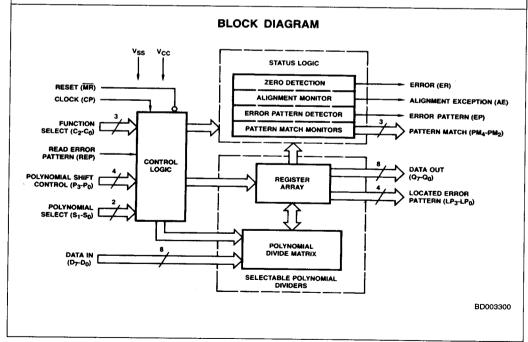

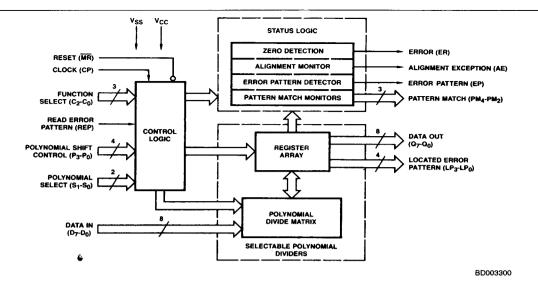

Figure 1. Am9520/Am9521/AmZ8065 Burst Error Processor

#### **ARCHITECTURE**

Figure 1 is a conceptual block diagram. It consists of four major sections – Register Array, Polynomial Divide Matrix, Status Logic and Control Logic.

### Register Array

This section consists of 56 flip-flops used for check bit computation during write operation, syndrome computation during read operation and error pattern extraction during error correction operation. In general, the Polynomial Divide Matrix provides the bit patterns required for the Register Array. The combination of Register Array and Polynomial Divide Matrix mechanizes the familiar serial form of feedback shift register arrangement in an 8-bit parallel form. The  $Q_0\!-\!Q_7$  outputs of the Am9520 are obtained from the Register Array. When correction operations are complete, the error pattern is available on 12 outputs: eight bits on the  $Q_0\!-\!Q_7$  outputs and the remaining four bits on the LP $_0\!-\!LP_3$  outputs. The Read Error Pattern (REP) input must be HIGH for the error pattern to be available. The Control Logic generates Clock signals for the Register Array.

#### Status Logic

This section monitors the register arrays to generate the various error detection outputs of the BEP, including ER, AE, PM<sub>2</sub>, PM<sub>3</sub>, PM<sub>4</sub> and EP.

# Polynomial Divide Matrix

Polynomial Divide Matrix is the heart of the BEP. The Control Logic decodes the Polynomial Select  $(S_0-S_1)$  and Function Select  $(C_0-C_2)$  inputs to generate the necessary gating signals to the matrix. The matrix establishes connections such that a byte of data presented on the  $D_0-D_7$  inputs will be suitably divided by the selected generator polynomial. Four different polynomials are selected by logic levels on the  $S_0-S_1$  inputs (Table 1).

These devices can be used in three fundamentally different types of operations: write, read and correct. The various functions are selected by the  $C_0$ - $C_2$  control inputs.

### Write

While data is being written on the disk, the BEP is in the Compute Check Bits mode looking at the data bytes without affecting the flow of data to the disk. After the last data byte, the BEP is switched into the Write Check Bits function, outputting the 4, 5, 6 or 7 check bytes. This is the additional information appended to the data stream that allows the detection and correction of possible read errors.

#### Read

When information (data plus appended check bits) is being read, the BEP must be in either Read Normal mode or Read High Speed mode. These modes differ only in the correction algorithm that will be used if an error has occurred. In both modes parallel bytes are read into the device. After the last information byte has been entered, the ER output is checked. If it is LOW, there is no error; if it is HIGH, there is an error.

#### Correction

After the read operation, the syndrome held in the Register Array contains all the information necessary to find the error location and the error pattern, i.e., to allow error correction. In the Correct Normal mode, the error location is found by counting the number of clock pulses required to make the EP output go HIGH. The error pattern is then available on the LP $_0$ -LP $_3$  and  $Q_0$ -Q $_7$  outputs and can be used to Exclusive OR with data.

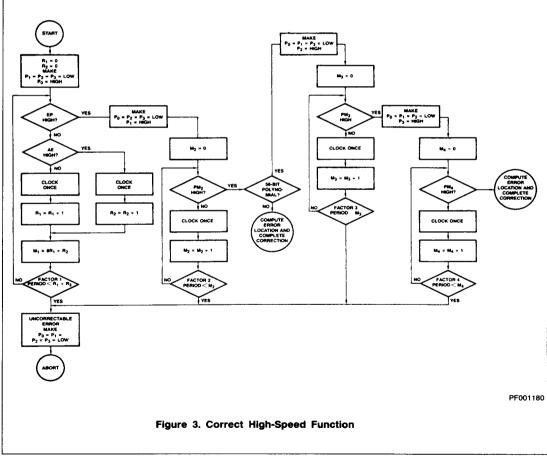

In Correct High Speed mode, the error location is also found by counting clock pulses, but they are routed in succession to the different sections of the Register Array. This results in slightly more complicated but substantially faster operation.

#### TABLE 1. POLYNOMIALS

| Polynominal                                                                                                                                       | Number of<br>Check Bits | Period<br>(Bits)           | Correctable<br>Burst Error<br>Length (Bits) |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------|---------------------------------------------|

| $(x^{22} + 1) \cdot (x^{11} + 7^7 + x^6 + x + 1) \cdot (x^{12} + x^{11} + x^{10} + \dots + x + 1) \cdot (x^{11} + x^9 + x^7 + x^6 + x^5 + x + 1)$ | 56                      | 585,442                    | 11                                          |

| $(X^{21} + 1) \cdot (X^{11} + X^2 + 1)$                                                                                                           | 32                      | 42,987                     | 11                                          |

| $(X^{23} + 1) \cdot (X^{12} + X^{11} + X^8 + X^7 + X^3 + X + 1)$                                                                                  | 35                      | 94,185                     | 12                                          |

| $(X^{13} + 1) \cdot (X^{35} + X^{23} + X^8 + X^2 + 1)$                                                                                            | 48                      | 13 · (2 <sup>35</sup> – 1) | 7                                           |

# **DETAILED DESCRIPTION**

#### Compute Check Bits

The check bits to be appended to the data are computed using this function. The  $S_0-S_1$  inputs select the desired polynomial. The Polynomial Matrix will be configured such that the generator polynomial is in the expanded form. The expanded form of a polynomial is obtained by multiplying out its factors and combining proper terms using modulo-2 arithmetic. Assume that the 32-bit polynomial is selected: the factored form of the 32-bit polynomial in Table 1 is  $(X^{21}+1)$   $(X^{11}+X^2+1)$ . The corresponding expanded form is  $X^{32}+X^{23}+X^{21}+X^{11}+X^2+1$ .

The sequence of events to compute the check bits is as follows:

- 1. The CP input is in guiescent HIGH state.

- Initialize by activating the MR input LOW and return it to HIGH.

- Through appropriate logic levels on the S<sub>0</sub>-S<sub>1</sub> inputs, specify the desired polynomial. Also, select

Compute Check Bits code through the C<sub>0</sub>-C<sub>2</sub> inputs.

- Establish a byte of data on the D<sub>0</sub>-D<sub>7</sub> inputs.

- Make CP input LOW and then HIGH. See timing diagram for detailed timing specifications.

- Keep repeating from step 4 until all data bytes are entered.

#### Write Check Bits

In Compute Check Bits mode, the polynomial matrix and the Register Array are mechanizing a feedback shift register configuration. However, when Write Check Bits Code is established on the  $C_0\!-\!C_2$  inputs, the feedback paths are disabled such that the Register Array will behave as a simple shift register. When the last data byte is entered in the Compute Check Bits mode, the Register Array holds the check bits. These check bits will be available on the  $Q_0\!-\!Q_7$  outputs, one byte at a time.

The sequence of events to obtain the check bits is as follows:

- 1. The CP is in quiescent HIGH state.

- Establish appropriate code on the S<sub>0</sub>-S<sub>1</sub> inputs. This

code must be the same as that used for Compute

Check Bits function.

- 3. Establish Write Check Bits code on the C<sub>0</sub>-C<sub>2</sub> inputs.

- After a propagation delay, the Q<sub>0</sub>-Q<sub>7</sub> outputs will contain the first check byte.

- Make CP input LOW and then HIGH. The next check byte will be available on the Q<sub>0</sub>-Q<sub>7</sub> outputs.

- Keep repeating from step 5 until all check bytes that correspond to the selected polynomial are read out.

#### **Read Normal**

Two methodologies are available for error correction with these devices: (a) Full period clock around (normal method) and (b) Chinese remainder theorem (high-speed method). The

Read Normal function must be used for reading data from the disk if the normal method is used for error correction. When Read Normal is selected, the Polynomial Matrix establishes the polynomial in the expanded form. In this mode, the input stream consisting of data and check bytes is divided by the selected polynomial to obtain the syndrome. If the resulting syndrome is not zero, an error is detected. The ER output indicates whether the syndrome is zero or not. HIGH on the ER output indicates non-zero syndrome.

The sequence of events for Read Normal\_is as follows:

- 1. The CP input is in quiescent HIGH state.

- Initialize the Am9520 by activating the MR input LOW and then return it to HIGH.

- Establish proper code on the S<sub>0</sub>-S<sub>1</sub> inputs. The

polynomial selected for the read operation must be

the same as the one originally used for generating

the check bits.

- 4. Establish Read Normal code on the Cn-C2 inputs.

- Present a byte of information read from the disk on the D<sub>0</sub>-D<sub>7</sub> inputs.

- 6. Make the CP input LOW and then HIGH.

- Keep repeating from step 5 until the last check byte read from the disk is processed.

- After entering last check byte, test the ER output. HIGH on this output is indicative of an error and LOW means no error detected.

# Read High Speed

This function must be used for reading data if the Chinese remainder theorem method is to be used for error correction. In general, the Chinese remainder method accomplishes error correction in fewer clock cycles than the normal method. This method of correction, however, is not available for the 48-bit polynomial due to the nature of the factors that make up this polynomial. As explained later, the reciprocal polynomial technique is used for error correction when the 48-bit polynomial is selected.

The only difference between Read Normal and Read-High Speed Modes is as follows: in the Read Normal, the input stream is divided by the expanded version of the polynomial; whereas, in the Read High-Speed Mode, the input stream is simultaneously divided by all factors of the polynomial. Thus, the high-speed mode results in as many syndromes as the number of factors of the polynomial. If all syndromes are zero after entering the last check byte, the ER output will be LOW, indicating error-free operation. If there was an error, the ER will be HIGH.

The sequence of events in this mode are as follows:

- 1. The CP input is in its guiescent HIGH state.

- Specify the polynomial on the S<sub>0</sub>-S<sub>1</sub> input. This

must obviously be the same polynomial that generated the check bits originally.

- Specify Read High-Speed function on the C<sub>0</sub>-C<sub>2</sub> inputs.

00617B

2-494

- Initialize by activating the MR input LOW and then return it to HIGH.

- 5. Present a byte read from the disk on the Do-D7 inputs.

- 6. Make the CP input LOW and then HIGH.

- Keep repeating from step 5 until all data and check bytes are entered.

- Test the ER output after entering the last check byte. HIGH on this output is indicative of an error, and LOW signifies no error.

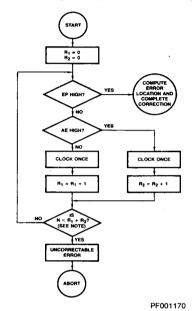

#### **Correct Normal**

The syndrome obtained from Read Normal operation is manipulated to extract the error pattern as well as its location using the Correct Normal function. Of the four polynomials listed in Table 1, the 48-bit version requires a separate explanation. For all cases except the 48-bit version, the polynomial is established in the expanded form.

In the Correct Normal, the syndrome is repeatedly divided by the polynomial until the error pattern is located. This division is accomplished by repeated clocking while ignoring the  $D_0\!-\!D_7$  inputs. HIGH on the EP output signifies that the error pattern is found. The error pattern is always characterized by a known number of consecutive zeros at specified Register Array locations. The exact number of zeros and their location is a function of the select polynomial. The status logic detects this unique combination to generate the EP output. The number of clock cycles needed to locate the error pattern is a measure of the error location. If the number of clock cycles has exceeded the natural period of the selected polynomial without finding the error pattern, then an uncorrectable error has occurred. The AE output must also be considered in the Correct Normal mode of operation.

The polynomial matrix is an 8-bit parallel mechanization of the familiar serial polynomial division scheme. Because of this, there are certain conditions under which the error pattern will not line up automatically. The Status Logic also monitors this condition. When such an alignment exception is detected, the AE output of the device goes HIGH.