**TLV2553**

SLAS354C - SEPTEMBER 2001 - REVISED SEPTEMBER 2015

# TLV2553 12-Bit, 200-KSPS, 11-Channel, Low-Power, Serial ADC

#### **Features**

- 12-Bit-Resolution A/D Converter

- Up to 200 KSPS (150 KSPS for 3 V) Throughput Over Operating Temperature Range With 12-Bit **Output Mode**

- 11 Analog Input Channels

- 3 Built-In Self-Test Modes

- Inherent Sample and Hold Function

- Linearity Error, ±1 LSB Maximum

- On-Chip Conversion Clock

- Unipolar or Bipolar Output Operation

- Programmable MSB or LSB First

- Programmable Power Down

- Programmable Output Data Length

- SPI Compatible Serial Interface With I/O Clock Frequencies up to 15 MHz (CPOL=0, CPHA=0)

# **Applications**

- Process Control

- Portable Data Logging

- **Battery-Powered Instruments**

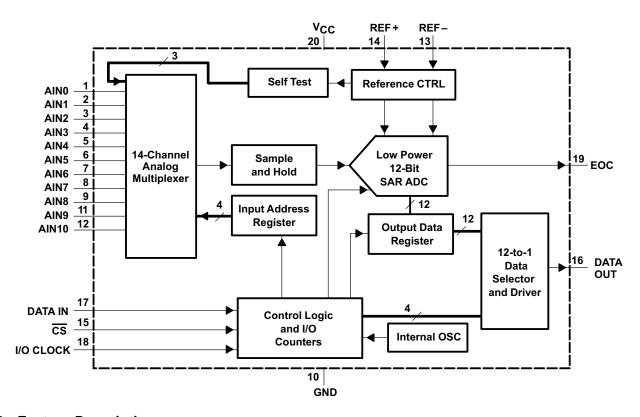

# 3 Description

The TLV2553 is a 12-bit, switched-capacitor, successive-approximation, analog-to-digital converter. The ADC has three control inputs [chip select (CS), the input-output clock, and the address/control input (DATAIN)], designed for communication with the serial port of a host processor or peripheral through a serial 3-state output.

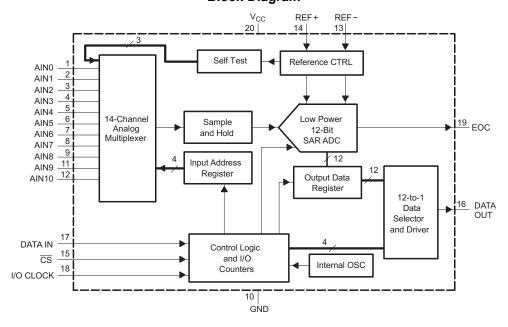

In addition to the high-speed converter and versatile control capability, the device has an on-chip 14channel multiplexer that can select any one of 11 inputs or any one of three internal self-test voltages using configuration register 1. The sample-and-hold function is automatic. At the end of conversion, when programmed as EOC, the pin 19 output goes high to indicate that conversion is complete. The converter incorporated in the device features differential, highimpedance reference inputs that facilitate ratiometric conversion, scaling, and isolation of analog circuitry from logic and supply noise. A switched-capacitor design allows low-error conversion over the full operating temperature range.

The TLV2553I is characterized for operation from  $T_A = -40$ °C to 85°C.

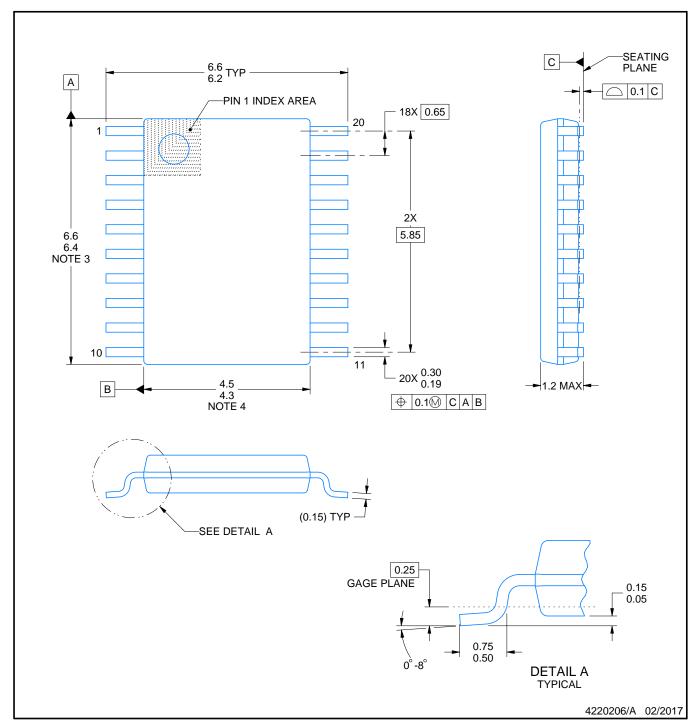

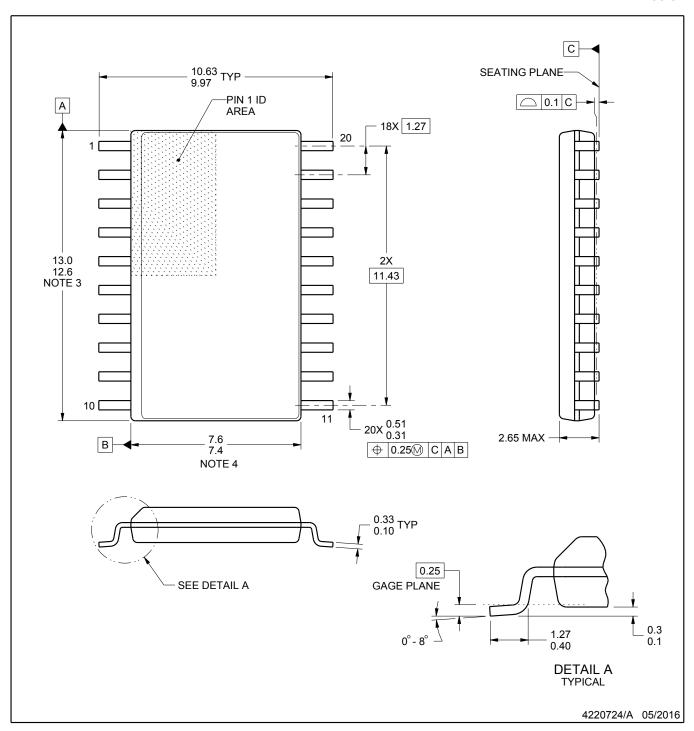

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)    |  |  |

|-------------|------------|--------------------|--|--|

| TLV2553IPW  | TSSOP (20) | 6.50 mm × 4.40 mm  |  |  |

| TLV2553IDW  | SOIC (20)  | 12.80 mm × 7.50 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### **Block Diagram**

# **Table of Contents**

| 1 | Features 1                                         |    | 8.1 Overview                                     | 20             |

|---|----------------------------------------------------|----|--------------------------------------------------|----------------|

| 2 | Applications 1                                     |    | 8.2 Functional Block Diagram                     | 20             |

| 3 | Description 1                                      |    | 8.3 Feature Description                          | 20             |

| 4 | Revision History2                                  |    | 8.4 Device Functional Modes                      | 2 <sup>,</sup> |

| 5 | Pin Configuration and Functions                    | 9  | Application and Implementation                   |                |

| 6 | Specifications4                                    |    | 9.1 Application Information                      |                |

| • | 6.1 Absolute Maximum Ratings 4                     |    | 9.2 Typical Application                          | 2              |

|   | 6.2 ESD Ratings                                    | 10 | Power Supply Recommendations                     | 29             |

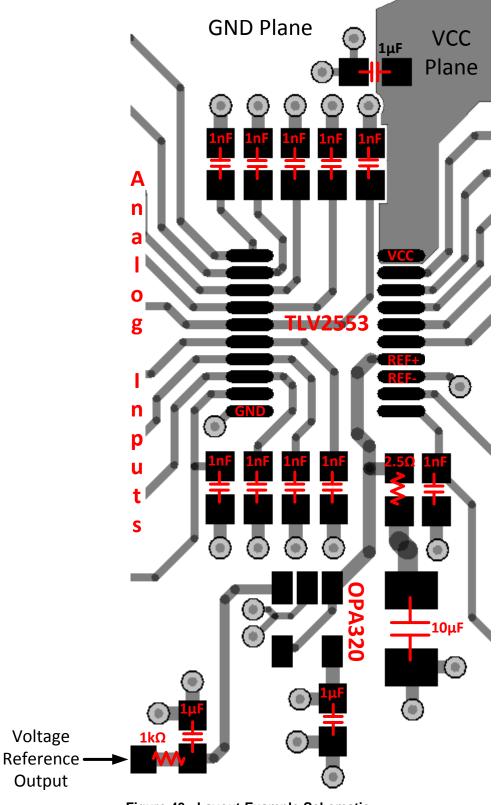

|   | 6.3 Recommended Operating Conditions               | 11 | Layout                                           | 29             |

|   | 6.4 Thermal Information5                           |    | 11.1 Layout Guidelines                           | 29             |

|   | 6.5 Electrical Characteristics                     |    | 11.2 Layout Example                              | 30             |

|   | 6.6 External Reference Specifications              | 12 | Device and Documentation Support                 | 3 <sup>-</sup> |

|   | 6.7 Operating Characteristics                      |    | 12.1 Community Resources                         | 3 <sup>.</sup> |

|   | 6.8 Timing Requirements: V <sub>REF+</sub> = 5 V   |    | 12.2 Trademarks                                  | 3 <sup>.</sup> |

|   | 6.9 Timing Requirements: V <sub>RFF+</sub> = 2.5 V |    | 12.3 Electrostatic Discharge Caution             | 3 <sup>.</sup> |

|   | 6.10 Typical Characteristics                       |    | 12.4 Glossary                                    | 3 <sup>.</sup> |

| 7 | Parameter Measurement Information 18               | 13 | Mechanical, Packaging, and Orderable Information | 3 <sup>.</sup> |

| 8 | Detailed Description 20                            |    |                                                  |                |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

# Changes from Revision B (September 2002) to Revision C

**Page**

| • | ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and | 4 |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|   | Mechanical, Packaging, and Orderable Information section                                                                                                                                                             |   |

|   | Deleted Lead temperature row from Absolute Maximum Ratings                                                                                                                                                           |   |

# 5 Pin Configuration and Functions

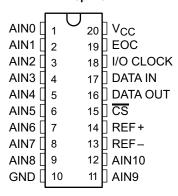

DW or PW Package 20-Pin SOIC or TSSOP Top View

### **Pin Functions**

| PIN             |                | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO.            | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AIN0 to AIN10   | 1 to 9, 11, 12 | 1   | Analog input. These 11 analog-signal inputs are internally multiplexed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <del>CS</del>   | 15             | I   | Chip select. A high-to-low transition on $\overline{\text{CS}}$ resets the internal counters and controls and enables DATA OUT, DATA IN, and I/O CLOCK. A low-to-high transition disables DATA IN and I/O CLOCK within a setup time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

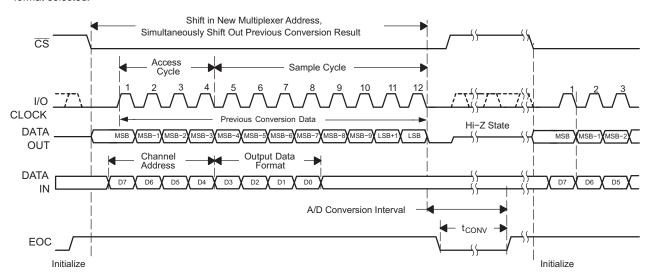

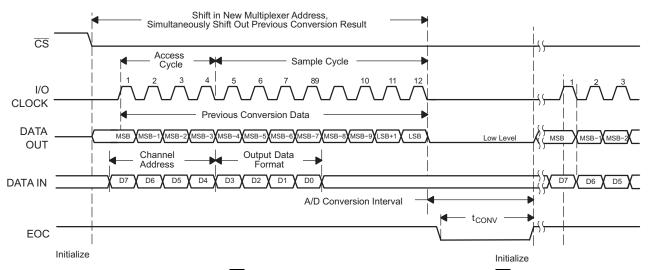

| DATA IN         | 17             | I   | Serial data input. The 4-bit serial data can be used as address selects the desired analog input channel or test voltage to be converted next, or a command to activate other features. The input data is presented with the MSB (D7) first and is shifted in on the first four rising edges of the I/O CLOCK. After the four address/command bits are read into the command register CMR, I/O CLOCK clocks the remaining four bits of configuration in.                                                                                                                                                                                                                                                                                                                                                       |

| DATA OUT        | 16             | 0   | 3-state serial output for the A/D conversion result. DATA OUT is in the high-impedance state when $\overline{CS}$ is high and active when $\overline{CS}$ is low. With a valid $\overline{CS}$ , DATA OUT is removed from the high-impedance state and is driven to the logic level corresponding to the MSB/LSB value of the previous conversion result. The next falling edge of I/O CLOCK drives DATA OUT to the logic level corresponding to the next MSB/LSB, and the remaining bits are shifted out in order.                                                                                                                                                                                                                                                                                            |

| EOC             | 19             | 0   | End-of-convertions status. Used to indicate the end of conversion (EOC) to the host processor. EOC goes from a high to a low logic level after the falling edge of the last I/O CLOCK and remains low until the conversion is complete and the data is ready for transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| GND             | 10             | _   | Ground. GND is the ground return terminal for the internal circuitry. Unless otherwise noted, all voltage measurements are with respect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

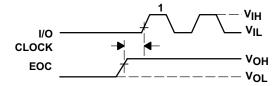

| I/O CLOCK       | 18             | I   | <ol> <li>Input /output clock. I/O CLOCK receives the serial input and performs the following four functions:</li> <li>It clocks the eight input data bits into the input data register on the first eight rising edges of I/O CLOCK with the multiplexer address available after the fourth rising edge.</li> <li>On the fourth falling edge of I/O CLOCK, the analog input voltage on the selected multiplexer input begins charging the capacitor array and continues to do so until the last falling edge of I/O CLOCK.</li> <li>The remaining 11 bits of the previous conversion data are shifted out on DATA OUT. Data changes on the falling edge of I/O CLOCK.</li> <li>Control of the conversion is transferred to the internal state controller on the falling edge of the last I/O CLOCK.</li> </ol> |

| REF+            | 14             | I/O | Positive reference voltage The upper reference voltage value (nominally $V_{CC}$ ) is applied to REF+. The maximum analog input voltage range is determined by the difference between the voltage applied to terminals REF+ and REF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| REF-            | 13             | I/O | Negative reference voltage. The lower reference voltage value (nominally ground) is applied to REF–. This pin is connected to analog ground (GND of the ADC) when internal reference is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>CC</sub> | 20             | _   | Positive supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                                        | MIN  | MAX            | UNIT  |

|------------------|----------------------------------------|------|----------------|-------|

| V <sub>CC</sub>  | Supply voltage <sup>(2)</sup>          | -0.5 | 6.5            |       |

| $V_{I}$          | Input voltage (any input)              | -0.3 | $V_{CC} + 0.3$ |       |

| Vo               | Output voltage                         | -0.3 | $V_{CC} + 0.3$ | V     |

| $V_{ref+}$       | Positive reference voltage             | -0.3 | $V_{CC} + 0.3$ |       |

| $V_{ref-}$       | Negative reference voltage             | -0.3 | $V_{CC} + 0.3$ |       |

| I                | Peak input current (any input)         | -20  | 20             | A     |

|                  | Peak total input current (all inputs)  | -30  | 30             | mA mA |

| $T_{J}$          | Operating virtual junction temperature | -40  | 150            |       |

| T <sub>A</sub>   | Operating free-air temperature         | -40  | 85             | °C    |

| T <sub>stg</sub> | Storage temperature                    | -65  | 150            |       |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                          |                                                                     | VALUE | UNIT |

|--------------------|--------------------------|---------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge  | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discriarge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> All voltage values are with respect to the GND terminal with REF- and GND wired together (unless otherwise noted).

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                                           |                                            |                                  | MIN  | NOM | MAX               | UNIT   |

|-----------------|-------------------------------------------|--------------------------------------------|----------------------------------|------|-----|-------------------|--------|

| V <sub>CC</sub> | Supply voltage                            |                                            | 2.7                              |      | 5.5 | V                 |        |

|                 |                                           |                                            | 16-bit I/O                       | 0.01 |     | 15                |        |

|                 | I/O CLOCK frequency                       | $V_{CC} = 4.5 \text{ V to } 5.5 \text{ V}$ | 12-bit I/O                       | 0.01 |     | 15                | NAL I— |

|                 |                                           |                                            | 8-bit I/O                        | 0.01 |     | 15                | MHz    |

|                 |                                           | $V_{CC} = 2.7 \text{ V to } 3.6 \text{ V}$ |                                  | 0.01 |     | 10                |        |

| I/O<br>CLOCK    | Tolerable clock jitter                    | V <sub>CC</sub> = 4.5 V to 5.5 V           |                                  |      |     | 0.38              | ns     |

|                 | Aperature jitter                          | V <sub>CC</sub> = 4.5 V to 5.5 V           |                                  |      | 100 |                   | ps     |

|                 |                                           | V <sub>CC</sub> = 4.5 V to 5.5 V           |                                  | 0    |     | (REF+ ) – (REF– ) |        |

|                 | Analog input voltage <sup>(1)</sup>       | V <sub>CC</sub> = 3 V to 3.6 V             |                                  | 0    |     | (REF+ ) – (REF– ) | V      |

|                 |                                           | V <sub>CC</sub> = 2.7 V to 3 V             |                                  | 0    |     | (REF+ ) – (REF– ) |        |

| M               | High level control inner which            | V <sub>CC</sub> = 4.5 V to 5.5 V           |                                  | 2    |     |                   | V      |

| $V_{IH}$        | High-level control input voltage          | $V_{CC} = 2.7 \text{ V to } 3.6 \text{ V}$ | V <sub>CC</sub> = 2.7 V to 3.6 V |      |     |                   | V      |

| M               | Law law I agetral in a structural to a se | V <sub>CC</sub> = 4.5 V to 5.5 V           |                                  |      |     | 0.8               | \ /    |

| $V_{IL}$        | Low-level control input voltage           | V <sub>CC</sub> = 2.7 V to 3.6 V           |                                  |      |     | 0.6               | V      |

| T <sub>A</sub>  | Operating free-air temperature            | TLV2553I                                   |                                  | -40  |     | 85                | °C     |

<sup>(1)</sup> Analog input voltages greater than the voltage applied to REF+ convert as all ones (11111111111), while input voltages less than the voltage applied to REF- convert as all zeros (000000000000).

### 6.4 Thermal Information

|                        |                                              | TLV       |            |      |

|------------------------|----------------------------------------------|-----------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | DW (SOIC) | PW (TSSOP) | UNIT |

|                        |                                              | 20 PINS   | 20 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 66        | 88.1       | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 31.4      | 21.6       | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 33.7      | 40.4       | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 7.4       | 0.8        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 33.3      | 39.7       | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# 6.5 Electrical Characteristics

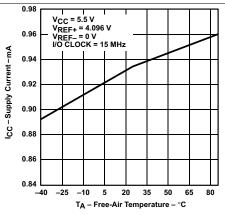

over recommended operating free-air temperature range, when  $V_{CC}$  = 5 V:  $V_{REF+}$  = 5 V, I/O CLOCK frequency = 15 MHz, when  $V_{CC}$  = 2.7 V:  $V_{REF+}$  = 2.5 V, I/O CLOCK frequency = 10 MHz (unless otherwise noted)

|                                                | PARAMETER                  |                                            | TEST C                                                                                                           | CONDITIONS                           |       | MIN                   | TYP <sup>(1)</sup> | MAX     | UNIT     |

|------------------------------------------------|----------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------|-----------------------|--------------------|---------|----------|

| V                                              | High-level output voltage  | 10                                         | $V_{CC} = 4.5 \text{ V}, I_{OH} = -6 \text{ V}_{CC} = 2.7 \text{ V}, I_{OH} = -6 \text{ V}_{CC} = 2.7 \text{ V}$ |                                      | 30 pF | 2.4                   |                    |         | V        |

| V <sub>OH</sub>                                | nign-ievei output voitag   | ge                                         | $V_{CC} = 4.5 \text{ V}, I_{OH} = -2.0 \text{ V}$<br>$V_{CC} = 2.7 \text{ V}, I_{OH} = -2.0 \text{ V}$           |                                      | 30 pr | V <sub>CC</sub> – 0.1 |                    |         | ٧        |

| $V_{OL}$                                       | Low-level output voltag    | ٥                                          | $V_{CC} = 4.5 \text{ V}, I_{OL} = -1 \text{ V}_{CC} = 2.7 \text{ V}, I_{OL} = -0 \text{ V}_{CC} = 2.7 \text{ V}$ |                                      | 30 pF |                       |                    | 0.4     | V        |

| VOL                                            | Low level output voltag    |                                            | $V_{CC} = 4.5 \text{ V}, I_{OL} = -2.0 \text{ V}$<br>$V_{CC} = 2.7 \text{ V}, I_{OL} = -2.0 \text{ V}$           |                                      | 30 pi |                       |                    | 0.1     | <b>V</b> |

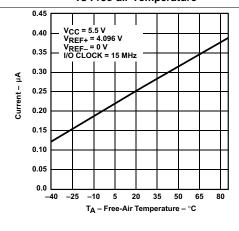

| 1                                              | High-impedance off-sta     | te output current                          | $V_O = V_{CC}, \overline{CS} = V_{CC}$                                                                           |                                      |       |                       | 1                  | 2.5     | μA       |

| I <sub>OZ</sub>                                | riigii-iiripedance oii-sta | ile output current                         | $V_O = 0 V, \overline{CS} = V_{CC}$                                                                              |                                      |       |                       | -1                 | -2.5    | μΛ       |

|                                                | Operating aupply aurre     | n+                                         | $\overline{\text{CS}} = 0 \text{ V},$                                                                            | $V_{CC} = 5 V$                       |       |                       |                    | 1.2     | mA       |

| I <sub>CC</sub>                                | Operating supply curre     | iii.                                       | External reference                                                                                               | $V_{CC} = 2.7 \text{ V}$             |       |                       |                    | 0.9     | ША       |

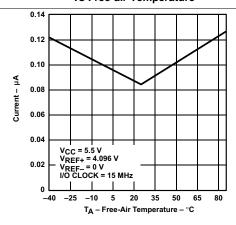

|                                                |                            |                                            | For all digital inputs,                                                                                          | Software power down  Auto power down |       |                       | 0.1                | 1       |          |

| I <sub>CC(PD)</sub>                            | Power-down current         |                                            | $0 \le V_1 \le 0.5 \text{ V or}$<br>$V_1 \ge V_{CC} - 0.5 \text{ V},$<br>I/O CLOCK = 0 V                         |                                      |       |                       | 0.1                | 10      | μΑ       |

| I <sub>IH</sub>                                | High-level input current   |                                            | $V_I = V_{CC}$                                                                                                   |                                      |       |                       | 0.005              | 2.5     | μΑ       |

| I <sub>IL</sub>                                | Low-level input current    |                                            | $V_I = 0 V$                                                                                                      |                                      |       |                       | -0.005             | -2.5    | μΑ       |

| L.                                             | Selected channel leaka     | ao current                                 | Selected channel at V <sub>CC</sub> ,<br>Unselected channel at 0 V                                               |                                      |       |                       | 1                  | μA      |          |

| I <sub>lkg</sub>                               | Selected Charmer leaka     | ige current                                | Selected channel at 0 V,<br>Unselected channel at V <sub>CC</sub>                                                |                                      |       |                       | -1                 | μΑ      |          |

| f                                              | Internal oscillator freque | onov                                       | V <sub>CC</sub> = 4.5 V to 5.5 V                                                                                 |                                      |       | 3.27                  |                    |         | MHz      |

| fosc                                           | internal oscillator frequi | епсу                                       | V <sub>CC</sub> = 2.7 V to 3.6 V                                                                                 |                                      | 2.56  |                       |                    | IVII IZ |          |

|                                                | Conversion time            |                                            | $V_{CC} = 4.5 \text{ V to } 5.5 \text{ V}$                                                                       |                                      |       |                       |                    | 4.15    |          |

| $t_{convert}$ (13.5 × (1/ $f_{OSC}$ ) + 25 ns) |                            | $V_{CC} = 2.7 \text{ V to } 3.6 \text{ V}$ |                                                                                                                  |                                      |       |                       | 5.54               | μs      |          |

|                                                | Internal oscillator freque | ency voltage                               |                                                                                                                  |                                      |       | 3.6                   |                    | 4.1     | V        |

| 7                                              | Input impedance (2)        | Analog inputs                              | V <sub>CC</sub> = 4.5 V                                                                                          |                                      |       |                       |                    | 500     | Ω        |

| Z <sub>i</sub>                                 | Input impedance (2)        | Analog inputs                              | V <sub>CC</sub> = 2.7 V                                                                                          |                                      |       |                       |                    | 600     | 77       |

|                                                | Innut conscitones          | Analog inputs                              |                                                                                                                  |                                      |       |                       | 45                 | 55      | nE       |

| C <sub>i</sub>                                 | Input capacitance          | Control inputs                             |                                                                                                                  |                                      |       |                       | 5                  | 15      | pF       |

All typical values are at  $V_{CC}$  = 5 V,  $T_A$  = 25°C. The switch resistance is very nonlinear and varies with input voltage and supply voltage. This is the worst case.

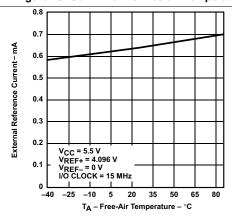

# 6.6 External Reference Specifications

|                          | PARAMETER                                    | TE                          | ST CONDITIONS                              | MIN  | TYP <sup>(1)</sup> | MAX             | UNIT |

|--------------------------|----------------------------------------------|-----------------------------|--------------------------------------------|------|--------------------|-----------------|------|

| DEE Defended in the land |                                              | $V_{CC} = 4.5 \text{ V to}$ | 5.5 V                                      | -0.1 | 0                  | 0.1             | V    |

| REF-                     | Reference input voltage                      | $V_{CC} = 2.7 \text{ V to}$ | 3.6 V                                      | -0.1 | 0                  | 0.1             | V    |

| DEE.                     | Deference input voltage                      | $V_{CC} = 4.5 \text{ V to}$ | 5.5 V                                      | 2    |                    | V <sub>CC</sub> | V    |

| REF+                     | Reference input voltage                      | V <sub>CC</sub> = 2.7 V to  | 3.6 V                                      | 2    |                    | V <sub>CC</sub> | V    |

|                          | External reference input voltage difference, | $V_{CC} = 4.5 \text{ V to}$ | 5.5 V                                      | 1.9  |                    | V <sub>CC</sub> | V    |

|                          | $(REF+) - (REF-)^{(2)}$                      | $V_{CC} = 2.7 \text{ V to}$ | 3.6 V                                      | 1.9  |                    | $V_{CC}$        | V    |

|                          | Estamal reference comply consent             | CS at 0 V                   | $V_{CC} = 4.5 \text{ V to } 5.5 \text{ V}$ |      |                    | 0.94            | A    |

|                          | External reference supply current            | CS at 0 v                   | V <sub>CC</sub> = 2.7 V to 3.6 V           |      |                    | 0.62            | mA   |

|                          |                                              |                             | Static                                     | 1    |                    |                 | ΜΩ   |

|                          |                                              | V <sub>CC</sub> = 5 V       | During sampling/conversion                 | 6    |                    | 9               | kΩ   |

|                          | Reference input impedance                    |                             | Static                                     | 1    |                    |                 | ΜΩ   |

|                          |                                              | V <sub>CC</sub> = 2.7 V     | During sampling/conversion                 | 6    |                    | 9               | kΩ   |

All typical values are at T<sub>A</sub> = 25°C.

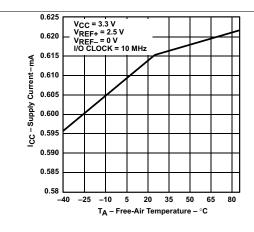

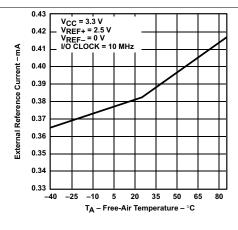

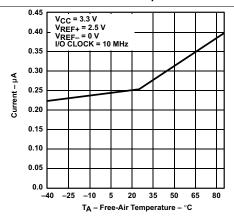

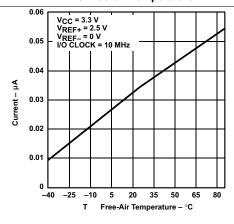

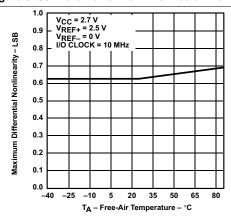

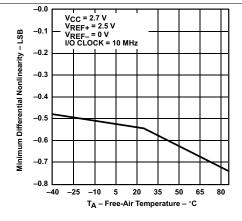

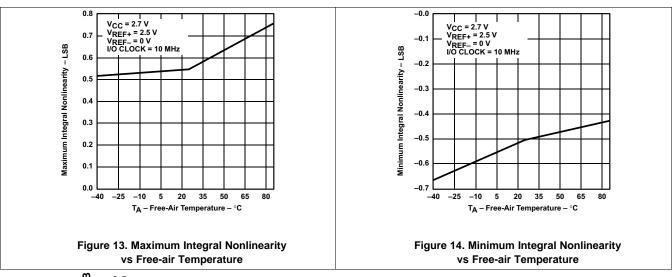

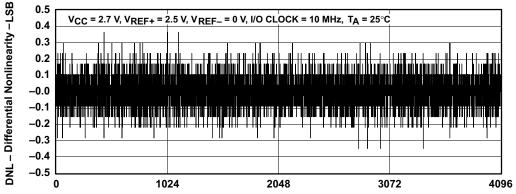

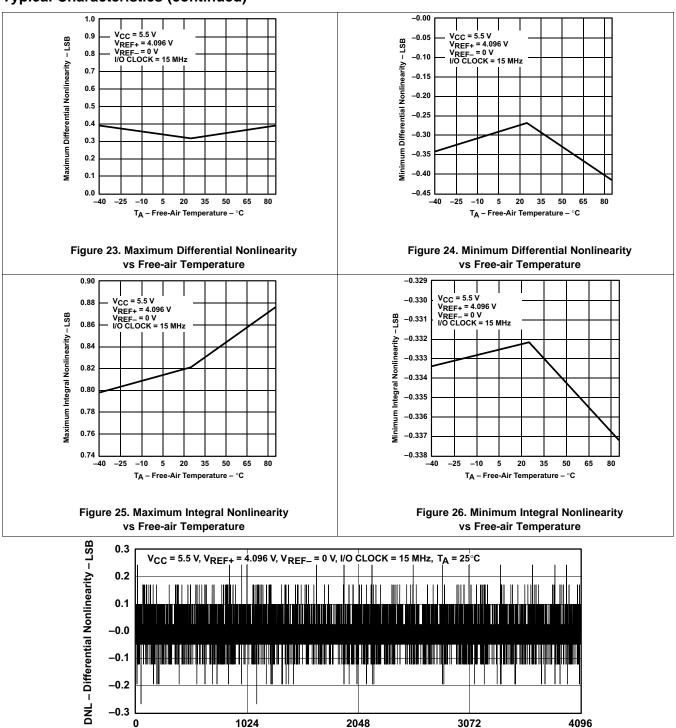

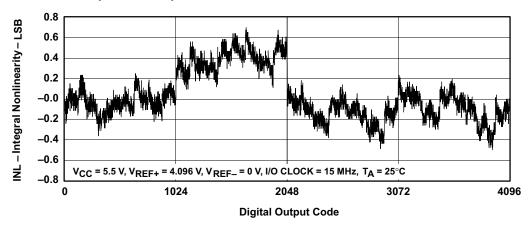

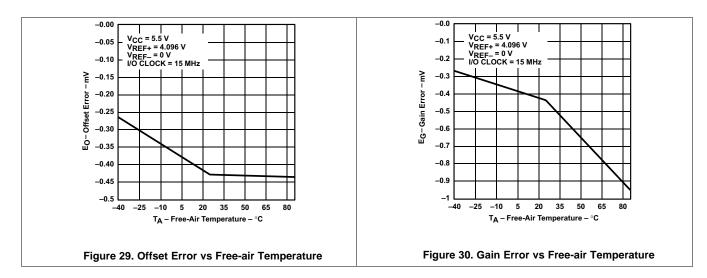

### 6.7 Operating Characteristics

over recommended operating free-air temperature range,  $V_{REF+} = 5 \text{ V}$ , I/O CLOCK frequency = 15 MHz when  $V_{CC} = 5 \text{ V}$ , I/O CLOCK frequency = 10 MHz when  $V_{CC} = 2.7 \text{ V}$  (unless otherwise noted)

|                | PARAMETER                               | TEST CONDITIONS           | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|----------------|-----------------------------------------|---------------------------|-----|--------------------|-----|------|

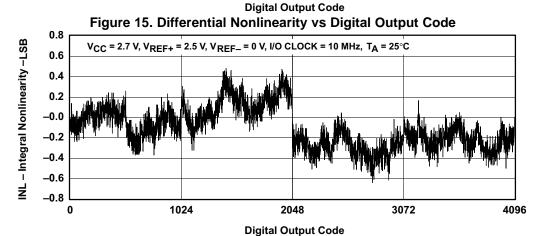

| INL            | Integral linearity error <sup>(2)</sup> |                           | -1  |                    | 1   | LSB  |

| DNL            | Differential linearity error            |                           | -1  |                    | 1   | LSB  |

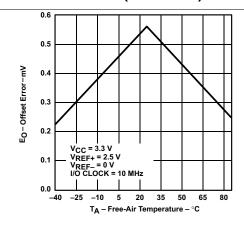

| Eo             | Offset error <sup>(3)</sup>             | See (4)                   | -2  |                    | 2   | mV   |

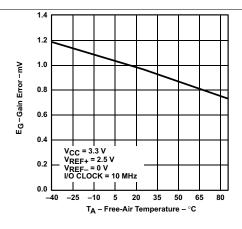

| EQ             | Gain error <sup>(3)</sup>               | See <sup>(4)</sup>        | -3  |                    | 3   | mV   |

| E <sub>T</sub> | Total unadjusted error <sup>(5)</sup>   |                           |     | ±15                |     | LSB  |

|                |                                         | Address data input = 1011 |     | 2048               |     |      |

|                | Self-test output code Table 2, (6)      | Address data input = 1100 |     | 0                  |     |      |

|                |                                         | Address data input = 1101 |     | 4095               |     |      |

<sup>(1)</sup> All typical values are at T<sub>A</sub> = 25°C.

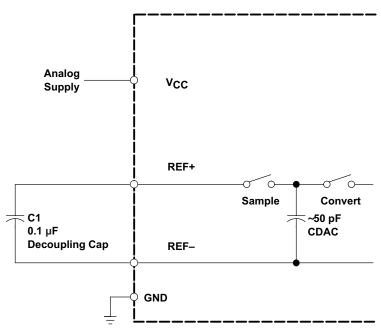

<sup>(2)</sup> Add a 0.1-µF capacitor between REF+ and REF- pins when external reference is used.

<sup>2)</sup> Linearity error is the maximum deviation from the best straight line through the A/D transfer characteristics.

<sup>(3)</sup> Gain error is the difference between the actual midstep value and the nominal midstep value in the transfer diagram at the specified gain point after the offset error has been adjusted to zero. Offset error is the difference between the actual midstep value and the nominal midstep value at the offset point.

<sup>(4)</sup> Analog input voltages greater than the voltage applied to REF+ convert as all ones (111111111111), while input voltages less than the voltage applied to REF- convert as all zeros (000000000000).

<sup>(5)</sup> Total unadjusted error comprises linearity, zero-scale, and full-scale errors.

<sup>(6)</sup> Both the input address and the output codes are expressed in positive logic.

# 6.8 Timing Requirements: V<sub>REF+</sub> = 5 V

over recommended operating free-air temperature range, I/O CLOCK frequency = 15 MHz,  $V_{CC}$  = 5 V, load = 25 pF (unless otherwise noted)

|                     |                                                                                         |                                     | MIN  | TYP MAX                                                      | UNIT |  |

|---------------------|-----------------------------------------------------------------------------------------|-------------------------------------|------|--------------------------------------------------------------|------|--|

| t <sub>w1</sub>     | Pulse duration I/O CLOCK high or low                                                    |                                     | 26.7 | 100000                                                       | ns   |  |

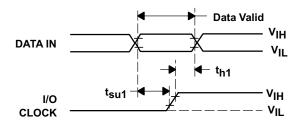

| t <sub>su1</sub>    | Setup time DATA IN valid before I/O CLOCK risin                                         | ng edge (see Figure 32)             | 12   |                                                              | ns   |  |

| t <sub>h1</sub>     | Hold time DATA IN valid after I/O CLOCK rising e                                        | edge (see Figure 32)                | 0    |                                                              | ns   |  |

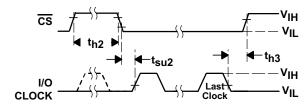

| t <sub>su2</sub>    | Setup time CS low before first rising I/O CLOCK                                         | edge <sup>(1)</sup> (see Figure 33) | 25   |                                                              | ns   |  |

| t <sub>h2</sub>     | Hold time CS pulse duration high time (see Figure                                       | e 33)                               | 100  |                                                              | ns   |  |

| t <sub>h3</sub>     | Hold time CS low after last I/O CLOCK falling edg                                       | ge (see Figure 33)                  | 0    |                                                              | ns   |  |

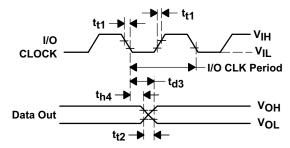

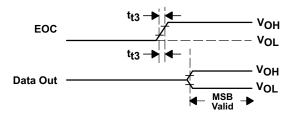

| t <sub>h4</sub>     | Hold time DATA OUT valid after I/O CLOCK fallin                                         | g edge (see Figure 34)              | 2    |                                                              | ns   |  |

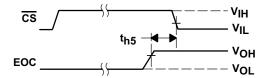

| t <sub>h5</sub>     | Hold time $\overline{\text{CS}}$ high after EOC rising edge when $\overline{\text{CS}}$ | S is toggled (see Figure 37)        | 0    |                                                              | ns   |  |

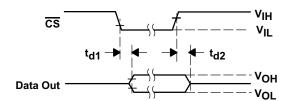

|                     | Delay time CS falling edge to DATA OUT valid                                            | Load = 25 pF                        |      | 28                                                           | ns   |  |

| t <sub>d1</sub>     | (MSB or LSB) (see Figure 31)                                                            | Load = 10 pF                        |      | 20                                                           | ns   |  |

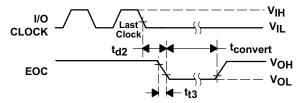

| t <sub>d2</sub>     | Delay time CS rising edge to DATA OUT high imp                                          | pedance (see Figure 31)             |      | 10                                                           | ns   |  |

| t <sub>d3</sub>     | Delay time I/O CLOCK falling edge to next DATA                                          | OUT bit valid (see Figure 34)       | 2    | 20                                                           | ns   |  |

| t <sub>d4</sub>     | Delay time Last I/O CLOCK falling edge to EOC f                                         | alling edge                         |      | 55                                                           | ns   |  |

| t <sub>d5</sub>     | Delay time last I/O CLOCK falling edge to CS falli                                      | ing edge to abort conversion        |      | 1.5                                                          | μs   |  |

| t <sub>t1</sub>     | Transition time I/O CLOCK (1)(see Figure 34)                                            |                                     |      | 1                                                            | μs   |  |

| t <sub>t2</sub>     | Transition time DATA OUT (see Figure 34)                                                |                                     |      | 5                                                            | ns   |  |

| t <sub>t3</sub>     | Transition time INT/EOC, C <sub>L</sub> at 7 pF (see Figure 3                           | 36)                                 |      | 2.4                                                          | ns   |  |

| t <sub>t4</sub>     | Transition time DATA IN, CS                                                             |                                     |      | 10                                                           | μs   |  |

| t <sub>cycle</sub>  | Total cycle time (sample, conversion and delays) <sup>(1)</sup>                         |                                     |      | MAX(t <sub>convert</sub> ) +<br>I/O period<br>(8/12/16 CLKs) | μs   |  |

|                     |                                                                                         | Source impedance = 25 $\Omega$      | 600  |                                                              |      |  |

|                     | Channel acquisition time (sample), at 1 k $\Omega$ , (1)                                | Source impedance = 100 Ω            | 650  |                                                              |      |  |

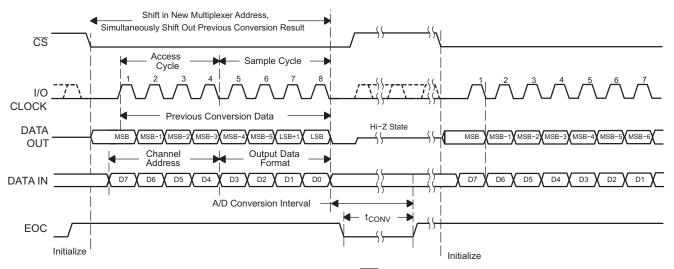

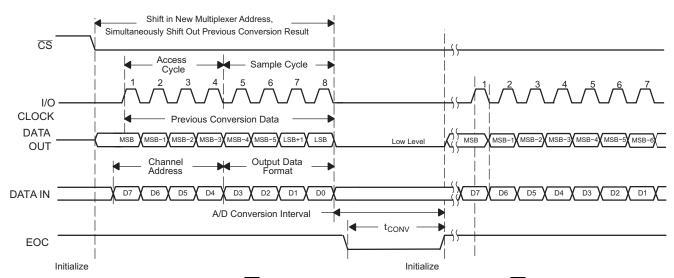

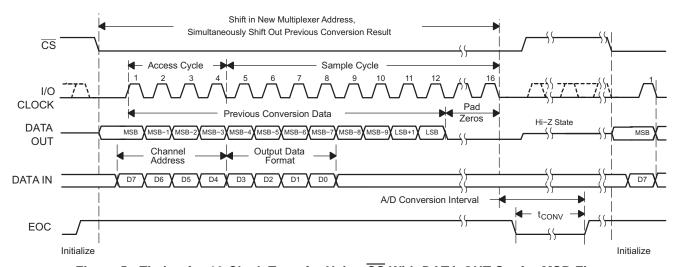

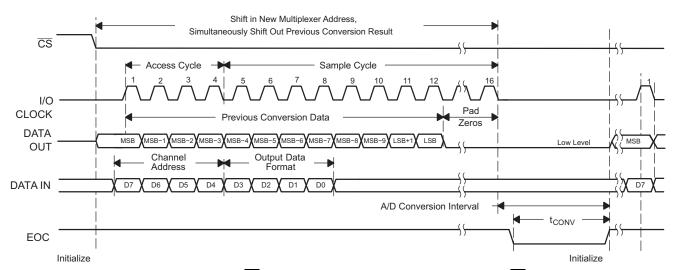

| t <sub>sample</sub> | (See Figure 1 through Figure 6)                                                         | Source impedance = $500 \Omega$     | 700  |                                                              | ns   |  |

|                     |                                                                                         | Source impedance = 1 kΩ             | 1000 |                                                              |      |  |

|                     |                                                                                         |                                     |      |                                                              |      |  |

<sup>(1)</sup> I/O CLOCK period = 8X [1/(I/O CLOCK frequency)] or 12X [1/(I/O CLOCK frequency)] or 16X [1/(I/O CLOCK frequency)] depends on I/O format selected.

# 6.9 Timing Requirements: $V_{REF+} = 2.5 \text{ V}$

over recommended operating free-air temperature range, I/O CLOCK frequency = 10 MHz,  $V_{CC}$  = 2.7 V, load = 25 pF (unless otherwise noted)

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                      | MIN  | TYP MAX                                                      | UNIT                                                  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------|--------------------------------------------------------------|-------------------------------------------------------|--|

| t <sub>w1</sub>     | Pulse duration I/O CLOCK high or low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                      | 40   | 100000                                                       | ns                                                    |  |

| t <sub>su1</sub>    | Setup time DATA IN valid before I/O CLOCK ris                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ing edge (see Figure 32)             | 22   |                                                              | ns                                                    |  |

| t <sub>h1</sub>     | Hold time DATA IN valid after I/O CLOCK rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | edge (see Figure 32)                 | 0    |                                                              | ns                                                    |  |

| t <sub>su2</sub>    | Setup time CS low before first rising I/O CLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | cedge <sup>(1)</sup> (see Figure 33) | 33   |                                                              | ns                                                    |  |

| t <sub>h2</sub>     | Pulse duration I/O CLOCK high or low  detup time DATA IN valid before I/O CLOCK rising edge (see Figure 32)  delot time DATA IN valid after I/O CLOCK rising edge (see Figure 32)  delot time DATA IN valid after I/O CLOCK rising edge (see Figure 32)  delot time CS low before first rising I/O CLOCK edge <sup>(1)</sup> (see Figure 33)  delot time CS pulse duration high time (see Figure 33)  delot time CS low after last I/O CLOCK falling edge (see Figure 33)  delot time DATA OUT valid after I/O CLOCK falling edge (see Figure 33)  delot time DATA OUT valid after I/O CLOCK falling edge (see Figure 37)  delay time CS falling edge to DATA OUT valid  MSB or LSB) (see Figure 31)  delay time CS rising edge to DATA OUT high impedance (see Figure 34)  delay time I/O CLOCK falling edge to next DATA OUT bit valid (see Figure 34)  delay time Last I/O CLOCK falling edge to EOC falling edge  delay time Last I/O CLOCK falling edge to EOC falling edge  delay time last I/O CLOCK falling edge to EOC falling edge  delay time Last I/O CLOCK falling edge to EOC falling edge  delay time Last I/O CLOCK falling edge to EOC falling edge  delay time Last I/O CLOCK falling edge to EOC falling edge  delay time Last I/O CLOCK falling edge to EOC falling edge  delay time Last I/O CLOCK falling edge to EOC falling edge  delay time Last I/O CLOCK falling edge to EOC falling edge  delay time Last I/O CLOCK falling edge to EOC falling edge  delay time Last I/O CLOCK falling edge to EOC falling edge  delay time Last I/O CLOCK falling edge to EOC falling edge  delay time Last I/O CLOCK falling edge to EOC falling edge  delay time Last I/O CLOCK falling edge to EOC falling edge  delay time Last I/O CLOCK falling edge to EOC falling edge  delay time Last I/O CLOCK falling edge to EOC falling edge  delay time Last I/O CLOCK falling edge to EOC falling edge  delay time Last I/O CLOCK falling edge to EOC falling edge  delay time Last I/O CLOCK falling edge to EOC falling edge  delay time Last I/O CLOCK falling edge  delay time Last I/O CLOCK falling edge  delay time |                                      |      |                                                              | ns                                                    |  |

| t <sub>h3</sub>     | Hold time CS low after last I/O CLOCK falling ed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | dge (see Figure 33)                  | 0    |                                                              | ns                                                    |  |

| t <sub>h4</sub>     | Hold time DATA OUT valid after I/O CLOCK fall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ing edge (see Figure 33)             | 2    |                                                              | ns                                                    |  |

| t <sub>h5</sub>     | Hold time CS high after EOC rising edge when 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CS is toggled (see Figure 37)        | 0    |                                                              | ns                                                    |  |

|                     | Delay time CS falling edge to DATA OUT valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Load = 25 pF                         |      | 30                                                           | ns                                                    |  |

| t <sub>d1</sub>     | (MSB or LSB) (see Figure 31)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Load = 10 pF                         |      | 22                                                           | ns                                                    |  |

| t <sub>d2</sub>     | Delay time CS rising edge to DATA OUT high in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | npedance (see Figure 31)             |      | 10                                                           | ns                                                    |  |

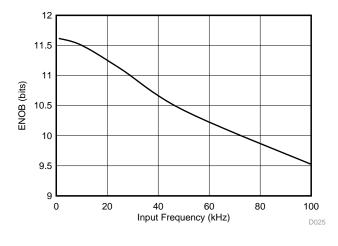

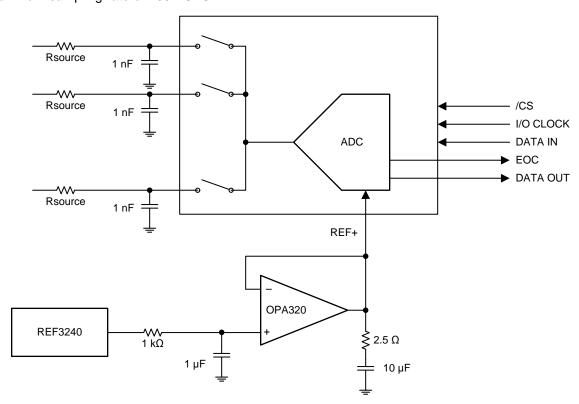

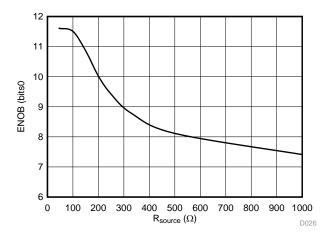

| t <sub>d3</sub>     | elay time I/O CLOCK falling edge to next DATA OUT bit valid (see Figure 34)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                      |      |                                                              | ns                                                    |  |