# MAX98096

## Audio Hub with Wideband FlexSound Processor

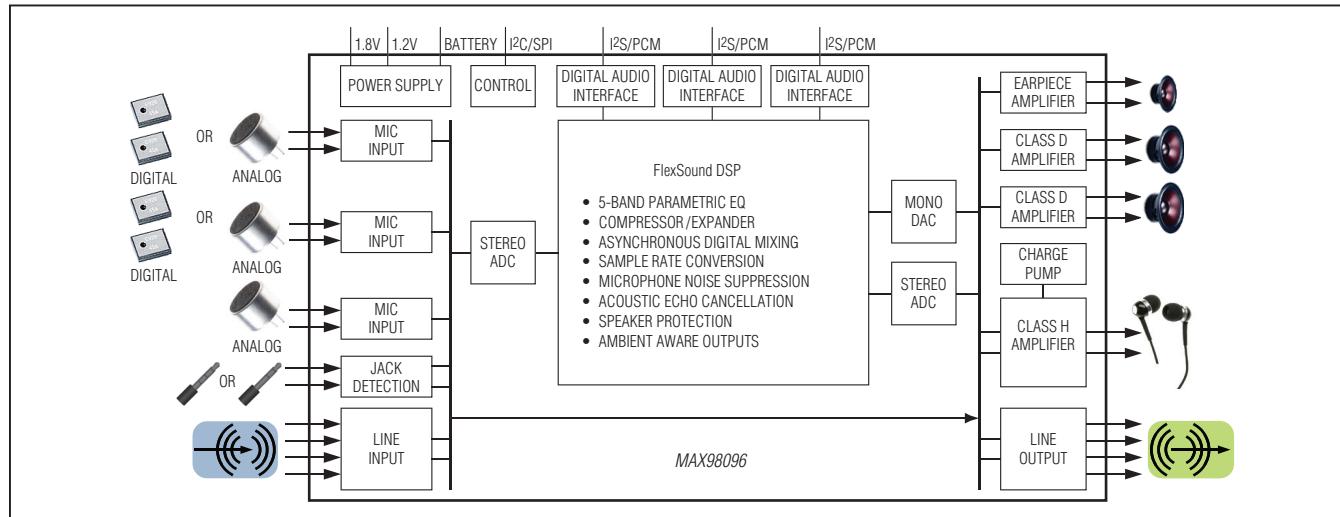

### General Description

The MAX98096 is a full-featured high performance audio hub with low power consumption and advanced signal processing, making it ideal for a wide range of portable applications.

Three differential analog microphone inputs and four 1-bit digital microphone inputs accept audio from main, accessory, and background microphones. Analog line inputs accept four single-ended or two differential audio signals.

Three digital audio interfaces supports standard PCM formats such as I<sup>2</sup>S, left justified, and TDM. Three integrated sample rate converters and highly configurable signal routing enable a wide range of use cases. The FlexSound™ audio processor provides low-power advanced signal processing, including equalization, dynamic range compression, speaker protection, microphone noise suppression during wideband calls, acoustic echo cancellation, and ambient aware outputs.

Integrated amplifiers can output signals from three DACs or any of the analog inputs. Amplifiers include a differential receiver amplifier, a stereo Class D speaker amplifier, a stereo Class H headphone amplifier, and four single-ended line outputs.

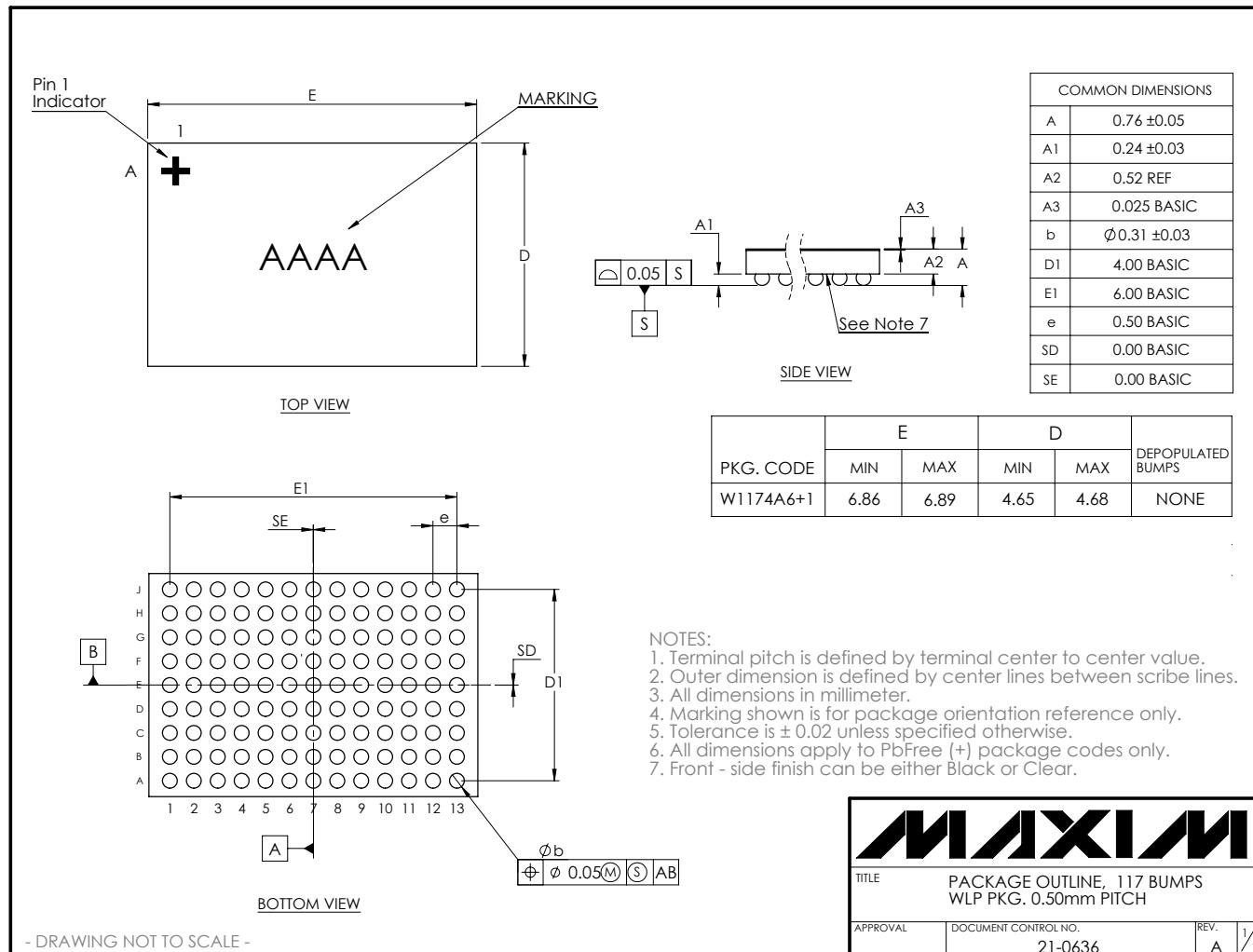

The 117-bump WLP (6.9mm x 4.7mm x 0.5mm pitch) package is fully specified over the -40°C to +85°C extended temperature range.

FlexSound is a trademark and DirectDrive is a registered trademark of Maxim Integrated Products, Inc.

### Benefits and Features

- ◆ 101dB DR Stereo DAC (8kHz < f<sub>S</sub> < 96kHz)

- ◆ 90dB DR Stereo ADC (8kHz < f<sub>S</sub> < 96kHz)

- ◆ 5.9mW Playback Power Consumption

- ◆ 40kB Local Data RAM, 56kB Local Instruction ROM

- ◆ 3 Stereo Single-Ended/Differential Analog Microphone Inputs (or 1 Analog/2 Stereo PDM Digital Microphone Inputs)

- ◆ 2 Stereo Single-Ended/Mono Differential Line Inputs

- ◆ Three I<sup>2</sup>S/PCM/TDM Digital Audio Interfaces

- ◆ FlexSound Technology Signal Processing

- ◆ Enhanced Speakerphone

- ◆ Single/Dual Microphone Wideband Noise Suppression (16kHz Sampling Rate)

- ◆ Ambient Aware Receiver Output

- ◆ Acoustic Echo Cancellation

- ◆ Stereo Low EMI Class D Amplifiers

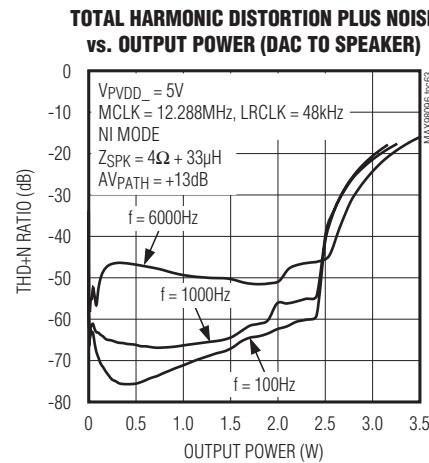

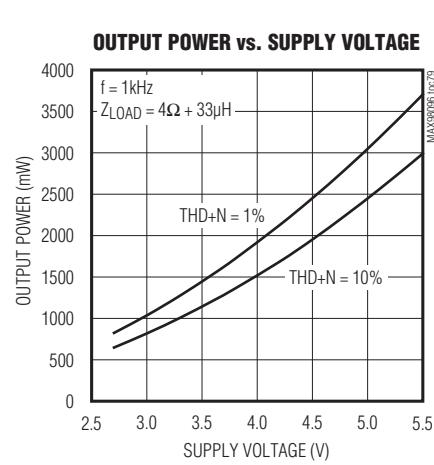

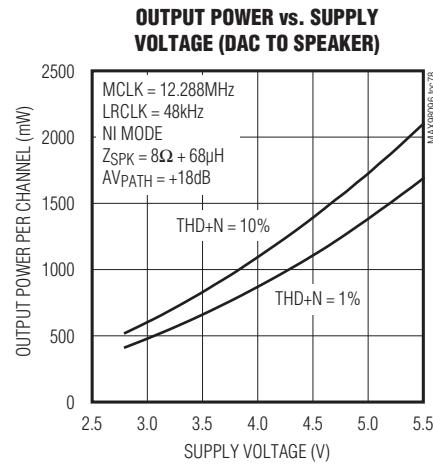

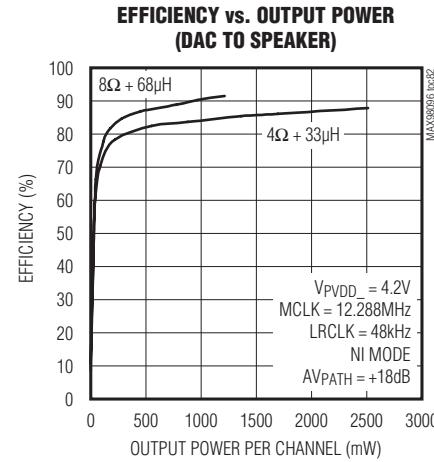

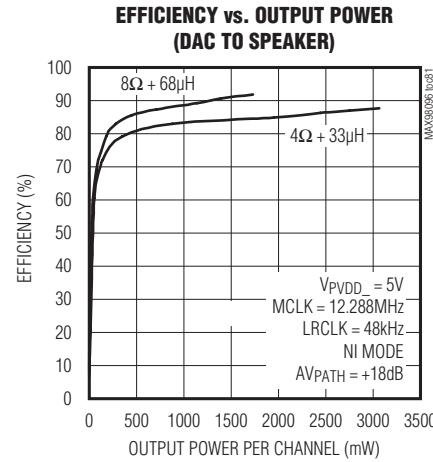

- ◆ 3.2W per Channel (4Ω, V<sub>PPDD</sub> = 5.0V)

- ◆ 1.2W per Channel (8Ω, V<sub>PPDD</sub> = 4.2V)

- ◆ Stereo DirectDrive® Headphone Amplifiers

- ◆ Jack Detection and Identification

- ◆ Differential Receiver Amplifier/Stereo Line Output

- ◆ Asynchronous Digital Mixing and Sample Rate Conversion

**Ordering Information** appears at end of data sheet.

For related parts and recommended products to use with this part, refer to [www.maxim-ic.com/MAX98096.related](http://www.maxim-ic.com/MAX98096.related).

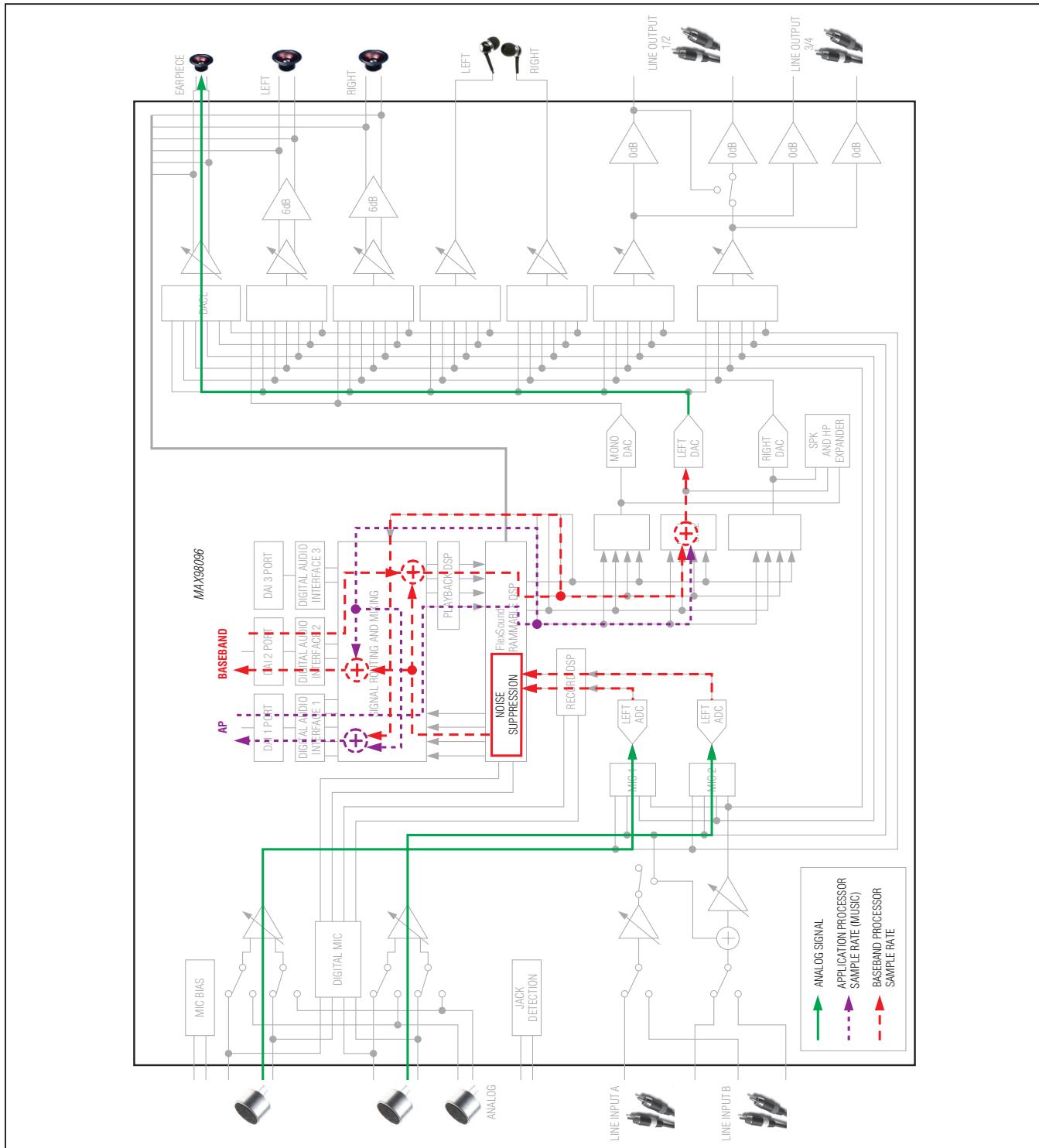

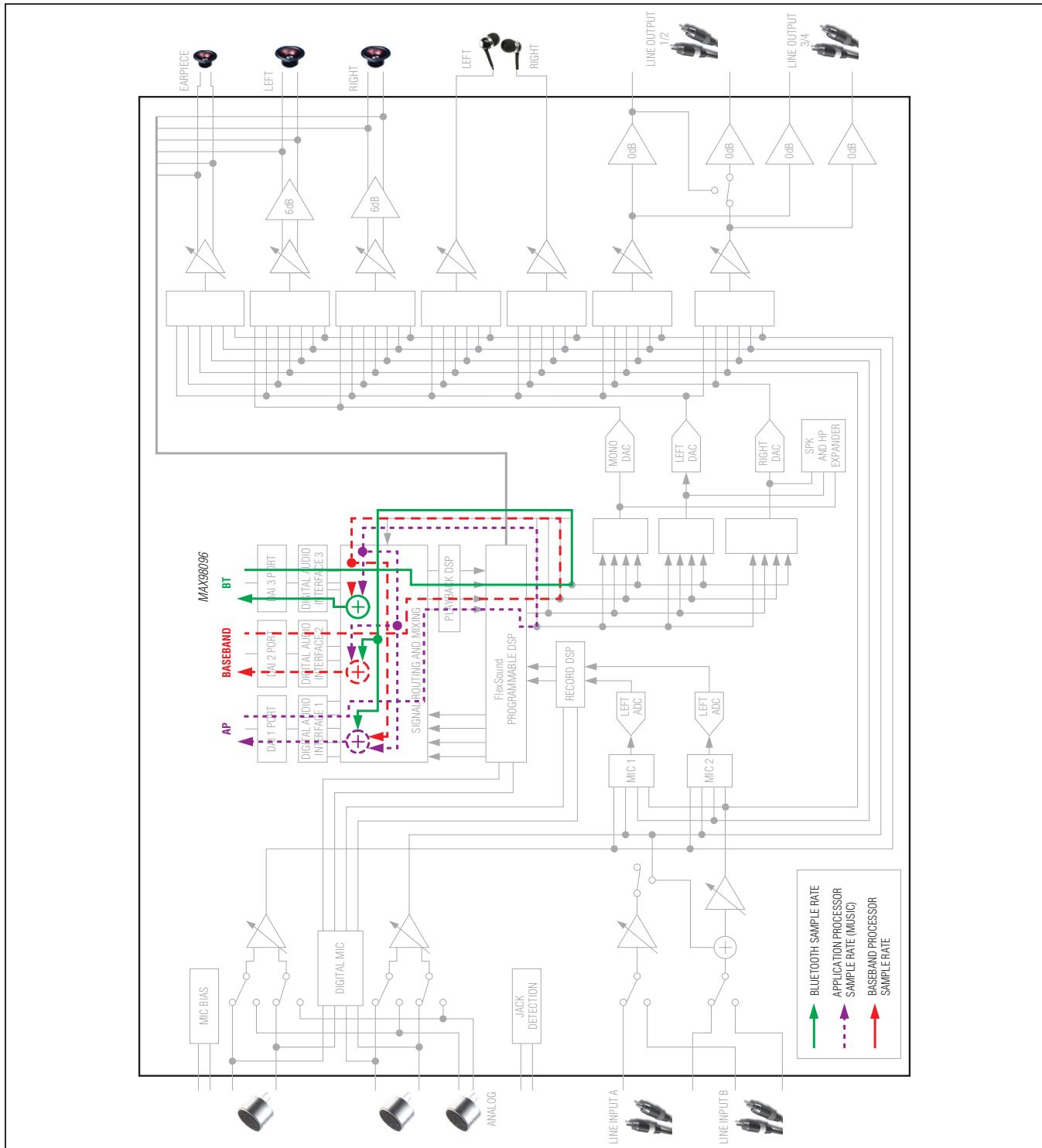

### Simplified Block Diagram

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at [www.maxim-ic.com](http://www.maxim-ic.com).

# Audio Hub with Wideband FlexSound Processor

---

## TABLE OF CONTENTS

---

|                                                                        |    |

|------------------------------------------------------------------------|----|

| General Description . . . . .                                          | 1  |

| Benefits and Features . . . . .                                        | 1  |

| Simplified Block Diagram . . . . .                                     | 1  |

| Functional Diagram (1 of 3) . . . . .                                  | 9  |

| Absolute Maximum Ratings . . . . .                                     | 12 |

| Package Thermal Characteristics . . . . .                              | 12 |

| Electrical Characteristics . . . . .                                   | 12 |

| Digital Inputs/Outputs Characteristics . . . . .                       | 31 |

| Input Clock Characteristics . . . . .                                  | 35 |

| Digital Audio Interface Timing Characteristics . . . . .               | 36 |

| Digital Microphone Timing Characteristics . . . . .                    | 37 |

| I <sup>2</sup> C Timing Characteristics . . . . .                      | 38 |

| SPI Timing Characteristics . . . . .                                   | 40 |

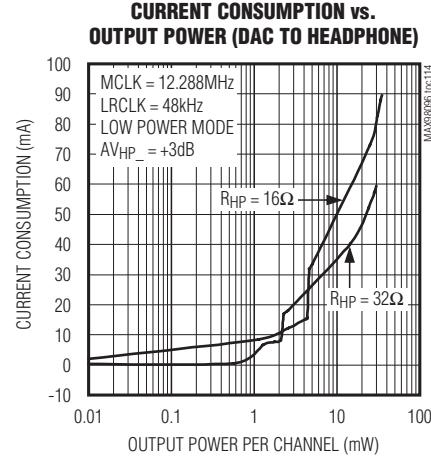

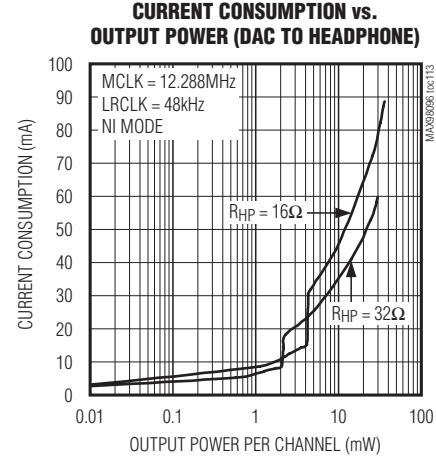

| Power Consumption . . . . .                                            | 41 |

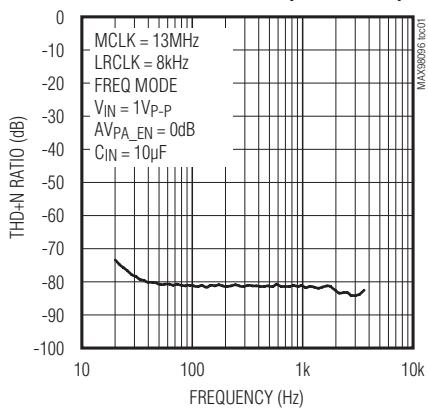

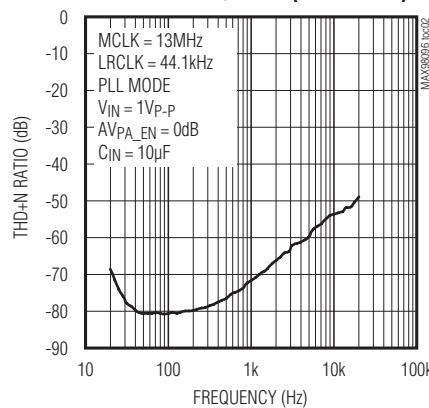

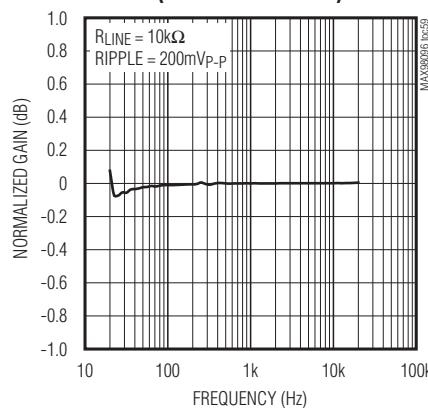

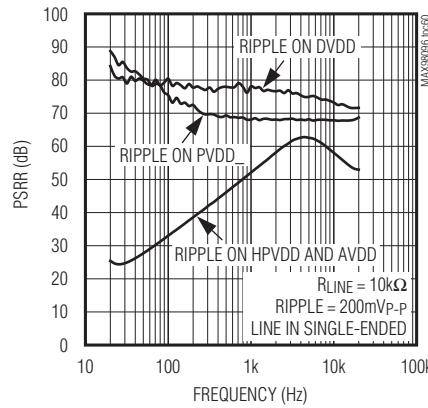

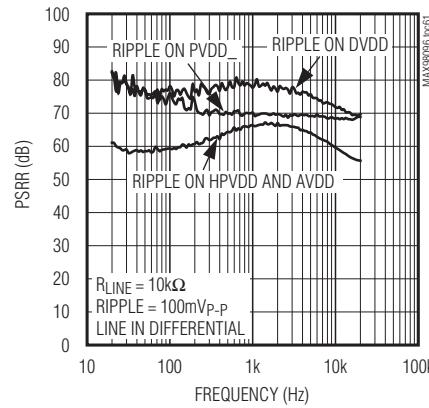

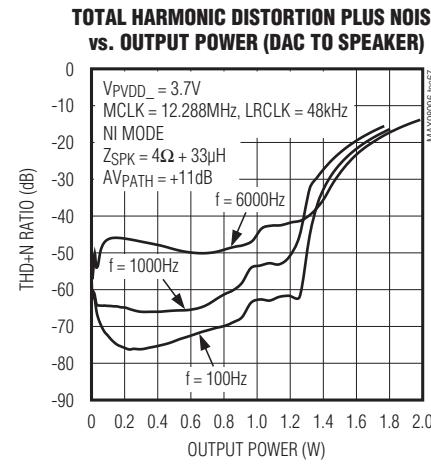

| Typical Operating Characteristics . . . . .                            | 44 |

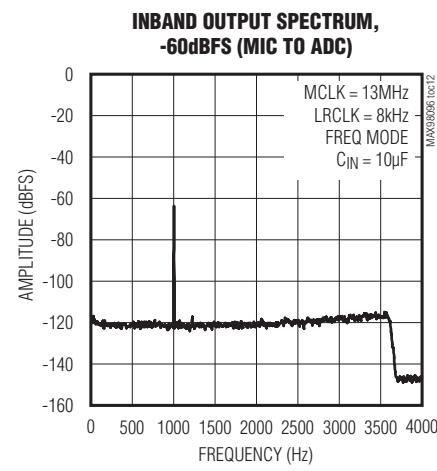

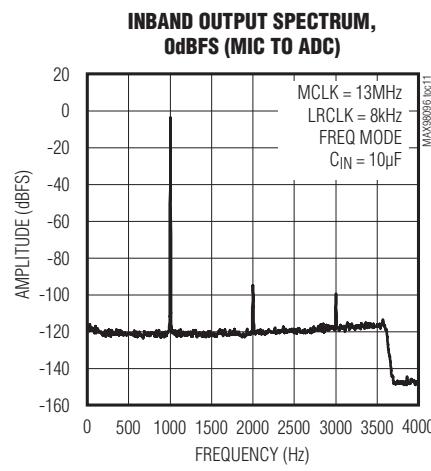

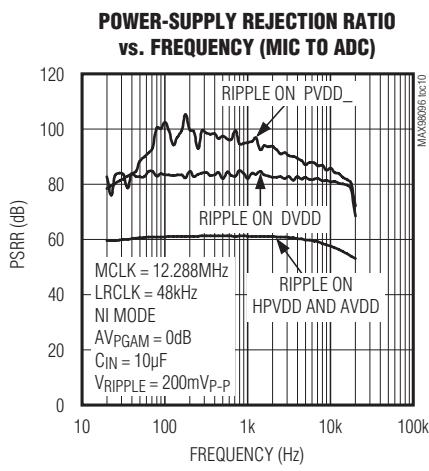

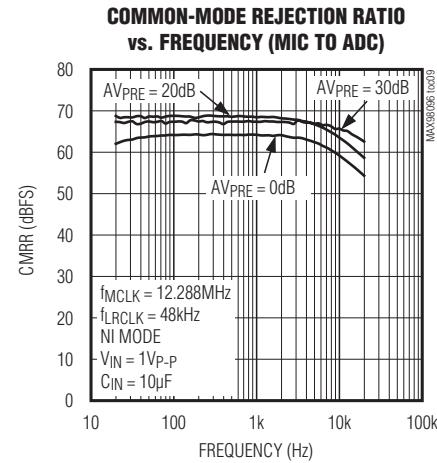

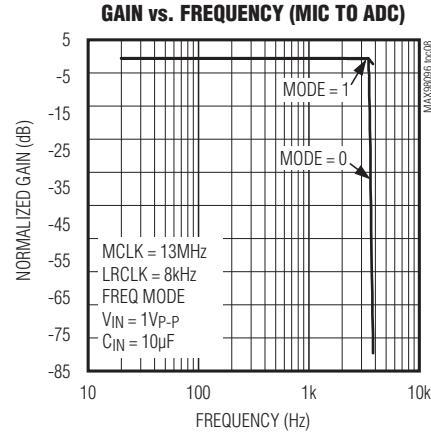

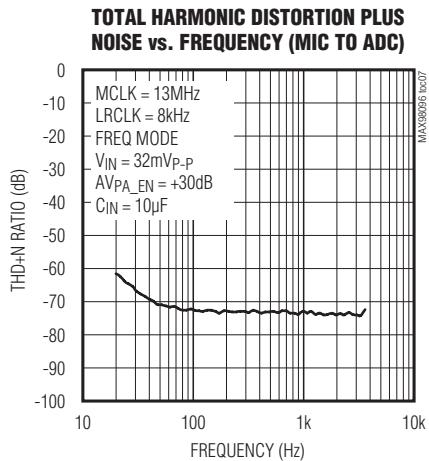

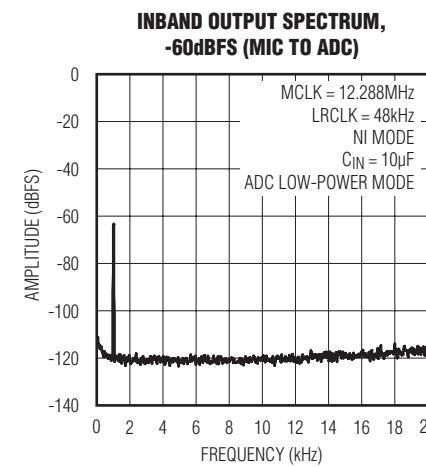

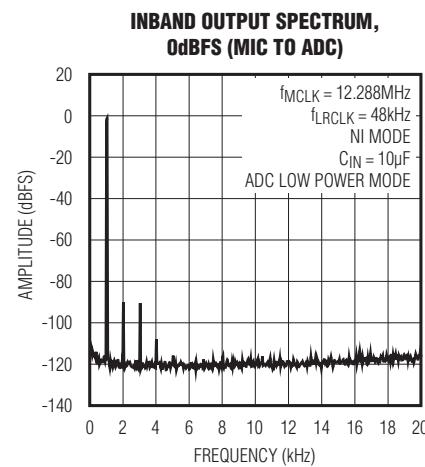

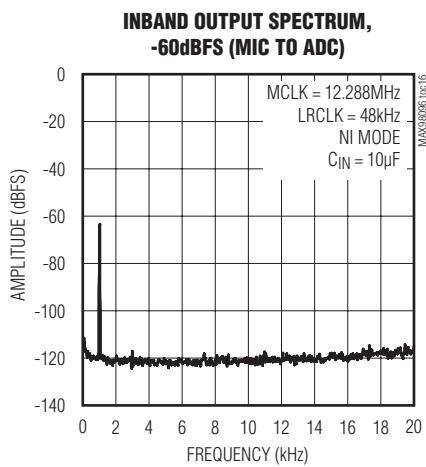

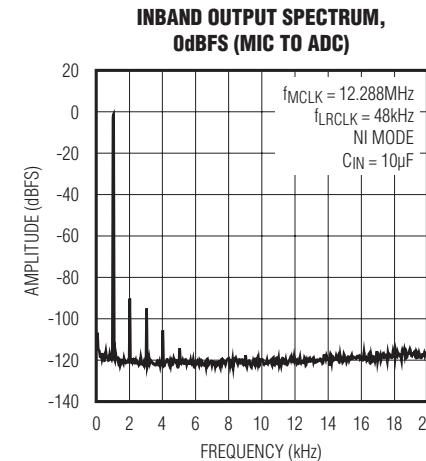

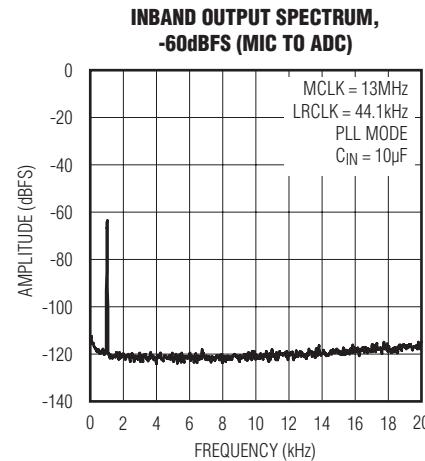

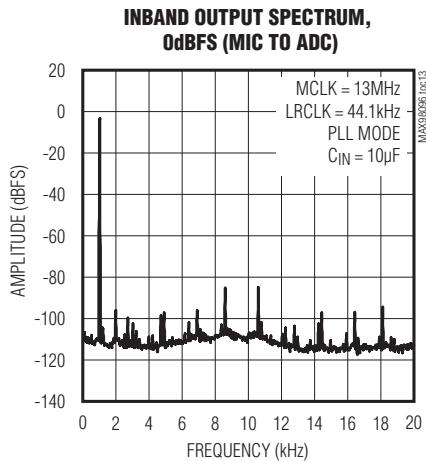

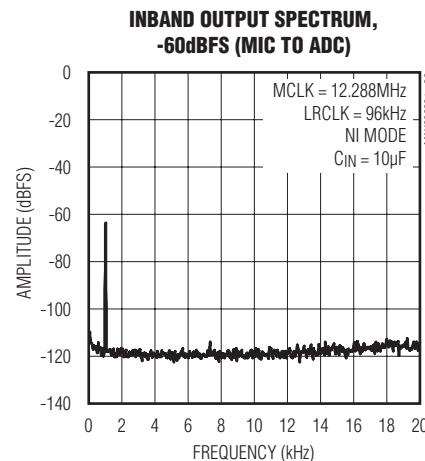

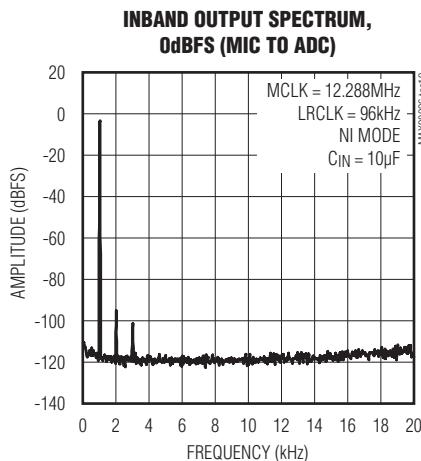

| Microphone to ADC . . . . .                                            | 44 |

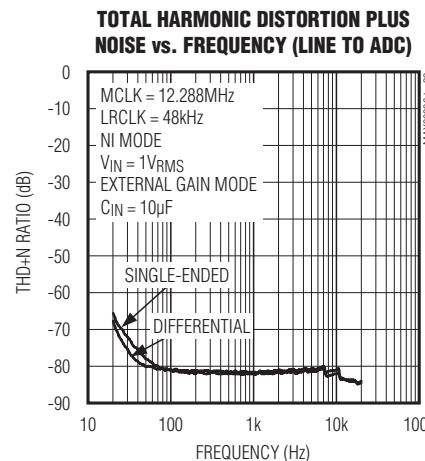

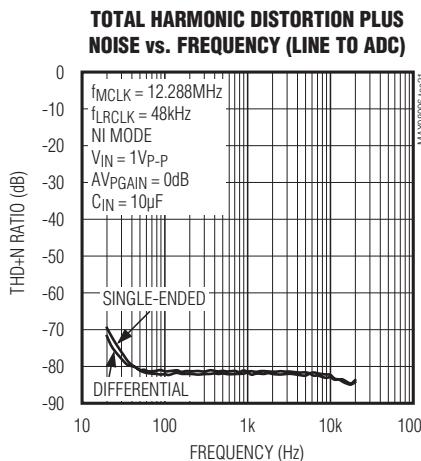

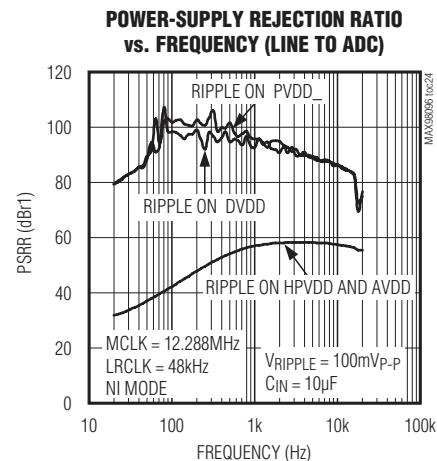

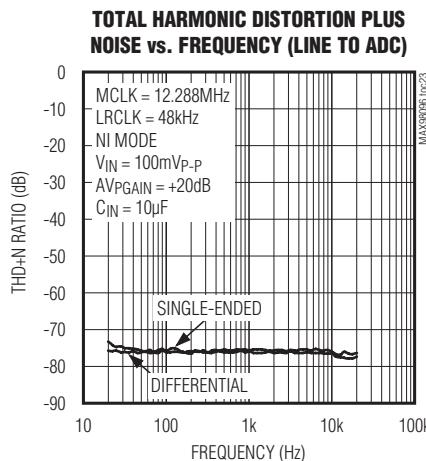

| Line In to ADC . . . . .                                               | 47 |

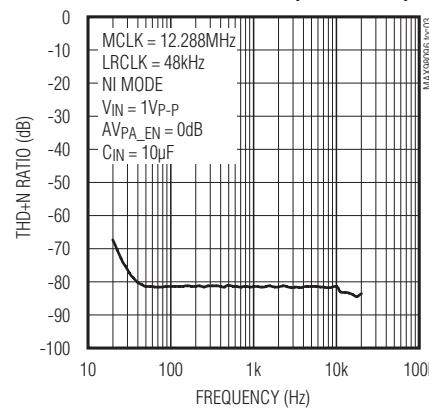

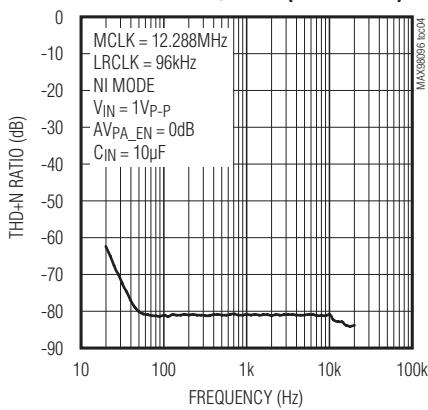

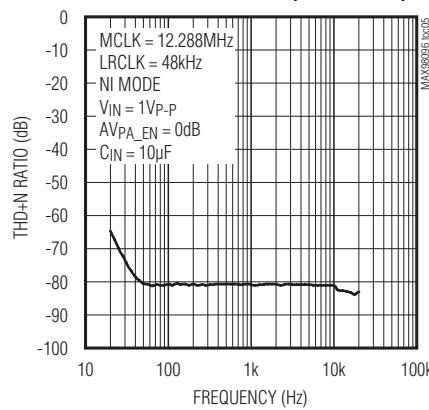

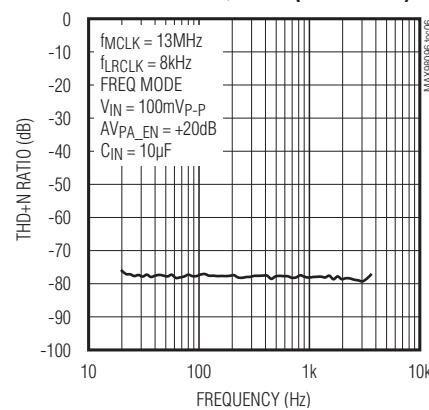

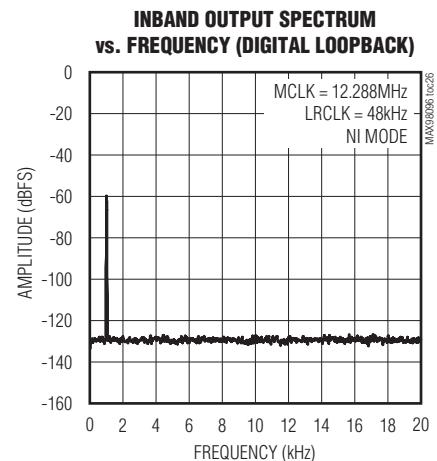

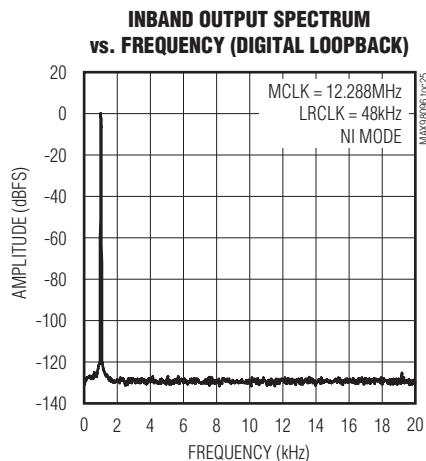

| Digital Loopback—I <sup>2</sup> S In to I <sup>2</sup> S Out . . . . . | 48 |

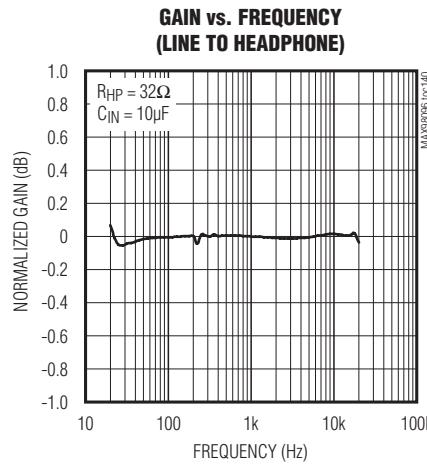

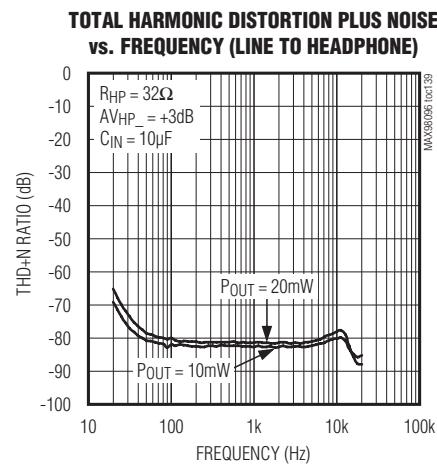

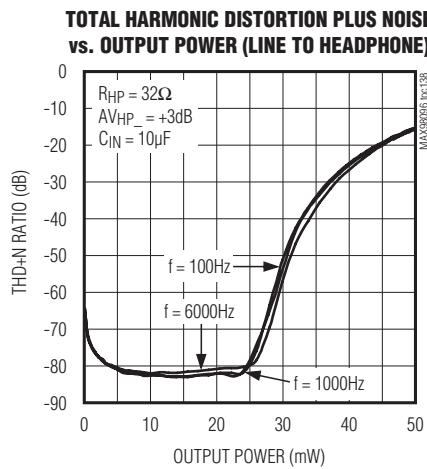

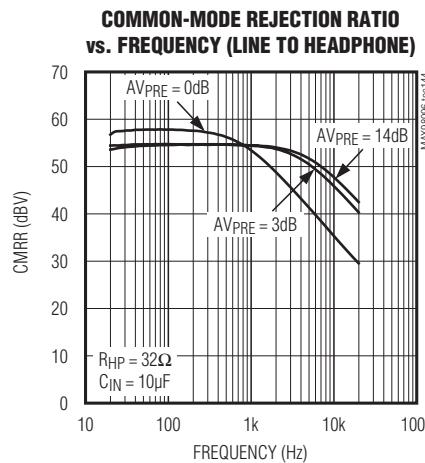

| Analog Loopback—Line Input to Headphone Output . . . . .               | 49 |

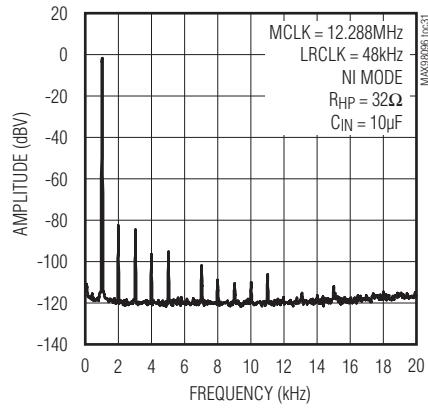

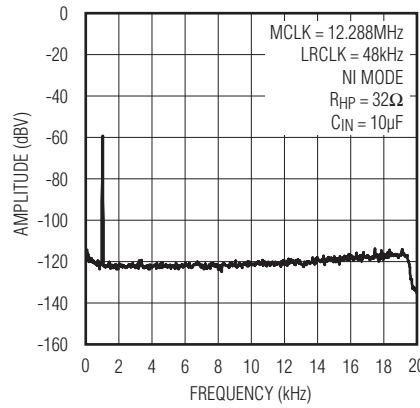

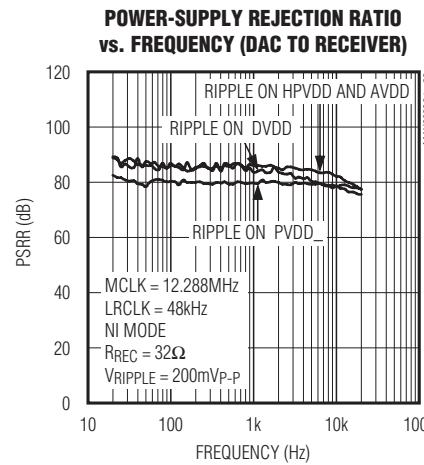

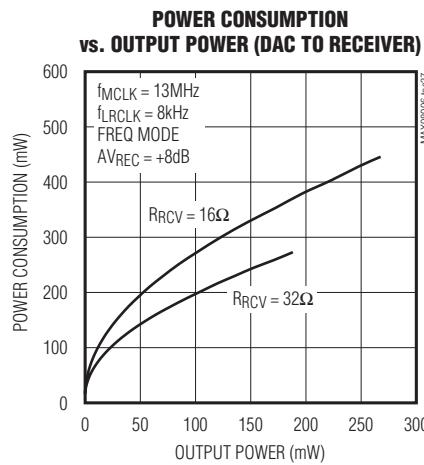

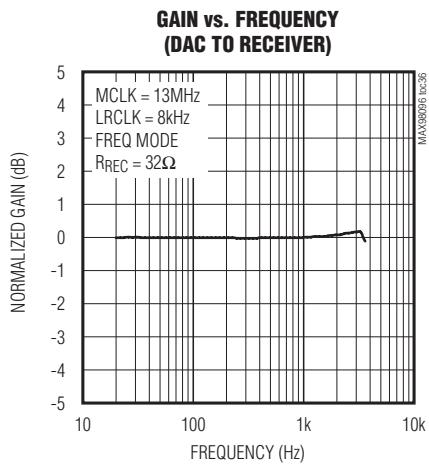

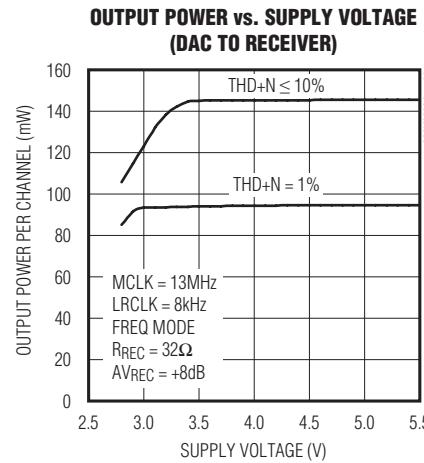

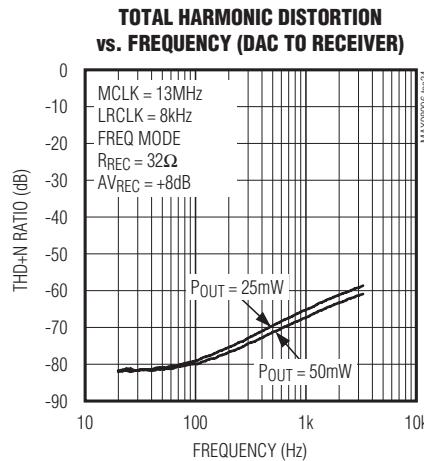

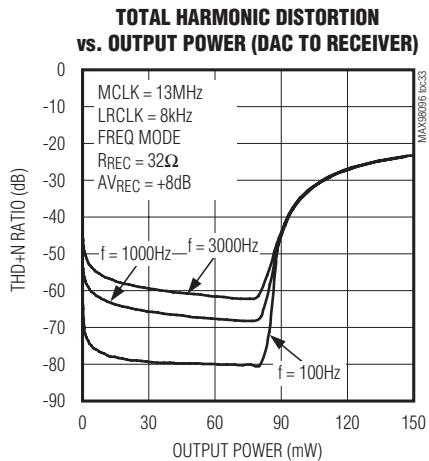

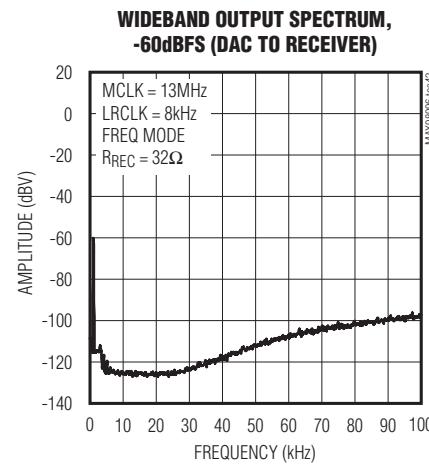

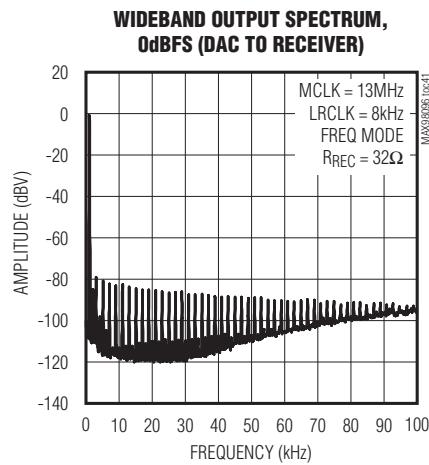

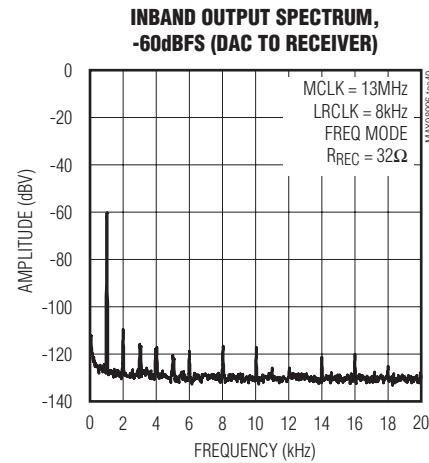

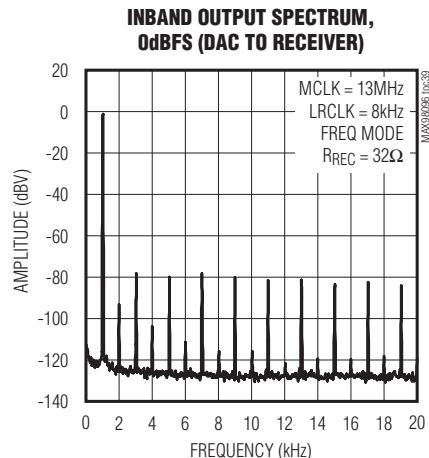

| DAC to Receiver . . . . .                                              | 50 |

| Line In to Receiver . . . . .                                          | 52 |

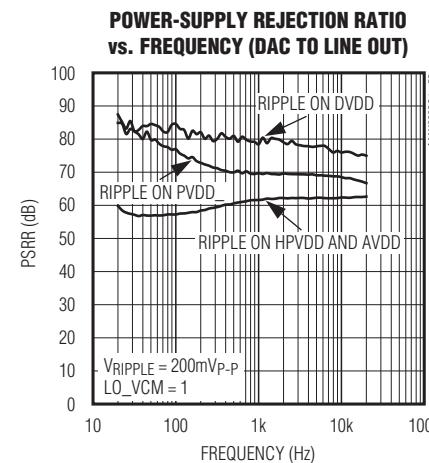

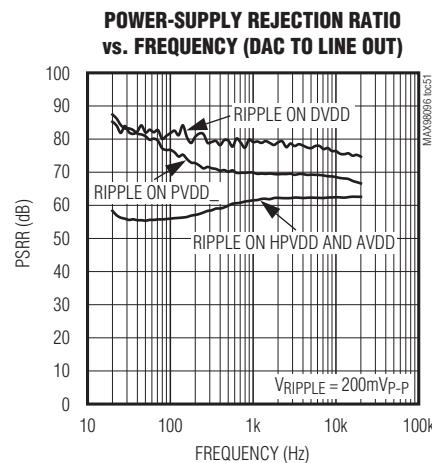

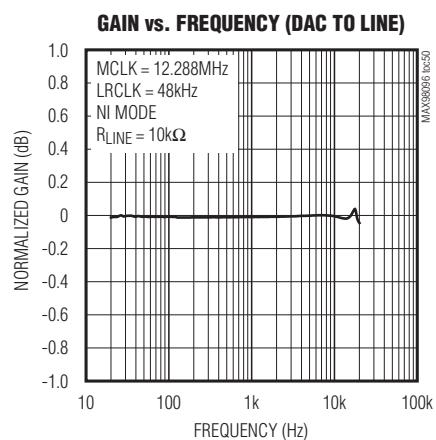

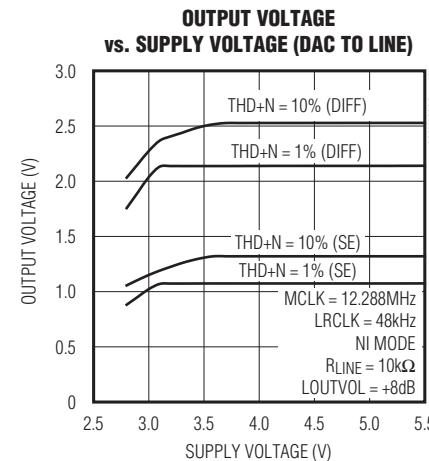

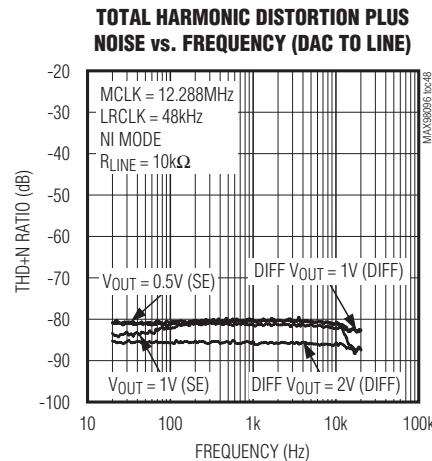

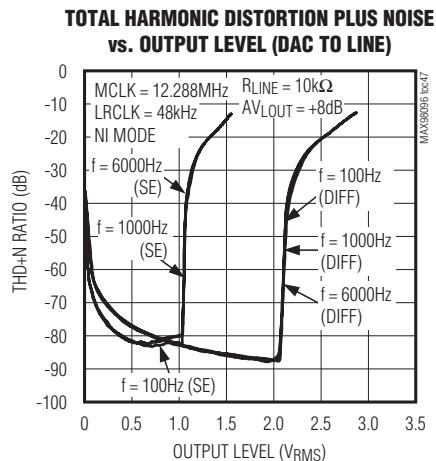

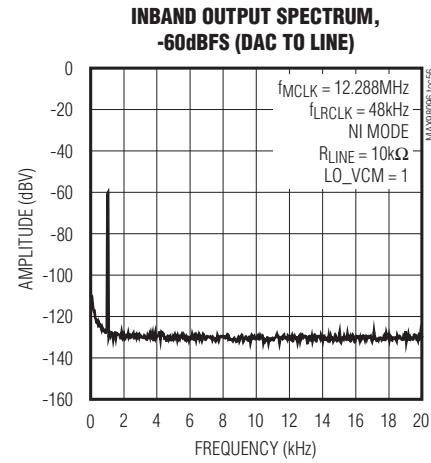

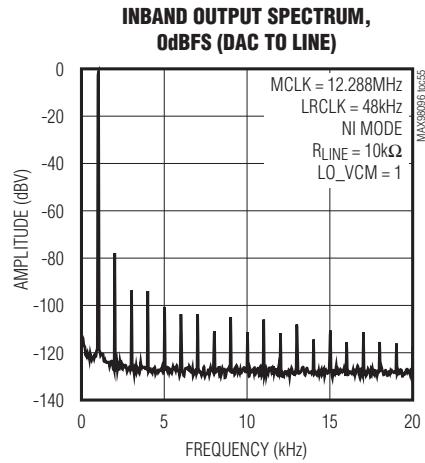

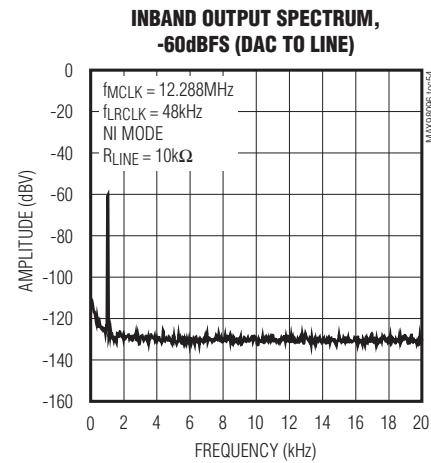

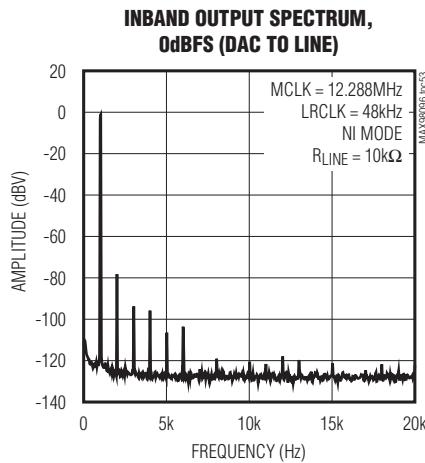

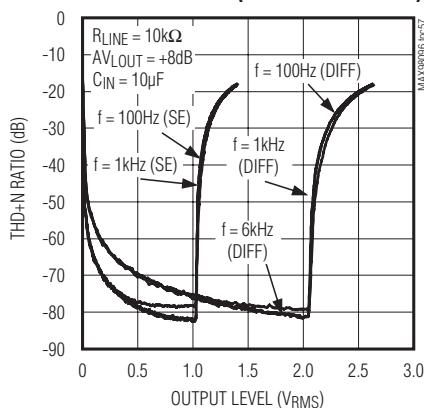

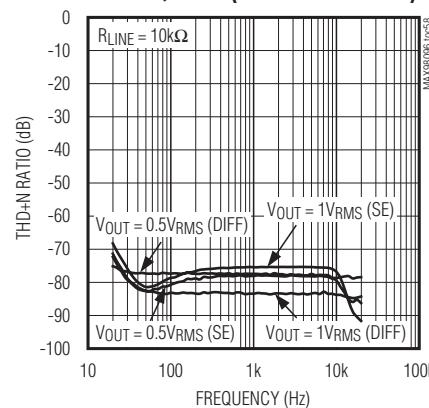

| DAC to Line Output . . . . .                                           | 53 |

| (Single-Ended and Differential Output) . . . . .                       | 53 |

| Line In to Line Out . . . . .                                          | 55 |

| (Single-Ended and Differential Output) . . . . .                       | 55 |

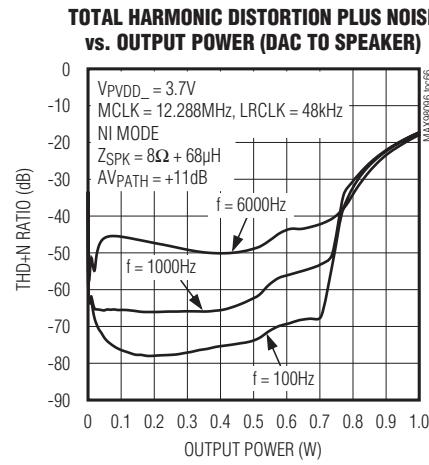

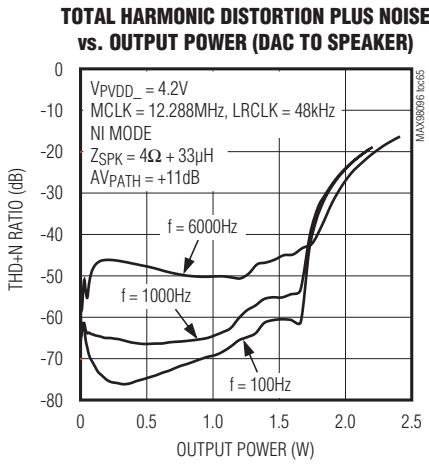

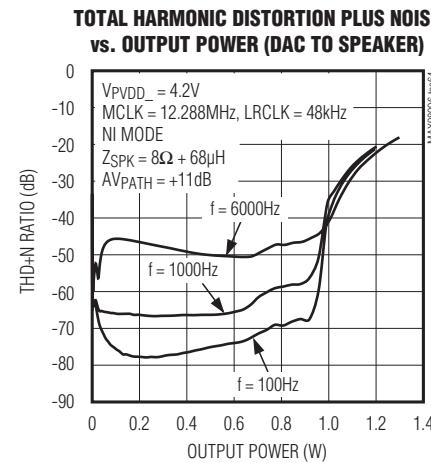

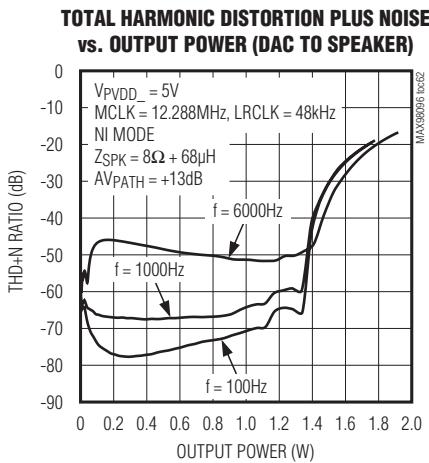

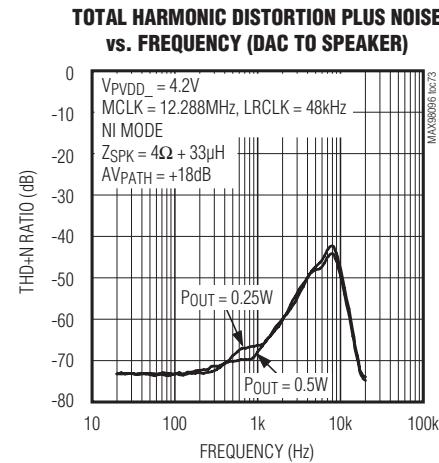

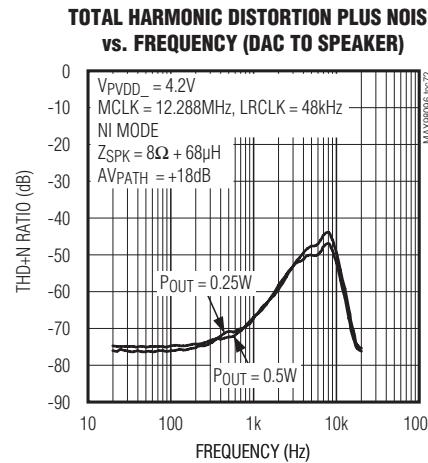

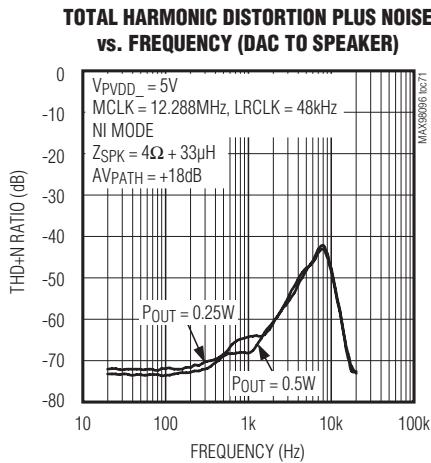

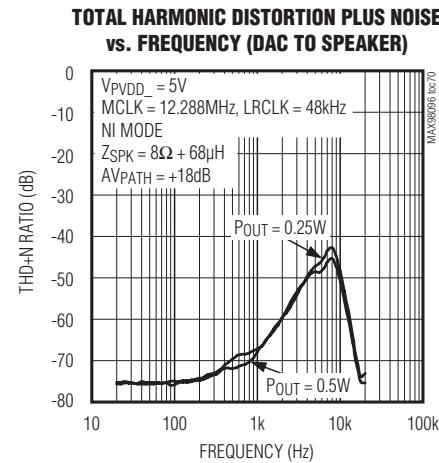

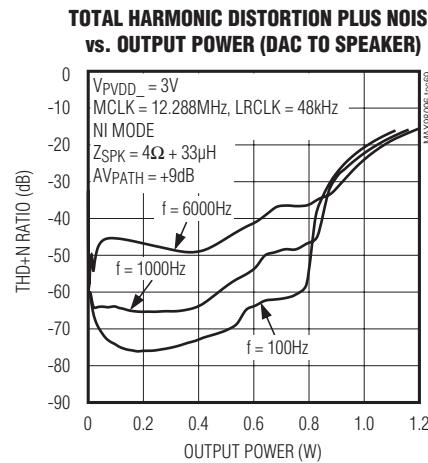

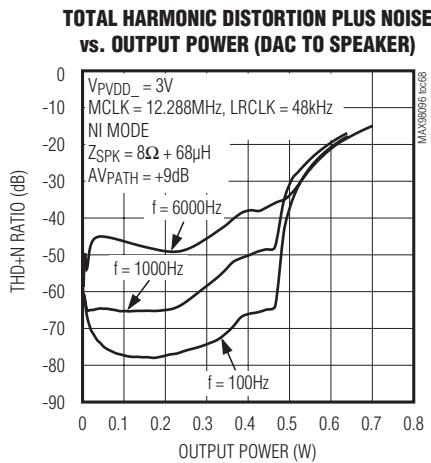

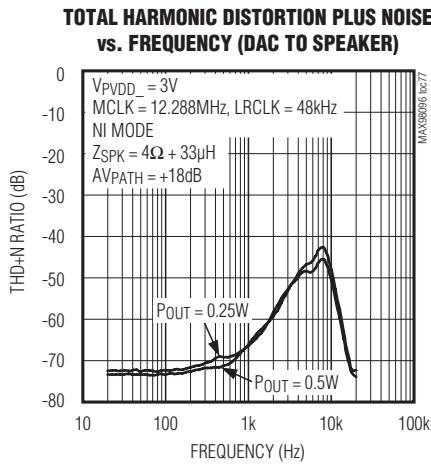

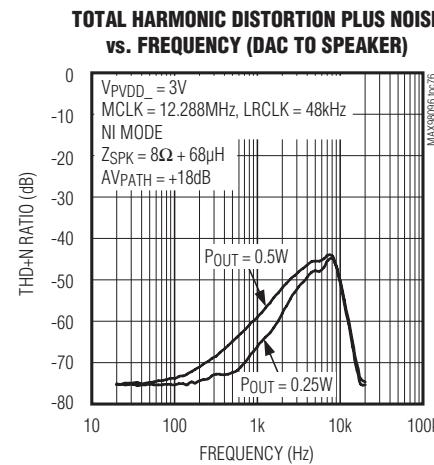

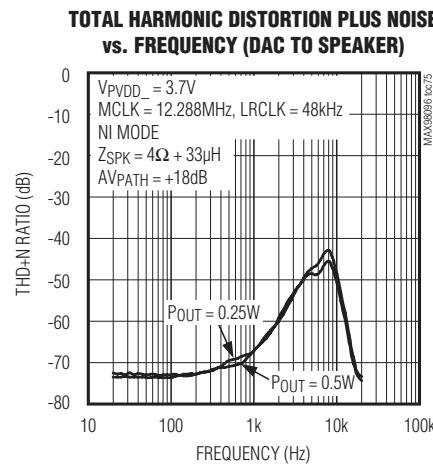

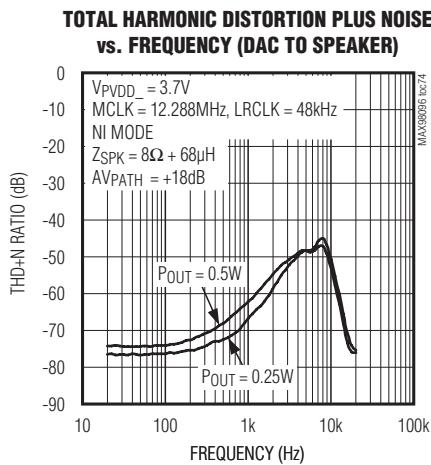

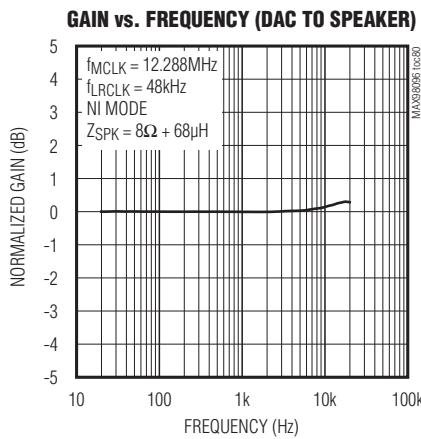

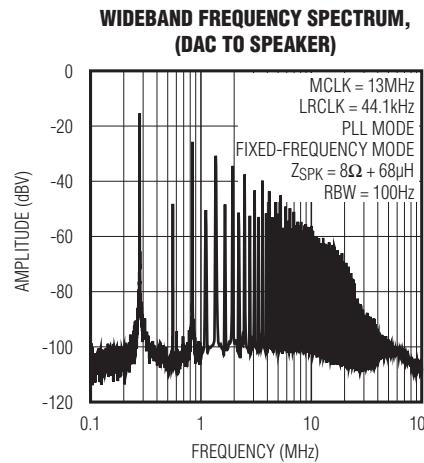

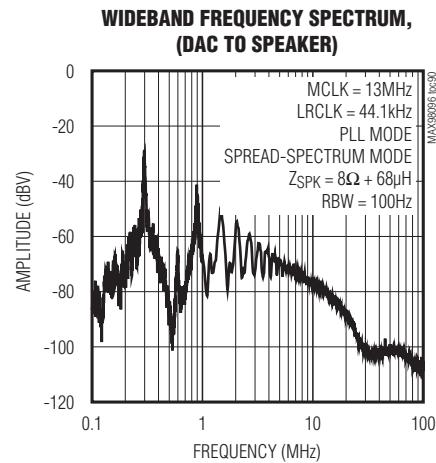

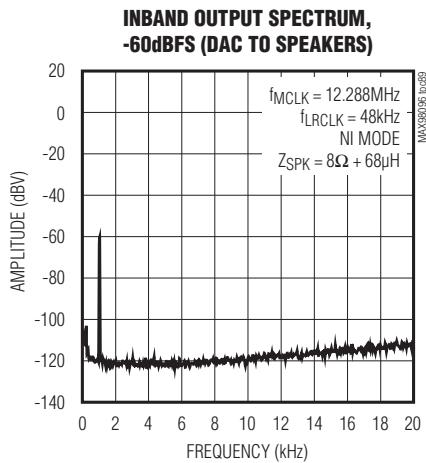

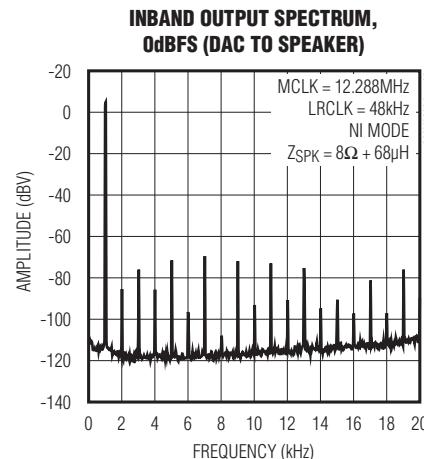

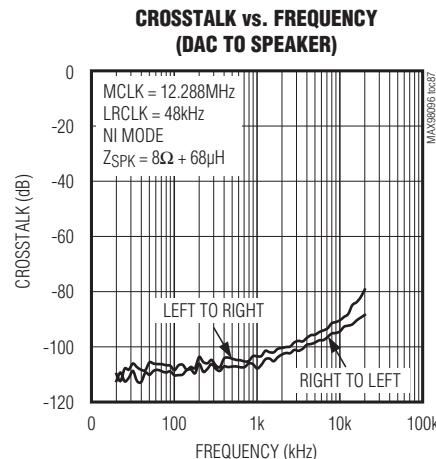

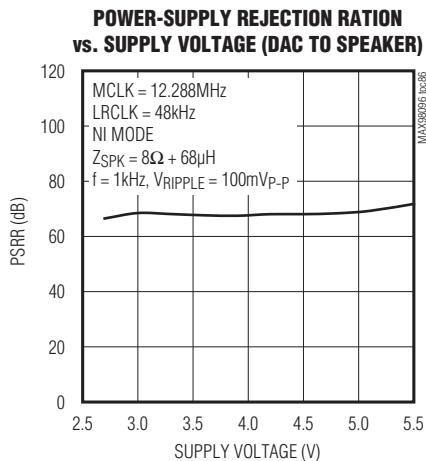

| DAC to Speaker . . . . .                                               | 56 |

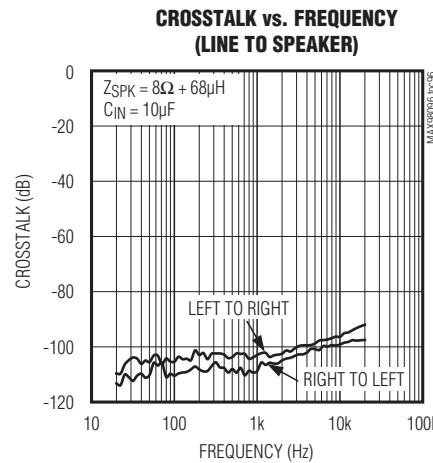

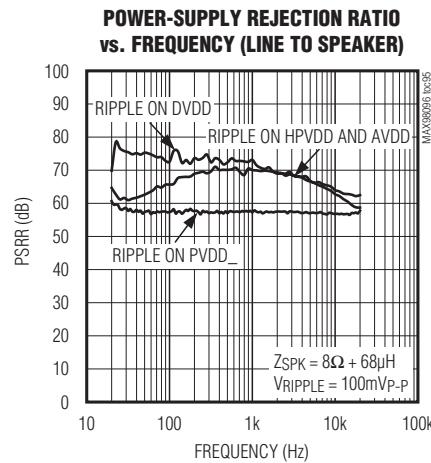

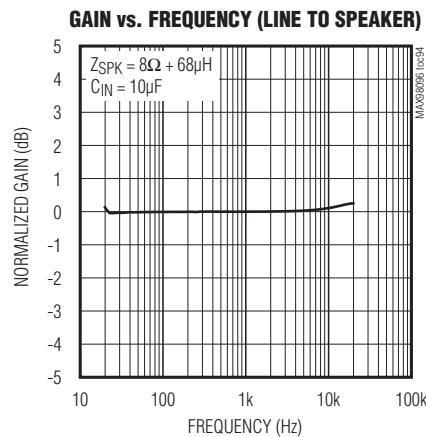

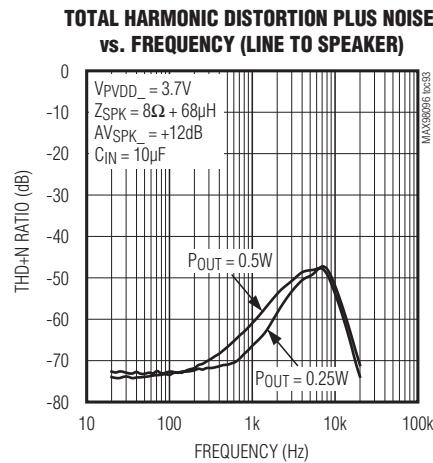

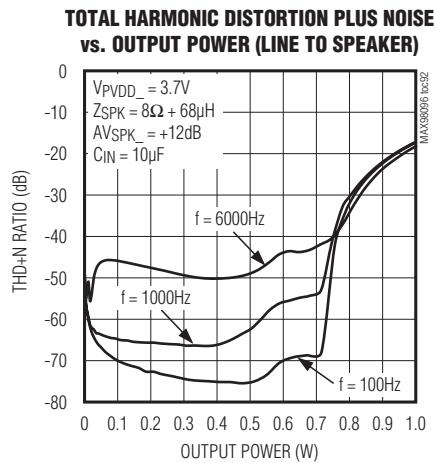

| Line In to Speaker . . . . .                                           | 61 |

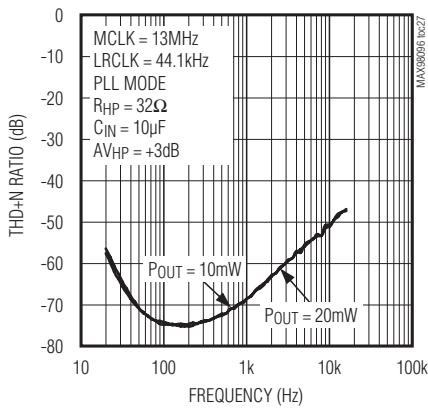

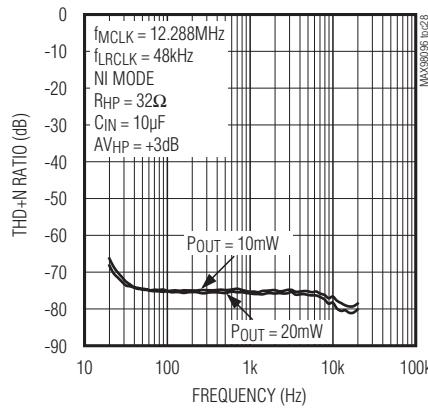

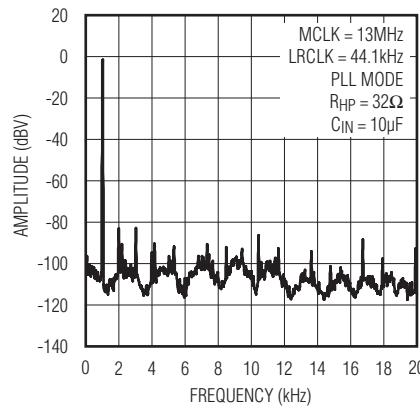

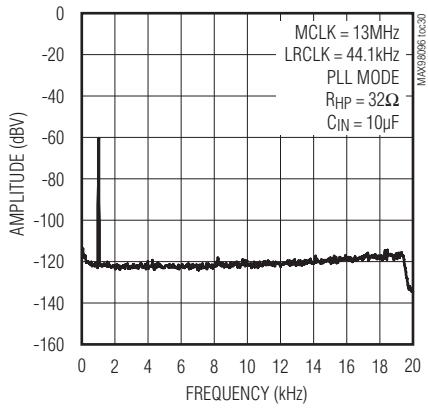

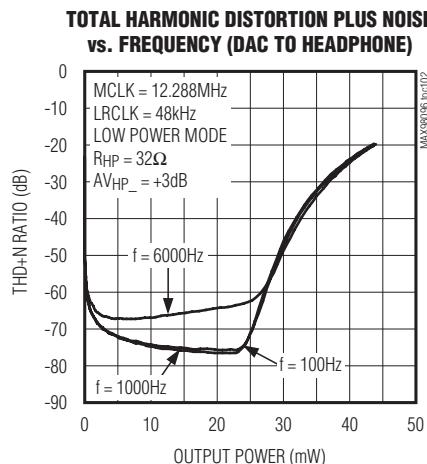

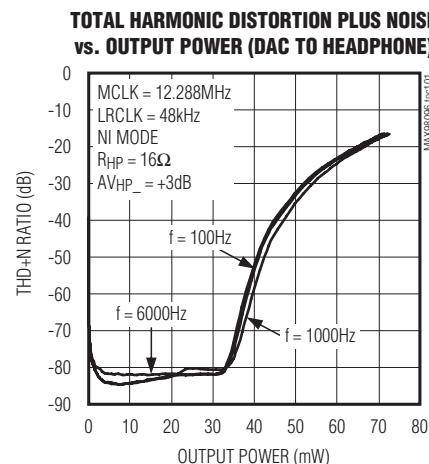

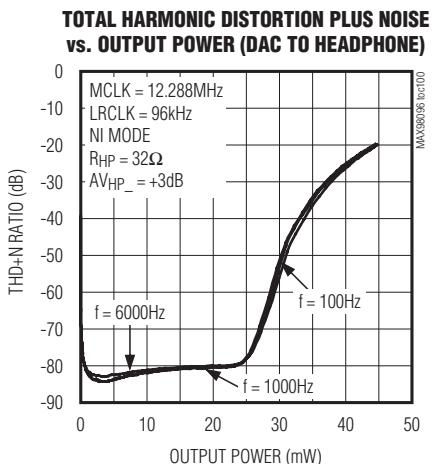

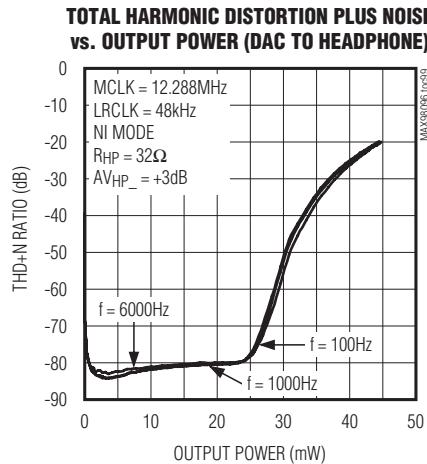

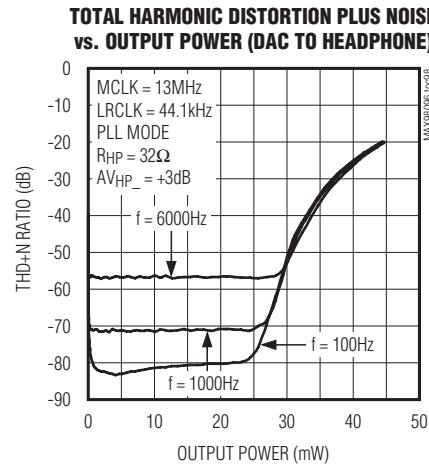

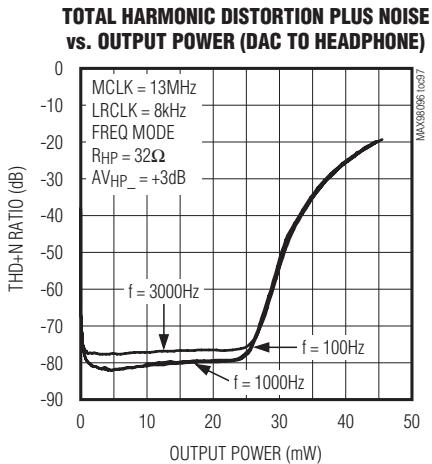

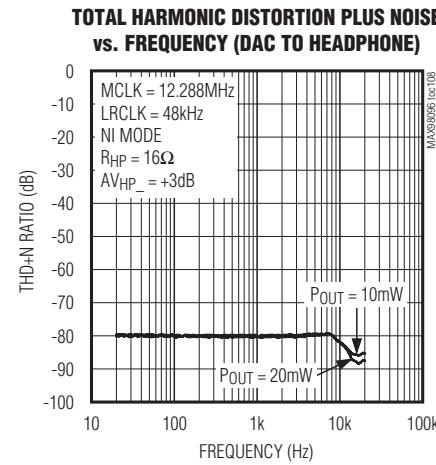

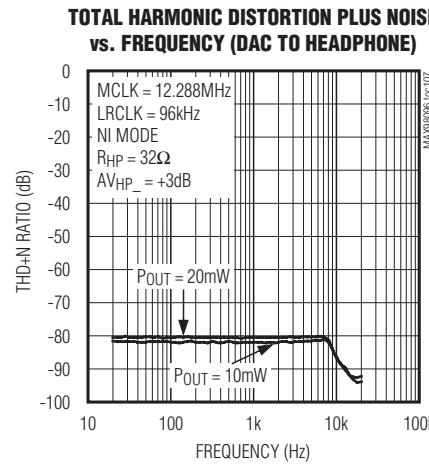

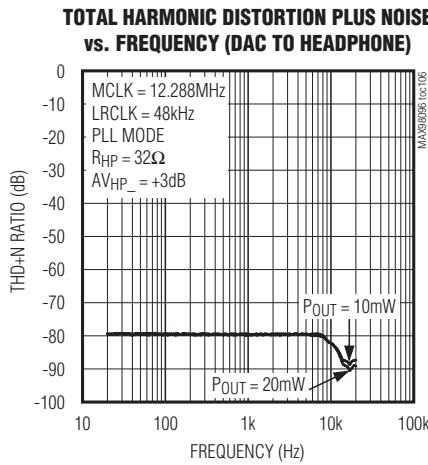

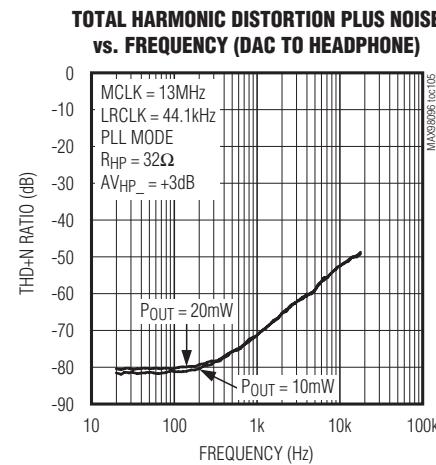

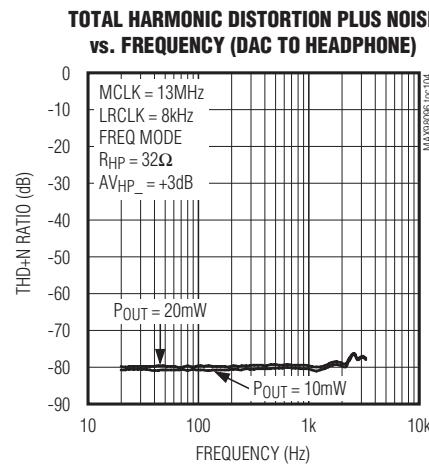

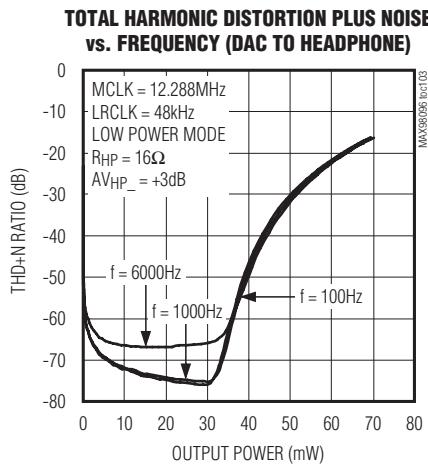

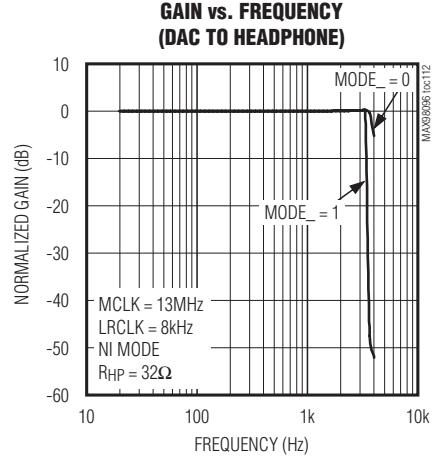

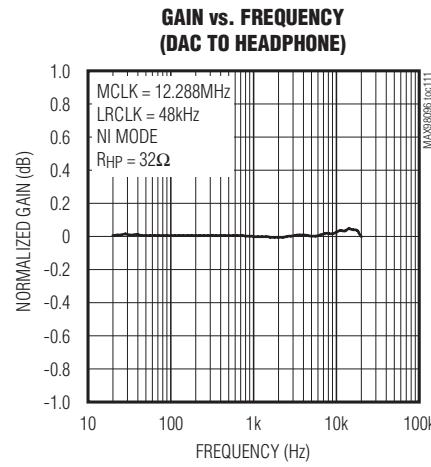

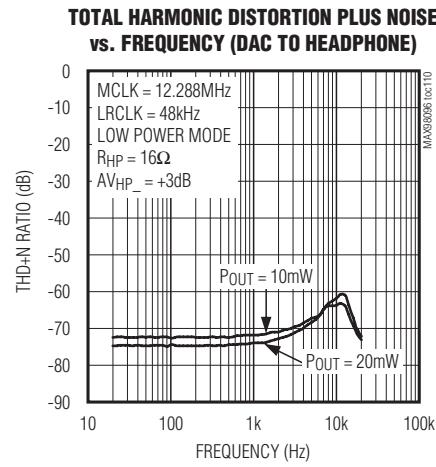

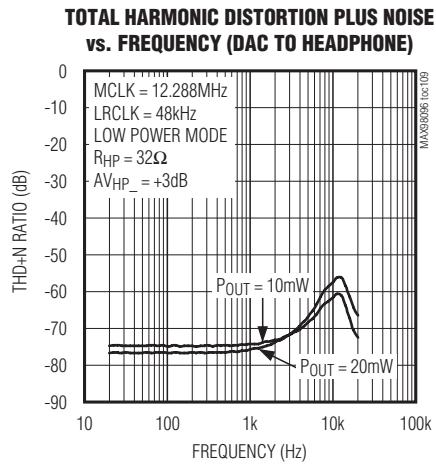

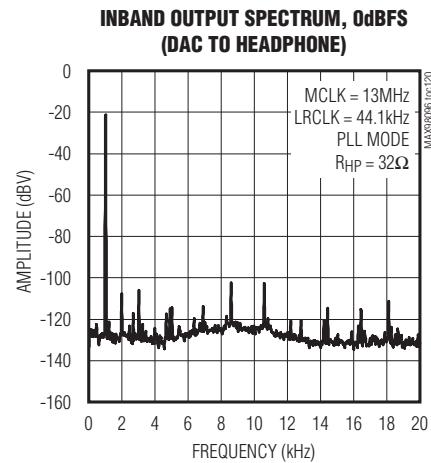

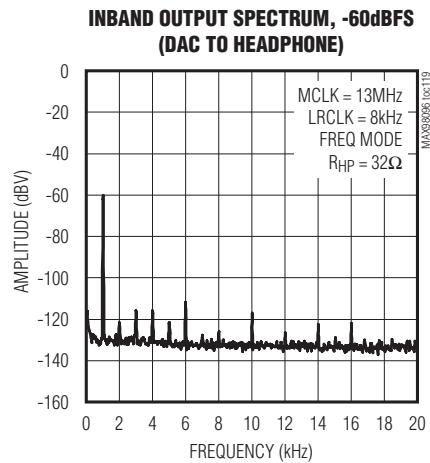

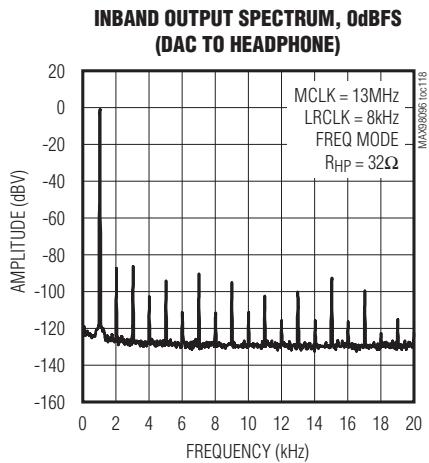

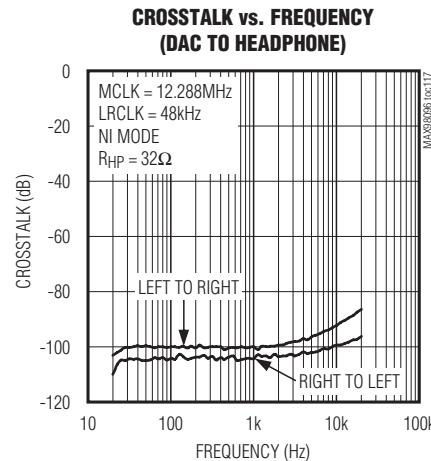

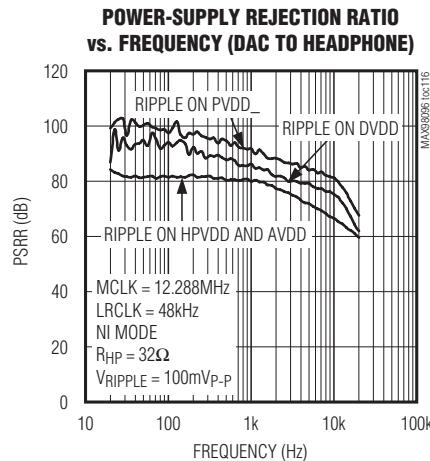

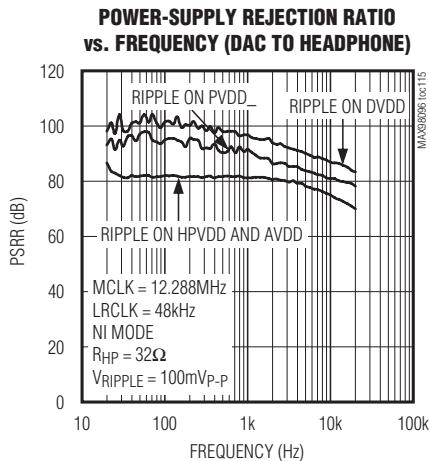

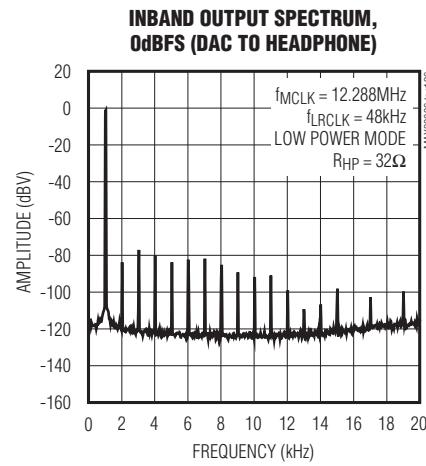

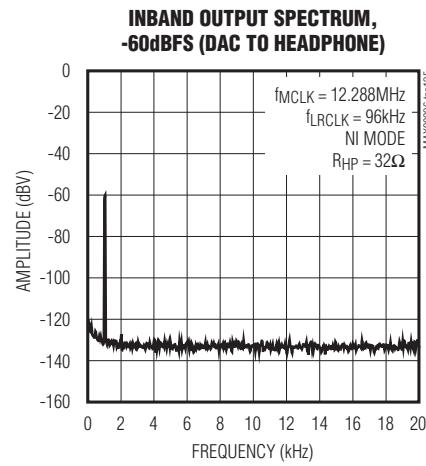

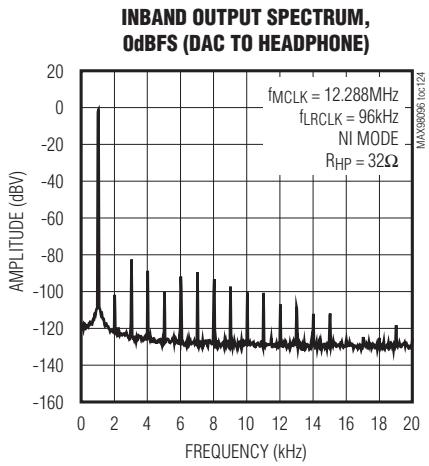

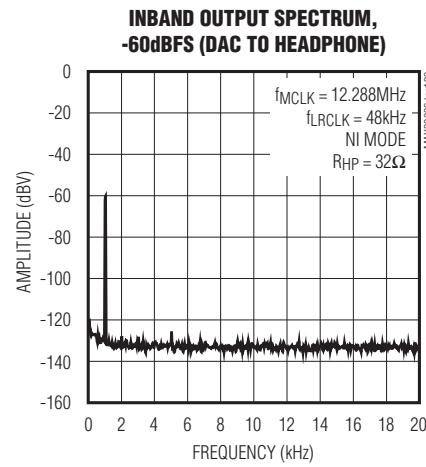

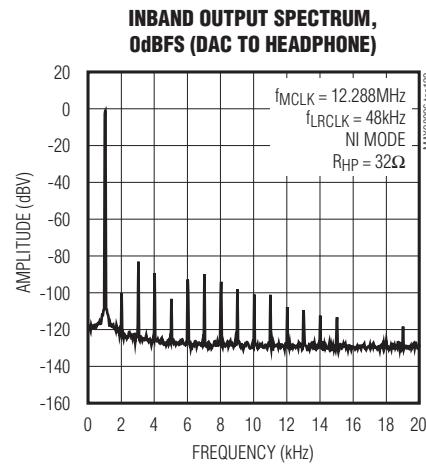

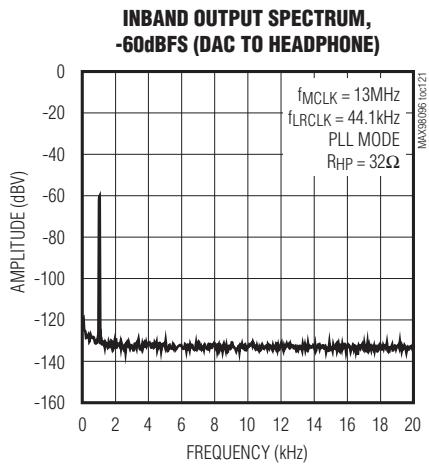

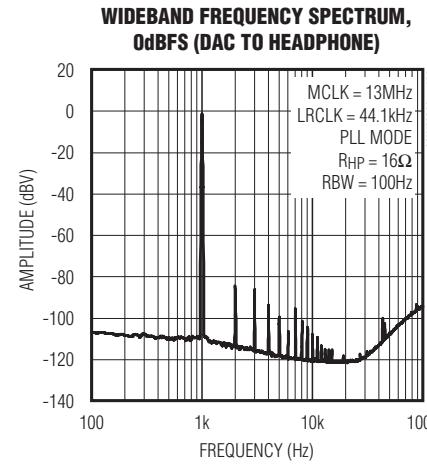

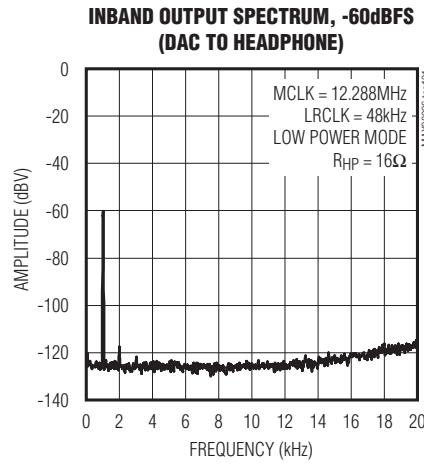

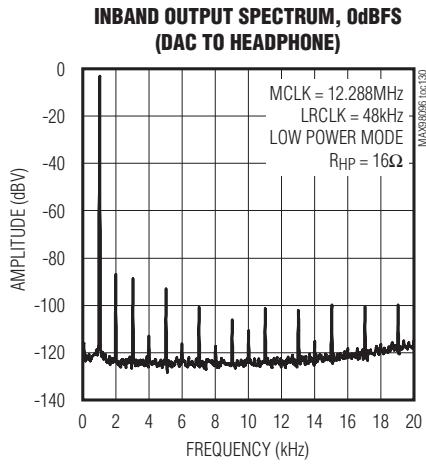

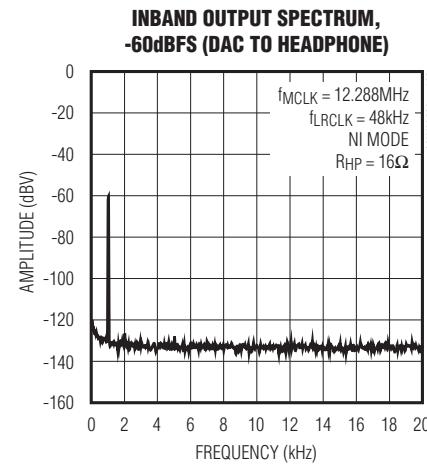

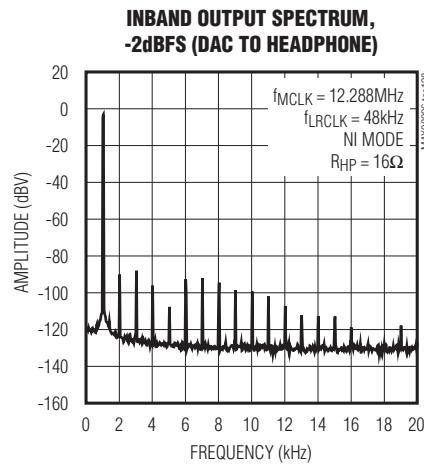

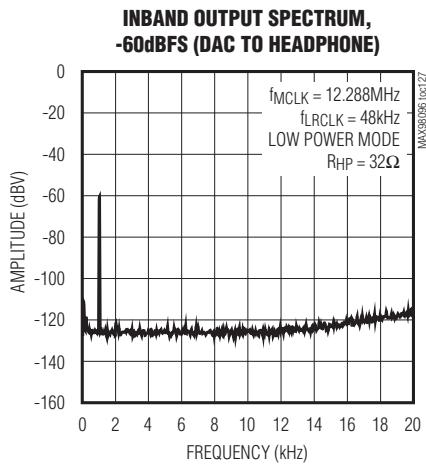

| DAC to Headphone . . . . .                                             | 62 |

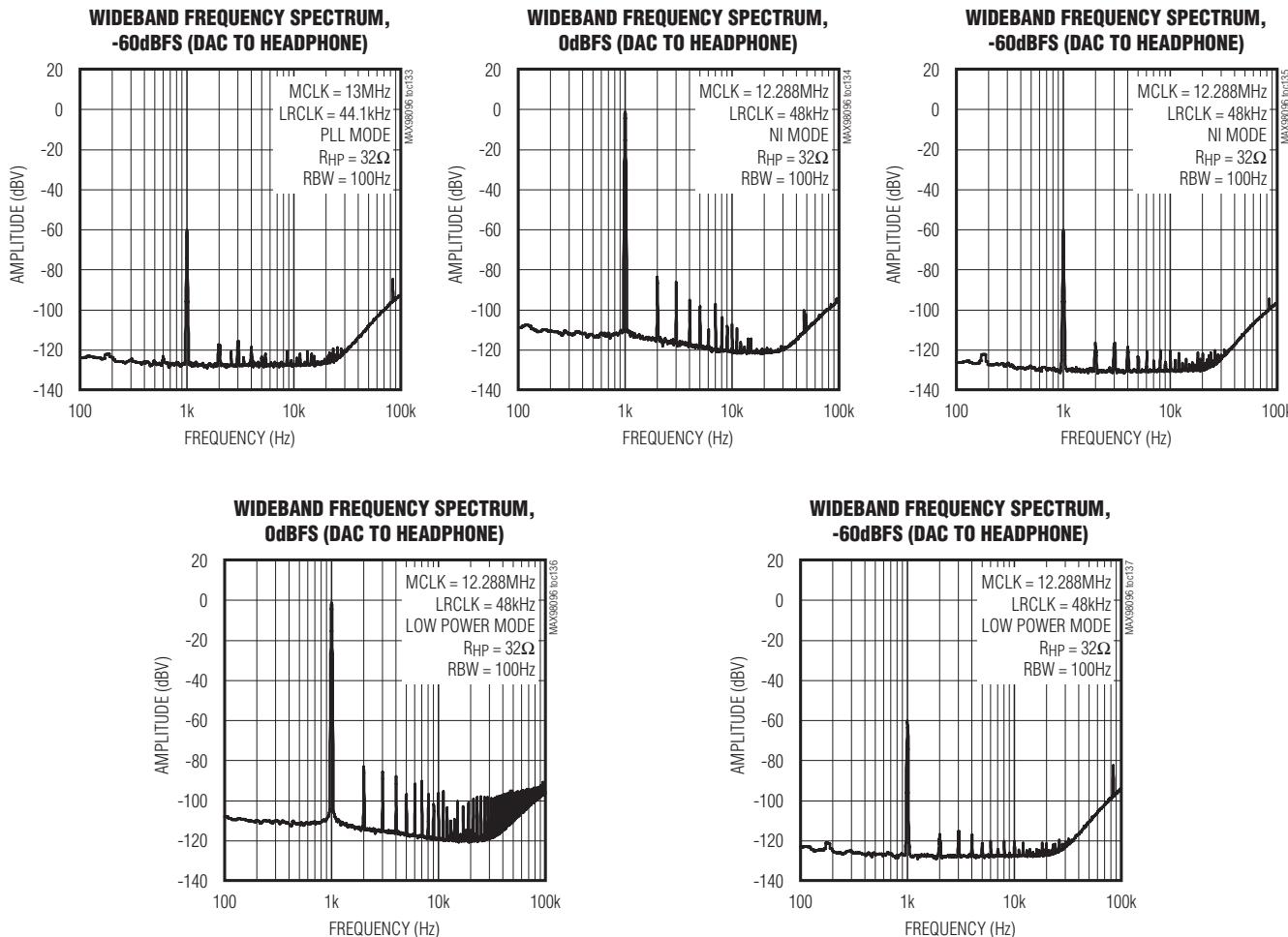

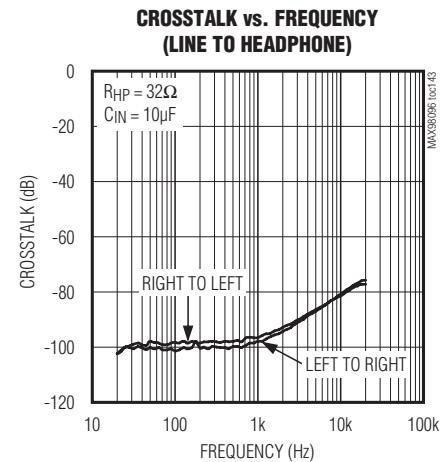

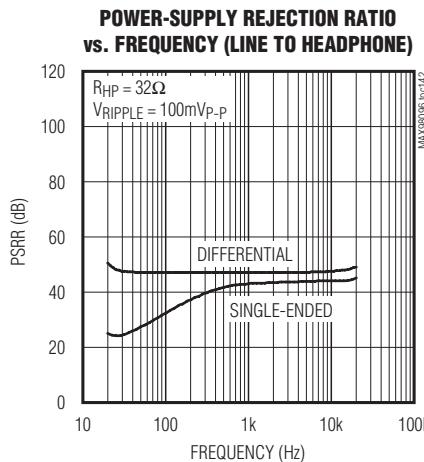

| Line In to Headphone . . . . .                                         | 69 |

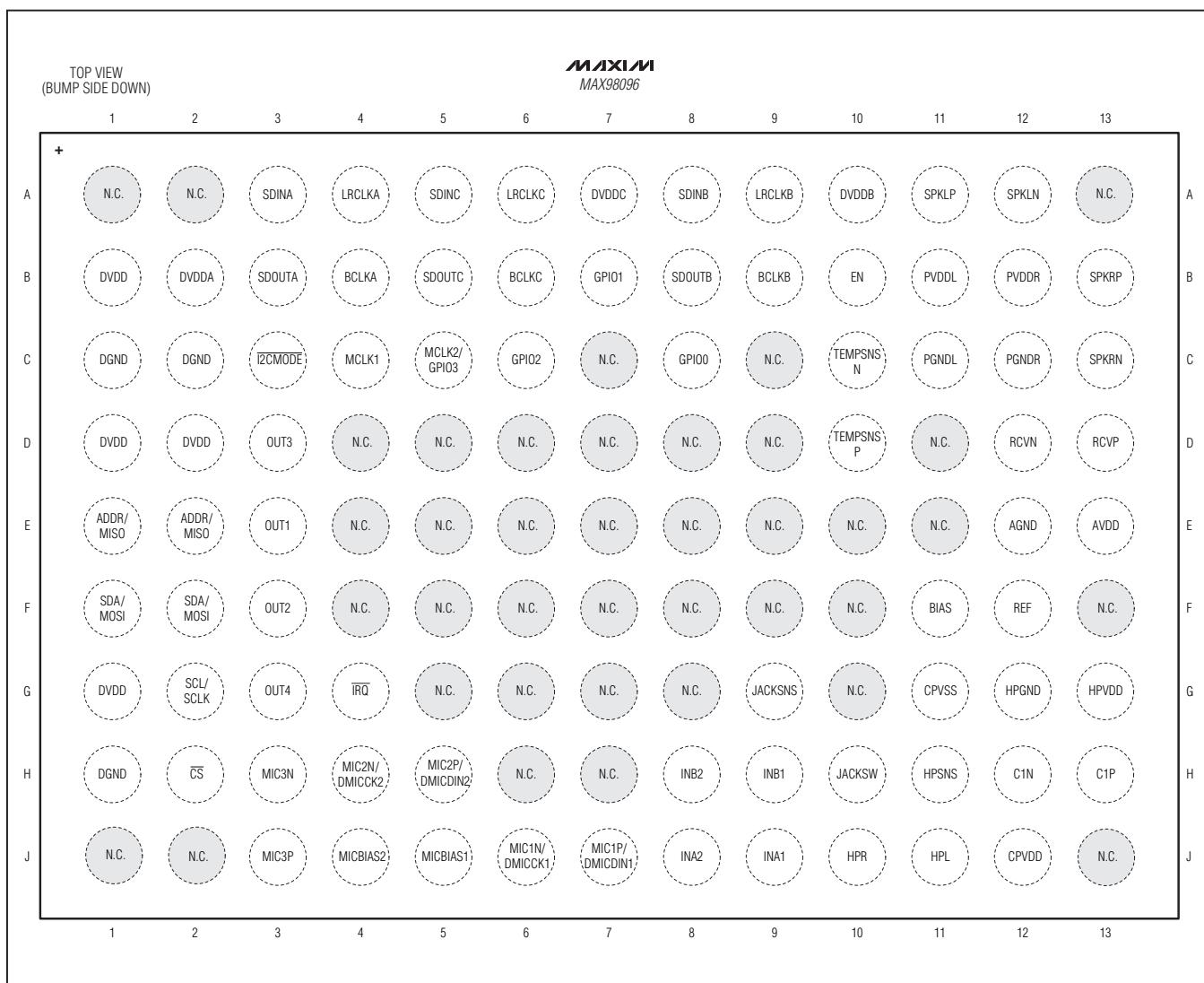

| Bump Configuration . . . . .                                           | 71 |

| Bump Description . . . . .                                             | 72 |

| Detailed Description . . . . .                                         | 75 |

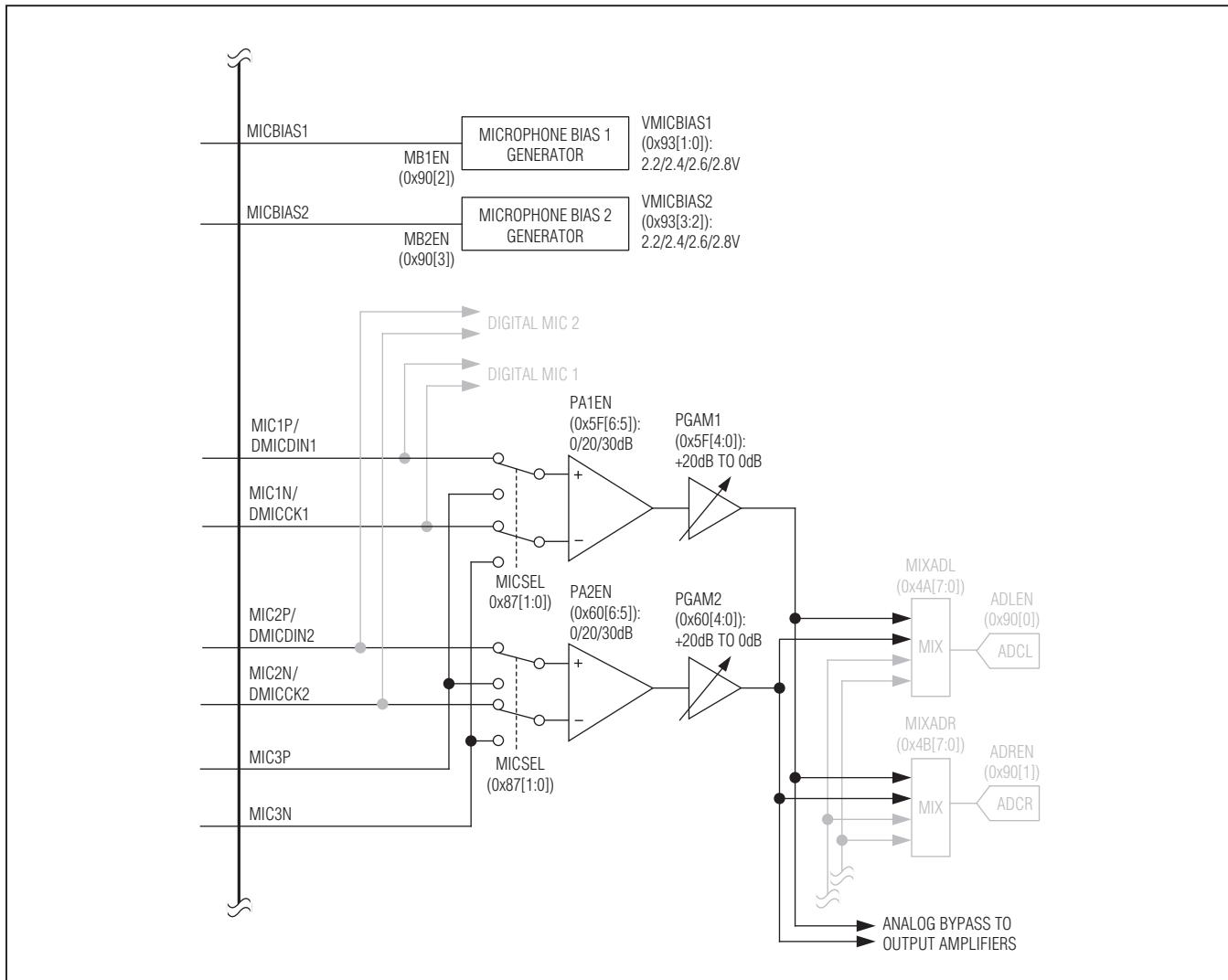

| Analog Microphone Inputs . . . . .                                     | 76 |

| Microphone Bias . . . . .                                              | 77 |

| Digital Microphone Inputs . . . . .                                    | 78 |

| Line Inputs . . . . .                                                  | 79 |

## **Audio Hub with Wideband FlexSound Processor**

---

### **TABLE OF CONTENTS (continued)**

---

|                                                          |     |

|----------------------------------------------------------|-----|

| ADC Input Mixers . . . . .                               | 80  |

| Record Path Signal Processing (Record DSP) . . . . .     | 80  |

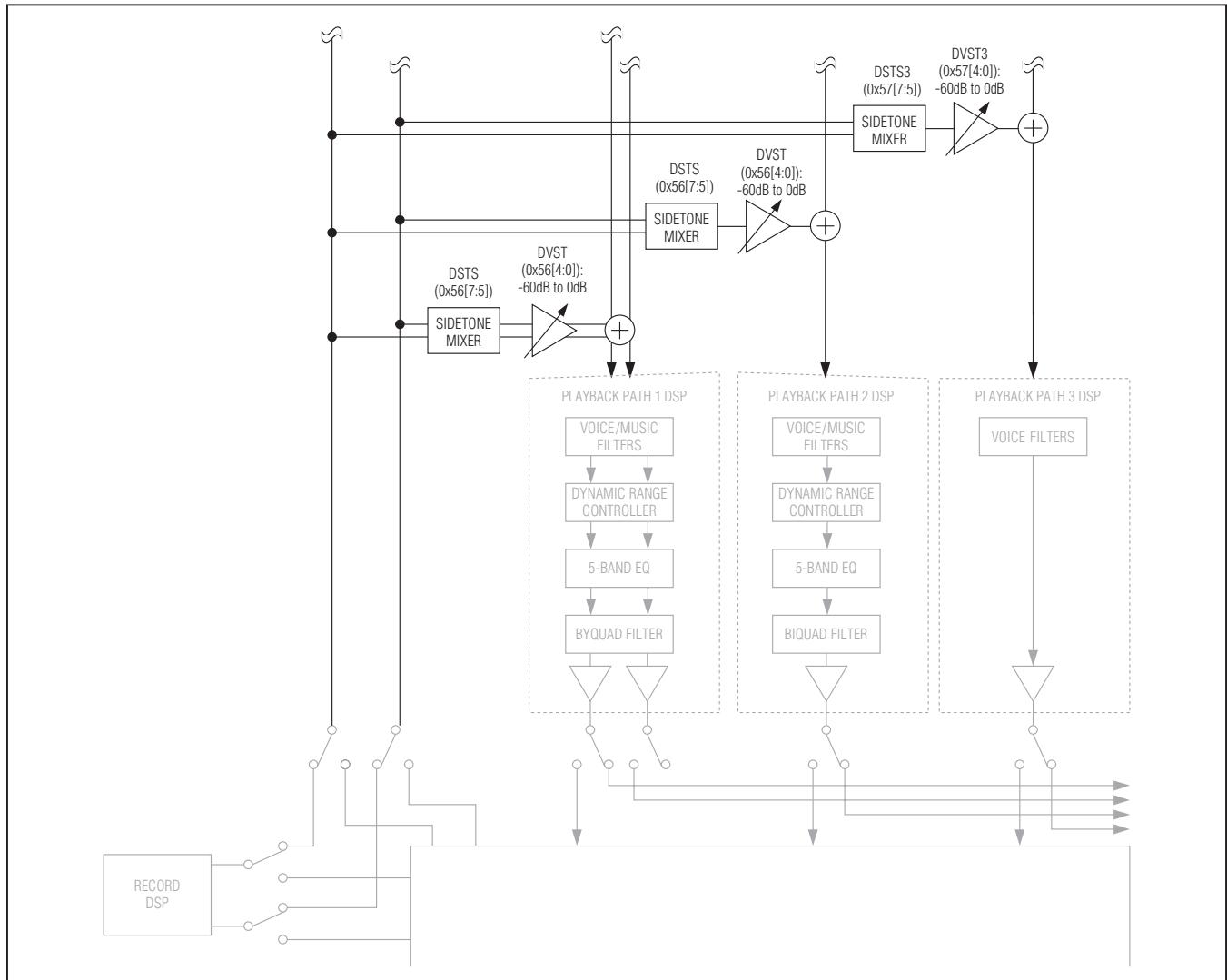

| Sidetone . . . . .                                       | 81  |

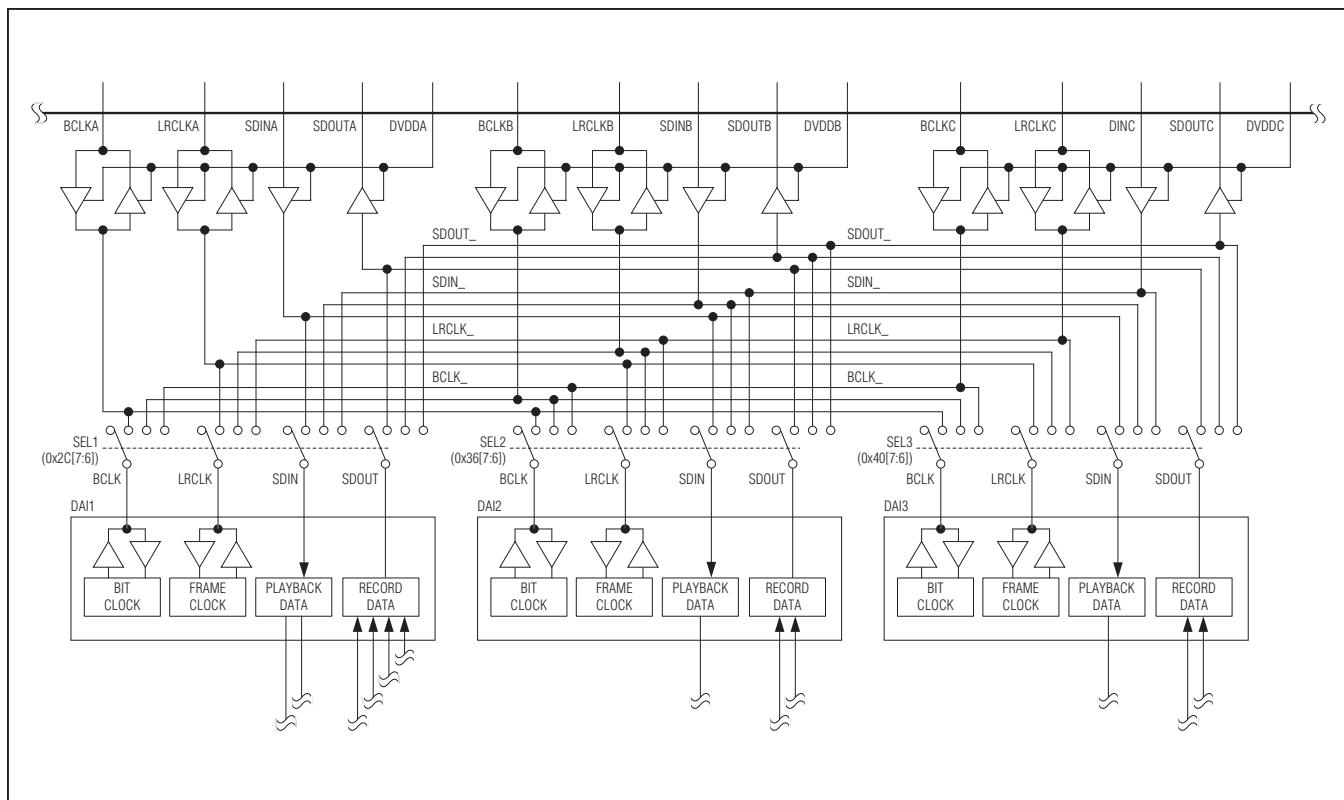

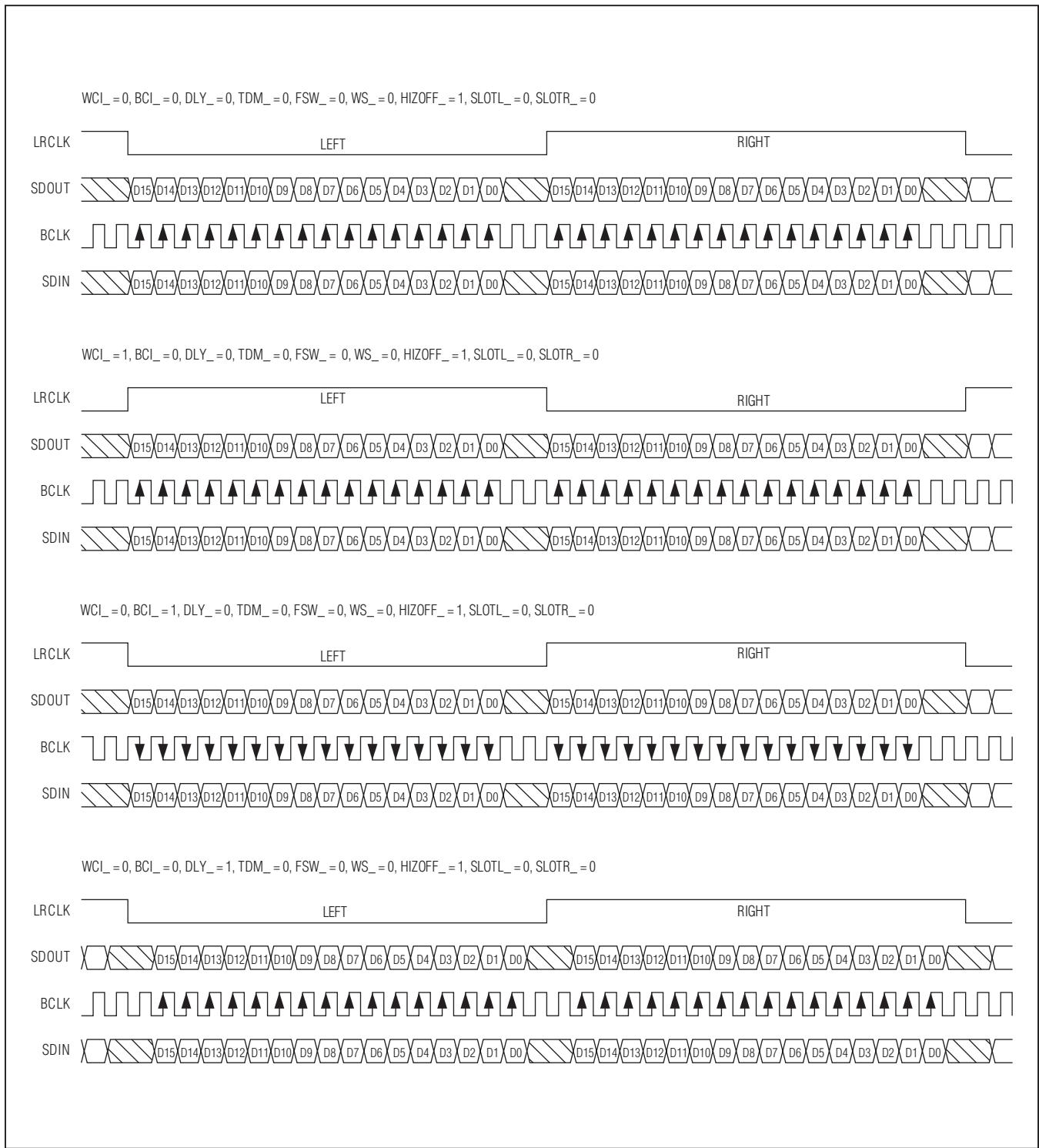

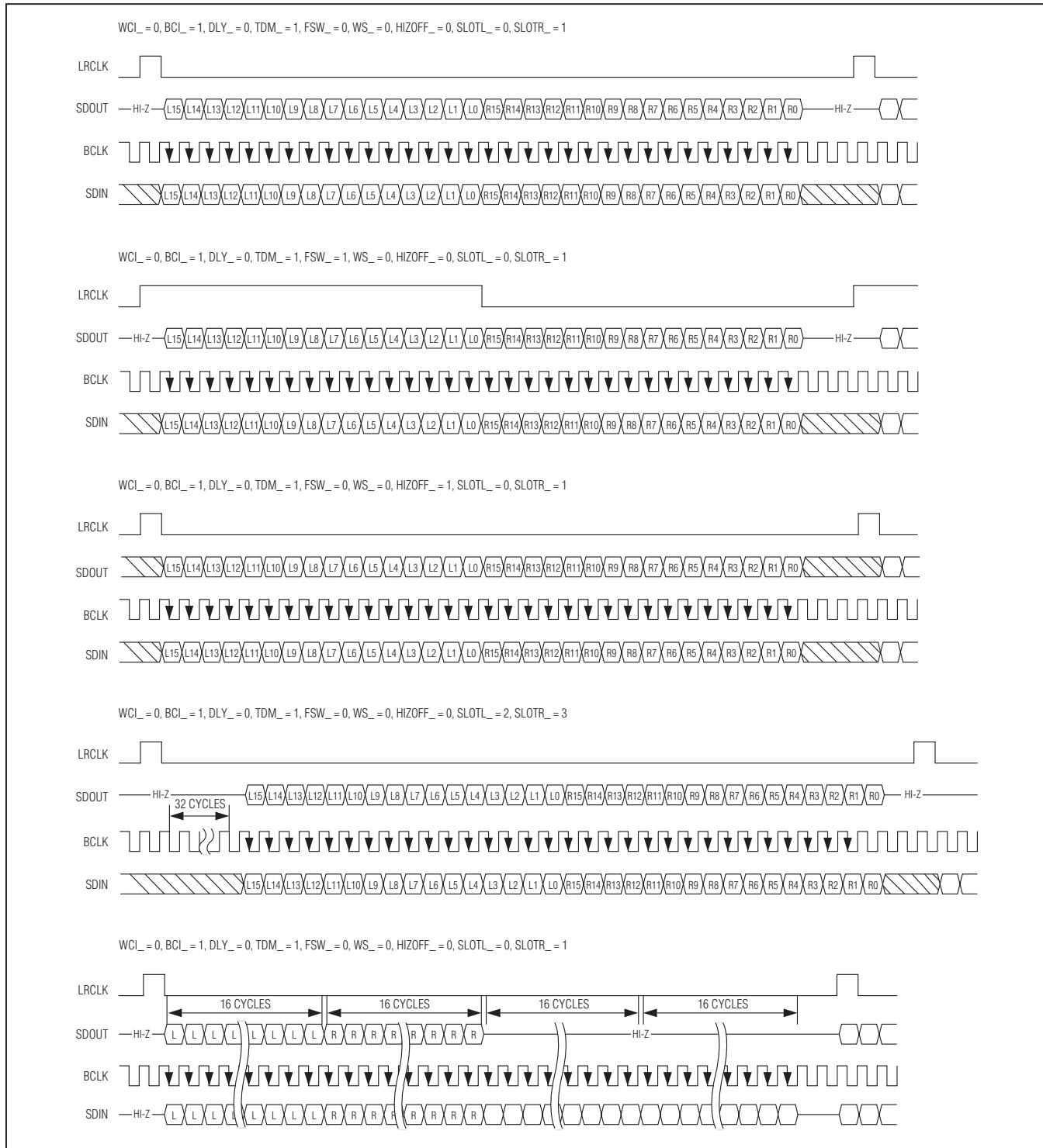

| Digital Audio Interfaces . . . . .                       | 82  |

| Clock Control . . . . .                                  | 86  |

| Digital Signal Routing . . . . .                         | 87  |

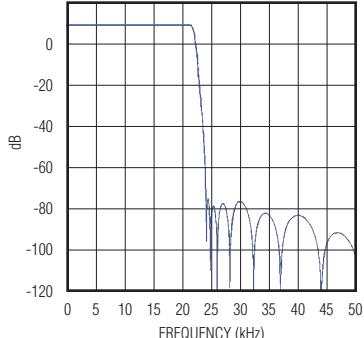

| Sample Rate Converter . . . . .                          | 87  |

| Playback Path Signal Processing (Playback DSP) . . . . . | 89  |

| Selectable Highpass Filtering . . . . .                  | 89  |

| Dynamic Range Control (DRC) . . . . .                    | 92  |

| Parametric Equalizer . . . . .                           | 94  |

| Biquad Filters . . . . .                                 | 95  |

| Headphone and Speaker Expander . . . . .                 | 96  |

| FlexSound System . . . . .                               | 96  |

| FlexSound Processor Usage Models . . . . .               | 96  |

| FlexSound Processor . . . . .                            | 96  |

| Control Interface . . . . .                              | 98  |

| Register Access . . . . .                                | 98  |

| Analog Feedback . . . . .                                | 98  |

| Code Protection . . . . .                                | 99  |

| FlexSound Processor Clock . . . . .                      | 99  |

| Receiver Amplifier . . . . .                             | 99  |

| Receiver Output Mixer . . . . .                          | 100 |

| Speaker Amplifiers . . . . .                             | 100 |

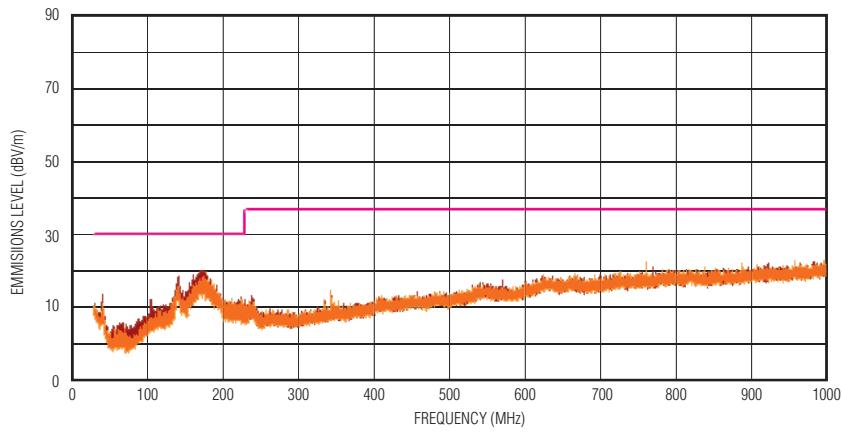

| Ultra-Low EMI Filterless Output Stage . . . . .          | 102 |

| Speaker Output Mixers . . . . .                          | 102 |

| Headphone Amplifier . . . . .                            | 103 |

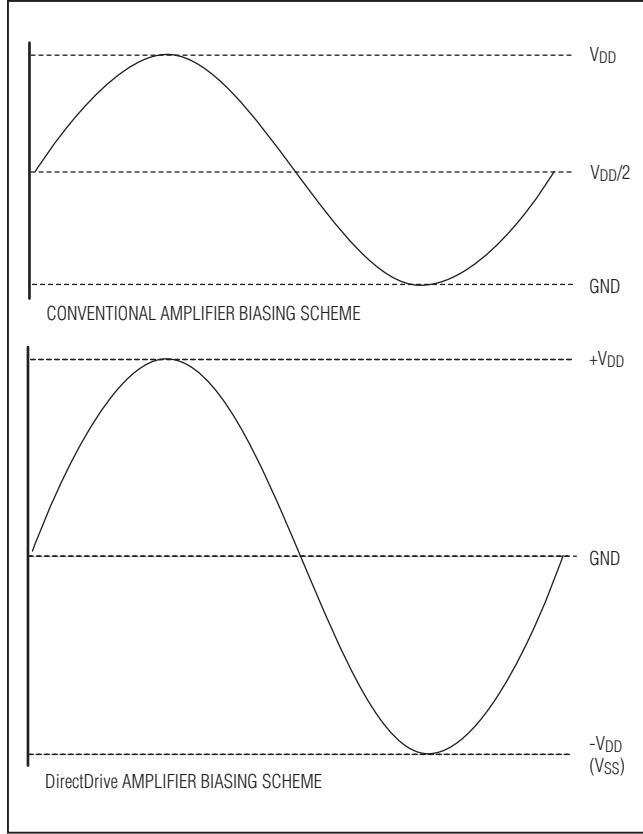

| DirectDrive Headphone Amplifier . . . . .                | 103 |

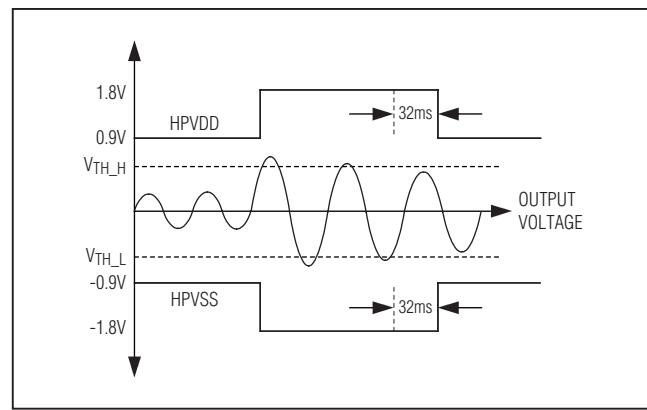

| Class H Operation . . . . .                              | 103 |

| Charge Pump . . . . .                                    | 103 |

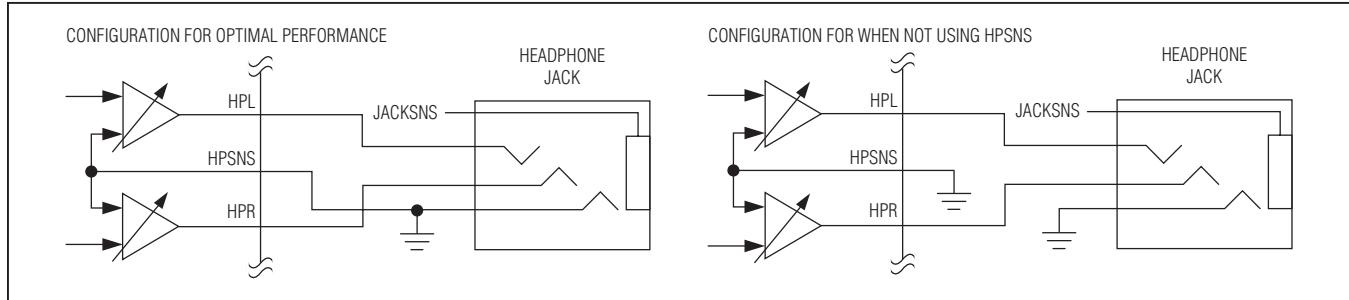

| Headphone Ground Sense (HPSNS) . . . . .                 | 104 |

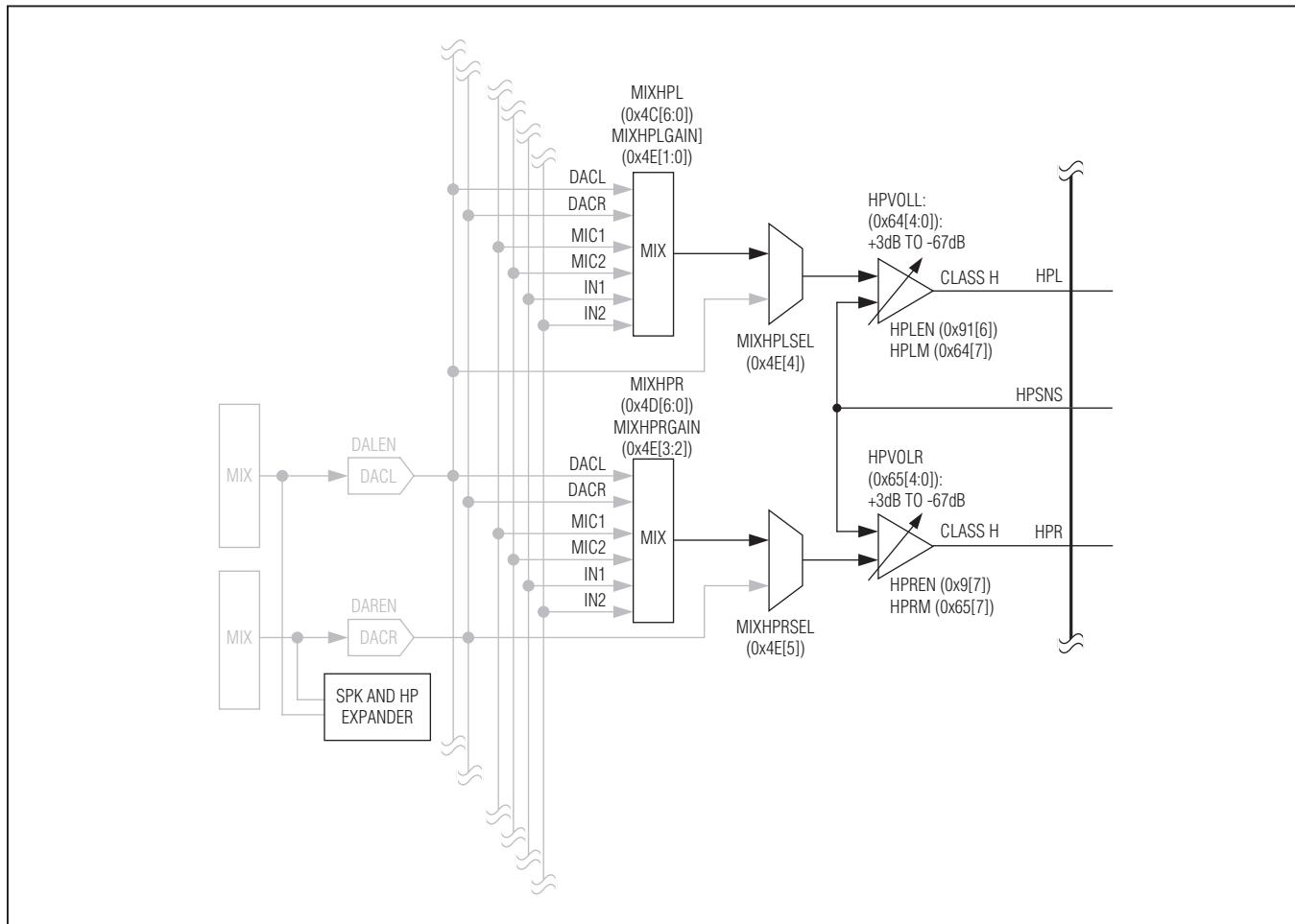

| Headphone Output Mixers . . . . .                        | 105 |

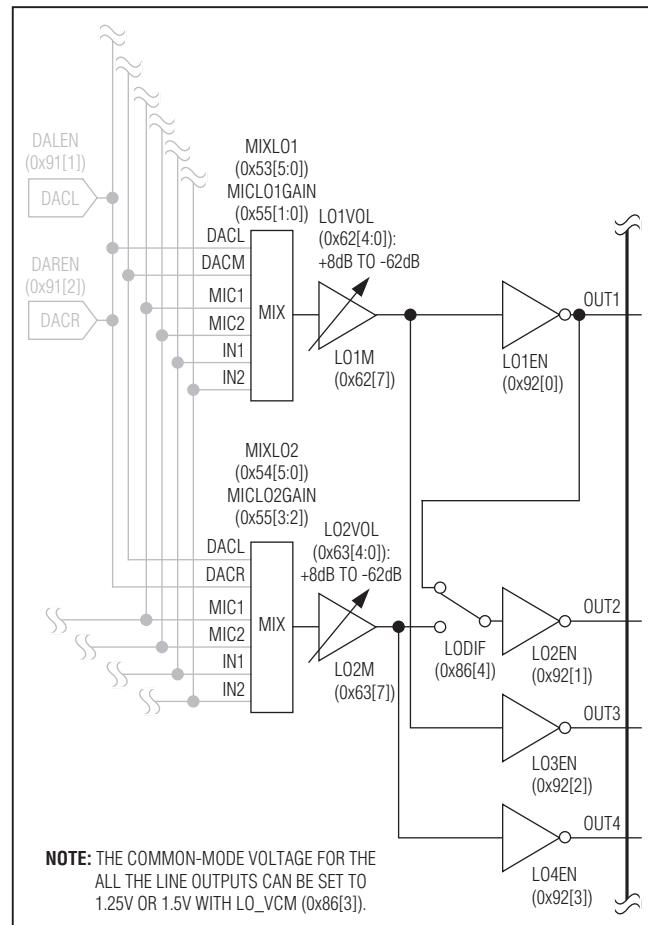

| Line Output Amplifier . . . . .                          | 105 |

| Line Output Mixer . . . . .                              | 106 |

| Click-and-Pop Reduction . . . . .                        | 106 |

| Accessory Detection . . . . .                            | 107 |

# Audio Hub with Wideband FlexSound Processor

---

## TABLE OF CONTENTS (continued)

---

|                                                                |     |

|----------------------------------------------------------------|-----|

| Jack Insertion Testing .....                                   | 108 |

| Detecting Jack Removal .....                                   | 108 |

| Power Modes .....                                              | 108 |

| Key-Switch Encoder .....                                       | 108 |

| Key-Switch Encoder Timing .....                                | 108 |

| Single Button, Hook-Switch/MIC Switch .....                    | 109 |

| Passive Multibutton Headset (MBH) .....                        | 109 |

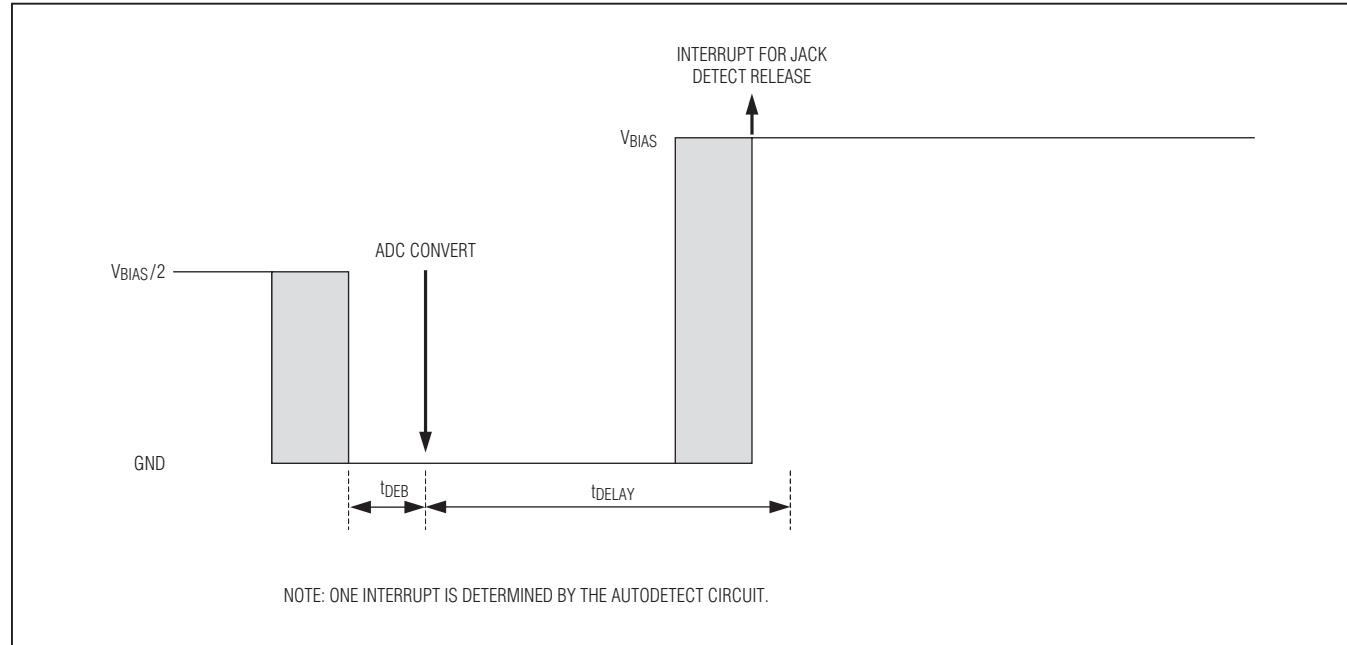

| Slow Jack Removal .....                                        | 112 |

| Interrupt ( $\overline{IRQ}$ ) .....                           | 112 |

| Control Interface .....                                        | 113 |

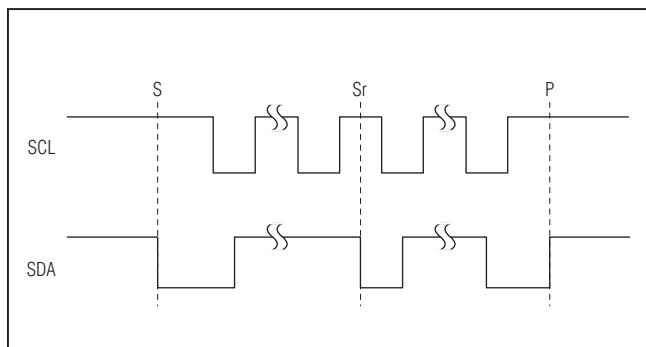

| I <sup>2</sup> C Serial Interface .....                        | 113 |

| Bit Transfer .....                                             | 114 |

| START and STOP Conditions .....                                | 114 |

| Early STOP Conditions .....                                    | 114 |

| Slave Address .....                                            | 114 |

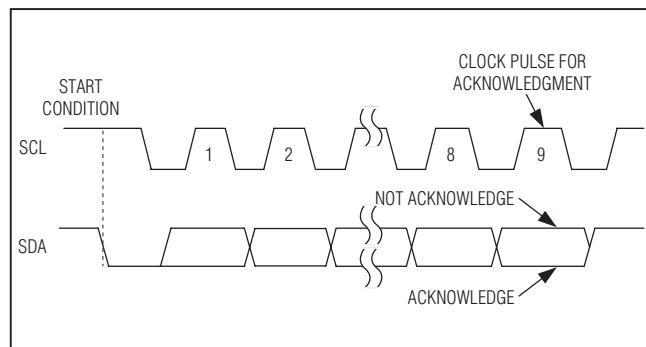

| Acknowledge .....                                              | 114 |

| Write Data Format .....                                        | 115 |

| Read Data Format .....                                         | 115 |

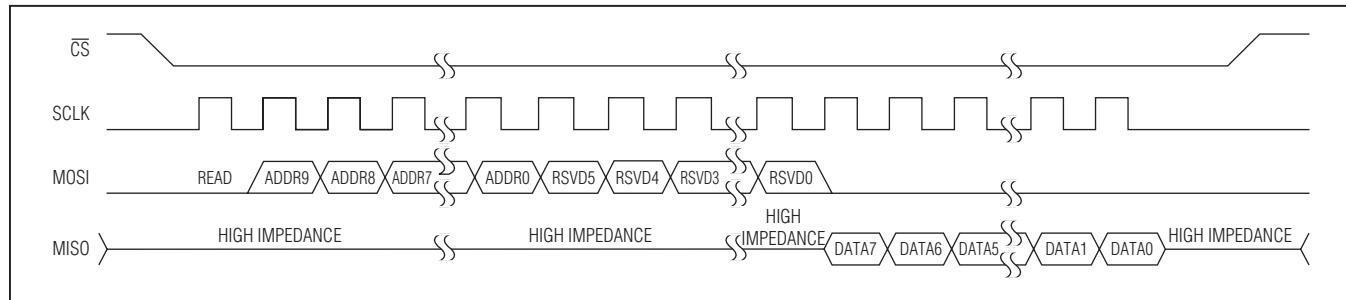

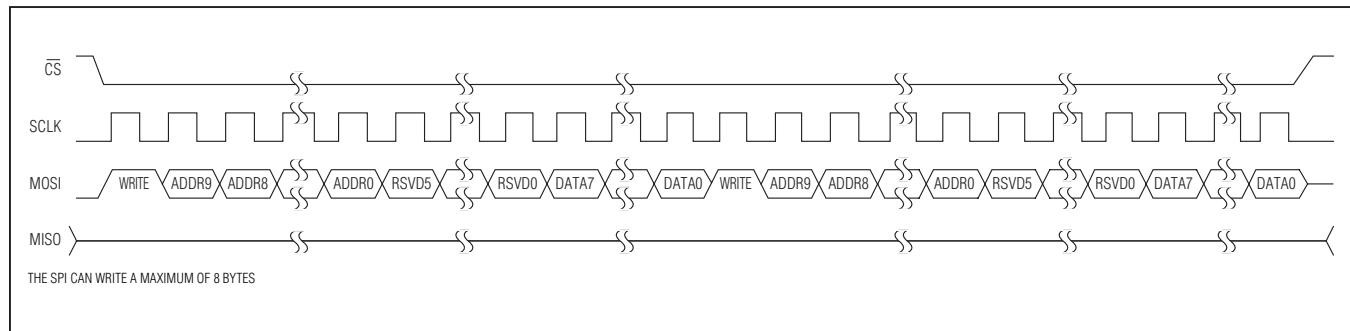

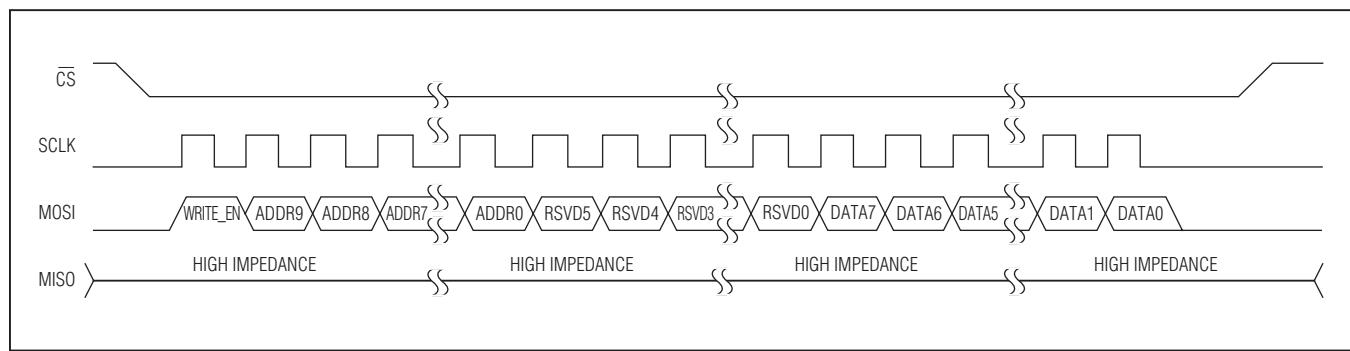

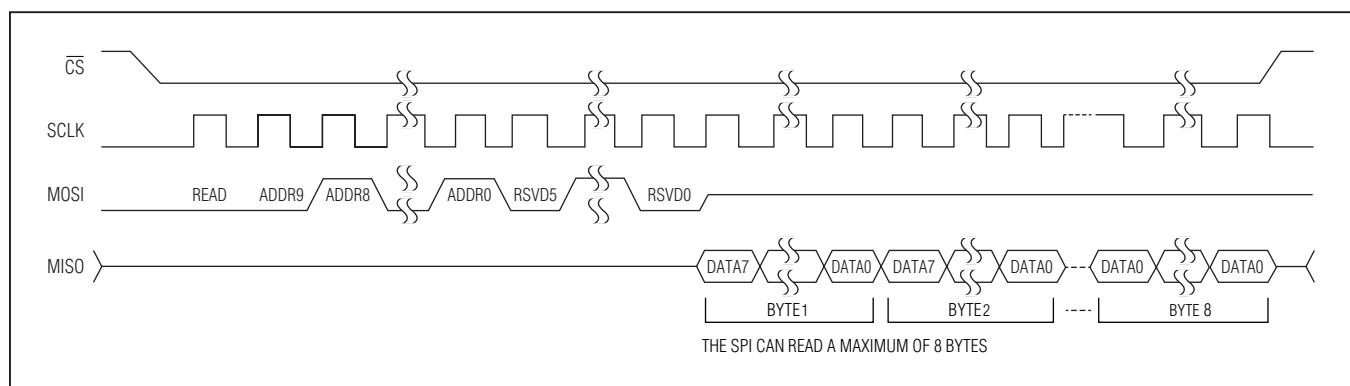

| Serial Peripheral Interface (SPI) .....                        | 116 |

| Serial Clock (SCLK) .....                                      | 116 |

| Chip Select ( $\overline{CS}$ ) .....                          | 116 |

| Write Format .....                                             | 117 |

| Read Format .....                                              | 117 |

| Applications Information .....                                 | 120 |

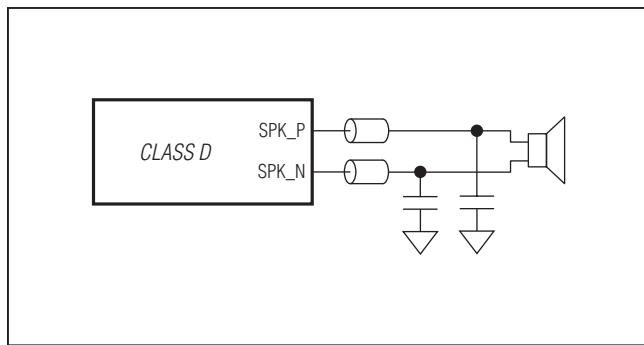

| Filterless Class D Operation .....                             | 120 |

| Power Sequence .....                                           | 120 |

| Startup/Shutdown Sequencing .....                              | 120 |

| Component Selection .....                                      | 123 |

| Optional Ferrite Bead Filter .....                             | 123 |

| Input Capacitor .....                                          | 123 |

| Charge-Pump Capacitor Selection .....                          | 123 |

| Charge-Pump Flying Capacitor ( $C_{C1P-C1N}$ ) .....           | 123 |

| Charge-Pump Holding Capacitor ( $C_{CPVDD}, C_{CPVSS}$ ) ..... | 123 |

| Ambient Temperature Sensor .....                               | 123 |

| Unused Pins .....                                              | 124 |

# Audio Hub with Wideband FlexSound Processor

---

## TABLE OF CONTENTS (continued)

---

|                                               |     |

|-----------------------------------------------|-----|

| Supply Bypassing, Layout, and Grounding ..... | 124 |

| Use Cases .....                               | 125 |

| Recording a Voice Call with Music .....       | 125 |

| Recording a Blue Tooth Call with Music .....  | 125 |

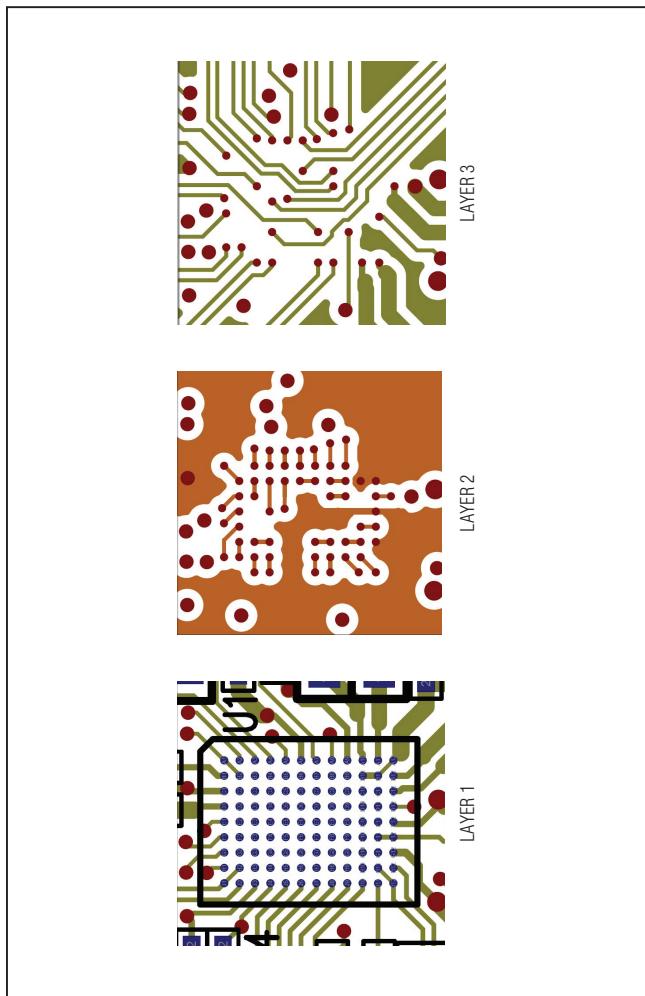

| Recommended PCB Routing .....                 | 125 |

| RF Susceptibility .....                       | 125 |

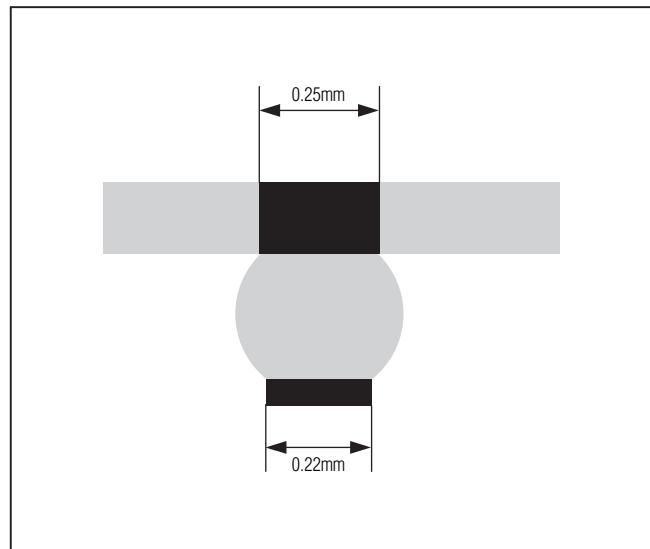

| WLP Applications Information .....            | 125 |

| Ordering Information .....                    | 128 |

| Package Information .....                     | 129 |

| Revision History .....                        | 130 |

---

## LIST OF FIGURES

---

|                                                                                            |    |

|--------------------------------------------------------------------------------------------|----|

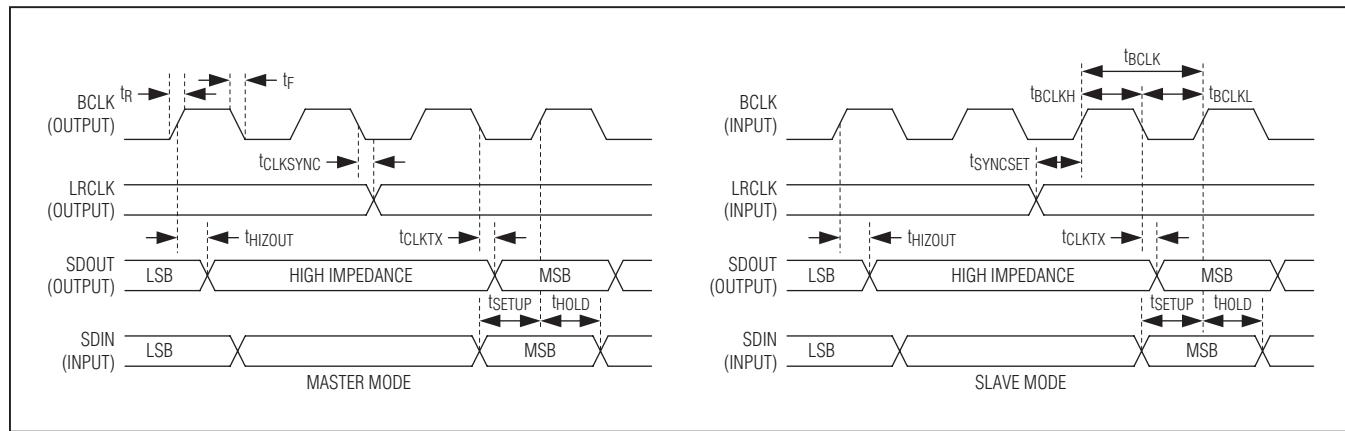

| Figure 1. Non-TDM Audio Interface Timing Diagrams (TDM_ = 0) .....                         | 36 |

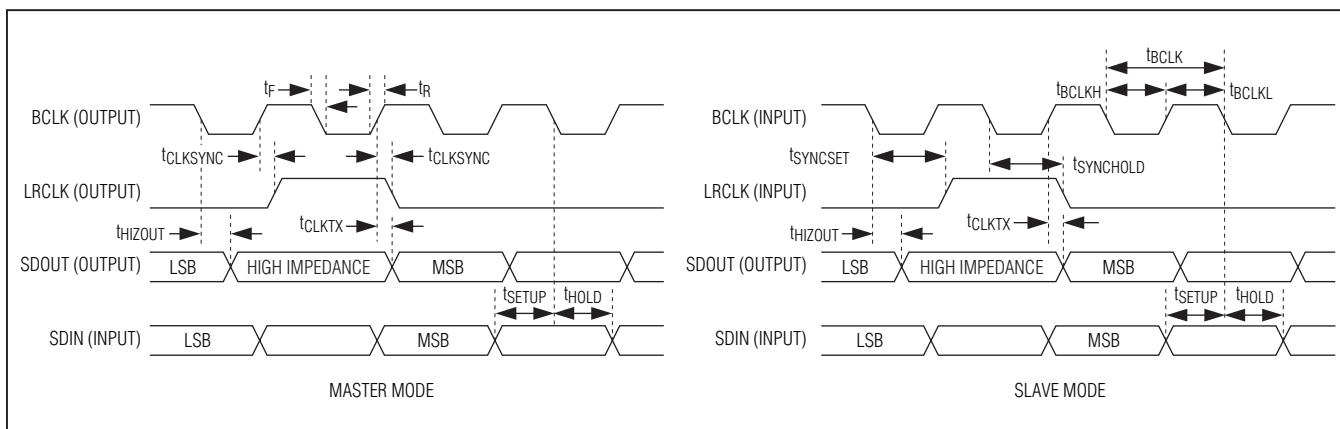

| Figure 2. TDM Audio Interface Timing Diagram (TDM_ = 1, FSW_ = 0) .....                    | 37 |

| Figure 3. TDM Audio Interface Timing Diagram (TDM_ = 1, FSW_ = 1) .....                    | 37 |

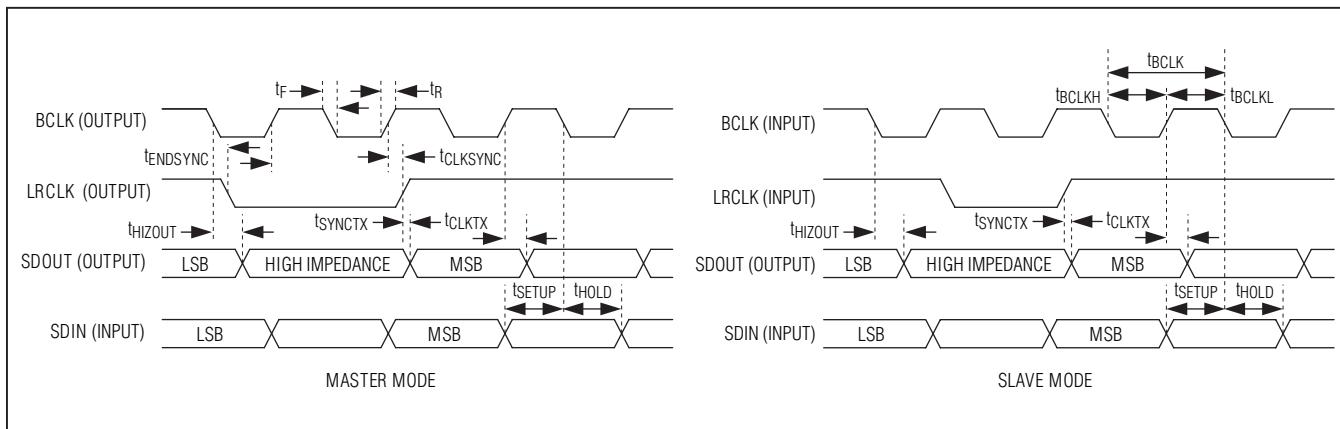

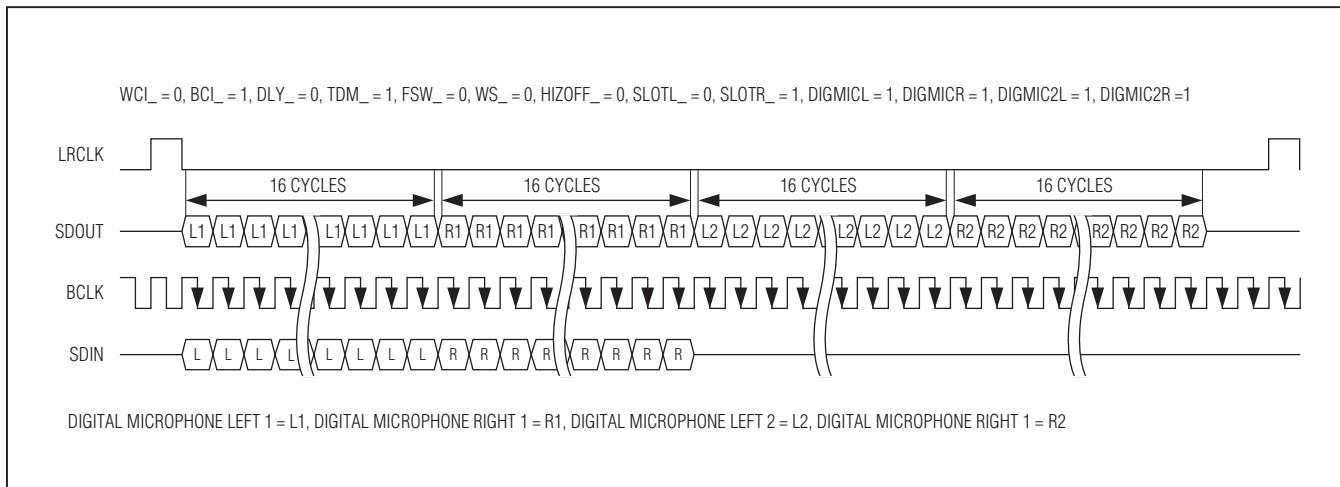

| Figure 4. Digital Microphone Timing Diagram .....                                          | 38 |

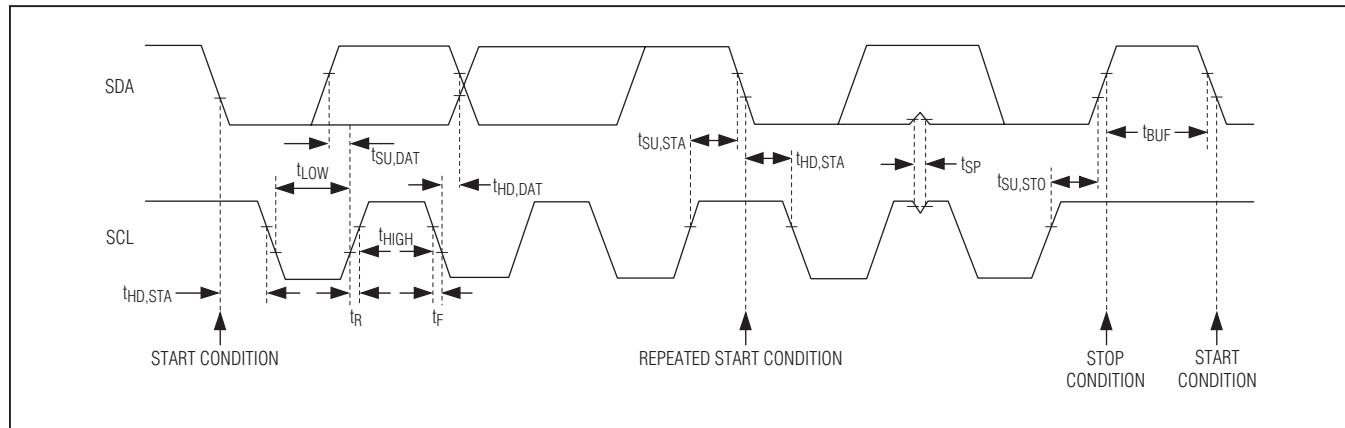

| Figure 5. I <sup>2</sup> C Interface Timing Diagram .....                                  | 39 |

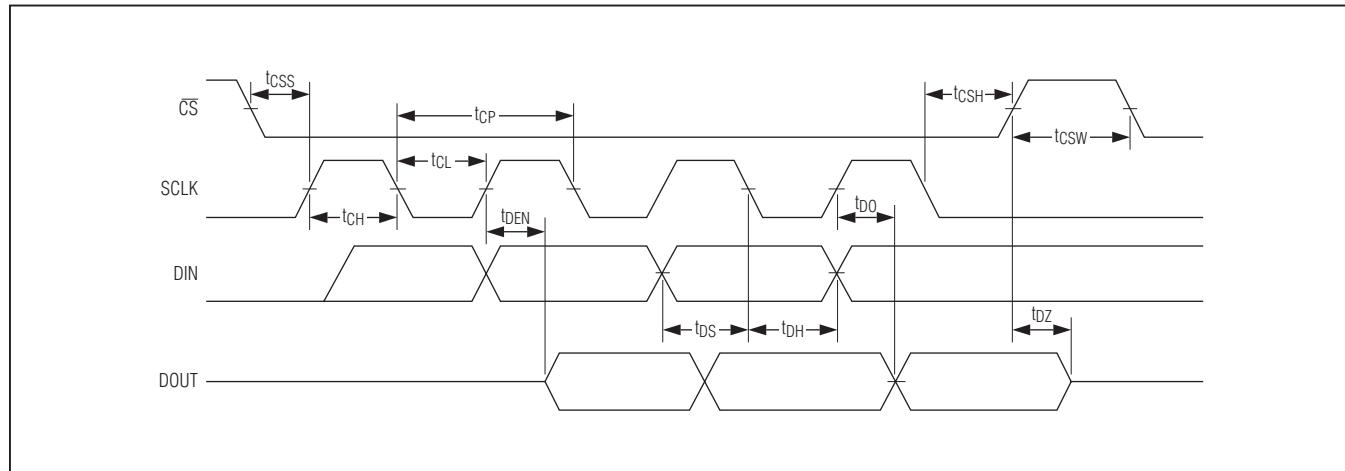

| Figure 6. SPI Interface Timing Diagram .....                                               | 40 |

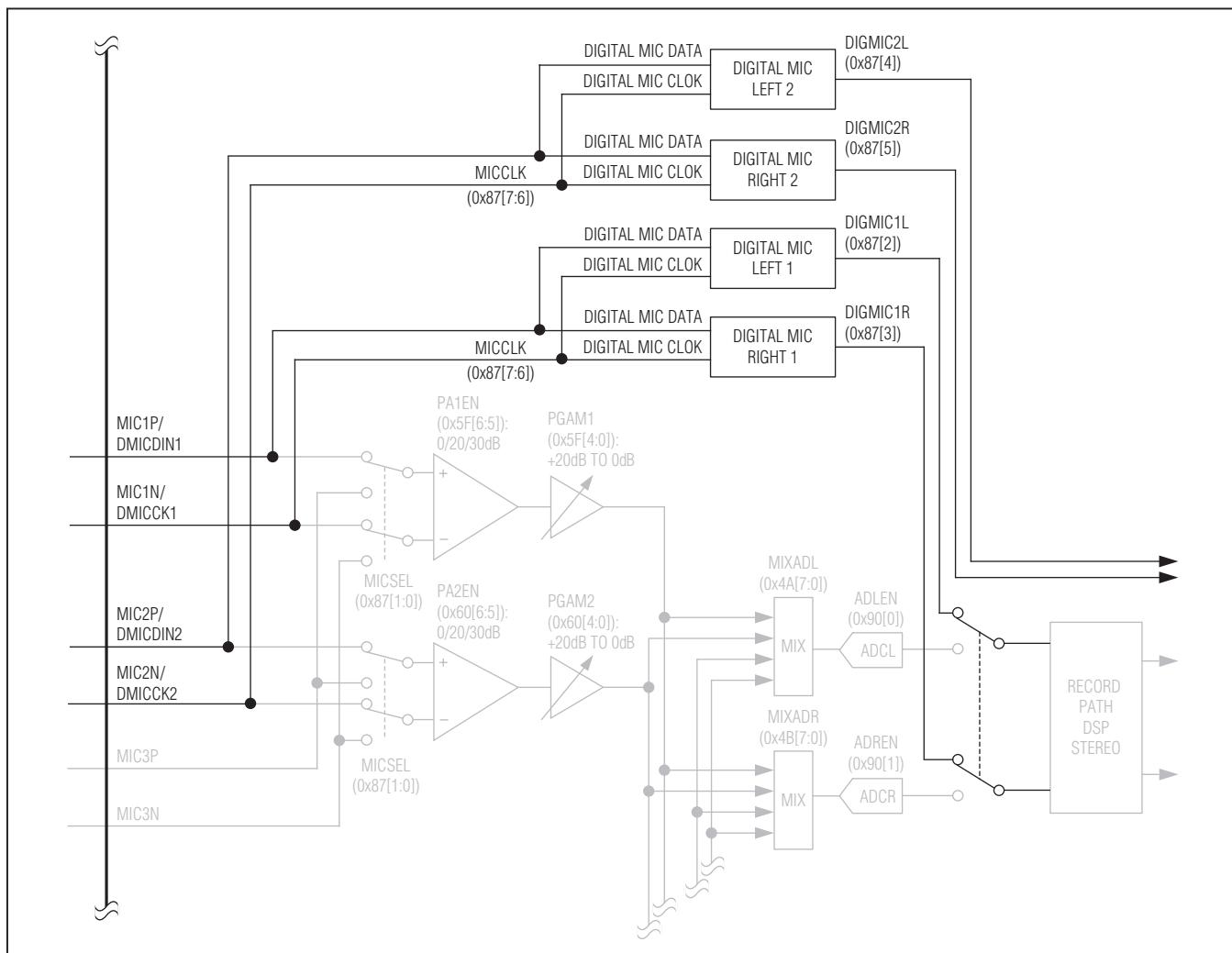

| Figure 7. Analog Microphone Block Diagram .....                                            | 77 |

| Figure 8. Digital Microphone Block Diagram .....                                           | 78 |

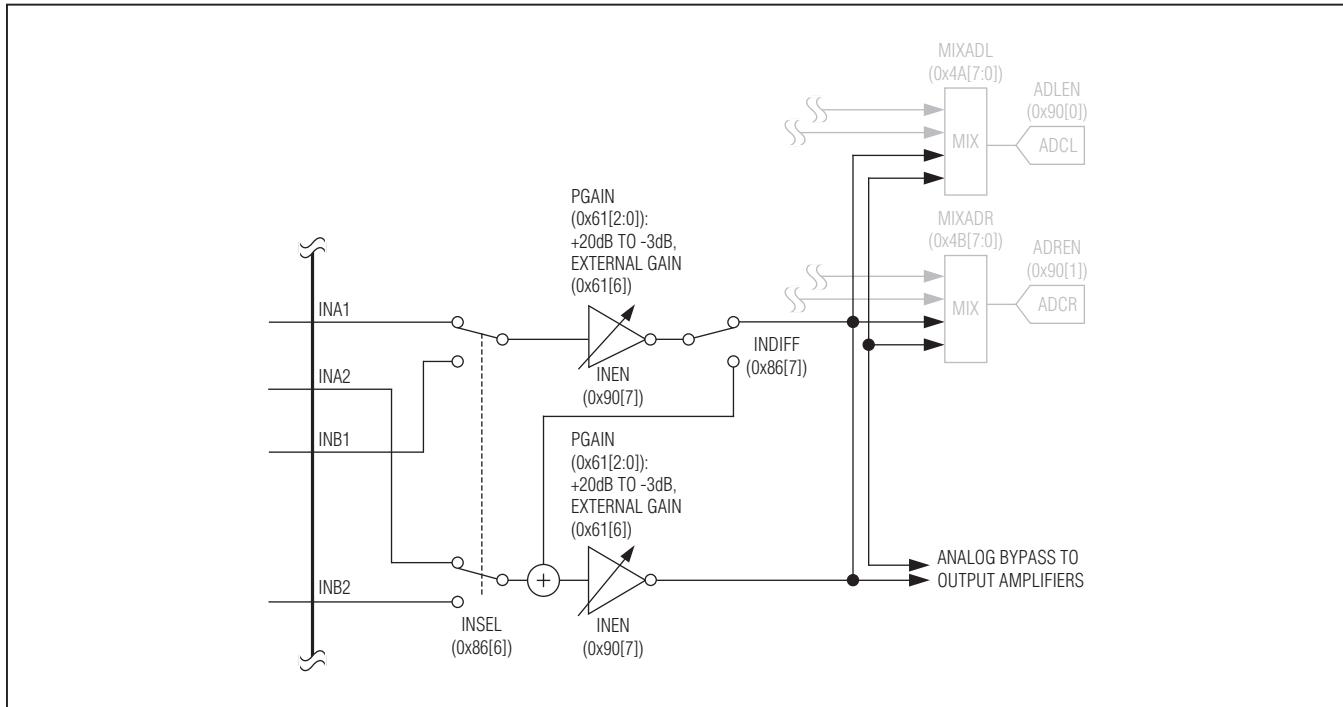

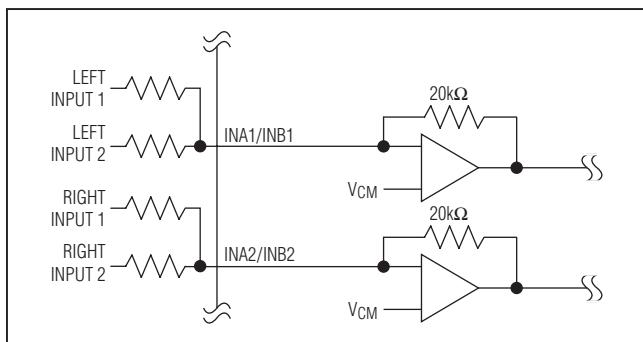

| Figure 9. Line Input Block Diagram .....                                                   | 79 |

| Figure 10. Summing Multiple Signals at the Line Inputs .....                               | 79 |

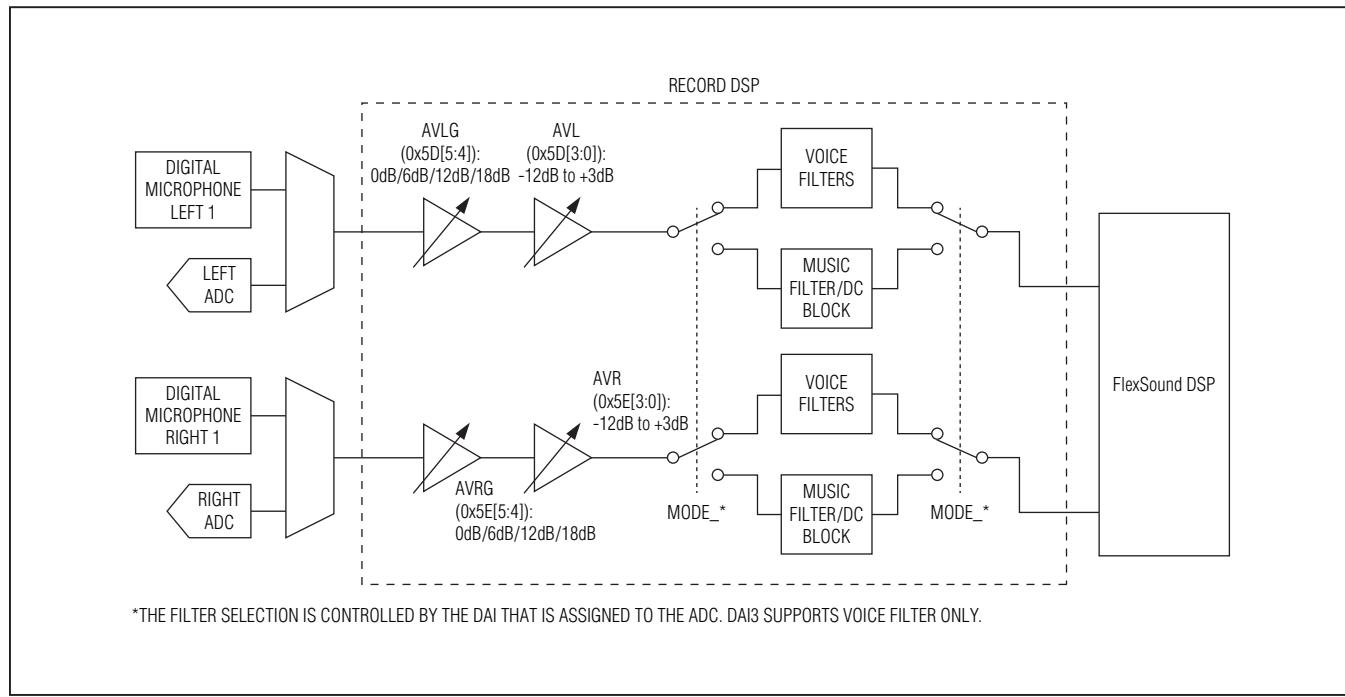

| Figure 11. Record Path Signal Processing .....                                             | 80 |

| Figure 12. Sidetone Block Diagram .....                                                    | 81 |

| Figure 13. Digital Audio Interfaces Block Diagram .....                                    | 82 |

| Figure 14. Non-TDM Data Format Examples .....                                              | 84 |

| Figure 15. TDM Mode Data Format Examples .....                                             | 85 |

| Figure 16. TDM Mode Data Format Examples (Cont.) .....                                     | 86 |

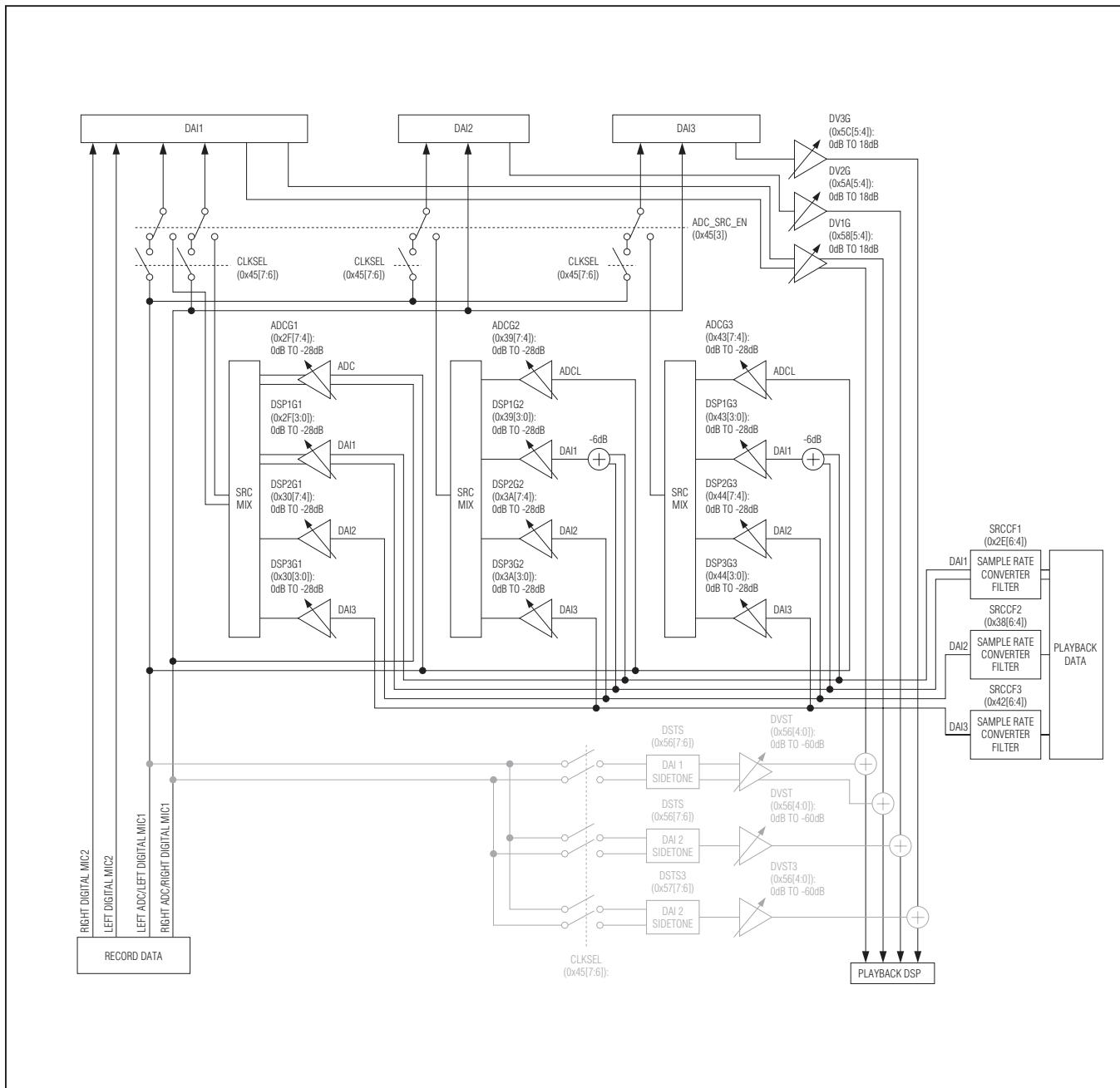

| Figure 17. Detailed Digital Signal Routing Diagram .....                                   | 88 |

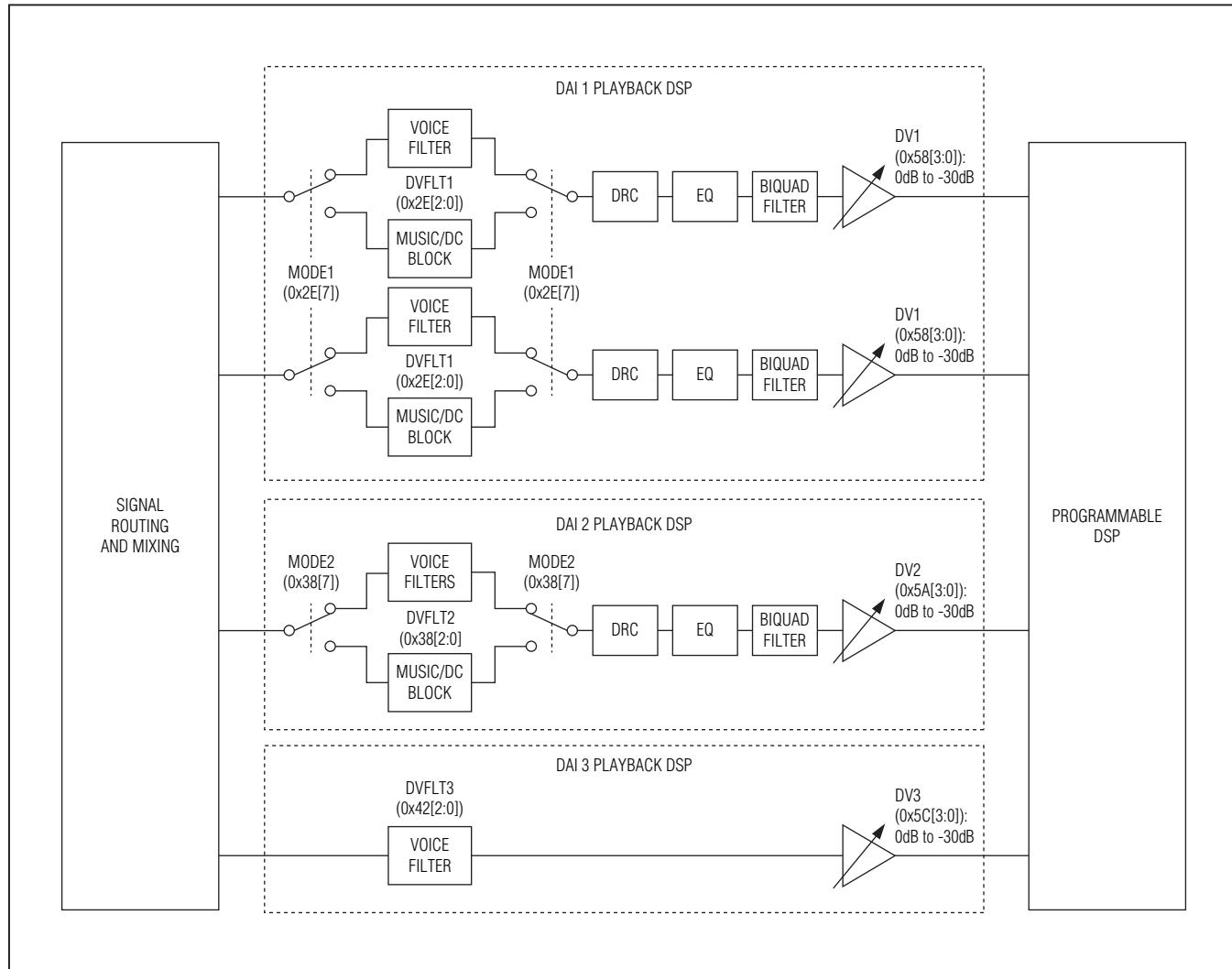

| Figure 18. Fixed Function Playback Signal Processing .....                                 | 89 |

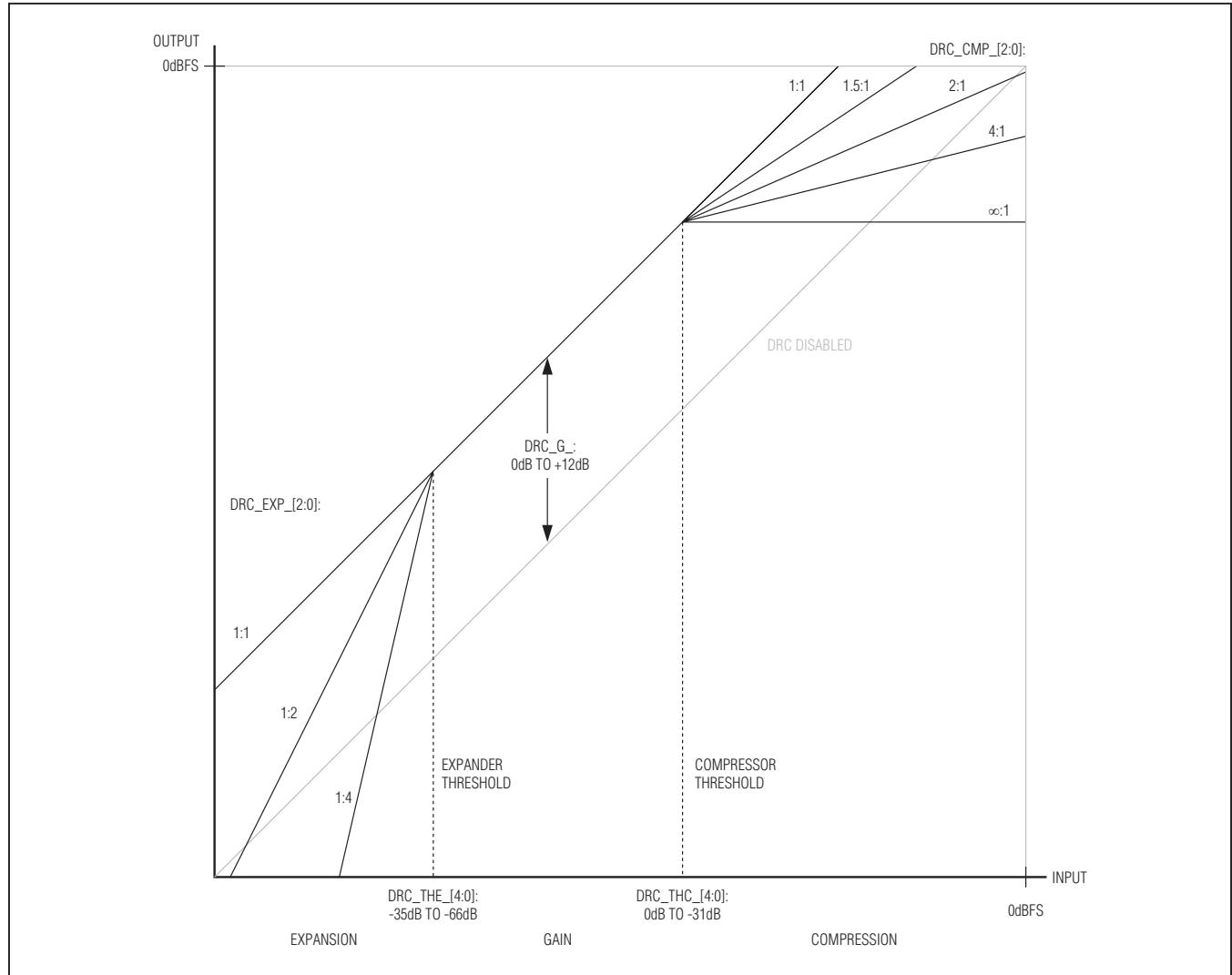

| Figure 19. DRC Gain Response .....                                                         | 92 |

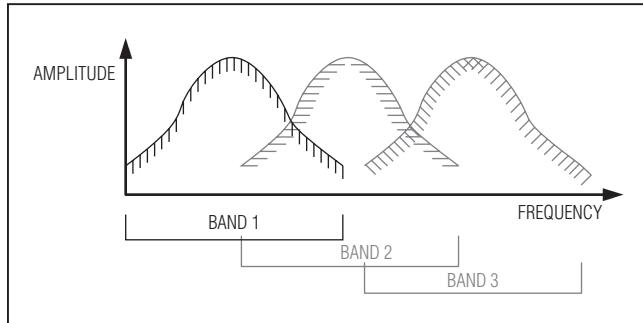

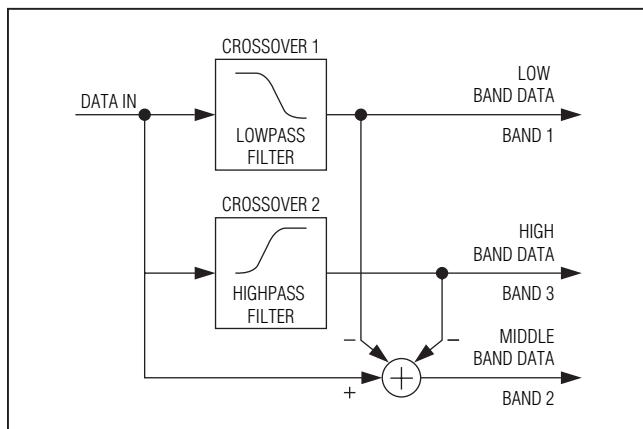

| Figure 20. DRC Three Bands .....                                                           | 93 |

| Figure 21. DRC 3-Band Crossover Filter .....                                               | 93 |

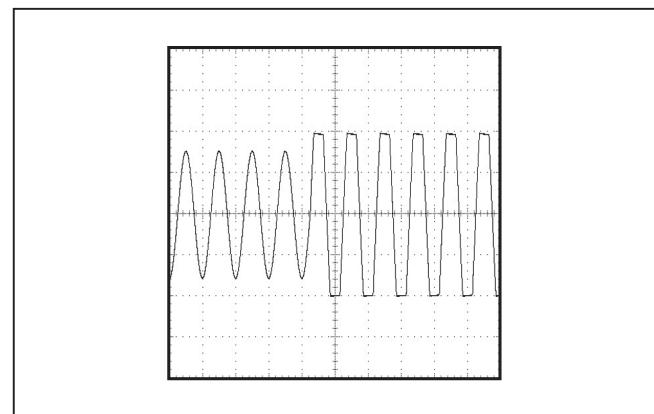

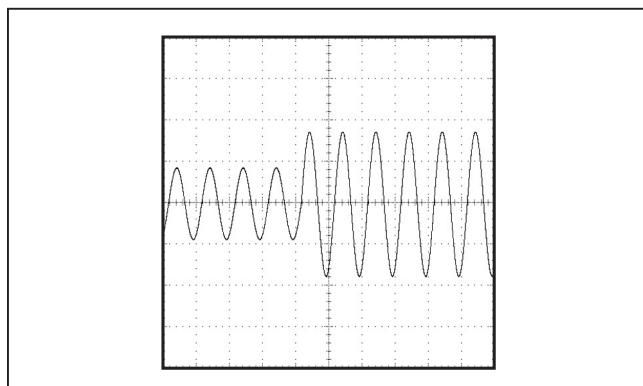

| Figure 22. Low-Signal to High-Signal Transition, No Clipping, Compressor Disabled .....    | 93 |

| Figure 23. Low-Signal to High-Signal Transition, Increased Gain, Compressor Disabled ..... | 93 |

# Audio Hub with Wideband FlexSound Processor

---

## LIST OF FIGURES (continued)

---

|                                                                                           |     |

|-------------------------------------------------------------------------------------------|-----|

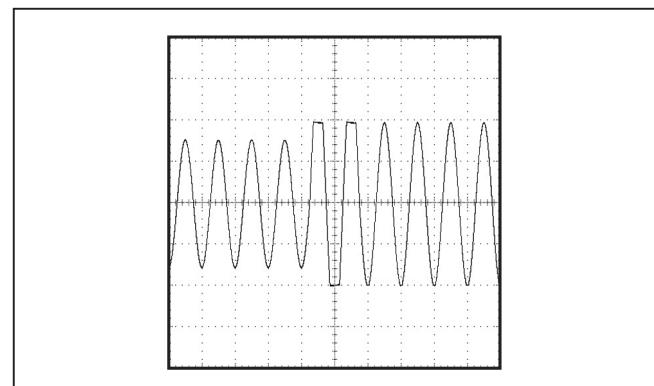

| Figure 24. Low-Signal to High-Signal Transition, Increased Gain, DRC Enabled .....        | 93  |

| Figure 25. High-Signal to Low-Signal Transition, Expander Disabled .....                  | 94  |

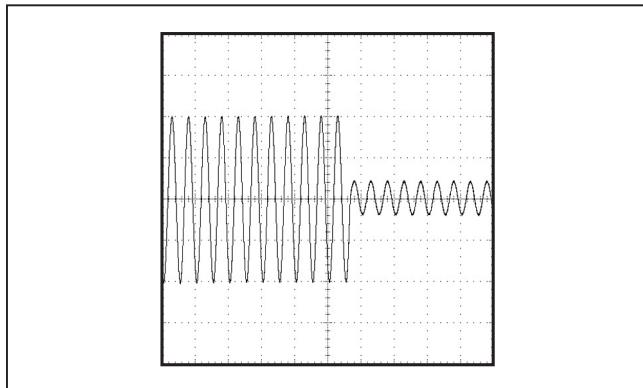

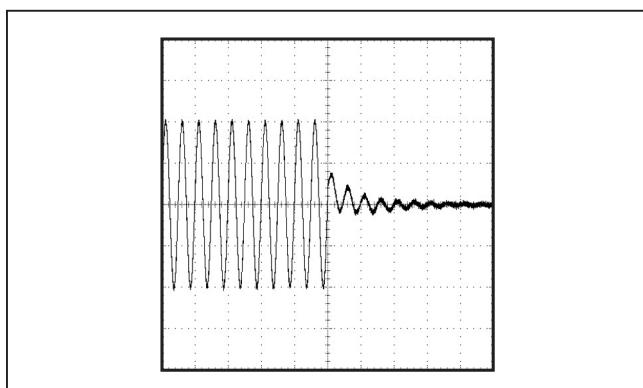

| Figure 26. High-Signal to Low-Signal Transition, Expander Enabled .....                   | 94  |

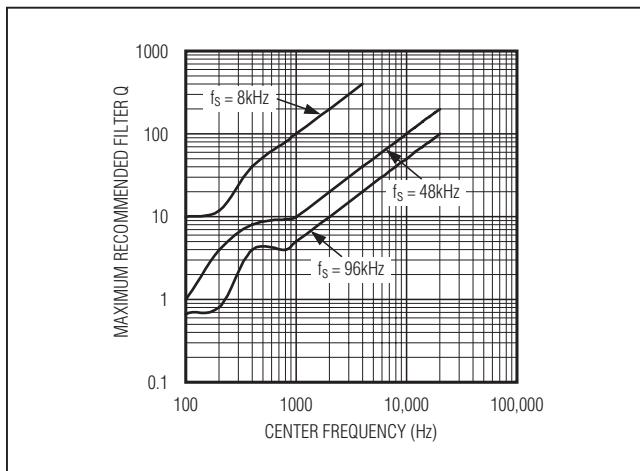

| Figure 27. Maximum Recommended Filter Q vs. Frequency .....                               | 95  |

| Figure 28. FlexSound Analog Feedback Block Diagram .....                                  | 98  |

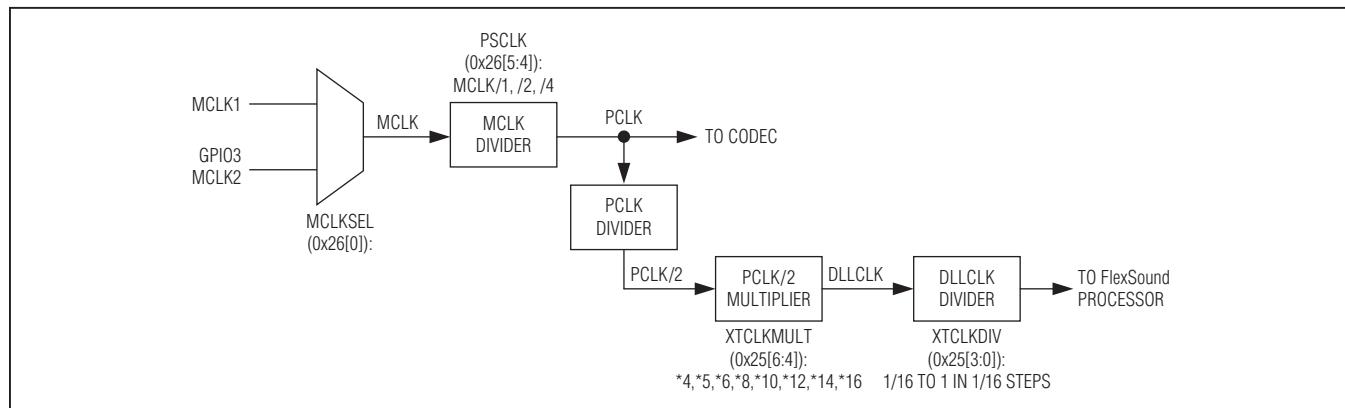

| Figure 29. FlexSound Processor Clock Detail Block Diagram .....                           | 99  |

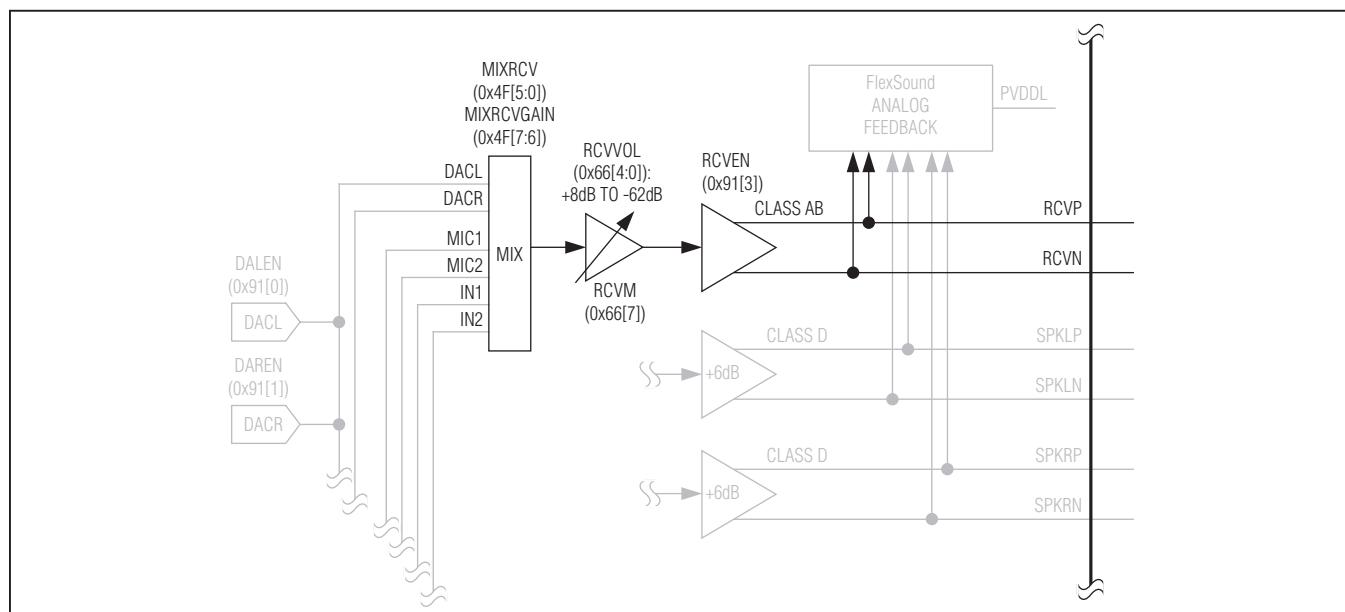

| Figure 30. Receiver Amplifier Block Diagram .....                                         | 99  |

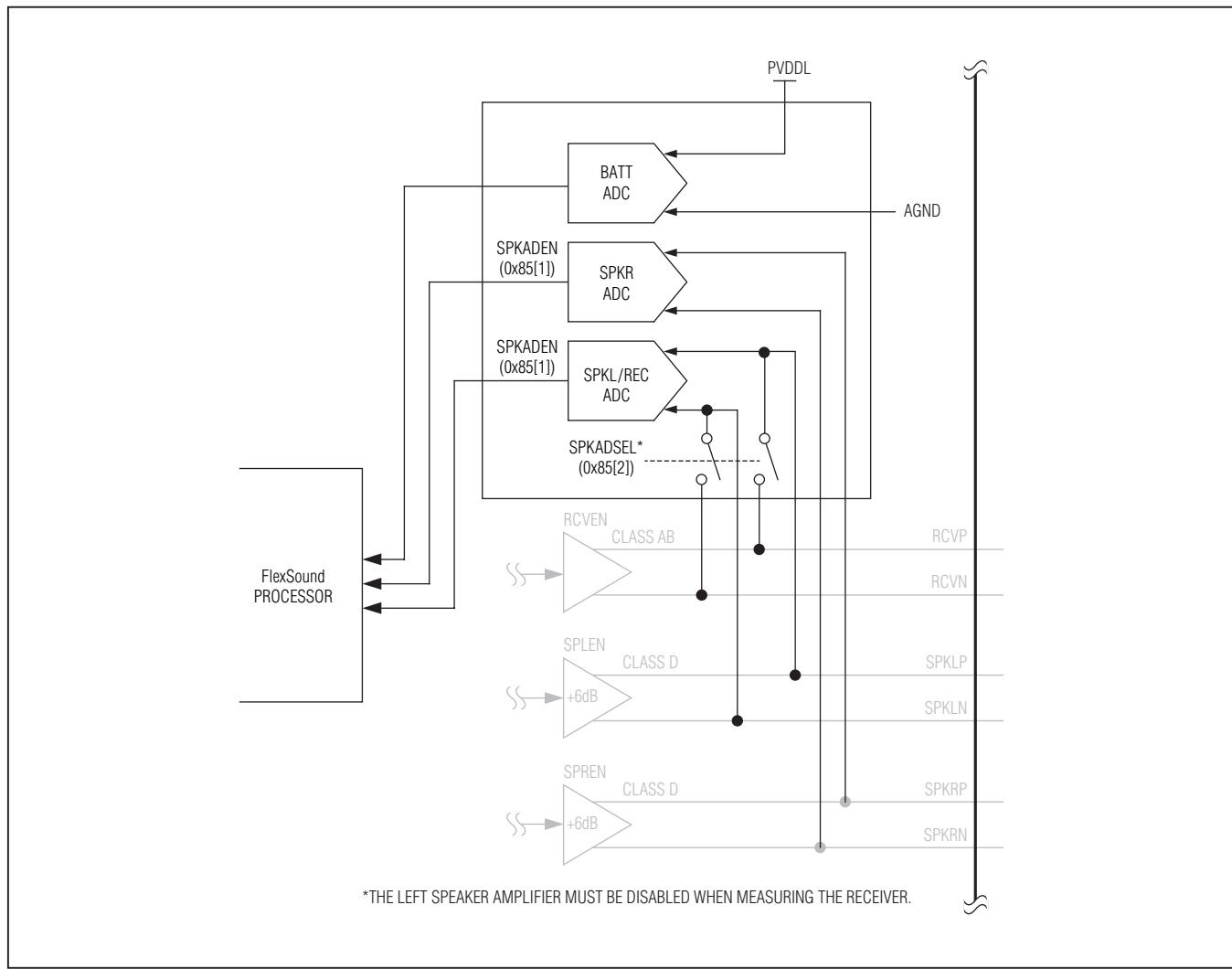

| Figure 31. Speaker Amplifier Block Diagram .....                                          | 101 |

| Figure 32. EMI with 30.2cm of Speaker Cable .....                                         | 102 |

| Figure 33. Traditional Amplifier Output vs. DirectDrive Output .....                      | 103 |

| Figure 34. Class H Operation .....                                                        | 103 |

| Figure 35. HPSNS Configuration .....                                                      | 104 |

| Figure 36. Headphone Amplifier Block Diagram .....                                        | 104 |

| Figure 37. Line Output Block Diagram .....                                                | 105 |

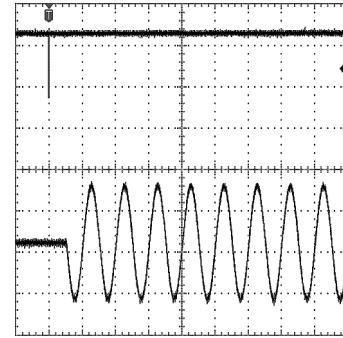

| Figure 38. Zero-Crossing Detection Enabled .....                                          | 106 |

| Figure 39. Zero-Crossing Detection Disabled .....                                         | 106 |

| Figure 40. Volume Slew Enabled .....                                                      | 107 |

| Figure 41. Volume Slew Disabled .....                                                     | 107 |

| Figure 42. Passive Single Button Hookswitch .....                                         | 109 |

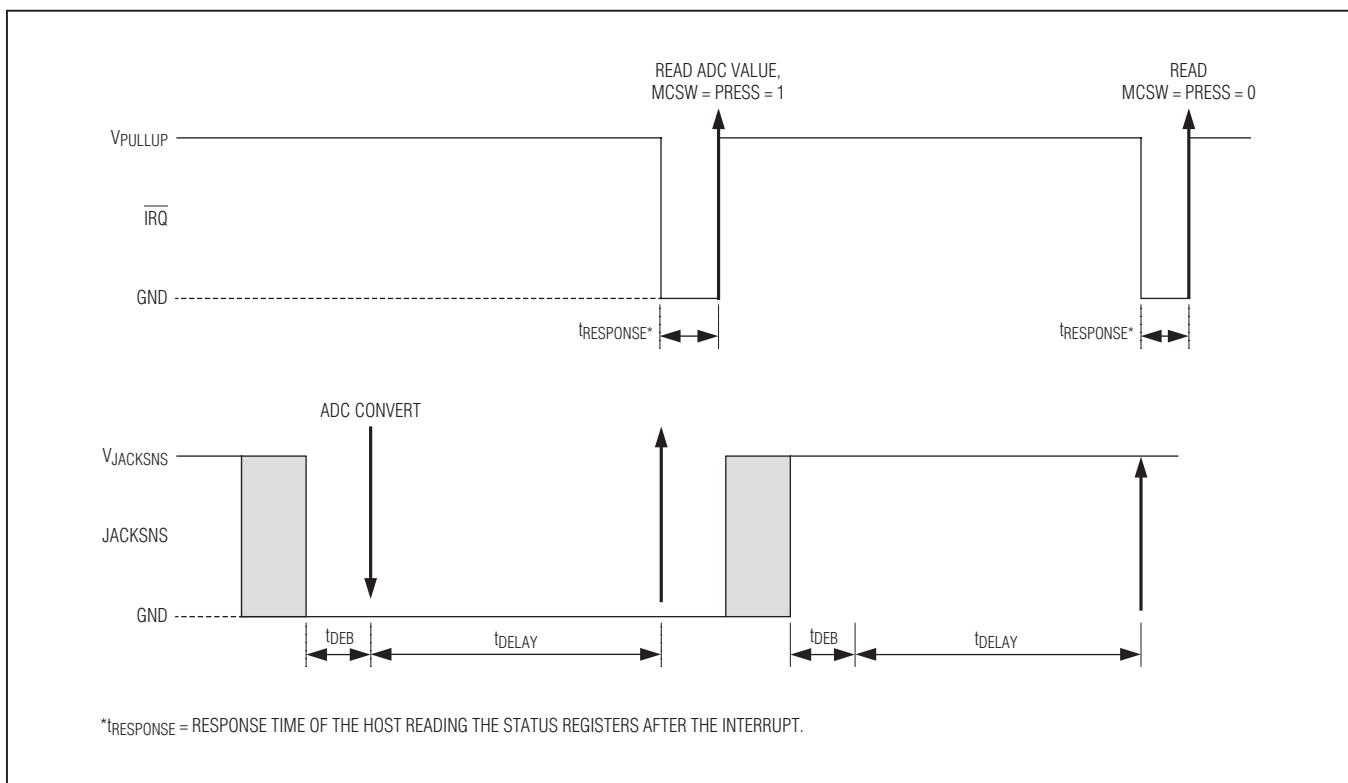

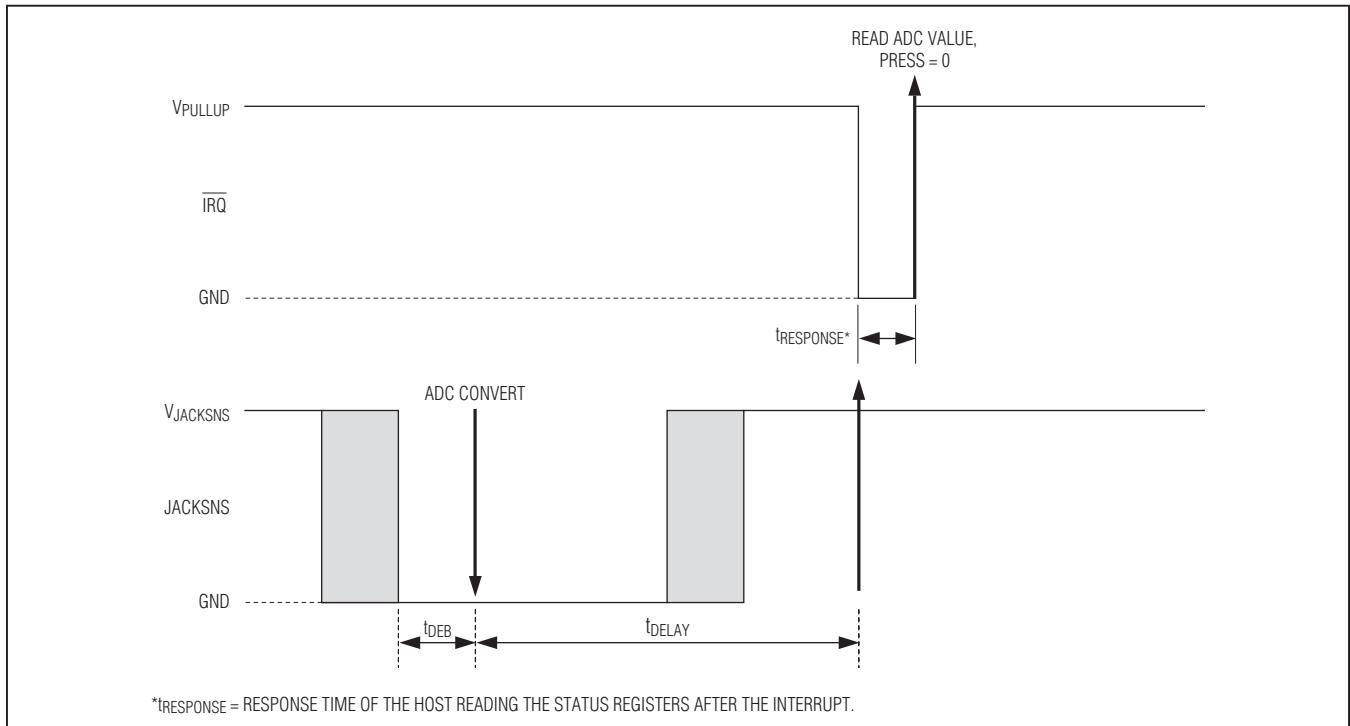

| Figure 43. Single Hook Switch/Mic Switch Timing $t_{DELAY}$ .....                         | 109 |

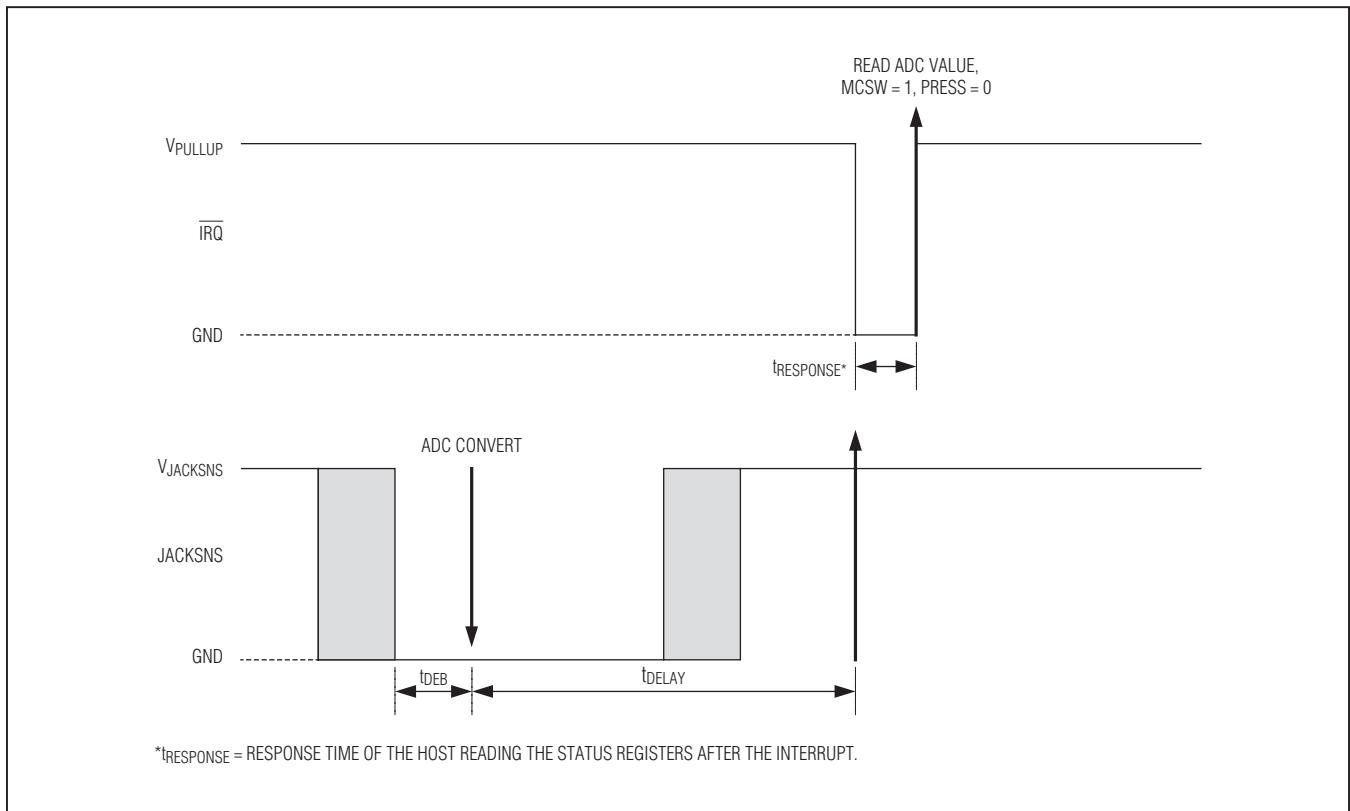

| Figure 44. Single Hook Switch/Mic Switch Timing $t_{DELAY}$ .....                         | 110 |

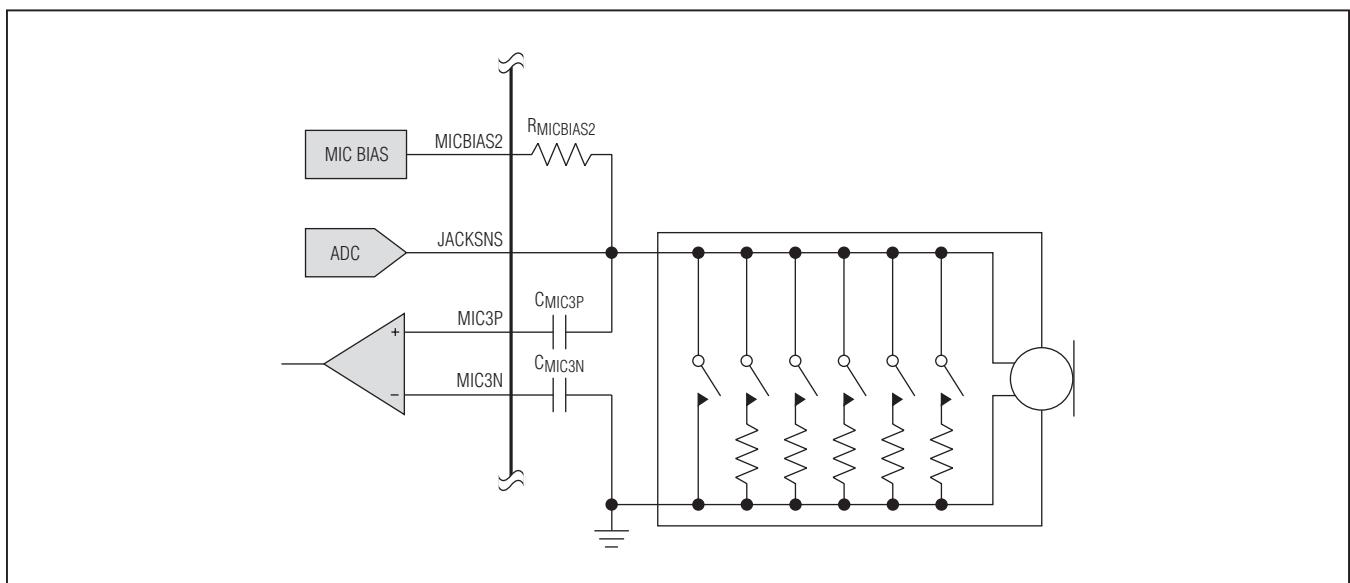

| Figure 45. Passive MBH .....                                                              | 110 |

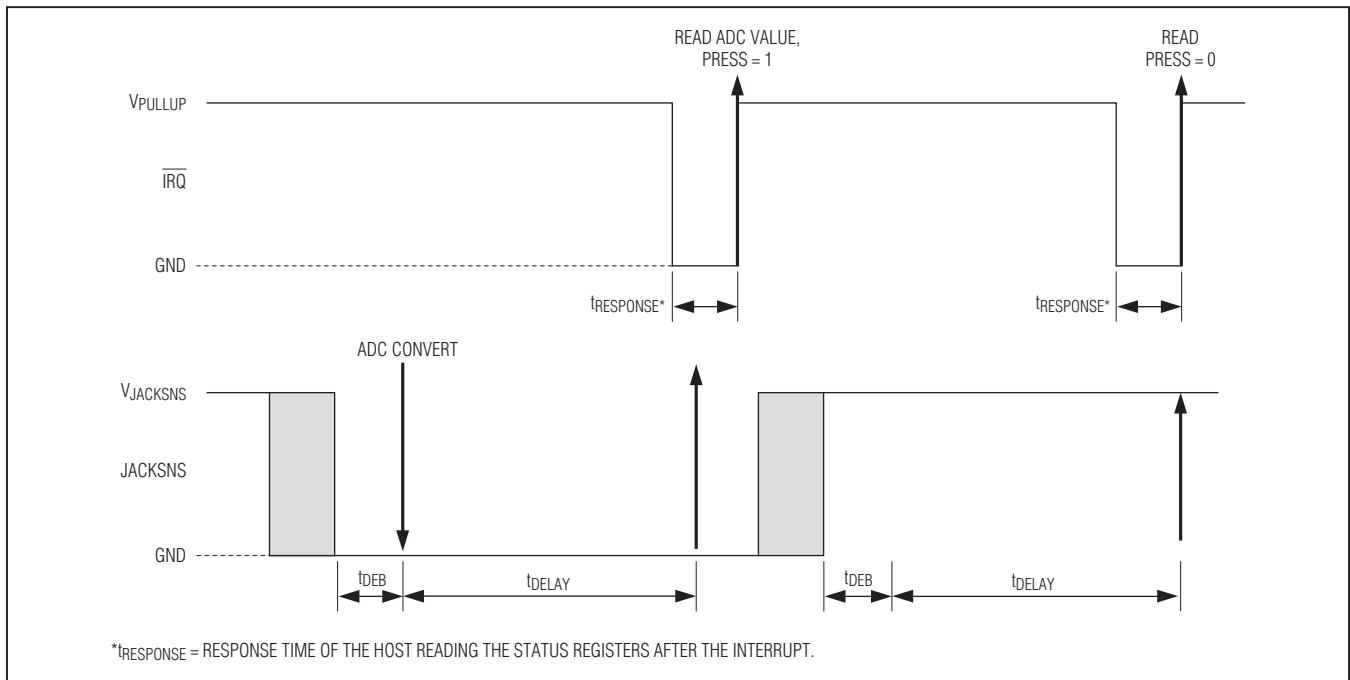

| Figure 46. MBH Timing $t_{DELAY}$ .....                                                   | 111 |

| Figure 47. MBH Timing $t_{DELAY}$ .....                                                   | 111 |

| Figure 48. Slow Jack Removal Timing .....                                                 | 112 |

| Figure 49. START, STOP, and REPEATED START Conditions .....                               | 114 |

| Figure 50. Acknowledge .....                                                              | 114 |

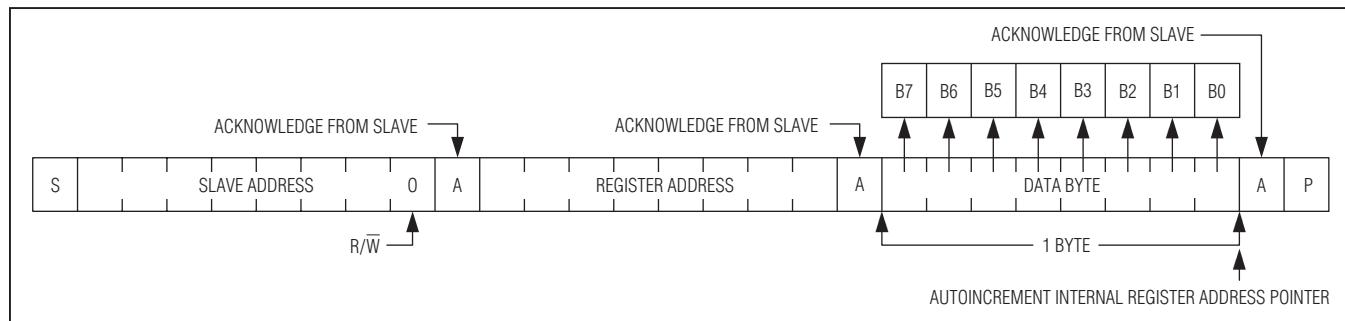

| Figure 51. Writing One Byte of Data to the IC .....                                       | 115 |

| Figure 52. Writing n-Bytes of Data to the IC .....                                        | 115 |

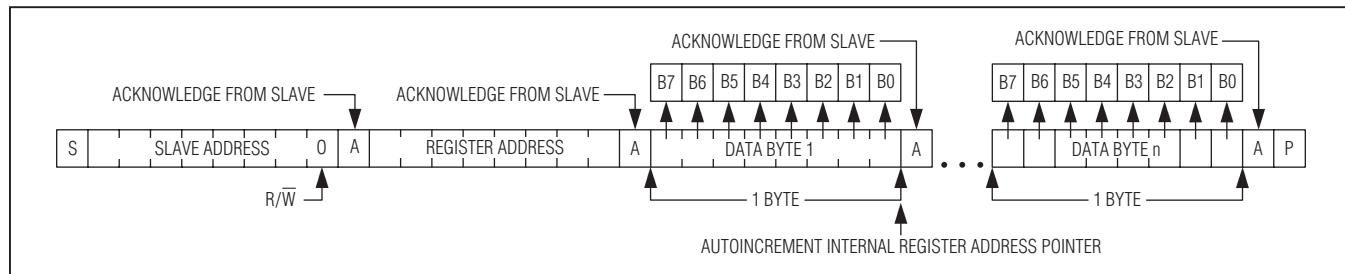

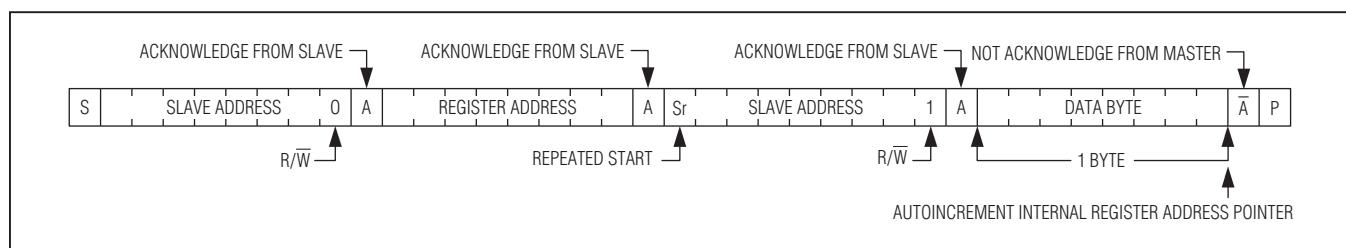

| Figure 53. Reading One Byte of Data from the IC .....                                     | 116 |

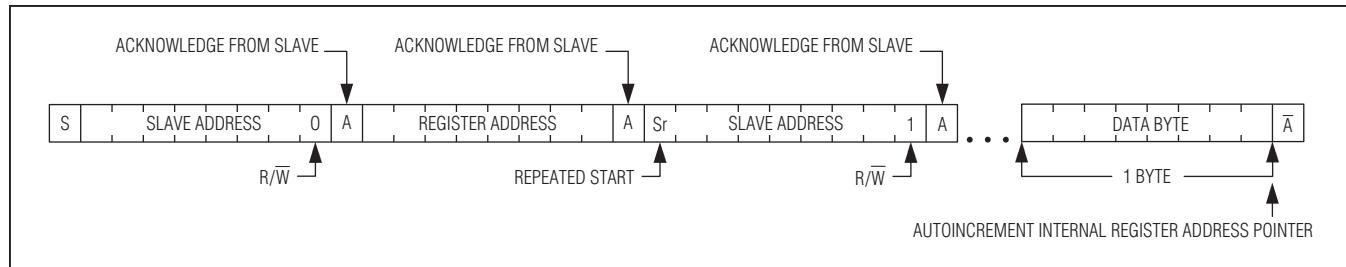

| Figure 54. Reading n-Bytes of Data from the IC .....                                      | 116 |

| Figure 55. SPI Byte Write .....                                                           | 116 |

| Figure 56. SPI Multiple Byte Write .....                                                  | 117 |

| Figure 57. SPI Read Format .....                                                          | 117 |

| Figure 58. SPI Read Format .....                                                          | 117 |

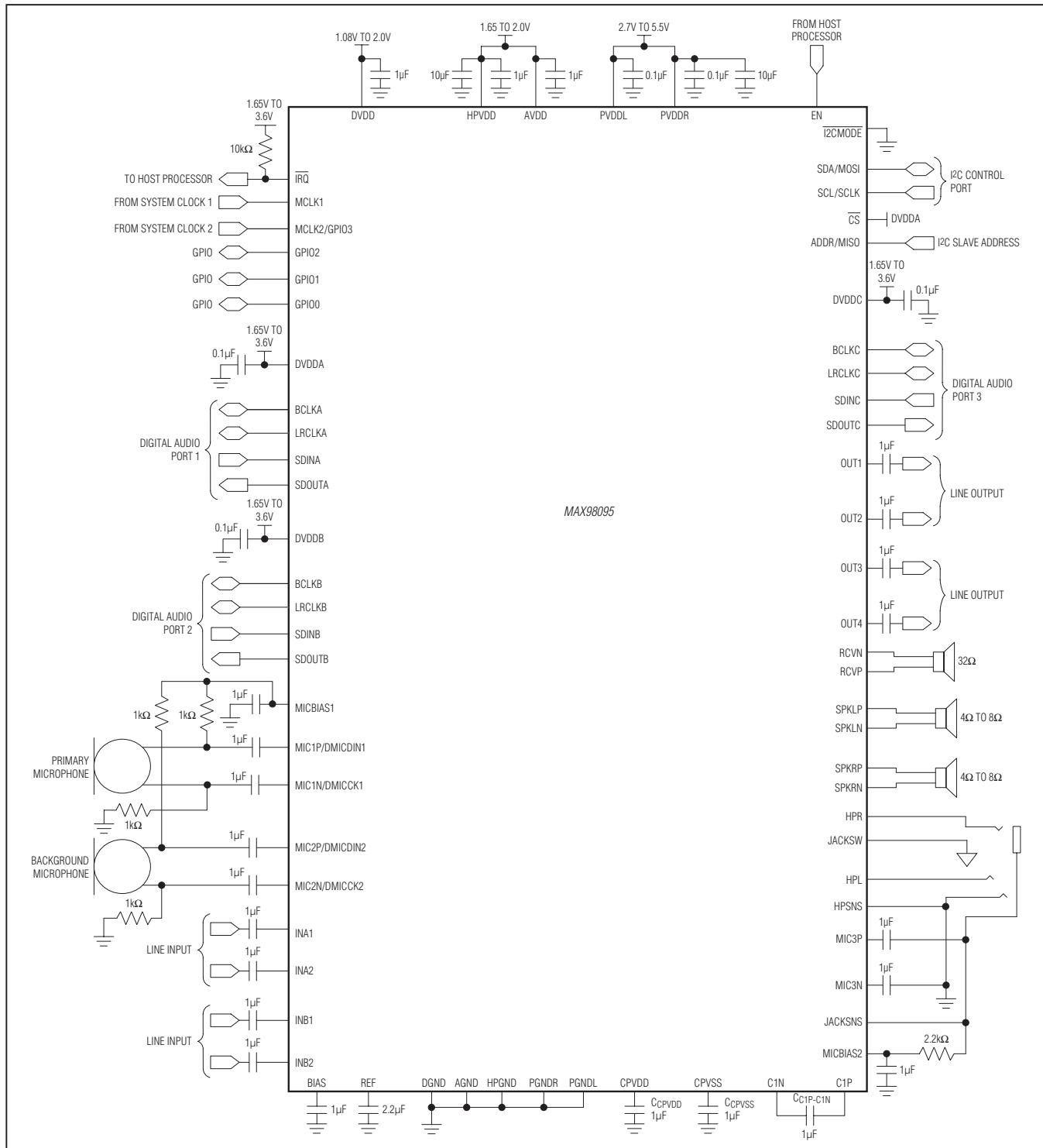

| Figure 59. Typical Operating Circuit with Analog Microphones and I2C Host Interface ..... | 118 |

# Audio Hub with Wideband FlexSound Processor

---

## LIST OF FIGURES (continued)

---

|                                                                                            |     |

|--------------------------------------------------------------------------------------------|-----|

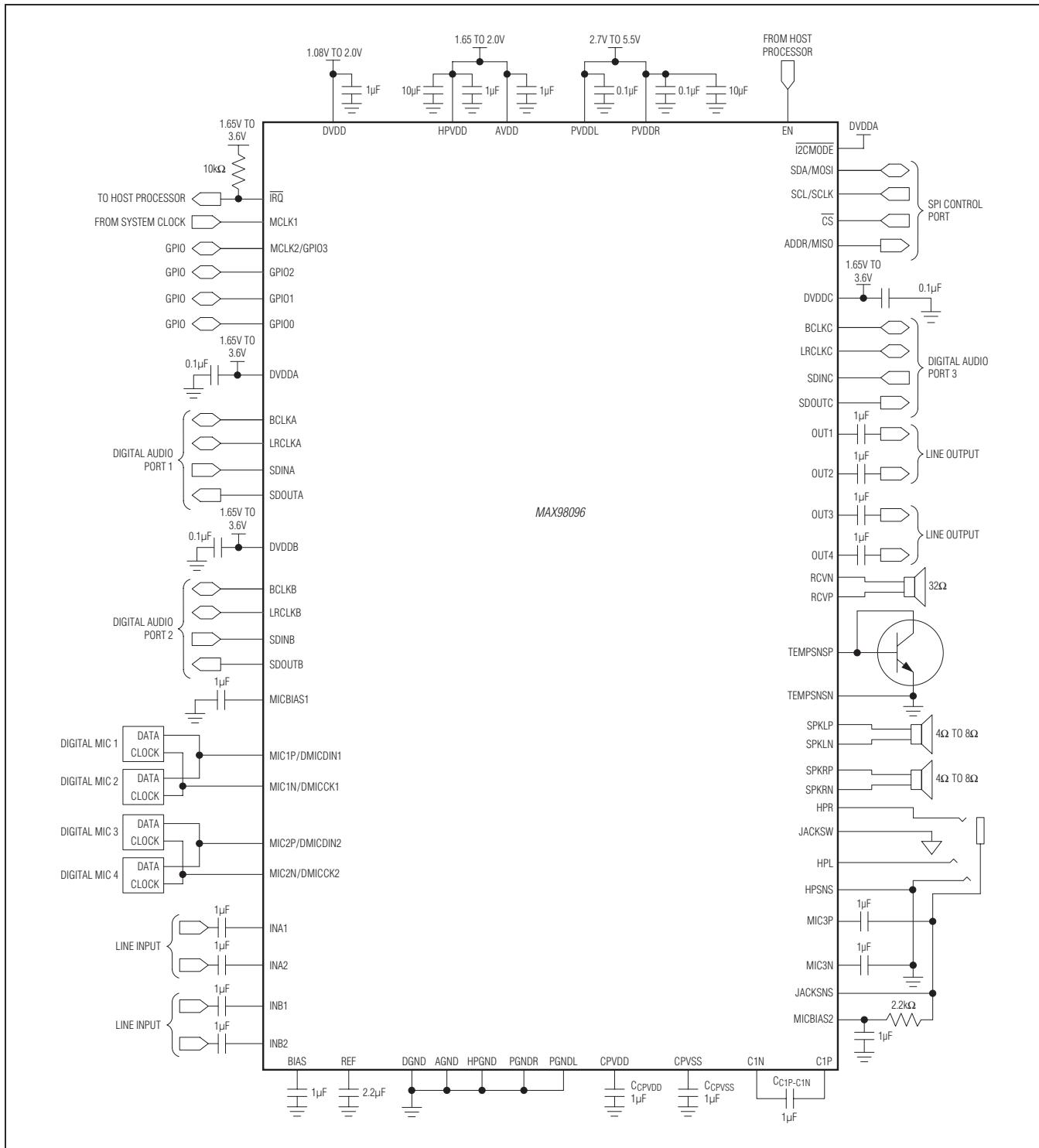

| Figure 60. Typical Operating Circuit with Digital Microphones and SPI Host Interface. .... | 119 |

| Figure 61. Optional Class D Ferrite Bead Filter .....                                      | 123 |

| Figure 62. Recording a Phone Call with Music .....                                         | 126 |

| Figure 63. Recording a Blue Tooth Phone Call with Music .....                              | 127 |

| Figure 64. Suggested Routing .....                                                         | 128 |

| Figure 65. WLP Ball Dimensions .....                                                       | 128 |

---

## LIST OF TABLES

---

|                                                                             |     |

|-----------------------------------------------------------------------------|-----|

| Table 1. Microphone Register Names and Addresses. ....                      | 76  |

| Table 2. Microphone Bias Register Name and Address .....                    | 77  |

| Table 3. Digital Microphone Register Name and Address. ....                 | 78  |

| Table 4. Line Input Register Names and Addresses .....                      | 79  |

| Table 5. ADC Input Mixers Register Names and Addresses.....                 | 80  |

| Table 6. Record DSP Register Names and Addresses .....                      | 80  |

| Table 7. Sidetone Register Names and Addresses .....                        | 81  |

| Table 8. Common Digital Audio Formats .....                                 | 83  |

| Table 9. Digital Audio Interface Register Names and Addresses .....         | 83  |

| Table 10. Common NI1/2 Values .....                                         | 86  |

| Table 11. Clock Control Register Names and Addresses .....                  | 87  |

| Table 12. Digital Signal Routing Register Names and Addresses.....          | 87  |

| Table 13. Voice/Music Lowpass Filters .....                                 | 90  |

| Table 14. Voice Highpass Filters .....                                      | 91  |

| Table 15. Selectable Highpass Filter Register Names and Addresses .....     | 92  |

| Table 16. Dynamic Range Control Register Names and Addresses.....           | 94  |

| Table 17. Parametric Equalizer Register Names and Addresses.....            | 95  |

| Table 18. Biquad Filter Register Names and Addresses .....                  | 95  |

| Table 19. Headphone and Speaker Expander Register Names and Addresses ..... | 96  |

| Table 20. FlexSound Processor Register Names and Addresses .....            | 97  |

| Table 21. Receiver Register Names and Addresses .....                       | 100 |

| Table 22. Receiver Mixer Attenuation Levels .....                           | 100 |

| Table 23. Speaker Register Names and Addresses .....                        | 100 |

| Table 24. Speaker Mixer Attenuation Levels .....                            | 102 |

| Table 25. Headphone Register Names and Addresses. ....                      | 105 |

| Table 26. Headphone Mixer Attenuation Levels .....                          | 105 |

| Table 27. Line Output Mixer Attenuation Levels.....                         | 106 |

## **Audio Hub with Wideband FlexSound Processor**

---

### **LIST OF TABLES (continued)**

---

|                                                                                   |     |

|-----------------------------------------------------------------------------------|-----|

| Table 28. Line Output Register Names and Addresses . . . . .                      | 106 |

| Table 29. Click-and-Pop Reduction Register Names and Addresses . . . . .          | 107 |

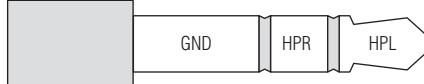

| Table 30. Accessories Identified by the IC . . . . .                              | 107 |

| Table 31. Programming Polarity of Jack Switch (Register 0x45) . . . . .           | 108 |

| Table 32. Jack Detection Register Names and Addresses . . . . .                   | 108 |

| Table 33. Key Switch Encoder Register Names and Addresses . . . . .               | 112 |

| Table 34. Codec Interrupt Control Bits and Their Associated Status Bits . . . . . | 113 |

| Table 35. Interrupt/Status Register Names and Addresses . . . . .                 | 113 |

| Table 36. I <sup>2</sup> C Slave Address . . . . .                                | 114 |

| Table 37. Startup Sequence . . . . .                                              | 120 |

| Table 38. Register Changes that Require CODEC_SHDN = 1 . . . . .                  | 120 |

| Table 39. Recommended Ambient Temperature Transistors . . . . .                   | 123 |

| Table 40. Recommended Connections for Unused Pins . . . . .                       | 124 |

## Audio Hub with Wideband FlexSound Processor

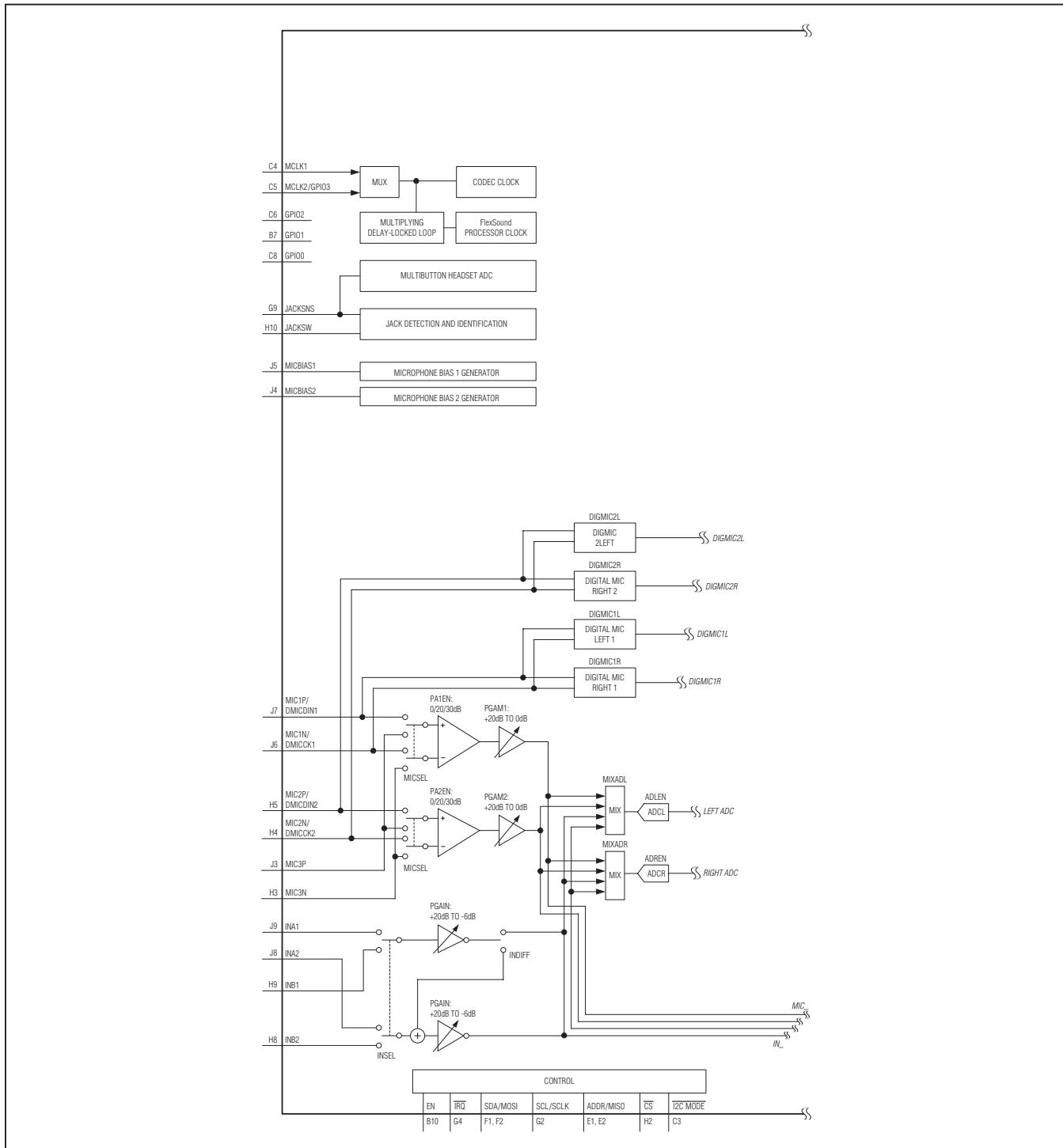

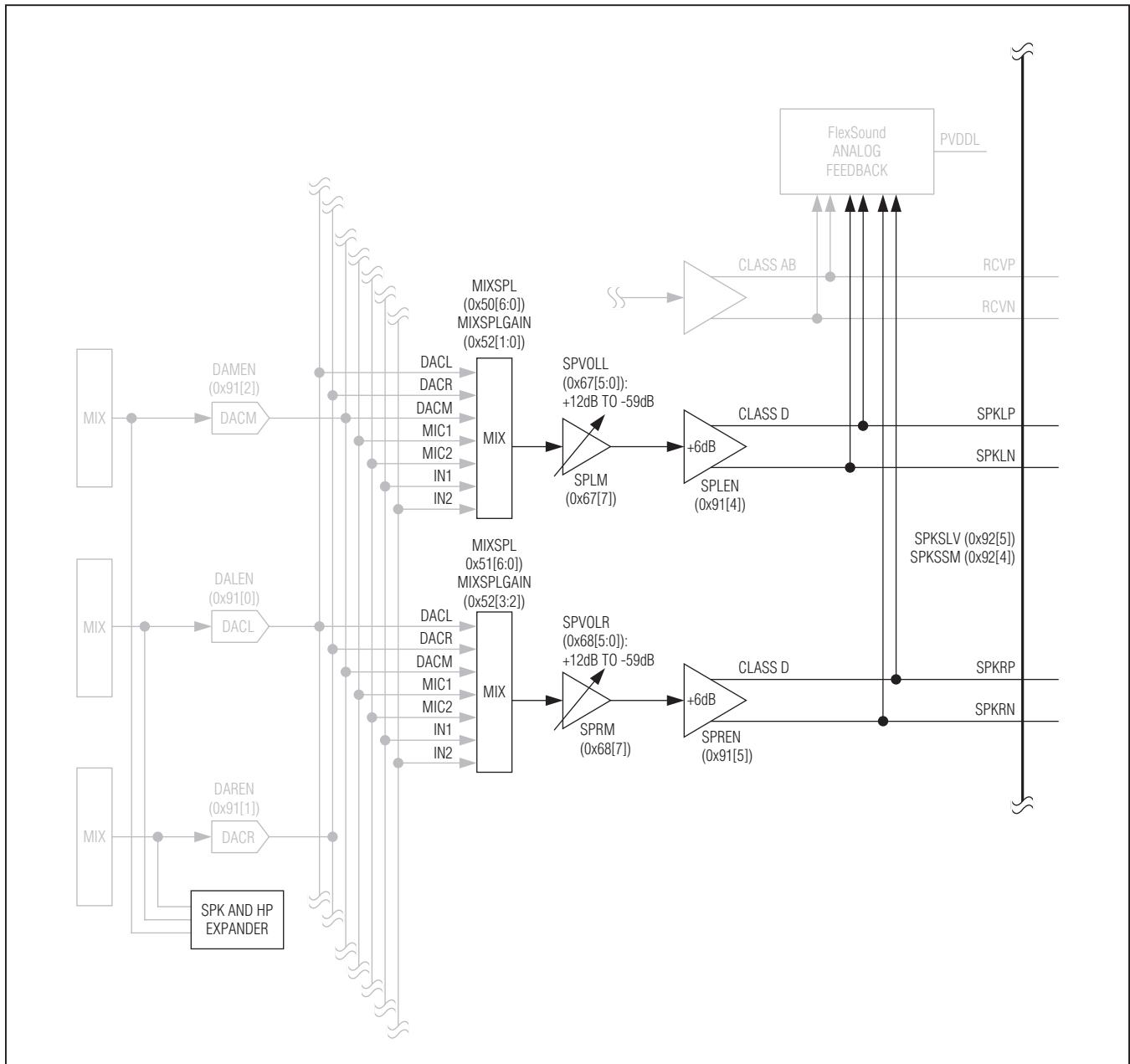

### Functional Diagram (1 of 3)

## Audio Hub with Wideband FlexSound Processor

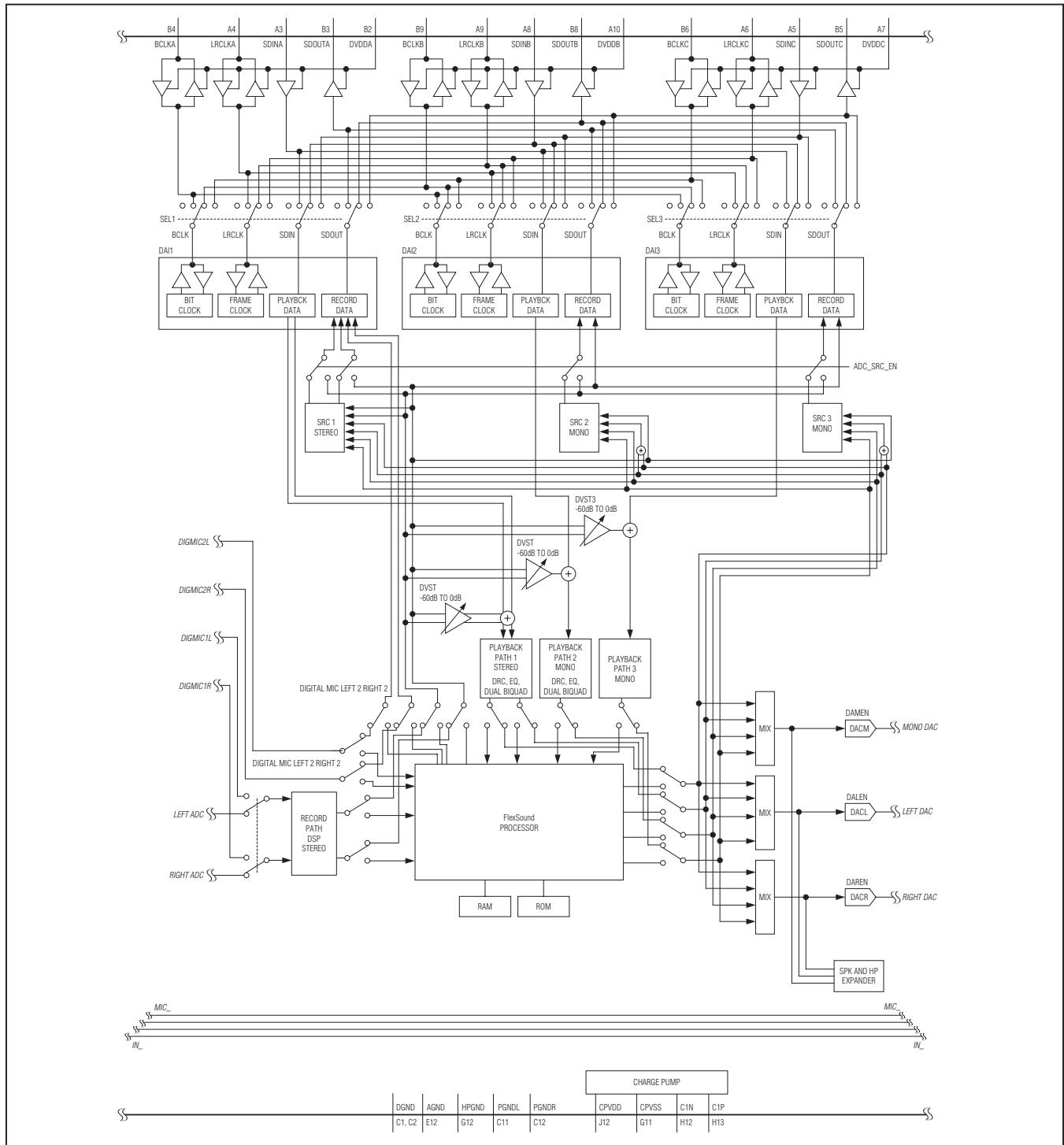

### Functional Diagram (2 of 3)

# MAX98096

## Audio Hub with Wideband FlexSound Processor

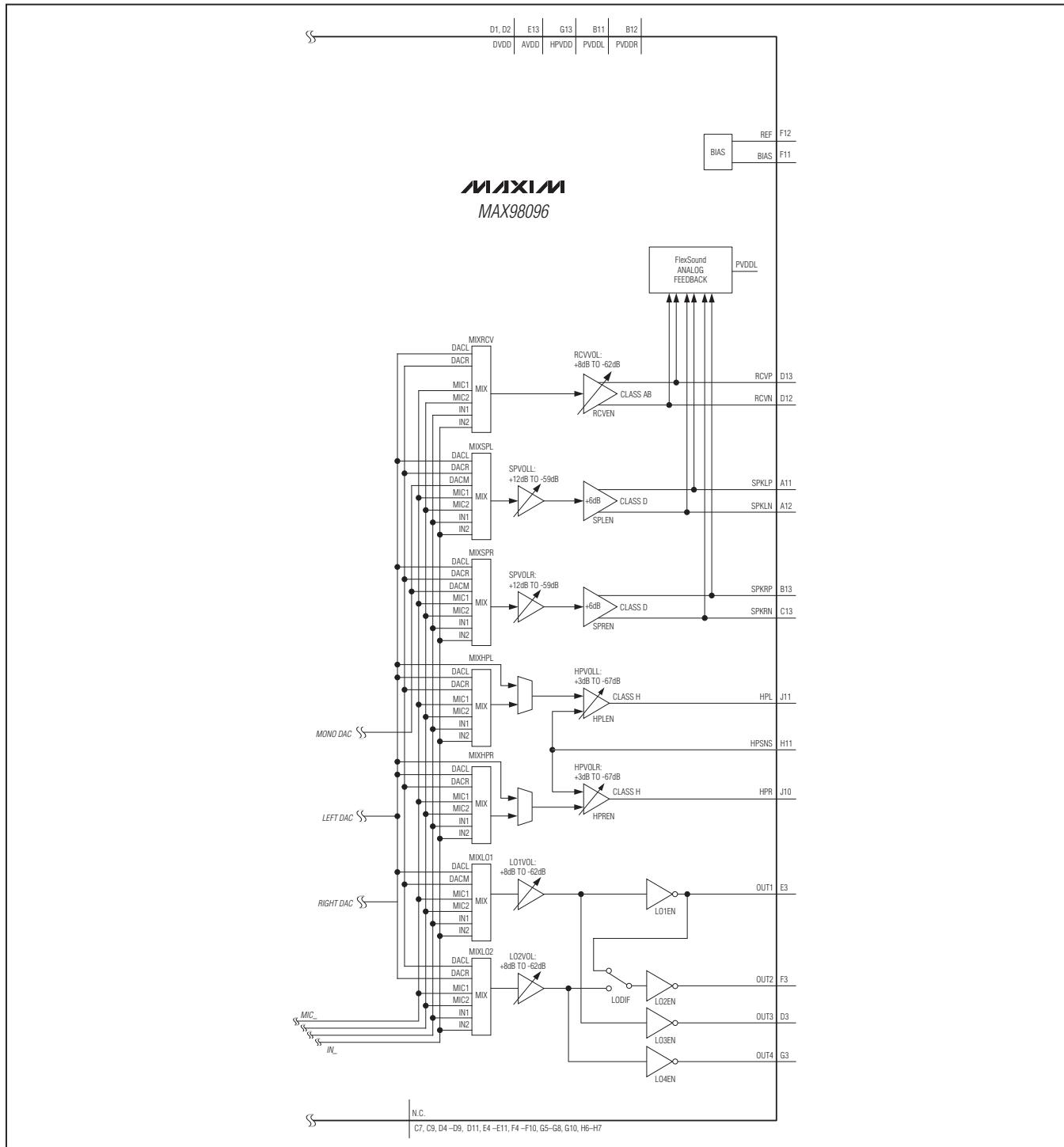

### Functional Diagram (3 of 3)

## Audio Hub with Wideband FlexSound Processor

### ABSOLUTE MAXIMUM RATINGS

(Voltages with respect to AGND unless otherwise noted.)

|                                                                                             |                                                            |

|---------------------------------------------------------------------------------------------|------------------------------------------------------------|

| DVDD, AVDD, HPVDD, CPVDD .....                                                              | -0.3V to +2.2V                                             |

| HPVDD .....                                                                                 | (V <sub>AVDD</sub> - 0.1V) to (V <sub>AVDD</sub> + 0.1V)   |

| PVDDL, PVDDR, DVDDA, DVDDB, DVDDC .....                                                     | -0.3V to +6.0V                                             |

| DGND, HPGND, PGNDL, PGNDR .....                                                             | -0.1V to +0.1V                                             |

| PVDDL to PVDDR .....                                                                        | -0.1V to +0.1V                                             |

| CPVDD .....                                                                                 | (V <sub>HPGND</sub> - 0.3V) to (V <sub>HPVDD</sub> + 0.3V) |

| CPVSS .....                                                                                 | (V <sub>HPGND</sub> - 2.2V) to (V <sub>HPGND</sub> + 0.3V) |

| C1N .....                                                                                   | (V <sub>HPGND</sub> - 0.3V) to (V <sub>HPGND</sub> + 0.3V) |

| C1P .....                                                                                   | (V <sub>HPGND</sub> - 0.3V) to (V <sub>HPVDD</sub> + 0.3V) |

| MICBIAS1, MICBIAS2 .....                                                                    | -0.3V to (V <sub>PVDDR</sub> + 0.3V)                       |

| JACKSW .....                                                                                | -2.2V to +6.0V                                             |

| MCLK1, SDINA, SDINB, SDINC, SDA/MOSI,<br>SCL/SCLK, CS, IRQ, EN, I <sub>2</sub> C MODE ..... | -0.3V to +6.0V                                             |

| LRCLKA, BCLKA, SDOUTA,<br>ADDR/MISO .....                                                   | -0.3V to (V <sub>DVDDA</sub> + 0.3V)                       |

| LRCLKB, BCLKB, SDOUTB, GPIO0,<br>GPIO1, GPIO2, MCLK2/GPIO3 .....                            | -0.3V to (V <sub>DVDBB</sub> + 0.3V)                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### PACKAGE THERMAL CHARACTERISTICS (Note 1)

#### WLP

|                                                                |        |

|----------------------------------------------------------------|--------|

| Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) ..... | 21°C/W |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) .....    | 1°C/W  |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to [www.maxim-ic.com/thermal-tutorial](http://www.maxim-ic.com/thermal-tutorial).

### ELECTRICAL CHARACTERISTICS

(V<sub>AVDD</sub> = V<sub>HPVDD</sub> = V<sub>DVDDA</sub> = V<sub>DVDBB</sub> = V<sub>DVDDC</sub> = +1.8V, V<sub>DVDD</sub> = +1.8V, V<sub>PVDDL</sub> = V<sub>PVDDR</sub> = +4.2V. Speaker loads (Z<sub>SPK</sub>) connected between SPK\_P and SPK\_N. Receiver load (R<sub>RCV</sub>) connected between RCV and RCVN. Headphone loads (R<sub>H</sub>) connected from HPL or HPR to ground. Line output loads (R<sub>LO</sub>) connected from OUT1, OUT2, OUT3, or OUT4 to ground. R<sub>H</sub> =  $\infty$ , R<sub>RCV</sub> =  $\infty$ , Z<sub>SPK</sub> =  $\infty$ , R<sub>LO</sub> =  $\infty$ , C<sub>REF</sub> = 2.2 $\mu$ F, C<sub>MICBIAS1</sub> = C<sub>MICBIAS2</sub> = C<sub>REG</sub> = 1 $\mu$ F, C<sub>C1N-C1P</sub> = 1 $\mu$ F, C<sub>CPVDD</sub> = C<sub>CPVSS</sub> = 1 $\mu$ F. AV<sub>MICPRE</sub> = +20dB. All other gain settings are 0dB, unless otherwise stated. MCLK = 12.288MHz, LRCLK = 48kHz, MAS = 0, 24-bit source data. T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are valid for T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                     | SYMBOL             | CONDITIONS                                                   | MIN  | TYP | MAX | UNITS |

|-------------------------------|--------------------|--------------------------------------------------------------|------|-----|-----|-------|

| <b>POWER SUPPLY</b>           |                    |                                                              |      |     |     |       |

| Supply Voltage Range (Note 3) | Guaranteed by PSRR | V <sub>PVDDL</sub> , V <sub>PVDDR</sub>                      | 2.7  |     | 5.5 | V     |

|                               |                    | V <sub>AVDD</sub> , V <sub>HPVDD</sub>                       | 1.65 | 1.8 | 2   |       |

|                               |                    | V <sub>DVDD</sub>                                            | 1.33 | 1.8 | 2   |       |

|                               |                    | V <sub>DVDDA</sub> , V <sub>DVDBB</sub> , V <sub>DVDDC</sub> | 1.65 |     | 3.6 |       |

## Audio Hub with Wideband FlexSound Processor

### ELECTRICAL CHARACTERISTICS (continued)

( $V_{AVDD} = V_{HPVDD} = V_{DVDDA} = V_{DVDDB} = V_{DVDDC} = +1.8V$ ,  $V_{DVDD} = +1.8V$ ,  $V_{PVDDL} = V_{PVDDR} = +4.2V$ . Speaker loads ( $Z_{SPK}$ ) connected between SPK\_P and SPK\_N. Receiver load ( $R_{RCV}$ ) connected between RCV\_P and RCV\_N. Headphone loads ( $R_{HP}$ ) connected from HPL or HPR to ground. Line output loads ( $R_{LO}$ ) connected from OUT1, OUT2, OUT3, or OUT4 to ground.  $R_{HP} = \infty$ ,  $R_{RCV} = \infty$ ,  $Z_{SPK} = \infty$ ,  $R_{LO} = \infty$ ,  $C_{REF} = 2.2\mu F$ ,  $C_{MICBIAS1} = C_{MICBIAS2} = C_{REG} = 1\mu F$ ,  $C_{C1N-C1P} = 1\mu F$ ,  $C_{CPVDD} = C_{CPVSS} = 1\mu F$ .  $AV_{MICPRE\_} = +20dB$ . All other gain settings are 0dB, unless otherwise stated. MCLK = 12.288MHz, LRCLK = 48kHz, MAS = 0, 24-bit source data.  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are valid for  $T_A = +25^\circ C$ .) (Note 2)

| PARAMETER                         | SYMBOL           | CONDITIONS                                                                | MIN     | TYP                            | MAX  | UNITS   |

|-----------------------------------|------------------|---------------------------------------------------------------------------|---------|--------------------------------|------|---------|

| Total Supply Current (Note 4)     | I <sub>VDD</sub> | Mono full duplex, microphone input, receiver output, $fs = 8kHz$ (Note 5) | Analog  | 2.5                            | 4.2  | mA      |

|                                   |                  |                                                                           | Speaker | 1.5                            | 2.5  |         |

|                                   |                  |                                                                           | Digital | 2.1                            | 3    |         |

|                                   |                  | Low-power stereo DAC playback, headphone outputs (Note 5)                 | Analog  | 1.3                            | 2.1  |         |

|                                   |                  |                                                                           | Speaker | 0                              | 0.02 |         |

|                                   |                  |                                                                           | Digital | 1.95                           | 3.3  |         |

|                                   |                  | Stereo full duplex, line inputs, speaker outputs (Note 5)                 | Analog  | 3.0                            | 5.4  |         |

|                                   |                  |                                                                           | Speaker | 2.8                            | 4    |         |

|                                   |                  |                                                                           | Digital | 5.6                            | 7.2  |         |

| Shutdown Supply Current (Note 4)  |                  | $T_A = +25^\circ C$ , EN = 0V                                             | Analog  | 0.4                            | 2    | $\mu A$ |

|                                   |                  |                                                                           | Speaker | 0.1                            | 1    |         |

|                                   |                  |                                                                           | Digital | 8                              | 50   |         |

|                                   |                  | $T_A = +25^\circ C$                                                       | Analog  | 0.9                            | 3    | $\mu A$ |

|                                   |                  |                                                                           | Speaker | 4                              | 10   |         |

|                                   |                  |                                                                           | Digital | 10.5                           | 50   |         |

| REF Voltage                       |                  |                                                                           |         | 1.25                           |      | V       |

| BIAS Voltage                      |                  |                                                                           |         | $V_{AVDD} \times \frac{7}{16}$ |      | V       |

| <b>MICROPHONE TO ADC PATH</b>     |                  |                                                                           |         |                                |      |         |

| Dynamic Range (Note 6)            | DR               | $f = 1kHz$ , $AV_{MICPRE\_} = 0dB$                                        | 75      | 88                             |      | dB      |

| Total Harmonic Distortion + Noise | THD+N            | $AV_{MICPRE\_} = 0dB$ , $V_{IN} = -10dBV$                                 |         | -77                            | -65  | dB      |

|                                   |                  | $AV_{MICPRE\_} = 20dB$ , $V_{IN} = -30dBV$ , $f = 1kHz$                   |         | -82                            |      |         |

|                                   |                  | $AV_{MICPRE\_} = +30dB$ , $V_{IN} = -40dBV$ , $f = 1kHz$                  |         | -71                            |      |         |

| Common-Mode Rejection Ratio       | CMRR             | $V_{IN} = -30dBV$ , $f = 217Hz$                                           |         | 65                             |      | dB      |

| Power-Supply Rejection Ratio      | PSRR             | $V_{AVDD} = 1.65V$ to $2.0V$ , input referred, MIC inputs unconnected     | 50      | 60                             |      | dB      |

|                                   |                  | $f = 217Hz$ , $V_{RIPPLE} = 100mV_{P-P}$ , input referred                 |         | 60                             |      |         |

|                                   |                  | $f = 1kHz$ , $V_{RIPPLE} = 100mV_{P-P}$ , input referred                  |         | 60                             |      |         |

|                                   |                  | $f = 10kHz$ , $V_{RIPPLE} = 100mV_{P-P}$ , input referred                 |         | 55                             |      |         |

| Absolute Gain Accuracy            |                  | DC accuracy (Note 7)                                                      | -1.5    | 0                              | +1   | dB      |

## Audio Hub with Wideband FlexSound Processor

### ELECTRICAL CHARACTERISTICS (continued)

( $V_{AVDD} = V_{HPVDD} = V_{DVDDA} = V_{DVDDB} = V_{DVDDC} = +1.8V$ ,  $V_{DVDD} = +1.8V$ ,  $V_{PVDDL} = V_{PVDDR} = +4.2V$ . Speaker loads ( $Z_{SPK}$ ) connected between SPK\_P and SPK\_N. Receiver load ( $R_{RCV}$ ) connected between RCV\_P and RCV\_N. Headphone loads ( $R_{HP}$ ) connected from HPL or HPR to ground. Line output loads ( $R_{LO}$ ) connected from OUT1, OUT2, OUT3, or OUT4 to ground.  $R_{HP} = \infty$ ,  $R_{RCV} = \infty$ ,  $Z_{SPK} = \infty$ ,  $R_{LO} = \infty$ ,  $C_{REF} = 2.2\mu F$ ,  $C_{MICBIAS1} = C_{MICBIAS2} = C_{REG} = 1\mu F$ ,  $C_{C1N-C1P} = 1\mu F$ ,  $C_{CPVDD} = C_{CPVSS} = 1\mu F$ .  $AV_{MICPRE\_} = +20dB$ . All other gain settings are 0dB, unless otherwise stated. MCLK = 12.288MHz, LRCLK = 48kHz, MAS = 0, 24-bit source data.  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are valid for  $T_A = +25^\circ C$ .) (Note 2)

| PARAMETER                          | SYMBOL | CONDITIONS                                                                             | MIN                        | TYP  | MAX | UNITS |

|------------------------------------|--------|----------------------------------------------------------------------------------------|----------------------------|------|-----|-------|

| Path Phase Delay                   |        | 1kHz, 0dB input, highpass filter disabled measured from analog input to digital output | MODE = 0 (IIR voice) 8kHz  | 2.2  |     | ms    |

|                                    |        |                                                                                        | MODE = 0 (IIR voice) 16kHz | 1.1  |     |       |

|                                    |        |                                                                                        | MODE = 1 (FIR music) 8kHz  | 4.5  |     |       |

|                                    |        |                                                                                        | MODE = 1 (FIR music) 48kHz | 0.76 |     |       |

| <b>DIGITAL MICROPHONE PATH</b>     |        |                                                                                        |                            |      |     |       |

| Dynamic Range (Note 6)             | DR     | $f = 1kHz, f_S = 8kHz, AV_{ADCGAIN} = AV_{ADCLVL} = 0dB$                               | MCLK = 12.288MHz           | 90   |     | dB    |

|                                    |        |                                                                                        | MCLK = 13MHz               | 90   |     |       |

|                                    |        | $f = 1kHz, f_S = 24kHz, AV_{ADCGAIN} = AV_{ADCLVL} = 0dB$                              | MCLK = 12.288MHz           | 90   |     |       |

|                                    |        |                                                                                        | MCLK = 13MHz               | 90   |     |       |

|                                    |        | $f = 1kHz, f_S = 48kHz, AV_{ADCGAIN} = AV_{ADCLVL} = 0dB$                              | MCLK = 12.288MHz           | 90   |     |       |

|                                    |        |                                                                                        | MCLK = 13MHz               | 90   |     |       |

| Total Harmonic Distortion + Noise  | THD+N  | $f = 1kHz, f_S = 8kHz, AV_{ADCGAIN} = AV_{ADCLVL} = 0dB$                               | MCLK = 12.288MHz           | -85  |     | dB    |

|                                    |        |                                                                                        | MCLK = 13MHz               | -75  |     |       |

|                                    |        | $f = 1kHz, f_S = 24kHz, AV_{ADCGAIN} = AV_{ADCLVL} = 0dB$                              | MCLK = 12.288MHz           | -80  |     |       |

|                                    |        |                                                                                        | MCLK = 13MHz               | -75  |     |       |

|                                    |        | $f = 1kHz, f_S = 48kHz, AV_{ADCGAIN} = AV_{ADCLVL} = 0dB$                              | MCLK = 12.288MHz           | -72  |     |       |

|                                    |        |                                                                                        | MCLK = 13MHz               | -72  |     |       |

| Path Phase Delay                   |        | 1kHz, 0dB input, highpass filter disabled measured from analog input to digital output | MODE = 0 (IIR voice) 8kHz  | 2.2  |     | ms    |

|                                    |        |                                                                                        | MODE = 0 (IIR voice) 16kHz | 1.1  |     |       |

|                                    |        |                                                                                        | MODE = 1 (FIR music) 8kHz  | 4.5  |     |       |

|                                    |        |                                                                                        | MODE = 1 (FIR music) 48kHz | 0.76 |     |       |

| <b>MICROPHONE TO LINE OUT PATH</b> |        |                                                                                        |                            |      |     |       |

| Dynamic Range (Note 6)             | DR     | $f = 1kHz, AV_{MICPRE\_} = 0dB$                                                        | 80                         | 93   |     | dB    |

| Total Harmonic Distortion + Noise  | THD+N  | $AV_{MICPRE\_} = 0dB, V_{IN} = -10dBV, f = 1kHz$                                       | -80                        | -65  |     |       |

| Absolute Gain Accuracy             |        | DC accuracy (Note 7)                                                                   | -1.5                       | 0    | +1  | dB    |

## Audio Hub with Wideband FlexSound Processor

### ELECTRICAL CHARACTERISTICS (continued)

( $V_{AVDD} = V_{HPVDD} = V_{DVDDA} = V_{DVDB} = V_{DVDC} = +1.8V$ ,  $V_{DVDD} = +1.8V$ ,  $V_{PVDDL} = V_{PVDDR} = +4.2V$ . Speaker loads ( $Z_{SPK}$ ) connected between SPK\_P and SPK\_N. Receiver load ( $R_{RCV}$ ) connected between RCV\_P and RCV\_N. Headphone loads ( $R_{HP}$ ) connected from HPL or HPR to ground. Line output loads ( $R_{LO}$ ) connected from OUT1, OUT2, OUT3, or OUT4 to ground.  $R_{HP} = \infty$ ,  $R_{RCV} = \infty$ ,  $Z_{SPK} = \infty$ ,  $R_{LO} = \infty$ ,  $C_{REF} = 2.2\mu F$ ,  $C_{MICBIAS1} = C_{MICBIAS2} = C_{REG} = 1\mu F$ ,  $C_{C1N-C1P} = 1\mu F$ ,  $C_{CPVDD} = C_{CPVSS} = 1\mu F$ .  $AV_{MICPRE\_} = +20dB$ . All other gain settings are 0dB, unless otherwise stated. MCLK = 12.288MHz, LRCLK = 48kHz, MAS = 0, 24-bit source data.  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are valid for  $T_A = +25^\circ C$ .) (Note 2)

| PARAMETER                         | SYMBOL          | CONDITIONS                                                         |                      | MIN   | TYP              | MAX                   | UNITS |  |  |  |

|-----------------------------------|-----------------|--------------------------------------------------------------------|----------------------|-------|------------------|-----------------------|-------|--|--|--|

| <b>MICROPHONE PREAMP</b>          |                 |                                                                    |                      |       |                  |                       |       |  |  |  |

| Input Range                       | $V_{IN}$        | $AV_{MICPRE\_} = 0dB$                                              |                      | 1.4   |                  | $V_{P-P}$             |       |  |  |  |

|                                   |                 | $AV_{MICPRE\_} = 20dB$                                             |                      | 0.14  |                  |                       |       |  |  |  |

|                                   |                 | $AV_{MICPRE\_} = 30dB$                                             |                      | 0.045 |                  |                       |       |  |  |  |

| Preamplifier Gain                 | $AV_{MICPRE\_}$ | (Note 8)                                                           | $PA1EN/PA2EN = 01$   | 0     |                  | dB                    |       |  |  |  |

|                                   |                 |                                                                    | $PA1EN/PA2EN = 10$   | 19.5  | 20               | 20.5                  |       |  |  |  |

|                                   |                 |                                                                    | $PA1EN/PA2EN = 11$   | 29.4  | 30               | 30.5                  |       |  |  |  |

| PGA Gain                          | $AV_{MICPGA\_}$ | $AV_{MICPRE\_} = 0dB$ (Note 8)                                     | $PGAM1/PGAM2 = 0x00$ | 19.5  | 20               | 20.5                  | dB    |  |  |  |

|                                   |                 |                                                                    | $PGAM1/PGAM2 = 0x14$ | 0     |                  |                       |       |  |  |  |

| MIC Input Resistance              | $R_{IN\_MIC}$   | All gain settings, measured at MIC1P/MIC1N/MIC2P/MIC2N/MIC3P/MIC3N |                      | 6.5   | 10               | $\text{k}\Omega$      |       |  |  |  |

| <b>MICROPHONE BIAS</b>            |                 |                                                                    |                      |       |                  |                       |       |  |  |  |

| MICBIAS Output Voltage            | $V_{MICBIAS}$   | $I_{LOAD} = 1mA$ , $MIC\_BIAS\_ = 00$                              | 2.14                 |       | 2.2              | 2.25                  | V     |  |  |  |

|                                   |                 | $I_{LOAD} = 1mA$ , $MIC\_BIAS\_ = 01$                              | 2.33                 |       | 2.4              | 2.45                  |       |  |  |  |

|                                   |                 | $I_{LOAD} = 1mA$ , $MIC\_BIAS\_ = 10$                              | 2.53                 |       | 2.6              | 2.66                  |       |  |  |  |

|                                   |                 | $I_{LOAD} = 1mA$ , $MIC\_BIAS\_ = 11$                              | 2.72                 |       | 2.8              | 2.87                  |       |  |  |  |

| Load Regulation                   |                 | $MIC\_BIAS\_ = 00$                                                 | 0.8                  |       | 11               | $\text{mV}/\text{mA}$ |       |  |  |  |

| Line Regulation                   |                 | $V_{PVDDR} = 2.7V$ to $5.5V$ , $MIC\_BIAS\_ = 00$                  | 70                   | 82    | dB               |                       |       |  |  |  |

| Ripple Rejection                  |                 | $f = 217\text{Hz}$ , $V_{RIPPLE} = 100\text{mV}_{P-P}$             | 92                   |       | dB               |                       |       |  |  |  |

|                                   |                 | $f = 10\text{kHz}$ , $V_{RIPPLE} = 100\text{mV}_{P-P}$             | 83                   |       |                  |                       |       |  |  |  |

| Noise Voltage                     |                 | A-weighted, $f = 20\text{Hz}$ – $20\text{kHz}$                     | 3.8                  |       | $\mu\text{VRMS}$ |                       |       |  |  |  |

| <b>LINE INPUT TO ADC PATH</b>     |                 |                                                                    |                      |       |                  |                       |       |  |  |  |

| Dynamic Range (Note 6)            | DR              | MODE = 1 (FIR audio)                                               |                      | 96    |                  | dB                    |       |  |  |  |

| Total Harmonic Distortion + Noise | THD+N           | $V_{IN} = -10\text{dBV}$ , $f = 1\text{kHz}$                       | -80                  |       | dB               |                       |       |  |  |  |

| Absolute Gain Accuracy            |                 | DC accuracy (Note 6)                                               | -1                   | 0     | +1               | dB                    |       |  |  |  |

## Audio Hub with Wideband FlexSound Processor

### ELECTRICAL CHARACTERISTICS (continued)

( $V_{AVDD} = V_{HPVDD} = V_{DVDDA} = V_{DVDDB} = V_{DVDDC} = +1.8V$ ,  $V_{DVDD} = +1.8V$ ,  $V_{PVDDL} = V_{PVDDR} = +4.2V$ . Speaker loads ( $Z_{SPK}$ ) connected between SPK\_P and SPK\_N. Receiver load ( $R_{RCV}$ ) connected between RCV\_P and RCV\_N. Headphone loads ( $R_{HP}$ ) connected from HPL or HPR to ground. Line output loads ( $R_{LO}$ ) connected from OUT1, OUT2, OUT3, or OUT4 to ground.  $R_{HP} = \infty$ ,  $R_{RCV} = \infty$ ,  $Z_{SPK} = \infty$ ,  $R_{LO} = \infty$ ,  $C_{REF} = 2.2\mu F$ ,  $C_{MICBIAS1} = C_{MICBIAS2} = C_{REG} = 1\mu F$ ,  $C_{C1N-C1P} = 1\mu F$ ,  $C_{CPVDD} = C_{CPVSS} = 1\mu F$ .  $AV_{MICPRE\_} = +20dB$ . All other gain settings are 0dB, unless otherwise stated. MCLK = 12.288MHz, LRCLK = 48kHz, MAS = 0, 24-bit source data.  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are valid for  $T_A = +25^\circ C$ .) (Note 2)

| PARAMETER                                        | SYMBOL                | CONDITIONS                     | MIN                          | TYP                   | MAX  | UNITS            |            |

|--------------------------------------------------|-----------------------|--------------------------------|------------------------------|-----------------------|------|------------------|------------|

| <b>LINE INPUT AMPLIFIER</b>                      |                       |                                |                              |                       |      |                  |            |

| Level Adjust Gain                                | AV <sub>PGAIN_-</sub> | $T_A = +25^\circ C$ , (Note 7) | PGAIN = 0x0                  | 19                    | 20   | 21               |            |

|                                                  |                       |                                | PGAIN = 0x1                  | 13                    | 14   | 15               |            |

|                                                  |                       |                                | PGAIN = 0x2                  | 2                     | 3    | 4                |            |

|                                                  |                       |                                | PGAIN = 0x3                  |                       | 0    |                  |            |

|                                                  |                       |                                | PGAIN = 0x4                  | -4                    | -3   | -2               |            |

|                                                  |                       |                                | PGAIN = 0x5, 0x6, 0x7        | -1                    | 0    | +1               |            |

| Input Range                                      | V <sub>IN</sub>       | AV <sub>PGAIN_-</sub> = +20dB  |                              | 0.14                  |      | V <sub>P-P</sub> |            |

|                                                  |                       | AV <sub>PGAIN_-</sub> = +14dB  |                              | 0.28                  |      |                  |            |

|                                                  |                       | AV <sub>PGAIN_-</sub> = +3dB   |                              | 1                     |      |                  |            |

|                                                  |                       | AV <sub>PGAIN_-</sub> = 0dB    |                              | 1.4                   |      |                  |            |

|                                                  |                       | AV <sub>PGAIN_-</sub> = -3dB   |                              | 2                     |      |                  |            |

| Input Resistance                                 | R <sub>IN</sub>       | AV <sub>PGAIN_-</sub> = +20dB  | 7.3                          | 10                    | 13.7 | k $\Omega$       |            |

|                                                  |                       | AV <sub>PGAIN_-</sub> = +14dB  |                              | 10                    |      |                  |            |

|                                                  |                       | AV <sub>PGAIN_-</sub> = +3dB   |                              | 10                    |      |                  |            |

|                                                  |                       | AV <sub>PGAIN_-</sub> = 0dB    | 7.3                          | 10                    | 13.7 |                  |            |

|                                                  |                       | AV <sub>PGAIN_-</sub> = -3dB   |                              | 10                    |      |                  |            |

| Feedback Resistance                              | R <sub>IN_F</sub>     | INEXT = 1                      | $T_A = +25^\circ C$          | 18.5                  | 20   | 21.5             | k $\Omega$ |

|                                                  |                       |                                | $T_A = T_{MIN}$ to $T_{MAX}$ | 17                    |      | 23               |            |

| <b>ADC LEVEL CONTROL</b>                         |                       |                                |                              |                       |      |                  |            |

| ADC Conversion Gain                              | AV <sub>ADCVFS</sub>  |                                |                              | 0.707                 |      | V/FFS            |            |

| ADC Level Adjust Range                           | AV <sub>ADCLVL</sub>  | AVL/AVR = 0xF to 0x0 (Note 8)  | -12                          | 3                     |      | dB               |            |

| ADC Level Adjust Step Size                       |                       |                                |                              | 1                     |      | dB               |            |

| ADC Gain Adjust Range                            | AV <sub>ADCGAIN</sub> | AVLG/AVRG = 00 to 11 (Note 8)  | 0                            | 18                    |      | dB               |            |

| ADC Gain Adjust Step Size                        |                       |                                |                              | 6                     |      | dB               |            |

| <b>ADC DIGITAL FILTERS</b>                       |                       |                                |                              |                       |      |                  |            |

| <b>VOICE MODE IIR LOWPASS FILTER (MODE_ = 0)</b> |                       |                                |                              |                       |      |                  |            |

| Passband Cutoff                                  | f <sub>PLP</sub>      | Ripple limit cutoff            | 0.441 x f <sub>S</sub>       |                       |      | Hz               |            |

|                                                  |                       | -3dB cutoff                    | 0.449 x f <sub>S</sub>       |                       |      |                  |            |

| Passband Ripple                                  |                       | f < f <sub>PLP</sub>           | -0.1                         | 0.1                   |      | dB               |            |

| Stopband Cutoff                                  | f <sub>SLP</sub>      |                                |                              | 0.47 x f <sub>S</sub> |      | Hz               |            |

| Stopband Attenuation (Note 9)                    |                       | f > f <sub>SLP</sub>           | 74                           |                       |      | dB               |            |

## Audio Hub with Wideband FlexSound Processor

### ELECTRICAL CHARACTERISTICS (continued)

( $V_{AVDD} = V_{HPVDD} = V_{DVDDA} = V_{DVDDB} = V_{DVDDC} = +1.8V$ ,  $V_{DVDD} = +1.8V$ ,  $V_{PVDDL} = V_{PVDDR} = +4.2V$ . Speaker loads ( $Z_{SPK}$ ) connected between SPK\_P and SPK\_N. Receiver load ( $R_{RCV}$ ) connected between RCV\_P and RCV\_N. Headphone loads ( $R_{HP}$ ) connected from HPL or HPR to ground. Line output loads ( $R_{LO}$ ) connected from OUT1, OUT2, OUT3, or OUT4 to ground.  $R_{HP} = \infty$ ,  $R_{RCV} = \infty$ ,  $Z_{SPK} = \infty$ ,  $R_{LO} = \infty$ ,  $C_{REF} = 2.2\mu F$ ,  $C_{MICBIAS1} = C_{MICBIAS2} = C_{REG} = 1\mu F$ ,  $C_{C1N-C1P} = 1\mu F$ ,  $C_{CPVDD} = C_{CPVSS} = 1\mu F$ .  $AV_{MICPRE\_} = +20dB$ . All other gain settings are 0dB, unless otherwise stated. MCLK = 12.288MHz, LRCLK = 48kHz, MAS = 0, 24-bit source data.  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are valid for  $T_A = +25^\circ C$ .) (Note 2)

| PARAMETER                                                                        | SYMBOL      | CONDITIONS                                                        | MIN    | TYP          | MAX          | UNITS |

|----------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------|--------|--------------|--------------|-------|

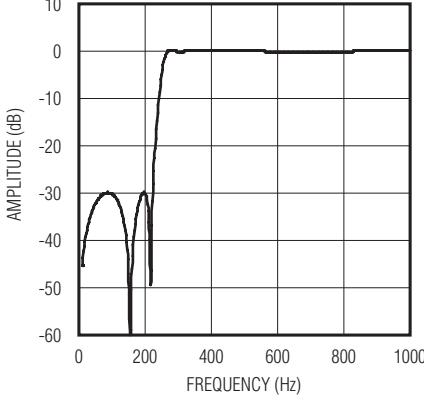

| <b>VOICE MODE IIR HIGHPASS FILTER (MODE_ = 0)</b>                                |             |                                                                   |        |              |              |       |

| Passband Cutoff<br>(-3dB from Peak)                                              | $f_{AHPPB}$ | AVFLT = 0x1 (elliptical tuned for $f_S = 16kHz$<br>+ 217Hz notch) | 0.0161 | $\times f_S$ |              | Hz    |

|                                                                                  |             | AVFLT = 0x2 (500Hz Butterworth tuned for<br>$f_S = 16kHz$ )       | 0.0319 | $\times f_S$ |              |       |

|                                                                                  |             | AVFLT = 0x3 (elliptical tuned for $f_S = 8kHz$<br>+ 217Hz notch)  | 0.0321 | $\times f_S$ |              |       |

|                                                                                  |             | AVFLT = 0x4 (500Hz Butterworth tuned for<br>$f_S = 8kHz$ )        | 0.0632 | $\times f_S$ |              |       |

|                                                                                  |             | AVFLT = 0x5 ( $f_S/240$ Butterworth)                              | 0.0043 | $\times f_S$ |              |       |

| Stopband Cutoff<br>(-30dB from Peak)                                             | $f_{AHPB}$  | AVFLT = 0x1 (elliptical tuned for $f_S = 16kHz$<br>+ 217Hz notch) | 0.0139 | $\times f_S$ |              | Hz    |

|                                                                                  |             | AVFLT = 0x2 (500Hz Butterworth tuned for<br>$f_S = 16kHz$ )       | 0.0156 | $\times f_S$ |              |       |

|                                                                                  |             | AVFLT = 0x3 (elliptical tuned for $f_S = 8kHz$<br>+ 217Hz notch)  | 0.0279 | $\times f_S$ |              |       |

|                                                                                  |             | AVFLT = 0x4 (500Hz Butterworth tuned for<br>$f_S = 8kHz$ )        | 0.0312 | $\times f_S$ |              |       |

|                                                                                  |             | AVFLT = 0x5 ( $f_S/240$ Butterworth)                              | 0.0018 | $\times f_S$ |              |       |

| DC Attenuation                                                                   | DCATTEN     | AVFLT ≠ 000                                                       | 90     |              |              | dB    |

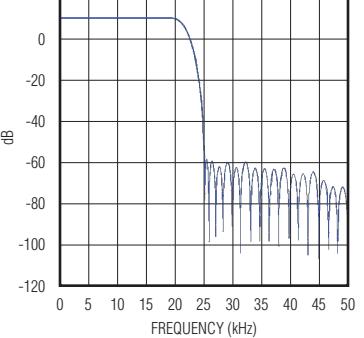

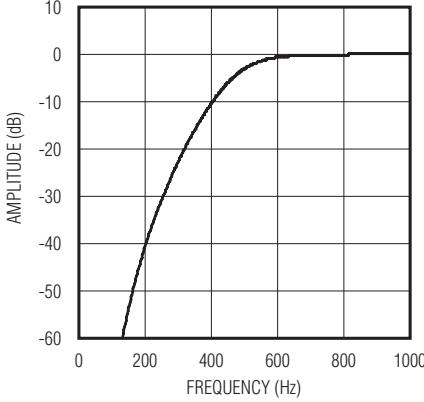

| <b>AUDIO MODE FIR LOWPASS FILTER (MODE_ = 1, DHF1 = 0, LRCLK &lt; 50kHz)</b>     |             |                                                                   |        |              |              |       |

| Passband Cutoff                                                                  | $f_{PLP}$   | Ripple limit cutoff                                               | 0.43   | $\times f_S$ |              | Hz    |

|                                                                                  |             | -3dB cutoff                                                       | 0.48   | $\times f_S$ |              |       |

|                                                                                  |             | -6.02dB cutoff                                                    | 0.5    | $\times f_S$ |              |       |

| Passband Ripple                                                                  |             | $f < f_{PLP}$                                                     | -0.1   | 0.1          |              | dB    |

| Stopband Cutoff                                                                  | $f_{SLP}$   |                                                                   |        | 0.58         | $\times f_S$ | Hz    |

| Stopband Attenuation (Note 9)                                                    |             | $f < f_{SLP}$                                                     | 60     |              |              | dB    |

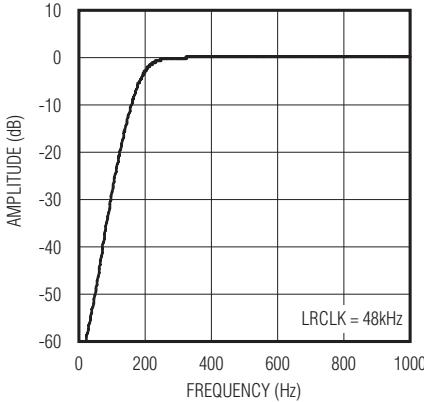

| <b>ADC AUDIO MODE FIR LOWPASS FILTER (MODE_ = 1, DHF1 = 1, LRCLK &gt; 50kHz)</b> |             |                                                                   |        |              |              |       |

| Passband Cutoff                                                                  | $f_{PLP}$   | Ripple limit cutoff                                               | 0.208  | $\times f_S$ |              | Hz    |

|                                                                                  |             | -3dB cutoff                                                       | 0.28   | $\times f_S$ |              |       |

| Passband Ripple                                                                  |             | $f < f_{PLP}$                                                     | -0.1   | 0.1          |              | dB    |

| Stopband Cutoff                                                                  | $f_{SLP}$   |                                                                   |        | 0.417        | $\times f_S$ | Hz    |

| Stopband Attenuation                                                             |             | $f < f_{SLP}$                                                     | 60     |              |              | dB    |

## Audio Hub with Wideband FlexSound Processor

### ELECTRICAL CHARACTERISTICS (continued)

( $V_{AVDD} = V_{HPVDD} = V_{DVDDA} = V_{DVDDB} = V_{DVDDC} = +1.8V$ ,  $V_{DVDD} = +1.8V$ ,  $V_{PVDDL} = V_{PVDDR} = +4.2V$ . Speaker loads ( $Z_{SPK}$ ) connected between SPK\_P and SPK\_N. Receiver load ( $R_{RCV}$ ) connected between RCV\_P and RCV\_N. Headphone loads ( $R_{HP}$ ) connected from HPL or HPR to ground. Line output loads ( $R_{LO}$ ) connected from OUT1, OUT2, OUT3, or OUT4 to ground.  $R_{HP} = \infty$ ,  $R_{RCV} = \infty$ ,  $Z_{SPK} = \infty$ ,  $R_{LO} = \infty$ ,  $C_{REF} = 2.2\mu F$ ,  $C_{MICBIAS1} = C_{MICBIAS2} = C_{REG} = 1\mu F$ ,  $C_{C1N-C1P} = 1\mu F$ ,  $C_{CPVDD} = C_{CPVSS} = 1\mu F$ .  $AV_{MICPRE\_} = +20dB$ . All other gain settings are 0dB, unless otherwise stated. MCLK = 12.288MHz, LRCLK = 48kHz, MAS = 0, 24-bit source data.  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are valid for  $T_A = +25^\circ C$ .) (Note 2)

| PARAMETER                                                     | SYMBOL          | CONDITIONS                                | MIN                | TYP                   | MAX | UNITS |

|---------------------------------------------------------------|-----------------|-------------------------------------------|--------------------|-----------------------|-----|-------|

| <b>ADC AUDIO MODE DC BLOCKING HIGHPASS FILTER (MODE_ = 1)</b> |                 |                                           |                    |                       |     |       |

| Passband Cutoff (-3dB from Peak)                              | $f_{AHPPB}$     | $AVFLT \neq 000$                          |                    | $0.000125 \times f_S$ |     | Hz    |

| DC Attenuation                                                | DCAtten         | $AVFLT \neq 000$                          |                    | 90                    |     | dB    |

| <b>ADC TO DAC DIGITAL SIDETONE (MODE_ = 0)</b>                |                 |                                           |                    |                       |     |       |

| Sidetone Gain Adjust Range                                    | AVSTGA          | DVST = 0x01                               |                    | -0.5                  |     | dB    |

|                                                               |                 | DVST = 0x1F                               |                    | -60.5                 |     |       |

| Sidetone Gain Adjust Step Size                                |                 |                                           |                    | 2                     |     | dB    |

| Sidetone Path Phase Delay                                     |                 | 1kHz, 0dB input, highpass filter disabled | 8kHz               | 2.2                   |     | ms    |

|                                                               |                 |                                           | 16kHz              | 1.1                   |     |       |

| <b>ADC TO DAC DIGITAL LOOP-THROUGH PATH</b>                   |                 |                                           |                    |                       |     |       |

| Dynamic Range (Note 6)                                        | DR              | $f = 1kHz$ , MODE = 1 (FIR audio)         | 80                 | 91                    |     | dB    |

| Total Harmonic Distortion                                     | THD             | $f = 1kHz$ , MODE = 1 (FIR audio)         | -71                | -66                   |     | dB    |

| <b>SAMPLE RATE CONVERTER</b>                                  |                 |                                           |                    |                       |     |       |

| Dynamic Range (Note 5)                                        | DR              | $f = 1kHz$                                | 88                 | 95                    |     | dB    |

| Total Harmonic Distortion + Noise                             | THD+N           | $f = 1kHz$                                | -60                |                       |     | dB    |

| <b>DAC LEVEL CONTROL</b>                                      |                 |                                           |                    |                       |     |       |

| DAC Conversion Gain                                           | $AV_{DACVFS}$   |                                           |                    | 1                     |     | V/FFS |

| DAC Attenuation Range                                         | $AV_{DACPATTN}$ | $DV1\DV2 = 0xF$ to $0x0$ (Note 8)         | -15                | 0                     |     | dB    |

| DAC Attenuation Step Size                                     |                 |                                           |                    | 1                     |     | dB    |

| DAC Gain Adjust Range                                         | $AV_{DAGAIN}$   | $DV1G = 00$ to $11$ (Note 8)              | 0                  | 18                    |     | dB    |

| DAC Gain Adjust Step Size                                     |                 |                                           |                    | 6                     |     | dB    |

| <b>DAC DIGITAL FILTERS</b>                                    |                 |                                           |                    |                       |     |       |

| <b>VOICE MODE IIR LOWPASS FILTER (MODE_ = 0)</b>              |                 |                                           |                    |                       |     |       |

| Passband Cutoff                                               | $f_{PLP}$       | Ripple limit cutoff                       | $0.448 \times f_S$ |                       |     | Hz    |

|                                                               |                 | -3dB cutoff                               | $0.451 \times f_S$ |                       |     |       |

| Passband Ripple                                               |                 | $f < f_{PLP}$                             | -0.1               | +0.1                  |     | dB    |

| Stopband Cutoff                                               | $f_{SLP}$       |                                           |                    | $0.476 \times f_S$    |     | Hz    |

| Stopband Attenuation (Note 9)                                 |                 | $f > f_{SLP}$                             | 75                 |                       |     | dB    |

## Audio Hub with Wideband FlexSound Processor

### ELECTRICAL CHARACTERISTICS (continued)

( $V_{AVDD} = V_{HPVDD} = V_{DVDDA} = V_{DVDDB} = V_{DVDDC} = +1.8V$ ,  $V_{DVDD} = +1.8V$ ,  $V_{PVDDL} = V_{PVDDR} = +4.2V$ . Speaker loads ( $Z_{SPK}$ ) connected between SPK\_P and SPK\_N. Receiver load ( $R_{RCV}$ ) connected between RCV\_P and RCV\_N. Headphone loads ( $R_{HP}$ ) connected from HPL or HPR to ground. Line output loads ( $R_{LO}$ ) connected from OUT1, OUT2, OUT3, or OUT4 to ground.  $R_{HP} = \infty$ ,  $R_{RCV} = \infty$ ,  $Z_{SPK} = \infty$ ,  $R_{LO} = \infty$ ,  $C_{REF} = 2.2\mu F$ ,  $C_{MICBIAS1} = C_{MICBIAS2} = C_{REG} = 1\mu F$ ,  $C_{C1N-C1P} = 1\mu F$ ,  $C_{CPVDD} = C_{CPVSS} = 1\mu F$ .  $AV_{MICPRE\_} = +20dB$ . All other gain settings are 0dB, unless otherwise stated. MCLK = 12.288MHz, LRCLK = 48kHz, MAS = 0, 24-bit source data.  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are valid for  $T_A = +25^\circ C$ .) (Note 2)

| PARAMETER                                                                            | SYMBOL       | CONDITIONS                                                     | MIN               | TYP                | MAX | UNITS |

|--------------------------------------------------------------------------------------|--------------|----------------------------------------------------------------|-------------------|--------------------|-----|-------|

| <b>VOICE MODE IIR HIGHPASS FILTER (MODE_ = 0)</b>                                    |              |                                                                |                   |                    |     |       |

| Passband Cutoff (-3dB from Peak)                                                     | $f_{DHPPB}$  | DVFLT = 0x1 (elliptical tuned for $f_S = 16kHz + 217Hz$ notch) | 0.0161            |                    |     | Hz    |

|                                                                                      |              | DVFLT = 0x2 (500Hz Butterworth tuned for $f_S = 16kHz$ )       | 0.0312            |                    |     |       |

|                                                                                      |              | DVFLT = 0x3 (elliptical tuned for $f_S = 8kHz + 217Hz$ notch)  | 0.0321            |                    |     |       |

|                                                                                      |              | DVFLT = 0x4 (500Hz Butterworth tuned for $f_S = 8kHz$ )        | 0.0625            |                    |     |       |

|                                                                                      |              | DVFLT = 0x5 ( $f_S/240$ Butterworth)                           | 0.0042            |                    |     |       |

| Stopband Cutoff (-30dB from Peak)                                                    | $f_{DHPSB}$  | DVFLT = 0x1 (Elliptical tuned for $f_S = 16kHz + 217Hz$ notch) | 0.0139            |                    |     | Hz    |

|                                                                                      |              | DVFLT = 0x2 (500Hz Butterworth tuned for $f_S = 16kHz$ )       | 0.0156            |                    |     |       |

|                                                                                      |              | DVFLT = 0x3 (Elliptical tuned for $f_S = 8kHz + 217Hz$ notch)  | 0.0279            |                    |     |       |

|                                                                                      |              | DVFLT = 0x4 (500Hz Butterworth tuned for $f_S = 8kHz$ )        | 0.0312            |                    |     |       |

|                                                                                      |              | DVFLT = 0x5 ( $f_S/240$ Butterworth)                           | 0.0021            |                    |     |       |

| DC Attenuation                                                                       | $DC_{ATTEN}$ | $DVFLT \neq 000$                                               |                   | 90                 |     | dB    |

| <b>AUDIO MODE FIR LOWPASS FILTER (MODE_ = 1, DHF1/DHF2 = 0, TLRCLK &lt; 50kHz)</b>   |              |                                                                |                   |                    |     |       |

| Passband Cutoff                                                                      | $f_{PLP}$    | Ripple limit cutoff                                            | 0.43 $\times f_S$ |                    |     | Hz    |

|                                                                                      |              | -3dB cutoff                                                    | 0.47 $\times f_S$ |                    |     |       |

|                                                                                      |              | -6.02dB cutoff                                                 | 0.5 $\times f_S$  |                    |     |       |

| Passband Ripple                                                                      |              | $f < f_{PLP}$                                                  | -0.1              | 0.1                |     | dB    |

| Stopband Cutoff                                                                      | $f_{SLP}$    |                                                                |                   | 0.58 $\times f_S$  |     | Hz    |

| Stopband Attenuation (Note 9)                                                        |              | $f > f_{SLP}$                                                  | 60                |                    |     | dB    |

| <b>AUDIO MODE FIR LOWPASS FILTER (MODE_ = 1, DHF1/DHF2 = 1 for LRCLK &gt; 50kHz)</b> |              |                                                                |                   |                    |     |       |

| Passband Cutoff                                                                      | $f_{PLP}$    | Ripple limit cutoff                                            | 0.24 $\times f_S$ |                    |     | Hz    |

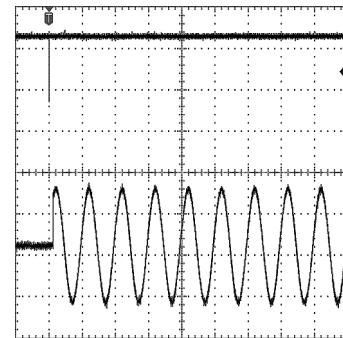

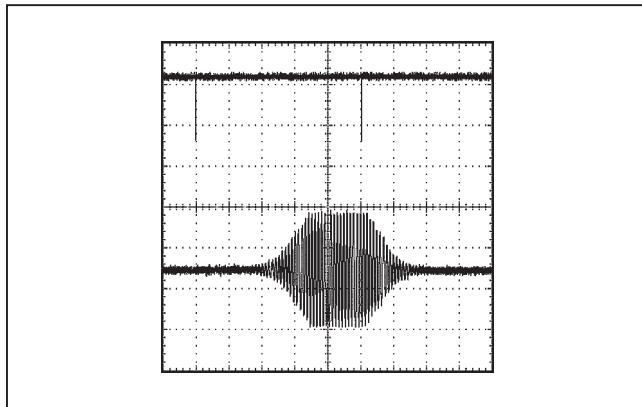

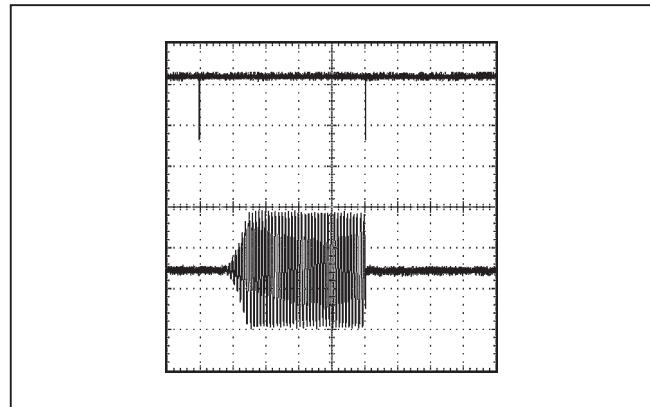

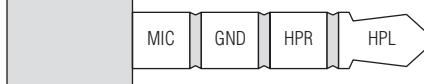

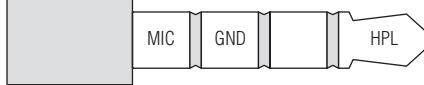

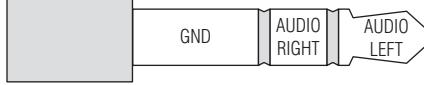

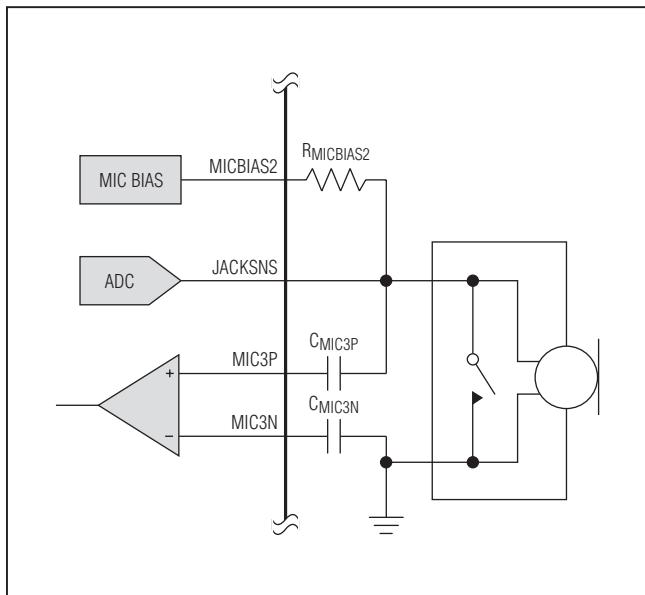

|                                                                                      |              | -3dB cutoff                                                    | 0.31 $\times f_S$ |                    |     |       |