# TLE8209-2SA

SPI Programmable H-Bridge

**Automotive Power**

#### **Table of Contents**

# **Table of Contents**

| I                                                                   | Overview                                                                                                                                                                                                                                                                                | . 3                                                      |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 2.1<br>2.2<br>2.3                                                   | Pin Configuration Pin Assignment Pin Definitions and Functions Terms                                                                                                                                                                                                                    | . 4<br>. 4                                               |

| 3                                                                   | Block Diagram                                                                                                                                                                                                                                                                           | . 6                                                      |

| <b>1</b><br>1.1<br>1.2<br>1.3                                       | General Product Characteristics Absolute Maximum Ratings Operating Range Thermal Resistance                                                                                                                                                                                             | . 7<br>. 8                                               |

| 5.1<br>5.2<br>5.3<br>5.4                                            | Power Supply  Basic Supply Characteristics  VDD Monitoring  VDDIO - Digital Output Supply and Diagnostic Mode Selection  Electrical Characteristics Power Supply and V <sub>DD</sub> -Monitoring                                                                                        | . 9<br>. 9<br>10<br>11                                   |

| 6                                                                   | Logic Inputs and Outputs                                                                                                                                                                                                                                                                | 12                                                       |

| 7<br>7.1<br>7.2<br>7.3                                              | Power Stages Parallel or SPI Control H-Bridge or Single Switch Usage Electrical Characteristics Power Stages                                                                                                                                                                            | 14<br>14                                                 |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10 | Protection and Monitoring Diagnosis in Status Flag Mode Current Limitation Temperature Dependent Current Reduction Short Circuit to Ground Short Circuit to Battery Short Circuit across the Load Overtemperature Undervoltage Shut-Down Open Load Diagnosis Electrical Characteristics | 18<br>18<br>19<br>20<br>20<br>20<br>20<br>20<br>20<br>22 |

| 9.1<br>9.2<br>9.3                                                   | SPI Interface General SPI Characteristics SPI Communication Electrical Characteristics SPI                                                                                                                                                                                              | 24<br>25                                                 |

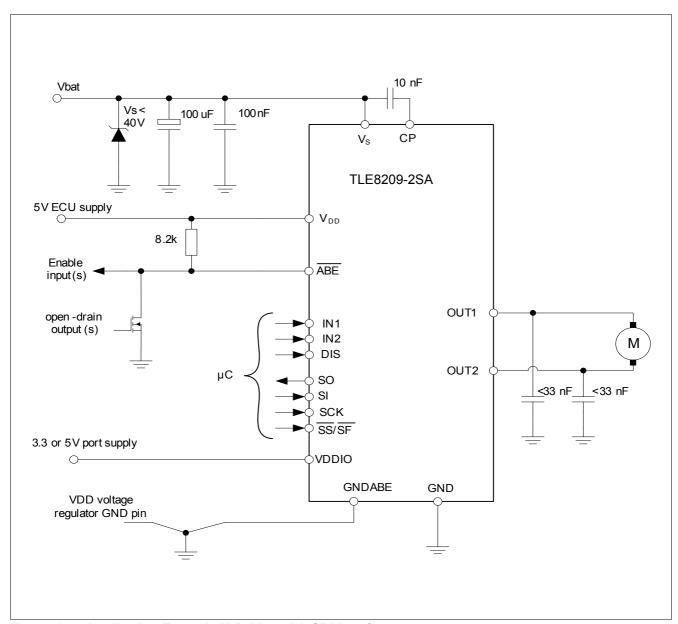

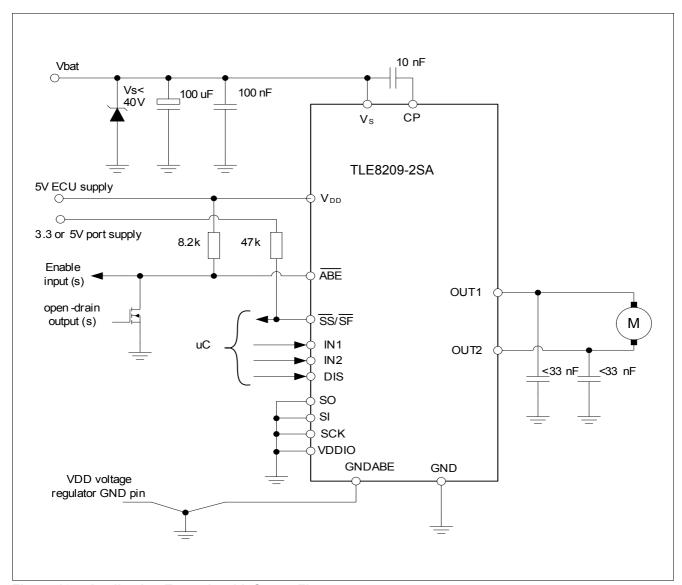

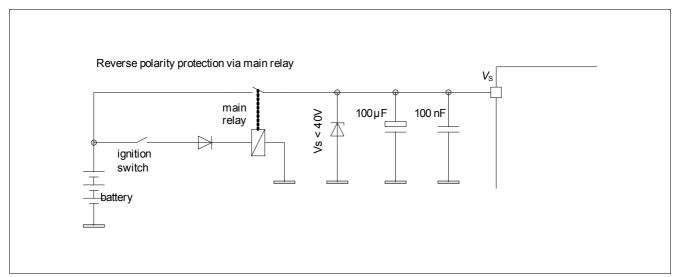

| 10                                                                  | Application Information                                                                                                                                                                                                                                                                 | 34                                                       |

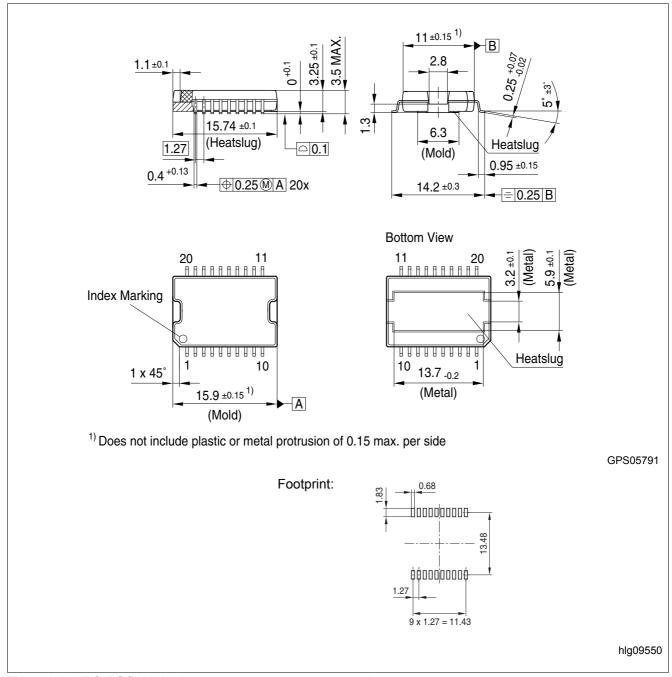

| 11                                                                  | Package Outlines TLE8209-2SA                                                                                                                                                                                                                                                            | 36                                                       |

| 12                                                                  | Revision History                                                                                                                                                                                                                                                                        | 37                                                       |

#### SPI Programmable H-Bridge

**TLE8209-2SA**

#### 1 Overview

#### **Features**

- Programmable current limitation from 1.5 to 8.6 A typ.

- Full path  $R_{\rm DSon}$  of 240 m $\Omega$  (typ. at Tj=25°C)

- Operating battery supply voltage 4.5 V to 28 V

- Operating logic supply voltage 4.4 to 5.25 V

- Low standby current (8 μA typ.)

- Logic inputs TTL/CMOS-compatible

- All I/O pins overvoltage tolerant up to 18 V

- Enable and disable input

- Short circuit and overtemperature protection

- V<sub>S</sub> undervoltage shutdown

- V<sub>DD</sub> over- and undervoltage monitoring

- Open load detection in off condition

- Temperature dependent current reduction

- Extensive diagnosis capabilities via SPI interface

- Status Flag for basic diagnosis without SPI

- · Configurable as H-bridge or two independent half bridges

- Control of power stages by parallel inputs or via SPI

- Output switching frequency up to 11 kHz

- Slewrate programmable through SPI

- Excellent EMC performance

- AEC qualified

- Green product (RoHS compliant)

# Confine on Property of the Confine on Property o

PG-DSO-20-65

#### **Functional Description**

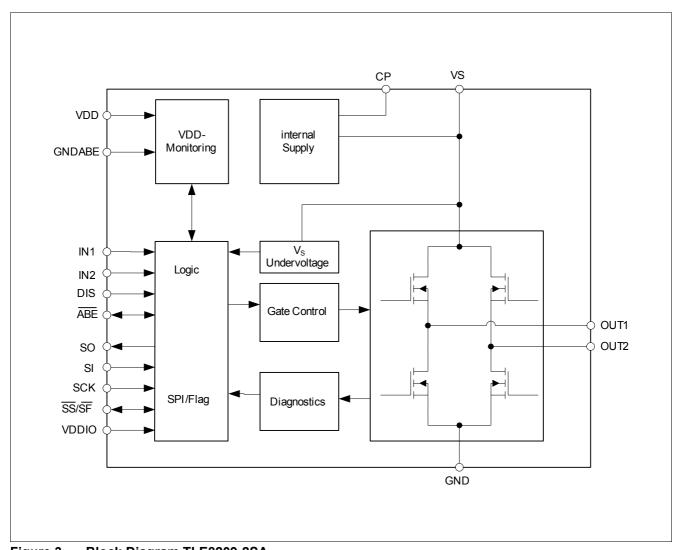

The TLE8209-2SA is a SPI programmable H-bridge, designed for the control of DC motors in safety critical automotive applications. It features four selectable current ranges, two selectable slew rate settings and extensive diagnosis via SPI. The device monitors the digital supply voltage  $V_{\rm DD}$  and shuts down the output stages in case of  $V_{\rm DD}$  over- or undervoltage, thus providing a safe switch off path in case of malfunction of the digital control circuitry.

In order to reduce power dissipation in extreme thermal conditions the current limitation threshold is reduced linearly for junction temperatures over 165°C. A thermal warning bit is set in the SPI.

The two half bridges can also be used independently to drive two separate loads like solenoids or unidirectional DC motors.

| Туре        | Package      | Body Width | Marking     |

|-------------|--------------|------------|-------------|

| TLE8209-2SA | PG-DSO-20-65 | 430 mil    | TLE8209-2SA |

Data Sheet 3 Rev. 1.2, 2012-12-20

**Pin Configuration**

# 2 Pin Configuration

# 2.1 Pin Assignment

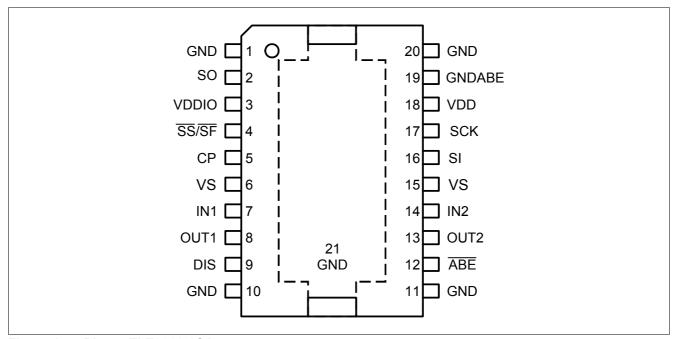

Figure 1 Pinout TLE8209-2SA

#### 2.2 Pin Definitions and Functions

| Pin | Symbol | Function in SPI Mode                                       | Function in Status Flag Mode                               |

|-----|--------|------------------------------------------------------------|------------------------------------------------------------|

| 1   | GND    | Ground                                                     | Ground                                                     |

| 2   | SO     | SPI Serial Data Out                                        | no function - connect to GND                               |

| 3   | VDDIO  | Supply Voltage for Logic Output Buffer                     | Switches to SF-mode if connected to GND                    |

| 4   | SS/SF  | Slave Select (low active)                                  | Status Flag (low active)                                   |

| 5   | СР     | Pin for external Charge Pump Capacitor                     | Pin for external Charge Pump Capacitor                     |

| 6   | VS     | Battery Supply Voltage, has to be connected to pin 15      | Battery Supply Voltage, has to be connected to pin 15      |

| 7   | IN1    | Input 1                                                    | Input 1                                                    |

| 8   | OUT1   | Output 1                                                   | Output 1                                                   |

| 9   | DIS    | Disable                                                    | Disable                                                    |

| 10  | GND    | Ground                                                     | Ground                                                     |

| 11  | GND    | Ground                                                     | Ground                                                     |

| 12  | ABE    | Bidirectional Enable Pin                                   | Bidirectional Enable Pin                                   |

| 13  | OUT2   | Output 2                                                   | Output 2                                                   |

| 14  | IN2    | Input 2                                                    | Input 2                                                    |

| 15  | VS     | Input battery supply voltage, has to be connected to pin 6 | Input battery supply voltage, has to be connected to pin 6 |

| 16  | SI     | SPI Serial Data Input                                      | no function - connect to GND                               |

#### **Pin Configuration**

| Pin | Symbol | Function in SPI Mode                          | Function in Status Flag Mode                  |

|-----|--------|-----------------------------------------------|-----------------------------------------------|

| 17  | SCK    | SPI Clock                                     | no function - connect to GND                  |

| 18  | VDD    | $V_{ m DD}$ supply                            | $V_{ m DD}$ supply                            |

| 19  | GNDABE | Sense ground for $V_{\mathrm{DD}}$ monitoring | Sense ground for $V_{\mathrm{DD}}$ monitoring |

| 20  | GND    | Ground                                        | Ground                                        |

| 21  | GND    | Heatslug - connect to GND                     | Heatslug - connect to GND                     |

#### 2.3 Terms

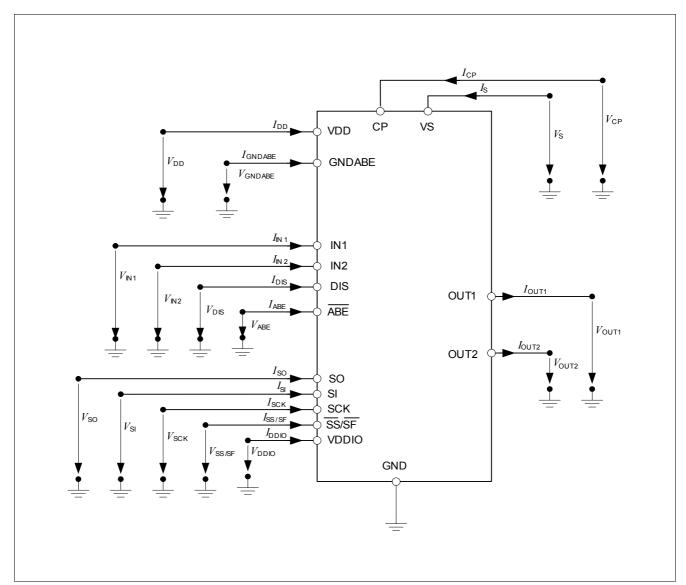

Figure 2 Terms TLE8209-2SA

**Block Diagram**

# 3 Block Diagram

Figure 3 Block Diagram TLE8209-2SA

**General Product Characteristics**

#### 4 General Product Characteristics

#### 4.1 Absolute Maximum Ratings

#### Absolute Maximum Ratings 1)

$T_{\rm j}$  = -40 ·C to 150 ·C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Pos. Parameter Symbol                                     |              | Limit               | Limit Values                  |    | Test Conditions / Comment                                                  |  |  |

|--------|-----------------------------------------------------------|--------------|---------------------|-------------------------------|----|----------------------------------------------------------------------------|--|--|

|        |                                                           |              | Min.                | Max.                          |    |                                                                            |  |  |

| 4.1.1  | Junction temperature                                      | $T_{i}$      | -40                 | 150                           | °C | _                                                                          |  |  |

|        |                                                           | ,            | 150                 | 175                           |    | 100h cumulative                                                            |  |  |

| 4.1.2  | Storage temperature                                       | $T_{s}$      | -55                 | 150                           | °C | -                                                                          |  |  |

| 4.1.3  | Ambient temperature                                       | $T_{a}$      | -40                 | 125                           | °C | _                                                                          |  |  |

| 4.1.4  | Battery supply voltage                                    | $V_{S}$      | -0.5                | 40                            | V  | Static destruction proof                                                   |  |  |

|        |                                                           |              | -2                  | 40                            | V  | Dynamic destruction proof $t < 0.5$ s (single pulse, $T_{jstart} < 85$ °C) |  |  |

| 4.1.5  | Logic supply voltage                                      | $V_{DD}$     | -0.5                | 18                            | V  | _                                                                          |  |  |

| 4.1.6  | Supply for logic out                                      | $V_{DDIO}$   | -0.5                | 18                            | V  | _                                                                          |  |  |

| 4.1.7  | Voltage at logic pins  ABE, IN1, IN2, DIS, SCK, SS/SF, SI | $V_{IN}$     | -0.5                | 18                            | V  | -                                                                          |  |  |

| 4.1.8  | Voltage at SO                                             | $V_{SO}$     | -0.5                | <i>V</i> <sub>DDIO</sub> +0.3 | V  | -                                                                          |  |  |

| 4.1.9  | Voltage at CP                                             | $V_{CP}$     | V <sub>S</sub> -0.3 | V <sub>S</sub> +5.0           | V  | 0V < V <sub>S</sub> < 40V                                                  |  |  |

| 4.1.10 | Voltage at GNDABE                                         | $V_{GNDABE}$ | $V_{GND}$ -0.3      | $V_{\rm GND}$ +0.3            | V  |                                                                            |  |  |

| ESD Su | sceptibility                                              | +            | +                   | +                             |    |                                                                            |  |  |

| 4.1.11 | ESD Resistivity to GND                                    | $V_{ESD}$    | -2                  | 2                             | kV | HBM <sup>2)</sup>                                                          |  |  |

| 4.1.12 |                                                           |              | -8                  | 8                             | kV | HBM <sup>2)</sup> , Pins OUT1 and OUT2                                     |  |  |

| 4.1.13 |                                                           |              | -500                | 500                           | V  | CDM <sup>3)</sup>                                                          |  |  |

| 4.1.14 |                                                           |              | -750                | 750                           | V  | CDM <sup>3)</sup> , Pins 1, 10, 11, 20                                     |  |  |

<sup>1)</sup> Not subject to production test, specified by design.

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

<sup>2)</sup> ESD susceptibility HBM according to EIA/JESD22-A114-B (1.5k $\Omega$ , 100pF)

<sup>3)</sup> ESD susceptibility, Charged Device Model "CDM" EIA/JESD22-C101

#### **General Product Characteristics**

## 4.2 Operating Range

| Pos.  | Parameter                          | Symbol     | Limit Values |      | Limit Values |   | Unit | Remark |

|-------|------------------------------------|------------|--------------|------|--------------|---|------|--------|

|       |                                    |            | Min.         | Max. |              |   |      |        |

| 4.2.1 | $V_{\rm S}$ supply voltage range   | $V_{S}$    | 4.5          | 28   | V            | _ |      |        |

| 4.2.2 | $V_{\mathrm{DD}}$ supply voltage   | $V_{DD}$   | 4.4          | 5.25 | V            | - |      |        |

| 4.2.3 | $V_{\mathrm{DDIO}}$ supply voltage | $V_{DDIO}$ | 0            | 5.5  | V            | - |      |        |

| 4.2.4 | PWM frequency                      | f          | _            | 11   | kHz          | _ |      |        |

| 4.2.5 | Junction temperature               | $T_{J}$    | -40          | 150  | °C           | - |      |        |

Note: Within the operating range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

#### 4.3 Thermal Resistance

| Pos.  | Parameter                         | Symbol     | Limit Values |      |      | Unit | Remark |

|-------|-----------------------------------|------------|--------------|------|------|------|--------|

|       |                                   |            | Min.         | Тур. | Max. |      |        |

| 4.3.6 | Junction to Case <sup>1)</sup>    | $R_{thJC}$ | _            | _    | 1.6  | K/W  | -      |

| 4.3.7 | Junction to Ambient <sup>1)</sup> | $R_{thJA}$ | _            | 17   | _    | K/W  | 2)     |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> Simulation according to Jedec JESD51-2,-5,-7; natural convection; FR4 2s2p board 76.2 x 114.3 x 1.5 mm (2 x  $70\mu$ m Cu, 2 x  $35\mu$ m Cu)

**Power Supply**

# 5 Power Supply

#### 5.1 Basic Supply Characteristics

The TLE8209-2SA has three different supply pins: VDD, VS and VDDIO. VDD is used to supply the internal logic circuitry. VS connects to battery voltage and supplies the output stages. The voltage at pin VDDIO defines the high level output voltage at the pin SO of the SPI interface. VDDIO is also used as a mode select pin. If VDDIO is connected to ground, the device is set to status flag mode (SPI inactive).

On power up the device will enter a functional state when  $V_{\rm DD}$  rises above the functional reset threshold  $V_{\rm DD\_RES}$ . In this state all output stages are inactive and internal registers are cleared. When  $V_{\rm DD}$  rises further above the power on reset threshold  $V_{\rm DD\_POR}$  the device starts operation with a delay time of  $t_{\rm POR}$ .

#### 5.2 VDD Monitoring

The logic supply voltage level at the pin VDD is monitored. If the voltage at pin  $V_{\rm DD}$  is out of the permissible range of  $V_{\rm DD\_L}$  ...  $V_{\rm DD\_H}$  the power stages of TLE8209-2SA are switched off and pin ABE is pulled to ground. To suppress glitches in the  $V_{\rm DD}$  monitoring, a glitch filter is implemented.  $V_{\rm DD}$  is measured with reference to pin GNDABE. The state of VDD monitoring is stored in STATCON\_REG and can be read out via SPI.

The output stages can also be turned off by pulling the ABE pin to ground externally.

In case of VDD failure, the output stages are switched off, even if the pin  $\overline{ABE}$  should be connected to a high level signal because of external short circuit to VDD or battery voltage (up to 18V). OUT1 and OUT2 cannot be switched on in over- or undervoltage condition, switching off is always possible. A power on reset ( $V_{DD} < V_{DD\_POR}$ ) switches off all stages without delay.

Control of VDD-monitoring is possible in SPI mode only. Detailed information (differentiation of over and undervoltage detection) is only possible by SPI interface.

#### Behavior of VDD monitoring in SF mode:

- monitoring is present with the specified values for over- and undervoltage

- any test of over- and undervoltage threshold is not possible

- the latch for overvoltage is disabled

#### VDD Undervoltage

If the VDD voltage is lower than the supply voltage supervisory lower threshold ( $V_{\rm DD\_THL}$ ), output stages are shut off after a filtering time ( $t_{\rm FIL\_OFF}$ ) and the bi-directional pin  $\overline{\rm ABE}$  is pulled low. At the transition from undervoltage to normal voltage the signal at pin  $\overline{\rm ABE}$  goes high and the output stages will return to normal operation after a filtering time ( $t_{\rm FIL\_ON}$ ) has expired. For output control via SPI the bits MUX and SINx in the config register have to be reprogrammed. New failures are not stored to diagnostic registers during undervoltage, register content remains valid, writing new information to configuration registers is possible as far as they are not reset by  $\overline{\rm ABE}$ . If VDD falls below the power-on-reset supply voltage ( $V_{\rm DD\_POR}$ ) all stages are shut off and  $\overline{\rm ABE}$  is switched active low. When VDD is rising above the power-on-reset supply voltage threshold ( $V_{\rm DD\_POR}$ ) a power-on-reset is generated ( $t_{\rm POR}$ ), setting all registers to its default state.

#### VDD Overvoltage

If the VDD voltage is higher than the supply voltage supervisory upper threshold ( $V_{\rm DD\_THH}$ ), all output stages are shut off after a filtering time ( $t_{\rm FIL\_OFF}$ ) and the bi-directional pin ABE is pulled low. The behavior of the ABE level and output stages on the return of VDD from overvoltage to the correct range is configured in STATCON\_REG, bit CONFIG0)

CONFIG0='1': ABE is latched and outputs remain off after overvoltage. Return to normal operation is only possible with power-on reset or by changing this bit via SPI.

Data Sheet 9 Rev. 1.2, 2012-12-20

**Power Supply**

CONFIG0='0': ABE is inactive after VDD returned to normal operating voltage and filtering time has expired.

At the transition from overvoltage to normal condition, the output stages will return to normal operation. For output control via SPI the bits MUX and SINx in the config register have to be re-programmed. New failures are not stored to diagnostic registers during overvoltage, register content remains valid, writing new information to configure registers is possible as far as they are not reset by  $\overline{ABE}$ .

#### **VDD Monitoring Test Mode**

Testing of VDD monitoring is possible in SPI mode only. The latch function for over voltage at VDD has to be switched of (CONFIG0=0 in STATCON REG)

#### Testing upper threshold:

By writing 00xxxxxxb into STATCON\_REG, the overvoltage threshold is reduced to VDD\_TEST\_H. STATCON\_REG bit 2 and 0 have to be LOW then. After writing 1xxxxxxxxb to STATCON\_REG, bit 2 and 0 in STATCON REG must be HIGH again

#### **Testing lower threshold:**

By writing 01xxxxxxb into STATCON\_REG, the undervoltage threshold is increased to VDD\_TEST\_L. STATCON\_REG bit 2 and 1 have to be LOW then. After writing 1xxxxxxxxb to STATCON\_REG, bit 2 and 1 in STATCON\_REG must be HIGH again.

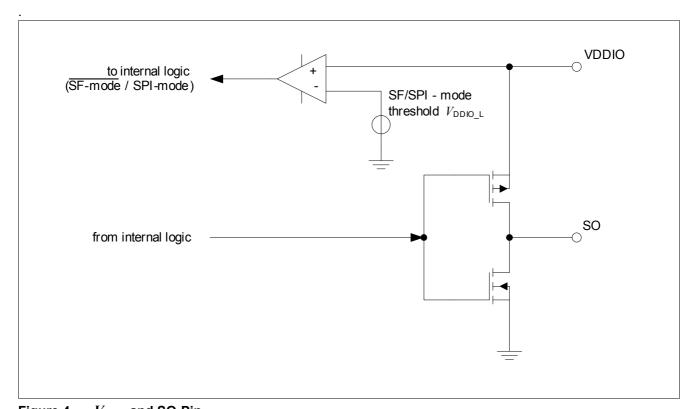

#### 5.3 VDDIO - Digital Output Supply and Diagnostic Mode Selection

The voltage at  $V_{\rm DDIO}$  is used to supply the output buffer at the SO pin (serial output of SPI-interface). The VDDIO pin is also used to select SPI- or in status flag (SF) diagnostic mode. As soon as  $V_{\rm DDIO}$  is lower than  $V_{\rm DDIO\_L}$ , the device is put into status flag mode.

Figure 4  $V_{\rm DDIO}$  and SO-Pin

**Power Supply**

# 5.4 Electrical Characteristics Power Supply and V<sub>DD</sub>-Monitoring

# Electrical Characteristics: Power Supply and $\mathbf{V}_{\mathrm{DD}}\text{-}\mathbf{Monitoring}$

$V_{\rm S}$  = 5 V to 28 V;  $V_{\rm DD}$  = 5.0 V,  $T_{\rm j}$  = -40 ·C to 150 ·C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.              | Parameter                                  | Symbol                 | ı        | Limit Val | ues  | Unit | <b>Test Conditions</b>                                                                                                            |  |

|-------------------|--------------------------------------------|------------------------|----------|-----------|------|------|-----------------------------------------------------------------------------------------------------------------------------------|--|

|                   |                                            |                        | Min.     | Тур.      | Max. |      |                                                                                                                                   |  |

| Supply            |                                            |                        |          |           |      |      |                                                                                                                                   |  |

| 5.4.1             | Supply Current                             | $I_{ m VS}$            | _        | 8         | 20   | μA   | $I_{\text{OUT}} = 0 \text{ A, V}_{\text{DD}} = 0 \text{V,}$<br>$V_{\text{S}} < 18 \text{ V, T}_{\text{j}} < 125 ^{\circ}\text{C}$ |  |

|                   |                                            |                        | _        | 2.1       | 4    | mA   | bridge disabled, $I_{\rm OUT}$ = 0 A, 5 V < $V_{\rm S}$ < 18 V                                                                    |  |

|                   |                                            |                        | _        | 2.5       | 5    | mA   | $f$ = 2 kHz, $I_{\rm OUT}$ = 0 A, 5 V < $V_{\rm S}$ < 18 V                                                                        |  |

|                   |                                            |                        | _        | 4         | 9    | mA   | $f = \text{10 kHz}, I_{\text{OUT}} = \text{0 A}, \\ \text{5 V} < V_{\text{S}} < \text{18 V}$                                      |  |

|                   |                                            |                        | _        | 4.8       | 13   | mA   | $f$ = 10 kHz, $I_{\rm OUT}$ = 0 A, 5 V < $V_{\rm S}$ < 28 V                                                                       |  |

| 5.4.2             | Functional Reset Threshold                 | $V_{\mathrm{DD\_RES}}$ | _        | 1.4       | 2.5  | V    | _                                                                                                                                 |  |

| 5.4.3             | Power On Reset Threshold                   | $V_{ m DD\_POR}$       | 3.5      | 3.75      | 4.0  | V    | _                                                                                                                                 |  |

| 5.4.4             | Power On Reset Delay<br>Time               | $t_{POR}$              | _        | 0.22      | 0.5  | ms   | $V_{\rm DD}$ = on> output stage active, no load                                                                                   |  |

| 5.4.5             | VDD Input current                          | $I_{DD}$               | _        | 7         | 9    | mA   | 4.5V < V <sub>DD</sub> < 5.5V                                                                                                     |  |

| 5.4.6             | VDDIO Input current                        | $I_{DDIO}$             | _        | 30        | 100  | μA   | SPI-mode<br>no load at SO<br>no SPI communication                                                                                 |  |

| 5.4.7             | SF-mode Threshold                          | $V_{DDIO\_L}$          | _        | _         | 1.0  | V    | _                                                                                                                                 |  |

| 5.4.8             | SPI-mode Threshold                         | $V_{DDIO_H}$           | 2.0      | _         | _    | V    | _                                                                                                                                 |  |

| 5.4.9             | Mode selection hysteresis                  | V <sub>DDIO_HYS</sub>  | 0.2      | 0.5       | 1.0  | V    | _                                                                                                                                 |  |

| $V_{DD}	ext{-}Mo$ | nitoring                                   |                        | <u>'</u> |           |      |      |                                                                                                                                   |  |

| 5.4.10            | Overvoltage threshold                      | $V_{ m DD\_THH}$       | 5.25     | 5.4       | 5.5  | V    | Voltage referred to                                                                                                               |  |

| 5.4.11            | Undervoltage threshold                     | $V_{ m DD\_THL}$       | 4.2      | 4.3       | 4.4  | V    | GNDABE                                                                                                                            |  |

| 5.4.12            | Test mode reduced Overvoltage threshold    | $V_{ m DD\_TEST\_H}$   | 4.2      | 4.3       | 4.4  | V    | _                                                                                                                                 |  |

| 5.4.13            | Test mode increased Undervoltage threshold | $V_{ m DD\_TEST\_L}$   | 5.25     | 5.4       | 5.5  | V    |                                                                                                                                   |  |

| 5.4.14            | Filter time for glitch suppression         | $t_{FIL}$              | 60       | 100       | 135  | μS   | _                                                                                                                                 |  |

| 5.4.15            | Maximum Slew Rate on VDD <sup>1)</sup>     | $V_{ m DD\_slew}$      | _        | -         | 0.5  | V/µs | _                                                                                                                                 |  |

<sup>1)</sup> Not subject to production test; specified by design

**Logic Inputs and Outputs**

# 6 Logic Inputs and Outputs

The threshold specifications for the logic inputs are compatible to both 5 and 3.3 V standard CMOS microcontroller ports. All inputs (except  $\overline{ABE}$ ) feature internal pull-up current sources. The logic output SO is supplied by  $V_{\rm DDIO}$ .  $V_{\rm DDIO}$  can be supplied with either 5 or 3.3 V, so the output thresholds of SO can be configured to the required I/O voltage.

#### **Electrical Characteristics: Control Inputs**

$V_{\rm S}$  = 5 V to 28 V;  $V_{\rm DD}$  = 5.0 V;  $T_{\rm j}$  = -40 ·C to 150 ·C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.    | Parameter                         | Symbol              | Limit Values        |      |                      | Unit | Test Conditions                                                        |

|---------|-----------------------------------|---------------------|---------------------|------|----------------------|------|------------------------------------------------------------------------|

|         |                                   |                     | Min.                | Тур. | Max.                 |      |                                                                        |

| N1, IN2 |                                   |                     |                     |      | -                    |      |                                                                        |

| 6.0.1   | Low level                         | $V_{INx\_L}$        | -0.3                | _    | 1.0                  | V    | _                                                                      |

| 6.0.2   | High level                        | $V_{INx\_H}$        | 2.0                 | _    | V <sub>DD</sub> +0.3 | ٧    | _                                                                      |

| 6.0.3   | Hysteresis                        | $V_{INx\_HYS}$      | 0.2                 | _    | 1.0                  | ٧    | _                                                                      |

| 6.0.4   | Input Current (Pull Up)           | $I_{INx}$           | -30                 | -20  | -10                  | μΑ   | $0 \text{ V} < V_{\text{INx}} < 2.1 \text{ V}$                         |

| 6.0.5   |                                   |                     | 0                   | 2    | 5                    | μΑ   | V <sub>INx</sub> > 3.0 V                                               |

| 6.0.6   | Input Capacity <sup>1)</sup>      | C <sub>INx</sub>    | _                   | _    | 20                   | pF   | 2)                                                                     |

| DIS     |                                   |                     |                     |      |                      | 1-   |                                                                        |

| 3.0.7   | Low level                         | $V_{DIS\_L}$        | -0.3                | _    | 1.0                  | ٧    | _                                                                      |

| 8.0.8   | High level                        | $V_{DIS\_H}$        | 2.0                 | _    | V <sub>DD</sub> +0.3 | V    | _                                                                      |

| 5.0.9   | Hysteresis                        | $V_{DIS\_HYS}$      | 0.2                 | _    | 1.0                  | V    | _                                                                      |

| 3.0.10  | Input Current (Pull Up)           | $I_{DIS}$           | -200                | -125 | -50                  | μA   | 0 V < V <sub>DIS</sub> < 2.1 V                                         |

| 6.0.11  |                                   | 3.0                 | 0                   | 2    | 5                    | μΑ   | V <sub>DIS</sub> > 3.0 V                                               |

| 5.0.12  | Input Capacity <sup>1)</sup>      | C <sub>DIS</sub>    | _                   | _    | 20                   | pF   | 2)                                                                     |

| 3.0.13  | Minimum Pulse Width <sup>1)</sup> | $t_{\sf DIS}$       | 0.4                 | 0.8  | 1.5                  | μs   | _                                                                      |

| ABE     |                                   | 1                   |                     |      |                      | '    |                                                                        |

| 6.0.14  | Output low-level voltage          | $V_{ABE\_OUTL}$     | _                   | _    | 1.2                  | V    | $V_{\rm DD\_THH} < V_{\rm DD} < 18~{\rm V}$ $I_{\rm ABE} < 5~{\rm mA}$ |

| 6.0.15  |                                   |                     | _                   | -    | 1.0                  | V    | $ I_{\rm ABE} < 1~{\rm mA} $                                           |

| 5.0.16  | Input threshold high              | $V_{ABE\_INH}$      | 0.7*V <sub>DD</sub> | _    | _                    | V    | _                                                                      |

| 5.0.17  | Input threshold low               | $V_{ABE\_INL}$      | _                   | _    | 0.3*V <sub>DD</sub>  | V    | _                                                                      |

| 3.0.18  | Hysteresis                        | $V_{ABE\_INHY}$     | 0.2                 | _    | 1.0                  | V    | _                                                                      |

| 5.0.19  | Minimum pulse width <sup>1)</sup> | $t_{ABE}$           | 0.4                 | 0.8  | 1.5                  | μs   | _                                                                      |

| 6.0.20  | ABE Input current (Pull           | -I <sub>ABE_L</sub> | 20                  | 40   | 120                  | μА   | 1.5 V < V <sub>ABE</sub> < 18 V                                        |

| 6.0.21  | Down)                             |                     | 0                   | _    | 60                   | μΑ   | 0 V < V <sub>ABE</sub> < 1.5 V                                         |

| SI      | I                                 |                     |                     |      |                      |      | · · · · · · · · · · · · · · · · · · ·                                  |

| 5.0.22  | Low level                         | $V_{SI\_L}$         | -0.3                | _    | 1.0                  | V    | _                                                                      |

| 5.0.23  | High level                        | V <sub>SI_H</sub>   | 2.0                 | _    | V <sub>DD</sub> +0.3 | V    | _                                                                      |

| 5.0.24  | Hysteresis                        | $V_{SI\_HYS}$       | 0.2                 | _    | 1.0                  | V    | _                                                                      |

| 5.0.25  | Input Current (Pull Up)           | $I_{SI}$            | -30                 | -20  | -10                  | μΑ   | 0 V < V <sub>SI</sub> < 2.1 V                                          |

| 3.0.26  | Input Capacity <sup>1)</sup>      | C <sub>SI</sub>     | 1                   |      | 14                   | pF   | 2)                                                                     |

#### **Logic Inputs and Outputs**

#### **Electrical Characteristics: Control Inputs** (cont'd)

$V_{\rm S}$  = 5 V to 28 V;  $V_{\rm DD}$  = 5.0 V;  $T_{\rm j}$  = -40 ·C to 150 ·C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                        | Symbol               | Liı                  | Limit Values |                        |    | <b>Test Conditions</b>                              |  |

|--------|----------------------------------|----------------------|----------------------|--------------|------------------------|----|-----------------------------------------------------|--|

|        |                                  |                      | Min.                 | Тур.         | Max.                   |    |                                                     |  |

| SCK    | 1                                |                      | <u> </u>             |              |                        |    |                                                     |  |

| 6.0.27 | Low level                        | $V_{SCK\_L}$         | -0.3                 | _            | 1.0                    | V  | _                                                   |  |

| 6.0.28 | High level                       | $V_{SCK\_H}$         | 2.0                  | _            | V <sub>DD</sub> +0.3   | V  | _                                                   |  |

| 6.0.29 | Hysteresis                       | $V_{SCK\_HYS}$       | 0.2                  | _            | 1.0                    | V  | _                                                   |  |

| 6.0.30 | Input Current (Pull Up)          | $I_{SCK}$            | -30                  | -20          | -10                    | μΑ | $0 \text{ V} < V_{\text{SCK}} < 2.1 \text{ V}$      |  |

| 6.0.31 | Input Capacity <sup>1)</sup>     | C <sub>SCK</sub>     | _                    | _            | 14                     | pF | 2)                                                  |  |

| SS/SF  |                                  |                      |                      |              |                        |    |                                                     |  |

| 6.0.32 | Low level                        | $V_{\mathrm{SS\_L}}$ | -0.3                 | _            | 1.0                    | V  | _                                                   |  |

| 6.0.33 | High level                       | $V_{\mathrm{SS\_H}}$ | 2.0                  | _            | $V_{\mathrm{DD}}$ +0.3 | V  | _                                                   |  |

| 6.0.34 | Hysteresis                       | $V_{\rm SS\_HYS}$    | 0.2                  | _            | 1.0                    | V  | _                                                   |  |

| 6.0.35 | Input Current in SPI             | $I_{\rm SS}$         | -30                  | -20          | -10                    | μΑ | $0 \text{ V} < V_{SS} < 2.1 \text{ V}$              |  |

| 6.0.36 | mode (Pull Up)                   |                      | -30                  | _            | 5                      | μΑ | $2.1 \text{ V} < V_{SS} < 3.0 \text{ V}$            |  |

| 6.0.37 |                                  |                      | 0                    | 2            | 5                      | μΑ | V <sub>SS</sub> > 3.0 V                             |  |

| 6.0.38 | Input Current in SF              | $I_{\mathrm{SF}}$    | 0                    | 2            | 5                      | μΑ | $V_{\rm SF}$ = 5.0 V, SF inactive                   |  |

| 6.0.39 | mode (Open Drain)                |                      | 300                  | _            | _                      | μΑ | $V_{\rm SF}$ = 1.0 V, SF active                     |  |

| 6.0.40 | Input Capacity <sup>1)</sup>     | $C_{SS}$             | _                    | _            | 15                     | pF | 2)                                                  |  |

| so     |                                  |                      |                      |              |                        |    |                                                     |  |

| 6.0.41 | Low level                        | $V_{SO\_L}$          | 0.0                  | _            | 0.4                    | V  | $I_{\rm SO}$ = 2 mA                                 |  |

| 6.0.42 | High level                       | $V_{SO\_H}$          | $V_{\rm DDIO}$ -0.75 | _            | $V_{DDIO}$             | V  | $I_{\rm SO}$ = -2 mA 2.9 V < $V_{\rm DDIO}$ < 5.5 V |  |

| 6.0.43 | Output capacitance <sup>1)</sup> | $C_{SO}$             | _                    | _            | 19                     | pF | In tristate <sup>2)</sup>                           |  |

| 6.0.44 | Leakage current                  | $I_{SO}$             | -2                   | _            | 2                      | μА | In tristate $0 < V_{SO} < V_{DDIO}$                 |  |

<sup>1)</sup> Not subject to production test; specified by design

<sup>2)</sup>  $V_{\text{bias}}$  = 2 V;  $V_{\text{test}}$  = 20 mVpp; f = 1 MHz

## 7 Power Stages

The TLE8209-2SA contains four n-channel power-DMOS transistors that can be used in an H-bridge or in dual half bridge configuration.

Integrated circuits protect the outputs against overcurrent and over-temperature, in case of short-circuit to ground, to the supply voltage or across the load. Positive and negative voltage spikes, which occur when switching inductive loads, are limited by integrated freewheeling diodes (body diodes of power-DMOS).

#### 7.1 Parallel or SPI Control

By default the setting of the power switches is controlled by the Inputs IN1, IN2 (parallel control). The outputs OUT1 and OUT2 are set to High (high-side switch ON, low-side switch OFF) or Low (high-side switch OFF, low-side switch ON) by the parallel inputs IN1 and IN2, respectively. In SPI mode there is also the option to control the outputs via the SPI bits SIN1 and SIN2 of the SPI configuration register. To switch to SPI control the bit MUX has to be set to '0'.

In addition, the outputs can be disabled (set to tristate, high- and low-side switch OFF) by the disable input DIS and the bidirectional reset pin ABE. Disabling sets the device to parallel control

**Table 1** shows the different options for the output control.

#### 7.2 H-Bridge or Single Switch Usage

The IC can be set to H-bridge mode or single-switch mode by SPI. This setting changes the behavior of the device in the following features:

- current limiting

- · overcurrent shut-down

- · open load diagnosis

Table 1 Functional Truth Table

| Pos.                               | DIS | ABE | IN1 | IN2 | SPI<br>MUX | SPI<br>SIN1 | SPI<br>SIN2 | OUT1 | OUT2 |

|------------------------------------|-----|-----|-----|-----|------------|-------------|-------------|------|------|

| Forward, parallel ctrl.            | L   | Н   | Н   | L   | 1          | X           | X           | Н    | L    |

| Reverse, parallel ctrl.            | L   | Н   | L   | Н   | 1          | Х           | Х           | L    | Н    |

| Free-wheeling low, parallel ctrl.  | L   | Н   | L   | L   | 1          | Х           | Х           | L    | L    |

| Free-wheeling high, parallel ctrl. | L   | Н   | Н   | Н   | 1          | Х           | Х           | Н    | Н    |

| Forward, SPI ctrl.                 | L   | Н   | Х   | Х   | 0          | 1           | 0           | Н    | L    |

| Reverse, SPI ctrl.                 | L   | Н   | Х   | Х   | 0          | 0           | 1           | L    | Н    |

| Free-wheeling low, SPI ctrl.       | L   | Н   | Х   | Х   | 0          | 0           | 0           | L    | L    |

| Free-wheeling high, SPI ctrl.      | L   | Н   | Х   | Х   | 0          | 1           | 1           | Н    | Н    |

| Disabled by DIS                    | Н   | Х   | Х   | Х   | Х          | Х           | Х           | Z    | Z    |

| Disabled by ABE                    | Х   | L   | Х   | Х   | Х          | Х           | Х           | Z    | Z    |

Table 2 OUT States

| OUT | High-Side DMOS | Low-Side DMOS |  |

|-----|----------------|---------------|--|

| Н   | ON             | OFF           |  |

| L   | OFF            | ON            |  |

| Z   | OFF            | OFF           |  |

# 7.3 Electrical Characteristics Power Stages

#### **Electrical Characteristics: Power Stage**

$V_{\rm S}$  = 5 V to 28 V;  $V_{\rm DD}$  = 5.0 V,  $T_{\rm j}$  = -40 ·C to 150 ·C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                                            | Symbol                                | Limit Values |             |     | Unit | <b>Test Conditions</b>                                             |  |

|--------|------------------------------------------------------|---------------------------------------|--------------|-------------|-----|------|--------------------------------------------------------------------|--|

|        |                                                      |                                       | Min.         | Min. Typ. I |     |      |                                                                    |  |

| Power  | Outputs OUT1, OUT2                                   | -                                     | '            |             | "   |      |                                                                    |  |

| 7.3.1  | Switch on resistance low                             | $R_{OUT1L}$                           | _            | 125         | _   | mΩ   | $I_{\text{OUTx}} = 3 \text{ A}; T_{\text{j}} = 25^{\circ}\text{C}$ |  |

|        | side                                                 | $R_{OUT2L}$                           | _            | 215         | 250 |      | $I_{\text{OUTx}}$ = 3 A; $T_{\text{j}}$ = 150°C                    |  |

| 7.3.2  | Switch on resistance high                            | $R_{OUT1H}$                           | _            | 115         | _   | mΩ   | $I_{\text{OUTx}} = 3 \text{ A}; T_{\text{j}} = 25^{\circ}\text{C}$ |  |

|        | side                                                 | $R_{OUT2H}$                           | _            | 200         | 240 |      | $I_{OUTx}$ = 3 A; $T_{j}$ = 150°C                                  |  |

| 7.3.3  | Leakage current                                      | $I_{ m OUT1(off)} \ I_{ m OUT2(off)}$ | -200         | _           | 200 | μΑ   | Output stage switched of $V_S = 13 \text{ V}$                      |  |

| 7.3.4  | Free-wheel diode forward voltage                     | $U_{D}$                               | _            | 0.9         | 1.1 | V    | I <sub>D</sub> = 3 A                                               |  |

| 7.3.5  | Free-wheel diode reverse recovery time <sup>1)</sup> | $t_{rr}$                              | _            | _           | 100 | ns   | _                                                                  |  |

| Output | Switching Times - Fast Sle                           | w Rate                                | ·            |             | ·   |      |                                                                    |  |

| 7.3.6  | Rise time HS                                         | t <sub>r (HS)</sub>                   | 3.5          | 6.0         | 10  | μS   | SPI bit SL='0'                                                     |  |

| 7.3.7  | Fall time HS                                         | t <sub>f (HS)</sub>                   | 3.5          | 6.0         | 10  |      | $V_{\rm S}$ = 818 V; $I_{\rm OUT}$ = 3 A                           |  |

| 7.3.8  | Rise time LS                                         | $t_{\rm r(LS)}$                       | 3.5          | 6.0         | 8.5 |      |                                                                    |  |

| 7.3.9  | Fall time LS                                         | $t_{f(LS)}$                           | 3.5          | 6.0         | 8.5 |      |                                                                    |  |

| Output | Switching Times - Slow Sle                           | w Rate                                |              |             |     |      |                                                                    |  |

| 7.3.10 | Rise time HS                                         | $t_{\rm r(HS)}$                       | 15           | 30          | 48  | μS   | SPI bit SL='1'                                                     |  |

| 7.3.11 | Fall time HS                                         | $t_{f  (HS)}$                         | 15           | 30          | 48  |      | $V_{\rm S}$ = 818 V; $I_{\rm OUT}$ = 3 A                           |  |

| 7.3.12 | Rise time LS                                         | $t_{\rm r(LS)}$                       | 18           | 30          | 48  |      |                                                                    |  |

| 7.3.13 | Fall time LS                                         | $t_{f(LS)}$                           | 18           | 30          | 48  |      |                                                                    |  |

|        | Delay - Parallel Control, Fa                         | st Slew Rat                           | :e           |             |     |      |                                                                    |  |

| 7.3.14 | Output on-delay                                      | $t_{\sf don}$                         | _            | _           | 12  | μS   | $V_{\rm S}$ = 818 V; $I_{\rm OUT}$ = 3 A                           |  |

| 7.3.15 | Output off-delay                                     | $t_{doff}$                            | _            | _           | 7   | μS   |                                                                    |  |

| Output | Delay - SPI Control, Fast S                          | lew Rate                              |              |             |     |      |                                                                    |  |

| 7.3.16 | Output on-delay                                      | $t_{\sf don}$                         | _            | _           | 13  | μS   | $V_{\rm S}$ = 818 V; $I_{\rm OUT}$ = 3 A                           |  |

| 7.3.17 | Output off-delay                                     | $t_{doff}$                            | _            | _           | 12  |      |                                                                    |  |

| Output | Delay - Parallel Control, Slo                        | ow Slew Ra                            | te           |             |     |      |                                                                    |  |

| 7.3.18 | Output on-delay                                      | $t_{\sf don}$                         | _            | _           | 41  | μS   | $V_{\rm S}$ = 818 V; $I_{\rm OUT}$ = 3 A                           |  |

| 7.3.19 | Output off-delay                                     | $t_{doff}$                            | _            | _           | 25  |      |                                                                    |  |

|        | Delay - SPI Control, Slow S                          | lew Rate                              |              |             |     |      |                                                                    |  |

| 7.3.20 | Output on-delay                                      | $t_{\sf don}$                         | _            |             | 42  | μS   | $V_{\rm S}$ = 818 V; $I_{\rm OUT}$ = 3 A                           |  |

| 7.3.21 | Output off-delay                                     | $t_{doff}$                            | -            | _           | 26  |      |                                                                    |  |

#### **Electrical Characteristics: Power Stage**

$V_{\rm S}$  = 5 V to 28 V;  $V_{\rm DD}$  = 5.0 V,  $T_{\rm j}$  = -40 ·C to 150 ·C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                          | Symbol         | Limit Values |      |      | Unit | <b>Test Conditions</b>                         |  |

|--------|------------------------------------|----------------|--------------|------|------|------|------------------------------------------------|--|

|        |                                    |                | Min.         | Тур. | Max. |      |                                                |  |

| Enable | and Disable Delay Times            |                |              |      | "    |      |                                                |  |

| 7.3.22 | Disable delay time, fast slew rate | $t_{\sf ddis}$ | _            | 8    | 20   | μS   | $V_{\rm S}$ = 818 V; $I_{\rm OUT}$ = 3 A       |  |

| 7.3.23 | Disable delay time, slow slew rate | $t_{ m ddis}$  | _            | 38   | 75   |      |                                                |  |

| 7.3.24 | Enable delay time, fast slew rate  | $t_{del}$      | _            | 8    | 20   |      |                                                |  |

| 7.3.25 | Enable delay time, slow slew rate  | $t_{del}$      | -            | 38   | 75   |      |                                                |  |

| 7.3.26 | Power on delay time                | $t_{ m del}$   | _            | 0.1  | 0.4  | ms   | $V_{\rm S}$ = on> output stage active, no load |  |

<sup>1)</sup> Not subject to production test - specified by design

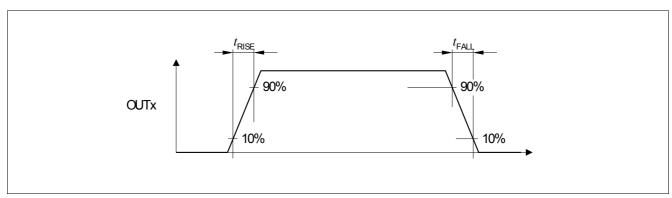

Figure 5 Output Switching Time

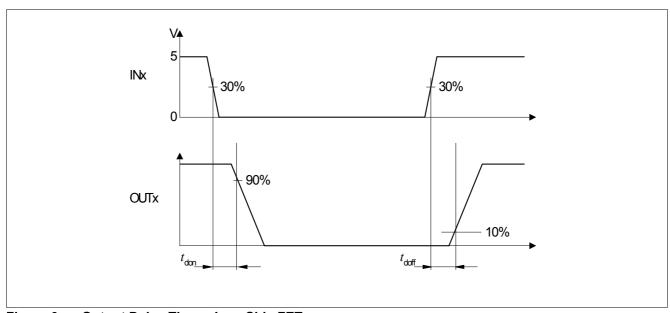

Figure 6 Output Delay Time - Low-Side FETs

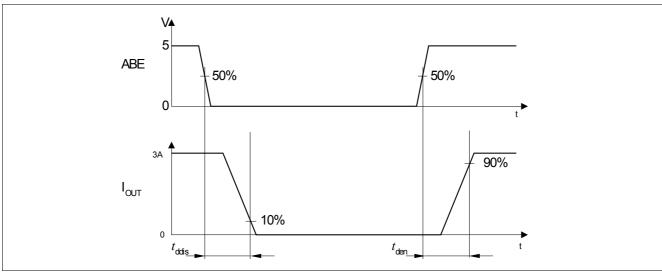

Figure 7 /ABE pin - Enable and Disable Delay Time

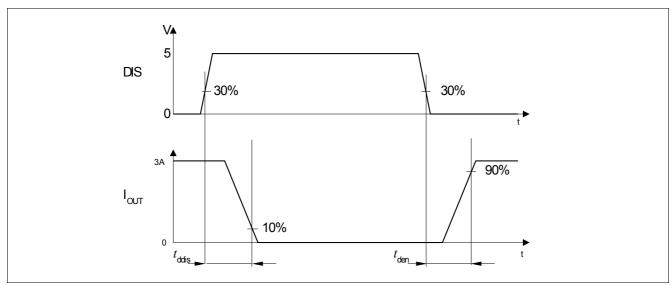

Figure 8 DIS pin - Enable and Disable Delay Time

# 8 Protection and Monitoring

Both output stages of the TLE8209-2SA are equipped with fault diagnostic functions:

- Short to battery voltage (SCB). Can be detected when low side-switches are turned on

- Short to ground (SCG). Can be detected when high side-switches are turned on

- · Open load (OL). Can be detected in inactive mode

- Over-temperature (OT). Can be detected in active and inactive mode

- VDD over- and under voltage (Chapter 5.2)

- · Battery under voltage detection. Can be detected in active and inactive mode

Individual detection for each output in single switch operation mode (SCB, SCG, OL) is possible. The corresponding diagnostics bits for each failure will be set in the SPI according to **Table 8 "Failure Encoding" on Page 29**.

#### 8.1 Diagnosis in Status Flag Mode

Instead of using the SPI interface for control and diagnosis of the TLE8209-2SA, the device can also be set into status flag mode by connecting pin VDDIO to GND as described in **Chapter 5.3**.

In status flag mode the pin SF will be pulled low in the following cases:

- undervoltage at VS

- bridge disabled by ABE or DIS

- bridge disabled by VDD monitoring

- bridge disabled by short circuit detection

- overtemperature shut down

SF will not be pulled low if  $V_{DD}$  is below the power on reset threshold (VDD\_POR).

#### 8.2 Current Limitation

To limit the output current at low power loss, a chopper current limitation is integrated. Current measurement for current limitation is done in the high side path. This requires high side freewheeling in case of active current limitation.

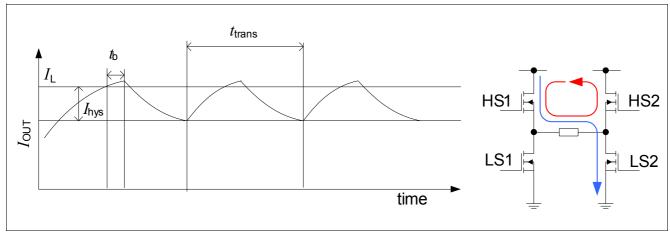

Figure 9 Chopper Current Limitation

**Figure 9** shows the behavior of the current limitation for over current detection in HS1. It applies accordingly also for HS2:

When the current in high-side switch of OUT1 (HS1) exceeds the limit  $I_L$  longer than the blanking time  $t_b$ , OUT2 is switched to high (e.g. LS2->OFF, HS2->ON), independent of the input signal at IN2. This leads to a slow-decay current decrease in the load and in HS1. As soon as the current falls below  $I_L$ - $I_{hvs}$ , OUT2 is switched back to normal

operation, i.e. the outputs follow the inputs according to the truth table. The current limit  $I_L$  can be programmed to four different values by setting the SPI bits CL1 and CL2 in the SPI configuration register. To avoid high chopper frequencies the time between two transients  $t_{trans}$  is limited.

Current limitation is available in H-bridge operation mode, not in single switch operation mode. This means, that the current limit, current limit hysteresis and blanking time has no effect in single switch operation mode.

#### 8.3 Temperature Dependent Current Reduction

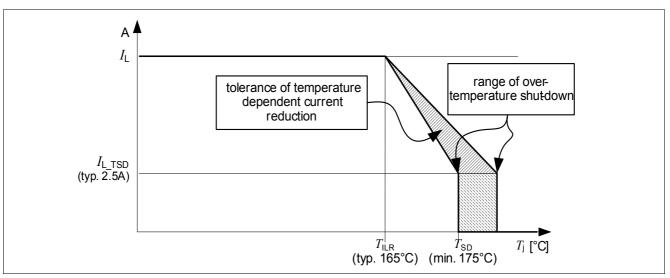

For  $T_{\rm ILR}$  <  $T_{\rm j}$  <  $T_{\rm SD}$  the current limit decreases from  $I_{\rm L}$  as set by the SPI to  $I_{\rm L\_TSD}$  = 2.5 A typ. as shown in Figure 10.

Figure 10 Temperature Dependent Current Reduction

#### 8.4 Short Circuit to Ground

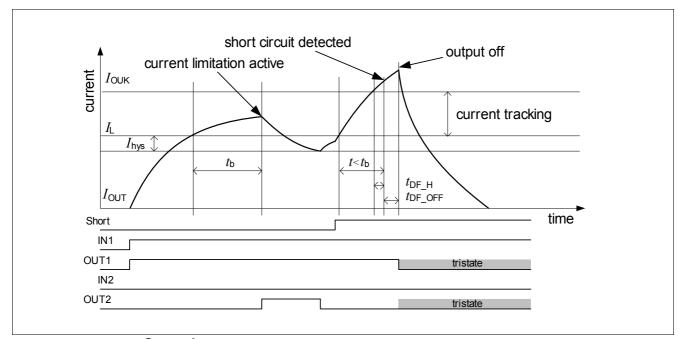

Figure 11 Short to Ground Detection

The short circuit to ground detection is activated when the current through one of the high side switches rises over the threshold  $I_{OUK}$  and remains higher than  $I_{OUK}$  for at least the filter time  $t_{DF}$  H within the blanking time  $t_b$ .

The output stage in which the short circuit was detected will be switched off within  $t_{\rm DF\ OFF}$ .

In H-bridge mode also the other output will be switched off after a short delay of  $t_{\text{DF del}}$  .

In single switch mode only the affected output will be switched off.

#### 8.5 Short Circuit to Battery

A short circuit to battery is detected in the same way as a short circuit to ground, only in the low side switch instead of the high side switch.

#### 8.6 Short Circuit across the Load

Short circuit over load is indicated by two failures - short circuit to ground on one output and short circuit to battery on the other output. Both failure bits will be set in the SPI diagnostics register. Both output stages will be turned off.

#### 8.7 Overtemperature

In case of high DC-currents, insufficient cooling or high ambient temperature, the chip temperature may rise above the thermal shut-down temperature  $T_{\rm SD}$  (see **Figure 10**). In that case, all output transistors are turned off.

#### 8.8 Undervoltage Shut-Down

If the supply voltage at the VS pins falls below the undervoltage detection threshold  $V_{UV\_OFF}$ , the outputs switches are turned off. As soon as  $V_S$  rises above  $V_{UV\_ON}$  again, the device is returning to normal operation.

#### 8.9 Open Load Diagnosis

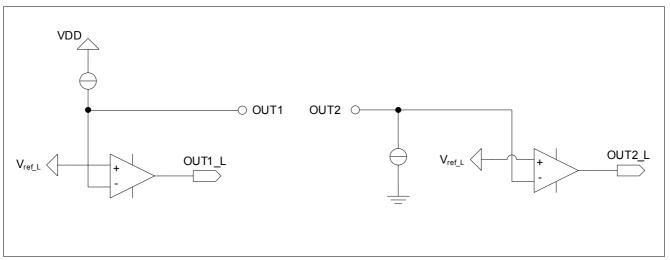

Open load diagnosis is only possible if outputs are switched off by DIS or  $\overline{ABE}$ . The diagnostic current sources are deactivated in status flag mode. Diagnostic current sources are disconnected if outputs are active. That means that the diagnostic current sources are also disconnected if the outputs are deactivated due to short circuit. The open load detection in H-bridge mode is different from the open load detection in single switch mode.

#### Open Load Detection in H-Bridge mode

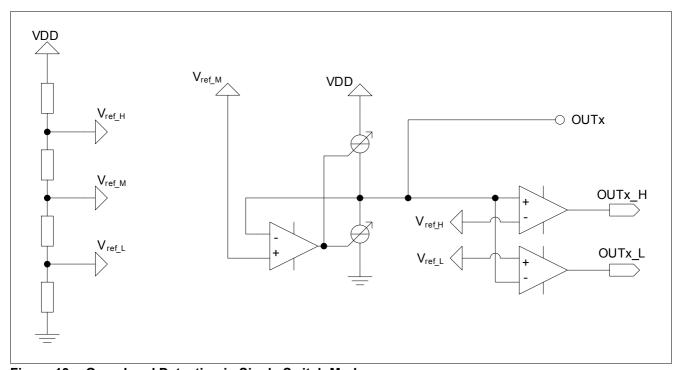

Figure 12 Open Load Detection in H-Bridge Mode

Table 3 Open Load Detection in H-Bridge Mode

| VOUT1                | OUT1_L | VOUT2                | OUT2_L | Diagnostic | Comment                       |

|----------------------|--------|----------------------|--------|------------|-------------------------------|

| < V <sub>ref_L</sub> | Н      | < V <sub>ref_L</sub> | Н      | Load o.k.  | pull down current is stronger |

| < V <sub>ref_L</sub> | Н      | > V <sub>ref_L</sub> | L      | Load o.k.  | transient area                |

| > V <sub>ref_L</sub> |        | < V <sub>ref_L</sub> | Н      | Open Load  |                               |

| > V <sub>ref_L</sub> | L      | > V <sub>ref_L</sub> | L      | Load o.k.  | transient area                |

#### **Open Load Detection in Single Switch Mode**

Figure 13 Open Load Detection in Single Switch Mode

Table 4 Open Load Detection in Single Switch Mode

| VOUTx (OFF State)                                                    | OUTx_H | OUTx_L | Diagnostic | Comment                |

|----------------------------------------------------------------------|--------|--------|------------|------------------------|

| $\overline{V_{\rm OUTx}} < V_{\rm ref\_L}$                           | L      | Н      | o.k.       | Load to ground         |

| $\overline{V_{\text{ref\_L}} < V_{\text{OUTx}} < V_{\text{ref\_H}}}$ | L      | L      | Open Load  | Output open            |

| $\overline{V_{\rm OUTx}} > V_{\rm ref\_H}$                           | Н      | L      | o.k.       | Load to V <sub>S</sub> |

#### 8.10 Electrical Characteristics

#### **Electrical Characteristics: Protection and Monitoring**

$V_{\rm S}$  = 5 V to 28 V;  $V_{\rm DD}$  = 5.0 V,  $T_{\rm j}$  = -40 ·C to 150 ·C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.     | Parameter                                        | Symbol                                 |      | Limit Va | lues | Unit | Test Conditions                                         |  |

|----------|--------------------------------------------------|----------------------------------------|------|----------|------|------|---------------------------------------------------------|--|

|          |                                                  |                                        | Min. | Тур.     | Max. |      |                                                         |  |

| Choppe   | r Current Limitation                             |                                        |      |          | ·    | ·    |                                                         |  |

| 8.10.1   | Current Limit                                    | $ I_{L1} $                             | 1.0  | 1.5      | 2.0  | Α    | -40 °C < $T_{\rm j}$ < $T_{\rm ILR}$                    |  |

| 8.10.2   |                                                  | $ I_{L2} $                             | 3.3  | 4.0      | 4.7  |      | Dependent on SPI                                        |  |

| 8.10.3   |                                                  | $ I_{L3} $                             | 5.5  | 6.6      | 7.7  |      | setting; Default = $I_{L3}$                             |  |

| 8.10.4   |                                                  | $ I_{L4} $                             | 7.7  | 8.6      | 10.0 |      |                                                         |  |

| 8.10.5   | Current Limit Hysteresis                         | $I_{hys}$                              | 0    | 0.25     | 0.40 | Α    | $-40  ^{\circ}\text{C} < T_{\text{j}} < T_{\text{ILR}}$ |  |

| 8.10.6   | Blanking time                                    | t <sub>b</sub>                         | 8    | 11       | 15   | μs   | -                                                       |  |

| 8.10.7   | Time between transients                          | $t_{trans}$                            | 90   | _        | 130  | μS   | _                                                       |  |

| Tempera  | ature Dependent Current L                        |                                        |      |          |      |      | 1                                                       |  |

| 8.10.8   | Current Limit at T <sub>SD</sub>                 | I <sub>L_TSD</sub>                     | 1.4  | 2.5      | 3.6  | Α    | _                                                       |  |

| 8.10.9   | Start of current limit reduction                 | $T_{ILR}$                              | 150  | 165      | _    | °C   | -                                                       |  |

| 8.10.10  | Thermal shut-down                                | $T_{SD}$                               | 175  | _        | _    | °C   | _                                                       |  |

| 8.10.11  | Range of temperature dependent current reduction | $T_{\rm SD}$ - $T_{\rm ILR}$           | 20   | 25       | 30   | °C   | _                                                       |  |

| Short Ci | rcuit Detection to GND                           | - 1                                    |      |          |      |      |                                                         |  |

| 8.10.12  | Short circuit detection                          | $ I_{\text{OUKH1}} $                   | 2.5  | 5.0      | 6.5  | Α    | $-40  ^{\circ}\text{C} < T_{\text{j}} < T_{\text{ILR}}$ |  |

| 8.10.13  | current (HS)                                     | $ I_{\text{OUKH2}} $                   | 5.0  | 7.3      | 10   |      | Dependent on SPI-                                       |  |

| 8.10.14  |                                                  | $ I_{OUKH3} $                          | 7.5  | 9.5      | 11.5 |      | setting for $ I_L $ ; Default =                         |  |

| 8.10.15  | -                                                | $ I_{OUKH4} $                          | 9.5  | 11.8     | 17.4 |      | $I_{OUKH3}$                                             |  |

| 8.10.16  | Current tracking                                 | $ I_{\text{OUKH1}}  -  I_{\text{L1}} $ | 2.0  | 3.5      | 5.0  | Α    | <del>-</del>                                            |  |

| 8.10.17  |                                                  | $ I_{\text{OUKH2}}  -  I_{\text{L2}} $ |      | 3.3      | 5.0  |      |                                                         |  |

| 8.10.18  | -                                                | $ I_{\text{OUKH3}}  -  I_{\text{L3}} $ |      | 3.2      | 5.0  |      |                                                         |  |

| 8.10.19  |                                                  | $ I_{\text{OUKH4}}  -  I_{\text{L4}} $ | 1.8  | 3.0      | 5.0  |      |                                                         |  |

| Short Ci | rcuit Detection to VS                            |                                        |      |          |      |      |                                                         |  |

| 8.10.20  | Short circuit detection                          | $ I_{OUKL1} $                          | 2.5  | 4.6      | 6.5  | Α    | $-40  ^{\circ}\text{C} < T_{j} < T_{ILR}$               |  |

| 8.10.21  | current (LS)                                     | $ I_{OUKL2} $                          | 5.0  | 7.9      | 10   |      | Dependent on SPI-                                       |  |

| 8.10.22  | -                                                | $ I_{OUKL3} $                          | 7.5  | 9.8      | 11.5 |      | setting for $ I_L $ ; Default =                         |  |

| 8.10.23  |                                                  | $ I_{\rm OUKL4} $                      | 9.5  | 14       | 17.4 |      | I <sub>OUKL3</sub>                                      |  |

| 8.10.24  | Current tracking                                 | $ I_{\text{OUKL1}}  -  I_{\text{L1}} $ | 1.5  | 3.0      | 5.0  | Α    |                                                         |  |

| 8.10.25  |                                                  | $ I_{\text{OUKL2}}  -  I_{\text{L2}} $ | 2.0  | 4.0      | 5.5  |      |                                                         |  |

| 8.10.26  |                                                  | $ I_{\rm OUKL3} $ - $ I_{\rm L3} $     |      | 3.5      | 5.5  |      |                                                         |  |

| 8.10.27  |                                                  | $ I_{\text{OUKL4}}  -  I_{\text{L4}} $ | 2.0  | 5.1      | 8.0  |      |                                                         |  |

#### **Electrical Characteristics: Protection and Monitoring**

$V_{\rm S}$  = 5 V to 28 V;  $V_{\rm DD}$  = 5.0 V,  $T_{\rm j}$  = -40 ·C to 150 ·C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.     | Parameter                                                                    | Symbol                 | Limit Values                      |                          |                                | Unit | Test Conditions                       |  |

|----------|------------------------------------------------------------------------------|------------------------|-----------------------------------|--------------------------|--------------------------------|------|---------------------------------------|--|

|          |                                                                              |                        | Min.                              | Тур.                     | Typ. Max.                      |      |                                       |  |

| Short Ci | rcuit Detection Timing                                                       |                        |                                   |                          |                                |      |                                       |  |

| 8.10.28  | Delay time for fault detection                                               | $t_{DF\_H}, t_{DF\_L}$ | 1                                 | 2                        | 5                              | μs   | _                                     |  |

| 8.10.29  | Time from detected fault to high impedance of output <sup>1)</sup>           | $t_{DF\_OFF}$          | _                                 | _                        | 4                              | μs   | -                                     |  |

| 8.10.30  | Delay time between<br>switching off of the output<br>stages in short circuit | t <sub>DF_del</sub>    | 5                                 | 17                       | 40                             | μs   | _                                     |  |

| Open Lo  | oad                                                                          | 1                      |                                   |                          |                                | •    |                                       |  |

| 8.10.31  | Open Load Diagnostic Filter Time <sup>1)</sup>                               | $t_{ m OL\_DIAG}$      | 60                                | -                        | 135                            | μs   | _                                     |  |

| 8.10.32  | Low Diagnosis Threshold                                                      | V <sub>ref_L</sub>     | 0.4 *<br>V <sub>DD</sub> -<br>0.2 | 0.4 *<br>V <sub>DD</sub> | 0.4 * V <sub>DD</sub><br>+ 0.2 | V    | -                                     |  |

| 8.10.33  | High Diagnosis Threshold                                                     | V <sub>ref_H</sub>     | 0.8 *<br>V <sub>DD</sub> -<br>0.2 | 0.8 *<br>V <sub>DD</sub> | 0.8 * V <sub>DD</sub><br>+ 0.2 | V    | _                                     |  |

| 8.10.34  | Diagnosis Bias Voltage                                                       | V <sub>ref_M</sub>     | 0.6 *<br>V <sub>DD</sub> -<br>0.2 | 0.6 *<br>V <sub>DD</sub> | 0.6 * V <sub>DD</sub><br>+ 0.2 | V    | _                                     |  |

| 8.10.35  | Positive Diagnostic Current                                                  | I <sub>DIA_P</sub>     | 300                               | 620                      | 980                            | μΑ   | V <sub>OUTx</sub> = 14 V              |  |

| 8.10.36  | (pull down current source)                                                   | _                      | 270                               | 610                      | 980                            | μΑ   | $V_{\text{OUTx}} = V_{\text{ref\_H}}$ |  |

| 8.10.37  | Negative Diagnostic                                                          | I <sub>DIA_N</sub>     | -350                              | -240                     | -100                           | μΑ   | V <sub>OUTx</sub> = 0 V               |  |

| 8.10.38  | Current                                                                      |                        | -350                              | -210                     | -80                            | μΑ   | $V_{\text{OUTx}} = V_{\text{ref\_L}}$ |  |

| 8.10.39  | Ratio of current sources (Pos/Neg)                                           | Ratio <sub>I_DIA</sub> | 2                                 | 2.9                      | 4                              | -    | -                                     |  |

| Undervo  | oltage                                                                       |                        |                                   | ·                        | ·                              |      |                                       |  |

| 8.10.40  | Undervoltage at $V_{\rm S}$                                                  | $V_{UVOFF}$            | 3.1                               | 3.7                      | 4.4                            | V    | Switch off threshold                  |  |

|          |                                                                              | $V_{UVON}$             | 3.3                               | 3.9                      | 4.6                            | V    | Switch on threshold                   |  |

|          |                                                                              | $V_{UVHY}$             | 100                               | 200                      | 400                            | mV   | Hysteresis                            |  |

| 8.10.41  | VS Undervoltage Detection Filter Time <sup>1)</sup>                          | $t_{\sf UV}$           | _                                 | -                        | 1.5                            | μs   |                                       |  |

|          |                                                                              |                        |                                   |                          |                                |      |                                       |  |

<sup>1)</sup> Not subject to production test; specified by design.

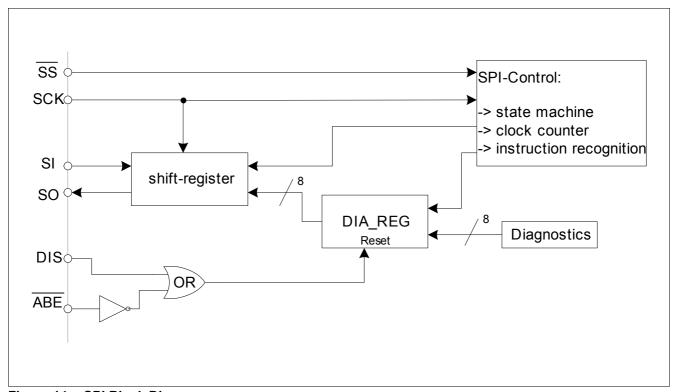

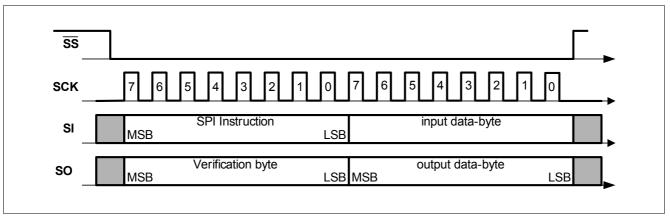

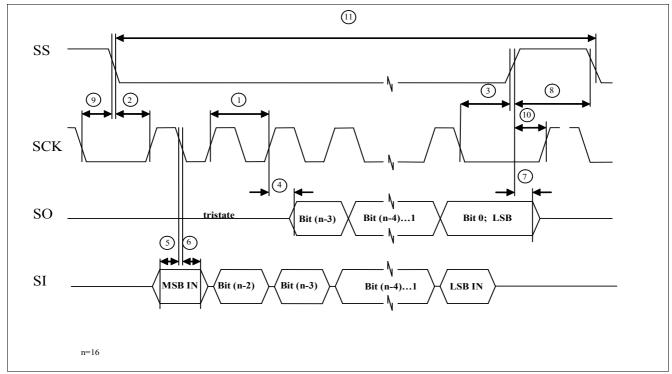

#### 9 SPI Interface

The serial SPI interface establishes a communication link between TLE8209-2SA and the systems microcontroller. The TLE8209-2SA always operates in slave mode whereas the controller provides the master function. The maximum baud rate is 2 MBaud.

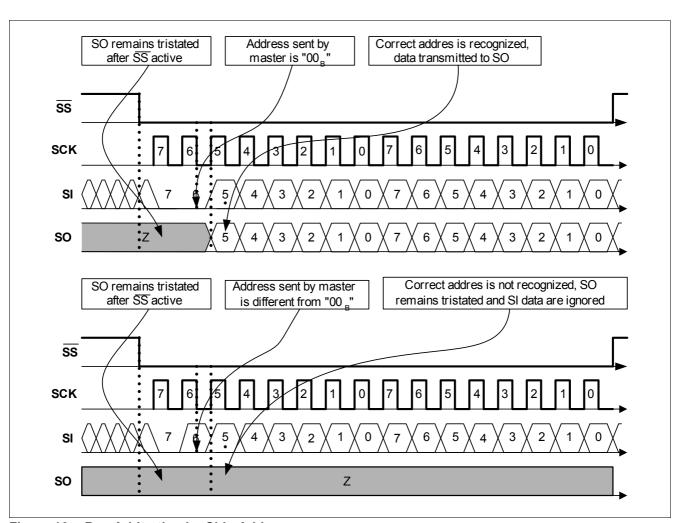

By applying an active slave select signal at  $\overline{SS}$  the TLE8209-2SA is selected by the SPI-master. SI is the data input (Slave In), SO the data output (Slave Out). Via SCK (Serial Clock Input) the SPI-clock is provided by the master. In case of inactive slave select signal (High) the data output SO goes into tristate.

The first two bits of an instruction may be used to establish an extended device-addressing. This gives the opportunity to operate up to 4 Slave-devices sharing one common SS signal from the Master-Unit (see Figure 16).

Figure 14 SPI Block Diagram

#### 9.1 General SPI Characteristics

- 1. During active reset conditions the SPI is driven into its default state. The output SO is set to high impedance (tristate). When reset becomes inactive, the state machine enters into a wait state for the next instruction.