# SC1549 Instantly Available ACPI Controller for Advanced Motherboards

# **POWER MANAGEMENT**

**PRELIMINARY**

### Description

The new ACPI specification extends the computers use by reducing boot time, enabling remote access and reducing power consumption.

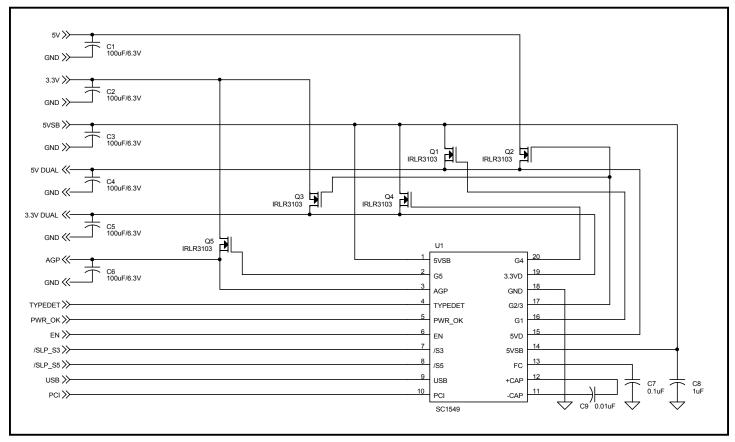

Semtech's SC1549, SC243x, SC112A with SC1175 or SC1114 with SC1110 provide all the voltages necessary for a Pentium 4 Brookdale-G ACPI system.

The SC1549 offers three independant supplies: a 5V dual supply for USB, a 3.3V dual supply for PCI or 3.3VSB and a 1.5V or 3.3V supply for AGP or 1.5VSB. The AGP supply is programmable using the system TYPEDET signal.

An on-board internal charge pump eliminates the need for P-channel MOSFETs and enables function from a single 5V supply (system 5VSB). Both dual outputs are over current protected.

### **Features**

- Complete programmable supply for instantly available PC systems

- ◆ 5V dual and 3.3V dual supplies are programmable to be active or inactive in S5

- Integrated AGP voltage supply with "TYPEDET" signal for 3.3V or 1.5V operation can be used to generate a 1.5V standby supply

- Integrated charge pump removes the need for PMOS FETs, enables single supply operation

- Over current protection on dual outputs

- ◆ TSSOP-20 package

### **Applications**

Instantly available motherboards

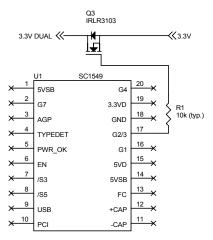

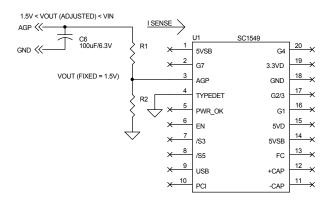

# Typical Application Circuit

# **PRELIMINARY**

# Absolute Maximum Ratings

Exceeding the specifications below may result in permanent damage to the device, or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not implied.

| Parameter                              | Symbol                | Maximum                   | Units |

|----------------------------------------|-----------------------|---------------------------|-------|

| Input Supply Voltage                   | V <sub>5VSB</sub>     | -0.3 to 7                 | V     |

| Logic Input Pins                       |                       | -0.3 to V <sub>5VSB</sub> | V     |

| Charge Pump Output Voltage             | V <sub>FC</sub>       | -0.3 to 13.2              | V     |

| Thermal Impedance Junction to Case     | $\theta_{	extsf{JC}}$ | 17                        | °C/W  |

| Thermal Resistance Junction to Ambient | $\theta_{JA}$         | 90.2                      | °C/W  |

| Operating Ambient Temperature Range    | T <sub>A</sub>        | 0 to 70                   | °C    |

| Operating Junction Temperature Range   | T <sub>J</sub>        | 0 to 125                  | °C    |

| Storage Temperature Range              | T <sub>STG</sub>      | -65 to +150               | °C    |

| Lead Temperature (Soldering) 10 Sec.   | T <sub>LEAD</sub>     | 300                       | °C    |

# Electrical Characteristics(1)

Unless specified: all applicable silver box supplies (3.3V, 5V, 5VSB)  $\pm$  5%, GND = 0V,  $V_{SENSE\ PINS} = V_{OUT(NOM)}$ ,  $T_A = 25^{\circ}C$ . Values in **bold** apply over full operating ambient temperature range.

| Parameter                             | Symbol             | Test Conditions                                  | Min   | Тур   | Max   | Units |

|---------------------------------------|--------------------|--------------------------------------------------|-------|-------|-------|-------|

| IN                                    |                    |                                                  |       |       |       |       |

| Supply Voltage                        | V <sub>5VSB</sub>  |                                                  | 4.5   |       | 5.5   | V     |

| Quiescent Current                     | I <sub>Q</sub>     | All states (S0, S3, S5, disabled)                |       | 10    | 15    | mA    |

|                                       |                    |                                                  |       |       | 20    |       |

| Undervoltage Lockout                  |                    |                                                  | •     |       |       |       |

| Threshold Voltage                     | V <sub>UVLO</sub>  | V <sub>5VSB</sub> Rising                         | 3.5   | 4.0   | 4.4   | V     |

| Logic Inputs (EN, PCI, PV             | VR_OK, /S          | 3, /S5, TYPEDET, USB)                            |       |       |       |       |

| Logic Pin Sink Current <sup>(2)</sup> | I <sub>sink</sub>  | V <sub>BIAS</sub> = 5V, all logic pins           |       | 0.1   | 1     | μA    |

| Logic Pin Source Current              | SOURCE             | EN, V <sub>EN</sub> = 0V                         |       | 0.5   | 3     | μA    |

|                                       |                    | PCI, TYPEDET, USB, $V_{PIN} = 0V$                |       | 50    | 200   |       |

|                                       |                    | /S3, PWR_OK, V <sub>PIN</sub> = 0V               |       | 100   | 400   |       |

|                                       |                    | /S5, V <sub>/S5</sub> = 0V                       |       | 150   | 600   |       |

| Threshold Voltage                     | V <sub>IH</sub>    |                                                  | 2.4   |       |       | V     |

|                                       | V <sub>L</sub>     |                                                  |       |       | 8.0   | V     |

| 3.3V Dual Output                      |                    |                                                  | •     |       |       | •     |

| Output Voltage(3)                     | V <sub>3.3VD</sub> | $1\text{mA} \le I_{\text{OUT}} \le 720\text{mA}$ | 3.250 | 3.300 | 3.350 | V     |

|                                       |                    |                                                  | 3.217 |       | 3.383 |       |

# **PRELIMINARY**

# Electrical Characteristics (Cont.)(1)

Unless specified: all applicable silver box supplies (3.3V, 5V, 5VSB)  $\pm$  5%, GND = 0V,  $V_{SENSE\ PINS} = V_{OUT(NOM)}$ ,  $T_A = 25^{\circ}C$ . Values in **bold** apply over full operating ambient temperature range.

| Parameter                                          | Symbol                  | Test Conditions                                                         | Min  | Тур                   | Max  | Units |

|----------------------------------------------------|-------------------------|-------------------------------------------------------------------------|------|-----------------------|------|-------|

| 3.3V Dual Output (Cont.)                           | 1                       |                                                                         |      |                       |      | 1     |

| Line Regulation <sup>(3)</sup> REG                 |                         | $V_{5VSB} = 4.75V$ to 5.25V, $I_{OUT} = 0A$                             | 0.0  |                       | 0.10 | %     |

| Load Regulation <sup>(3)</sup>                     | REG <sub>LOAD</sub>     | $V_{5VSB}$ = 5V, $I_{OUT}$ = 0A to 720mA                                |      | 0.01                  | 0.20 | %     |

| Gate 3 Drive Voltage <sup>(4)</sup>                | V <sub>G3(HI)</sub>     | I <sub>G3</sub> = 10μA                                                  | 8.00 | 8.75                  |      | V     |

|                                                    | V <sub>G3(LO)</sub>     | $I_{G3} = -10 \mu A$                                                    |      | 40                    | 100  | mV    |

| Gate 3 Drive Current <sup>(4)</sup>                | I <sub>G3(SOURCE)</sub> | V <sub>G3</sub> = 5V                                                    | 0.5  | 0.7                   |      | mA    |

|                                                    | I <sub>G3(SINK)</sub>   | V <sub>G3</sub> = 3V                                                    | -10  | -14                   |      |       |

| Gate 4 Drive Voltage <sup>(5)</sup>                | V <sub>G4(HI)</sub>     | $V_{3.3VD} = 3.2V, I_{G4} = 10\mu A$                                    | 8.00 | 8.75                  |      | V     |

|                                                    | V <sub>G4(LO)</sub>     | $V_{3.3VD} = 3.4V, I_{G4} = -10\mu A$                                   |      | 0.8                   | 1.0  |       |

| Gate 4 Drive Current <sup>(5)</sup>                | I <sub>G4(SOURCE)</sub> | $V_{3.3VD} = V_{OUT(NOM)} - 100 \text{mV}, V_{G4} = 5 \text{V}$         | 2    | 4                     |      | mA    |

|                                                    | I <sub>G4(SINK)</sub>   | $V_{3.3VD} = V_{OUT(NOM)} + 100 \text{mV}, V_{G4} = 3 \text{V}$         | -3.5 | 5                     |      |       |

| Sense Pin Bias Current                             | I <sub>3.3VD</sub>      | Sinking, V <sub>3.3VD</sub> = 3.3V                                      | -70  | -100                  | -130 | μA    |

| 5V Dual Output                                     |                         |                                                                         |      |                       |      |       |

| Gate 2 Drive Voltage <sup>(6)</sup>                | V <sub>G2(HI)</sub>     | I <sub>G2</sub> = 10μA                                                  | 8.00 | 8.75                  |      | V     |

|                                                    | V <sub>G2(LO)</sub>     | I <sub>G2</sub> = -10μA                                                 |      | 40                    | 100  | mV    |

| Gate 2 Drive Current <sup>(6)</sup>                | G2(SOURCE)              | V <sub>G2</sub> = 5V                                                    | 0.5  | 0.7                   |      | mA    |

|                                                    | I <sub>G2(SINK)</sub>   | V <sub>G2</sub> = 3V                                                    | -10  | -14                   |      |       |

| Gate 1 Drive Voltage <sup>(7)</sup>                | V <sub>G1(HI)</sub>     | I <sub>G1</sub> = 10μA                                                  | 8.00 | 8.75                  |      | V     |

|                                                    | V <sub>G1(LO)</sub>     | I <sub>G1</sub> = -10μA                                                 |      | 40                    | 100  | mV    |

| Gate 1 Drive Current <sup>(7)</sup>                | I <sub>G1(SOURCE)</sub> | V <sub>G1</sub> = 5V                                                    | 0.5  | 0.7                   |      | mA    |

|                                                    | I <sub>G1(SINK)</sub>   | V <sub>G1</sub> = 3V                                                    | -10  | -14                   |      |       |

| Sense Pin Bias Current(2)                          | I <sub>5VD</sub>        | V <sub>SVD</sub> = 5V                                                   |      |                       | 16   | μΑ    |

| AGP Output                                         |                         |                                                                         |      |                       |      |       |

| Output Voltage <sup>(8)</sup>                      | V <sub>AGP</sub>        | 1mA ≤ I <sub>OUT</sub> ≤ 720mA                                          | -2.0 | V <sub>OUT(NOM)</sub> | +2.0 | %     |

|                                                    |                         |                                                                         | -3.0 |                       | +3.0 |       |

| Line Regulation <sup>(8)</sup> REG <sub>LINE</sub> |                         | $V_{\text{5VSB}} = 4.75 \text{V to 5.25V}, I_{\text{OUT}} = 0 \text{A}$ |      | 0.01                  | 0.10 | %     |

| Load Regulation <sup>(8)</sup>                     | REG <sub>LOAD</sub>     | $V_{5VSB}$ = 5V, $I_{OUT}$ = 0A to 720mA                                |      | 0.01                  | 0.20 | %     |

| Gate 5 Drive Voltage <sup>(9)</sup>                | V <sub>G5(HI)</sub>     | $V_{AGP} = V_{OUT(NOM)} - 100 \text{mV}, I_{GS} = 10 \mu \text{A}$      | 8.00 | 8.75                  |      | V     |

|                                                    | V <sub>G5(LO)</sub>     | $V_{AGP} = V_{OUT(NOM)} + 100 \text{mV}, I_{G5} = -10 \mu \text{A}$     |      | 0.8                   | 1.0  | V     |

**PRELIMINARY**

# Electrical Characteristics (Cont.)(1)

Unless specified: all applicable silver box supplies (3.3V, 5V, 5VSB)  $\pm$  5%, GND = 0V,  $V_{SENSE\ PINS} = V_{OUT(NOM)}$ ,  $T_A = 25^{\circ}C$ . Values in **bold** apply over full operating ambient temperature range.

| Parameter                          | Symbol                                 | Test Conditions                                               | Test Conditions Min |      |      | Units             |  |  |  |

|------------------------------------|----------------------------------------|---------------------------------------------------------------|---------------------|------|------|-------------------|--|--|--|

| AGP Output (Cont.)                 |                                        |                                                               | -                   |      | '    | !                 |  |  |  |

| Gate 5 Drive Current(9)            | I <sub>G5(SOURCE)</sub>                | $V_{AGP} = V_{OUT(NOM)} - 100 \text{mV}, V_{G5} = 5 \text{V}$ | 2                   | 4    |      | mA                |  |  |  |

|                                    | I <sub>G5(SINK)</sub>                  | $V_{AGP} = V_{OUT(NOM)} + 100mV, V_{G5} = 3V$                 | -3.5                | -5   |      |                   |  |  |  |

| Sense Pin Bias Current             | I <sub>AGP</sub>                       | V <sub>AGP</sub> = 3.3V, TYPEDET = High                       | -235                | -340 | -445 | μA                |  |  |  |

|                                    |                                        | V <sub>AGP</sub> = 1.5V, TYPEDET = Low                        | -110                | -160 | -210 |                   |  |  |  |

| FC (Charge Pump)                   |                                        |                                                               |                     |      |      |                   |  |  |  |

| Output Voltage                     | V <sub>FC</sub>                        | V <sub>5VSB</sub> = 5V                                        | 9.0                 | 9.5  | 10.0 | V                 |  |  |  |

| Overcurrent Protection(10          | Overcurrent Protection <sup>(10)</sup> |                                                               |                     |      |      |                   |  |  |  |

| Trip Threshold V <sub>TH(OC)</sub> |                                        |                                                               | 30                  | 50   | 70   | %V <sub>OUT</sub> |  |  |  |

| Short Circuit Immunity(11)         |                                        |                                                               | 1                   |      | 75   | ms                |  |  |  |

### **Notes:**

- (1) This device is ESD sensitive. Use of standard ESD handling precautions is required.

- (2) Guaranteed by design.

- (3) Applies to S3 sleep state and S5 sleep state when the PCI pin is high.

- (4) Gate 3 is high in SO and low in the S3 and S5 sleep states.

- (5) Gate 4 is high in the S3 sleep state and the S5 sleep state when the PCI pin is high. Gate 4 is low in S0, and in the S5 sleep state when the PCI pin is low.

- (6) Gate 2 is high in SO and low in the S3 and S5 sleep states.

- (7) Gate 1 is high in the S3 sleep state and the S5 sleep state when the USB pin is high. Gate 1 is low in S0, and in the S5 sleep state when the USB pin is low.

- (8) Applies to SO only.  $V_{AGP} = 3.3V$  when TYPEDET is high and 1.5V when the TYPEDET pin is low.

- (9) Gate 5 is high whenever 5VSB is present and > UVLO, unless OCP has been tripped.

- (10) Applies to 3.3V Dual and 5V Dual outputs when enabled only. When an output is disabled, that output is not monitored for OCP. The AGP output does not have over current protection.

- (11) Minimum and maximum time limits for over current protection to trip when powered up (or enabled) into a shorted output and when a short is applied to an enabled, OCP protected output.

**PRELIMINARY**

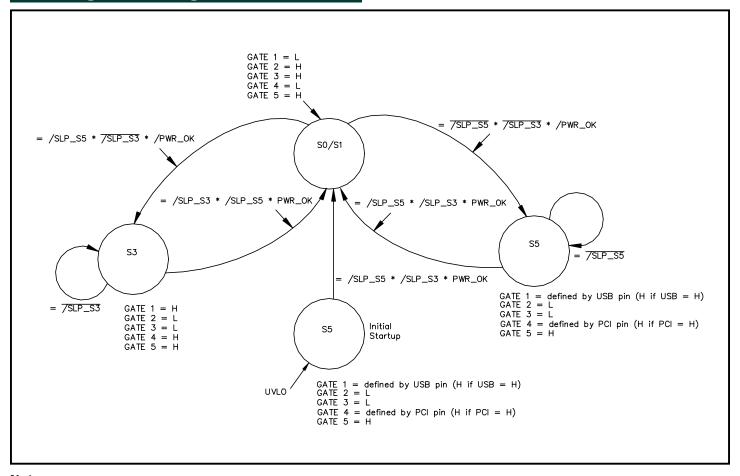

# State Diagram Showing Gate Drive Status

### Note:

(1) State machine will not allow illegal transitions such as S3 to S5. In order to get to S5 from S3, it is first necessary to enter S0.

POWER MANAGEMENT PRELIMINARY

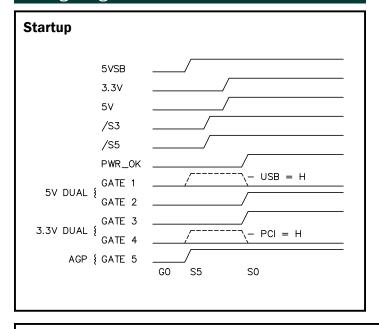

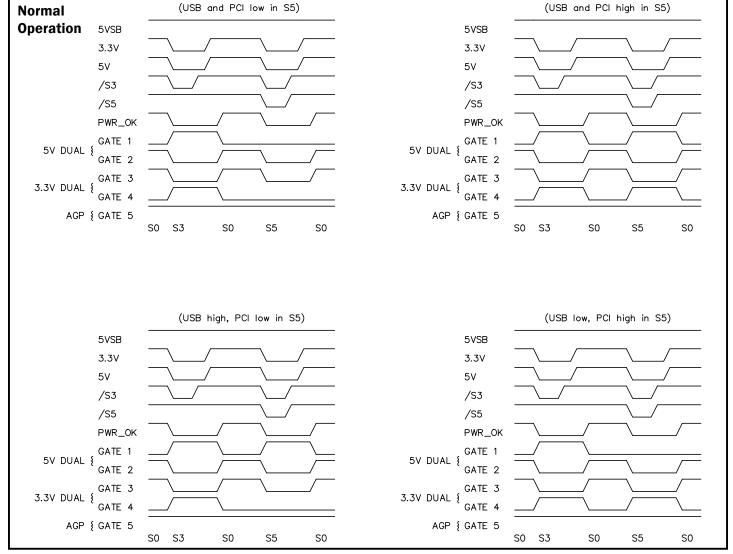

### Timing Diagrams

**PRELIMINARY**

# **Power Matrix**

This table shows which output is powered from which supply under each system state.

| System State | USB              | PCI              | /\$3 | /S5 | PWR_OK | 3.3V Dual | 5V Dual | 3.3V/1.5V<br>AGP <sup>(2)</sup> | Comments          |

|--------------|------------------|------------------|------|-----|--------|-----------|---------|---------------------------------|-------------------|

| S0           | X <sup>(1)</sup> | X <sup>(1)</sup> | 1    | 1   | 1      | 3.3V      | 5V      | 3.3V                            |                   |

| S3           | X <sup>(1)</sup> | X <sup>(1)</sup> | 0    | 1   | 0      | 5VSB      | 5VSB    | ON                              |                   |

| S5           | 0                | 0                | 0    | 0   | 0      | OFF       | OFF     | ON                              | All outputs off   |

|              | 0                | 1                | 0    | 0   | 0      | 5VSB      | OFF     | ON                              | PCI enabled       |

|              | 1                | 0                | 0    | 0   | 0      | OFF       | 5VSB    | ON                              | USB enabled       |

|              | 1                | 1                | 0    | 0   | 0      | 5VSB      | 5VSB    | ON                              | PCI & USB enabled |

### **Notes:**

- (1) X = "don't care". In SO and S3, the 3.3V dual and 5V dual outputs are not affected by the state of the PCI and USB pins. These outputs are only controlled by the state of the PCI and USB pins in S5.

- (2) Gate 5 is high in all states with 5VSB > UVLO and OCP not tripped. If powered from 3.3V as shown in the table, the AGP output is only present in SO, and will ramp with the 3.3V supply as it comes up. This avoids dips in the 3.3V supply which would otherwise occur if Gate 5 went high <u>after</u> the 3.3V supply came up, demanding high currents to charge output capacitors. If powered from 5VSB this output can be used to create 1.5VSB or 3.3VSB as required.

# Gates At A Glance

This table shows which gate drive pin controls which MOSFET:

| Gate Number: | Pin Number:       | Drive | s the F | FET mode: |                  |

|--------------|-------------------|-------|---------|-----------|------------------|

| 1            | 16                | 5VSB  |         | 5V Dual   | pass device      |

| 2            | 17 <sup>(1)</sup> | 5V    |         | 5V Dual   | pass device      |

| 3            | 17(1)             | 3.3V  | and     | 3.3V Dual | pass device      |

| 4            | 20                | 5VSB  |         | 3.3V Dual | linear regulator |

| 5            | 2                 | 3.3V  |         | AGP       | linear regulator |

### **Notes:**

(1) Note common pin for Gate 2 and Gate 3 - both FETs are operating as pass devices only in SO.

# POWER MANAGEMENT PRELIMINARY

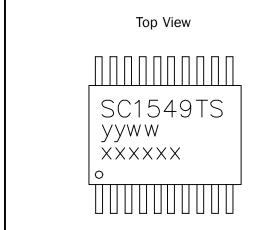

# Pin Configuration

#### **Top View** 5VSB 🗆 □ G4 20 2 19 3.3VD G5 [ 3 ⊐ GND AGP [ 18 TYPEDET 17 ⊐ G2/3 PWR\_OK [ 5 ⊐ G1 16 EN D 6 ⊐5VD 15 /S3 c /S5 c 5VSB 14 8 13 ⊐ FC 9 ∃+CAP USB D 11 10 -CAPPCI 12 **TSSOP-20**

# Ordering Information

| Part Number    | Package  |

|----------------|----------|

| SC1549TSTR (1) | TSSOP-20 |

### Note:

(1) Only available in tape and reel packaging. A reel contains 2500 devices.

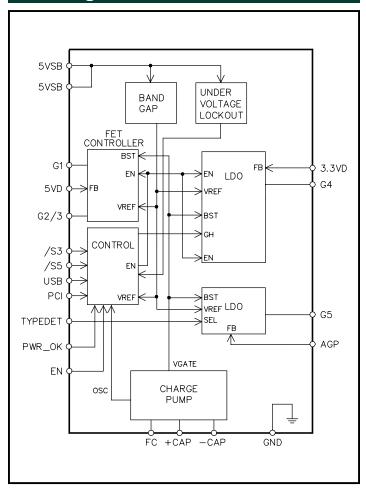

# **Block Diagram**

# Marking Information

yyww = Date code (Example: 0012) xxxxxx = Lot number (Example: P94A01)

# **PRELIMINARY**

# Pin Descriptions

| Pin # | Pin Name | Pin Function                                                                                                                                                        |

|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | 5VSB     | 5V standby supply from silver box. Connect this pin to pin 14.                                                                                                      |

| 2     | G5       | Gate drive for MOSFET between 3.3V and 1.5V/3.3V AGP. High when 5VSB is present and greater than UVLO.                                                              |

| 3     | AGP      | Sense pin for 1.5V/3.3V AGP.                                                                                                                                        |

| 4     | TYPEDET  | Select 1.5V or 3.3V for AGP, high = 3.3V.                                                                                                                           |

| 5     | PWR_OK   | Power_OK signal from silver box.                                                                                                                                    |

| 6     | EN       | Enable signal active high. Connect to 5VSB if not being used. Cycling the enable pin will reset the over current latches.                                           |

| 7     | /\$3     | Pulling this pin low (with /S5 high) causes the device to enter the S3 sleep state. Pulling both /S3 and /S5 low will cause the device to enter the S5 sleep state. |

| 8     | /S5      | Pulling this pin low along with /S3 causes the device to enter the S5 sleep state.                                                                                  |

| 9     | USB      | Enable pin for 5V Dual during S5 sleep state, high = ON.                                                                                                            |

| 10    | PCI      | Enable pin for 3.3V Dual during S5 sleep state, high = ON.                                                                                                          |

| 11    | -CAP     | Negative end of charge pump capacitor. Connect a 10nF ceramic capacitor between this pin and pin 12 (+CAP).                                                         |

| 12    | +CAP     | Positive end of charge pump capacitor.                                                                                                                              |

| 13    | FC       | Charge pump output (9V nominal). Decouple this pin with a 0.1µF ceramic capacitor.                                                                                  |

| 14    | 5VSB     | 5V standby supply from silver box. Decouple this pin with a 1µF ceramic capacitor.                                                                                  |

| 15    | 5VD      | Sense pin for 5V Dual.                                                                                                                                              |

| 16    | G1       | Gate drive for MOSFET between 5VSB and 5V Dual.                                                                                                                     |

| 17    | G2/3     | Gate drive for MOSFETs between 5V and 5V Dual and 3.3V and 3.3V Dual.                                                                                               |

| 18    | GND      | Reference ground.                                                                                                                                                   |

| 19    | 3.3VD    | Sense pin for 3.3V Dual.                                                                                                                                            |

| 20    | G4       | Gate drive for MOSFET between 5VSB and 3.3V Dual.                                                                                                                   |

### **PRELIMINARY**

### Applications Information

### **Theory Of Operation**

The SC1549 provides a simple way to power three seperate voltage buses while controlling them correctly using the ACPI control interface (PWR\_OK, /SLP\_S3 and /SLP\_S5).

It requires only a single supply rail (5VSB from the system silver box) to operate. An internal charge pump generates the gate voltages required to enable the use of n-channel MOSFETs throughout the design. The external FETs are operated in two discrete modes:

- 1) as pass devices where  $V_{OUT} = V_{IN} (I_{OUT} * R_{DS(ON)})$

- 2) as linear regulators.

Please refer to the "Gates At A Glance" section on page 7 and the Typical Applications Circuit on page 1 to determine which FETs operate in which mode.

Linear Mode: the SC1549 contains a bandgap reference trimmed for optimal temperature coefficient which is fed into the inverting input of an error amplifier. The output voltage of each linear regulator (monitored by the sense pin for that output) is divided down internally using a resistor divider and compared to the bandgap voltage. The error amplifier drives the gate of the appropriate external FET to maintain the voltage at the non inverting input, and hence the output voltage.

**Pass Device Mode:** when a particular output is enabled (please refer to the "Power Matrix" section on page 7) in pass mode (i.e. 5VSB to 5V Dual), the appropriate gate drive will be driven high to turn the FET hard on, minimizing the voltage drop due to  $I_{OUT}*R_{DS(ON)}$ .

The **sense pins** serve two functions:

- 1) to sense the output voltage for the linear regulators

- 2) to sense the output voltage for over current protection

**Over Current Protection** is provided for both dual outputs. OCP is implemented by utilizing the  $R_{DS(ON)}$  of the FETs. As the output current increases, the regulation loop maintains the output voltage (linear mode only) by turning on the FET more and more. Eventually, as the  $R_{DS(ON)}$  low limit is reached (pass devices are already operating at this point) the FET will be unable to turn on any further and the output voltage will start to fall. When the output voltage falls to approximately 50% of nominal, all outputs are latched off. Toggling the enable pin or cycling 5VSB

will reset the latch.

To prevent false latching due to capacitor inrush currents, low supply rails or momentary overloads, the current limit latch has a timer. If  $V_{\text{OUT}}$  is above the OCP threshold ( $V_{\text{TH(OC)}}$ ) before the timer "times out", then the outputs do not latch.

### **Reducing Commutation Noise**

The slew rate of the linears is slow enough to provide soft commutation. The non-linear switch outputs (5V and 3.3V Duals) have fast slew rates. It may be necessary to put a resistor in series with the gate to reduce transients (3.3V Dual shown):

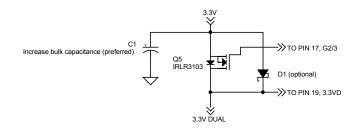

Another possible source of commutation noise occurs at startup on 3.3V Dual and 5V Dual, when the standby FET and the pass-through FET are both off. Each output will charge to 3.3V (or 5V as applicable) minus 0.7V (the drop across the body diode). When PWR\_OK asserts, the main pass FET turns on shorting the supply to the output, 0.7V below it, pulling it down locally momentarily. This should not be an issue as long as there is sufficient capacitance on the supplies locally. Another way to reduce this drop is to place a schottky diode across the FET with the cathode towards the output so it charges to the supply voltage minus 0.4V, thus reducing the drop when the FET turns on (3.3V Dual shown):

### **PRELIMINARY**

### Applications Information (Cont.)

### **Adjusting the Output Voltage of the Linear Regulator**

It is possible to adjust the output voltage of the linear regulator (1.5V/3.3V/AGP) by applying an external resistor divider to the sense pin (see below). Since the sense pin sinks a nominal 160 $\mu$ A (TYPEDET = low, 340 $\mu$ A for TYPEDET = high), the resistor values should be selected to allow 100x that current to flow through the divider. This will ensure that variations in the sense current will have negligible affect on the output voltage regulation. Thus a target value for R2 (maximum) can be calculated:

$$R2 \leq \frac{V_{\text{OUT(FIXED)}}}{I_{\text{SENSE}} \bullet 100} \quad \Omega$$

For TYPEDET = low:

$$R2 \le \frac{1.5}{160\mu\text{A} \cdot 100} \le 94 \Omega$$

The output voltage can only be adjusted upwards from the fixed output voltage, and can be calculated using the following equation:

$$V_{\text{OUT}(\text{ADJUSTED})} = V_{\text{OUT}(\text{FIXED})} \bullet \left(1 + \frac{R1}{R2}\right) + R1 \bullet I_{\text{SENSE}} \text{ Volts}$$

Therefore to set the linear regulator with TYPEDET = low to 1.8V, for example, R1 = 17.8 $\Omega$  and R2 = 90.9 $\Omega$ . The maximum voltage to which an output can be set using this method is limited by the input voltage to the FET(s) and the R<sub>DS(ON)</sub> of the FET(s).

Please note that this technique cannot be used for the 3.3V Dual and 5V Dual outputs since the output is switched via a pass device (i.e. not regulated) when not in S0.

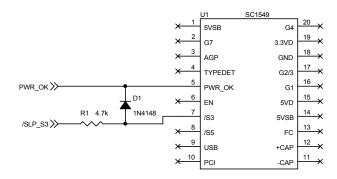

### **Fault Protection Hints**

Loss of AC Power: if it is possible during brownouts or

momentary loss of AC power to the computer "silver box" that PWR\_OK can assert low while S3 and S5 remain high then the over current protection may trigger. This is because the state machine will ignore this illegal transition and monitor all outputs as if they are still in S0, despite the fact that the inputs are going away. If 5VSB decays slowly, S3 and S5 remain high, and one output drops below the OCP threshold for long enough that the OCP "times out" then the outputs will latch off. Then if the AC power returns after the OCP latches off, but before the 5VSB supply drops below UVLO, then the device will not start up again until EN or 5VSB is cycled. One way to avoid this happening is to force the device into S3 if PWR\_OK goes low but S3 and S5 remain high using the circuit shown below. This will supply the outputs from 5VSB which will either cause 5VSB to drop below UVLO and reset the part when the AC power comes back up, or it may prevent OCP occuring at all. Either way correct functionality will be guaranteed once AC power returns.

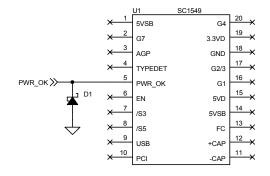

Incorrect Signals From Silver Box: Some silver boxes have been found that produce incorrect voltages on the PWR\_OK line, producing dangerous negative voltage spikes up to -1V or greater. Such spikes exceed the absolute maximum ratings for this device and can cause the device to malfunction. If a supply produces such spikes they can be clamped to GND using a small schottky diode as shown below, completely removing any threat.

# **PRELIMINARY**

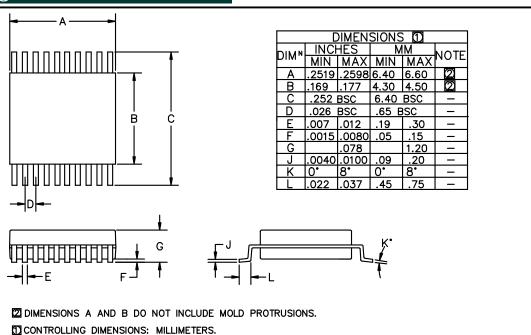

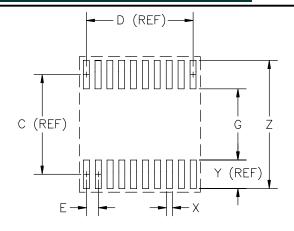

# Outline Drawing - TSSOP-20

### Land Pattern - TSSOP-20

|        |      | DIMEN: | <u>SIONS</u> |        |      |

|--------|------|--------|--------------|--------|------|

| DIMN   | INC  | HES    |              | М      | NOTE |

| DIIVI  | MIN  | MAX    | MIN          | MAX    | NOIL |

| $\cup$ | -    | .218   | _            | 5.53   | REF  |

| D      | -    | .230   | _            | 5.85   | REF  |

| Ε      | -    | .026   | _            | 0.65   | BSC  |

| G      | .155 | _      | 3.947        | -      | _    |

| X      | -    | .013   | _            | 0.323  | -    |

| Y      | _    | .062   | _            | 1.583  | REF  |

| 7      |      | 280    |              | 7 11 3 |      |

- Q GRID PLACEMENT COURTYARD IS 14 X 15 ELEMENTS (7mm X 7.5mm) IN ACCORDANCE WITH THE INTERNATIONAL GRID DETAILED IN THE IEC PUBLICATION 97.

- 1 CONTROLLING DIMENSIONS: MILLIMETERS.

# **Contact Information**

Semtech Corporation Power Management Products Division 200 Flynn Road, Camarillo, CA 93012 Phone: (805)498-2111 FAX (805)498-3804