#### **New Product**

# **Vishay Siliconix**

# **Quad SPST CMOS Analog Switch with Latches**

#### **FEATURES**

#### **BENEFITS**

#### **APPLICATIONS**

- Accepts 150-ns Write Pulse Width

- 5-V On-Chip Regulator

- Latches Are Transparent with WR Low

- Low On-Resistance: 60 Ω

- Compatible with Most μP Buses

- Allows Wide Power Supply Tolerance Without Affecting TTL Compatibility

- Reduced Power Consumption

- Allows Flexibility of Design

- μP Based Systems

- Automatic Test Equipment

- Communication Systems

- Data Acquisition Systems

- Medical Instrumentation

- Factory Automation

#### **DESCRIPTION**

The DG221B is a monolithic quad single-pole, single-throw analog switch designed for precision switching applications in communication, instrumentation and process control systems. Featuring independent onboard latches and a common  $\overline{\text{WR}}$  pin, each DG221B can be memory mapped, and addressed as a single data byte for simultaneous switching.

The DG221B combines low power and low on-resistance (60  $\Omega$  typical) while handling continuous currents up to 20 mA. An epitaxial layer prevents latchup.

The device features true bidirectional performance in the on condition.

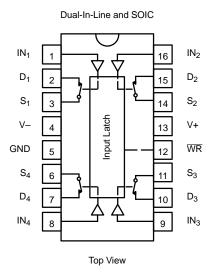

#### FUNCTIONAL BLOCK DIAGRAM AND PIN CONFIGURATION

Four Latchable SPST Switches per Package

| TRUTH TABLE               |   |                                                                                       |  |  |  |

|---------------------------|---|---------------------------------------------------------------------------------------|--|--|--|

| IN <sub>X</sub> WR Switch |   |                                                                                       |  |  |  |

| 0                         | 0 | ON                                                                                    |  |  |  |

| 1                         | 0 | OFF                                                                                   |  |  |  |

| х                         | Ŀ | Control data latched-in,<br>switches on or off as selected<br>by last IN <sub>X</sub> |  |  |  |

| Х                         | 1 | Maintains previous state                                                              |  |  |  |

Logic "0" ≤ 0.8 V Logic "1" ≥ 2.4 V

| ORDERING INFORMATION |                    |             |  |  |  |

|----------------------|--------------------|-------------|--|--|--|

| Temp Range           | Package            | Part Number |  |  |  |

| -40°C to 85°C        | 16-Pin Plastic DIP | DG221BDJ    |  |  |  |

| -40 C t0 65 C        | 16-Pin Narrow SOIC | DG221BDY    |  |  |  |

# Vishay Siliconix

# **New Product**

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltages Referenced to V-                                     |                         |

|---------------------------------------------------------------|-------------------------|

| V+                                                            | 34 \                    |

| GND                                                           |                         |

| Digital Inputs <sup>a</sup> , V <sub>S</sub> , V <sub>D</sub> | (V-) -2 V to (V+) +2 \  |

| or 20 mA                                                      | , whichever occurs firs |

| Continuous Current (Any Terminal)                             | 30 mA                   |

| Continuous Current, S or D                                    | 20 m/                   |

| Peak Current S or D (Pulsed 1 ms. 10% duty cycle)             | 70 m/                   |

| Storage Temperature:       | (DJ and DY Suffix)65 | to 125°C |

|----------------------------|----------------------|----------|

| Power Dissipation (Package | e) <sup>b</sup>      |          |

| 16-Pin Plastic DIPc        |                      | 470 mW   |

| 16-Pin SOIC <sup>d</sup>   |                      | 600 mW   |

|                            |                      |          |

- a. Signals on S<sub>X</sub>, D<sub>X</sub>, or IN<sub>X</sub> exceeding V+ or V- will be clamped by internal diodes. Limit forward diode current to maximum current ratings.

b. All leads welded or soldered to PC Board.

c. Derate 6.5 mW/°C above 25°C

d. Derate 7.7 mW/°C above 75°C

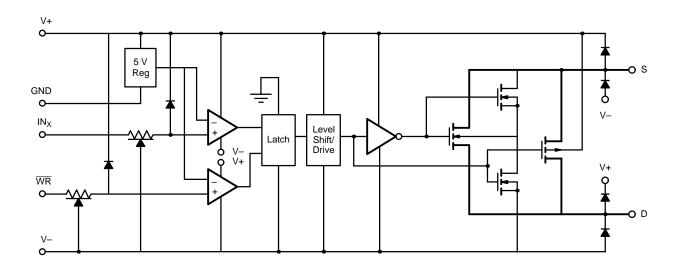

# **SCHEMATIC DIAGRAM (TYPICAL CHANNEL)**

FIGURE 1.

# **New Product**

# Vishay Siliconix

| SPECIFICATIONS                                    | 3                     |                                                                                                  |                   |                       |         |                  |      |

|---------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------|-------------------|-----------------------|---------|------------------|------|

|                                                   |                       | Test Conditions<br>Unless Otherwise Specified                                                    |                   | Limits<br>-40 to 85°C |         |                  |      |

| Parameter                                         | Symbol                | V+ = 15  V, V- = -15  V<br>$V_{IN} = 2.4 \text{ V}, 0.8^{f} \text{ V}, \overline{\text{WR}} = 0$ | Temp <sup>b</sup> | Mind                  | Турс    | Max <sup>d</sup> | Unit |

| Analog Switch                                     |                       |                                                                                                  | 1                 | •                     |         | '                |      |

| Analog Signal Rangee                              | V <sub>ANALOG</sub>   |                                                                                                  | Full              | -15                   |         | 15               | V    |

| Drain-Source<br>On-Resistance                     | r <sub>DS(on)</sub>   | $I_S = -10$ mA, $V_D = \pm 10$ V                                                                 | Room<br>Full      |                       | 60      | 90<br>135        | Ω    |

| Source Off<br>Leakage Current                     | I <sub>S(off)</sub>   |                                                                                                  | Room<br>Full      | -5<br>-100            | ±0.01   | 5<br>100         |      |

| Drain Off<br>Leakage Current                      | I <sub>D(off)</sub>   | $V_S = \pm 14 \text{ V}, V_D = \mp 14 \text{ V}$                                                 | Room<br>Full      | -5<br>-100            | ±0.02   | 5<br>100         | nA   |

| Drain On<br>Leakage Current                       | I <sub>D(on)</sub>    | $V_S = V_D = \pm 14 \text{ V}$                                                                   | Room<br>Full      | -5<br>-200            | ±0.01   | 5<br>200         |      |

| Digital Control                                   | 1                     |                                                                                                  | 1                 |                       | •       | · I              |      |

| Input Current I <sub>INL</sub> , I <sub>INH</sub> |                       | V <sub>IN</sub> = 0 V or = 2.4 V                                                                 | Room<br>Full      | -1<br>-10             | -0.0004 | 1<br>10          | μΑ   |

| Dynamic Characteristic                            | cs                    |                                                                                                  | 1                 |                       |         |                  |      |

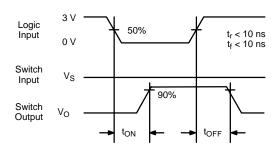

| Turn-On Time                                      | t <sub>ON</sub>       | 0 5:                                                                                             | Room              |                       |         | 550              |      |

| Turn-Off Time                                     | t <sub>OFF</sub>      | See Figure 2                                                                                     | Room              |                       |         | 340              |      |

| Turn-On Time Write                                | t <sub>ON</sub> , WR  | 0 5: 0                                                                                           | Room              |                       |         | 550              |      |

| Turn-Off Time Write                               | t <sub>OFF</sub> , WR | See Figure 3                                                                                     | Room              |                       |         | 340              | ns   |

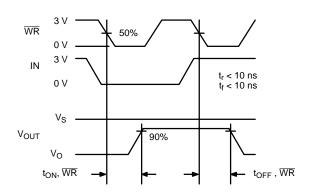

| Write Pulse Width                                 | t <sub>W</sub>        |                                                                                                  | Room              | 150                   | 120     |                  |      |

| Input Setup Time                                  | ts                    | See Figure 4                                                                                     | Room              | 180                   | 130     |                  |      |

| Input Hold Time                                   | t <sub>H</sub>        |                                                                                                  | Room              | 20                    | 18      |                  |      |

| Charge Injection                                  | Q                     | $C_L = 1000 \text{ pF}$<br>$V_{GEN} = 0 \text{ V}, R_{GEN} = 0 \Omega$                           | Room              |                       | 20      |                  | pC   |

| Source-Off Capacitance                            | C <sub>S(off)</sub>   |                                                                                                  | Room              |                       | 8       |                  |      |

| Drain-Off Capacitance                             | C <sub>D(off)</sub>   | $f = 1 \text{ MHz}, V_S, V_D = 0 \text{ V}$                                                      | Room              |                       | 9       |                  | pF   |

| Channel-On Capacitance                            | C <sub>D(on)</sub>    |                                                                                                  | Room              |                       | 29      |                  |      |

| Off Isolation                                     | OIRR                  | Ve = 1 Vo n f = 100 kHz                                                                          | Room              |                       | 70      |                  |      |

| Interchannel Crosstalk                            | X <sub>TALK</sub>     | $V_S = 1 V_{p-p}$ , $f = 100 \text{ kHz}$<br>$C_L = 15 \text{ pF}$ , $R_L = 1 \text{ k}\Omega$   | Room              |                       | 90      |                  | dB   |

| Power Supplies                                    | <b>'</b>              |                                                                                                  | •                 |                       |         |                  |      |

| Positive Supply Current                           | I+                    | All Channels On or Off                                                                           | Full              |                       | 0.8     | 1.5              |      |

| Negative Supply Current                           | I–                    | V <sub>IN</sub> = 0 V or 2.4 V                                                                   | Room              | -1                    | -0.4    |                  | mA   |

#### Notes:

- tes:

Refer to PROCESS OPTION FLOWCHART.

Room = 25°C, Full = as determined by the operating temperature suffix.

Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

Guaranteed by design, not subject to production test.

V<sub>IN</sub> = input voltage to perform proper function.

# **Vishay Siliconix**

# **New Product**

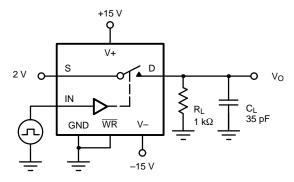

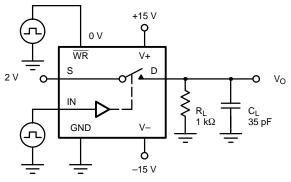

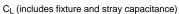

# **TEST CIRCUITS**

C<sub>L</sub> (includes fixture and stray capacitance)

$$V_O = V_S$$

$$\frac{R_L}{R_L + r_{DS(on)}}$$

FIGURE 2. Switching Time

$$V_{O} = V_{S} \qquad \frac{R_{L}}{R_{L} + r_{DS(on)}}$$

FIGURE 3. WR Switching Time

The latches are level sensitive. When  $\overline{WR}$  is held low the latches are transparent and the switches respond to the digital inputs. The digital inputs are latched on the rising edge of  $\overline{WR}$ .

FIGURE 4. WR Setup Conditions

Vishay Siliconix

# **TEST CIRCUITS**

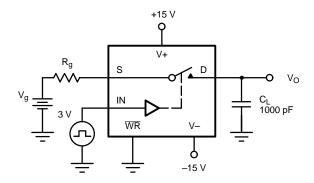

$\Delta V_O$  = measured voltage error due to charge injection The charge injection in coulombs is Q = C\_L x  $\Delta V_O$

FIGURE 5. Charge Injection

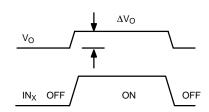

FIGURE 6. Off Isolation

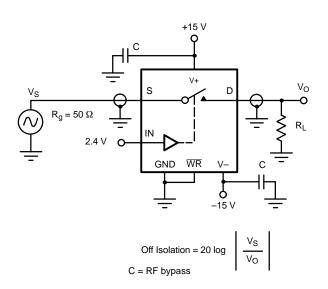

FIGURE 7. Channel-to-Channel Crosstalk

| APPLICATION HINTS <sup>a</sup>                    |     |            |         |         |                                                                    |  |  |

|---------------------------------------------------|-----|------------|---------|---------|--------------------------------------------------------------------|--|--|

| V+ V- Positive Supply Voltage (V) Voltage (V) (V) |     | GND<br>(V) |         |         | V <sub>S</sub> or V <sub>D</sub><br>Analog Voltage<br>Range<br>(V) |  |  |

| 15                                                | -15 | 0          | 2.4/0.8 | 2.4/0.8 | -15 to 15                                                          |  |  |

| 10                                                | -10 | 0          | 2.4/0.8 | 2.4/0.8 | -10 to 10                                                          |  |  |

| 10                                                | -5  | 0          | 2.4/0.8 | 2.4/0.8 | -5 to 10                                                           |  |  |

#### Notes:

a. Application Hints are for DESIGN AID ONLY, not guaranteed and not subject to production testing.

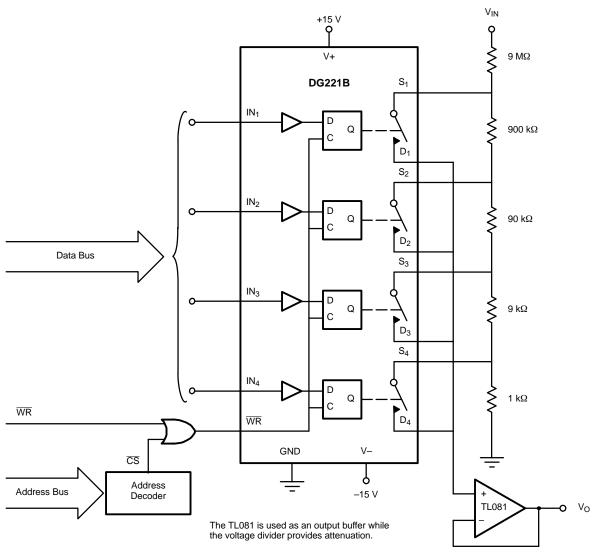

# **APPLICATIONS**

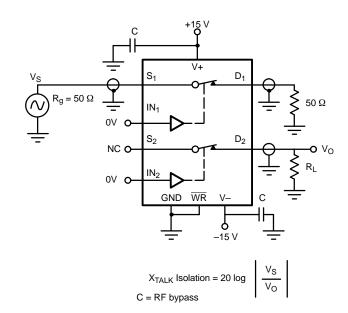

FIGURE 8. μP-Controlled Analog Signal Attenuator

| TRUTH TABLE     |                 |                 |                 |     |           |  |

|-----------------|-----------------|-----------------|-----------------|-----|-----------|--|

| IN <sub>1</sub> | IN <sub>2</sub> | IN <sub>3</sub> | IN <sub>4</sub> | WRA | ON SWITCH |  |

| 0               | 0               | 0               | 0               | 0   | All       |  |

| 1               | 1               | 1               | 1               | 0   | None      |  |

| 0               | 1               | 1               | 1               | 0   | 1         |  |

| 1               | 0               | 1               | 1               | 0   | 2         |  |

| 1               | 1               | 0               | 1               | 0   | 3         |  |

| 1               | 1               | 1               | 0               | 0   | 4         |  |

| OUTI | OUTPUT ATTENUATION FOR FIGURE 8 |                 |                 |                 |        |  |  |

|------|---------------------------------|-----------------|-----------------|-----------------|--------|--|--|

| WR   | IN <sub>1</sub>                 | IN <sub>2</sub> | IN <sub>3</sub> | IN <sub>4</sub> | Gain   |  |  |

| 0    | 0                               | 1               | 1               | 1               | 0.1    |  |  |

| 0    | 1                               | 0               | 1               | 1               | 0.01   |  |  |

| 0    | 1                               | 1               | 0               | 1               | 0.001  |  |  |

| 0    | 1                               | 1               | 1               | 0               | 0.0001 |  |  |

Notes: a.  $\overline{WR}$  may be held at "0" for temporary operation similar to DG201A/DG201B. With  $\overline{WR}$  at "0" SW<sub>1</sub> will remain on as long as IN<sub>1</sub> is held at "0".

Vishay

# **Disclaimer**

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.

Document Number: 91000 Revision: 18-Jul-08