# R32C/116 Group

User's Manual: Hardware

RENESAS MCU M16C Family / R32C/100 Series

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

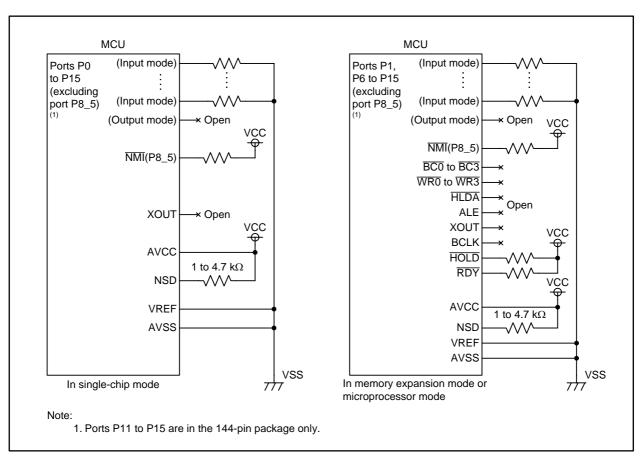

#### 1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

#### 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

— The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

#### 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

#### 4. Clock Signals

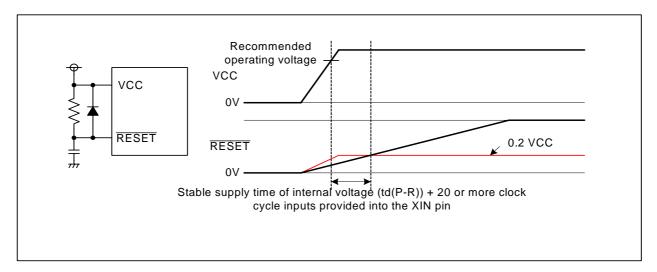

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

— When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

# 5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different part numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different part numbers, implement a system-evaluation test for each of the products.

# **About This Manual**

# 1. Purpose and Target User

This manual is designed to be read primarily by application developers who have an understanding of this microcomputer (MCU) including its hardware functions and electrical characteristics. The user should have a basic understanding of electric circuits, logic circuits and, MCUs.

This manual consists of 28 chapters covering six main categories: Overview, CPU, System Control, Peripherals, Electrical Characteristics, and Usage Notes.

Carefully read all notes in this document prior to use. Notes are found throughout each chapter, at the end of each chapter, and in the dedicated Usage Notes chapter.

The Revision History at the end of this manual summarizes primary modifications and additions to the previous versions. For details, please refer to the relative chapters or sections of this manual.

The R32C/116 Group includes the documents listed below. Verify this manual is the latest version by visiting the Renesas Electronics website.

| Type of Document                              | Contents                                                                                                                                                                                    | Document Name                                 | Document Number  |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------|

| Datasheet                                     | Overview of Hardware and Electrical Characteristics                                                                                                                                         | R32C/116 Group REJ03B0253-0110 Datasheet      |                  |

| User's Manual:<br>Hardware                    | Specifications and detailed descriptions of: -pin layout -memory map -peripherals -electrical characteristics -timing characteristics Refer to the Application Manual for peripheral usage. | R32C/116 Group<br>User's Manual:<br>Hardware  | This publication |

| User's Manual:<br>Software/Software<br>Manual | Descriptions of instruction set                                                                                                                                                             | R32C/100 Series<br>Software Manual            | REJ09B0267-0100  |

| Application Note                              | -Usages -Applications -Sample programs -Programing technics using Assembly language or C programming language                                                                               | Available on the Renesas Electronics website. |                  |

| Renesas Technical<br>Update                   | Bulletins on product specifications, documents, etc.                                                                                                                                        |                                               |                  |

# 2. Numbers and Symbols

The following explains the denotations used in this manual for registers, bits, pins and various numbers.

(1) Registers, bits, and pins

Registers, bits, and pins are indicated by symbols. Each symbol has a register/bit/pin identifier after the symbol.

Example: PM03 bit in the PM0 register

P3\_5 pin, VCC pin

(2) Numbers

A binary number has the suffix "b" except for a 1-bit value.

A hexadecimal number has the suffix "h".

A decimal number has no suffix. Example: Binary notation: 11b

Hexadecimal notation: EFA0h Decimal notation: 1234

# 3. Registers

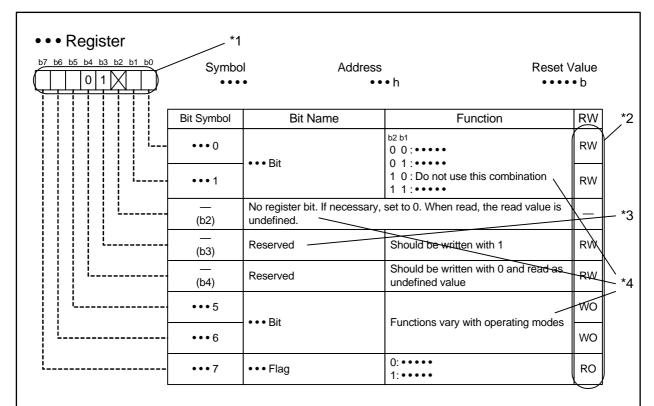

The following illustration describes registers used throughout this manual.

\*1

Blank box: Set this bit to 0 or 1 according to the function.

- 0: Set this bit to 0.

- 1: Set this bit to 1.

- X: Nothing is assigned to this bit.

\*2

RW: Read and write RO: Read only

WO: Write only (the read value is undefined)

-: Not applicable

\*3

• Reserved bit: This bit field is reserved. Set this bit to a specified value. For RW bits, the written value is read unless otherwise noted.

\*4

- No register bit(s): No register bit(s) is/are assigned to this field. If necessary, set to 0 for possible future implementation.

- Do not use this combination: Proper operation is not guaranteed when this value is set.

- Functions vary with operating modes: Functions vary with peripheral operating modes. Refer to register illustrations of the respective mode.

# 4. Abbreviations and Acronyms

The following acronyms and terms are used throughout this manual.

| Abbreviation/Acronym | Meaning                                      |

|----------------------|----------------------------------------------|

| ACIA                 | Asynchronous Communication Interface Adapter |

| bps                  | bits per second                              |

| CRC                  | Cyclic Redundancy Check                      |

| DMA                  | Direct Memory Access                         |

| DMAC                 | Direct Memory Access Controller              |

| GSM                  | Global System for Mobile Communications      |

| Hi-Z                 | High Impedance                               |

| IEBus                | Inter Equipment Bus                          |

| I/O                  | Input/Output                                 |

| IrDA                 | Infrared Data Association                    |

| LSB                  | Least Significant Bit                        |

| MSB                  | Most Significant Bit                         |

| NC                   | Non-Connection                               |

| PLL                  | Phase Locked Loop                            |

| PWM                  | Pulse Width Modulation                       |

| SIM                  | Subscriber Identity Module                   |

| UART                 | Universal Asynchronous Receiver/Transmitter  |

| VCO                  | Voltage Controlled Oscillator                |

# **TABLE OF CONTENTS**

| 1. Ov | rerview                                                               | 1  |

|-------|-----------------------------------------------------------------------|----|

| 1.1   | Features                                                              | 1  |

| 1.1.1 | Applications                                                          | 1  |

| 1.1.2 | Performance Overview                                                  | 2  |

| 1.2   | Product Information                                                   | 6  |

| 1.3   | Block Diagram                                                         | 9  |

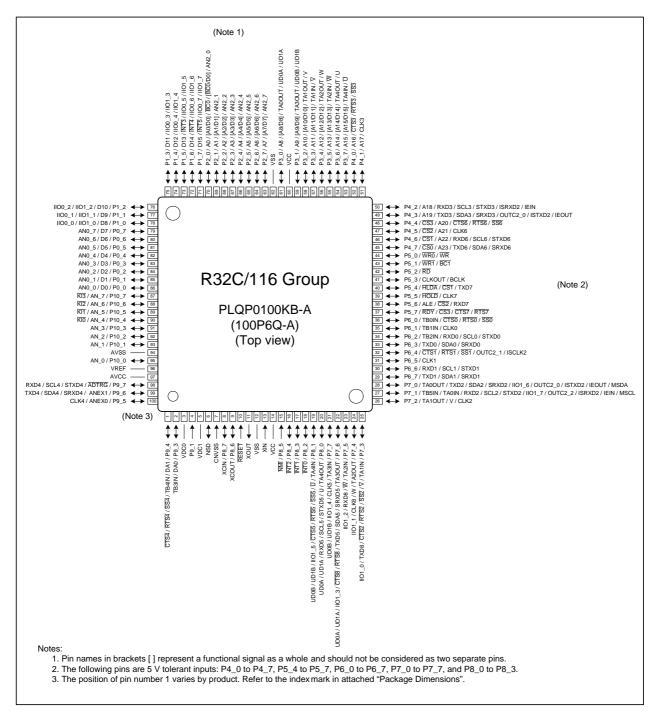

| 1.4   | Pin Assignments                                                       | 10 |

| 1.5   | Pin Definitions and Functions                                         | 19 |

| 2. Ce | entral Processing Unit (CPU)                                          | 24 |

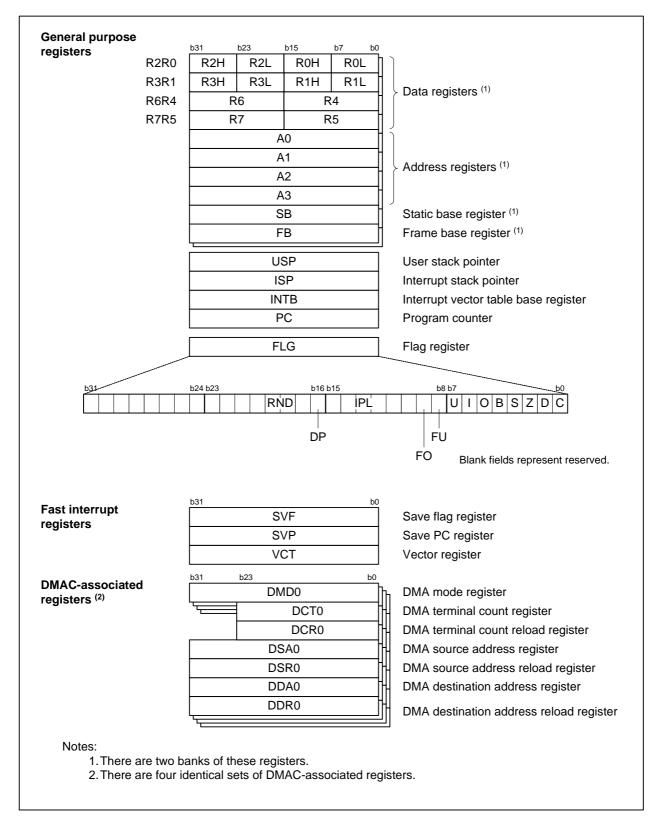

| 2.1   | General Purpose Registers                                             | 25 |

| 2.1.1 | Data Registers (R2R0, R3R1, R6R4, and R7R5)                           | 25 |

| 2.1.2 | Address Registers (A0, A1, A2, and A3)                                | 25 |

| 2.1.3 | Static Base Register (SB)                                             | 25 |

| 2.1.4 | Frame Base Register (FB)                                              | 25 |

| 2.1.5 | Program Counter (PC)                                                  | 25 |

| 2.1.6 | Interrupt Vector Table Base Register (INTB)                           | 25 |

| 2.1.7 | User Stack Pointer (USP) and Interrupt Stack Pointer (ISP)            | 25 |

| 2.1.8 | Flag Register (FLG)                                                   | 25 |

| 2.2   | Fast Interrupt Registers                                              | 27 |

| 2.2.1 | Save Flag Register (SVF)                                              | 27 |

| 2.2.2 | Save PC Register (SVP)                                                | 27 |

| 2.2.3 | Vector Register (VCT)                                                 |    |

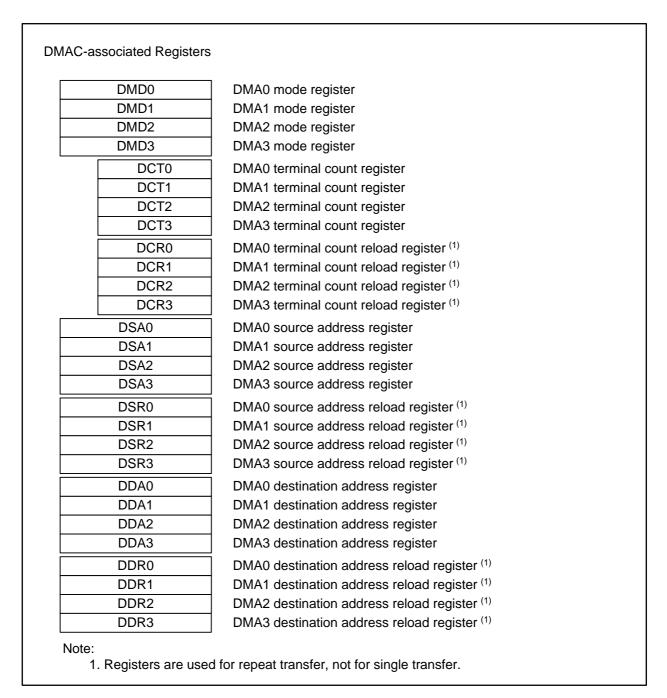

| 2.3   | DMAC-associated Registers                                             | 27 |

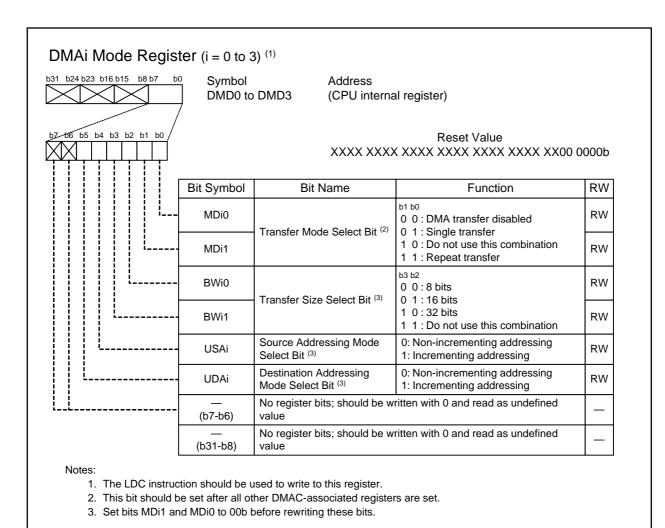

| 2.3.1 | DMA Mode Registers (DMD0, DMD1, DMD2, and DMD3)                       | 27 |

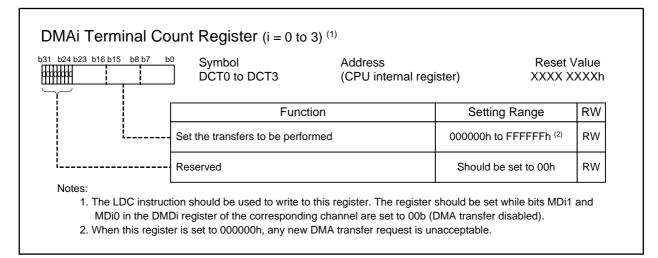

| 2.3.2 | DMA Terminal Count Registers (DCT0, DCT1, DCT2, and DCT3)             | 27 |

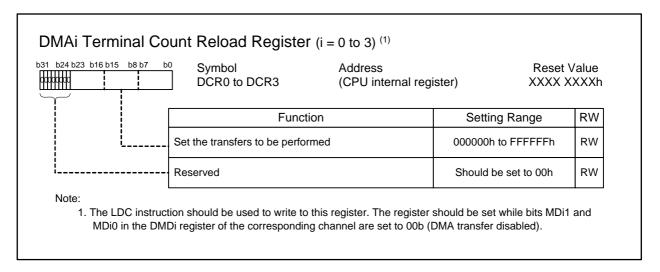

| 2.3.3 | DMA Terminal Count Reload Registers (DCR0, DCR1, DCR2, and DCR3)      | 27 |

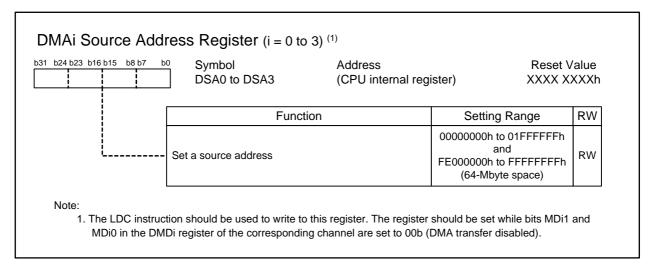

| 2.3.4 | DMA Source Address Registers (DSA0, DSA1, DSA2, and DSA3)             | 27 |

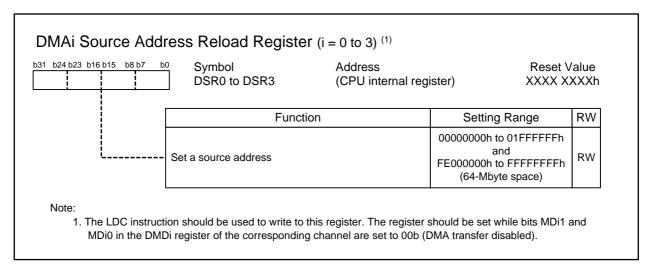

| 2.3.5 | DMA Source Address Reload Registers (DSR0, DSR1, DSR2, and DSR3)      | 27 |

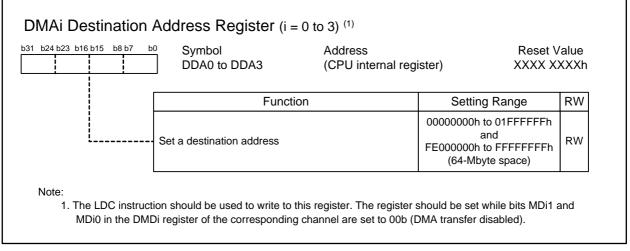

| 2.3.6 | DMA Destination Address Registers (DDA0, DDA1, DDA2, and DDA3)        |    |

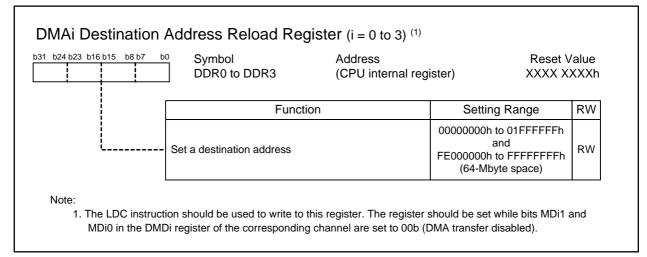

| 2.3.7 | DMA Destination Address Reload Registers (DDR0, DDR1, DDR2, and DDR3) | 27 |

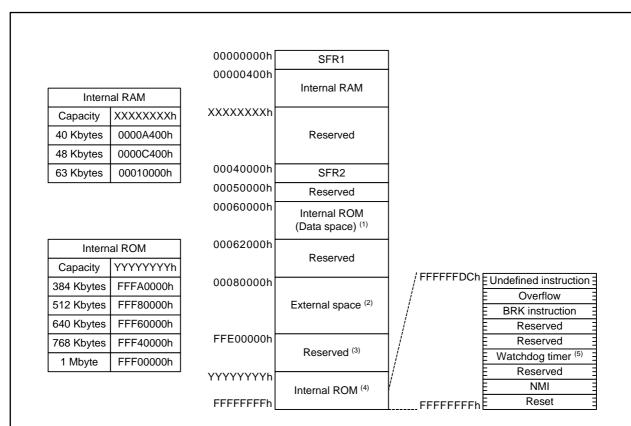

| 3. Me | emory                                                                 | 28 |

| 4. Sp | ecial Function Registers (SFRs)                                       | 29 |

| 5. Re | sets                                                                  | 54 |

| 5.1   | Hardware Reset                                                        | 54 |

| 5.2   | Software Reset                                                        | 57 |

| 5.3   | 5.3 Watchdog Timer Reset                                              |    |

| 5.4   | 5.4 Reset Vector                                                      |    |

| 6. Po  | wer Management                            | 58  |

|--------|-------------------------------------------|-----|

| 6.1    | Voltage Regulators for Internal Logic     | 58  |

| 6.1.1  | Decoupling Capacitor                      | 59  |

| 6.2    | Low Voltage Detector                      | 60  |

| 6.2.1  | Operational State of Low Voltage Detector | 63  |

| 6.2.2  | Low Voltage Detection Interrupt           | 63  |

| 6.2.3  | An Application of Low Voltage Detector    | 64  |

| 7. Pro | ocessor Mode                              | 65  |

| 7.1    | Types of Processor Modes                  | 65  |

| 7.2    | Processor Mode Setting                    | 65  |

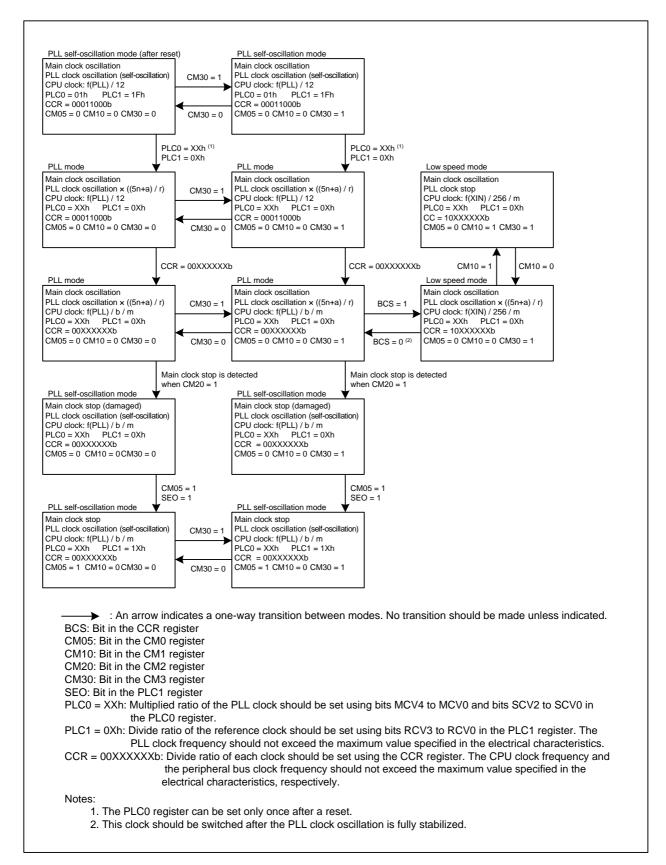

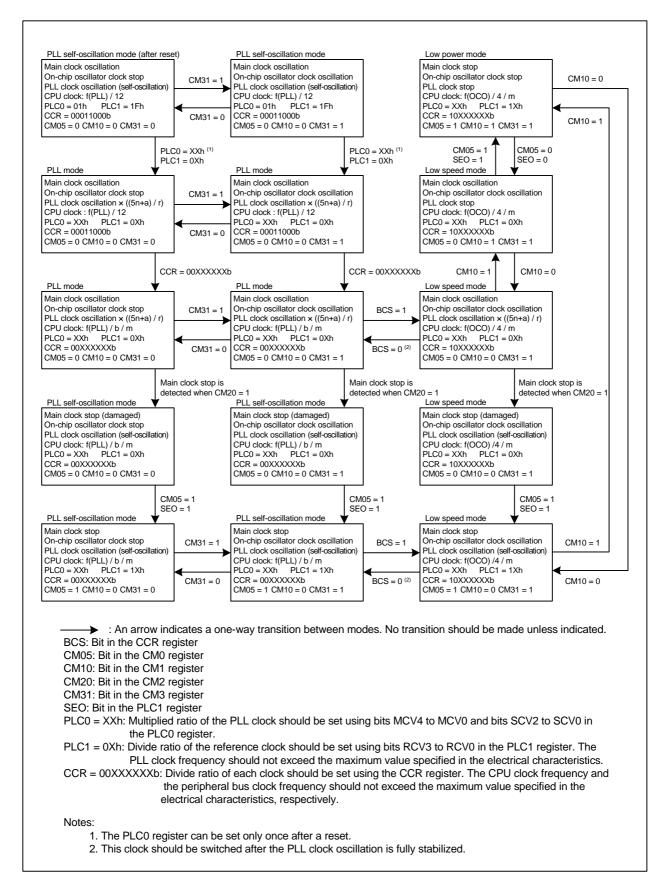

| 8. Clo | ock Generator                             | 68  |

| 8.1    | Clock Generator Types                     | 68  |

| 8.1.1  | Main Clock                                | 77  |

| 8.1.2  | Sub Clock (fC)                            | 78  |

| 8.1.3  | PLL Clock                                 | 79  |

| 8.1.4  | On-chip Oscillator Clock                  | 82  |

| 8.2    | Oscillator Stop Detection                 | 83  |

| 8.2.1  | How to Use Oscillator Stop Detection      |     |

| 8.3    | Base Clock                                | 83  |

| 8.4    | CPU Clock and Peripheral Bus Clock        | 84  |

| 8.5    | Peripheral Clock                          | 84  |

| 8.6    | Clock Output Function                     | 85  |

| 8.7    | Power Control                             | 86  |

| 8.7.1  | Normal Operating Mode                     | 87  |

| 8.7.2  | Wait Mode                                 | 92  |

| 8.7.3  | Stop Mode                                 | 95  |

| 8.8    | System Clock Protection                   | 97  |

| 8.9    | Notes on Clock Generator                  | 98  |

| 8.9.1  | Sub Clock                                 | 98  |

| 8.9.2  | Power Control                             | 98  |

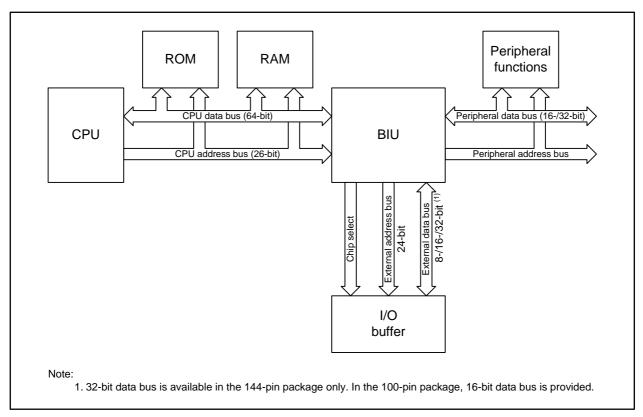

| 9. Bu  | s                                         | 99  |

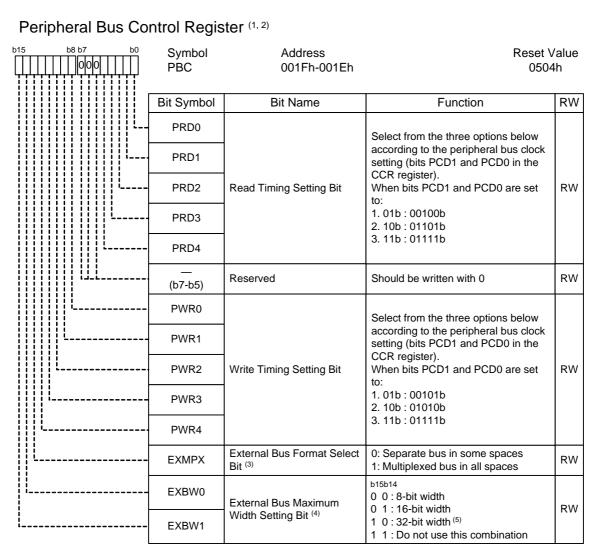

| 9.1    | Bus Setting                               | 99  |

| 9.2    | Peripheral Bus Timing Setting             | 100 |

| 9.3    | External Bus Setting                      | 101 |

| 9.3.1  | External Address Space Setting            | 101 |

| 9.3.2  | External Data Bus Width Setting           | 107 |

| 9.3.3  | Separate Bus/Multiplexed Bus Selection    | 109 |

| 9.3.4  | Read and Write Signals                    | 112 |

| 9.3.5  | External Bus Timing                       | 114 |

| 9.3.6    | ALE Signal                                        | 118 |

|----------|---------------------------------------------------|-----|

| 9.3.7    | RDY Signal                                        | 119 |

| 9.3.8    | HOLD Signal                                       | 122 |

| 9.3.9    | BCLK Output                                       | 122 |

| 9.4      | External Bus Status when Accessing Internal Space | 122 |

| 9.5      | Notes on Bus                                      | 123 |

| 9.5.1    | Notes on System Designing                         | 123 |

| 9.5.2    | Notes on Register Settings                        | 123 |

| 10. Pro  | tection                                           | 124 |

| 10.1     | Protect Register (PRCR Register)                  | 124 |

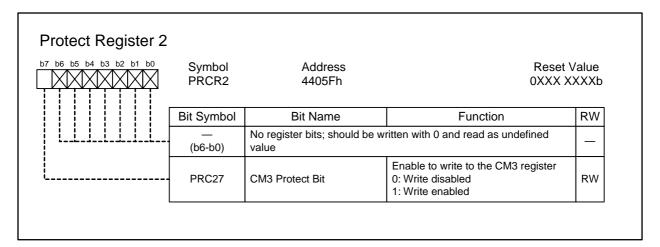

| 10.2     | Protect Register 2 (PRCR2 Register)               | 125 |

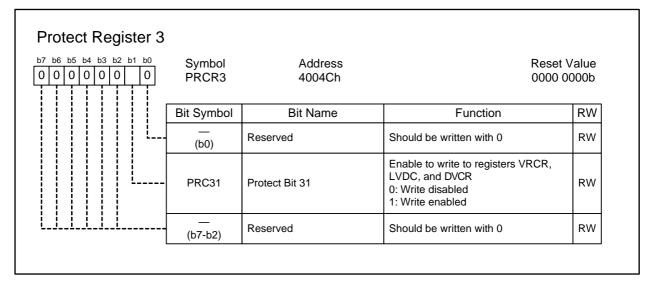

| 10.3     | Protect Register 3 (PRCR3 Register)               | 125 |

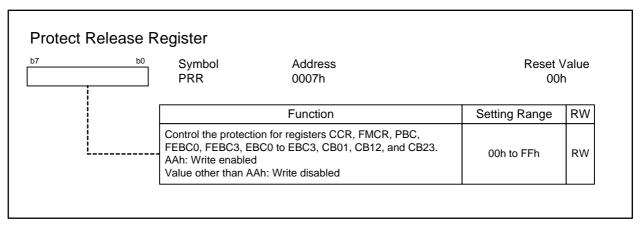

| 10.4     | Protect Release Register (PRR Register)           | 126 |

| 11. Inte | errupts                                           | 127 |

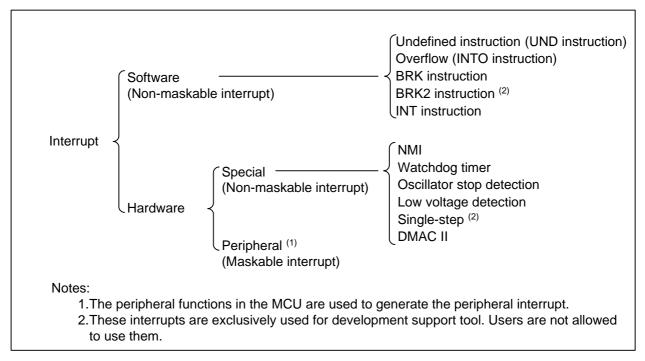

| 11.1     | Interrupt Types                                   | 127 |

| 11.2     | Software Interrupt                                | 128 |

| 11.3     | Hardware Interrupt                                | 129 |

| 11.3.1   | Special Interrupt                                 | 129 |

| 11.3.2   | Peripheral Interrupt                              | 129 |

| 11.4     | Fast Interrupt                                    | 130 |

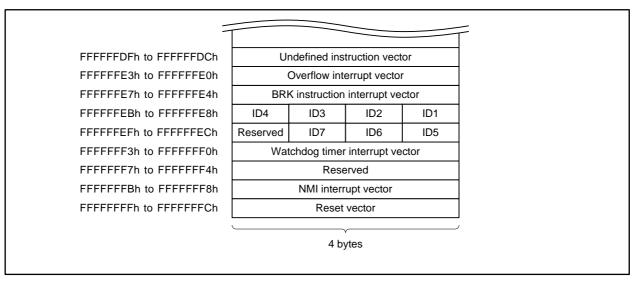

| 11.5     | Interrupt Vectors                                 | 130 |

| 11.5.1   | Fixed Vector Table                                | 131 |

| 11.5.2   | Relocatable Vector Table                          | 131 |

| 11.6     | Interrupt Request Acceptance                      | 136 |

| 11.6.1   | I Flag and IPL                                    | 136 |

| 11.6.2   | Interrupt Control Register                        | 137 |

| 11.6.3   | Wake-up IPL Setting Register                      | 140 |

| 11.6.4   | Interrupt Sequence                                | 141 |

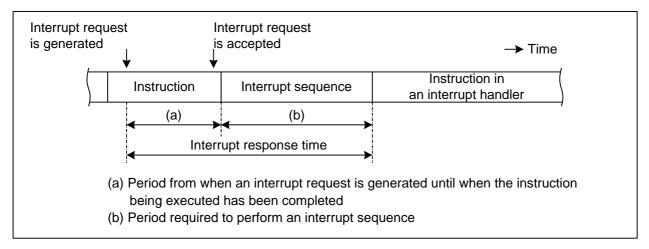

| 11.6.5   | Interrupt Response Time                           | 142 |

| 11.6.6   | IPL After Interrupt Request Acceptance            | 143 |

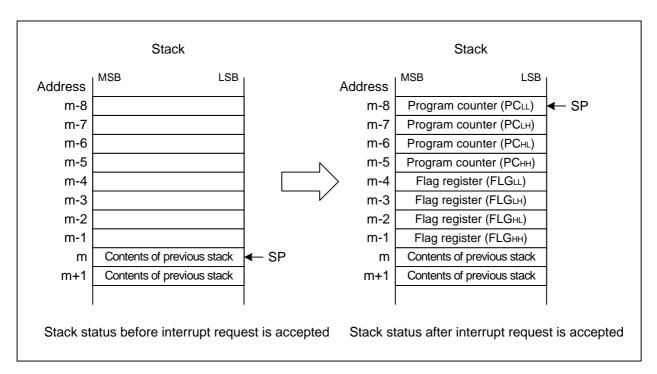

| 11.6.7   | Register Saving                                   | 143 |

| 11.7     | Register Restoring from Interrupt Handler         | 144 |

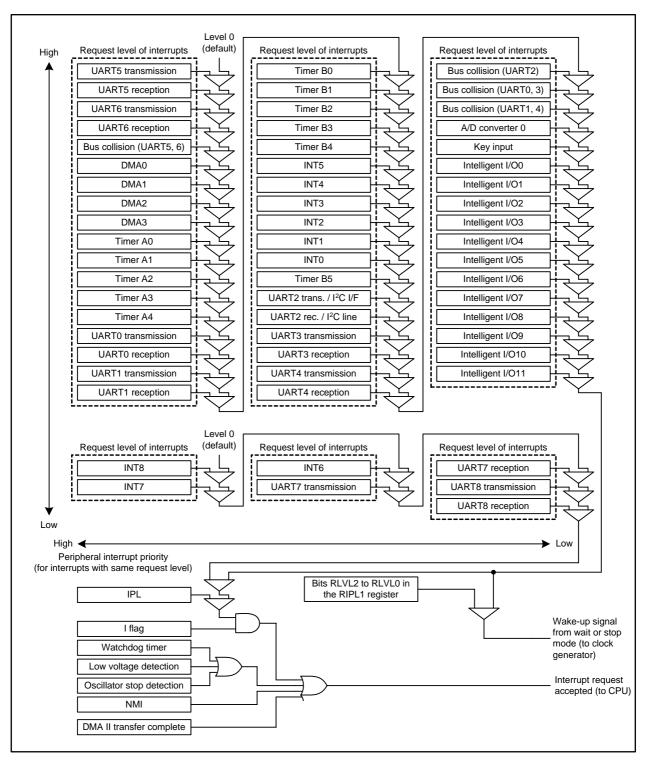

| 11.8     | Interrupt Priority                                | 144 |

| 11.9     | Priority Resolver                                 | 144 |

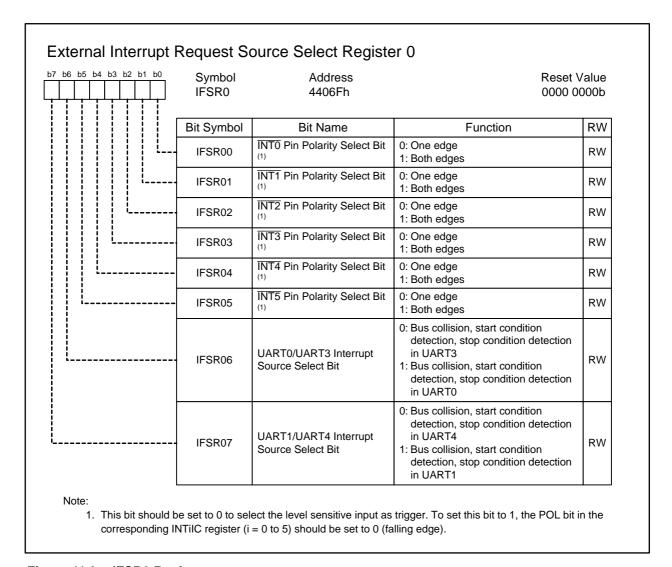

| 11.10    | External Interrupt                                | 146 |

| 11.11    | NMI                                               | 147 |

| 11.12    | Key Input Interrupt                               | 148 |

| 11.13    | Intelligent I/O Interrupt                         | 149 |

| 11.14    | Notes on Interrupts                               | 152 |

| 11 11    | 1 ISP Setting                                     | 152 |

|     | 11.14.2 | NMI                                                   | 152 |

|-----|---------|-------------------------------------------------------|-----|

|     | 11.14.3 | External Interrupt                                    | 152 |

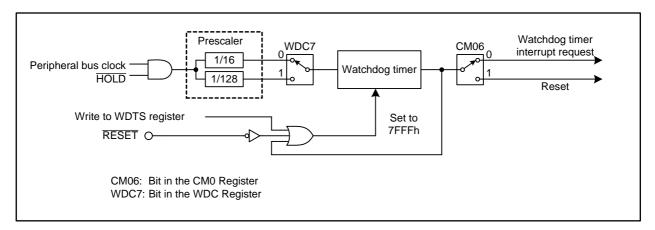

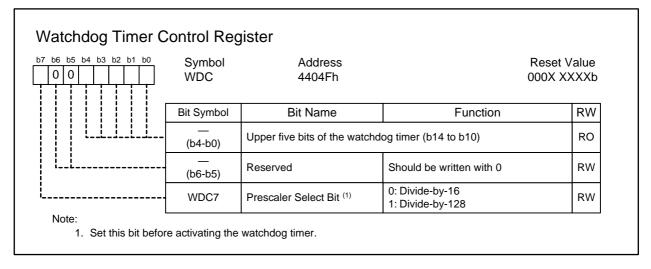

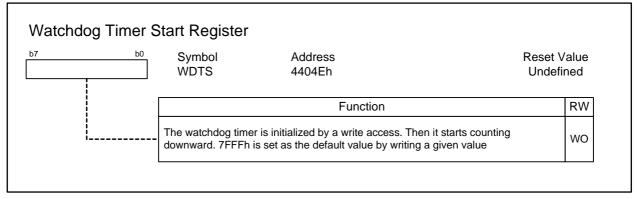

| 12. | Watch   | ndog Timer                                            | 153 |

| 13. | DMAC    |                                                       | 155 |

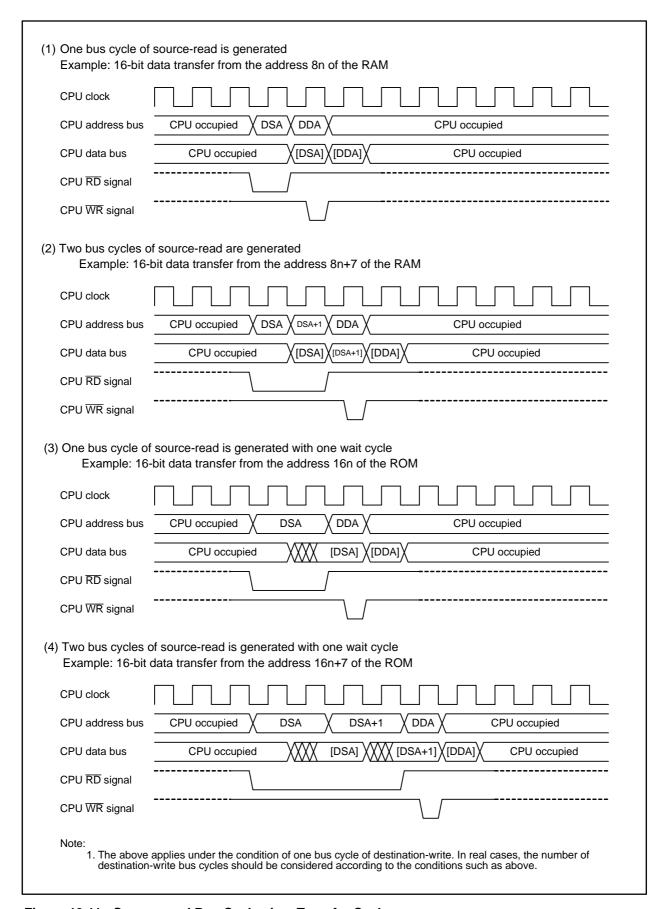

| 13  | 3.1 Tra | ansfer Cycle                                          | 164 |

|     | 13.1.1  | Effect of Transfer Address and Data Bus Width         | 164 |

|     | 13.1.2  | Effect of Bus Timing                                  | 165 |

|     | 13.1.3  | Effect of RDY Signal                                  | 165 |

| 13  | 3.2 DN  | //A Transfer Cycle                                    | 167 |

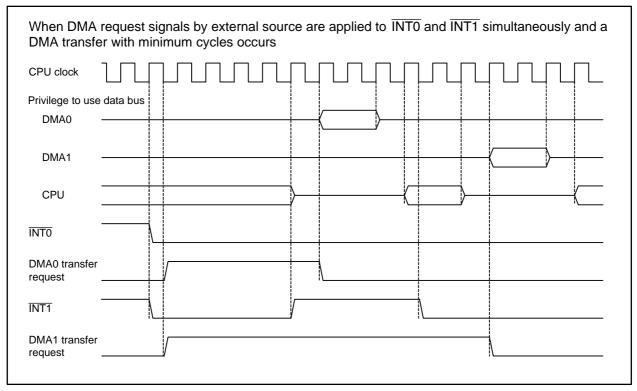

| 13  | 3.3 Ch  | nannel Priority and DMA Transfer Timing               | 168 |

| 13  | 3.4 No  | otes on DMAC                                          | 169 |

|     | 13.4.1  | DMAC-associated Register Settings                     | 169 |

|     | 13.4.2  | Read from DMAC-associated Registers                   | 169 |

| 14. | DMAC    |                                                       | 170 |

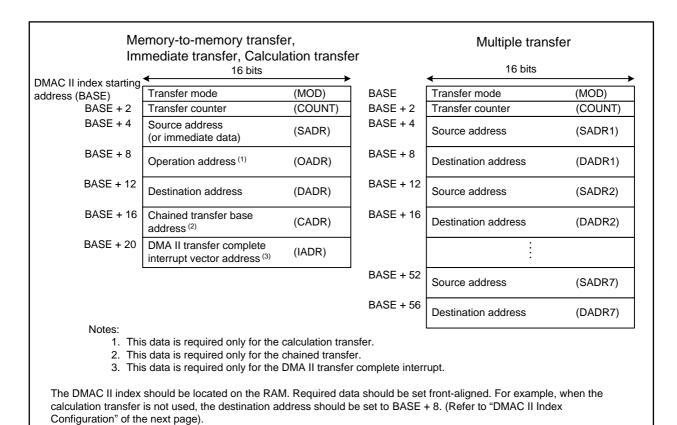

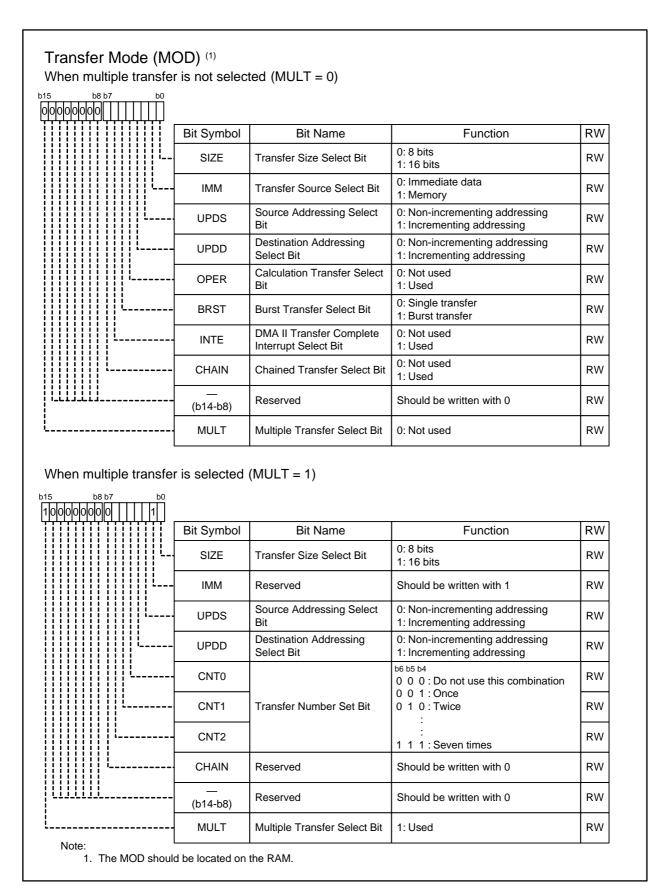

| 14  | 4.1 DN  | MAC II Settings                                       | 170 |

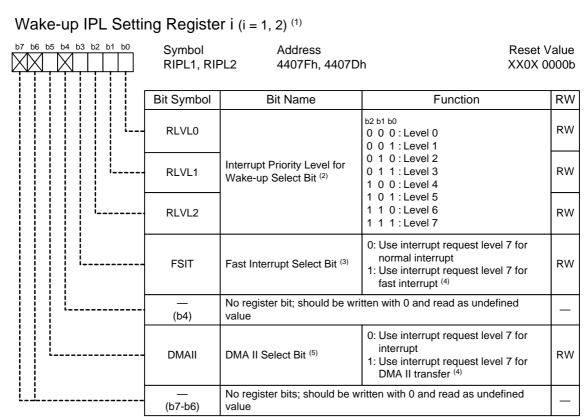

|     | 14.1.1  | Registers RIPL1 and RIPL2                             | 171 |

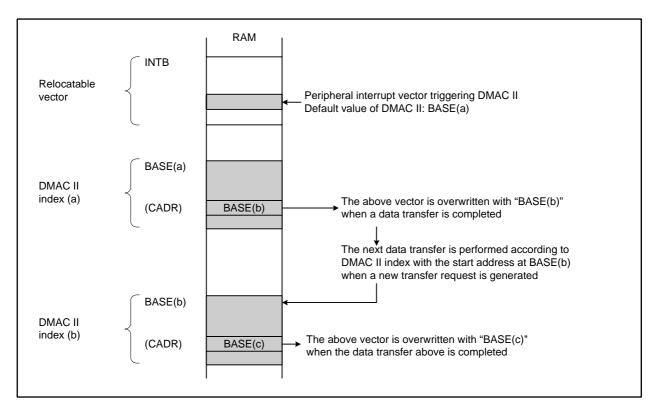

|     | 14.1.2  | DMAC II Index                                         | 172 |

|     | 14.1.3  | Interrupt Control Register of the Peripheral Function | 175 |

|     | 14.1.4  | Relocatable Vector Table of the Peripheral Function   | 175 |

|     | 14.1.5  | IRLT Bit in the IIOiIE Register (i = 0 to 11)         | 175 |

| 14  | 4.2 DN  | AAC II Performance                                    | 175 |

| 14  | 4.3 Tra | ansfer Types                                          | 175 |

|     | 14.3.1  | Memory-to-memory Transfer                             | 175 |

|     | 14.3.2  | Immediate Data Transfer                               | 176 |

|     | 14.3.3  | Calculation Transfer                                  | 176 |

| 14  | 4.4 Tra | ansfer Modes                                          | 176 |

|     | 14.4.1  | Single Transfer                                       | 176 |

|     | 14.4.2  | Burst Transfer                                        | 176 |

|     | 14.4.3  | Multiple Transfer                                     | 176 |

| 14  | 4.5 Ch  | nained Transfer                                       | 177 |

| 14  | 4.6 DN  | /IA II Transfer Complete Interrupt                    | 177 |

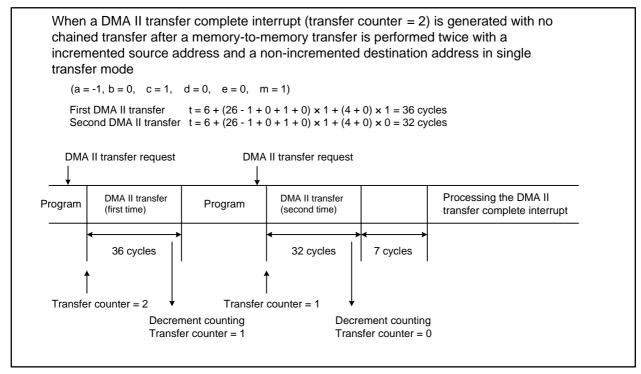

| 14  | 4.7 Ex  | ecution Time                                          | 178 |

| 15. | Progra  | ammable I/O Ports                                     | 179 |

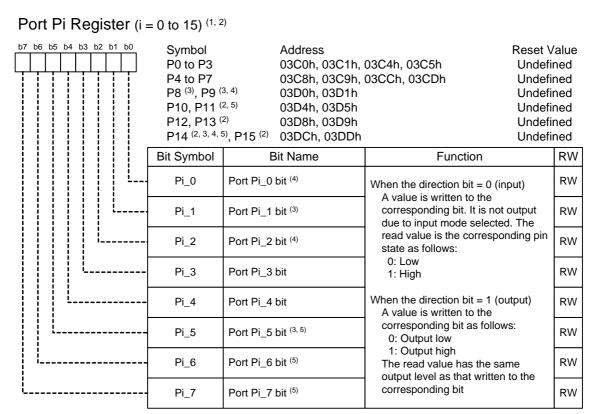

| 1   | 5.1 Po  | ort Pi Register (Pi register, i = 0 to 15)            | 181 |

| 16. | Timer   | S                                                     | 182 |

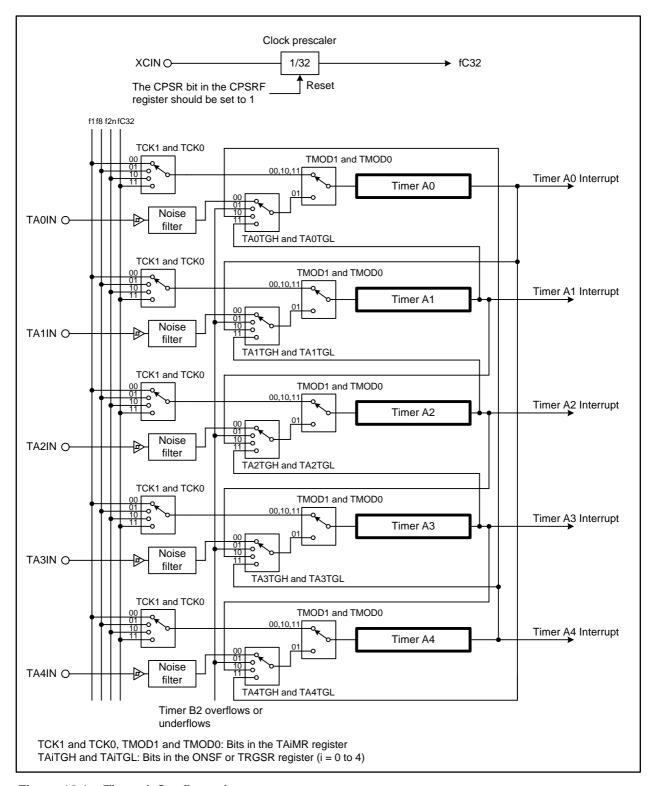

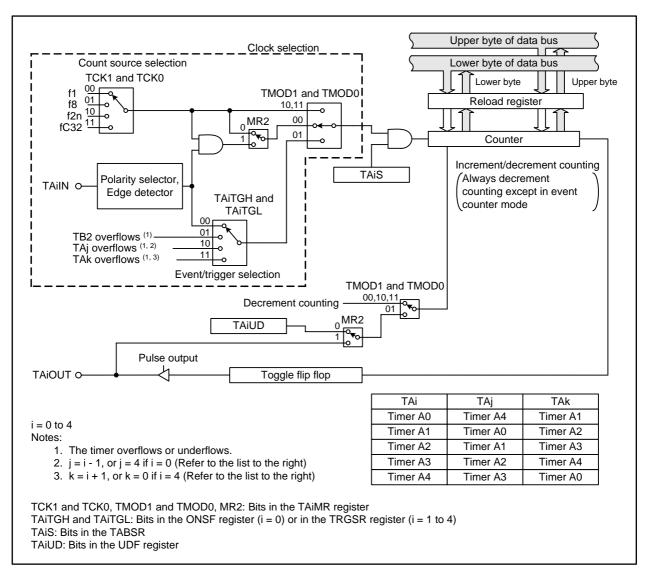

| 16  | 6.1 Tir | ner A                                                 | 184 |

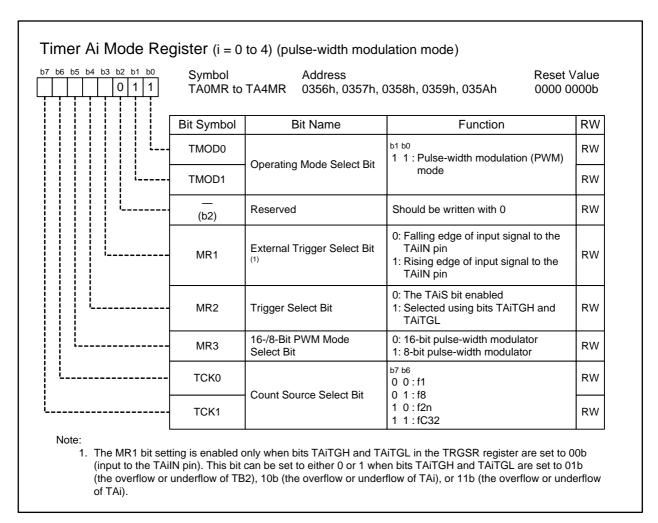

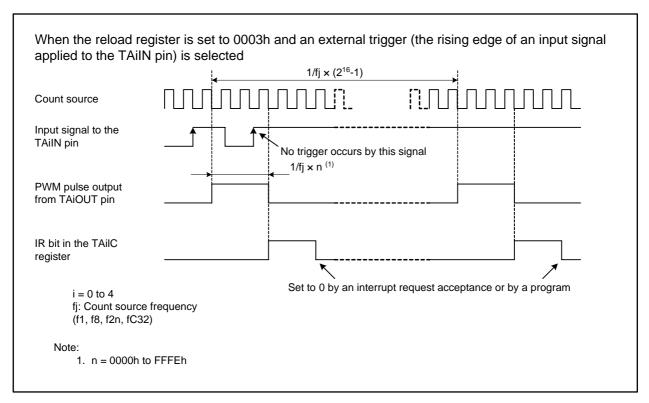

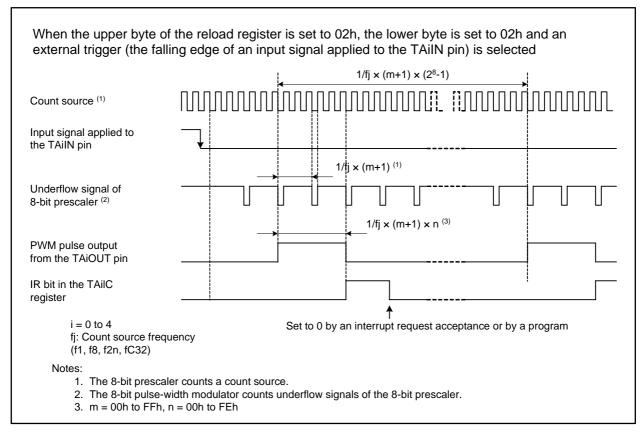

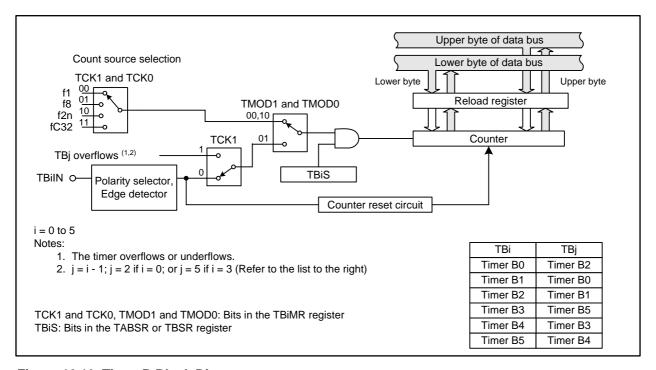

|     | 16.1.1  | Timer Mode                                            | 191 |

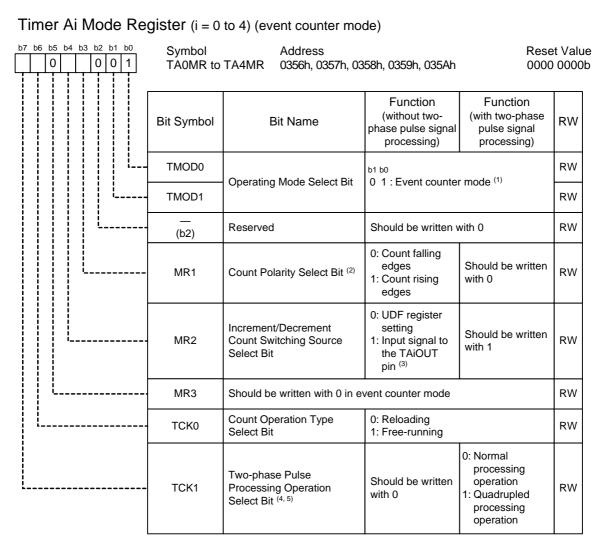

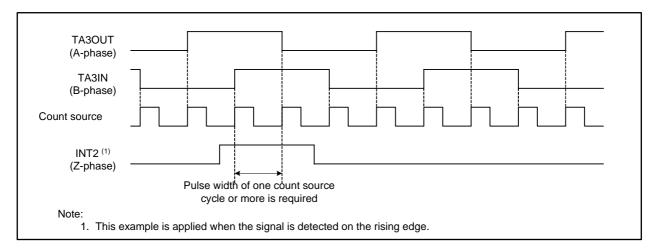

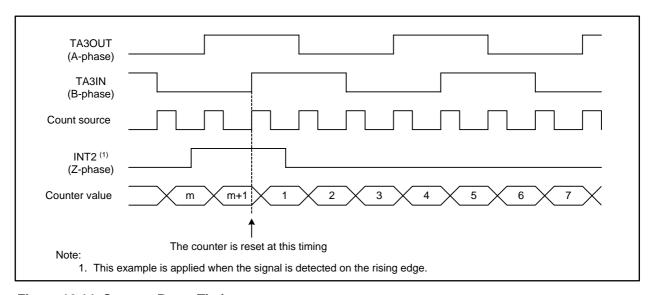

|     | 16 1 2  | Event Counter Mode                                    | 193 |

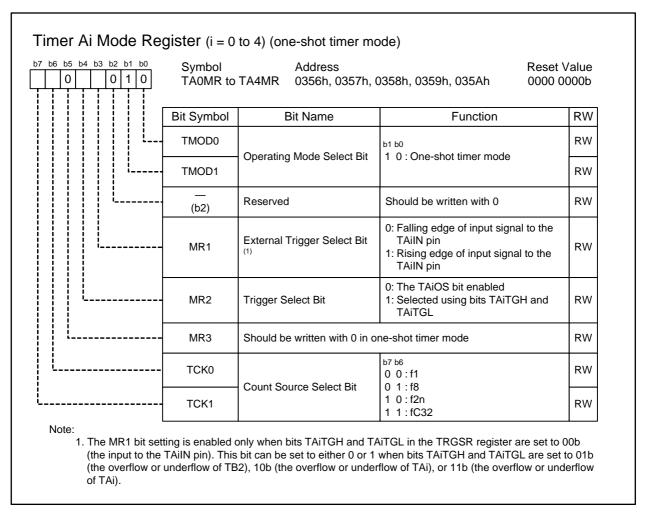

| 16.1.3  | One-shot Timer Mode                                    | 197 |

|---------|--------------------------------------------------------|-----|

| 16.1.4  | Pulse-width Modulation Mode                            | 199 |

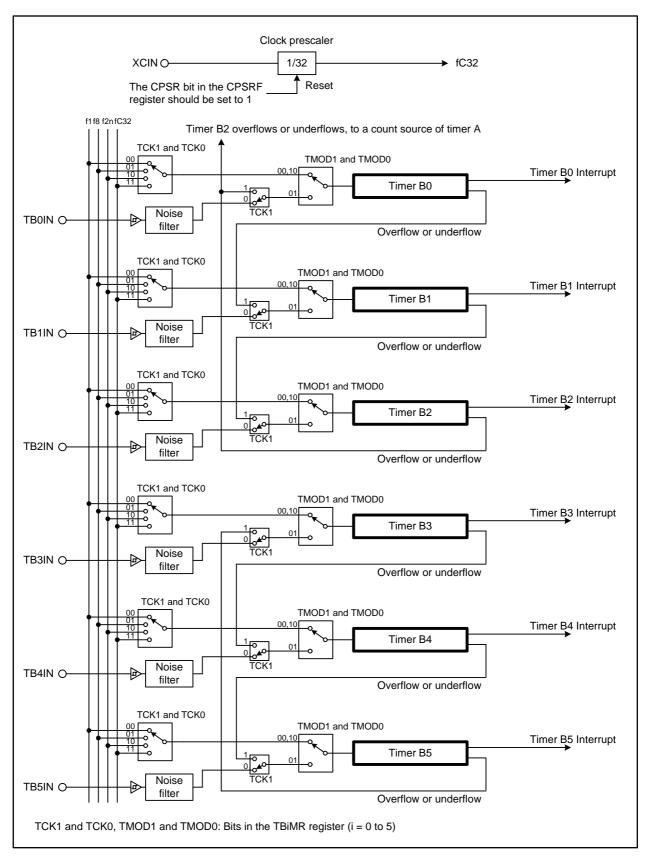

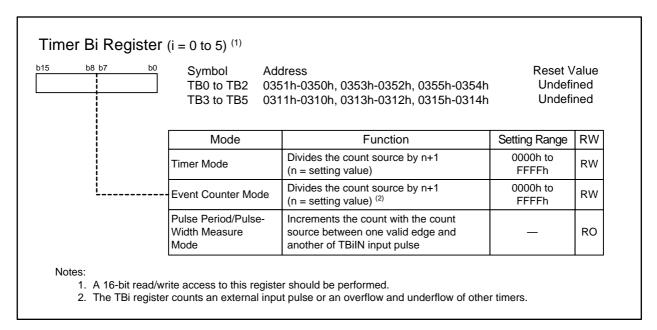

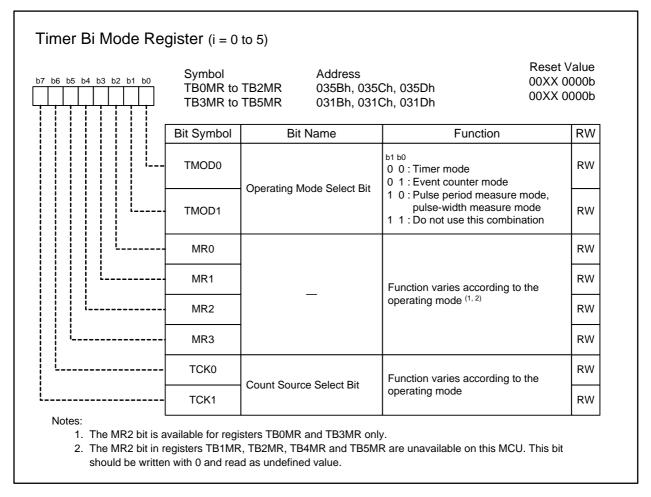

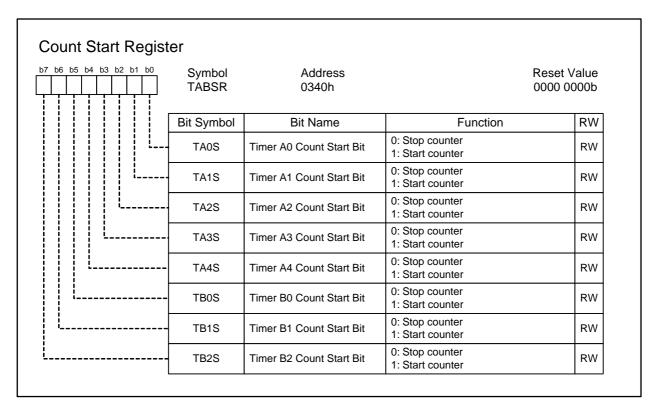

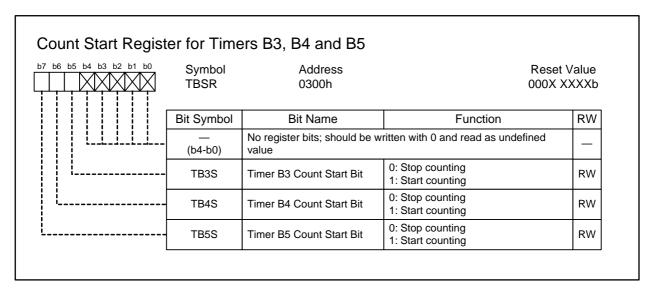

| 16.2    | Timer B                                                | 202 |

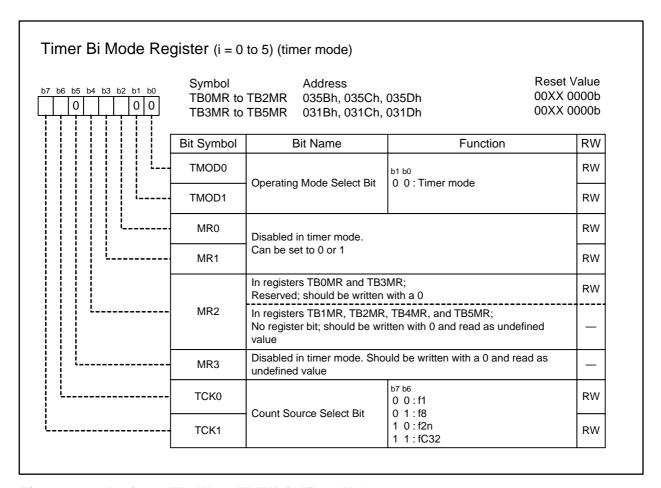

| 16.2.1  | Timer Mode                                             | 205 |

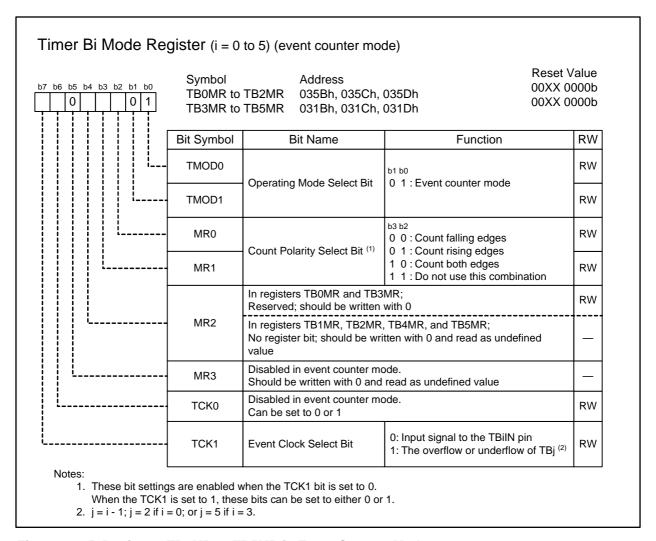

| 16.2.2  | Event Counter Mode                                     | 207 |

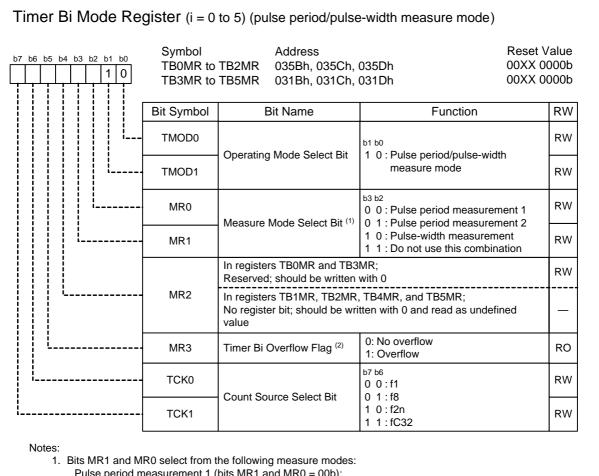

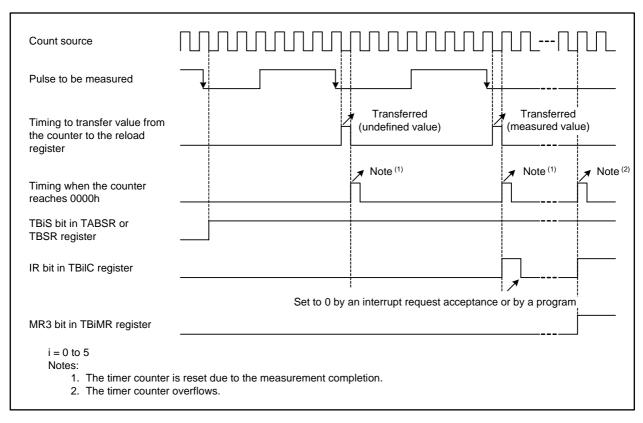

| 16.2.3  | Pulse Period/Pulse-width Measure Mode                  | 209 |

| 16.3    | Notes on Timers                                        | 212 |

| 16.3.1  | Timer A and Timer B                                    | 212 |

| 16.3.2  | Timer A                                                | 212 |

| 16.3.3  | Timer B                                                | 214 |

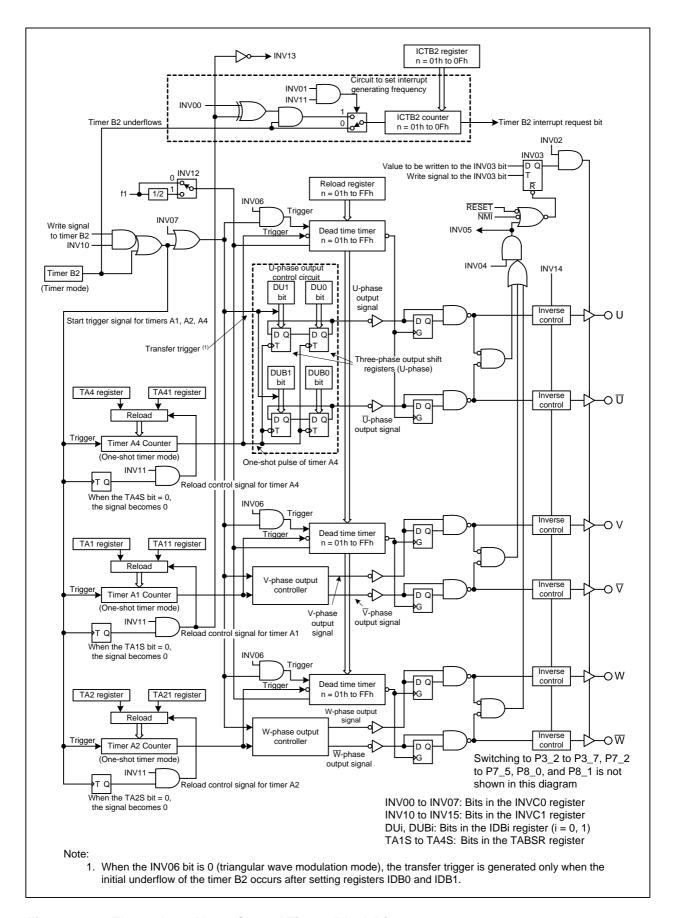

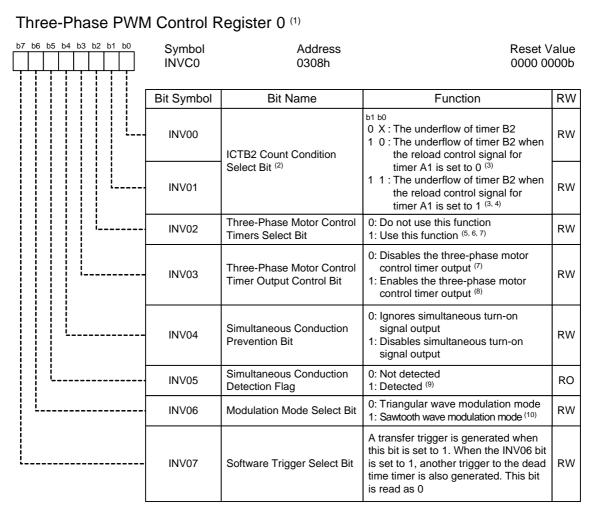

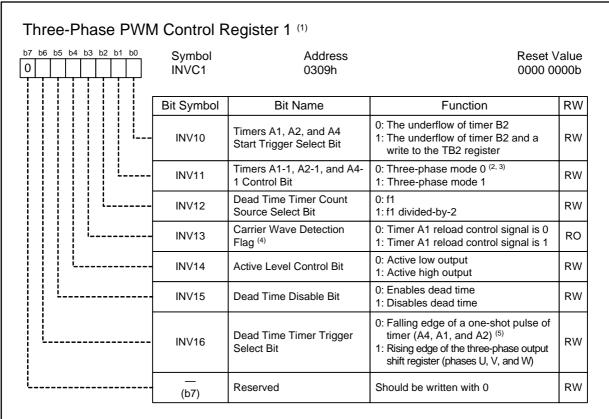

| 17. Thr | ee-phase Motor Control Timers                          | 215 |

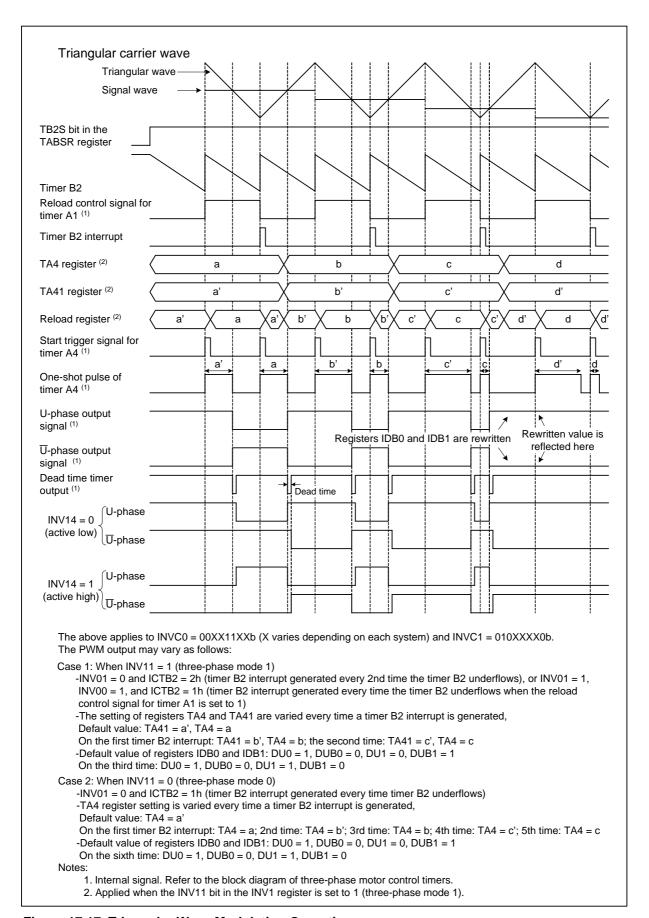

| 17.1    | Modulation Modes of Three-phase Motor Control Timers   | 222 |

| 17.2    | Timer B2                                               | 223 |

| 17.3    | Timers A4, A1, and A2                                  | 225 |

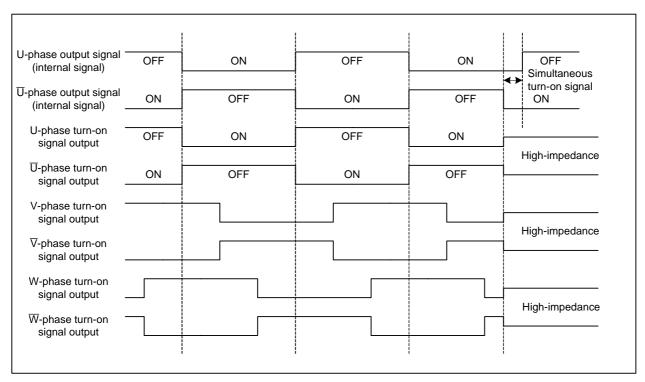

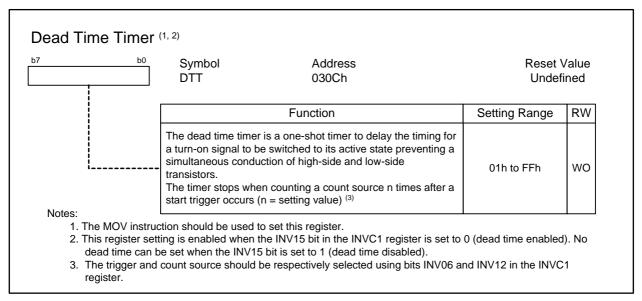

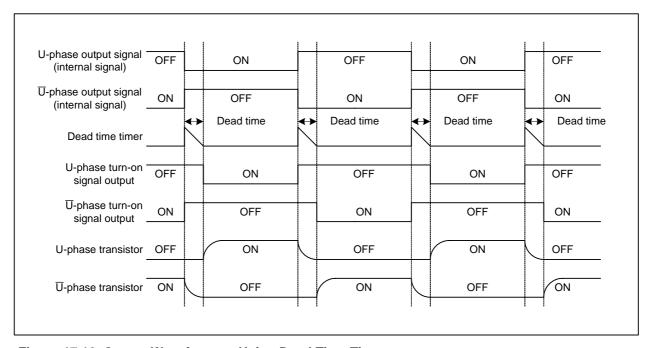

| 17.4    | Simultaneous Conduction Prevention and Dead Time Timer | 228 |

| 17.5    | Three-phase Motor Control Timer Operation              | 229 |

| 17.6    | Notes on Three-phase Motor Control Timers              | 232 |

| 17.6.1  | Shutdown                                               | 232 |

| 17.6.2  | Register setting                                       | 232 |

| l8. Ser | ial Interface                                          | 233 |

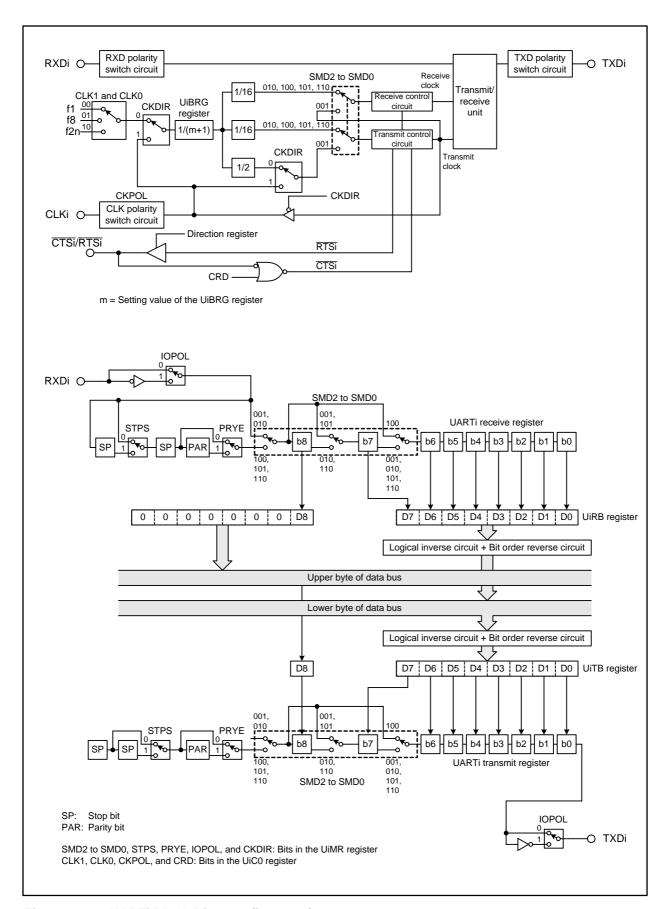

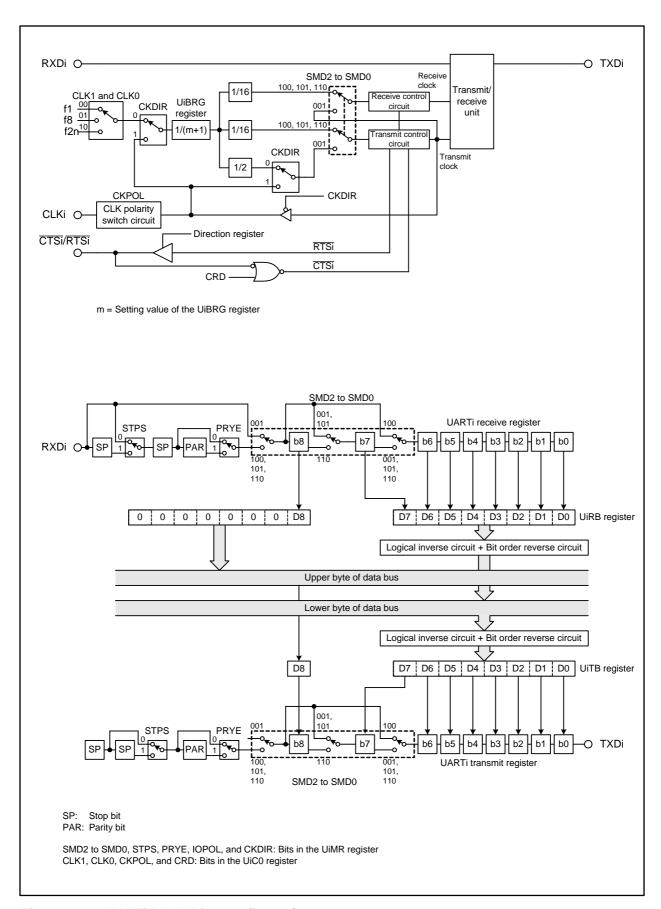

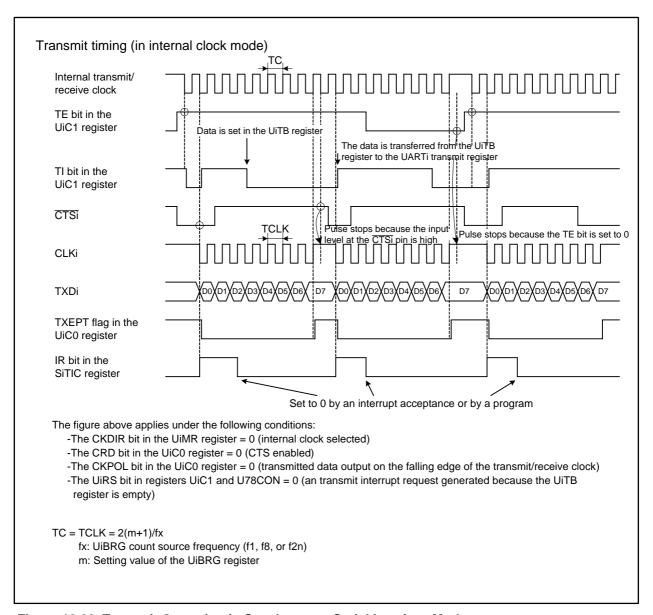

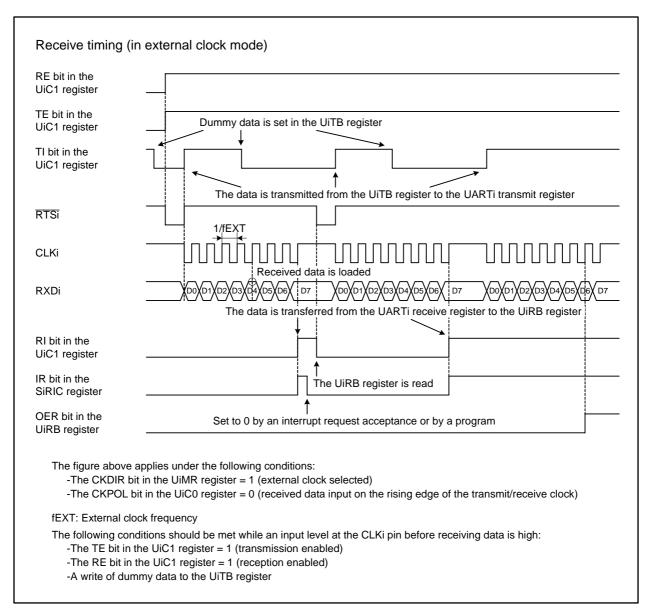

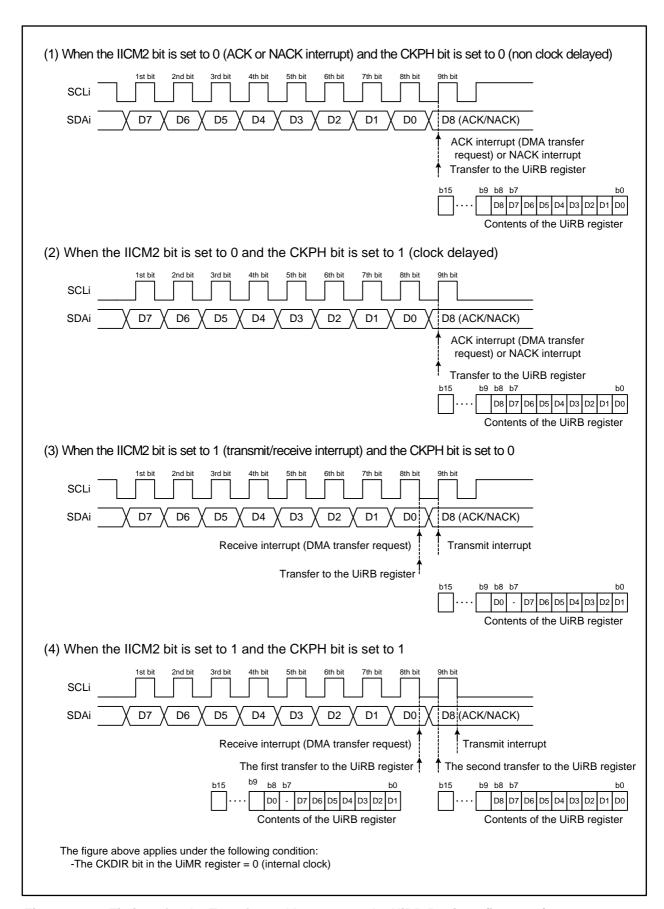

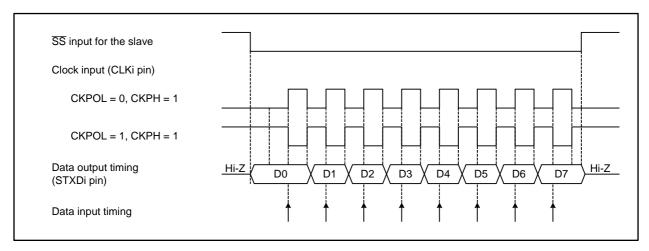

| 18.1    | Synchronous Serial Interface Mode                      | 250 |

| 18.1.1  | Reset Procedure on Transmit/Receive Error              | 255 |

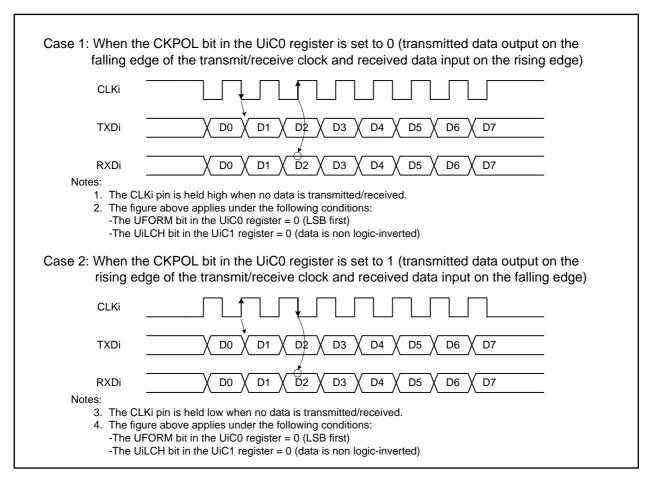

| 18.1.2  | CLK Polarity                                           | 255 |

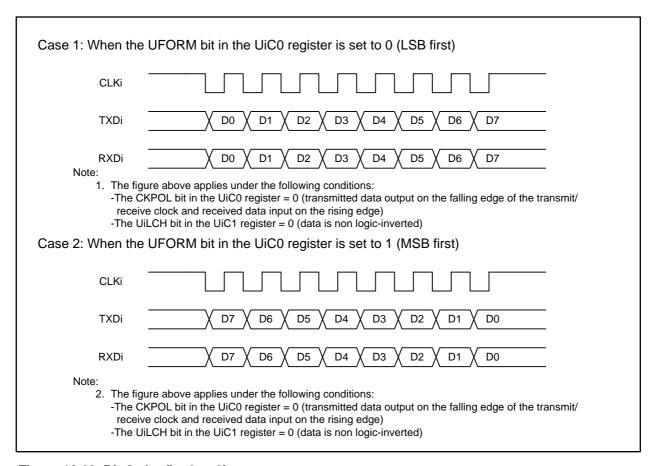

| 18.1.3  | LSB First and MSB First Selection                      | 256 |

| 18.1.4  | Continuous Receive Mode                                | 256 |

| 18.1.5  | Serial Data Logical Inversion                          | 257 |

| 18.1.6  | CTS/RTS Function                                       | 257 |

| 18.2    | Asynchronous Serial Interface Mode (UART Mode)         | 258 |

| 18.2.1  | Bit Rate                                               | 263 |

| 18.2.2  | Reset Procedure on Transmit/Receive Error              | 264 |

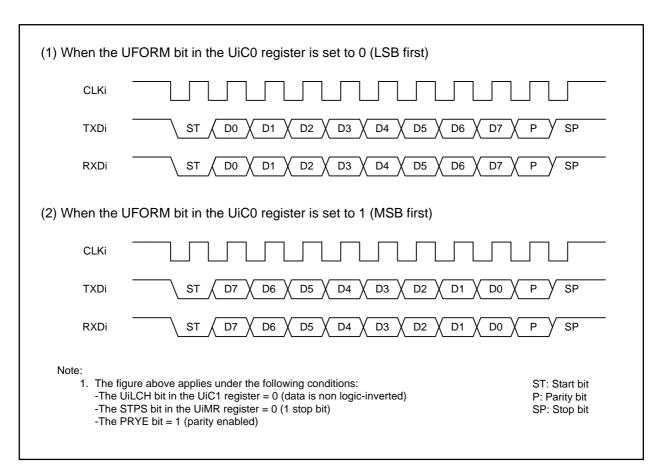

| 18.2.3  | LSB First and MSB First Selection                      | 264 |

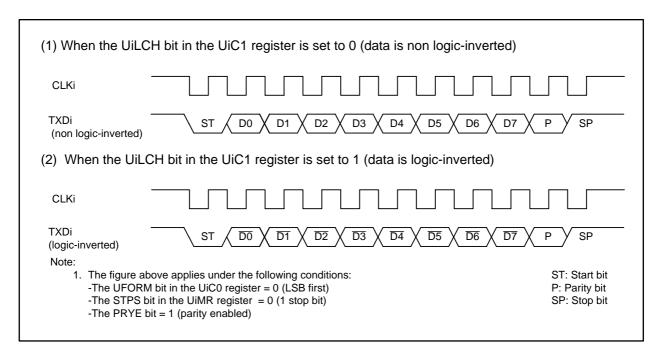

| 18.2.4  | Serial Data Logical Inversion                          | 265 |

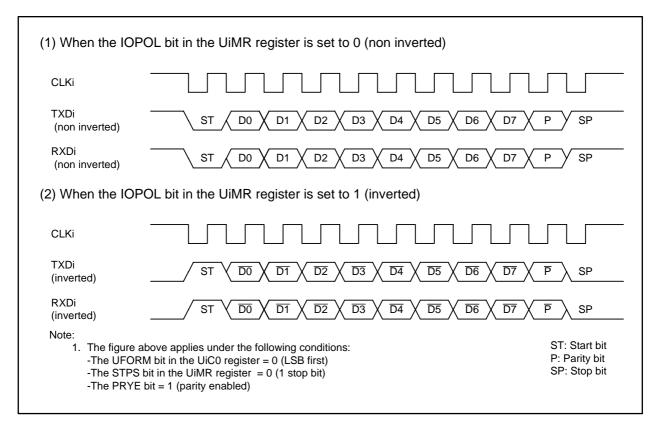

| 18.2.5  | TXD and RXD I/O Polarity Inversion                     | 266 |

| 18.2.6  | CTS/RTS Function                                       | 266 |

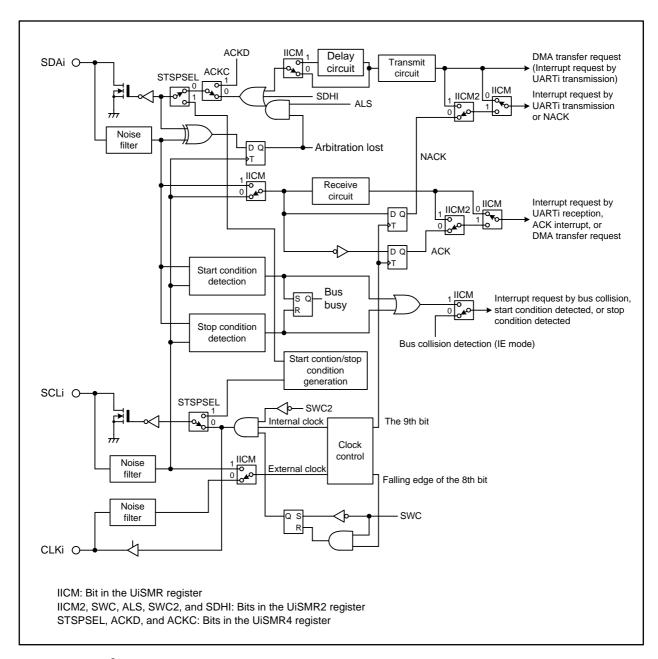

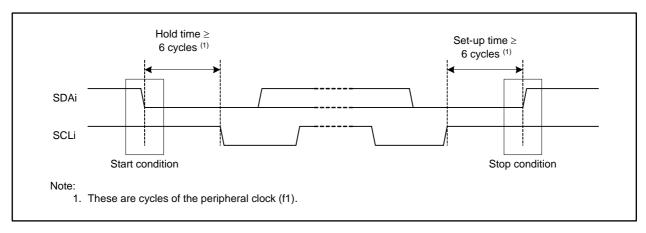

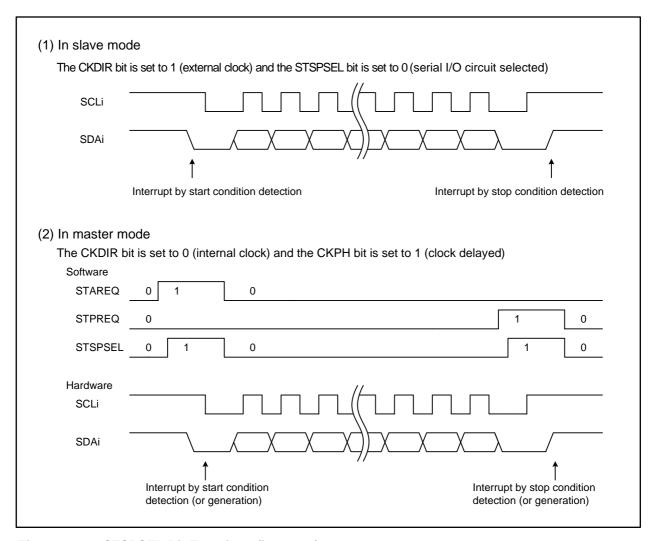

| 18.3    | Special Mode 1 (I <sup>2</sup> C Mode)                 | 267 |

| 18.3.1  | Start Condition and Stop Condition Detection           | 273 |

| 18.3.2  | Start Condition and Stop Condition Generation          | 273 |

| 18.3.3  | Arbitration                                            | 274 |

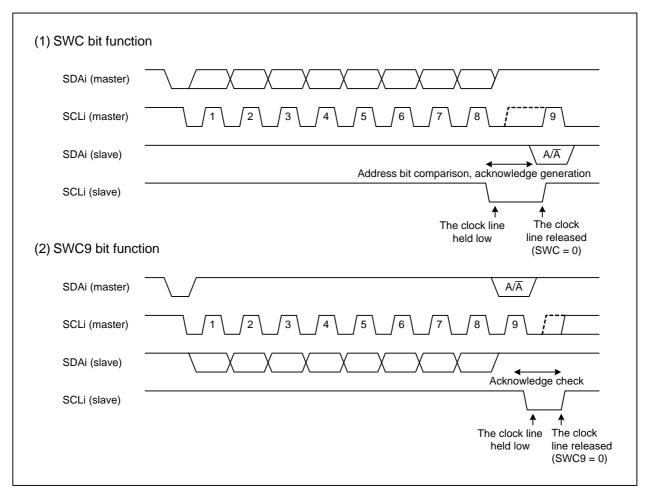

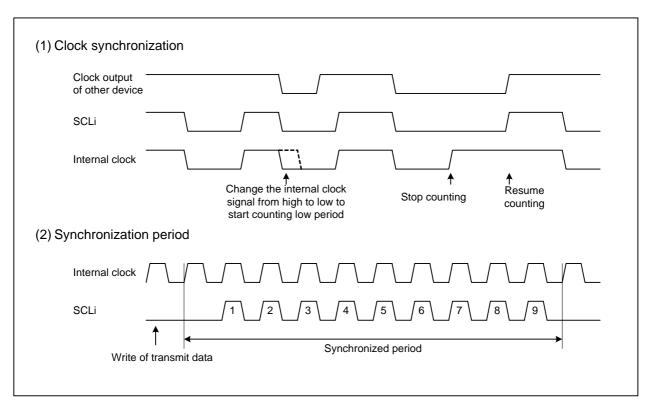

| 18.3.4  | SCL Control and Clock Synchronization                  | 275 |

| 18.3.5  | SDA Output                                             | 277 |

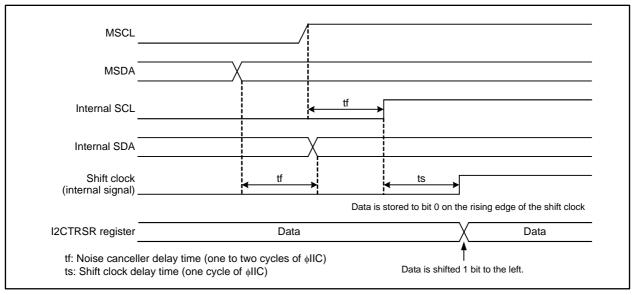

| 18.3.6  | SDA Input                                                          | 277 |

|---------|--------------------------------------------------------------------|-----|

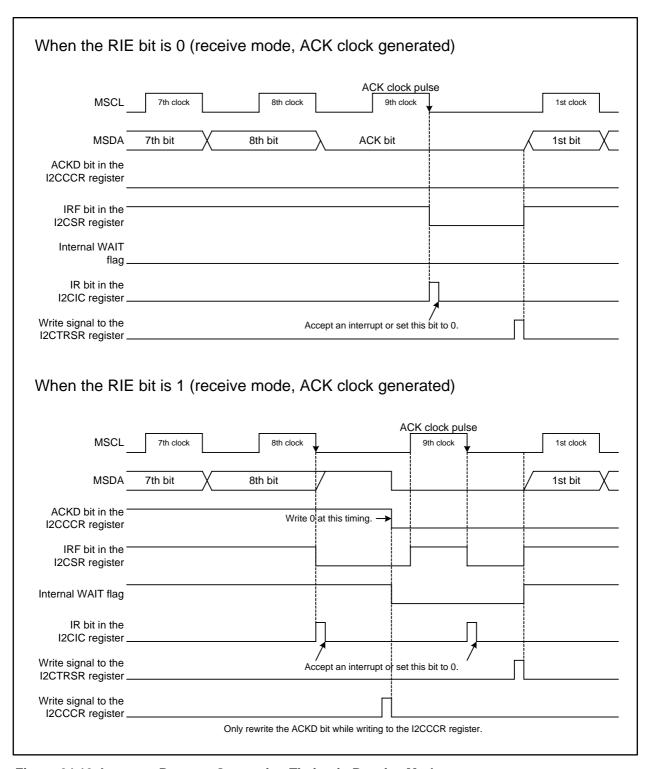

| 18.3.7  | Acknowledge                                                        | 277 |

| 18.3.8  | Initialization of Transmit/Receive Operation                       | 277 |

| 18.4    | Special Mode 2                                                     | 278 |

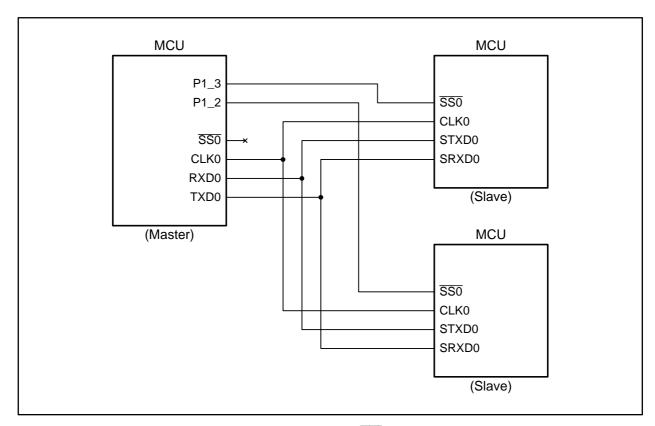

| 18.4.1  | SSi Input Pin Function (i = 0 to 6)                                | 280 |

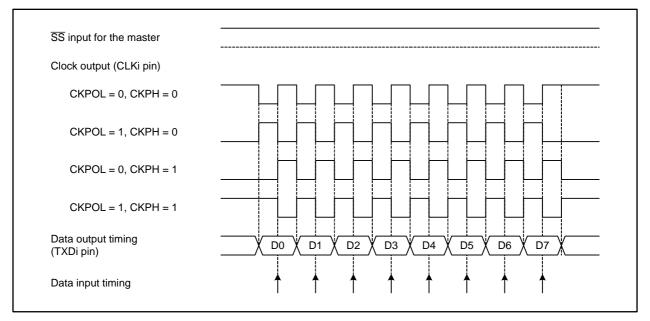

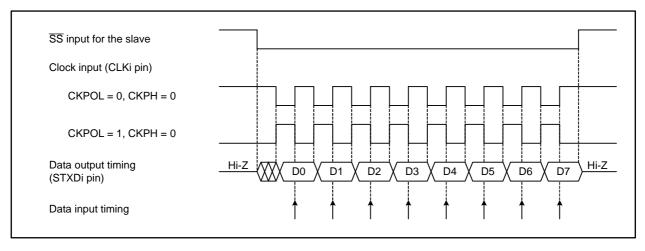

| 18.4.2  | Clock Phase Setting                                                | 281 |

| 18.5    | Notes on Serial Interface                                          | 283 |

| 18.5.1  | Changing the UiBRG Register (i = 0 to 8)                           | 283 |

| 18.5.2  | Synchronous Serial Interface Mode                                  | 283 |

| 18.5.3  | Special Mode 1 (I <sup>2</sup> C Mode)                             | 283 |

| 18.5.4  | Reset Procedure on Communication Error                             | 284 |

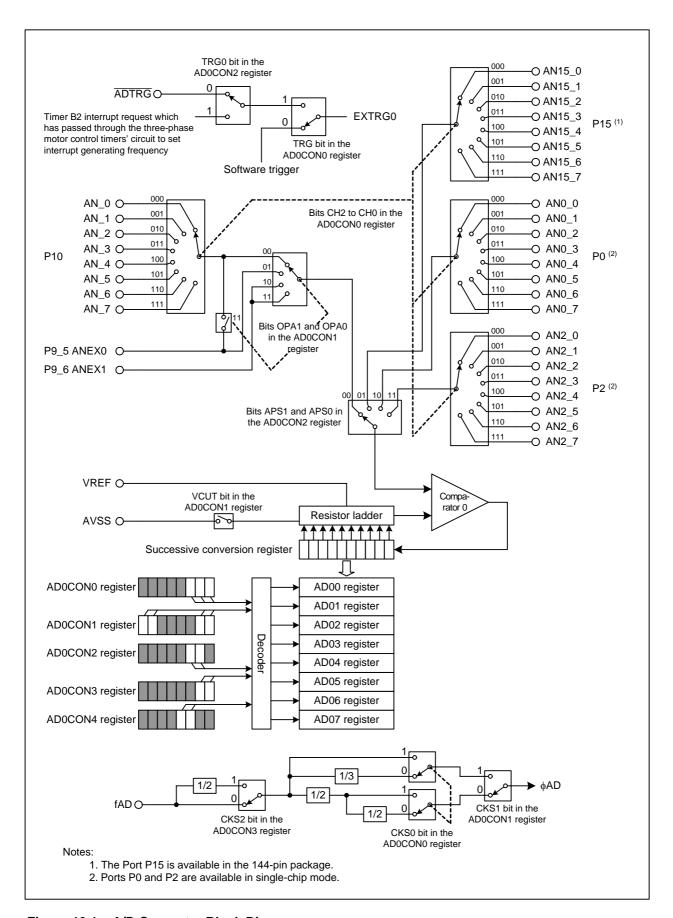

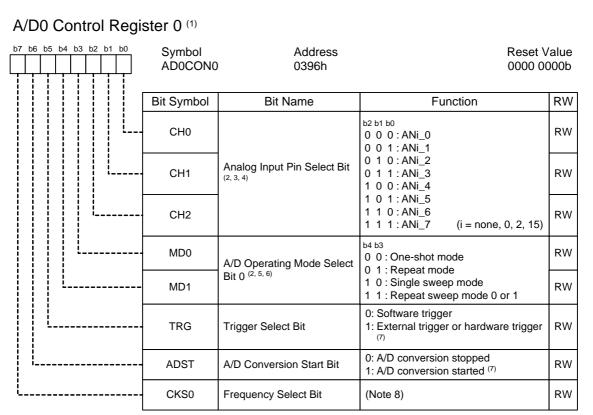

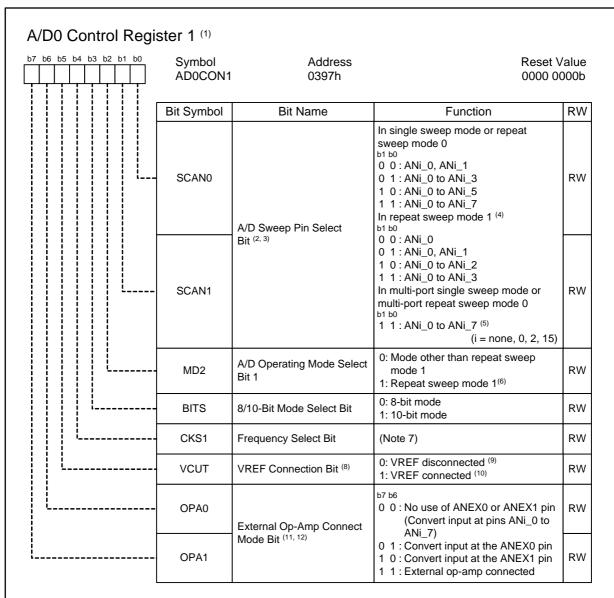

| 19. A/D | Converter                                                          | 285 |

| 19.1    | Mode Descriptions                                                  | 293 |

| 19.1.1  | One-shot Mode                                                      | 293 |

| 19.1.2  | Repeat Mode                                                        | 294 |

| 19.1.3  | Single Sweep Mode                                                  | 295 |

| 19.1.4  | Repeat Sweep Mode 0                                                | 296 |

| 19.1.5  | Repeat Sweep Mode 1                                                | 297 |

| 19.1.6  | Multi-port Single Sweep Mode                                       | 298 |

| 19.1.7  | Multi-port Repeat Sweep Mode 0                                     | 299 |

| 19.2    | Functions                                                          | 300 |

| 19.2.1  | Resolution Selection                                               | 300 |

| 19.2.2  | Sample and Hold Function                                           | 300 |

| 19.2.3  | Trigger Selection                                                  | 300 |

| 19.2.4  | DMAC Operating Mode                                                | 300 |

| 19.2.5  | Function-extended Analog Input Pins                                | 301 |

| 19.2.6  | External Operating Amplifier (Op-AMP) Connection Mode              | 301 |

| 19.2.7  | Power Saving                                                       | 302 |

| 19.2.8  | Output Impedance of Sensor Equivalent Circuit under A/D Conversion | 302 |

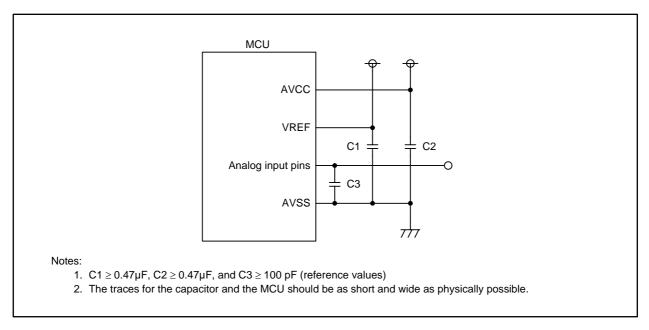

| 19.3    | Notes on A/D Converter                                             | 304 |

| 19.3.1  | Notes on Designing Boards                                          | 304 |

| 19.3.2  | Notes on Programming                                               | 305 |

| 20. D/A | Converter                                                          | 306 |

| 21. CR  | C Calculator                                                       | 308 |

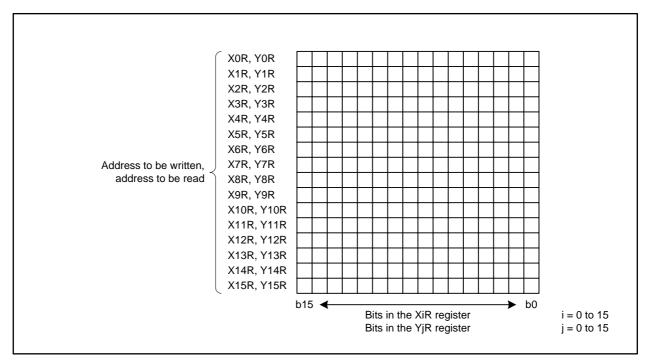

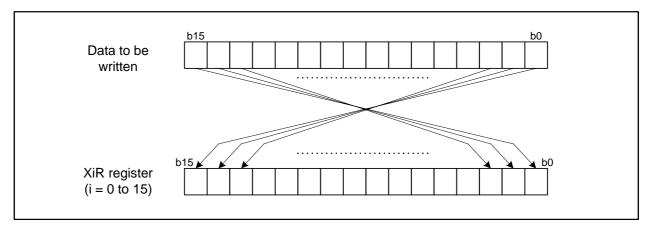

| 22. X-Y | Conversion                                                         | 311 |

| 22.1    | Data Conversion on Reading                                         | 312 |

| 22.2    | Data Conversion on Writing                                         | 21/ |

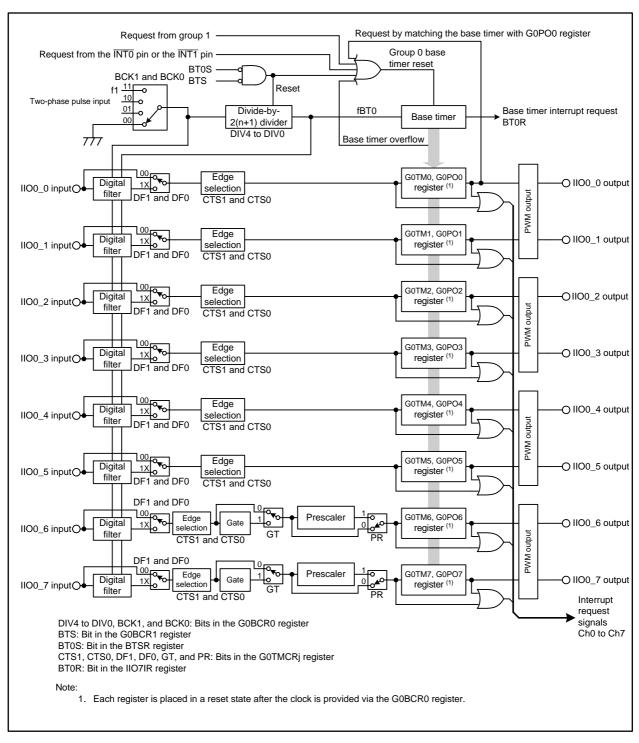

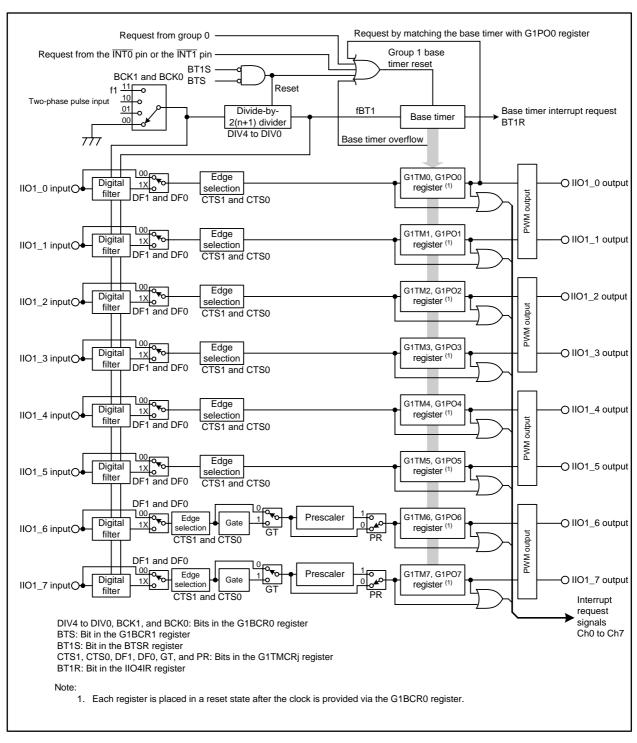

| 23. Inte | elligent I/O                                                                 | 315 |

|----------|------------------------------------------------------------------------------|-----|

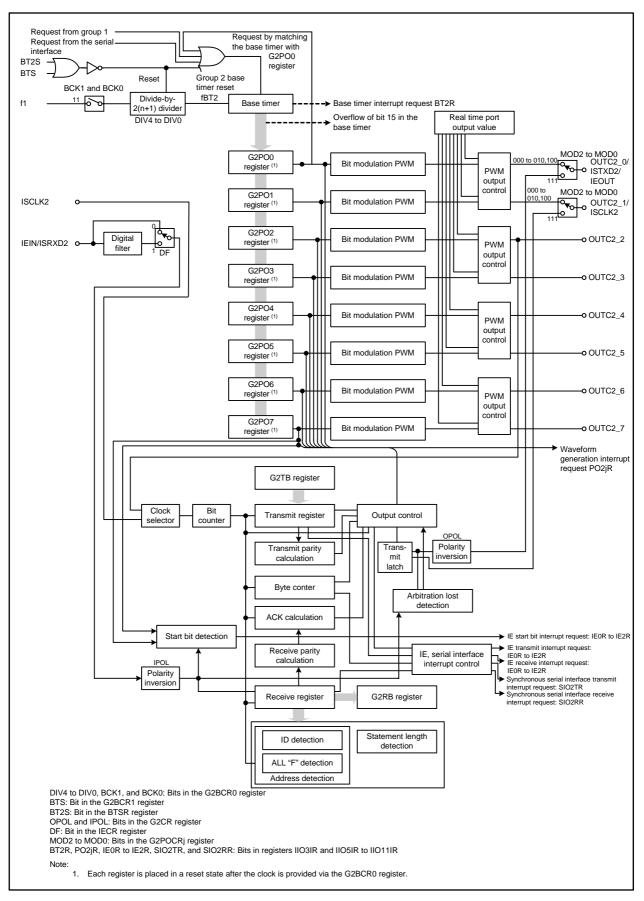

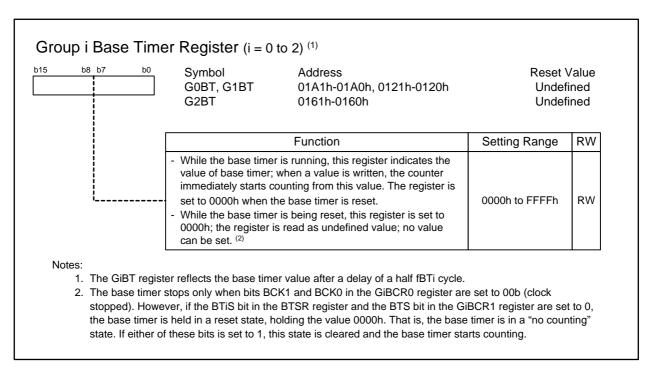

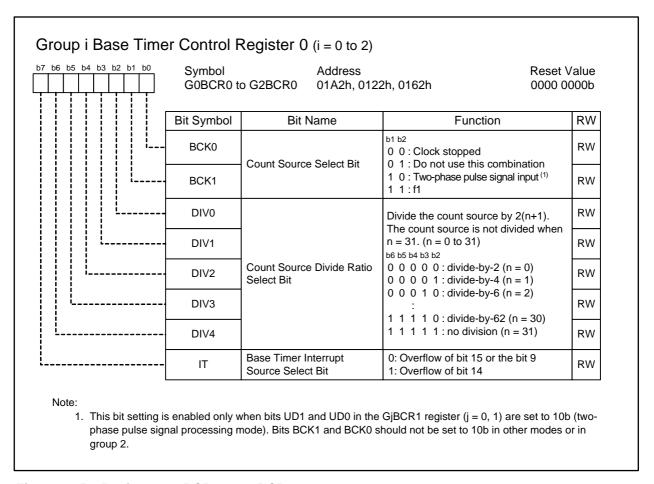

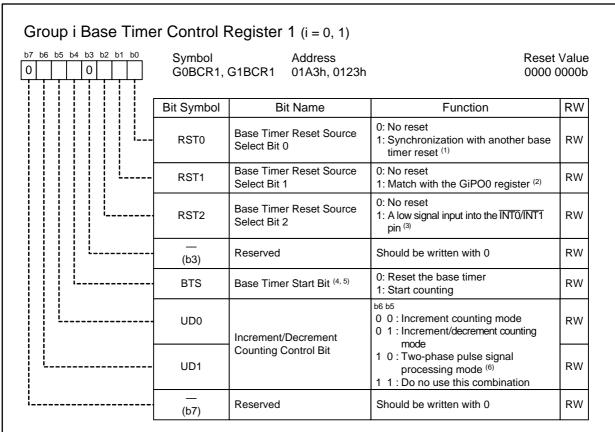

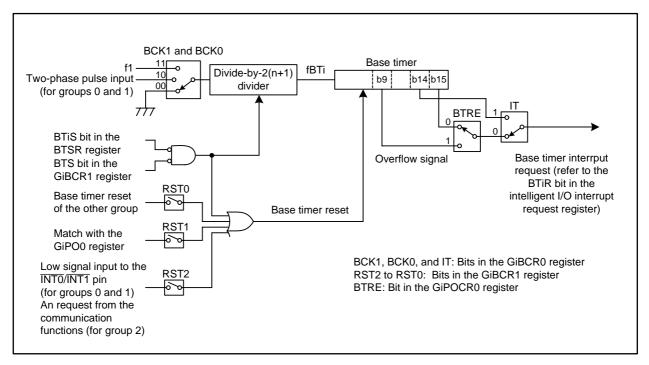

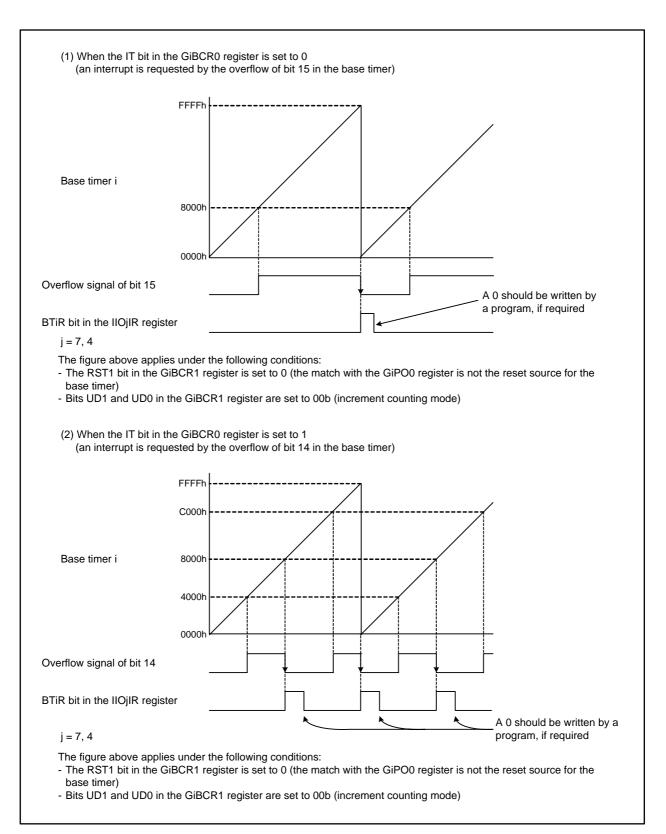

| 23.1     | Base Timer (for Groups 0 to 2)                                               | 330 |

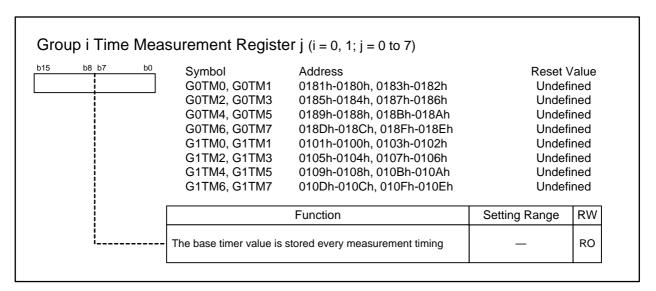

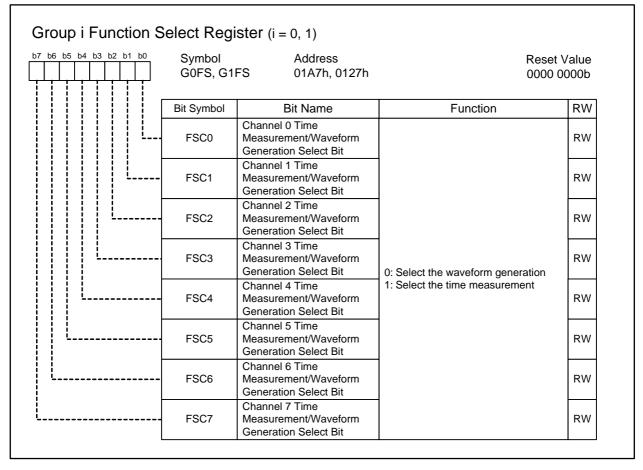

| 23.2     | Time Measurement (for Groups 0 and 1)                                        | 336 |

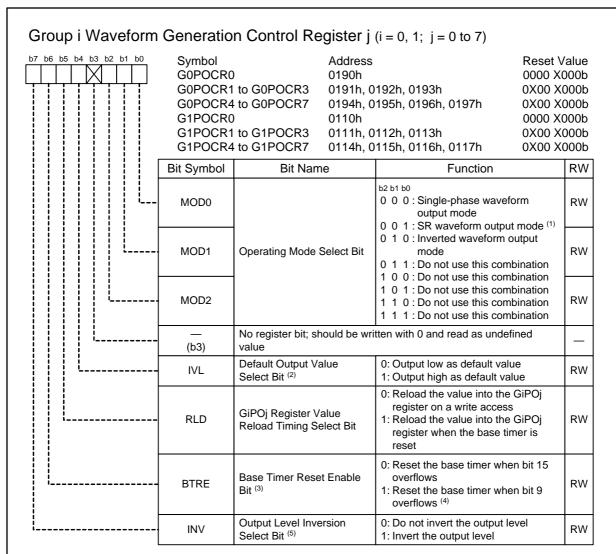

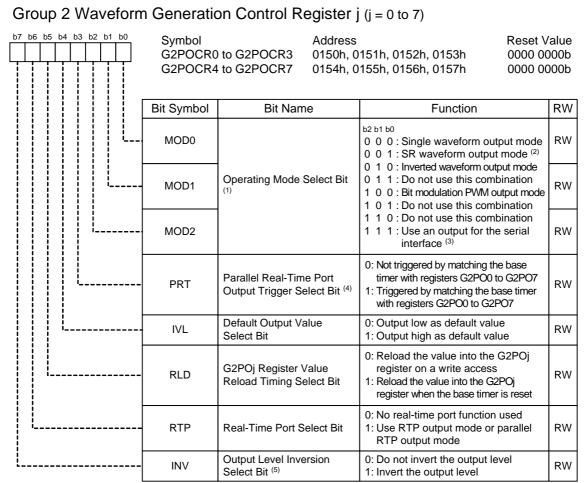

| 23.3     | Waveform Generation (for Groups 0 to 2)                                      | 340 |

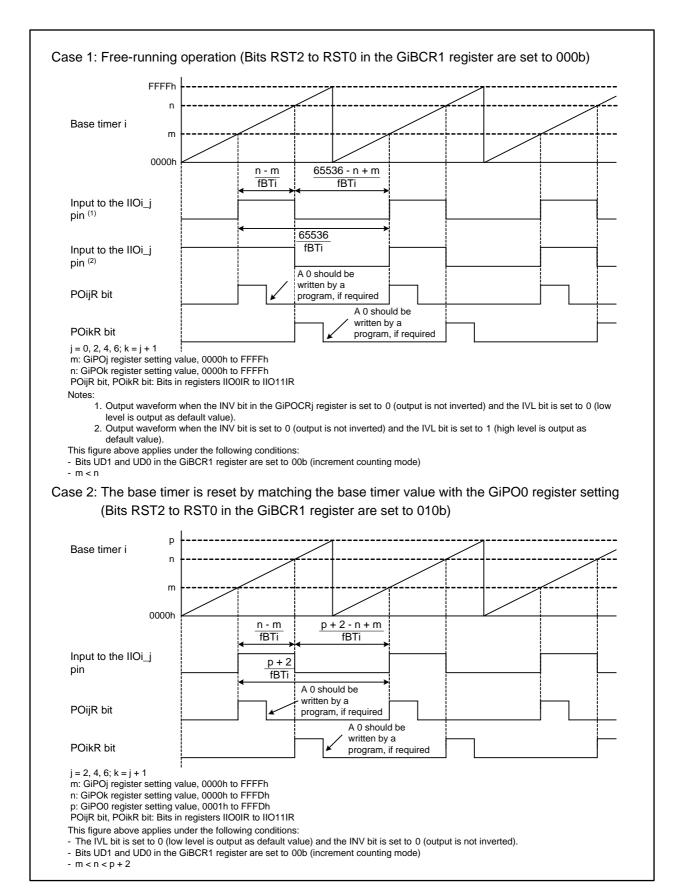

| 23.3.1   | Single-phase Waveform Output Mode (for Groups 0 to 2)                        | 341 |

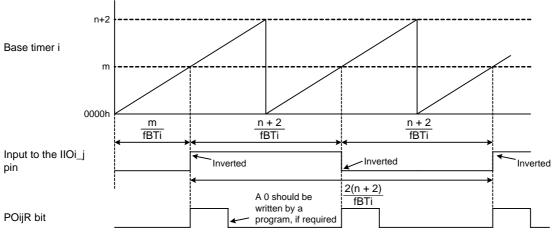

| 23.3.2   | Inverted Waveform Output Mode (for Groups 0 to 2)                            | 343 |

| 23.3.3   | Set/Reset Waveform Output Mode (SR Waveform Output Mode) (for Groups 0 to 2) | 345 |

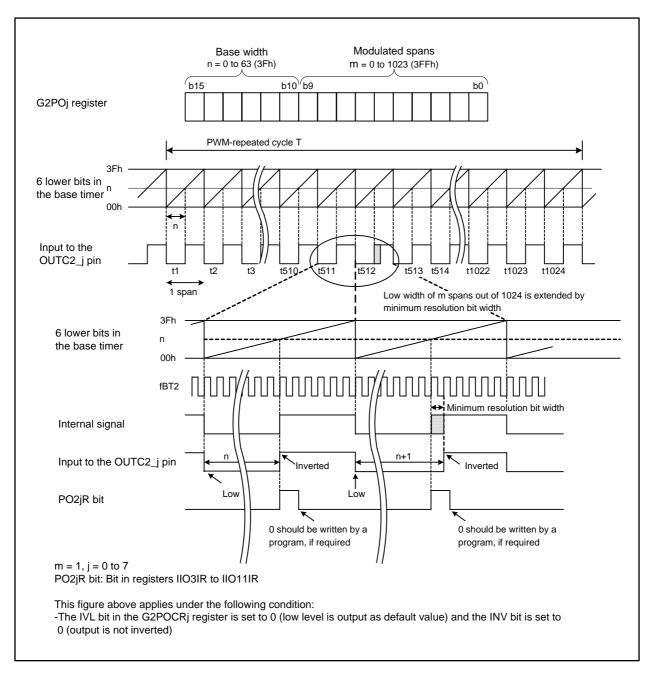

| 23.3.4   | Bit Modulation PWM Output Mode (for Group 2)                                 | 348 |

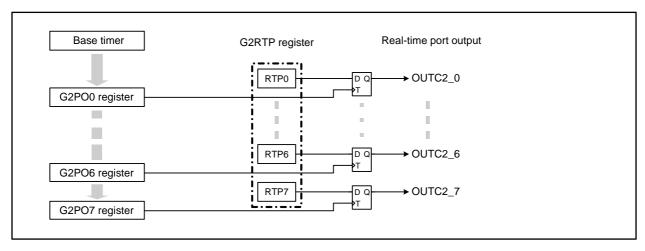

| 23.3.5   | Real-Time Port Output Mode (RTP Output Mode) (for Group 2)                   | 350 |

| 23.3.6   | Parallel Real-Time Port Output Mode (RTP Output Mode) (for Group 2)          | 352 |

| 23.4     | Group 2 Serial Interface                                                     | 354 |

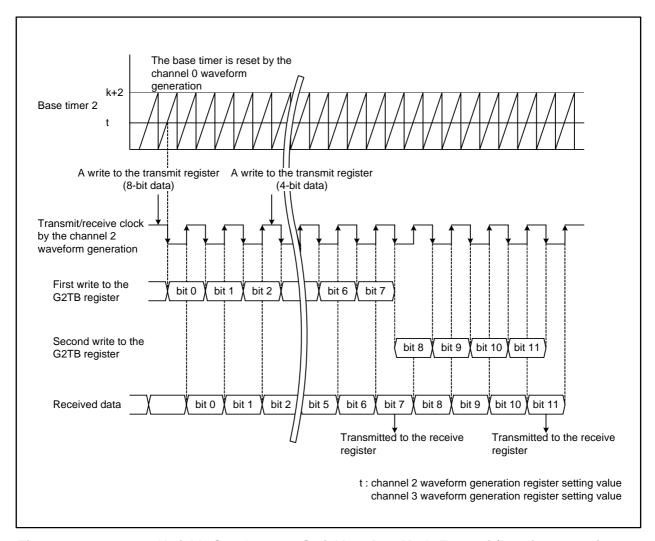

| 23.4.1   | Variable Synchronous Serial Interface Mode (for Group 2)                     | 359 |

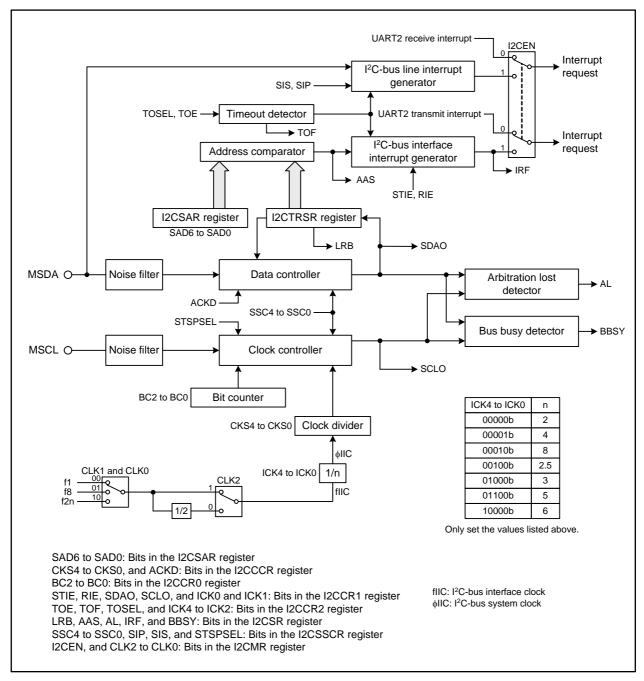

| 24. Mu   | lti-master I <sup>2</sup> C-bus Interface                                    | 362 |

| 24.1     | Multi-master I <sup>2</sup> C-bus Interface-associated Registers             | 364 |

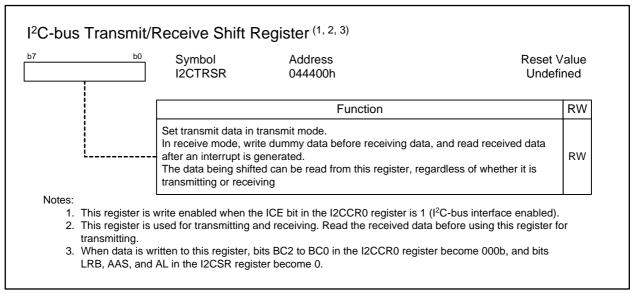

| 24.1.1   | I <sup>2</sup> C-bus Transmit/Receive Shift Register (I2CTRSR)               | 364 |

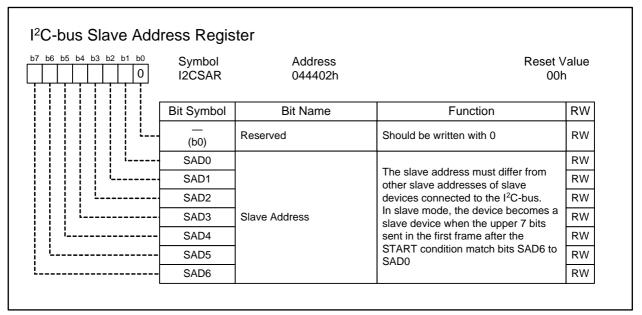

| 24.1.2   | I <sup>2</sup> C-bus Slave Address Register (I2CSAR)                         | 365 |

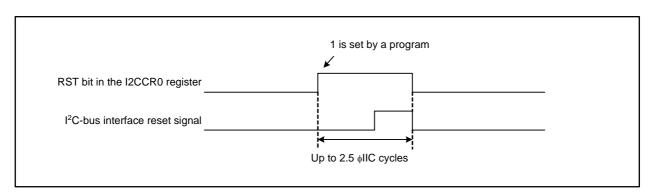

| 24.1.3   | I <sup>2</sup> C-bus Control Register 0 (I2CCR0)                             | 366 |

| 24.1.4   | I <sup>2</sup> C-bus Clock Control Register (I2CCCR)                         | 368 |

| 24.1.5   | I <sup>2</sup> C-bus START and STOP Conditions Control Register (I2CSSCR)    | 370 |

| 24.1.6   | I <sup>2</sup> C-bus Control Register 1 (I2CCR1)                             | 371 |

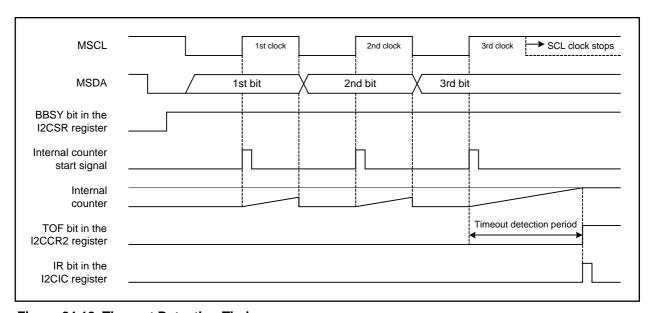

| 24.1.7   | I <sup>2</sup> C-bus Control Register 2 (I2CCR2)                             | 374 |

| 24.1.8   | I <sup>2</sup> C-bus Status Register (I2CSR)                                 | 376 |

| 24.1.9   | I <sup>2</sup> C-bus Mode Register (I2CMR)                                   | 380 |

| 24.2     | Generating a START Condition                                                 | 381 |

| 24.3     | Generating a STOP Condition                                                  | 383 |

| 24.4     | START Condition Redundancy Prevention Function                               | 384 |

| 24.5     | Detecting START and STOP Conditions                                          | 385 |

| 24.6     | Data Transmission and Reception                                              | 387 |

| 24.6.1   | Master Transmission                                                          | 388 |

| 24.6.2   | Slave Reception                                                              | 389 |

| 24.7     | Notes on Using Multi-master I <sup>2</sup> C-bus Interface                   | 390 |

| 24.7.1   | Accessing Multi-master I <sup>2</sup> C-bus Interface-Associated Registers   | 390 |

| 24.7.2   | Generating a Repeated START condition                                        | 392 |

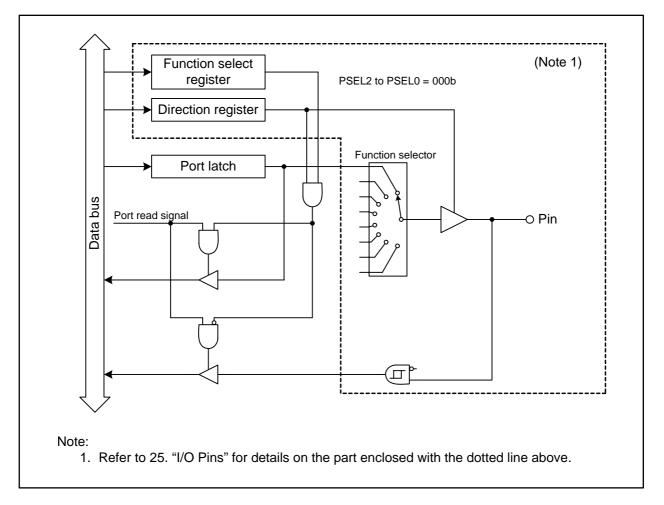

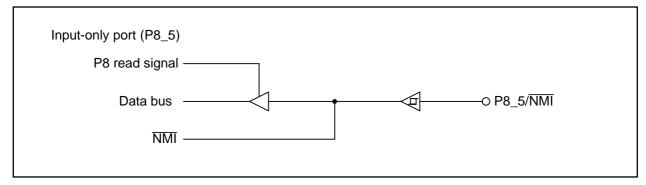

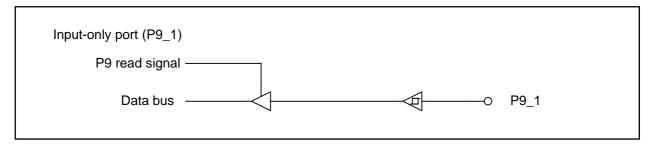

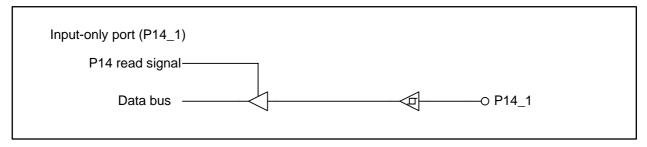

| 25. I/O  | Pins                                                                         | 393 |

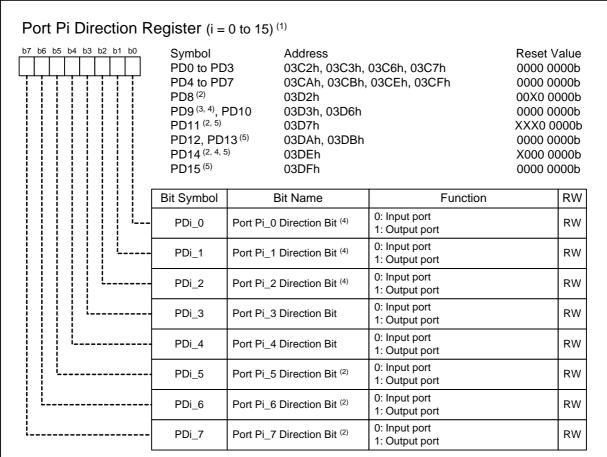

| 25.1     | Port Pi Direction Register (PDi Register, i = 0 to 15)                       | 394 |

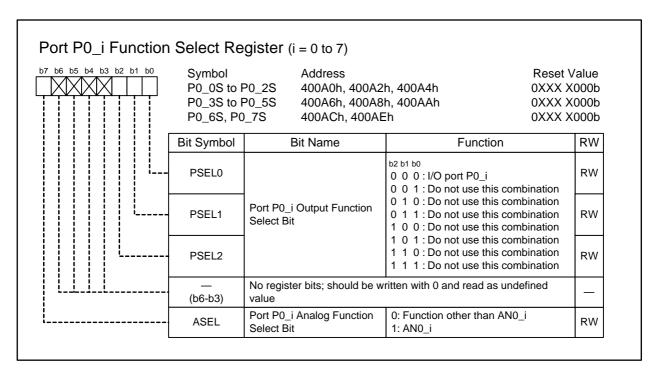

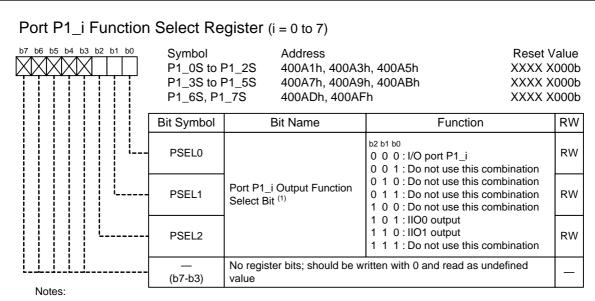

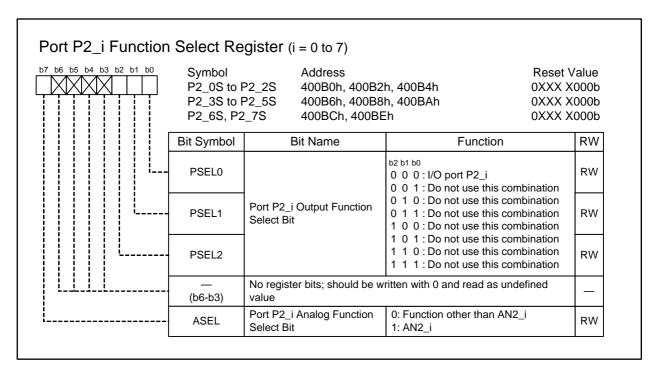

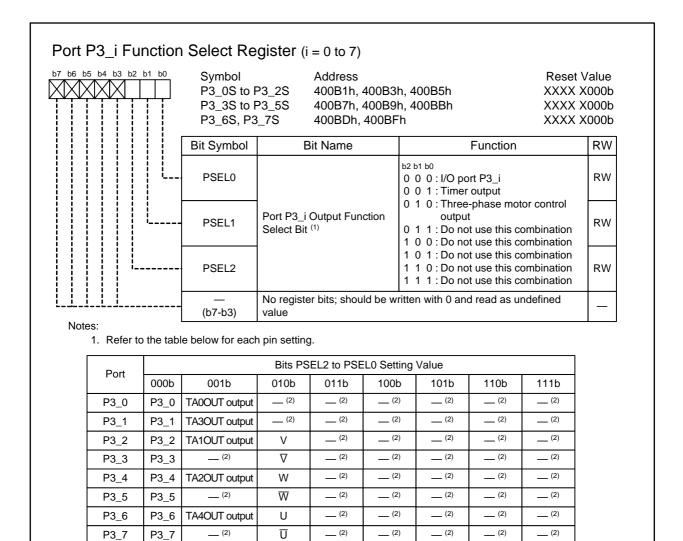

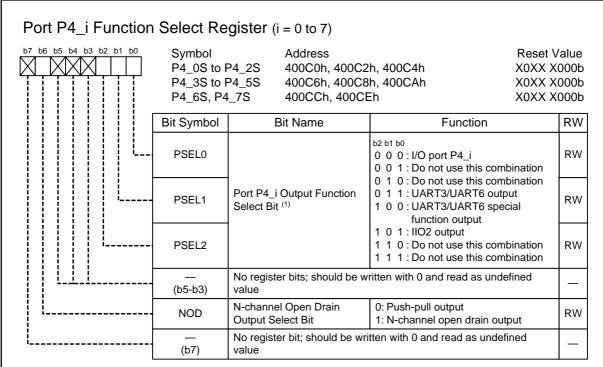

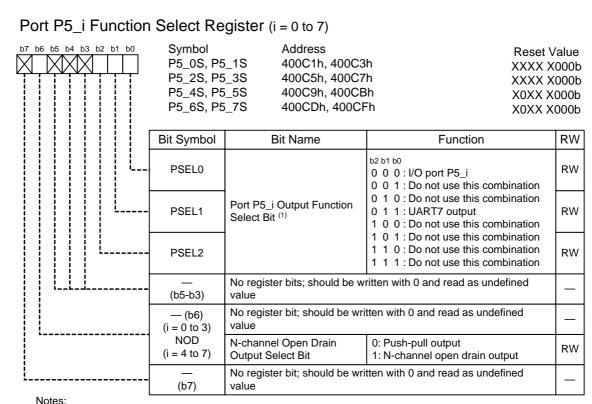

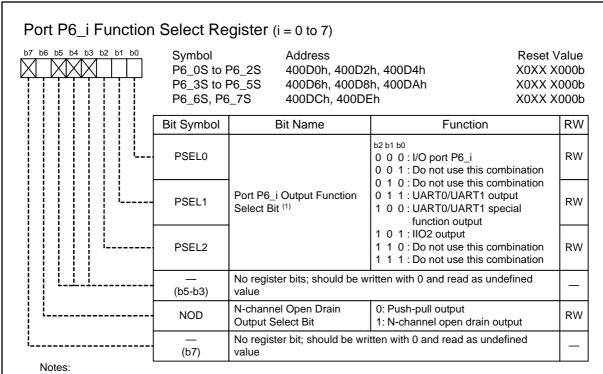

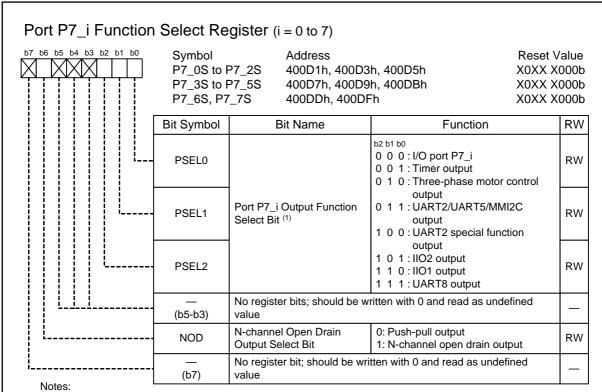

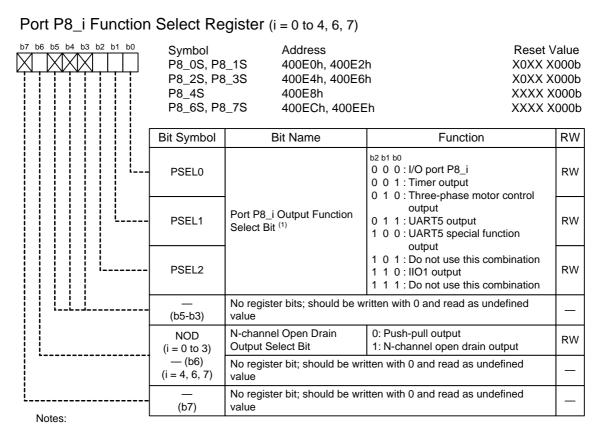

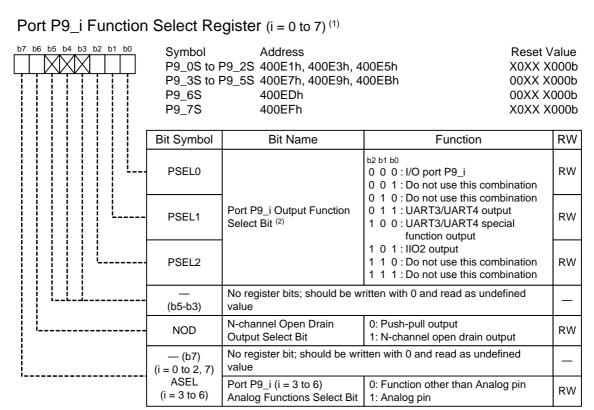

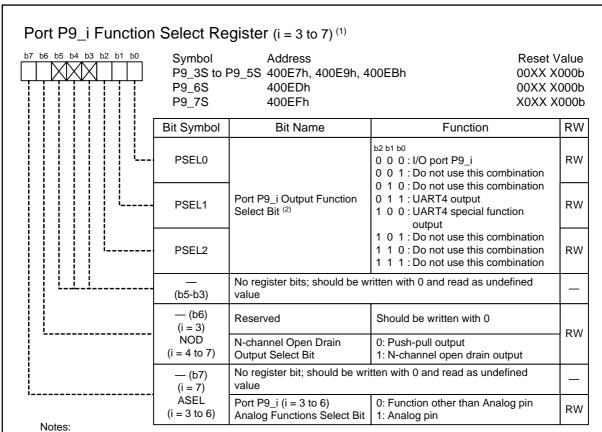

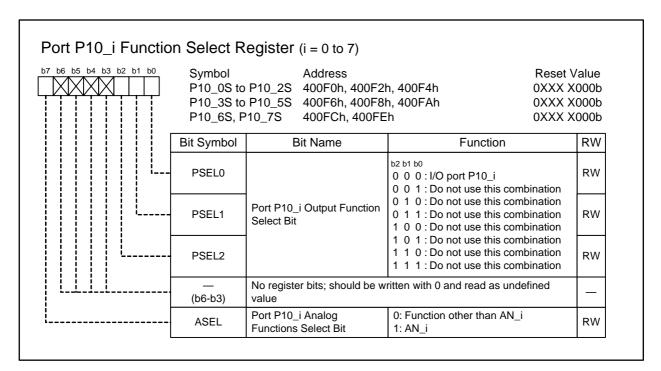

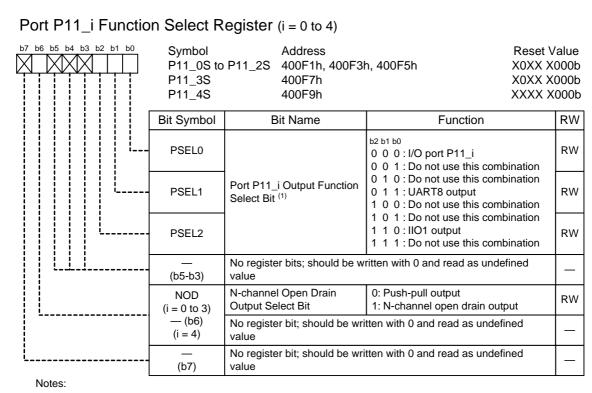

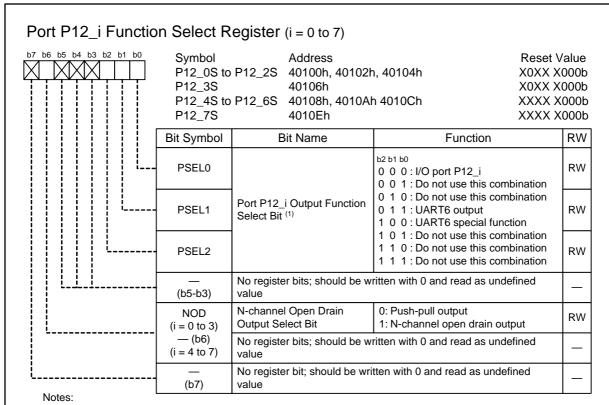

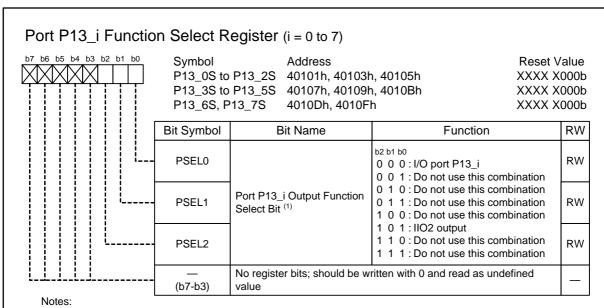

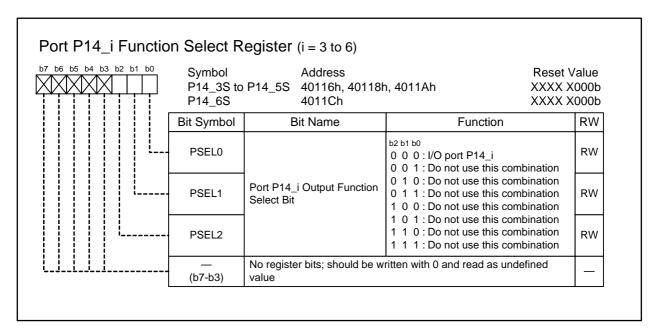

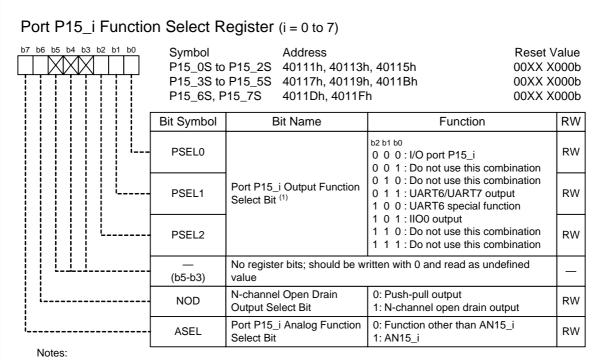

| 25.2     | Output Function Select Register                                              | 395 |

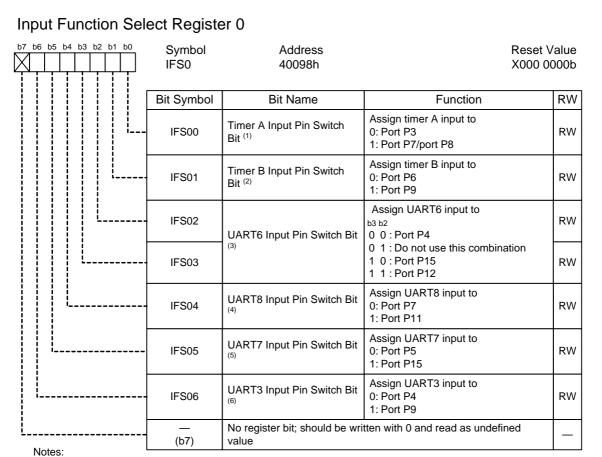

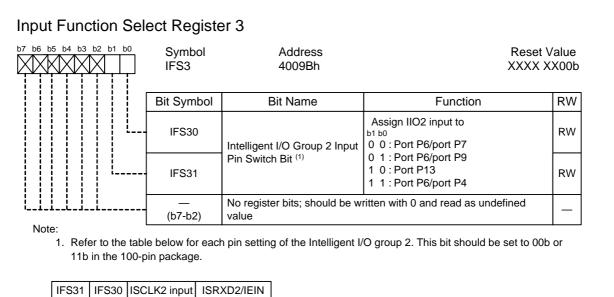

| 25.3     | Input Function Select Register                                               | 413 |

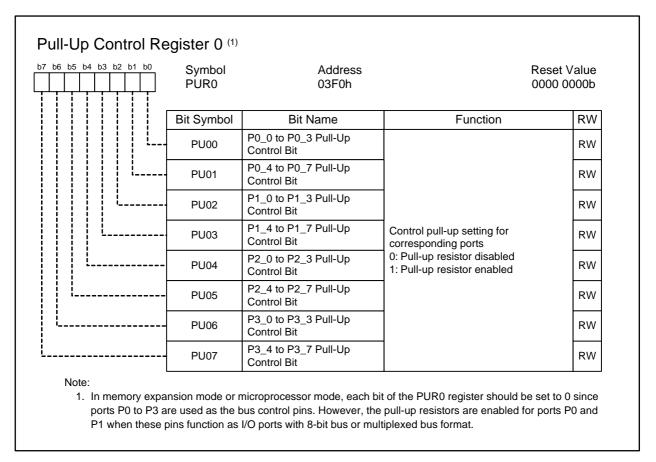

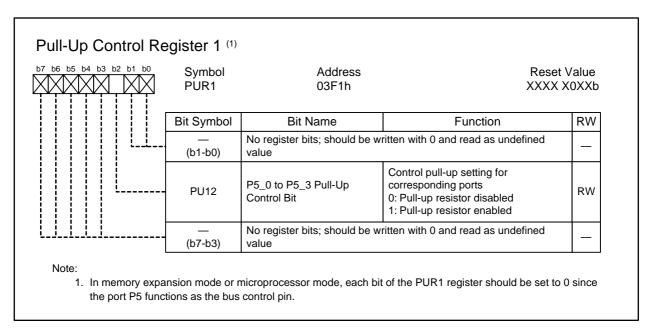

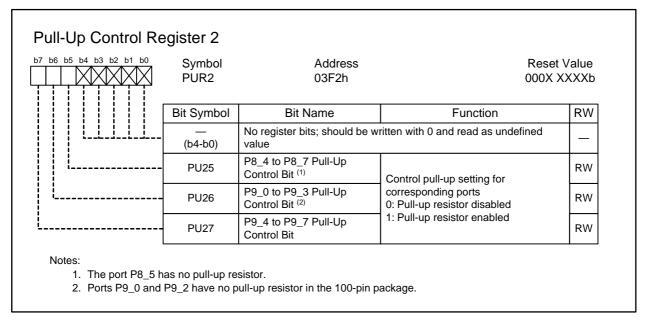

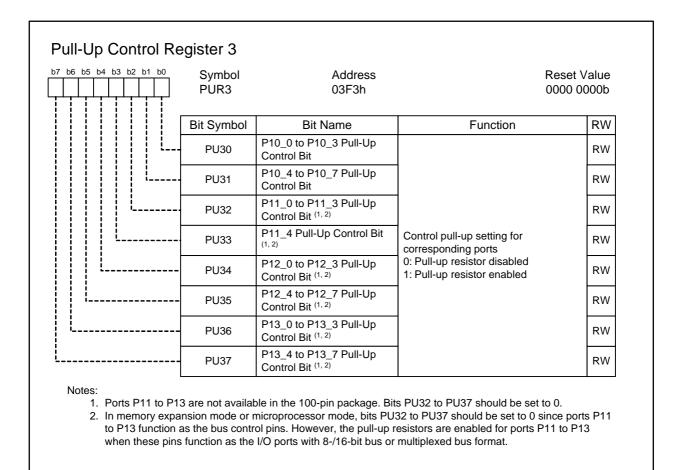

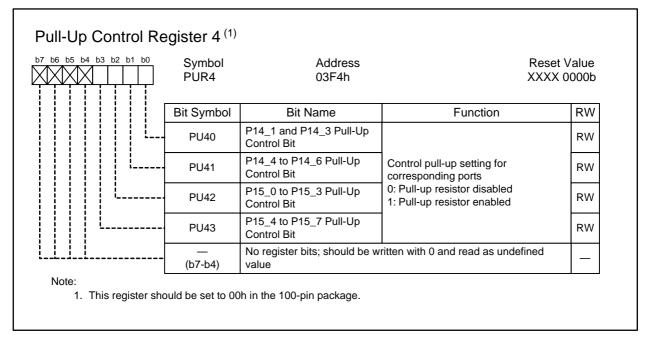

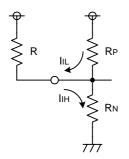

| 25.4     | Pull-up Control Registers 0 to 4 (Registers PUR0 to PUR4)                    | 417 |

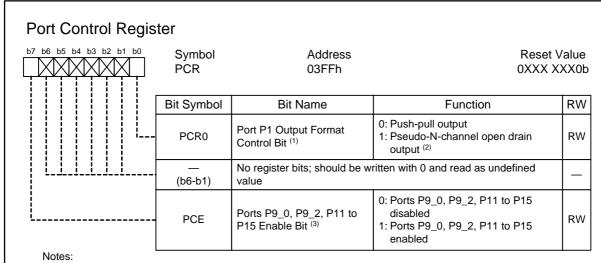

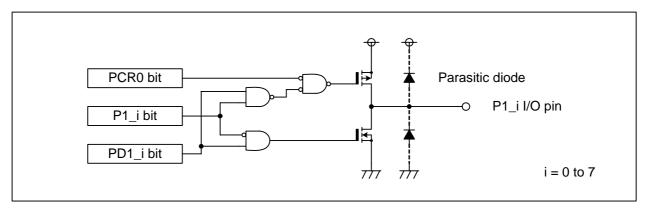

| 25.5     | Port Control Register (PCR Register)                                         | 420 |

| 25.6     | How To Configure Unused Pins                                                 | 421 |

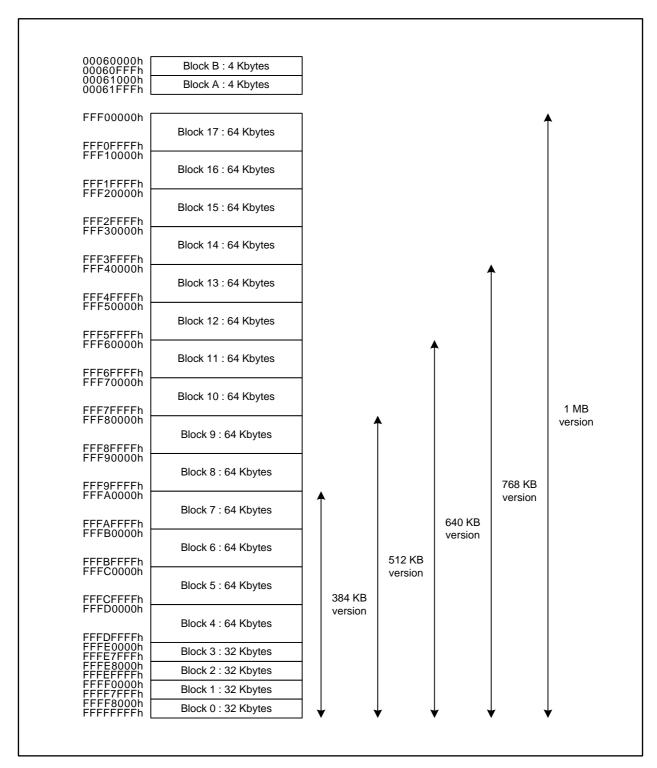

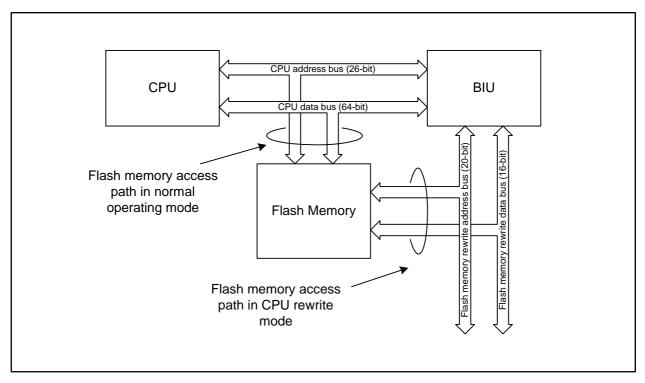

| 26. Flash Memory                                                             | 424      |

|------------------------------------------------------------------------------|----------|

| 26.1 Overview                                                                | 424      |

| 26.2 Flash Memory Protection                                                 | 426      |

| 26.2.1 Lock Bit Protection                                                   | 426      |

| 26.2.2 ROM Code Protection                                                   | 426      |

| 26.2.3 ID Code Protection                                                    | 427      |

| 26.2.4 Forcible Erase Function                                               | 428      |

| 26.2.5 Standard Serial I/O Mode Disable Function                             | 429      |

| 26.3 CPU Rewrite Mode                                                        | 430      |

| 26.3.1 CPU Operating Mode and Flash Memory Rewrite                           | 438      |

| 26.3.2 Flash Memory Rewrite Bus Timing                                       | 439      |

| 26.3.3 Software Commands                                                     | 443      |

| 26.3.4 Mode Transition                                                       | 444      |

| 26.3.5 How to Issue Software Commands                                        | 445      |

| 26.3.6 Status Check                                                          | 451      |

| 26.4 Standard Serial I/O Mode                                                | 452      |

| 26.5 Parallel I/O mode                                                       | 455      |

| 26.6 Notes on Flash Memory Rewriting                                         | 456      |

| 26.6.1 Note on Power Supply                                                  | 456      |

| 26.6.2 Note on Hardware Reset                                                | 456      |

| 26.6.3 Note on Flash Memory Protection                                       | 456      |

| 26.6.4 Notes on Programming                                                  | 456      |

| 26.6.5 Notes on Interrupts                                                   | 456      |

| 26.6.6 Notes on Rewrite Control Program                                      | 457      |

| 26.6.7 Notes on Number of Programming/Erasure and Software Command Execution | Time 457 |

| 26.6.8 Other Notes                                                           | 457      |

| 27. Electrical Characteristics                                               | 458      |

| 28. Usage Notes                                                              | 499      |

| 28.1 Notes on Board Designing                                                |          |

| 28.1.1 Power Supply Pins                                                     |          |

| 28.1.2 Supply Voltage                                                        |          |

| 28.2 Notes on Register Setting                                               |          |

| 28.2.1 Registers with Write-only Bits                                        |          |

| 28.3 Notes on Clock Generator                                                |          |

| 28.3.1 Sub Clock                                                             |          |

| 28.3.2 Power Control                                                         |          |

| 28.4 Notes on Bus                                                            |          |

| 28.4.1 Notes on System Designing                                             |          |

| 28.4.2 Notes on Register Settings                                            |          |

| 28.5 Notes on Interrupts                                                     |          |

| 20.0 110.00 On Interrupte                                                    |          |

| 28.5.1     | ISP Setting                                                                | 504 |

|------------|----------------------------------------------------------------------------|-----|

| 28.5.2     | NMI                                                                        | 504 |

| 28.5.3     | External Interrupt                                                         | 504 |

| 28.6 No    | tes on DMAC                                                                | 505 |

| 28.6.1     | DMAC-associated Register Settings                                          | 505 |

| 28.6.2     | Read from DMAC-associated Registers                                        | 505 |

| 28.7 No    | tes on Timers                                                              | 506 |

| 28.7.1     | Timer A and Timer B                                                        | 506 |

| 28.7.2     | Timer A                                                                    | 506 |

| 28.7.3     | Timer B                                                                    | 508 |

| 28.8 No    | tes on Three-phase Motor Control Timers                                    | 509 |

| 28.8.1     | Shutdown                                                                   | 509 |

| 28.8.2     | Register setting                                                           | 509 |

| 28.9 No    | tes on Serial Interface                                                    | 510 |

| 28.9.1     | Changing the UiBRG Register (i = 0 to 8)                                   | 510 |

| 28.9.2     | Synchronous Serial Interface Mode                                          | 510 |

| 28.9.3     | Special Mode 1 (I <sup>2</sup> C Mode)                                     | 510 |

| 28.9.4     | Reset Procedure on Communication Error                                     | 511 |

| 28.10 No   | tes on A/D Converter                                                       | 512 |

| 28.10.1    | Notes on Designing Boards                                                  | 512 |

| 28.10.2    | Notes on Programming                                                       | 513 |

| 28.11 No   | tes on Flash Memory Rewriting                                              | 514 |

| 28.11.1    | Note on Power Supply                                                       | 514 |

| 28.11.2    | Note on Hardware Reset                                                     | 514 |

| 28.11.3    | Note on Flash Memory Protection                                            | 514 |

| 28.11.4    | Notes on Programming                                                       | 514 |

| 28.11.5    | Notes on Interrupts                                                        | 514 |

| 28.11.6    | Notes on Rewrite Control Program                                           | 515 |

| 28.11.7    | Notes on Number of Programming/Erasure and Software Command Execution Time | 515 |

| 28.11.8    | Other Notes                                                                | 515 |

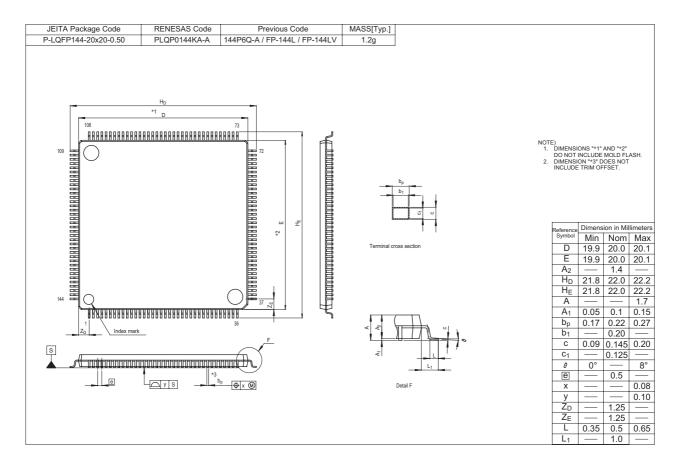

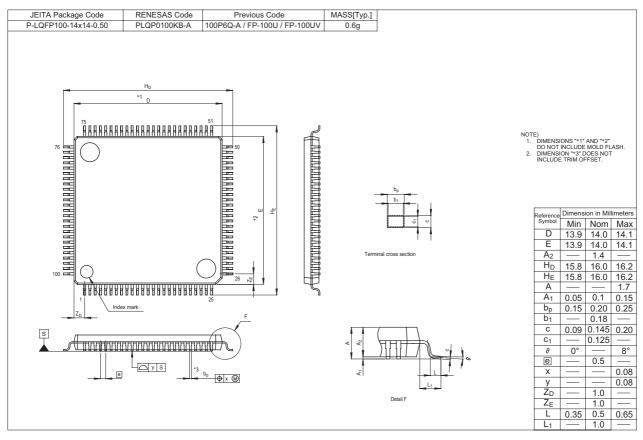

| Appendix 1 | . Package Dimensions                                                       | 516 |

| INDEX      |                                                                            | 517 |

R32C/116 Group RENESAS MCU

REJ09B0532-0110 Rev.1.10 Sep 08, 2010

### 1. Overview

#### 1.1 Features

The M16C Family offers a robust platform of 32-/16-bit CISC microcomputers (MCUs) featuring high ROM code efficiency, extensive EMI/EMS noise immunity, ultra-low power consumption, high-speed processing in actual applications, and numerous and varied integrated peripherals. Extensive device scalability from low- to high-end, featuring a single architecture as well as compatible pin assignments and peripheral functions, provides support for a vast range of application fields.

The R32C/100 Series is a high-end microcontroller series in the M16C Family. With a 4-Gbyte memory space, it achieves maximum code efficiency and high-speed processing with 32-bit CISC architecture, multiplier, multiply-accumulate unit, and floating point unit. The selection from the broadest choice of on-chip peripheral devices — UART, CRC, DMAC, A/D and D/A converters, timers, I<sup>2</sup>C, and watchdog timer enables to minimize external components.

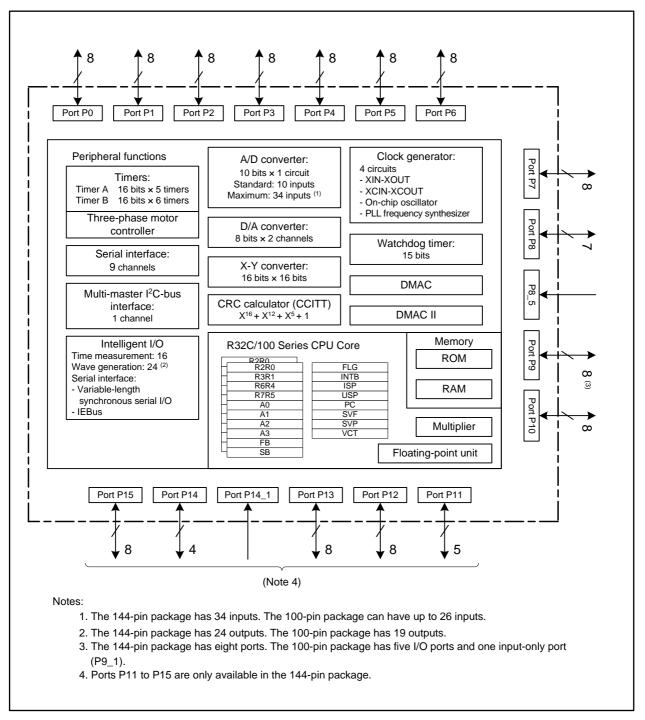

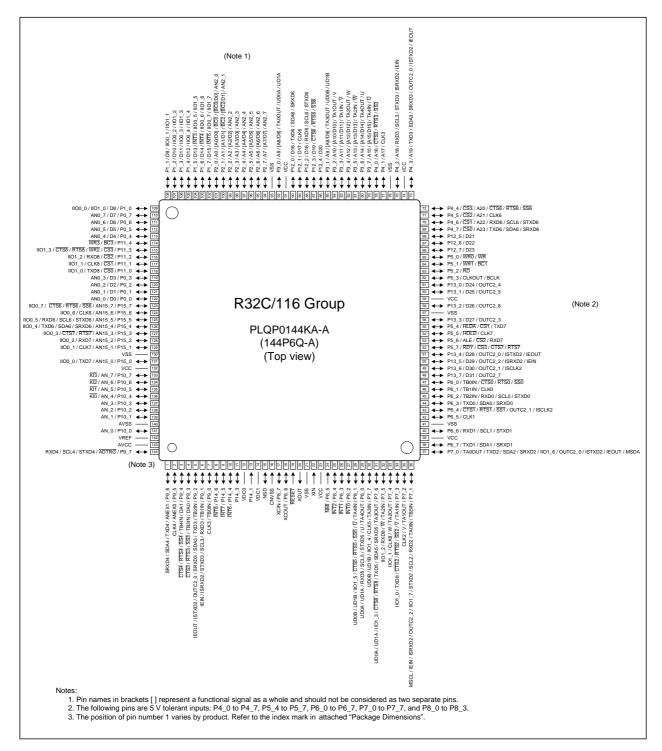

The R32C/116 Group is the standard MCU within the R32C/100 Series. This product, provided as 100-pin and 144-pin plastic molded LQFP packages, configures nine channels of serial interface and one channel of multi-master I<sup>2</sup>C-bus interface.

# 1.1.1 Applications

Car audio, audio, cameras, television, home appliance, printer, office/industrial equipment, communication/portable devices, etc.

# 1.1.2 Performance Overview

Table 1.1 to Table 1.4 list the performance overview of the R32C/116 Group.

Table 1.1 Performance Overview for the 144 pin-Package (1/2)

| Unit                      | Function                 | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU                       | Central processing unit  | R32C/100 Series CPU Core  • Basic instructions: 108  • Minimum instruction execution time: 15.625 ns (f(CPU) = 64 MHz)  • Multiplier: 32-bit × 32-bit → 64-bit  • Multiply-accumulate unit: 32-bit × 32-bit + 64-bit → 64-bit  • IEEE-754 floating point standard: Single precision  • 32-bit barrel shifter  • Operating mode: Single-chip mode, memory expansion mode, microprocessor mode (optional (1))  Flash memory: 384 Kbytes to 1 Mbyte |

|                           |                          | RAM: 40 K/48 K/63 Kbytes  Data flash: 4 Kbytes × 2 blocks  Refer to Table 1.5 for each product's memory size                                                                                                                                                                                                                                                                                                                                     |

| Voltage<br>Detector       | Low voltage detector     | Optional <sup>(1)</sup> Low voltage detection interrupt                                                                                                                                                                                                                                                                                                                                                                                          |

| Clock                     | Clock generator          | <ul> <li>4 circuits (main clock, sub clock, PLL, on-chip oscillator)</li> <li>Oscillation stop detector: Main clock oscillator stop/restart detection</li> <li>Frequency divide circuit: Divide-by-2 to divide-by-24 selectable</li> <li>Low power modes: Wait mode, stop mode</li> </ul>                                                                                                                                                        |

| External Bus<br>Expansion | Bus and memory expansion | <ul> <li>Address space: 4 Gbytes (of which up to 64 Mbytes is user accessible)</li> <li>External bus Interface: Support for wait-state insertion, 4 chip select outputs</li> <li>Bus format: Separate bus/Multiplexed bus selectable, data bus width selectable (8/16/32 bits)</li> </ul>                                                                                                                                                        |

| Interrupts                |                          | Interrupt vectors: 261 External interrupt inputs: NMI, NT × 9, key input × 4 Interrupt priority levels: 7                                                                                                                                                                                                                                                                                                                                        |

| Watchdog Tim              | er                       | 15 bits × 1 (selectable input frequency from prescaler output)                                                                                                                                                                                                                                                                                                                                                                                   |

| DMA                       | DMAC                     | <ul> <li>4 channels</li> <li>Cycle-steal transfer mode</li> <li>Request sources: 57</li> <li>2 transfer modes: Single transfer, repeat transfer</li> </ul>                                                                                                                                                                                                                                                                                       |

|                           | DMAC II                  | Can be activated by any peripheral interrupt source     3 transfer functions: Immediate data transfer, calculation transfer, chained transfer                                                                                                                                                                                                                                                                                                    |

| I/O Ports                 | Programmable I/O ports   | <ul> <li>2 input-only ports</li> <li>120 CMOS I/O ports (of which 32 are 5 V tolerant)</li> <li>A pull-up resistor is selectable for every 4 input ports (except 5 V tolerant inputs)</li> </ul>                                                                                                                                                                                                                                                 |

#### Note:

Table 1.2 Performance Overview for the 144-pin Package (2/2)

| Unit                          | Function                        | Explanation                                                                                                                                                                                                          |  |  |  |

|-------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Timer                         | Timer A                         | 16-bit timer x 5 Timer mode, event counter mode, one-shot timer mode, pulse-width modulation (PWM) mode Two-phase pulse signal processing in event counter mode (two-phase encoder input) x 3                        |  |  |  |

|                               | Timer B                         | 16-bit timer × 6 Timer mode, event counter mode, pulse frequency measurement mode, pulse-width measurement mode                                                                                                      |  |  |  |

|                               | Three-phase motor control timer | Three-phase motor control timer x 1 (timers A1, A2, A4, and B2 used) 8-bit programmable dead time timer                                                                                                              |  |  |  |

| Serial<br>Interface           | UART0 to UART8                  | Asynchronous/synchronous serial interface × 9 channels  • I <sup>2</sup> C-bus (UART0 to UART6)  • Special mode 2 (UART0 to UART6)  • IEBus (optional <sup>(1)</sup> ) (UART0 to UART6)                              |  |  |  |

| A/D Converter                 |                                 | 10-bit resolution × 34 channels Sample and hold functionality integrated                                                                                                                                             |  |  |  |

| D/A Converter                 |                                 | 8-bit resolution x 2                                                                                                                                                                                                 |  |  |  |

| CRC Calculator                | •                               | CRC-CCITT (X <sup>16</sup> + X <sup>12</sup> + X <sup>5</sup> + 1)                                                                                                                                                   |  |  |  |

| X-Y Converter                 |                                 | 16 bits × 16 bits                                                                                                                                                                                                    |  |  |  |

| Intelligent I/O               |                                 | Time measurement (input capture): 16 bits × 16 Waveform generation (output compare): 16 bits × 24 Serial interface: Variable-length synchronous serial I/O mode, IEBus mode (optional (1))                           |  |  |  |

| Multi-master I <sup>2</sup> C | C-bus Interface                 | 1 channel                                                                                                                                                                                                            |  |  |  |

| Flash Memory                  |                                 | Programming and erasure supply voltage: VCC = 3.0 to 5.5 V Minimum endurance: 1,000 program/erase cycles Security protection: ROM code protect, ID code protect Debugging: On-chip debug, on-board flash programming |  |  |  |

| Operating Frequency Voltage   | uency/Supply                    | 64 MHz (high speed version)/VCC = 3.0 to 5.5 V<br>50 MHz (normal speed version)/VCC = 3.0 to 5.5 V                                                                                                                   |  |  |  |

| Operating Temp                | oerature                        | -20°C to 85°C (N version)<br>-40°C to 85°C (D version)<br>-40°C to 85°C (P version)                                                                                                                                  |  |  |  |

| Current Consur                | nption                          | 45 mA (VCC = 5.0 V, f(CPU) = 64 MHz)<br>35 mA (VCC = 5.0 V, f(CPU) = 50 MHz)<br>8 μA (VCC = 3.3 V, f(XCIN) = 32.768 kHz, in wait mode)                                                                               |  |  |  |

| Package                       |                                 | 144-pin plastic molded LQFP (PLQP0144KA-A)                                                                                                                                                                           |  |  |  |

#### Note:

Table 1.3 Performance Overview for the 100-pin Package (1/2)

| Unit                      | Function                 | Explanation                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU                       | Central processing unit  | R32C/100 Series CPU Core  • Basic instructions: 108  • Minimum instruction execution time: 15.625 ns (f(CPU) = 64 MHz)  • Multiplier: 32-bit × 32-bit → 64-bit  • Multiply-accumulate unit: 32-bit × 32-bit + 64-bit → 64-bit  • IEEE-754 floating point standard: Single precision  • 32-bit barrel shifter  • Operating mode: Single-chip mode, memory expansion mode, microprocessor mode (optional (1)) |

| Memory                    |                          | Flash memory: 384 Kbytes to 1 Mbyte RAM: 40 K/48 K/63 Kbytes Data flash: 4 Kbytes × 2 blocks Refer to Table 1.5 for each product's memory size                                                                                                                                                                                                                                                              |

| Voltage<br>Detector       | Low voltage detector     | Optional <sup>(1)</sup> Low voltage detection interrupt                                                                                                                                                                                                                                                                                                                                                     |

| Clock                     | Clock generator          | <ul> <li>4 circuits (main clock, sub clock, PLL, on-chip oscillator)</li> <li>Oscillation stop detector: Main clock oscillator stop/restart detection</li> <li>Frequency divide circuit: Divide-by-2 to divide-by-24 selectable</li> <li>Low power modes: Wait mode, stop mode</li> </ul>                                                                                                                   |

| External Bus<br>Expansion | Bus and memory expansion | <ul> <li>Address space: 4 Gbytes (of which up to 64 Mbytes is user accessible)</li> <li>External bus Interface: Support for wait-state insertion, 4 chip select outputs</li> <li>Bus format: Separate bus/Multiplexed bus selectable, data bus width selectable (8/16 bits)</li> </ul>                                                                                                                      |

| Interrupts                |                          | Interrupt vectors: 261 External interrupt inputs: NMI, NT × 6, key input × 4 Interrupt priority levels: 7                                                                                                                                                                                                                                                                                                   |

| Watchdog Tim              | er                       | 15 bits × 1 (selectable input frequency from prescaler output)                                                                                                                                                                                                                                                                                                                                              |

| DMA                       | DMAC                     | 4 channels  • Cycle-steal transfer mode  • Request sources: 51  • 2 transfer modes: Single transfer, repeat transfer                                                                                                                                                                                                                                                                                        |

|                           | DMAC II                  | <ul> <li>Can be activated by any peripheral interrupt source</li> <li>3 transfer functions: Immediate data transfer, calculation transfer, chained transfer</li> </ul>                                                                                                                                                                                                                                      |

| I/O Ports                 | Programmable I/O ports   | <ul> <li>2 input-only ports</li> <li>84 CMOS I/O ports (of which 32 are 5 V tolerant)</li> <li>A pull-up resistor is selectable for every 4 input ports (except 5 V tolerant inputs)</li> </ul>                                                                                                                                                                                                             |

## Note:

Table 1.4 Performance Overview for the 100-pin Package (2/2)

| Unit                        | Function                        | Explanation                                                                                                                                                                                                          |  |  |  |

|-----------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Timer                       | Timer A                         | 16-bit timer x 5 Timer mode, event counter mode, one-shot timer mode, pulse-width modulation (PWM) mode Two-phase pulse signal processing in event counter mode (two-phase encoder input) x 3                        |  |  |  |

|                             | Timer B                         | 16-bit timer × 6 Timer mode, event counter mode, pulse frequency measurement mode, pulse-width measurement mode                                                                                                      |  |  |  |

|                             | Three-phase motor control timer | Three-phase motor control timer x 1 (timers A1, A2, A4, and B2 used) 8-bit programmable dead time timer                                                                                                              |  |  |  |

| Serial<br>Interface         | UART0 to UART8                  | Asynchronous/synchronous serial interface × 9 channels • I <sup>2</sup> C-bus (UART0 to UART6) • Special mode 2 (UART0 to UART6) • IEBus (optional <sup>(1)</sup> ) (UART0 to UART6)                                 |  |  |  |

| A/D Converter               |                                 | 10-bit resolution × 26 channels Sample and hold functionality integrated                                                                                                                                             |  |  |  |

| D/A Converter               |                                 | 8-bit resolution × 2                                                                                                                                                                                                 |  |  |  |

| CRC Calculato               | r                               | CRC-CCITT (X <sup>16</sup> + X <sup>12</sup> + X <sup>5</sup> + 1)                                                                                                                                                   |  |  |  |

| X-Y Converter               |                                 | 16 bits × 16 bits                                                                                                                                                                                                    |  |  |  |

| Intelligent I/O             |                                 | Time measurement (input capture): 16 bits × 16 Waveform generation (output compare): 16 bits × 19 Serial interface: Variable-length synchronous serial I/O mode, IEBus mode (optional <sup>(1)</sup> )               |  |  |  |

| Multi-master I <sup>2</sup> | C-bus Interface                 | 1 channel                                                                                                                                                                                                            |  |  |  |

| Flash Memory                |                                 | Programming and erasure supply voltage: VCC = 3.0 to 5.5 V Minimum endurance: 1,000 program/erase cycles Security protection: ROM code protect, ID code protect Debugging: On-chip debug, on-board flash programming |  |  |  |

| Operating Freq<br>Voltage   | uency/Supply                    | 64 MHz (high speed version)/VCC = 3.0 to 5.5 V<br>50 MHz (normal speed version)/VCC = 3.0 to 5.5 V                                                                                                                   |  |  |  |

| Operating Tem               | perature                        | -20°C to 85°C (N version) -40°C to 85°C (D version) -40°C to 85°C (P version)                                                                                                                                        |  |  |  |

| Current Consu               | mption                          | 45 mA (VCC = 5.0 V, f(CPU) = 64 MHz)<br>35 mA (VCC = 5.0 V, f(CPU) = 50 MHz)<br>8 μA (VCC = 3.3 V, f(XCIN) = 32.768 kHz, in wait mode)                                                                               |  |  |  |

| Package                     |                                 | 100-pin plastic molded LQFP (PLQP0100KB-A)                                                                                                                                                                           |  |  |  |

#### Note:

# 1.2 Product Information

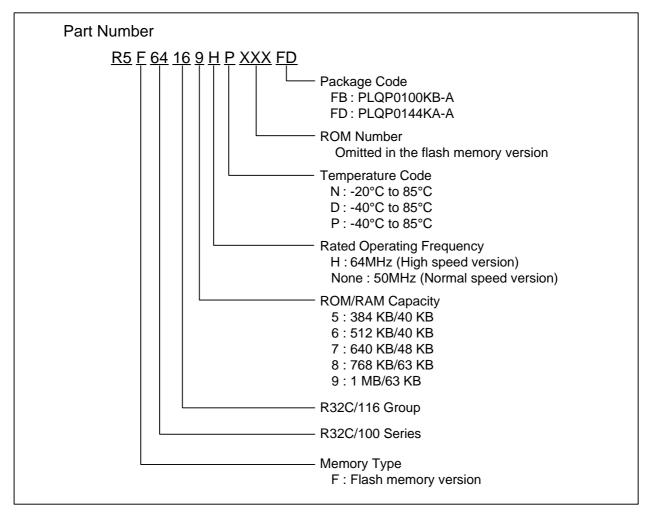

Table 1.5 and Table 1.6 list the product information and Figure 1.1 shows the details of the part number.

Table 1.5 R32C/116 Group Product List for Normal Speed Version (1/2) As of September, 2010

| Part Number |     | Package Code (1) | ROM Capacity (2) | RAM Capacity | Remarks                   |                           |

|-------------|-----|------------------|------------------|--------------|---------------------------|---------------------------|

| R5F64165NFD | (P) |                  |                  |              | -20°C to 85°C (N version) |                           |

| R5F64165DFD |     | PLQP0144KA-A     |                  |              | -40°C to 85°C (D version) |                           |

| R5F64165PFD |     |                  | 384 Kbytes       |              | -40°C to 85°C (P version) |                           |

| R5F64165NFB | (P) |                  | + 8 Kbytes       |              | -20°C to 85°C (N version) |                           |

| R5F64165DFB |     | PLQP0100KB-A     |                  |              | -40°C to 85°C (D version) |                           |

| R5F64165PFB |     |                  |                  | 40 Kbytes    | -40°C to 85°C (P version) |                           |

| R5F64166NFD | (P) |                  |                  | 40 Kbytes    | -20°C to 85°C (N version) |                           |

| R5F64166DFD |     | PLQP0144KA-A     |                  |              | -40°C to 85°C (D version) |                           |

| R5F64166PFD |     |                  | 512 Kbytes       |              | -40°C to 85°C (P version) |                           |

| R5F64166NFB | (P) |                  | + 8 Kbytes       |              | -20°C to 85°C (N version) |                           |

| R5F64166DFB |     | PLQP0100KB-A     |                  |              | -40°C to 85°C (D version) |                           |

| R5F64166PFB |     |                  |                  |              | -40°C to 85°C (P version) |                           |

| R5F64167NFD | (P) |                  |                  |              | -20°C to 85°C (N version) |                           |

| R5F64167DFD |     | PLQP0144KA-A     | 640 Kbytes       |              | -40°C to 85°C (D version) |                           |

| R5F64167PFD |     |                  |                  | 48 Kbytes    | -40°C to 85°C (P version) |                           |

| R5F64167NFB | (P) |                  | + 8 Kbytes       | 40 Noytes    | -20°C to 85°C (N version) |                           |

| R5F64167DFB |     |                  | PLQP0100KB-A     |              |                           | -40°C to 85°C (D version) |

| R5F64167PFB |     |                  |                  |              | -40°C to 85°C (P version) |                           |

| R5F64168NFD | (P) |                  |                  |              | -20°C to 85°C (N version) |                           |

| R5F64168DFD |     | PLQP0144KA-A     |                  |              | -40°C to 85°C (D version) |                           |

| R5F64168PFD |     |                  | 768 Kbytes       |              | -40°C to 85°C (P version) |                           |

| R5F64168NFB | (P) |                  | + 8 Kbytes       |              | -20°C to 85°C (N version) |                           |

| R5F64168DFB |     | PLQP0100KB-A     |                  |              | -40°C to 85°C (D version) |                           |

| R5F64168PFB |     |                  |                  | 63 Kbytes    | -40°C to 85°C (P version) |                           |

| R5F64169NFD | (P) |                  |                  | 05 Noytes    | -20°C to 85°C (N version) |                           |

| R5F64169DFD |     | PLQP0144KA-A     |                  |              | -40°C to 85°C (D version) |                           |

| R5F64169PFD |     |                  | 1 Mbyte          |              | -40°C to 85°C (P version) |                           |

| R5F64169NFB | (P) |                  | + 8 Kbytes       |              | -20°C to 85°C (N version) |                           |

| R5F64169DFB |     | PLQP0100KB-A     |                  |              | -40°C to 85°C (D version) |                           |

| R5F64169PFB |     |                  |                  |              | -40°C to 85°C (P version) |                           |

(D): Under development (P): On planning phase

# Notes:

- 1. The old package codes are as follows:PLQP0100KB-A: 100P6Q-A; PLQP0144KA-A: 144P6Q-A

- 2. Data flash memory provides an additional 8 Kbytes of ROM.

Table 1.6 R32C/116 Group Product List for High Speed Version (2/2) As of September, 2010

| Dort Number  | Ī   | Poskaga Coda (1) | DOM Consoity (2) | PAM Capacity | Pomorko                   |

|--------------|-----|------------------|------------------|--------------|---------------------------|

| Part Number  | (D) | Package Code (1) | ROM Capacity (2) | RAM Capacity | Remarks                   |

| R5F64165HNFD | (P) |                  |                  |              | -20°C to 85°C (N version) |

| R5F64165HDFD |     | PLQP0144KA-A     |                  |              | -40°C to 85°C (D version) |

| R5F64165HPFD | (D) |                  | 384 Kbytes       |              | -40°C to 85°C (P version) |

| R5F64165HNFB | (P) |                  | + 8 Kbytes       |              | -20°C to 85°C (N version) |

| R5F64165HDFB |     | PLQP0100KB-A     |                  |              | -40°C to 85°C (D version) |

| R5F64165HPFB | (D) |                  |                  | 40 Kbytes    | -40°C to 85°C (P version) |

| R5F64166HNFD | (P) |                  |                  | 10 Noytoo    | -20°C to 85°C (N version) |

| R5F64166HDFD |     | PLQP0144KA-A     |                  |              | -40°C to 85°C (D version) |

| R5F64166HPFD | (D) |                  | 512 Kbytes       |              | -40°C to 85°C (P version) |

| R5F64166HNFB | (P) |                  | + 8 Kbytes       |              | -20°C to 85°C (N version) |

| R5F64166HDFB |     | PLQP0100KB-A     |                  |              | -40°C to 85°C (D version) |

| R5F64166HPFB | (D) |                  |                  |              | -40°C to 85°C (P version) |

| R5F64167HNFD | (P) |                  |                  |              | -20°C to 85°C (N version) |

| R5F64167HDFD |     | PLQP0144KA-A     | 640 Kbytes       |              | -40°C to 85°C (D version) |

| R5F64167HPFD | (D) | )                |                  | 40 Khyton    | -40°C to 85°C (P version) |

| R5F64167HNFB | (P) |                  | + 8 Kbytes       | 48 Kbytes    | -20°C to 85°C (N version) |

| R5F64167HDFB |     | PLQP0100KB-A     |                  |              | -40°C to 85°C (D version) |

| R5F64167HPFB | (D) |                  |                  |              | -40°C to 85°C (P version) |

| R5F64168HNFD | (P) |                  |                  |              | -20°C to 85°C (N version) |

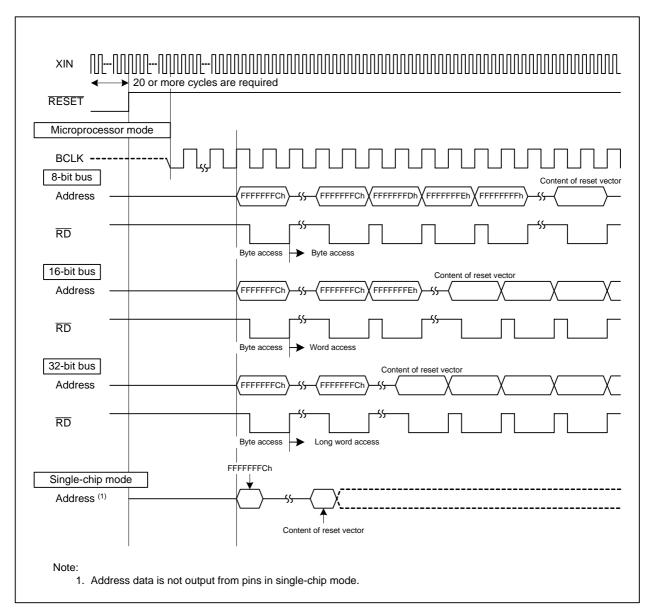

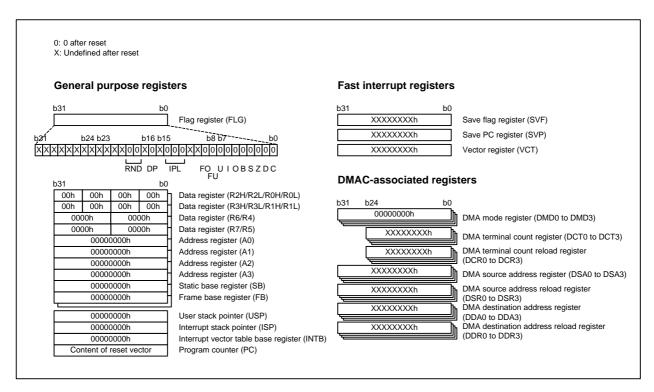

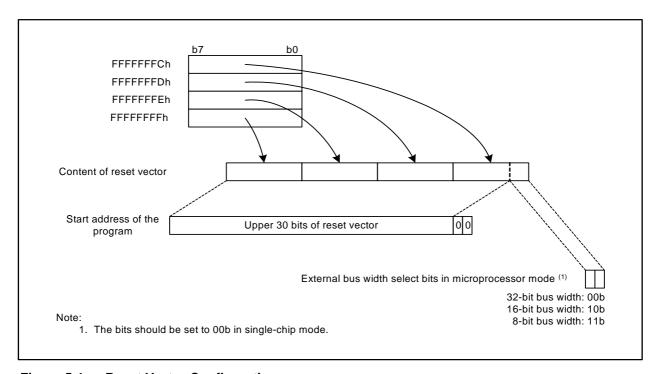

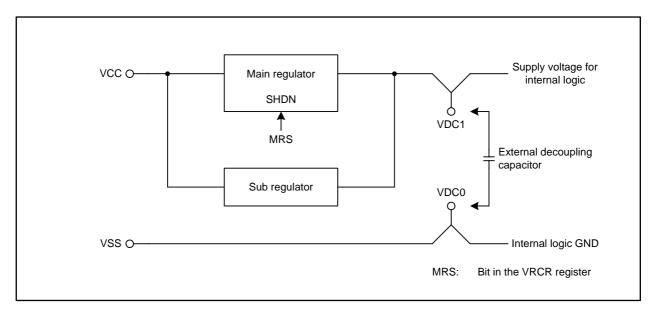

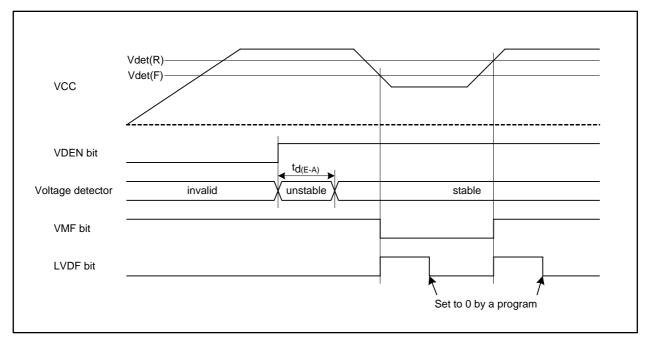

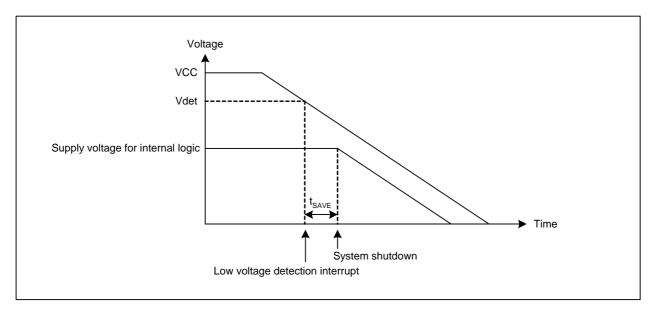

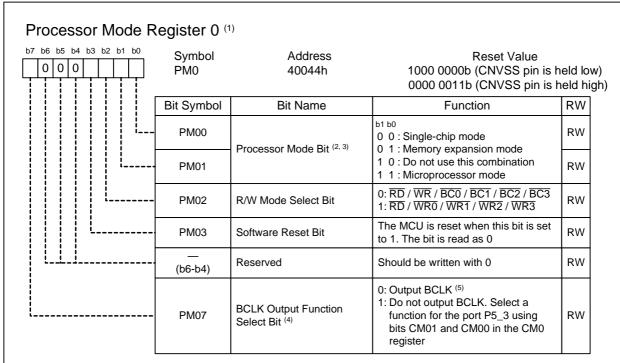

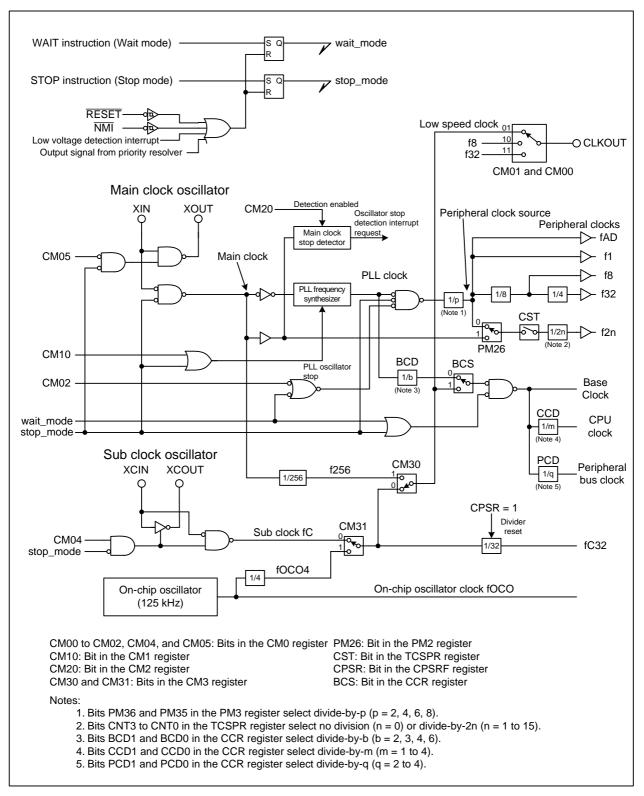

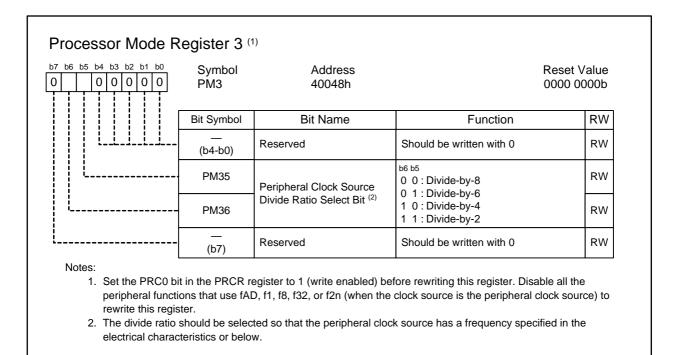

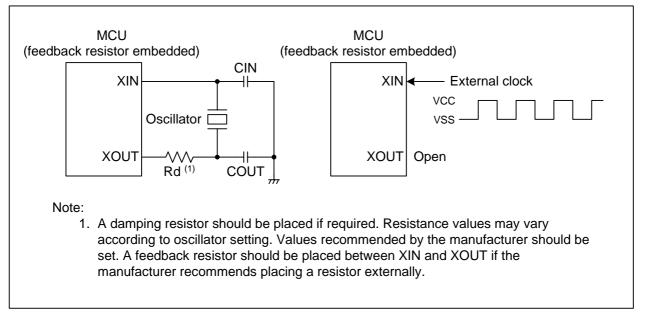

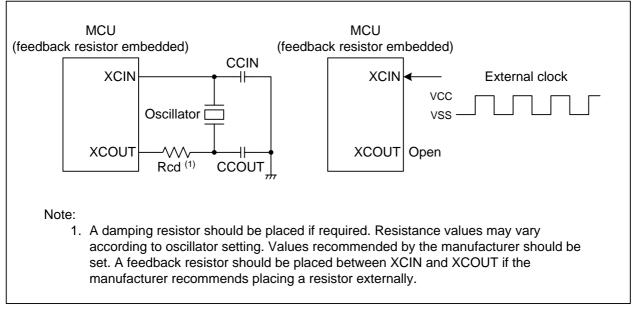

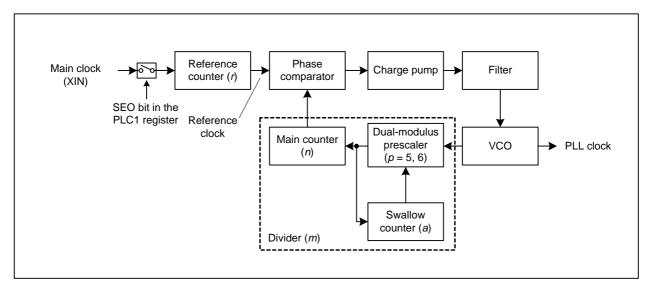

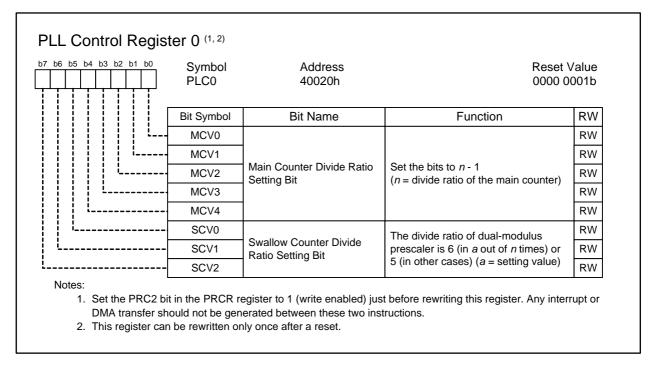

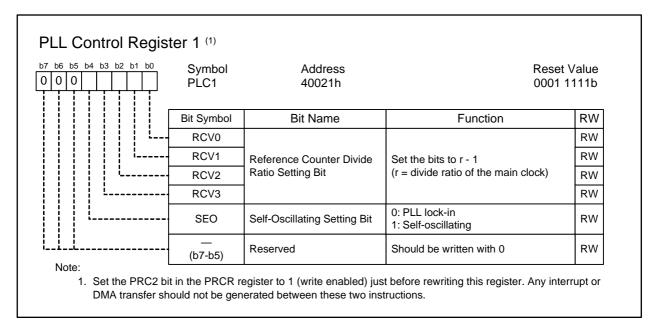

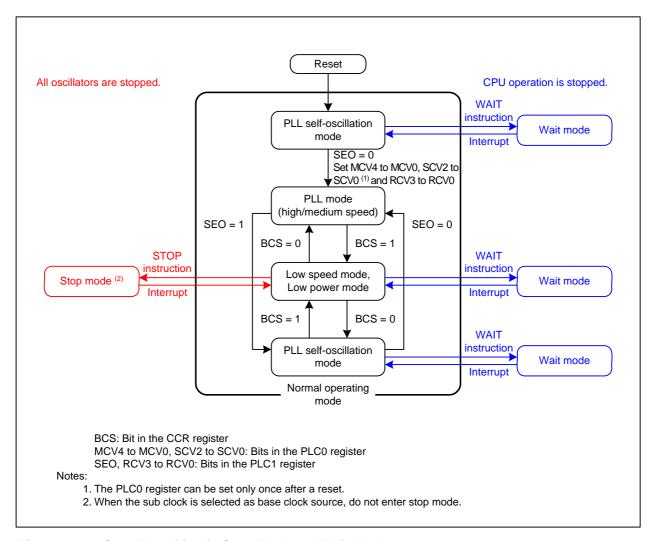

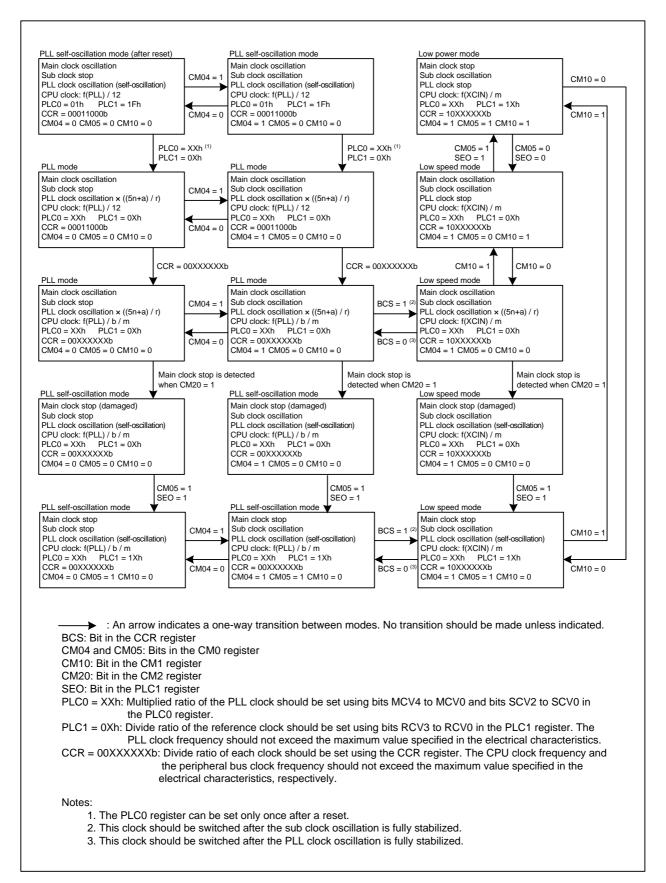

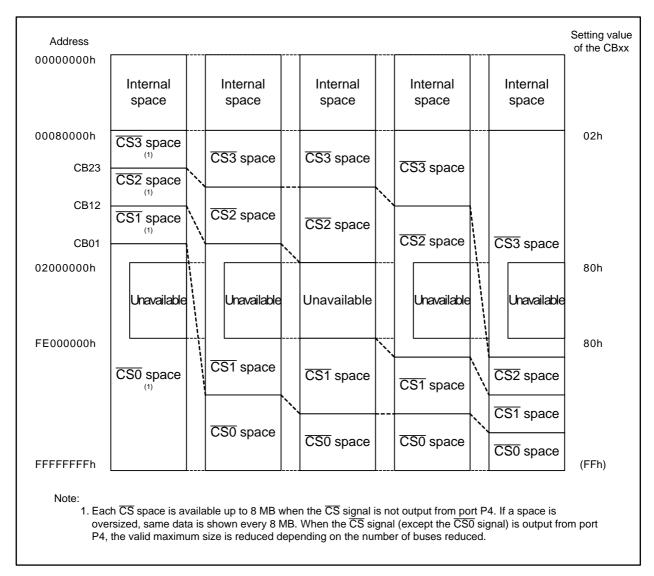

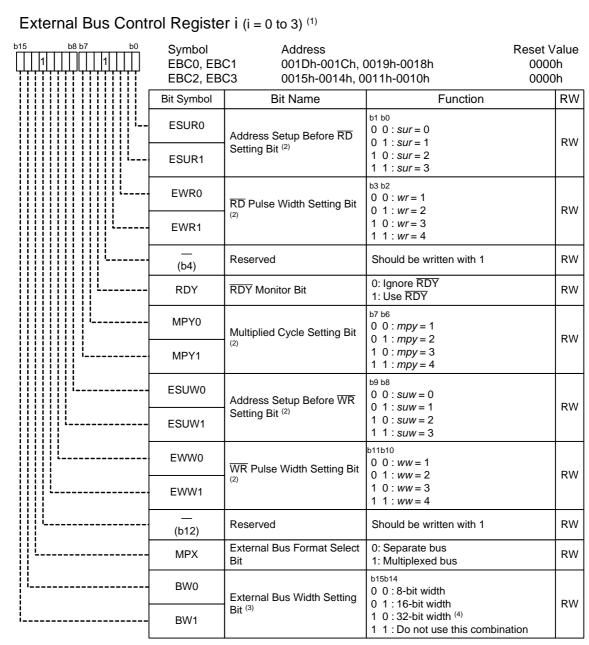

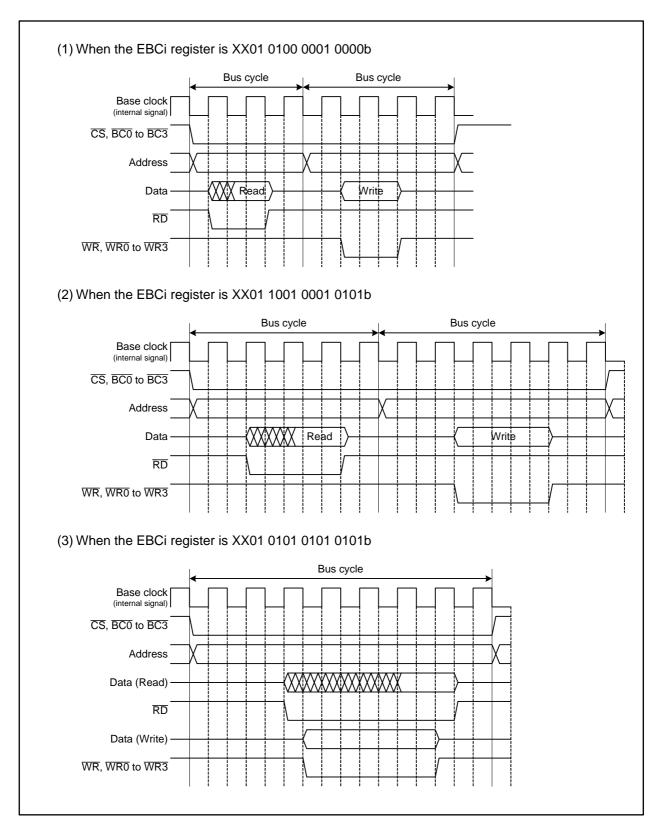

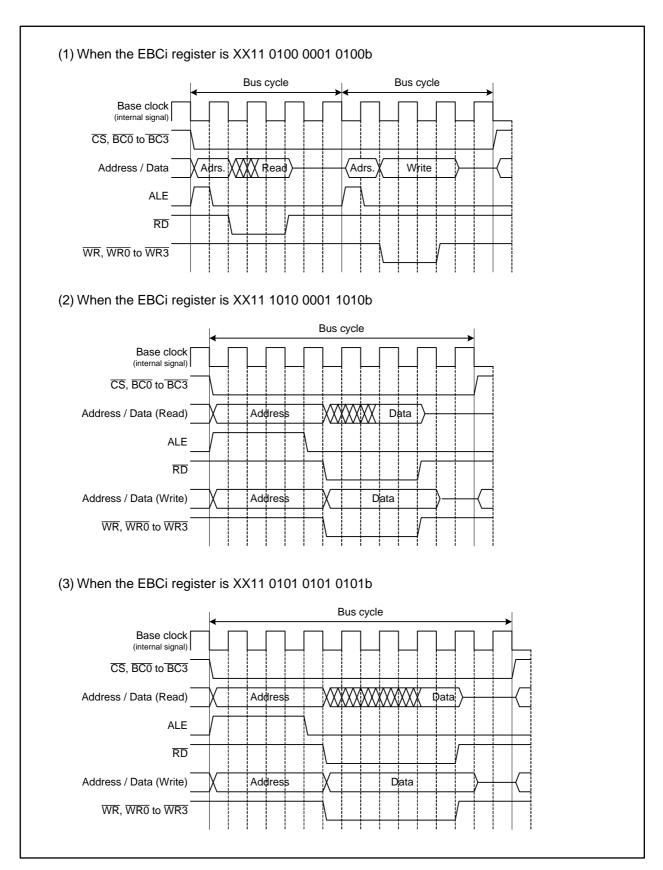

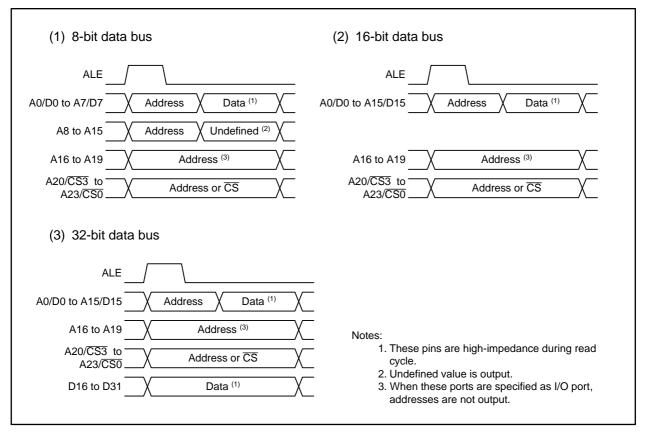

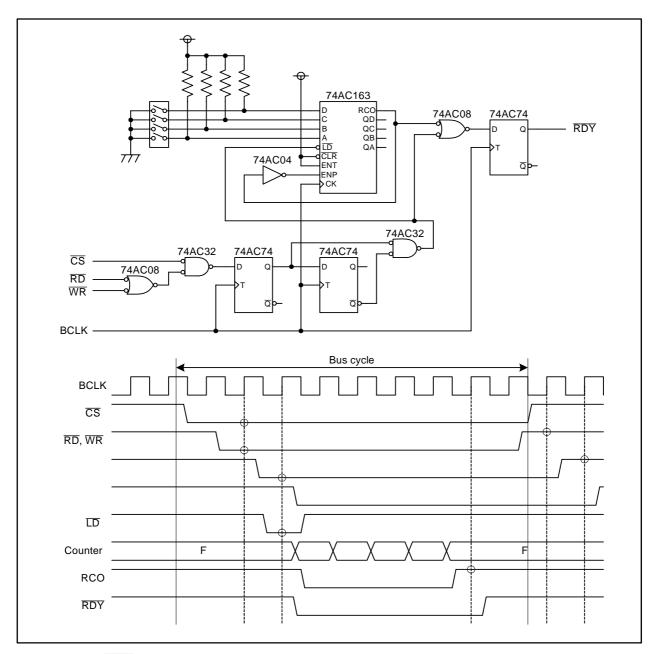

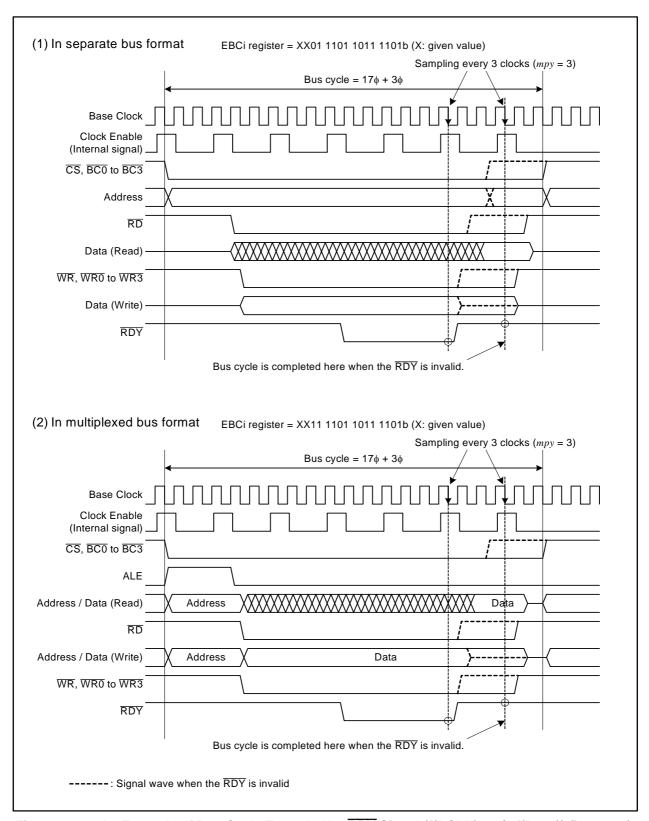

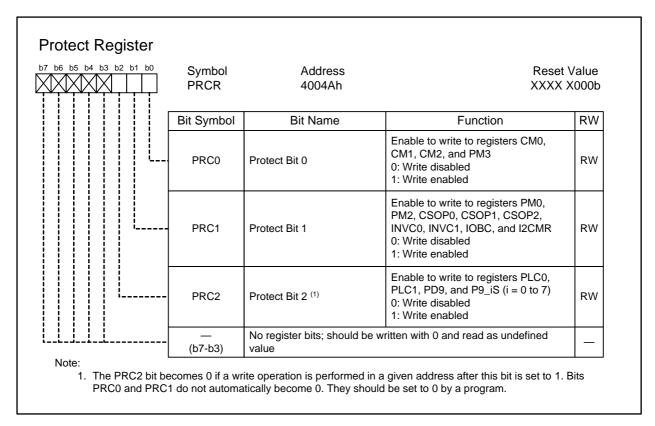

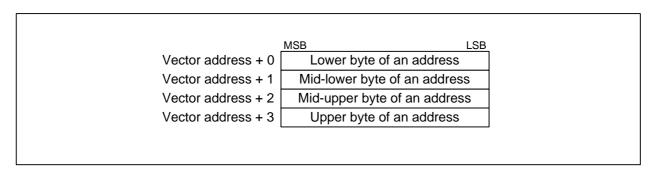

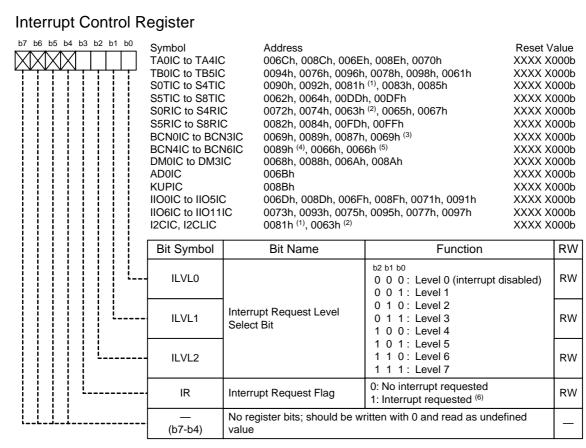

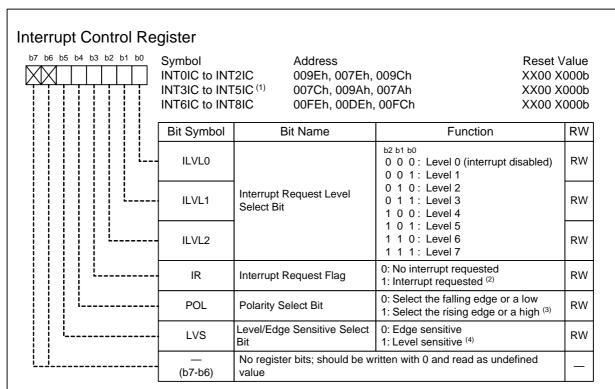

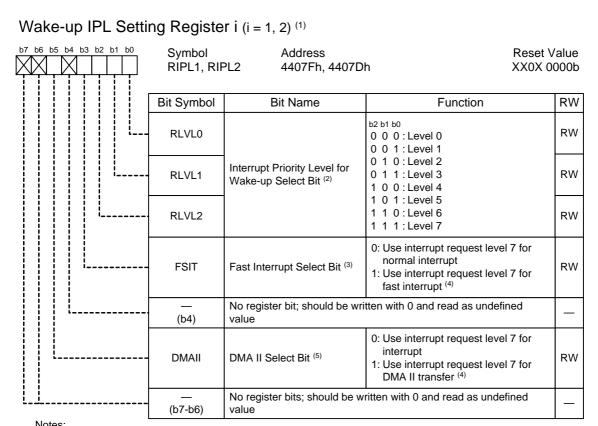

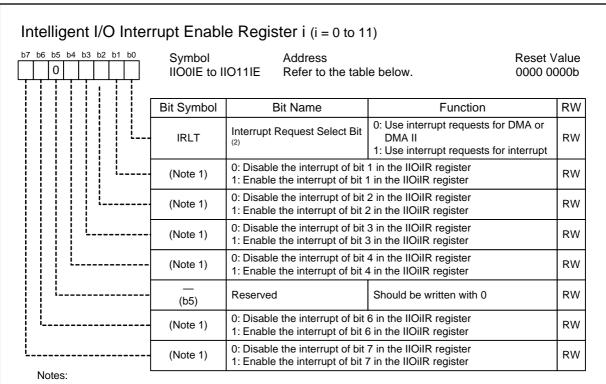

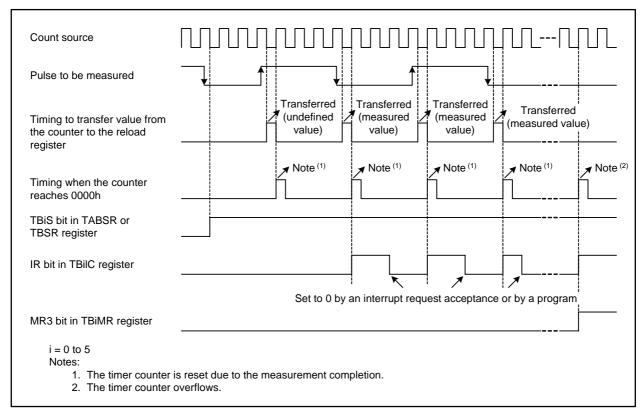

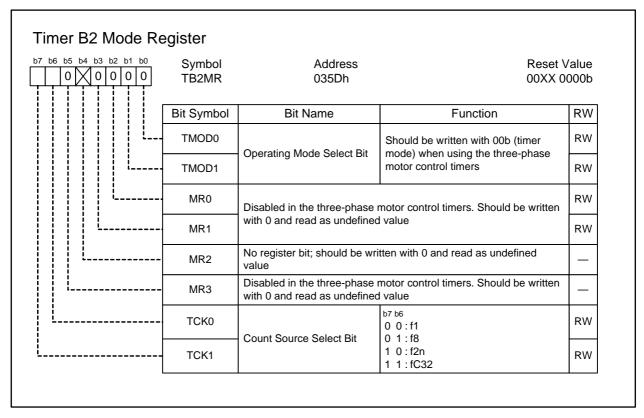

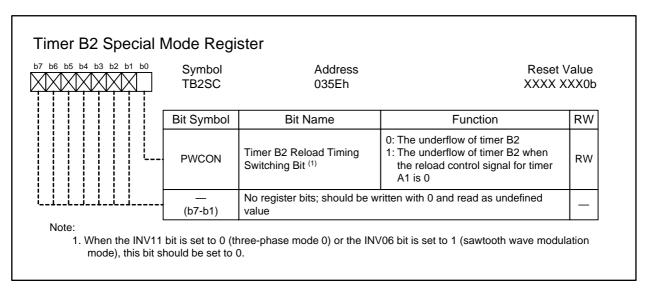

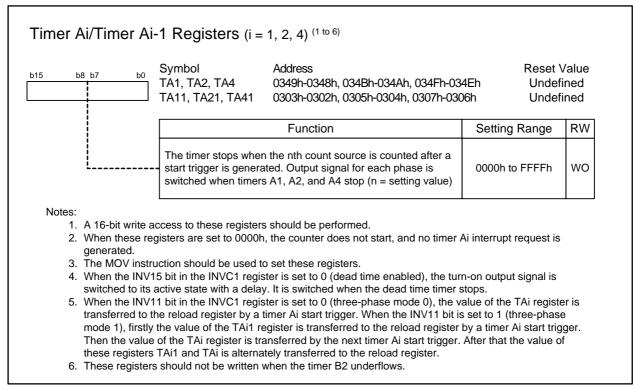

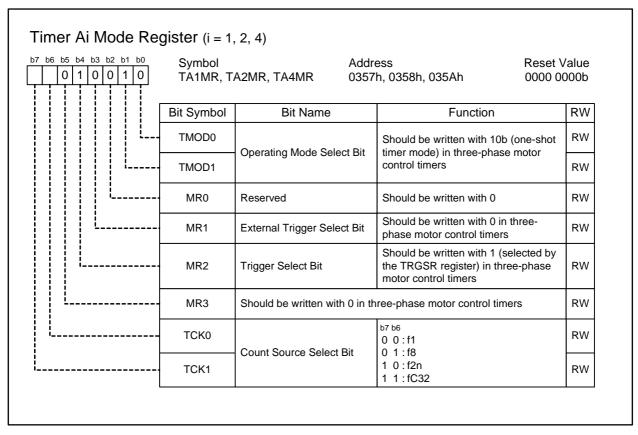

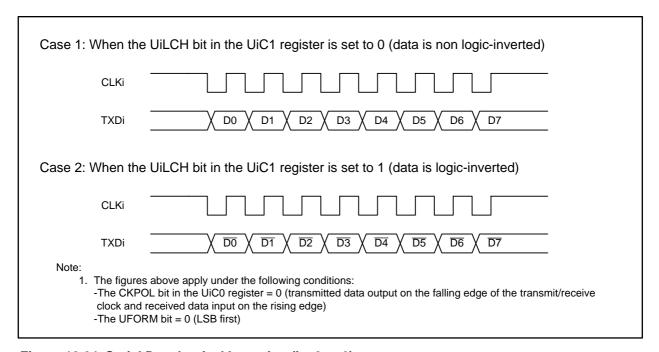

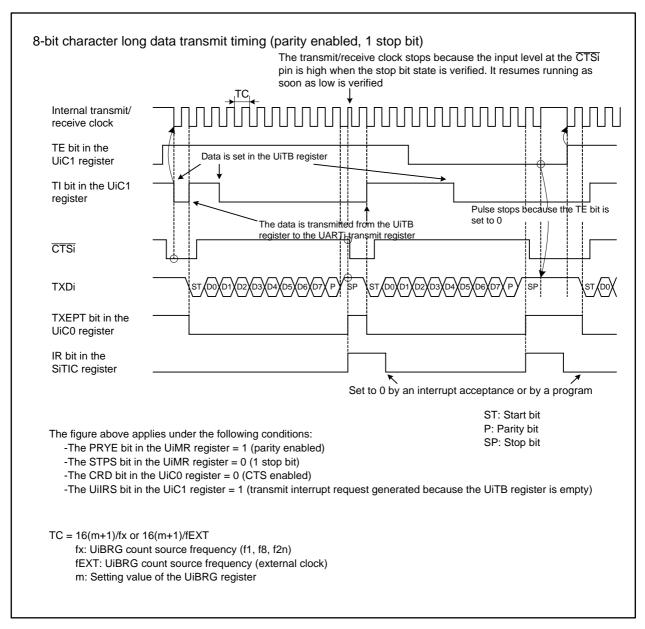

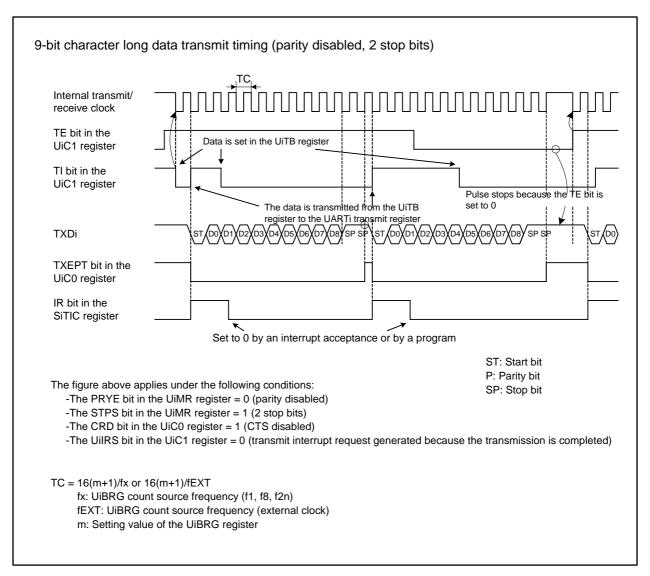

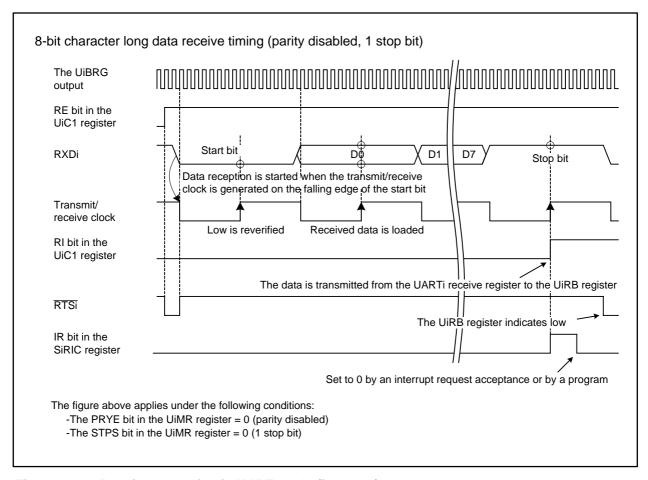

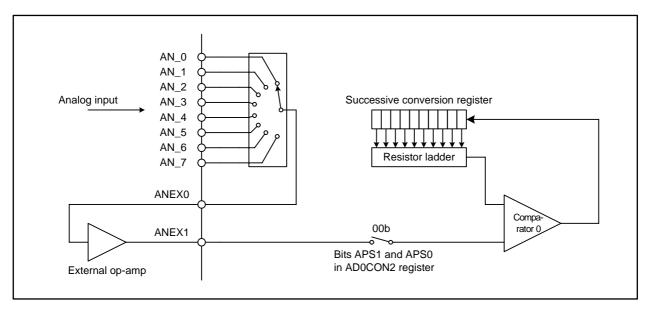

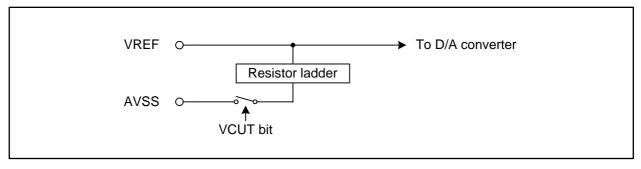

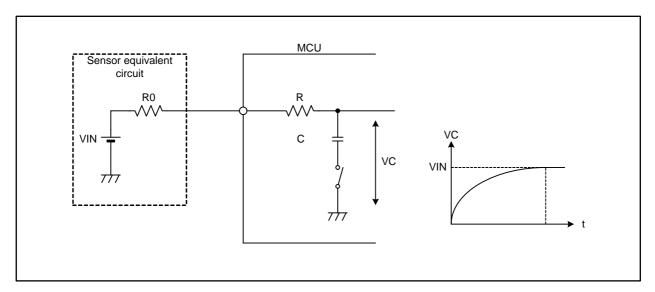

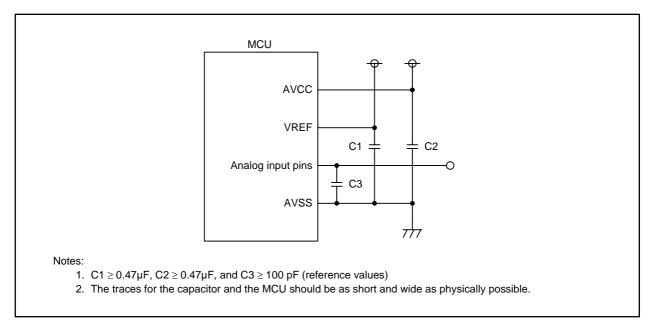

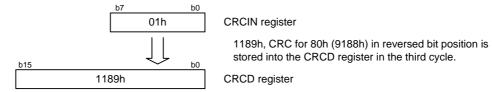

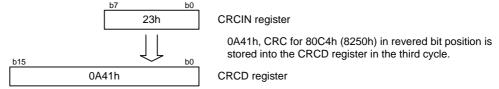

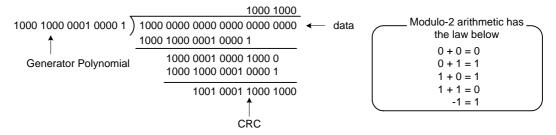

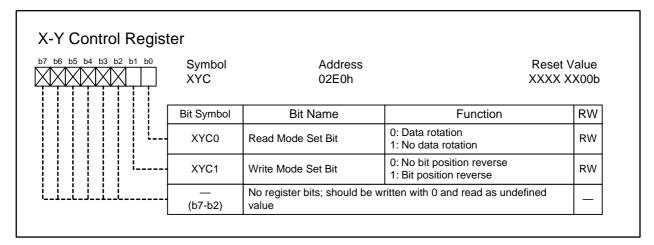

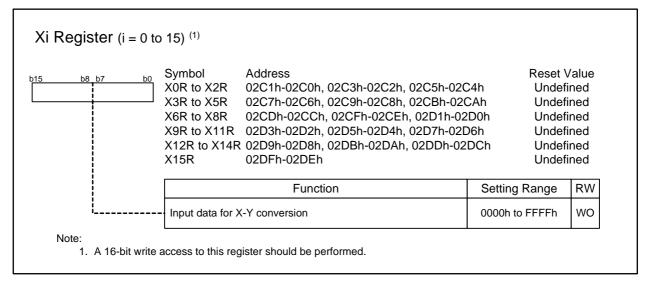

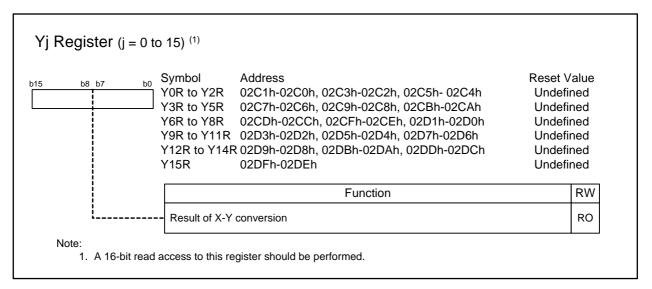

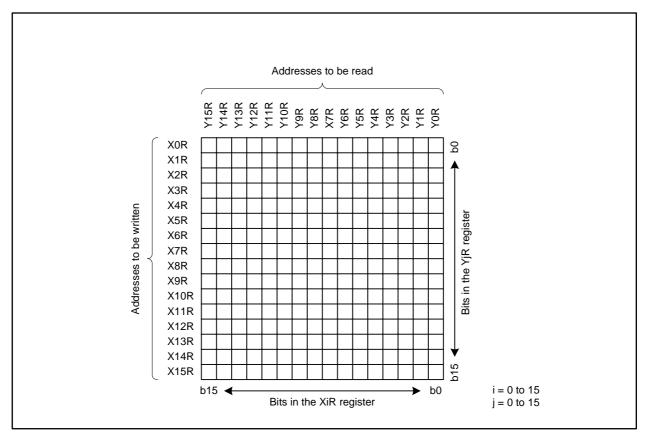

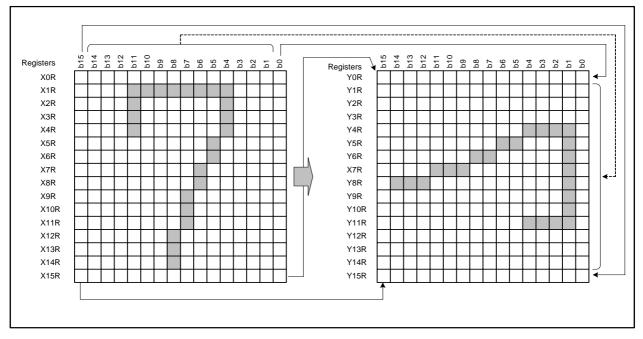

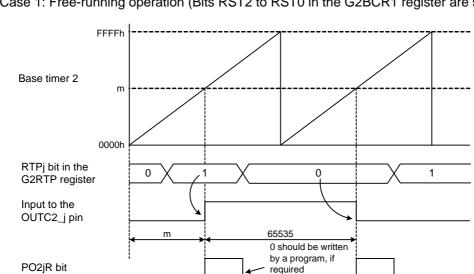

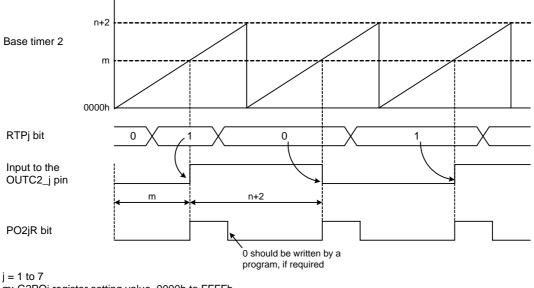

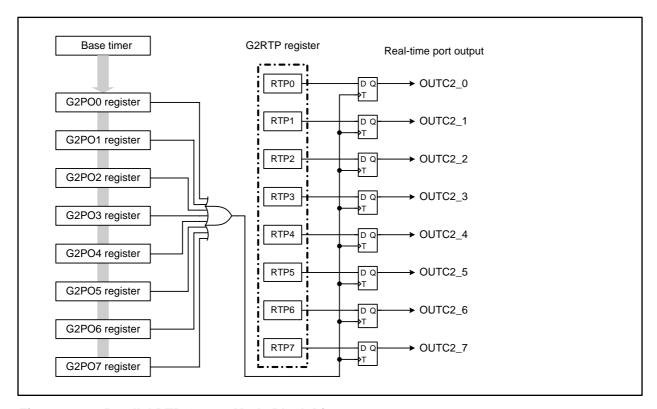

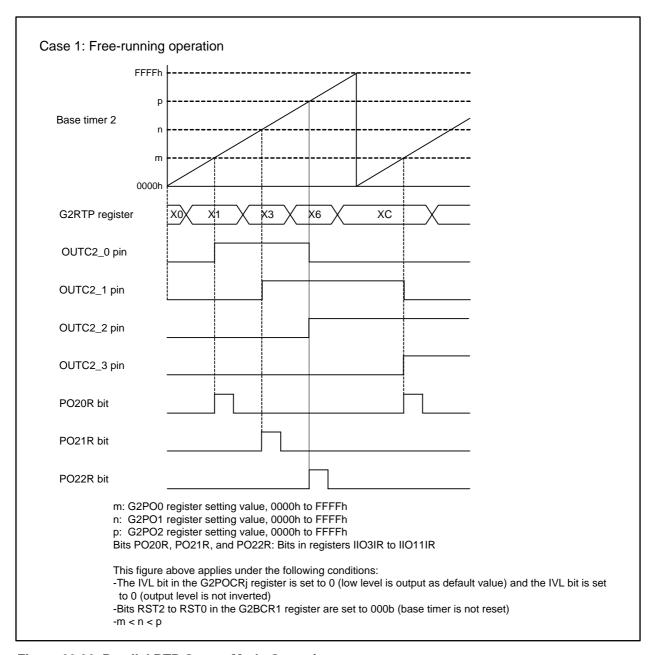

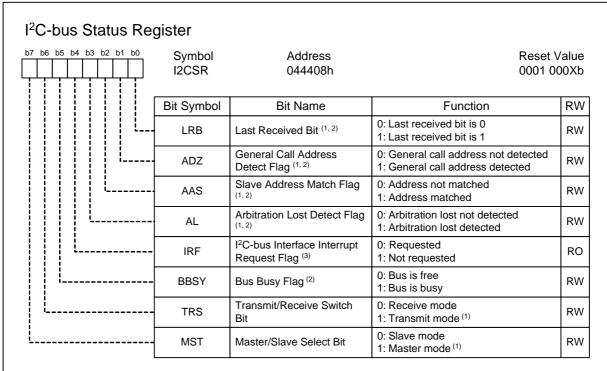

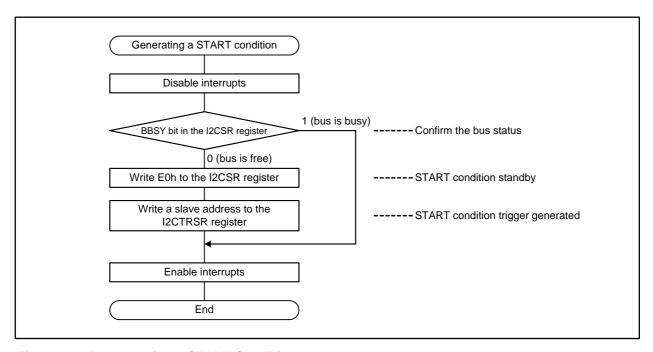

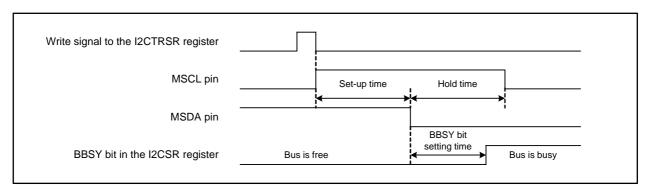

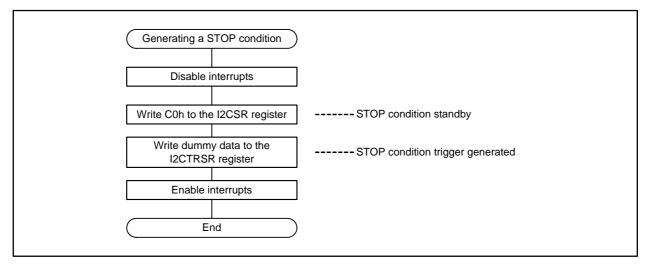

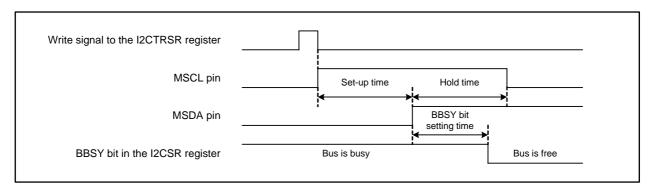

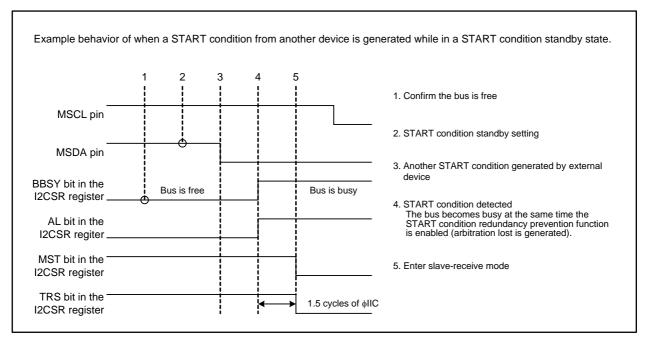

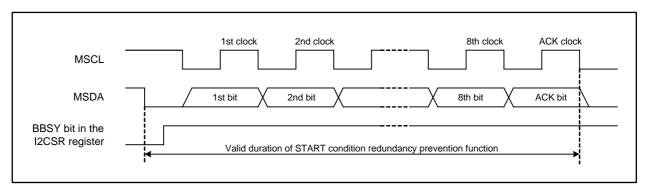

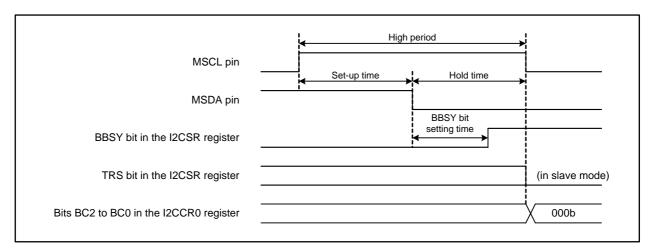

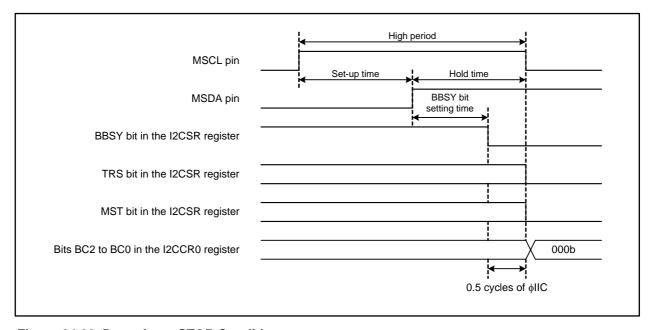

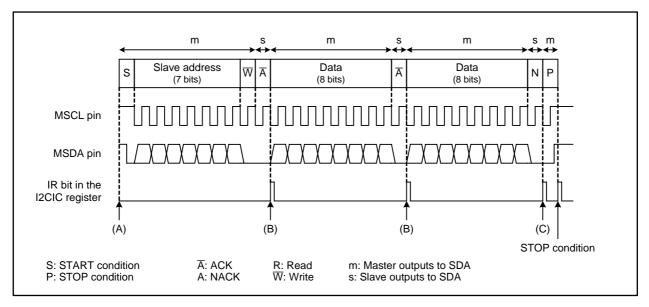

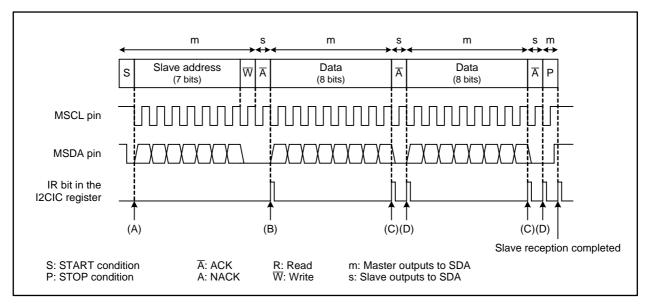

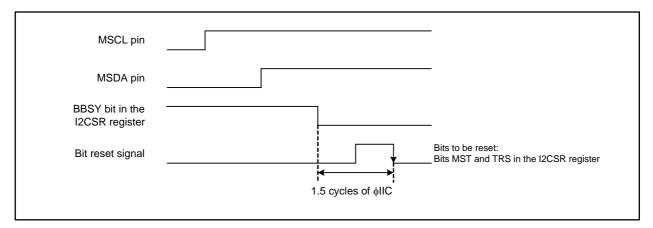

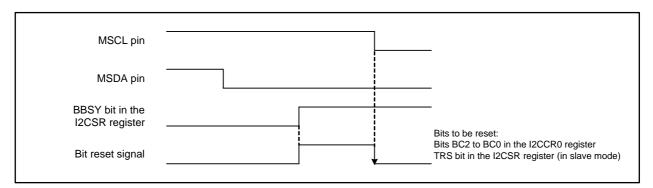

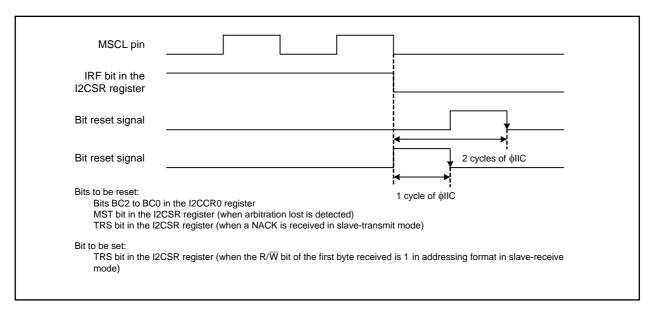

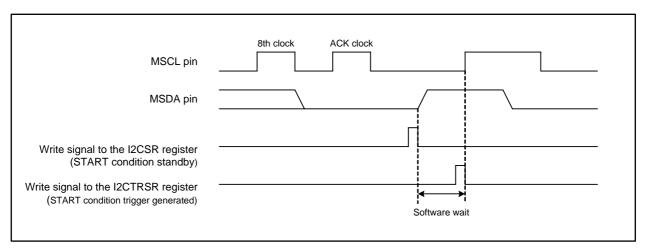

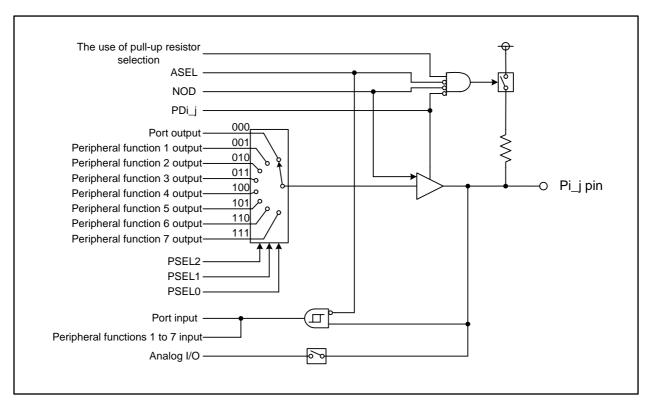

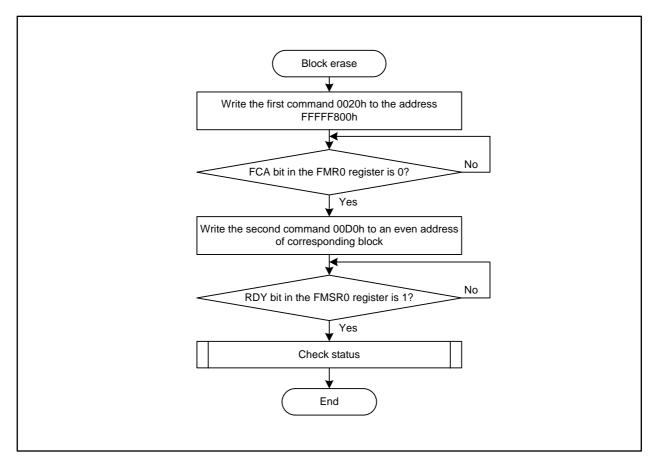

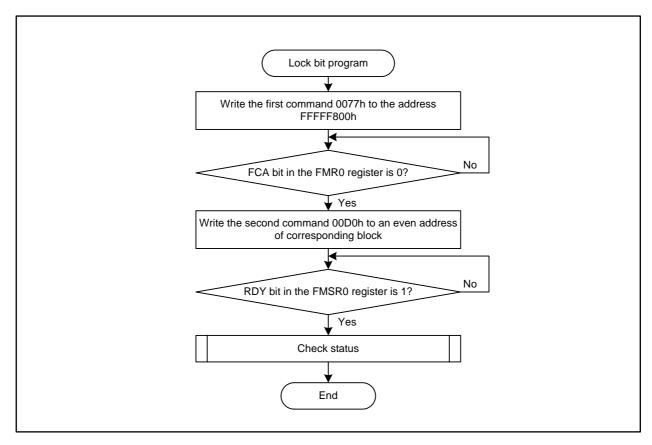

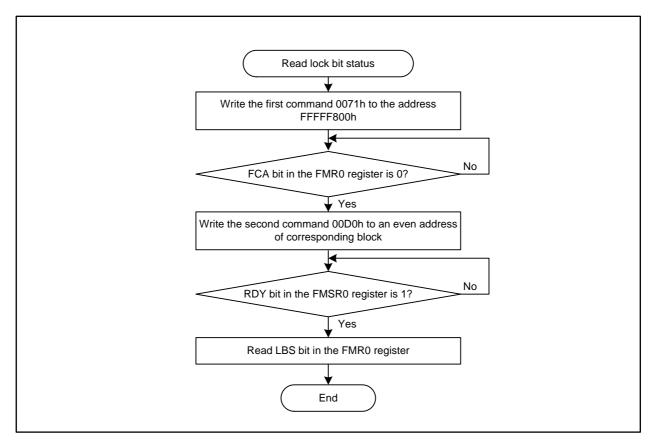

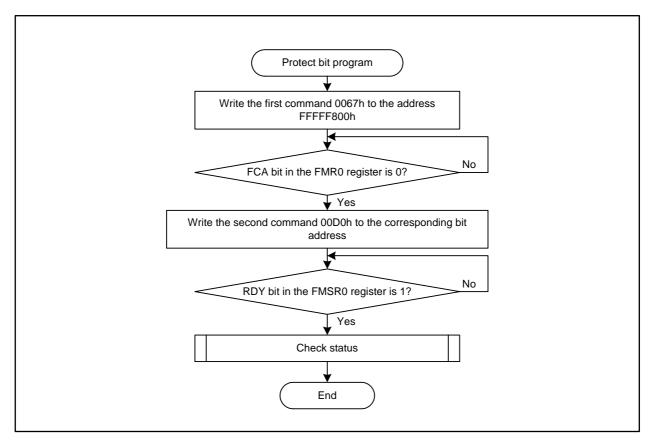

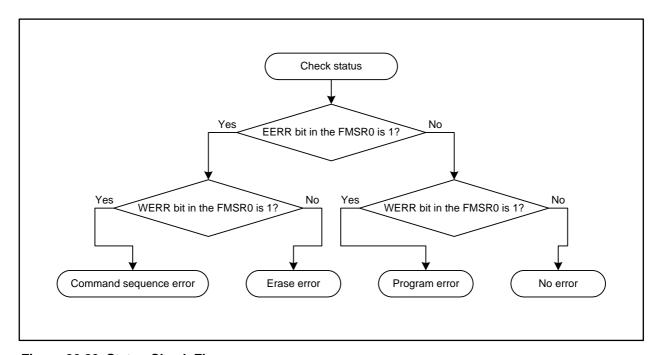

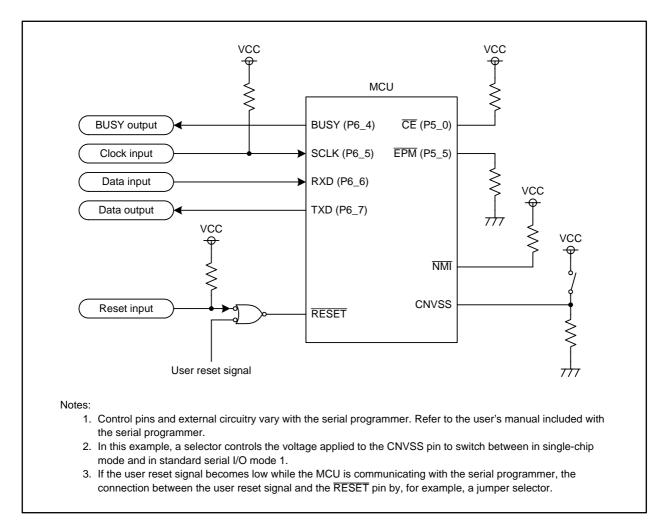

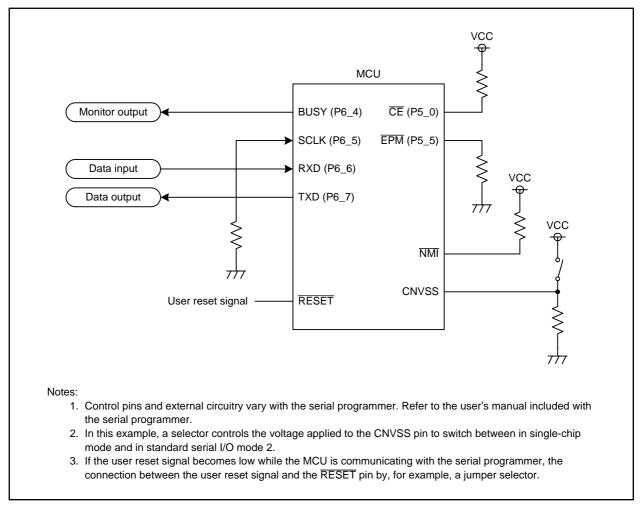

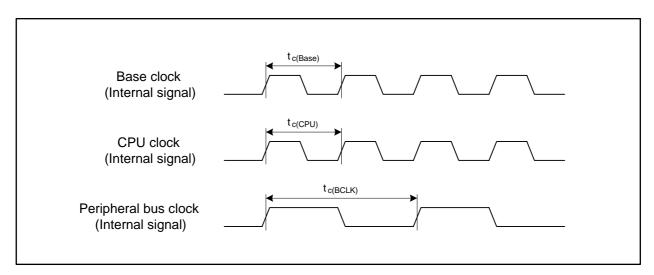

| R5F64168HDFD |     | PLQP0144KA-A     |                  |              | -40°C to 85°C (D version) |