SG6903

#### **FEATURES OVERVIEW**

- Interleaved PFC/PWM switching

- Green-mode PFC and PWM operation

- No switching of PFC at light loads for best power saving

- Low start-up and operating current

- Innovative switching-charge multiplier-divider

- Multi-vector control for improved PFC output transient response

- Average-current-mode Control for PFC

- Programmable two-level PFC output voltage

- PFC over-voltage and under-voltage protections

- PFC and PWM feedback open-loop protection

- Cycle-by-cycle current limiting for PFC/PWM

- Slope compensation for PWM

- Constant power limit for PWM

- Brownout protection

#### **APPLICATIONS**

Switching Power Suppliers with Active PFC

**High-Power Adaptors**

#### **DESCRIPTION**

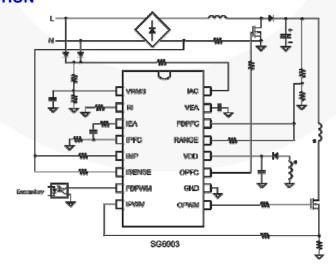

The highly integrated SG6903 is specially designed for power supplies consist of boost PFC and flyback PWM. It requires very few external components to achieve green-mode operation and versatile protections. It is available in 16-pin SOP packages.

The patented interleave-switching feature synchronizes the PFC and PWM stages and reduces switching noise. At light loads, the switching frequency is continuously decreased to reduce power consumption. If output loading is further reduced, the PFC stage is turned off to further reduce power consumption.

For PFC stage, the proprietary multi-vector control scheme provides a fast transient response in a low-bandwidth PFC loop, in which the overshoot and undershoot of the PFC voltage are clamped. If the feedback loop is broken, the SG6903 will shut off PFC to prevent extra-high voltage on output. Programmable two-level output voltage control will reduce the PFC output voltage at low line input to increase the efficiency of the power supply.

For the flyback PWM, the synchronized slope compensation ensures the stability of the current loop under continuous-conduction-mode operation. Built-in line-voltage compensation maintains constant output-power limit. Hiccup operation during output overloading is also guaranteed.

In addition, SG6903 provides complete protection functions such as brownout protection and RI pin open/short.

#### **TYPICAL APPLICATION**

## **MARKING DIAGRAMS**

#### **PIN CONFIGURATION**

#### **ORDERING INFORMATION**

| Part Number | Pb-Free | Package    |  |

|-------------|---------|------------|--|

| SG6903SZ    |         | 16-pin SOP |  |

#### **PIN DESCRIPTIONS**

| Name   | Pin No. | Туре                                           | Function                                                                                                                                                                                                                                                                      |

|--------|---------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VRMS   | 1       | Line-Voltage<br>Detection                      | Line voltage detection. The pin is used for PFC multiplier, RANGE control of PFC output voltage, brownout protection. For brownout protection, the controller will be disabled after a delay time when the VRMS voltage drops below a threshold.                              |

| RI     | 2       | Oscillator Setting                             | Reference setting. One resistor connected between RI and ground determines the switching frequency. The switching frequency is equal to [1560 / RI] KHz, where RI is in $K\Omega$ . For example, if RI is equal to $24K\Omega$ , then the switching frequency will be 65 KHz. |

| IEA    | 3       | Output for PFC<br>Current Amplifier            | This is the output of the PFC current amplifier. The signal from this pin will be compared with an internal saw-tooth and hence determine the pulse width for PFC gate drive.                                                                                                 |

| IPFC   | 4       | Inverting Input for PFC Current Amplifier      | The inverting input of the PFC current amplifier. Proper external compensation circuits will result in excellent input power factor via average-current-mode control.                                                                                                         |

| IMP    | 5       | Non-inverting Input for PFC Current Amplifier  | The non-inverting input of the PFC current amplifier and also the output of multiplier. Proper external compensation circuits will result in excellent input power factor via average-current-mode control.                                                                   |

| ISENSE | 6       | Peak Current Limit<br>Setting for PFC          | The peak current setting for PFC.                                                                                                                                                                                                                                             |

| FBPWM  | 7       | PWM Feedback Input                             | The control input for voltage-loop feedback of PWM stage. It is internally pulled high through a 6.5 K $\Omega$ resistance. Usually an external opto-coupler from secondary feedback circuit is connected to this pin.                                                        |

| IPWM   | 8       | PWM Current Sense                              | The current sense input for the Flyback PWM. Via a current sense resistor, this pin provides the control input for peak-current-mode control and cycle by cycle current limiting.                                                                                             |

| OPWM   | 9       | PWM Gate Drive                                 | The totem-pole output drive for the Flyback PWM MOSFET. This pin is internally clamped under 17V to protect the MOSFET.                                                                                                                                                       |

| GND    | 10      | Ground                                         | Ground                                                                                                                                                                                                                                                                        |

| OPFC   | 11      | PFC Gate Drive                                 | The totem-pole output drive for the PFC MOSFET. This pin is internally clamped under 17V to protect the MOSFET.                                                                                                                                                               |

| VDD    | 12      | Supply                                         | The power supply pin.                                                                                                                                                                                                                                                         |

| RANGE  | 13      | PFC Output-voltage Control                     | Two-level output-voltage setting for PFC. The PFC output voltage at low line can be reduced to improve efficiency. The RANGE pin has high impedance whenever the VRMS voltage is lower than a threshold.                                                                      |

| FBPFC  | 14      | Voltage Feedback<br>Input for PFC              | The feedback input for PFC voltage loop. The inverting input of PFC error amp. This pin is connected to the PFC output through a divider network.                                                                                                                             |

| VEA    | 15      | Error-Amp Output for PFC voltage feedback loop | The error-amp output for PFC voltage feedback loop. A compensation network (usually a capacitor) is connected between this pin and ground. A large capacitor value will result in a narrow bandwidth and hence improve the power factor.                                      |

| IAC    | 16      | Input AC Current                               | Before start-up, this input is used to provide startup current for VDD. For normal operation, this input is used to provide current reference for the multiplier.                                                                                                             |

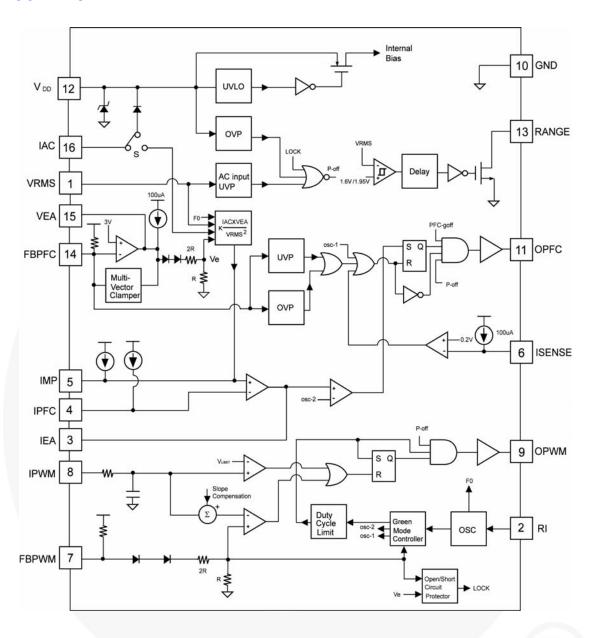

#### **BLOCK DIAGRAM**

SG6903

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                  | Parameter                                          | Value       | Unit                 |

|-------------------------|----------------------------------------------------|-------------|----------------------|

| $V_{VDD}$               | DC Supply Voltage*                                 | 25          | V                    |

| I <sub>AC</sub>         | Input AC Current                                   | 2           | mA                   |

| $V_{High}$              | OPWM, OPFC, IAC                                    | -0.3 to +25 | V                    |

| V <sub>Low</sub>        | Others                                             | -0.3 to +7  | V                    |

| P <sub>D</sub>          | Power Dissipation At T <sub>A</sub> < 50°C         | 0.8         | W                    |

| TJ                      | Operating Junction Temperature                     | -40 to +125 | $^{\circ}$           |

| T <sub>STG</sub>        | Storage Temperature Range                          | -55 to +150 | $^{\circ}$           |

| $R_{\theta j\text{-C}}$ | Thermal resistance (Junction to Case)              | 41.95       | °C/W                 |

| TL                      | Lead Temperature (Wave soldering or IR, 10seconds) | 260         | $^{\circ}\mathbb{C}$ |

| V <sub>ESD,HBM</sub>    | ESD capability, HBM model                          | 4.5         | KV                   |

| V <sub>ESD,MM</sub>     | ESD capability, Machine model                      | 250         | V                    |

<sup>\*</sup>All voltage values, except differential voltages, are given with respect to GND pin.

#### RECOMMENDED OPERATING CONDITIONS

| Symbol         | Parameter                      | Value      | Unit       |

|----------------|--------------------------------|------------|------------|

| T <sub>A</sub> | Operating Ambient Temperature* | -20 to +85 | $^{\circ}$ |

<sup>\*</sup>For proper operation, electrical characteristics (12V<V<sub>DD</sub><20V, -20°C <T<sub>A</sub><85°C Unless noted)

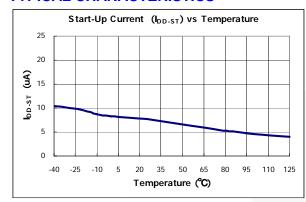

### **VDD** section

| Symbol                | Parameter                                           | Test Conditions                                    | Min.                        | Тур.                        | Max.                        | Unit |

|-----------------------|-----------------------------------------------------|----------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|------|

| V <sub>DD-OP</sub>    | Continuously Operating Voltage                      |                                                    |                             |                             | 20                          | V    |

| I <sub>DD-ST</sub>    | Start-up Current                                    | $0V < V_{DD} < V_{DD-ON}$                          |                             | 10                          | 25                          | μΑ   |

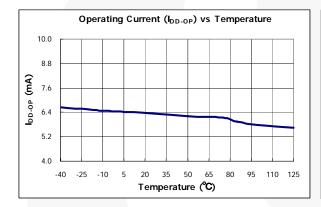

| I <sub>DD-OP</sub>    | Operating Current                                   | $V_{DD}$ = 15V; OPFC, OPWM open; RI = 24K $\Omega$ |                             | 6                           | 10                          | mA   |

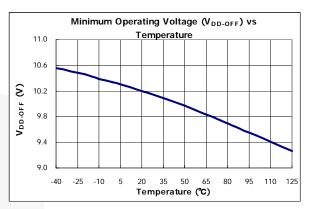

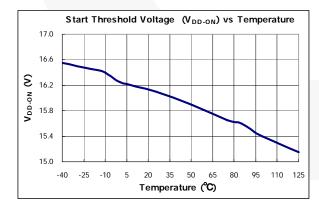

| $V_{DD-ON}$           | Start Threshold Voltage                             |                                                    | 15                          | 16                          | 17                          | V    |

| $V_{\text{DD-OFF}}$   | Min. Operating Voltage                              |                                                    | 9                           | 10                          | 11                          | V    |

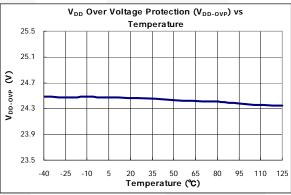

| $V_{\text{DD-OVP}}$   | VDD OVP Threshold                                   |                                                    | 23.5                        | 24.5                        | 25.5                        | V    |

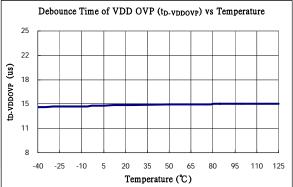

| t <sub>D-VDDOVP</sub> | Debounce Time of VDD OVP                            |                                                    | 8                           |                             | 25                          | μs   |

| $V_{\text{DD-TH-G}}$  | VDD Low-Threshold Voltage to Exit<br>Green-OFF Mode |                                                    | V <sub>DD-OFF</sub><br>+0.9 | V <sub>DD-OFF</sub><br>+1.5 | V <sub>DD-OFF</sub><br>+2.1 | V    |

<sup>\*</sup>Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device.

SG6903

## **Oscillator & Green-Mode Operation**

| Symbol                   | Parameter                                                                 | Test Conditions | Min. | Тур. | Max. | Unit |

|--------------------------|---------------------------------------------------------------------------|-----------------|------|------|------|------|

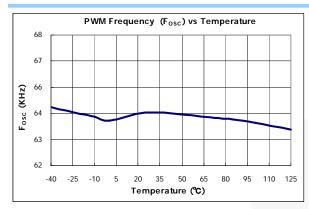

| Fosc                     | PWM Frequency                                                             | RI = 24KΩ       | 62   | 65   | 68   | KHz  |

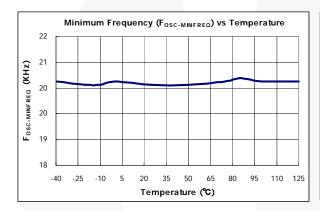

| F <sub>OSC-MINFREQ</sub> | Minimum Frequency in Burst Mode                                           | RI = 24KΩ       | 18   | 20   | 22   | KHz  |

| RI                       | RI Pin Resistance Range                                                   |                 | 15   |      | 47   | ΚΩ   |

| RI <sub>OPEN</sub>       | RI Pin Open Protection If RI> RI <sub>open</sub> , SG6903 will turn off   |                 |      | 200  |      | ΚΩ   |

| RI <sub>SHORT</sub>      | RI Pin Short Protection If RI< RI <sub>short</sub> , SG6903 will turn off |                 |      | 2    |      | ΚΩ   |

#### **VRMS for UVP and RANGE**

| Symbol                 | Parameter                                                                          | Test Conditions      | Min.                                             | Тур. | Max.                                            | Unit |

|------------------------|------------------------------------------------------------------------------------|----------------------|--------------------------------------------------|------|-------------------------------------------------|------|

| V <sub>RMS-UVP-1</sub> | RMS AC Voltage Under Voltage Protection<br>Threshold (with t <sub>UVP</sub> delay) |                      | 0.75                                             | 0.8  | 0.85                                            | V    |

| V <sub>RMS-UVP-2</sub> | Recovery level on VRMS                                                             |                      | V <sub>RMS-UV</sub><br><sub>P-1</sub> +0.1<br>6V |      | V <sub>RMS-UV</sub><br><sub>P-1</sub> +0.2<br>V | V    |

| t <sub>D-PWM</sub>     | When UVP Occurs ,The interval from PFC off to PWM off                              |                      | t <sub>UVP-Min</sub> +<br>9                      |      | t <sub>UVP-Min</sub><br>+14                     | ms   |

| t <sub>UVP</sub>       | Under Voltage Protection Delay Time (No delay for startup)                         |                      | 150                                              | 195  | 240                                             | ms   |

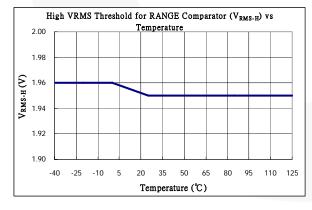

| V <sub>RMS-H</sub>     | High V <sub>RMS</sub> Threshold for RANGE Comparator                               |                      | 1.9                                              | 1.95 | 2.0                                             | V    |

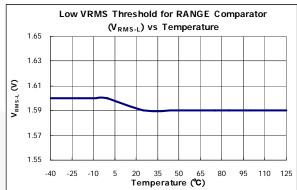

| $V_{RMS-L}$            | Low V <sub>RMS</sub> Threshold for RANGE Comparator                                |                      | 1.55                                             | 1.6  | 1.65                                            | V    |

| t <sub>RANGE</sub>     | Range-Enable Delay Time                                                            |                      | 140                                              | 170  | 200                                             | ms   |

| V <sub>OL</sub>        | Output Low Voltage of RANGE Pin                                                    | I <sub>o</sub> = 1mA | \                                                |      | 0.5                                             | V    |

| I <sub>OH</sub>        | Output High Leakage Current of RANGE Pin                                           | RANGE = 5V           |                                                  |      | 50                                              | nA   |

## **PFC** stage

## **Voltage Error Amplifier**

| Symbol                  | Parameter                                  | Test Conditions | Min. | Тур. | Max. | Unit      |

|-------------------------|--------------------------------------------|-----------------|------|------|------|-----------|

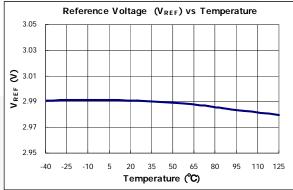

| $V_{REF}$               | Reference Voltage                          |                 | 2.95 | 3    | 3.05 | V         |

| Av                      | Open-loop Gain                             |                 |      | 60   |      | dB        |

| Z <sub>o</sub>          | Output Impedance                           |                 |      | 110  |      | ΚΩ        |

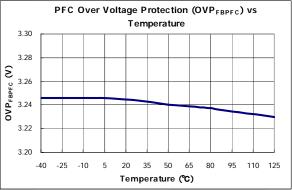

| $OVP_{FBPFC}$           | PFC Over Voltage Protection                |                 | 3.2  | 3.25 | 3.3  | V         |

| $\triangle OVP_{FBPFC}$ | PFC Feedback Voltage Protection Hysteresis |                 | 60   | 90   | 120  | mV        |

| t <sub>OVP-FBPFC</sub>  | Debounce Time of PFC OVP                   |                 | 40   | 70   | 120  | μs        |

| V <sub>FBPFC-H</sub>    | Clamp-High Feedback Voltage                |                 | 3.1  | 3.15 | 3.2  | V         |

| G <sub>FBPFC-H</sub>    | Clamp-High Gain                            |                 |      | 0.5  |      | μΑ/mV     |

| $V_{FBPFC-L}$           | Clamp-Low Feedback Voltage                 |                 | 2.75 | 2.85 | 2.9  | V         |

| G <sub>FBPFC-L</sub>    | Clamp-Low Gain                             |                 |      | 6.5  |      | mA/m<br>V |

| I <sub>FBPFC-L</sub>    | Maximum Source Current                     |                 | 1.5  | 2    | 7    | mA        |

| I <sub>FBPFC</sub> -H   | Maximum Sink Current                       |                 | 70   | 110  |      | μA        |

| UVP <sub>FBPFC</sub>    | PFC Feedback Under Voltage Protection      |                 | 0.35 | 0.4  | 0.45 | V         |

| t <sub>UVP-FBPFC</sub>  | Debounce Time of PFC UVP                   |                 | 40   | 70   | 120  | μs        |

SG6903

## **Current Error Amplifier**

| Symbol                | Parameter                        | Test Conditions                                | Min. | Typ. | Max. | Unit |

|-----------------------|----------------------------------|------------------------------------------------|------|------|------|------|

| V <sub>OFFSET</sub>   | Input Offset Voltage ((-) > (+)) |                                                |      | 8    |      | mV   |

| $A_{l}$               | Open-loop Gain                   |                                                |      | 60   |      | dB   |

| BW                    | Unit Gain Bandwidth              |                                                |      | 1.5  |      | MHz  |

| CMRR                  | Common-mode Rejection Ratio      | $V_{CM} = 0 \text{ to } +1.5V$                 |      | 70   |      | dB   |

| V <sub>OUT-HIGH</sub> | Output High Voltage              |                                                | 3.2  |      |      | V    |

| $V_{\text{OUT-LOW}}$  | Output Low Voltage               |                                                |      |      | 0.2  | V    |

| $I_{MR1}$ , $I_{MR2}$ | Reference Current Source         | $RI = 24 K\Omega (I_{MR} = 20 + I_{RI} * 0.8)$ | 50   |      | 70   | μA   |

| IL                    | Maximum Source Current           |                                                | 3    |      |      | mA   |

| I <sub>H</sub>        | Maximum Sink Current             |                                                |      | 0.25 |      | mA   |

## **Peak Current Limit**

| Symbol               | Parameter                                                                                            | Test Conditions | Min. | Тур. | Max. | Unit |

|----------------------|------------------------------------------------------------------------------------------------------|-----------------|------|------|------|------|

| l <sub>P</sub>       | Constant Current Output                                                                              | RI = 24KΩ       | 90   | 100  | 110  | μΑ   |

| $V_{PK}$             | Peak Current Limit Threshold Voltage<br>Cycle-by-Cycle Limit (V <sub>SENSE</sub> < V <sub>PK</sub> ) | VRMS = 1.05V    | 0.15 | 0.2  | 0.25 | V    |

|                      |                                                                                                      | VRMS = 3V       | 0.35 | 0.4  | 0.45 | V    |

| t <sub>PD-PFC</sub>  | Propagation Delay                                                                                    |                 |      |      | 200  | ns   |

| t <sub>LEB-PFC</sub> | Leading-Edge Blanking Time                                                                           |                 | 270  | 350  | 450  | ns   |

## Multiplier

| Symbol              | Parameter                                            | Test Conditions                                                         | Min. | Тур. | Max. | Unit |

|---------------------|------------------------------------------------------|-------------------------------------------------------------------------|------|------|------|------|

| I <sub>AC</sub>     | Input AC Current                                     | Multiplier Linear Range                                                 | 0    |      | 360  | μA   |

| I <sub>MO-max</sub> | Maximum Multiplier Current Output;                   | RI = 24 KΩ                                                              |      | 250  |      | μA   |

| I <sub>MO-1</sub>   | Multiplier Current Output<br>(low-line, high-power)  | $V_{RMS}$ = 1.05V; $I_{AC}$ = 90 $\mu$ A; VEA = 7.5V;RI = 24 k $\Omega$ | 200  | 250  | 280  | μΑ   |

| I <sub>MO-2</sub>   | Multiplier Current Output<br>(high-line, high-power) | $V_{RMS} = 3V; I_{AC} = 264\mu A;$<br>$V_{EA} = 7.5V; RI = 24 k\Omega$  | 65   | 85   |      | μΑ   |

| $V_{IMP}$           | Voltage of IMP Open                                  |                                                                         | 3.4  | 3.9  | 4.4  | V    |

## **PFC Output Driver**

| Symbol              | Parameter                                        | Test Conditions                                  | Min. | Тур. | Max. | Unit |

|---------------------|--------------------------------------------------|--------------------------------------------------|------|------|------|------|

| Vz                  | Output Voltage Maximum (Clamp)                   | V <sub>DD</sub> =20V                             |      | 16   | 18   | V    |

| V <sub>OL-PFC</sub> | Output Voltage Low                               | $V_{DD}$ =15V; $I_{O}$ = 100mA                   |      |      | 1.5  | V    |

| t <sub>PFC</sub>    | The interval of OPFC lags behind OPWM at startup |                                                  | 4.5  | 5.75 | 7    | ms   |

| V <sub>OH-PFC</sub> | Output Voltage High                              | $V_{DD}$ =13V; $I_{O}$ = 100mA                   | 8    |      |      | V    |

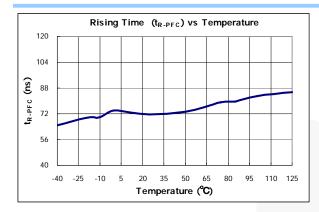

| t <sub>R-PFC</sub>  | Rising Time                                      | $V_{DD}$ =15V; $C_L$ =5nF ; O/P= 2V to 9V        | 40   | 70   | 120  | ns   |

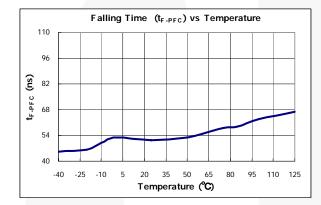

| t <sub>F-PFC</sub>  | Falling Time                                     | $V_{DD}$ =15V;C <sub>L</sub> =5nF ;O/P= 9V to 2V | 40   | 60   | 110  | ns   |

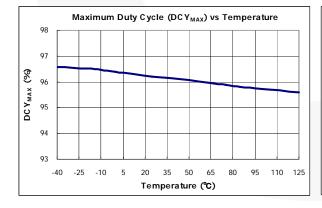

| DCY <sub>MAX</sub>  | Maximum Duty Cycle                               |                                                  | 93   |      | 98   | %    |

SG6903

## **PWM Stage**

#### **FBPWM**

| Symbol                   | Parameter                              | Test Conditions             | Min. | Тур.                      | Max. | Unit |

|--------------------------|----------------------------------------|-----------------------------|------|---------------------------|------|------|

| A <sub>v-PWM</sub>       | FB to Current Comparator Attenuation   |                             | 2.5  | 3.1                       | 3.5  | V/V  |

| Z <sub>FB</sub>          | Input Impedance                        |                             | 4    | 5                         | 7    | ΚΩ   |

| I <sub>FB</sub>          | Maximum Source Current                 |                             | 8.0  | 1.2                       | 1.5  | mA   |

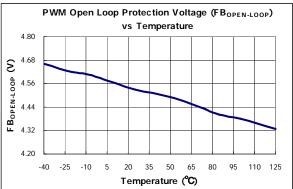

| FB <sub>OPEN-LOOP</sub>  | PWM Open Loop Protection voltage       |                             | 4.2  | 4.5                       | 4.8  | V    |

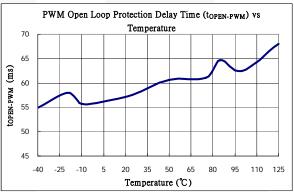

| t <sub>OPEN-PWM</sub>    | PWM Open Loop Protection Delay Time    |                             | 45   | 56                        | 70   | ms   |

| V <sub>PFC-OFF 1</sub>   | PFC off Voltage at FBPWM               | RANGE = Ground              |      | V <sub>G</sub> +0.2<br>V  |      | V    |

| V <sub>PFC-OFF 2</sub>   | PFC off Voltage at FBPWM               | RANGE = Open                |      | V <sub>G</sub> +0.2<br>V  |      | V    |

| t <sub>PFC-OFF</sub>     | PFC Off Propagation Delay Time         |                             | 450  | 600                       | 750  | ms   |

| V <sub>PFC-ON 1.6</sub>  | PFC on Voltage at FBPWM                | RANGE = Ground; VRMS =1.6V  |      | V <sub>G</sub> +0.3<br>5V |      | V    |

| V <sub>PFC-ON 2.85</sub> | PFC on Voltage at FBPWM                | RANGE = Ground; VRMS =2.85V |      | V <sub>G</sub> +0.3<br>5V |      | V    |

| V <sub>PFC-ON 0.8</sub>  | PFC on Voltage at FBPWM                | RANGE = Open; VRMS =0.8V    |      | V <sub>G</sub> +0.8<br>5V |      | V    |

| V <sub>PFC-ON 1.95</sub> | PFC on Voltage at FBPWM                | RANGE = Open; VRMS =1.95V   |      | V <sub>G</sub> +0.5<br>V  |      | V    |

| V <sub>N</sub>           | Frequency Reduction Threshold on FBPWM | RANGE = Ground              | 1.9  | 2.1                       | 2.3  | V    |

| $S_G$                    | Green-Mode Modulation Slope            |                             | 60   | 75                        | 90   | Hz/V |

| $V_G$                    | Voltage on FBPWM at Fs = 20KHz         |                             | 1.35 | 1.6                       | 1.75 | V    |

## **PWM-Current Sense**

| Symbol                       | Parameter                                                                                                                                                                                                                                          | Test Conditions      | Min. | Тур. | Max. | Unit |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|------|------|------|

| t <sub>PD-PWM</sub>          | Propagation Delay to Output                                                                                                                                                                                                                        | VDD = 15V,OPWM <= 9V | 60   |      | 120  | ns   |

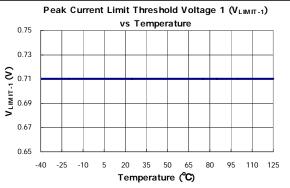

| V <sub>LIMIT-1</sub>         | Peak Current Limit Threshold Voltage1                                                                                                                                                                                                              | RANGE = Open         | 0.65 | 0.7  | 0.75 | V    |

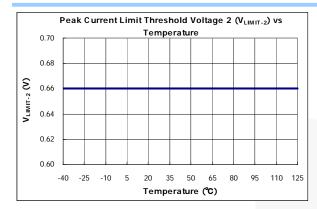

| V <sub>LIMIT-2</sub>         | Peak Current Limit Threshold Voltage2                                                                                                                                                                                                              | RANGE = Ground       | 0.6  | 0.65 | 0.7  | V    |

| t <sub>LEB-PWM</sub>         | Leading-Edge Blanking Time                                                                                                                                                                                                                         |                      | 270  | 350  | 450  | ns   |

| $	riangle V_{	extsf{SLOPE}}$ | $\label{eq:Slope Compensation} \begin{split} & \text{Slope Compensation} \\ & \triangle V_S = \triangle V_{\text{SLOPE}} \times (T_{\text{on}}/T) \\ & \triangle V_S : \text{Compensation Voltage Added to} \\ & \text{Current Sense} \end{split}$ |                      | 0.45 | 0.5  | 0.55 | V    |

## **PWM Output Driver**

| Symbol                | Parameter                      | Test Conditions                               | Min. | Тур. | Max. | Unit |

|-----------------------|--------------------------------|-----------------------------------------------|------|------|------|------|

| $V_{Z-PWM}$           | Output Voltage Maximum (Clamp) | V <sub>DD</sub> = 20V                         |      | 16   | 18   | V    |

| V <sub>OL-PWM</sub>   | Output Voltage Low             | V <sub>DD</sub> = 15V; I <sub>O</sub> = 100mA |      |      | 1.5  | V    |

| V <sub>OH-PWM</sub>   | Output Voltage High            | V <sub>DD</sub> = 13V; I <sub>O</sub> = 100mA | 8    |      |      | V    |

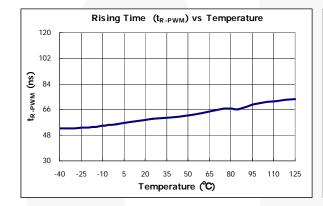

| t <sub>R-PWM</sub>    | Rising Time                    | $V_{DD}$ = 15V; $C_L$ = 5nF; O/P= 2V to 9V    | 30   | 60   | 120  | ns   |

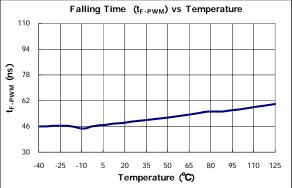

| t <sub>F-PWM</sub>    | Falling Time                   | $V_{DD}$ = 15V; $C_L$ = 5nF; O/P= 9V to 2V    | 30   | 50   | 110  | ns   |

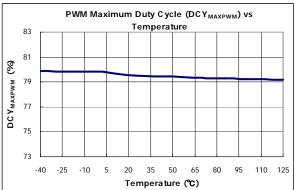

| DCY <sub>MAXPWM</sub> | Maximum Duty Cycle             |                                               | 73   | 78   | 83   | %    |

#### **TYPICAL CHARACTERISTICS**

#### **OPERATION DESCRIPTION**

SG6903 is a highly integrated PFC/PWM combo controller. Lots functions and protections are built in to provide a possible compact design. The following description will describe the operation and function in detail to give an overview of this chip.

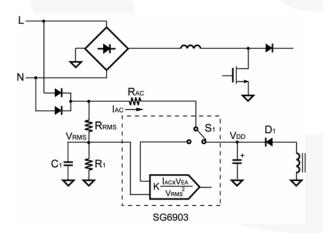

#### Start-up

Figure 1 shows the start-up circuit of the SG6903. A resistor R<sub>AC</sub> is utilized to charge V<sub>DD</sub> capacitor through S1. The turn-on and turn-off threshold of SG6903 are fixed internally at 16V/10V. During start-up, the hold-up capacitor must be charged to 16V through the start-up resistor so that SG6903 will be enabled. The hold-up capacitor will continue to supply V<sub>DD</sub> before the energy can be delivered from auxiliary winding of the main transformer. V<sub>DD</sub> must not drop below 10V during this start-up process. This UVLO hysteresis window ensures that hold-up capacitor is adequate to supply V<sub>DD</sub> during start-up. Since SG6903 consumes less than 25µA startup current, the value of RAC can be large to reduce power consumption. One 10µF capacitor should hold enough energy for successful start-up. After start-up, S1 will switch so that the current IAC will be the input for PFC multiplier. This helps reduce circuit complexity and power consumption.

FIG.1 Start-up circuit of the SG6903

# Switching Frequency and Current Sources

The switching frequency of SG6903 can be programmed by the resistor  $R_{\rm I}$  connected between RI pin and GND. The relationship is:

Fosc =

$$\frac{1560}{\text{Ri (k}\Omega)}$$

(KHz) .....(1)

For example, a  $24K\Omega$  resistor  $R_I$  results in a 65 KHz switching frequency. Accordingly, a constant Current  $I_T$  will flow through  $R_I$ .

$$I_T = \frac{1.2V}{R_I (k\Omega)} (mA)$$

.....(2)

I<sub>T</sub> is used to generate internal current reference.

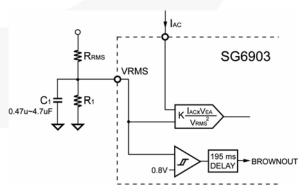

## Line Voltage Detection (VRMS)

Figure 2 shows a resistive divider with low-pass filtering for line-voltage detection on VRMS pin. The  $V_{RMS}$  voltage is used for the PFC multiplier, brownout protection, and range control.

For brownout protection, the SG6903 is disabled with 195ms delay time if the voltage  $V_{\text{RMS}}$  drops below 0.8V.

For PFC multiplier and range control, please refer to below section for more details.

FIG.2 Line voltage detection circuit

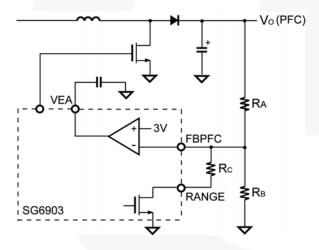

#### PFC Output Voltage Control (RANGE)

For a universal input  $(90 \sim 264 \text{Vac})$  power supply applying active boost PFC and Flyback as a second stage, the output voltage of PFC is usually designed around 250V at low line while it is 390V at high line. This can improve the efficiency at low-line input. In SG6903, the RANGE pin (open-drain structure) is used for the two-level output voltage setting.

Figure 3 shows the RANGE output that programs the PFC output voltage. The RANGE output is shorted to ground when the  $V_{RMS}$  voltage exceeds  $V_{RMS-H}$  (1.95V) while it is of high impedance (open) whenever the  $V_{RMS}$  voltage drops below  $V_{RMS-L}$  (1.6V). The output voltages can be designed using below equations.

Range = Open

$$\Rightarrow$$

Vo =  $\frac{R_A + R_B}{R_B} \times 3V$  ---- (3)

Range = Ground  $\Rightarrow$  Vo =  $\frac{R_A + (R_B // R_C)}{(R_B // R_C)} \times 3V$

FIG.3 Range control two level output voltage

#### Interleave Switching

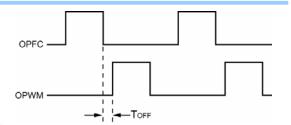

The SG6903 uses interleaved switching to synchronize the PFC and Flyback stages. This reduces switching noise and spreads the EMI emissions. Figure 4 shows that an off-time  $T_{\rm OFF}$  is inserted in between the turn-off of the PFC gate drive and the turn-on of the PWM.

FIG.4 Interleaved switching pattern

#### **PFC Operation**

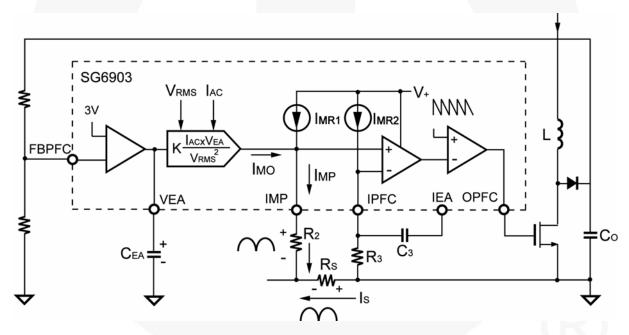

The purpose of a boost active power factor corrector (PFC) is to shape the input current of a power supply. The input current waveform and phase will follow that of the input voltage. Using SG6903, average-current-mode control is utilized for continuous-current-mode operation for the PFC booster. With the innovative multi-vector control for voltage loop and *Switching Charge®* multiplier/divider for current reference, excellent input power factor is achieved with good noise immunity and transient response. Figure 5 shows the total control loop for the average-current-mode control circuit of SG6903.

The current source output from the *Switching Charge*® multiplier/divider can be expressed as:

$$I_{MO} = K \times \frac{I_{AC} \times V_{EA}}{V_{RMS}^2} (uA) ----- (4)$$

Refer to Figure 5, the current output from IMP pin,  $I_{MP}$ , is the summation of  $I_{MO}$  and  $I_{MR1}$ .  $I_{MR1}$  and  $I_{MR2}$  are identical fixed current sources. They are used to pull high the operating point of the IMP and IPFC pins since the voltage across  $R_S$  goes negative with respect to ground. The constant current sources  $I_{MR1}$  and  $I_{MR2}$  are typically  $60\mu A$ .

Through the differential amplification of the signal across Rs, better noise immunity is achieved. The output of IEA will be compared with an internal sawtooth and hence the pulse width for PFC is determined. Through the average current-mode control loop, the input current Is will be proportional to I<sub>MO</sub>.

$$Imo \times R2 = Is \times Rs - ...$$

(5)

According to Equation (5), the minimum value of R2 and maximum of Rs can be determined since  $I_{MO}$  should not exceed the specified maximum value.

There are different concerns in determining the value of the sense resistor Rs. The value of Rs should be small to reduce power consumption, but it should be large enough to maintain the resolution. A current transformer (CT) may be used to improve the efficiency of high power converters.

To achieve good power factor, the voltage for  $V_{RMS}$  and  $V_{EA}$  should be kept as constant as possible according to Equation (4). In other words, good RC filtering for  $V_{RMS}$  and narrow bandwidth (lower than the line frequency) for voltage loop are suggested for better input current shaping. The trans-conductance error amplifier has output impedance  $Z_O$  and a capacitor  $C_{EA}$  (1 $\mu$ F  $\sim$  10 $\mu$ F) should be connected to ground. This establishes a dominant pole f1 (Equation (6)) for the voltage loop.

$$f_1 = \frac{1}{2\pi \times Z_0 \times CEA} \qquad -----(6)$$

The average total input power can be expressed as:

$$\begin{aligned} &\text{Pin} = \text{Vin}(\text{rms}) \times \text{Iin}(\text{rms}) \\ &\propto V_{\text{RMS}} \times I_{\text{MO}} \\ &\propto V_{\text{RMS}} \times \frac{I_{\text{AC}} \times V_{\text{EA}}}{V_{\text{RMS}}^2} \\ &\propto V_{\text{RMS}} \times \frac{\frac{\text{Vin}}{R_{\text{AC}}} \times V_{\text{EA}}}{V_{\text{RMS}}^2} \\ &= \sqrt{2} \times \frac{V_{\text{EA}}}{R_{\text{AC}}} \end{aligned}$$

From Equation (7),  $V_{EA}$ , the output of the voltage error amplifier, actually controls the total input power and hence the power delivered to the load.

FIG.5 Average current mode control loop

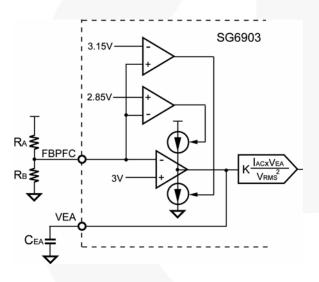

#### **Multi-vector Error Amplifier**

Although the PFC stage has a low bandwidth voltage loop for better input power factor, the innovative *Multi-Vector Error Amplifier* provides a fast transient response to clamp the overshoot and undershoot of the PFC output voltage.

Figure 6 shows the block diagram of the multi-vector error amplifier. When the variation of the feedback voltage exceeds  $\pm$  5% of the reference voltage, the trans-conductance error amplifier will adjust its output impedance to increase the loop response.

Once the voltage on the FBPFC pin is over  $OVP_{FBPFC}$ , the OPFC of the SG6903 will be disabled. THE OPFC will not be enabled again until the FBPFC voltage falls below  $OVP_{FBPFC}$ .

FIG. 6 Multi-vector error amplifier

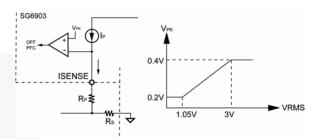

#### **Cycle-by-cycle Current Limiting**

SG6903 provides cycle-by-cycle current limiting for both PFC and PWM stages. The voltage of  $V_{RMS}$  determines the voltage of  $V_{PK}$ . The relationship between  $V_{PK}$  and VRMS is also shown in Figure 7. The PFC gate drive will be terminated once the voltage on ISENSE pin goes below  $V_{PK}$ .

The amplitude of the constant current  $I_P$  is determined by the internal current reference according to the following equation:

$$IP = 2 \times \frac{1.2V}{R_1}$$

----(8)

FIG. 7 VRMS controlled current limiting

Therefore the peak current of the  $I_{SENSE}$  is given by  $(V_{RMS} < 1.05V)$ ,

$$Isense_peak = \frac{(IP \times RP) - 0.2V}{Rs} -----(9)$$

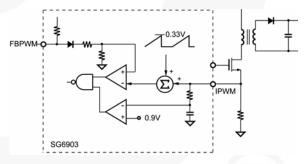

#### Flyback PWM and Slope Compensation

As shown in Figure 8, peak-current-mode control is utilized for Flyback PWM. The SG6903 inserts a synchronized 0.5V ramp at the beginning of each switching cycle. This built-in slope compensation ensures stable operation for continuous current-mode operation.

FIG. 8 Peak current control loop

When the IPWM voltage, across the sense resistor, reaches the threshold voltage (0.9V), the OPWM will be turned off after a small propagation delay t<sub>PD-PWM</sub>.

To improve stability or prevent sub-harmonic oscillation, a synchronized positive-going ramp in inserted at every switching cycle.

#### **Limited Power Control**

Every time when the output of power supply is shorted or over loaded, the FBPWM voltage will increase. If the FBPWM voltage is higher than a designed threshold,  $FB_{OPEN-LOOP}$  (4.5V), for longer than  $t_{OPEN-PWM}$  (56ms), the OPWM will then be turned off.

As long as the voltage on the VDD pin is larger than  $V_{\text{DD-OFF}}$  (minimum operating voltage), the OPWM will not be enabled. And this protection will be reset every  $t_{\text{OPEN-PWM-Hiccup}}$  interval. A low frequency hiccup mode protection will then be achieved to prevent the power supply from being overheated under over loading condition.

#### **Gate Drivers**

SG6903 output stage is a fast totem-pole gate driver. The output driver is clamped by an internal 18V Zener diode in order to protect the external power MOSFET.

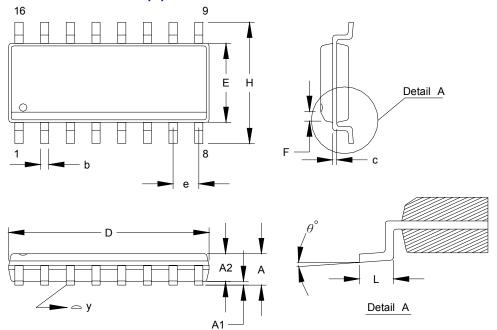

#### **PACKAGE INFORMATION**

## 16 PINS - PLASTIC SOP (S)

## **DIMENSION:**

| Symbol Millimeter   |       |           | Inch   |       |           |       |

|---------------------|-------|-----------|--------|-------|-----------|-------|

| Symbol              | Min.  | Тур.      | Max.   | Min.  | Тур.      | Max.  |

| Α                   | 1.346 |           | 1.753  | 0.053 |           | 0.069 |

| A1                  | 0.101 |           | 0.254  | 0.004 |           | 0.010 |

| A2                  | 1.244 |           | 1.499  | 0.049 |           | 0.059 |

| b                   |       | 0.406     |        |       | 0.016     | 4     |

| С                   |       | 0.203     |        |       | 0.008     |       |

| D                   | 9.804 |           | 10.008 | 0.386 |           | 0.394 |

| E                   | 3.810 |           | 3.988  | 0.150 |           | 0.157 |

| е                   |       | 1.270     |        |       | 0.050     |       |

| Н                   | 5.791 |           | 6.198  | 0.228 | A         | 0.244 |

| L                   | 0.406 |           | 1.270  | 0.016 |           | 0.050 |

| F                   |       | 0.381X45° |        |       | 0.015X45° |       |

| у                   |       |           | 0.101  |       |           | 0.004 |

| $\theta$ $^{ullet}$ | 0°    |           | 8°     | 0°    |           | 8°    |

#### TRADEMARKS

The following are registered and unregistered trademarks and service marks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

ACEx®

Build it Now™

CorePLUS™

CROSSVOLT™

CTL™

Current Transfer Logic™

EcoSPARK®

Fairopild®

Fairchild<sup>®</sup>

Fairchild Semiconductor<sup>®</sup>

FACT Quiet Series™

FACT<sup>®</sup>

FAST<sup>®</sup>

FastvCore™

FPS™

FRFET<sup>®</sup>

Global Power Resource<sup>™</sup>

Green FPS™ e-Series™

Green FPS™ e-Series™

GTO™

i-Lo™

IntelliMAX™

ISOPLANAR™

MegaBuck™

MICROCOUPLER™

MicroFET™

MicroFET™

MicroPak™

MICROCOUPLEF

MicroFETTM

MicroPakTM

MillerDriveTM

Motion-SPMTM

OPTOLOGIC®

OPTOPLANAR®

PDP-SPMTM

Power220®

Power247<sup>®</sup>

POWEREDGE<sup>®</sup>

Power-SPM™

PowerTrench<sup>®</sup>

Programmable Active Droop™

QFET<sup>®</sup>

QS™

QT Optoelectronics™

Quiet Series™

RapidConfigure™

SMART START™

SPM<sup>®</sup>

STEALTH™

SuperFET™

SuperSOT™-3

SuperSOT™-6

Syncfet<sup>M</sup>

The Power Franchise<sup>®</sup>

Power

TinyBoost<sup>M</sup>

TinyBoost<sup>M</sup>

TinyLogic<sup>®</sup>

TINYOPTO<sup>M</sup>

TinyPower<sup>TM</sup>

TinyPower<sup>TM</sup>

TinyPower<sup>TM</sup>

TinyPower<sup>TM</sup>

Unce<sup>TM</sup>

Unce<sup>TM</sup>

Unifet<sup>TM</sup>

VCX<sup>TM</sup>

SuperSOT™-8

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### PRODUCT STATUS DEFINITIONS

#### Definition of Terms

| Datasheet Identification | Product Status         | Definition                                                                                                                                                                                               |  |  |  |

|--------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Advance Information      | Formative or In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |  |  |

| Preliminary              | First Production       | This datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |  |

| No Identification Needed | Full Production        | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design.                                                   |  |  |  |

| Obsolete                 | Not In Production      | This datasheet contains specifications on a product that has been discontinued by Fairchild Semiconductor. The datasheet is printed for reference information only.                                      |  |  |  |

Rev. I31

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Fairchild Semiconductor: SG6903SZ