#### **General Description**

The DS4266 surface-mount ceramic crystal oscillator is part of Maxim's DS4-XO crystal oscillator product family. The DS4266 is a 266MHz crystal oscillator designed to support high-performance DDR memory applications that require a stable, low-jitter, and tight duty-cycle clock source. The device provides an overall accuracy and stability better than ±50ppm, including aging. Jitter performance is better than 0.7pspms typically over a 12kHz to 20MHz bandwidth, and duty-cycle performance is better than 48%/52%.

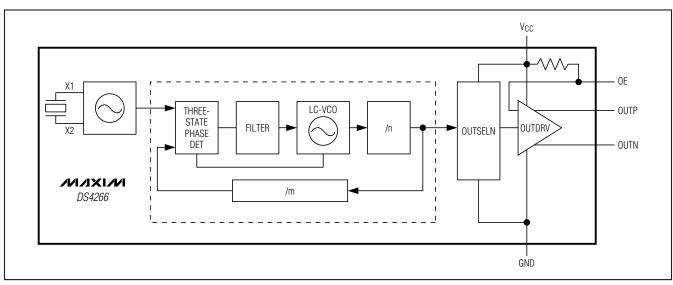

The DS4266 has an output frequency of 266MHz, and it supports LVDS and LVPECL output types. The DS4266 is constructed using a fundamental crystal in conjunction with high-performance silicon germanium PLL technology, enabling very low phase noise and phase jitter performance. The device operates from a 3.3V ±5% power supply and consumes a maximum current of 100mA.

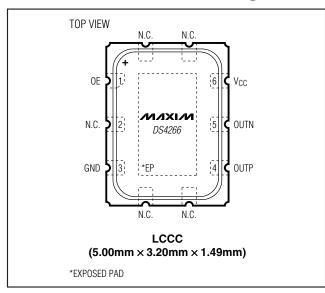

The DS4266 is packaged in a miniature 5mm x 3.2mm x 1.49mm, 10-lead LCCC ceramic package, making it suitable for applications where board space is critical.

### **Applications**

**DDR Memory Clock Source**

#### **Features**

- ♦ < 0.7ps<sub>RMS</sub> (typ) from 12kHz to 20MHz Jitter

- **♦ LVDS or LVPECL Output Types**

- **♦ 3.3V Operating Voltage**

- ♦ 5.0mm x 3.2mm x 1.49mm, 10-Pin LCCC Ceramic **Package**

- ♦ -40°C to +85°C Operating Temperature Range

- **♦ Lead-Free/RoHS Compliant**

### **Ordering Information**

| PART     | TEMP RANGE     | PIN-PACKAGE |

|----------|----------------|-------------|

| DS4266D+ | -40°C to +85°C | 10 LCCC     |

| DS4266P+ | -40°C to +85°C | 10 LCCC     |

+Denotes a lead(Pb)-free/RoHS-compliant package. The lead finish is JESD97 category e4 (Au over Ni) and is compatible with both lead-based and lead-free soldering processes.

Pin Configuration and Selector Guide appear at end of data sheet.

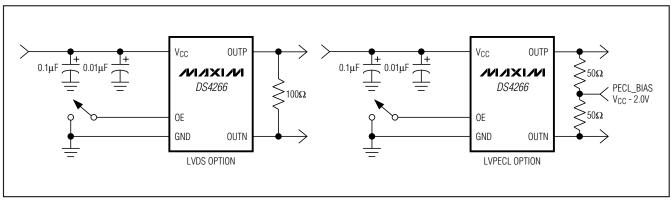

### **Typical Operating Circuits**

#### **ABSOLUTE MAXIMUM RATINGS**

| Power-Supply Voltage (V <sub>CC</sub> )0.3V, +4V | Storage Temperature Range55°C to +85°C         |

|--------------------------------------------------|------------------------------------------------|

| Operating Temperature Range40°C to +85°C         | Soldering Temperature Profile                  |

| Junction Temperature+150°C                       | (3 passes max of reflow)Refer to the IPC/JEDEC |

|                                                  | J-STD-020 Specification                        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

( $V_{CC} = 3.135V$  to 3.465V,  $T_A = -40$ °C to +85°C, unless otherwise noted.)

| PARAMETER                                                      | SYMBOL                  | CONDITIONS                                                                   | MIN                      | TYP              | MAX                       | UNITS |

|----------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------|--------------------------|------------------|---------------------------|-------|

| Operating Voltage Range                                        | Vcc                     | (Note 1)                                                                     | 3.135                    | 3.3              | 3.465                     | V     |

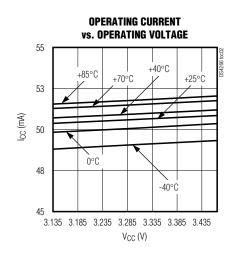

|                                                                | ICC_D                   | LVDS, output loaded or unloaded                                              |                          | 52               | 75                        |       |

| Operating Current                                              | ICC_PU                  | LVPECL, output unloaded                                                      |                          | 49               | 70                        | mA    |

|                                                                | ICC_PI                  | LVPECL, output load $50\Omega$ at V <sub>CC</sub> - 2.0V                     |                          | 74               | 100                       |       |

| Output Frequency                                               | fout                    |                                                                              |                          | fNOM             |                           | MHz   |

| Oscillator Startup Time                                        | tstartup                | (Note 2)                                                                     |                          |                  | 50                        | ms    |

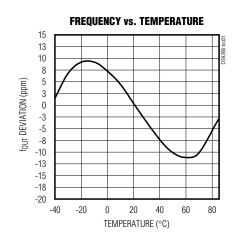

| Frequency Stability                                            | $\Delta$ f $TOTAL$      | Over temperature range, aging, load, supply, and initial tolerance (Note 3)  | -50                      | f <sub>NOM</sub> | +50                       | ppm   |

| Frequency Stability Over<br>Temperature with Initial Tolerance | $\Delta$ f $	ext{TEMP}$ | V <sub>CC</sub> = 3.3V                                                       | -35                      |                  | +35                       | ppm   |

| Initial Tolerance                                              | $\Delta$ finitial       | V <sub>CC</sub> = 3.3V, T <sub>A</sub> = +25°C                               |                          | ±20              |                           | ppm   |

| Frequency Change Due to ΔV <sub>CC</sub>                       | $\Delta$ f $_{VCC}$     | V <sub>CC</sub> = 3.3V ±5%                                                   | -3                       |                  | +3                        | ppm/V |

| Frequency Change Due to Load<br>Variation                      | $\Delta$ f $_{LOAD}$    | ±10% variation in termination resistance                                     |                          | ±1               |                           | ppm   |

| Aging (15 Years)                                               | $\Delta$ faging         |                                                                              | -7                       |                  | +7                        | ppm   |

|                                                                |                         | Integrated phase RMS; 12kHz to 5MHz, VCC = 3.3V, TA = +25°C                  |                          | 0.7              |                           |       |

| Jitter                                                         | JRMS                    | Integrated phase RMS; 12kHz to 20MHz, VCC = 3.3V, T <sub>A</sub> = +25°C     |                          | 0.7              |                           | ps    |

|                                                                |                         | Integrated phase RMS; 12kHz to 80MHz, $V_{CC} = 3.3V$ , $T_A = +25^{\circ}C$ |                          | 1.0              |                           |       |

| Input-Voltage High (OE)                                        | VIH                     | (Note 1)                                                                     | 0.7 x<br>V <sub>CC</sub> |                  | Vcc                       | V     |

| Input-Voltage Low (OE)                                         | V <sub>IL</sub>         | (Note 1)                                                                     | 0                        |                  | 0.3 x<br>V <sub>C</sub> C | V     |

| Input Leakage (OE)                                             | I <sub>LEAK</sub>       | GND ≤ OE ≤ V <sub>CC</sub>                                                   | -50                      |                  | +5.0                      | μΑ    |

### **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>CC</sub> = 3.135V to 3.465V,  $T_A$  = -40°C to +85°C, unless otherwise noted.)

| PARAMETER                                                       | SYMBOL                  | CONDITIONS                                                                  | MIN                     | TYP   | MAX                    | UNITS |

|-----------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------|-------------------------|-------|------------------------|-------|

| LVDS                                                            | I                       | ,                                                                           |                         |       |                        |       |

| Output High Voltage                                             | Vohlvdso                | 100Ω differential load (Note 1)                                             |                         |       | 1.475                  | V     |

| Output Low Voltage                                              | Vollydso                | 100Ω differential load (Note 1)                                             | 0.925                   |       |                        | V     |

| Differential Output Voltage                                     | Vodlvdso                | 100Ω differential load                                                      | 250                     |       | 425                    | mV    |

| Output Common-Mode Voltage<br>Variation                         | VLVDSOCOM               | 100Ω differential load                                                      |                         |       | 150                    | mV    |

| Change in Differential Magnitude or Complementary Inputs        | Δ V <sub>ODL</sub> VDSO | 100Ω differential load                                                      |                         |       | 25                     | mV    |

| Offset Output Voltage                                           | Vofflydso               | 100Ω differential load (Note 1)                                             | 1.125                   |       | 1.275                  | V     |

| Differential Output Impedance                                   | Rolvdso                 |                                                                             | 80                      |       | 140                    | Ω     |

| Output Current                                                  | Lvsslvdso               | OUTN or OUTP shorted to ground and measure the current in the shorting path |                         |       | 40                     | mA    |

|                                                                 | LLVDSO                  | OUTN or OUTP shorted together                                               |                         | 6.5   |                        | 1     |

| Output Rise Time (Differential)                                 | t <sub>RLVDSO</sub>     | 20% to 80%                                                                  |                         | 175   |                        | ps    |

| Output Fall Time (Differential)                                 | t <sub>FLVD</sub> SO    | 80% to 20%                                                                  |                         | 175   |                        | ps    |

| Duty Cycle                                                      | DCYCLE_LVDS             |                                                                             | 48                      |       | 52                     | %     |

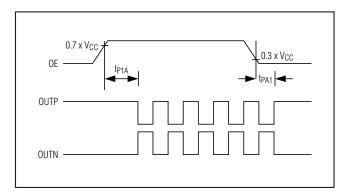

| Propagation Delay from OE Going<br>Low to Logical 1 at OUTP     | tPA1                    |                                                                             |                         |       | 200                    | ns    |

| Propagation Delay from OE Going<br>High to Output Active        | t <sub>P1A</sub>        |                                                                             |                         |       | 200                    | ns    |

| LVPECL                                                          | I                       | ,                                                                           |                         |       |                        |       |

| Output High Voltage                                             | V <sub>OH</sub>         | Output connected to $50\Omega$ at PECL_BIAS at V <sub>CC</sub> - 2.0V       | V <sub>CC</sub> - 1.085 |       | V <sub>CC</sub> - 0.88 | V     |

| Output Low Voltage                                              | V <sub>OL</sub>         | Output connected to $50\Omega$ at PECL_BIAS at V <sub>CC</sub> - 2.0V       | V <sub>CC</sub> - 1.825 |       | V <sub>CC</sub> - 1.62 | V     |

| Differential Voltage                                            | VDIFF_PECL              | Output connected to $50\Omega$ at PECL_BIAS at V <sub>CC</sub> - 2.0V       | 0.595                   | 0.710 |                        | V     |

| Rise Time                                                       | t <sub>R-PECL</sub>     |                                                                             |                         | 200   |                        | ps    |

| Fall Time                                                       | tF-PECL                 |                                                                             |                         | 200   |                        | ps    |

| Duty Cycle                                                      | DCYCLE_PECL             |                                                                             | 48                      |       | 52                     | %     |

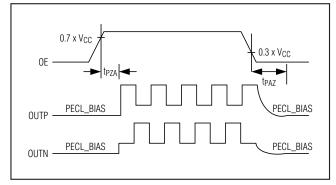

| Propagation Delay from OE Going<br>Low to Output High Impedance | tpaz                    |                                                                             |                         |       | 200                    | ns    |

| Propagation Delay from OE Going<br>High to Output Active        | t <sub>PZA</sub>        |                                                                             |                         |       | 200                    | ns    |

Note 1: All voltages referenced to ground.

Note 2: AC parameters are guaranteed by design and not production tested.

Note 3: Frequency stability is calculated as:  $\Delta f_{TOTAL} = \Delta f_{TEMP} + \Delta f_{VCC} \times (3.3 \times 5\%) + \Delta f_{LOAD} + \Delta f_{AGING}$ .

### Single-Sideband Phase Noise at fo = f<sub>NOM</sub>

| f                | SINGLE-SIDEBAND PHASE NOISE AT f <sub>O</sub> = f <sub>NOM</sub> (dBc/Hz) |  |  |

|------------------|---------------------------------------------------------------------------|--|--|

| f <sub>M</sub> = | 266MHz                                                                    |  |  |

| 10Hz             | -65                                                                       |  |  |

| 100Hz            | -95                                                                       |  |  |

| 1kHz             | -113                                                                      |  |  |

| 10kHz            | -113                                                                      |  |  |

| 100kHz           | -118                                                                      |  |  |

| 1MHz             | -137                                                                      |  |  |

| 10MHz            | -149                                                                      |  |  |

| 20MHz            | -153                                                                      |  |  |

### **Typical Operating Characteristics**

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

### **Pin Description**

| PIN     | NAME | FUNCTION                                                                      |

|---------|------|-------------------------------------------------------------------------------|

| 1       | OE   | Active-High Output Enable. Has an internal pullup 100kΩ resistor.             |

| 2, 7–10 | N.C. | No Connection. Must be floated.                                               |

| 3       | GND  | Ground                                                                        |

| 4       | OUTP | Positive Output for LVPECL or LVDS                                            |

| 5       | OUTN | Negative Output for LVPECL or LVDS                                            |

| 6       | Vcc  | Supply Voltage                                                                |

| _       | EP   | Exposed Paddle. Do not connect this pad or place exposed metal under the pad. |

Figure 1. Functional Diagram

### **Detailed Description**

The DS4266 consists of a fundamental-mode crystal and synthesizer IC packaged in a 5mm x 3.2mm x 1.49mm, 10-pin LCCC ceramic package. The device produces a frequency output of 266.00MHz. Two differential output types are available: LVDS and LVPECL. The device output can be enabled or disabled through the OE signal input. When the OE signal is low, LVPECL

outputs go to the PECL\_BAS level of  $V_{CC}$  - 2.9V, while the LVDS outputs are a logical 1. See Figures 2 and 3 for LVDS and LVPECL output timing diagrams.

### Additional Information

For more available frequencies in the DS4-XO family, refer to the DS4125 data sheet at <a href="https://www.maxim-ic.com/DS4125">www.maxim-ic.com/DS4125</a>.

Figure 2. LVDS Output Timing Diagram When OE Is Enabled and Disabled

Figure 3. LVPECL Output Timing Diagram When OE Is Enabled and Disabled

#### **Selector Guide**

| PART     | FREQUENCY (NOM)<br>(MHz) | FREQUENCY<br>STABILITY (ppm) | OUTPUT TYPE | TOP<br>MARK |

|----------|--------------------------|------------------------------|-------------|-------------|

| DS4266D+ | 266                      | ±50                          | LVDS        | 66D         |

| DS4266P+ | 266                      | ±50                          | LVPECL      | 66P         |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package. The lead finish is JESD97 category e4 (Au over Ni) and is compatible with both lead-based and lead-free soldering processes.

### **Pin Configuration**

### **Chip Information**

SUBSTRATE CONNECTED TO GROUND PROCESS: BiPOLAR SiGe

#### **Thermal Information**

| THETA-JA (°C/W) |  |

|-----------------|--|

| 90              |  |

### Package Information

For the latest package outline information and land patterns, go to  $\underline{\text{www.maxim-ic.com/packages}}.$

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 10 LCCC      | L1053+H2     | <u>21-0389</u> |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

DS4266D+ DS4266P+