# Spread Spectrum Clock Generator

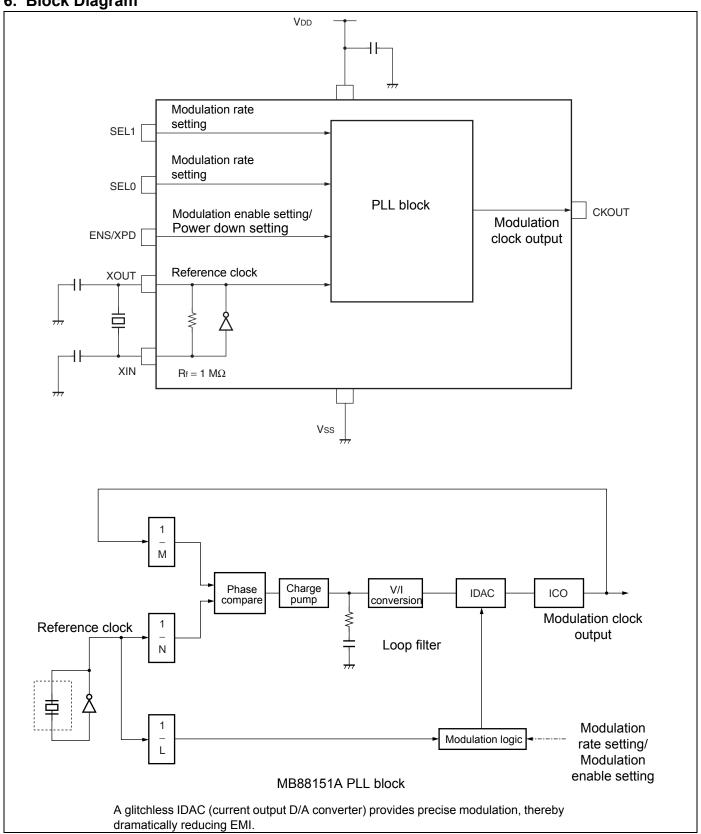

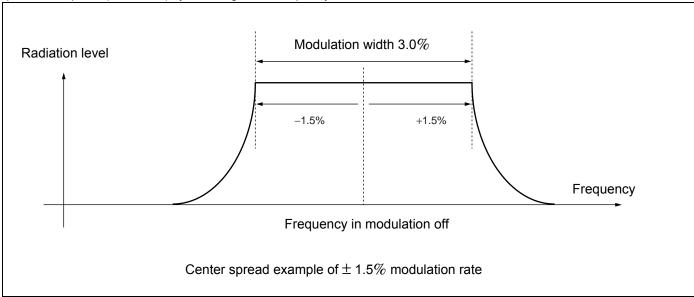

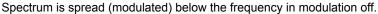

MB88151A is a clock generator for EMI (Electro Magnetic Interference) reduction. The peak of unnecessary radiation noise (EMI) can be attenuated by making the oscillation frequency slightly modulate periodically with the internal modulator. It corresponds to both of the center spread which modulates frequency in modulation off as Middle Centered and down spread which modulates so as not to exceed frequency in modulation off.

#### **Features**

|                                      | MB88151A-100<br>(Multiply-by-1)               | MB88151A-200<br>(Multiply-by-2)               |

|--------------------------------------|-----------------------------------------------|-----------------------------------------------|

| Input frequency/<br>Output frequency | 16.6 MHz to 33.4 MHz/<br>16.6 MHz to 33.4 MHz | 16.6 MHz to 33.4 MHz/<br>33.2 MHz to 66.8 MHz |

| Modulation clock cycle-cycle jitter  | Less than100 ps                               | Less than 100 ps                              |

■ Modulation rate :  $\pm 0.5\%$ ,  $\pm 1.5\%$  (Center spread), -1.0%, -3.0% (Down spread)

■ Equipped with oscillation circuit : Range of oscillation 16.6 MHz to 33.4 MHz

■ Modulation clock output Duty: 40% to 60%

■ Low current consumption by CMOS process : 5 mA (24 MHz : Typ-sample, no load)

$\blacksquare$  Power supply voltage : 3.3 V  $\pm$  0.3 V

■ Operating temperature : -40 °C to +85 °C

■ Package : SOP 8-pin

#### **Contents**

| PRODUCT LINEUP                                | 3  |

|-----------------------------------------------|----|

| PIN ASSIGNMENT                                | 3  |

| PIN DESCRIPTION                               | 3  |

| I/O CIRCUIT TYPE                              | 4  |

| HANDLING DEVICES                              | 6  |

| PREVENTING LATCH-UP                           |    |

| HANDLING UNUSED PINS                          | 6  |

| THE ATTENTION WHEN THE EXTERNAL CLOCK IS USED | 6  |

| POWER SUPPLY PINS                             | 6  |

| OSCILLATION CIRCUIT                           | 6  |

| BLOCK DIAGRAM                                 | 7  |

| PIN SETTING                                   | 8  |

| ABSOLUTE MAXIMUM RATINGS                      | 10 |

| RECOMMENDED OPERATING CONDITIONS              | 11 |

| ELECTRICAL CHARACTERISTICS               | 12 |

|------------------------------------------|----|

| OUTPUT CLOCK DUTY CYCLE (TDCC = TB/TA)   | 15 |

| INPUT FREQUENCY (FIN = 1/TIN)            | 15 |

| OUTPUT SLEW RATE (SR)                    | 15 |

| CYCLE-CYCLE JITTER (TJC =   TN - TN+1  ) | 16 |

| MODULATION WAVEFORM                      | 17 |

| LOCK-UP TIME                             | 18 |

| OSCILLATION CIRCUIT                      | 20 |

| INTERCONNECTION CIRCUIT EXAMPLE          | 21 |

| SPECTRUM EXAMPLE CHARACTERISTICS         | 22 |

| ORDERING INFORMATION                     | 23 |

| PACKAGE DIMENSION                        | 24 |

| DOCUMENT HISTORY                         | 25 |

| SALES, SOLUTIONS, AND LEGAL INFORMATION  | 26 |

### 1. Product Lineup

MB88151A has five kinds of multiplication type.

| Product      | Input Frequency Range    | Multiplier Ratio | Output Frequency Range |

|--------------|--------------------------|------------------|------------------------|

| MB88151A-100 | 16.6 MHz to 33.4 MHz     | Multiply-by-1    | 16.6 MHz to 33.4 MHz   |

| MB88151A-200 | 10.0 WH 12 to 35.4 WH 12 | Multiply-by-2    | 33.2 MHz to 66.8 MHz   |

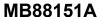

# 2. Pin Assignment

# 3. Pin Description

| Pin Name        | I/O | Pin No. | Description                                                                                      |

|-----------------|-----|---------|--------------------------------------------------------------------------------------------------|

| XIN             | I   | 1       | Resonator connection pin/clock input pin                                                         |

| Vss             |     | 2       | GND pin                                                                                          |

| SEL0            | I   | 3       | Modulation rate setting pin                                                                      |

| SEL1            | I   | 4       | Modulation rate setting pin                                                                      |

| CKOUT           | 0   | 5       | Modulated clock output pin                                                                       |

| ENS/XPD         | I   | 6       | Modulation enable setting pin (with pull-up resistance)/ Power down pin (with pull-up resistor)* |

| V <sub>DD</sub> | _   | 7       | Power supply voltage pin                                                                         |

| XOUT            | 0   | 8       | Resonator connection pin                                                                         |

<sup>\* :</sup> XPD = 800 k $\Omega$  pull-up resistor at "L"

# 4. I/O Circuit Type

| Pin           | Circuit Type       | Remarks                                                                                                                                                                 |

|---------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEL0,<br>SEL1 |                    | CMOS hysteresis input                                                                                                                                                   |

| ENS           | 50 kΩ    No. 10 kΩ | ■ With 50 kΩ pull-up resistors ■ CMOS hysteresis input                                                                                                                  |

| XPD           | 50 κΩ 800 κΩ       | <ul> <li>With 50 kΩ + 800 kΩ pull-up resistors</li> <li>Note: If "L" is input to XPD, 50 kΩ pull-up resistor is disconnected.</li> <li>CMOS hysteresis input</li> </ul> |

(Continued)

#### (Continued)

| Pin   | Circuit Type   | Remarks       |

|-------|----------------|---------------|

| CKOUT | +              | ■ CMOS output |

|       |                | ■ IoL = 4 mA  |

|       |                |               |

|       |                |               |

|       |                |               |

|       |                |               |

|       |                |               |

|       | \ <u>\</u>     |               |

|       |                |               |

|       | <del>111</del> |               |

Note: For XIN and XOUT pins, refer to "Oscillation Circuit".

#### 5. Handling Devices

#### 5.1 Preventing Latch-up

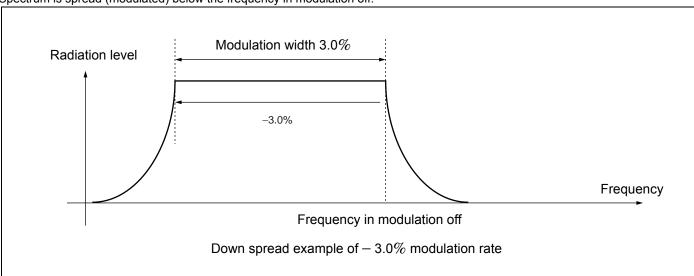

A latch-up can occur if, on this device, (a) a voltage higher than  $V_{DD}$  or a voltage lower than  $V_{SS}$  is applied to an input or output pin or (b) a voltage higher than the rating is applied between  $V_{DD}$  pin and  $V_{SS}$  pin. The latch-up, if it occurs, significantly increases the power supply current and may cause thermal destruction of an element. When you use this device, be very careful not to exceed the maximum rating.

#### 5.2 Handling Unused Pins

Do not leave an unused input pin open, since it may cause a malfunction. Handle by, using a pull-up or pull-down resistor.

Unused output pin should be opened.

#### 5.3 The Attention when the External Clock is Used

Input the clock to XIN pin, and XOUT pin should be opened when you use the external clock. Please pay attention so that an overshoot and an undershoot do not occur to an input clock of XIN pin.

#### 5.4 Power Supply Pins

Please design connecting the power supply pin of this device by as low impedance as possible from the current supply source.

We recommend connecting electrolytic capacitor (about 10  $\mu$ F) and the ceramic capacitor (about 0.01  $\mu$ F) in parallel between Vss pin and VDD pin near the device, as a bypass capacitor.

#### 5.5 Oscillation Circuit

Noise near the XIN and XOUT pins may cause the device to malfunction. Design printed circuit boards so that electric wiring of XIN or XOUT pin and the resonator do not intersect other wiring.

Design the printed circuit board that surrounds the XIN and XOUT pins with ground.

Document Number: 002-08311 Rev. \*B

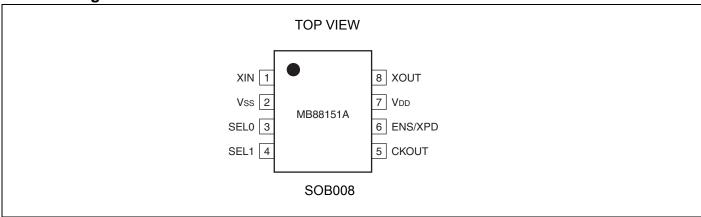

# 6. Block Diagram

# 7. Pin Setting

When changing the pin setting, the stabilization wait time for the modulation clock is required. The stabilization wait time for the modulation clock take the maximum value of "Electrical Characteristics AC Characteristics Lock-up time".

#### **ENS Modulation Enable Setting (MB88151A-100/200)**

| ENS | Modulation    |

|-----|---------------|

| L   | No modulation |

| Н   | Modulation    |

Note: Spectrum does not spread when "L" is set to ENS. The clock with low jitter can be obtained. Because of ENS has Pull-up resistance, spectrum spread when "H" is set to it or open the terminal.

#### SEL0, SEL1 Modulation Rate Setting

| SEL1 | SEL0 | Modulation Rate | Modulation Type |

|------|------|-----------------|-----------------|

| L    | L    | ± 1.5%          | Center spread   |

| L    | Н    | ± 0.5%          | Center spread   |

| Н    | L    | - 1.0%          | Down spread     |

| Н    | Н    | - 3.0%          | Down spread     |

Note: The modulation rate can be changed at the level of the terminal.

Document Number: 002-08311 Rev. \*B Page 8 of 26

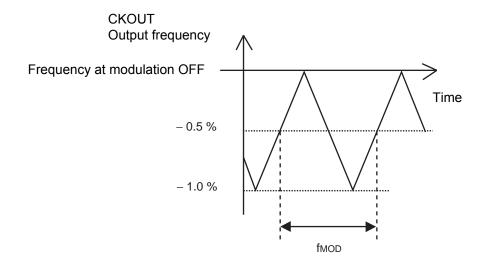

#### ■ Center Spread

#### ■ Down Spread

### 8. Absolute Maximum Ratings

| Parameter                      | Symbol          | Rat                      | Unit                                  |       |  |

|--------------------------------|-----------------|--------------------------|---------------------------------------|-------|--|

| Farameter                      | Symbol          | Min                      | Max                                   | Oille |  |

| Power supply voltage*          | V <sub>DD</sub> | - 0.5                    | +4.0                                  | V     |  |

| Input voltage*                 | Vı              | Vss - 0.5                | V <sub>DD</sub> + 0.5                 | V     |  |

| Output voltage*                | Vo              | Vss - 0.5                | V <sub>DD</sub> + 0.5                 | V     |  |

| Storage temperature            | Тѕт             | <b>–</b> 55              | + 125                                 | °C    |  |

| Operation junction temperature | TJ              | <b>-40</b>               | + 125                                 | °C    |  |

| Output current                 | lo              | <del>- 14</del>          | + 14                                  | mA    |  |

| Overshoot                      | Viover          | _                        | V <sub>DD</sub> + 1.0 (tover ≤ 50 ns) | V     |  |

| Undershoot                     | Viunder         | Vss-1.0 (tunder ≤ 50 ns) | _                                     | V     |  |

$<sup>^{\</sup>star}$  : The parameter is based on  $V_{\text{SS}} = 0.0 \ \text{V}.$

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

### 9. Recommended Operating Conditions

(Vss = 0.0 V)

| Parameter               | Symbol          | Pin                   | Conditions              |                       | Unit |                       |       |

|-------------------------|-----------------|-----------------------|-------------------------|-----------------------|------|-----------------------|-------|

|                         |                 |                       |                         | Min                   | Тур  | Max                   | Offic |

| Power supply voltage    | V <sub>DD</sub> | V <sub>DD</sub>       | _                       | 3.0                   | 3.3  | 3.6                   | V     |

| "H" level input voltage | ViH             | XIN,                  | _                       | V <sub>DD</sub> × 0.8 | _    | V <sub>DD</sub> + 0.3 | V     |

| "L" level input voltage | VıL             | SEL0,<br>SEL1,<br>ENS | _                       | Vss                   | _    | V <sub>DD</sub> × 0.2 | V     |

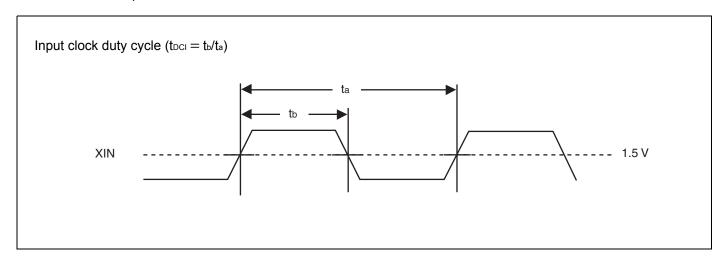

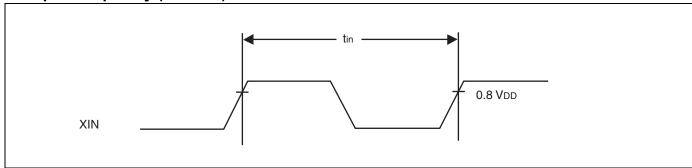

| Input clock duty cycle  | <b>t</b> DCI    | XIN                   | 16.6 MHz to<br>33.4 MHz | 40                    | 50   | 60                    | %     |

| Operating temperature   | Та              | _                     | _                       | - 40                  | _    | + 85                  | °C    |

WARNING:

The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure. No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

### 10. Electrical Characteristics

#### ■ DC Characteristics

(Ta = - 40 °C to  $\,+$  85 °C, VDD = 3.3 V  $\pm$  0.3 V, Vss = 0.0 V)

| Parameter                | Symbol   | Pin                                                   | Conditions                                                        |                       | Value |                 | Unit  |

|--------------------------|----------|-------------------------------------------------------|-------------------------------------------------------------------|-----------------------|-------|-----------------|-------|

| Faiailletei              | Syllibol | FIII                                                  | Conditions                                                        | Min                   | Тур   | Max             | Oille |

| Power supply current     | Icc      | VDD No load capacitance at output 24 MHz MB88151A-100 |                                                                   | _                     | 5.0   | 7.0             | mA    |

| Output voltage           | Vон      | CKOUT                                                 | "H" level output, $I_{OH} = -4 \text{ mA}$                        | V <sub>DD</sub> - 0.5 | _     | V <sub>DD</sub> | V     |

|                          | Vol      | CKOUT                                                 | "L" level output,<br>loL = 4 mA                                   | Vss                   | _     | 0.4             | V     |

| Output impedance         | Zo       | CKOUT                                                 | 16.6 MHz to 66.8 MHz                                              | _                     | 45    | _               | Ω     |

| Input capacitance        | Cin      | XIN,<br>SEL0,<br>SEL1,<br>ENS                         | $Ta = +25 ^{\circ}C,$<br>$V_{DD} = V_{I} = 0.0  V,$<br>f = 1  MHz | _                     | _     | 16              | pF    |

| Load capacitance         | C∟       | CKOUT                                                 | 16.6 MHz to 66.8 MHz                                              | _                     | _     | 15              | pF    |

| Input pull-up resistance | RPUE     | ENS                                                   | V1L = 0.0 V                                                       | 25                    | 50    | 200             | kΩ    |

|                          | Rpup     | XPD                                                   | VIL = 0.0 V                                                       | 500                   | 800   | 1200            | K22   |

#### ■ AC Characteristics

(Ta = - 40 °C to  $\,+$  85 °C, VDD = 3.3 V  $\pm$  0.3 V, Vss = 0.0 V)

| Parameter                                                       | Symbol Pin     | Din                | Conditions                                                                              | Value              |                    |                    | Unit          |  |

|-----------------------------------------------------------------|----------------|--------------------|-----------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|---------------|--|

| Parameter                                                       |                | PIII               | Conditions                                                                              | Min                | Тур                | Max                | Oilit         |  |

| Oscillation frequency                                           | fx             | XIN,<br>XOUT       | Fundamental oscillation                                                                 | 8.3                | _                  | 33.4               | MHz           |  |

| Input frequency                                                 | fin            | XIN                | External clock input (multiply-by-1, 2)                                                 | 16.6               | _                  | 33.4               | MHz           |  |

| Output frequency                                                | four           | fоит <b>СКОU</b> T | MB88151A-100<br>(Multiply by 1)                                                         | 16.6               | _                  | 33.4               | MHz           |  |

|                                                                 | 1001           |                    | MB88151A-200<br>(Multiply by 2)                                                         | 33.2               | _                  | 66.8               | IVITIZ        |  |

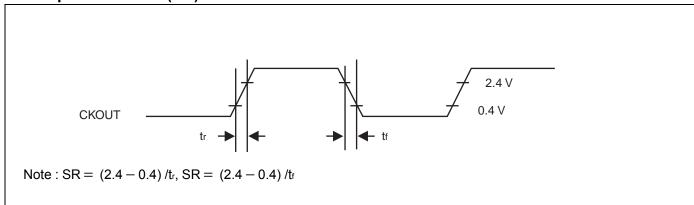

| Output slew rate                                                | SR             | СКОИТ              | 0.4 V to 2.4 V<br>Load capacitance 15 pF                                                | 0.4                | _                  | 4.0                | V/ns          |  |

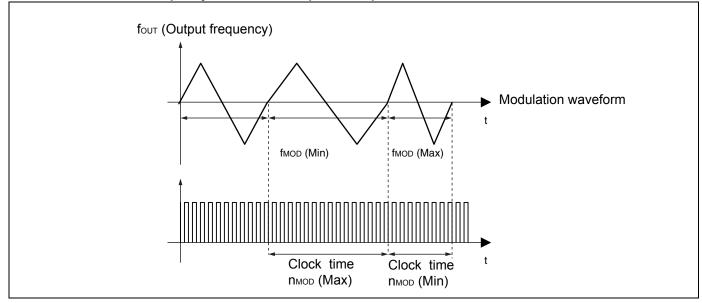

| Output clock duty cycle                                         | <b>t</b> DCC   | CKOUT              | 1.5 V                                                                                   | 40                 | _                  | 60                 | %             |  |

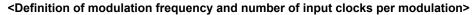

| Modulation period<br>(Number of input clocks<br>per modulation) | fмор<br>(nмор) | CKOUT              | MB88151A-100,<br>MB88151A-200                                                           | fin/2200<br>(2200) | fin/1900<br>(1900) | fin/1600<br>(1600) | kHz<br>(clks) |  |

| Lock-up time                                                    | <b>t</b> LK    | CKOUT              | 16.6 MHz to 66.8 MHz                                                                    | _                  | 2                  | 5                  | ms            |  |

| Cycle-cycle jitter                                              | tuc            | CKOUT              | MB88151A-100<br>MB88151A-200<br>No load capacitance,<br>$Ta = +25$ °C, $V_{DD} = 3.3$ V |                    |                    | 100                | ps-rms        |  |

Note: The modulation clock stabilization wait time is required after the power is turned on, the IC recovers from power saving, or after FREQ (frequency range) or ENS (modulation ON/OFF) setting is changed. For the modulation clock stabilization wait time, assign the maximum value for lock-up time.

Document Number: 002-08311 Rev. \*B Page 13 of 26

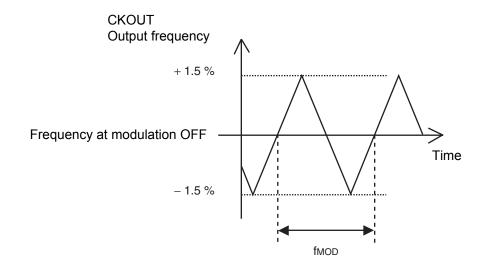

MB88151A contains the modulation period to realize the efficient EMI reduction.

The modulation period fmod depends on the input frequency and changes between fmod (Min) and fmod (Max).

Furthermore, the average value of fMOD equals the typical value of the electrical characteristics.

# 11. Output Clock Duty Cycle ( $t_{DCC} = t_b/t_a$ )

# 12. Input Frequency ( $f_{in} = 1/t_{in}$ )

# 13. Output Slew Rate (SR)

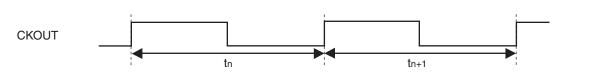

# 14. Cycle-cycle Jitter ( $t_{JC} = |t_n - t_{n+1}|$ )

Note: Cycle-cycle jitter is defined the difference between a certain cycle and immediately after (or, immediately before).

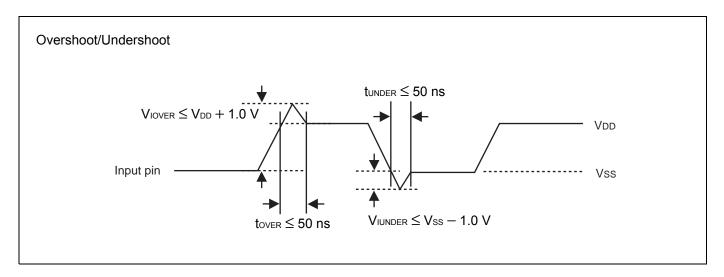

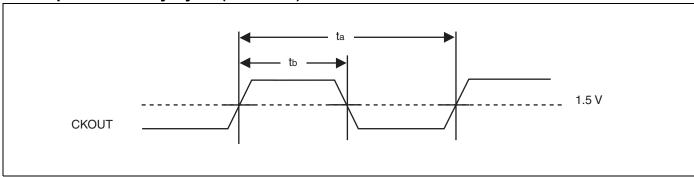

#### 15. Modulation Waveform

■ ±1.5% modulation rate, Example of center spread

■ -1.0% modulation rate, Example of down spread

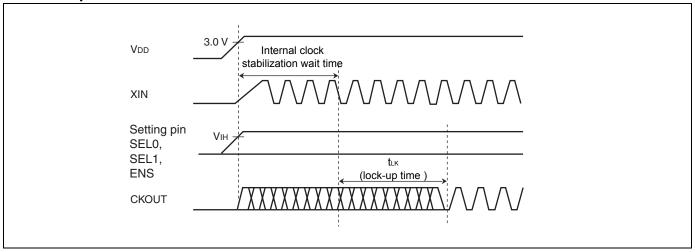

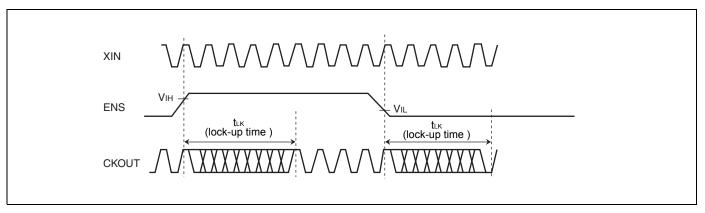

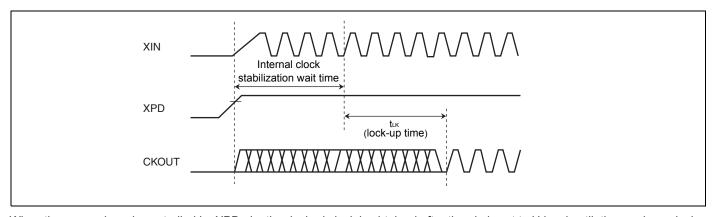

### 16. Lock-up Time

If the setting pin is fixed at the "H" or "L" level, the maximum time after the power is turned on until the set clock signal is output from CKOUT pin is (the stabilization wait time of input clock to XIN pin) + (the lock-up time "tlk"). For the input clock stabilization time, check the characteristics of the resonator or oscillator used.

For modulation enable control using the ENS pin during normal operation, the set clock signal is output from CKOUT pin at most the lock-up time (tlk) after the level at the ENS pin is determined.

Note: When the pin setting is changed, the CKOUT pin output clock stabilization time is required. Until the output clock signal becomes stable, the output frequency, output clock duty cycle, modulation period, and cycle-cycle jitter cannot be guaranteed. It is therefore advisable to perform processing such as cancelling a reset of the device at the succeeding stage after the lock-up time.

When the power down is controlled by XPD pin, the desired clock is obtained after the pin is set to H level until the maximum lock-up time  $t_{\rm LK}$  is elapsed.

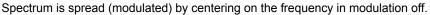

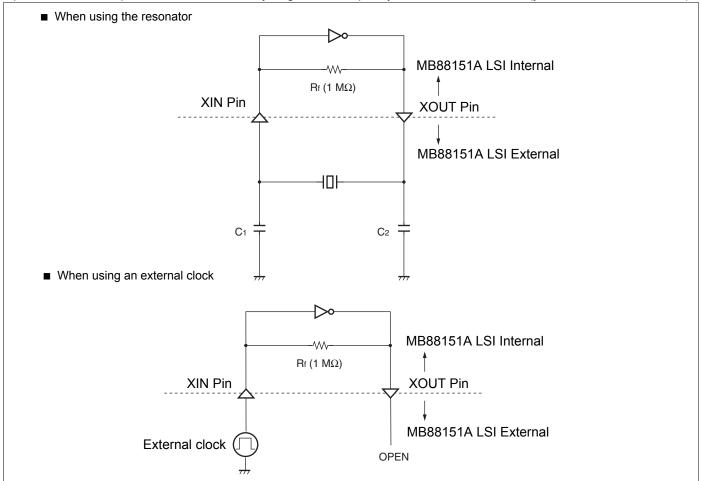

#### 17. Oscillation Circuit

The figure below shows the connection example about general resonator. The oscillation circuit has the built-in resistance (Rf). The value of capacity ( $C_1$  and  $C_2$ ) is required adjusting to the most suitable value of individual resonator.

The most suitable value is different by individual resonator. Please refer to the resonator manufacturer which you use for the most suitable value.

Input the clock to XIN pin, and do not connect anything with XOUT pin if you use the external clock (you do not use the resonator).

Note: Note that a jitter characteristic of an input clock may cause an affect a cycle-cycle jitter characteristic.

Document Number: 002-08311 Rev. \*B

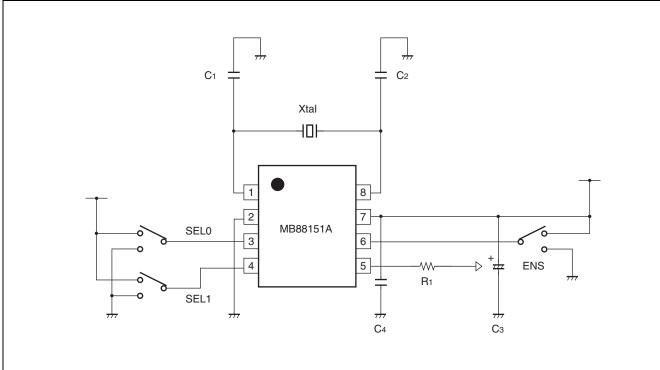

### 18. Interconnection Circuit Example

$C_1,\,C_2$  : Oscillation stabilization capacitance (refer to "Oscillation Circuit".)

$C_3$ : Capacitor of 10  $\mu F$  or higher

$C_4$  : Capacitor about 0.01  $\mu F$  (connect a capacitor of good high frequency

property (ex. laminated ceramic capacitor) to close to this device.)

R<sub>1</sub>: Impedance matching resistor for board pattern

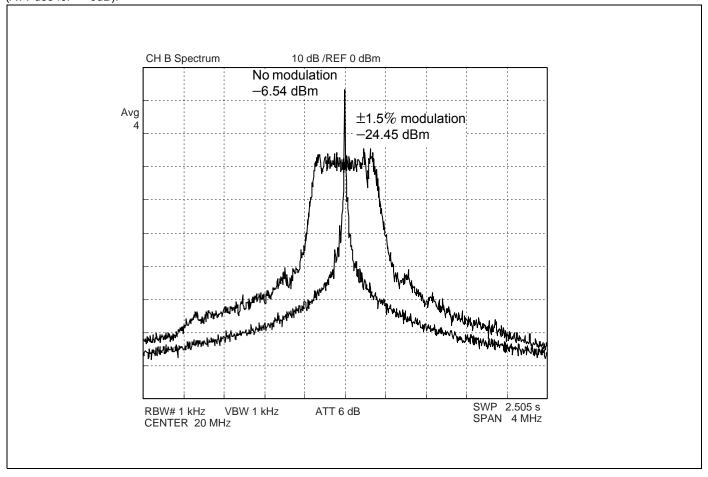

### 19. Spectrum Example Characteristics

The condition of the examples of the characteristic is shown as follows : Input frequency = 20 MHz (Output frequency = 20 MHz : Using MB88151A-100 (Multiply-by-1)), Power - supply voltage = 3.3 V, None load capacity, Modulation rate =  $\pm 1.5\%$  (center spread).

Spectrum analyzer HP4396B is connected with CKOUT. The result of the measurement with RBW = 1 kHz (ATT use for -6dB).

# 20. Ordering Information

| Part Number              | Input Frequency<br>Range | Multiplier<br>Ratio | Output Frequency<br>Range | Package                          | Remarks                       |

|--------------------------|--------------------------|---------------------|---------------------------|----------------------------------|-------------------------------|

| MB88151APNF-G-100-JNE1   | 16.6 MHz to              | Multiply-<br>by-1   | 16.6 MHz to 33.4 MHz      | 8-pin plastic<br>SOP<br>(SOB008) |                               |

| MB88151APNF-G-200-JNE1   | 33.4 MHz                 | Multiply-<br>by-2   | 33.2 MHz to 66.8 MHz      |                                  |                               |

| MB88151APNF-G-100-JNEFE1 | 16.6 MHz to              | Multiply-<br>by-1   | 16.6 MHz to 33.4 MHz      |                                  | Emboss<br>taping<br>(EF type) |

| MB88151APNF-G-200-JNEFE1 | 33.4 MHz                 | Multiply-<br>by-2   | 33.2 MHz to 66.8 MHz      |                                  |                               |

| MB88151APNF-G-100-JNERE1 | 16.6 MHz to              | Multiply-<br>by-1   | 16.6 MHz to 33.4 MHz      |                                  | Emboss<br>taping<br>(ER type) |

| MB88151APNF-G-200-JNERE1 | 33.4 MHz                 | Multiply-<br>by-2   | 33.2 MHz to 66.8 MHz      |                                  |                               |

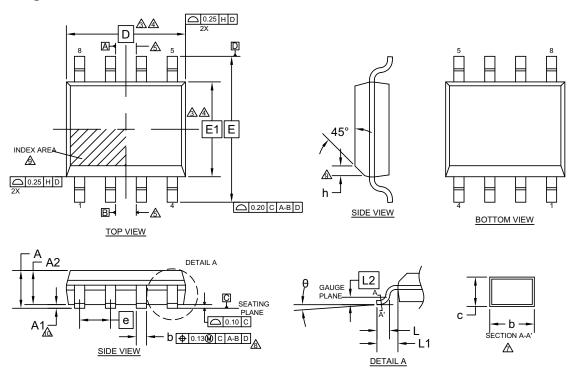

### 21. Package Dimension

| SYMBOL   | DIMENSIONS |      |      |  |  |

|----------|------------|------|------|--|--|

| STIVIBOL | MIN.       | NOM. | MAX. |  |  |

| Α        | _          | _    | 1.75 |  |  |

| A1       | 0.05       |      | 0.25 |  |  |

| A2       | 1.30       | 1.40 | 1.50 |  |  |

| D        | 5.05 BSC.  |      |      |  |  |

| E        | 6.00 BSC.  |      |      |  |  |

| E1       | 3.90 BSC   |      |      |  |  |

| θ        | 0°         |      | 8°   |  |  |

| С        | 0.15       | _    | 0.25 |  |  |

| b        | 0.36       | 0.44 | 0.52 |  |  |

| L        | 0.45       | 0.60 | 0.75 |  |  |

| L 1      | 1.05 REF   |      |      |  |  |

| L 2      | 0.25 BSC   |      |      |  |  |

| е        | 1.27 BSC.  |      |      |  |  |

| h        | 0.40 BSC.  |      |      |  |  |

#### NOTES

- 1. ALL DIMENSIONS ARE IN MILLIMETER.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- ⚠ DIMENSIONING D INCLUDE MOLD FLASH, DIMENSIONING E1 DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.025 mm PER SIDE. D and E1 DIMENSION ARE DETERMINED AT DATUM H.

- ATHE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM.

DIMENSIONING D and E1 ARE DETERMINED AT THE OUTERMOST

EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH,

THE BAR BURRS, GATE BURRS AND INTERLEAD FLASH, BUT INCLUDING

ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.

- ⚠ DATUMS A & B TO BE DETERMINED AT DATUM H.

- "N" IS THE MAXIMUM NUMBER OF TERMINAL POSITIONS FOR THE SPECIFIED PACKAGE LENGTH.

- THE DIMENSION APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10 mm TO 0.25mm FROM THE LEAD TIP.

- ⚠ DIMENSION "b" DOES NOT INCLUDE THE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.10mm TOTAL IN EXCESS OF THE "b" DIMENSION AT MAXIMUM MATERIAL CONDITION.

- THE DAMBAR MAY NOT BE LOCATED ON THE LOWER RADIUS OF THE FOOT.

- THIS CHAMFER FEATURE IS OPTIONAL. LF IT IS NOT PRESENT, THEN A PIN 1 IDENTIFIER MUST BE LOCATED WITHIN THE INDEX AREA INDICATED

- /1Ò, "A1" IS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY EXCLUDING THE LID AND OR THERMAL ENHANCEMENT ON CAVITY DOWN PACKAGE CONFIGURATIONS.

- 11. JEDEC SPECIFICATION NO. REF: N/A

002-15856 Rev.\*\*

### **Document History**

**Spansion Publication Number: DS04-29127-3E**

| Document Title: MB88151A Spread Spectrum Clock Generator Document Number: 002-08311 |         |                    |                    |                                                                                                                                                                                     |  |

|-------------------------------------------------------------------------------------|---------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision                                                                            | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                               |  |

| **                                                                                  | _       | TAOA               | 06/29/2009         | Initial Release                                                                                                                                                                     |  |

| *A                                                                                  | 5569547 | TAOA               | 12/30/2016         | Updated to Cypress Template                                                                                                                                                         |  |

| *B                                                                                  | 5993569 | TAOA               | 12/18/2017         | Deleated EOL part number: MB88151A-101/201/400/401/500/501/800/801<br>Updated Package Dimensions: Updated to Cypress format.<br>Changed the package name from FPT-8P-M02 to SOB008. |  |

#### Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

ARM® Cortex® Microcontrollers

Automotive

Clocks & Buffers

Interface

Internet of Things

cypress.com/automotive

cypress.com/clocks

cypress.com/interface

cypress.com/interface

Memory cypress.com/memory

Microcontrollers cypress.com/mcu

PSoC cypress.com/psoc

#### PSoC® Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2007-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress parally a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 002-08311 Rev. \*B Revised December 18, 2017 Page 26 of 26