SLWS107A - JUNE 2000 - REVISED OCTOBER 2000

- Complete Discrete Multitone-Based Asymmetric Digital Subscriber Line Coder/Decoder

- Supports Full Rate ADSL and G.Lite Application in Both Echo Cancellation or FDM Modes

- Integrated 14-Bit Converter for Transmitter/Receiver

- Integrated Transmit/Receive Channel Filters

- Integrated Transmit/Receive Attenuation/Gain

- Integrated Reference

- High-Speed Parallel Interface

- 16-Bit 2s-Complement Data Format

- Selectable Parallel Data Transfer Rate

- Serial Configuration Port

- Eight General-Purpose Output Terminals

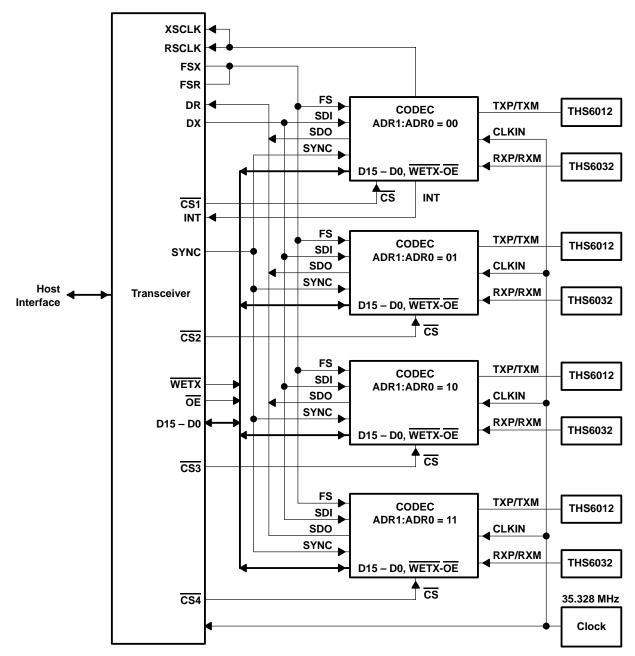

- Supports Multiple-Channel Configuration

- Single 3.3-V Supply

- Low Power Consumption, –450 mW at External Bias Mode

- -40°C to 85°C Operational Temperature

- Hardware/Software Power Down

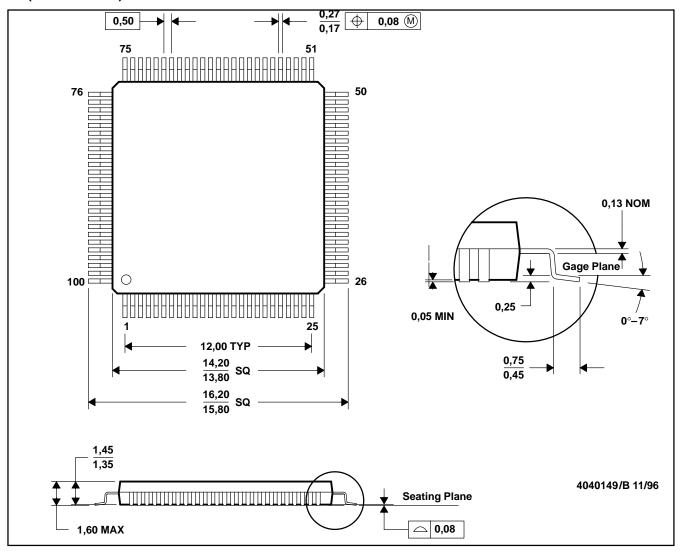

- 100-Terminal LQFP (PZ) Package

# description

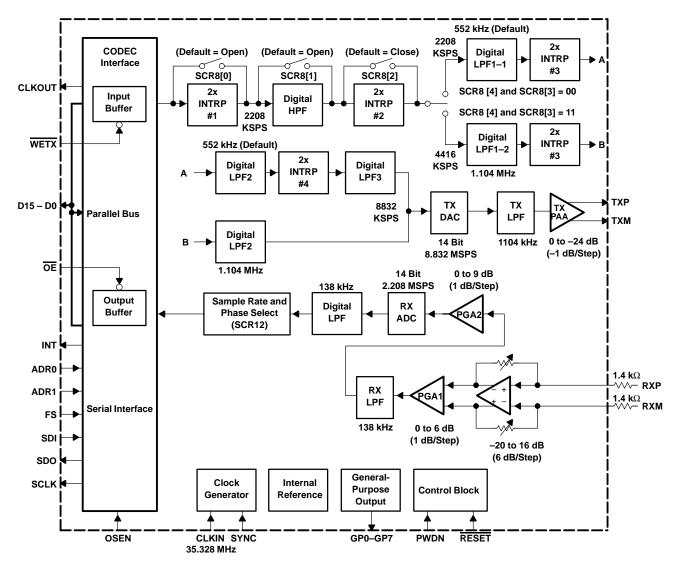

The TLV320AD16 is a high-speed coder/decoder (codec) for a central office-side (CO) discrete-multitone-based (DMT) asymmetric-digital subscriber line (ADSL) access that supports full rate ADSL, G.lite, and reduced-NEXT (near end cross talk) digital-filter FDM applications. The codec is a low-power device comprised of five functional blocks: transmitter (TX), receiver (RX), clock, reference, and host interface.

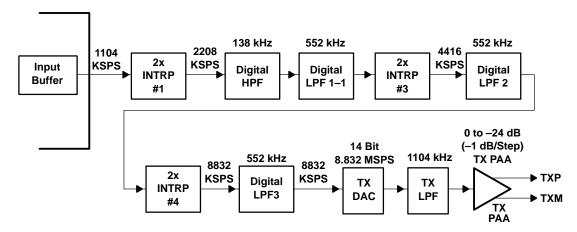

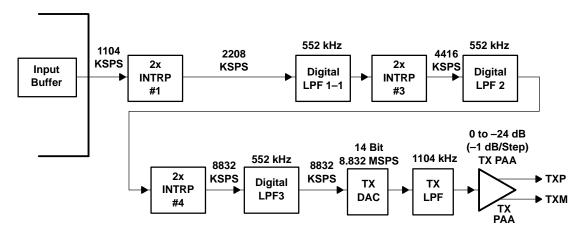

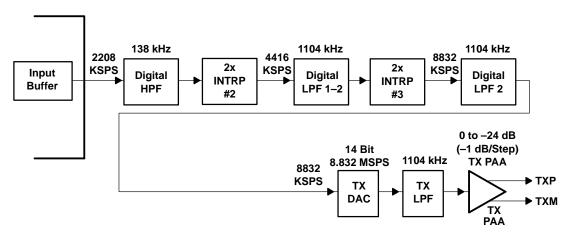

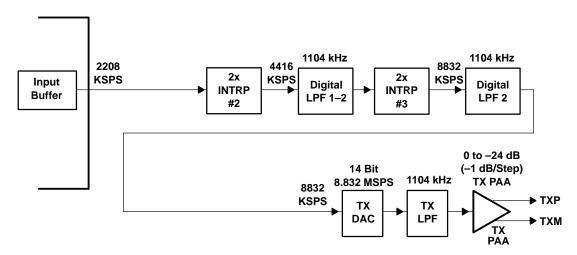

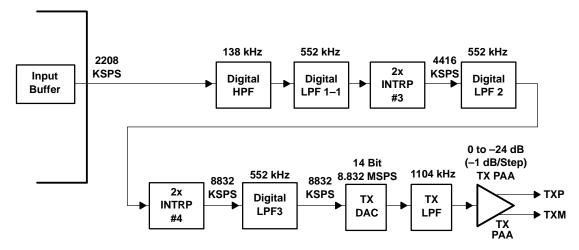

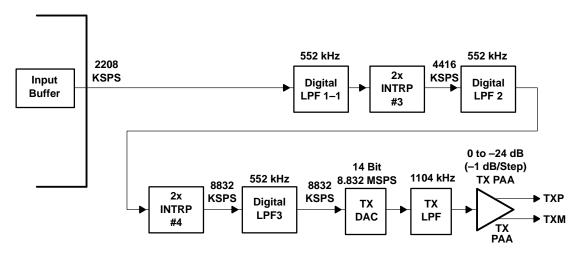

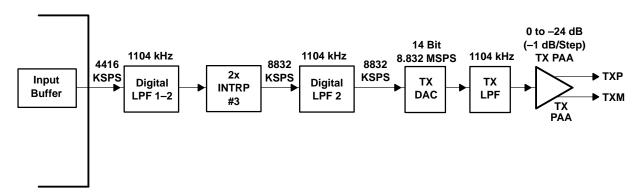

The transmit channel consists of selectable digital filters, a 14-bit, 8.832-MSPS DAC, a 1.104-MHz analog low-pass filter, and a transmit attenuator. The receiver channel consists of a three programmable-gain-amplifier stages (PGA), a 138-kHz analog low-pass filter (LPF), a 14-bit, 2.208-MSPS ADC, and a 138-kHz digital LPF. The sample phase and rate can be software selected. An onboard reference circuit generates 1.5-V reference voltage for the converters.

The codec has two interface ports: a parallel port for data transfer and a serial port for control. The parallel port is 16 bits wide, and is reserved for moving data between the codec and the host transceiver, such as the TMS320C6XX. Configuration is done via the serial port. A special interface scheme enables multichannel system design. The TLV320AD16 can be powered down via a dedicated terminal or through software control to reduce heat dissipation. Additionally, there is a general-purpose (GP) port consisting of eight output terminals for control of external circuitry.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

MicroStar Junior is a trademark of Texas Instruments.

#### (TOP VIEW) NC NC NC NC AVSS\_DAC2\_ COMPB\_DAC\_ ADRO PWDN RESET CS ADR1 NC□ 50 NC□ 77 □ NC 49 NC□ □ WETX 78 48 NC□ 79 □ DVDD\_LG 47 NC□ 80 □ DVSS\_LG 46 SYNC $\mathsf{TXP} \square$ 81 45 $TXM \square$ 82 $\square$ $\mathsf{DVDD}_\mathsf{CLK}$ 44 AVDD FIL TX 43 DVSS\_CLK AVSS\_FIL\_TX ☐ CLKIN NC□ 85 41 CLKOUT AVDD\_REF 86 40 🗆 INT AVSS\_REF□ 87 39 DSEN REFP□ 88 38 🗆 FS REFM□ □ SCLK 89 37 VMID REF 90 □ SDI 36 IEXTERN □ 91 35 □ SDO Vss □ 92 □ D15 34 AVDD\_FIL\_RX □ D14 93 33 AVSS\_FIL\_RX [ □ D13 94 32 $RXP \square$ 95 31 □ D12 □ D11 RXM96 30 □ D10 NC□ 97 29 28 🗖 D9 NC ☐ 98 NC ☐ 99 DVSS\_BF 27 NC□ 100 🔾 26 DVDD\_BF VMID\_ADC AVDD\_ADC AVSS\_ADC AVSS\_ADC DVSS\_RX DVSS\_RX DVS\_RX DVS B GP0 GP1 GP2 GP3 GP4 GP6 GP6

**PZ PACKAGE**

NC - No internal connection

# functional block diagram

NOTE: SCR8 and SCR12 are system control registers (see register programming for details).

# **Terminal Functions**

| TERMINAL                                           |                                                                                  |      |                                                                                                                       |  |  |  |  |

|----------------------------------------------------|----------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME NO.                                           |                                                                                  | 1/0† | DESCRIPTION                                                                                                           |  |  |  |  |

| NAME                                               | PZ                                                                               |      |                                                                                                                       |  |  |  |  |

| ADR0<br>ADR1                                       | 54<br>55                                                                         | ı    | Serial-port chip ID address. ADR0 is the least significant bit. See multiple-channel configuration for detail.        |  |  |  |  |

| AVDD_ADC                                           | 12                                                                               | I    | Analog-to-digital converter (ADC) analog power supply                                                                 |  |  |  |  |

| AVDD_DAC1_TX                                       | 66                                                                               | I    | TX-channel analog power supply 1                                                                                      |  |  |  |  |

| AVDD_DAC2_TX                                       | 70                                                                               | ı    | TX-channel analog power supply 2                                                                                      |  |  |  |  |

| AVDD_FIL_RX                                        | 93                                                                               | ı    | RX-channel filter analog power supply                                                                                 |  |  |  |  |

| AVDD_FIL_TX                                        | 83                                                                               | ı    | TX-channel filter analog power supply                                                                                 |  |  |  |  |

| AVDD_REF                                           | 86                                                                               | ı    | Reference analog power supply                                                                                         |  |  |  |  |

| AVSS                                               | 14                                                                               | ı    | Analog ground                                                                                                         |  |  |  |  |

| AVSS_ADC                                           | 13                                                                               | ı    | ADC analog ground                                                                                                     |  |  |  |  |

| AVSS_DAC1_TX                                       | 67                                                                               | ı    | TX-channel analog ground 1                                                                                            |  |  |  |  |

| AVSS_DAC2_TX                                       | 71                                                                               | ı    | TX-channel analog ground 2                                                                                            |  |  |  |  |

| AVSS_FIL_RX                                        | 94                                                                               | Τ    | RX-channel filter analog ground                                                                                       |  |  |  |  |

| AVSS_FIL_TX                                        | 84                                                                               | Τ    | TX-channel filter analog ground                                                                                       |  |  |  |  |

| AVSS_REF                                           | 87                                                                               | ı    | Reference analog ground                                                                                               |  |  |  |  |

| CLKIN                                              | 42                                                                               | T    | 35.328-MHz external oscillator clock input                                                                            |  |  |  |  |

| CLKOUT                                             | 41                                                                               | 0    | RX channel digital interface data rate indicator of Rx internal buffer                                                |  |  |  |  |

| COMPA_DAC_TX                                       | 68                                                                               | ı    | TX-channel decoupling capacitor input A (add 500 pF X7R ceramic capacitor between this terminal and AVDD_DAC1_TX)     |  |  |  |  |

| COMPB_DAC_TX                                       | 69                                                                               | I    | TX-channel decoupling capacitor input B (add 1- $\mu$ F X7R ceramic capacitor between this terminal and AVDD_DAC1_TX) |  |  |  |  |

| CS                                                 | 51                                                                               | ı    | Parallel-port chip select from host processor                                                                         |  |  |  |  |

| D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 | 34<br>33<br>32<br>31<br>30<br>29<br>28<br>25<br>24<br>23<br>22<br>21<br>20<br>19 | 1/0  | (MSB)  Parallel-port data. D0 is the least significant bit.                                                           |  |  |  |  |

| D0                                                 | 17                                                                               |      | (LSB)                                                                                                                 |  |  |  |  |

| DVDD_BF                                            | 26                                                                               |      | Digital I/O buffer power supply                                                                                       |  |  |  |  |

| DVDD_CLK                                           | 44                                                                               | ı    | Digital clock power supply                                                                                            |  |  |  |  |

| DVDD_DAC                                           | 57                                                                               | ı    | Digital power supply for digital-to-analog converter (DAC)                                                            |  |  |  |  |

| DVDD_LG                                            | 47                                                                               | ı    | Digital logic power supply                                                                                            |  |  |  |  |

| DVDD_RX                                            | 15                                                                               | I    | Digital power supply for RX channel                                                                                   |  |  |  |  |

| DVSS                                               | 9                                                                                | I    | Digital ground                                                                                                        |  |  |  |  |

| DVSS_BF                                            | 27                                                                               | ı    | Digital I/O buffer ground                                                                                             |  |  |  |  |

| DVSS_CLK                                           | 43                                                                               | ı    | Digital clock ground                                                                                                  |  |  |  |  |

<sup>†</sup> I = input, O = output, I/O = 3-state input/output

# **Terminal Functions**

| TERMINAL |                                                                                                                  |      |                                                                                                                                                                                                |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|          | NO.                                                                                                              | 1/0† | DESCRIPTION                                                                                                                                                                                    |  |  |  |  |

| NAME     | PZ                                                                                                               | 1    |                                                                                                                                                                                                |  |  |  |  |

| DVSS_DAC | 56                                                                                                               | ı    | Digital ground for DAC                                                                                                                                                                         |  |  |  |  |

| DVSS_LG  | 46                                                                                                               | ı    | Digital logic ground                                                                                                                                                                           |  |  |  |  |

| DVSS_RX  | 16                                                                                                               | ı    | Digital ground for RX channel                                                                                                                                                                  |  |  |  |  |

| FS       | 38                                                                                                               | ı    | Frame sync input for serial interface                                                                                                                                                          |  |  |  |  |

| GP7      | 8                                                                                                                |      |                                                                                                                                                                                                |  |  |  |  |

| GP6      | 7                                                                                                                |      |                                                                                                                                                                                                |  |  |  |  |

| GP5      | 6                                                                                                                |      |                                                                                                                                                                                                |  |  |  |  |

| GP4      | 5                                                                                                                | 0    | General-purpose output port                                                                                                                                                                    |  |  |  |  |

| GP3      | 4                                                                                                                |      |                                                                                                                                                                                                |  |  |  |  |

| GP2      | 3                                                                                                                |      |                                                                                                                                                                                                |  |  |  |  |

| GP1      | 2                                                                                                                |      |                                                                                                                                                                                                |  |  |  |  |

| GP0      | 1                                                                                                                |      |                                                                                                                                                                                                |  |  |  |  |

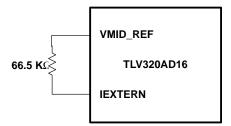

| IEXTERN  | 91                                                                                                               | I    | External bias current input. Used in external bias mode only. See voltage reference section for detail.                                                                                        |  |  |  |  |

| INT      | 40                                                                                                               | 0    | Transmit channel digital interface data rate indicator. Indicates the update rate of the internal transmit buffer.                                                                             |  |  |  |  |

| NC       | 10, 49, 59,<br>60, 61, 62,<br>63, 64, 65,<br>72, 73, 74,<br>75, 76, 77,<br>78, 79, 80,<br>85, 97, 98,<br>99, 100 |      | No connection. All the NC terminals should be left open.                                                                                                                                       |  |  |  |  |

| ŌĒ       | 50                                                                                                               | I    | Parallel-port output enable for receive channel from host processor                                                                                                                            |  |  |  |  |

| OSEN     | 39                                                                                                               | ı    | Hardware configuration: OSEN = 1 enables oversampling mode for the TX channel and the interface data rate needs to be doubled. The default state is low.                                       |  |  |  |  |

| PWDN     | 53                                                                                                               | ı    | Hardware power-down input. When PWDN = 1, the device is in the hardware power-down mode. The default state is low.                                                                             |  |  |  |  |

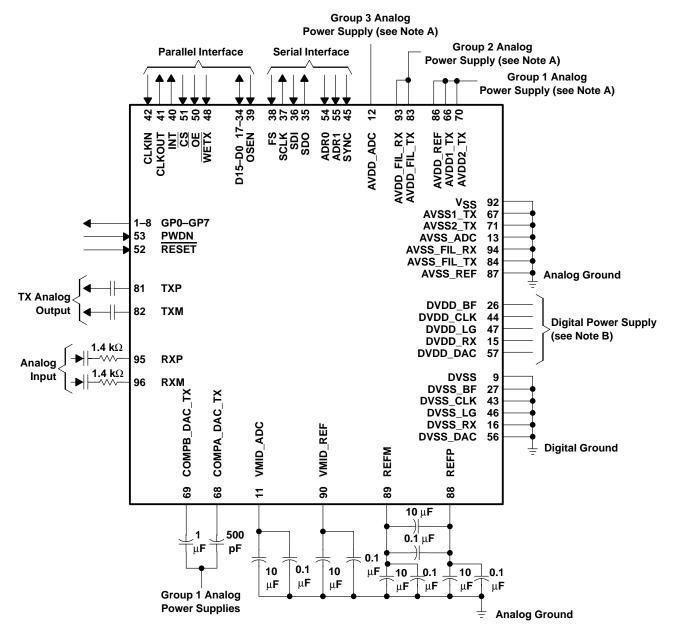

| REFM     | 89                                                                                                               | 0    | Decoupling reference voltage minus. Add 10-μF X5R and 0.1-μF X7R ceramic capacitors to AVSS_REF and REFP. The normal dc voltage at this terminal is 0.5 V. See Figure18 for the configuration. |  |  |  |  |

| REFP     | 88                                                                                                               | 0    | Decoupling reference voltage plus. Add 10-μF X5R and 0.1-μF X7R ceramic capacitors to AVSS_REF and REFM. The normal dc voltage at this terminal is 2.5 V. See Figure 18 for the configuration. |  |  |  |  |

| RESET    | 52                                                                                                               | ı    | Hardware system reset. A low level pulse will reset the device to its default state.                                                                                                           |  |  |  |  |

| RXM      | 96                                                                                                               | I    | Analog input minus for the Rx channel. RXM is self-biased to AVDD_FIL_RX/2. A 1.4 k $\Omega$ series resister is needed for the input.                                                          |  |  |  |  |

| RXP      | 95                                                                                                               | I    | Analog input plus for the Rx channel. RXP is self-biased to AVDD_FIL_RX/2.A 1.4 k $\Omega$ series resister is needed for the input.                                                            |  |  |  |  |

| SCLK     | 37                                                                                                               | 0    | Clock output for serial interface                                                                                                                                                              |  |  |  |  |

| SDI      | 36                                                                                                               | 1    | Data input for serial interface                                                                                                                                                                |  |  |  |  |

| SDO      | 35                                                                                                               | 0    | Data output for serial interface                                                                                                                                                               |  |  |  |  |

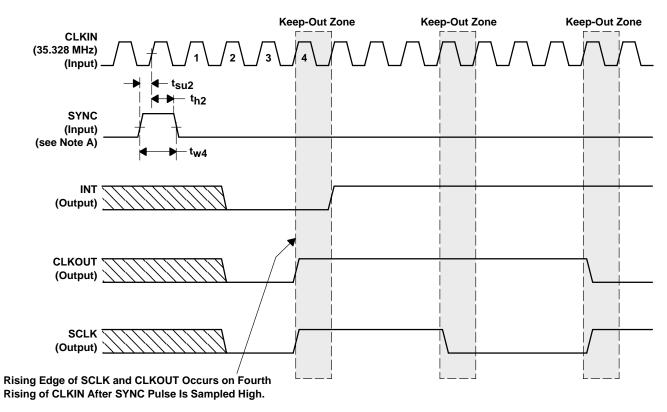

| SYNC     | 45                                                                                                               | I    | SYNC pulse for INT synchronization. A high pulse to this terminal synchronizes the clock operation. Refer to Figure 3 for detail.                                                              |  |  |  |  |

### **Terminal Functions**

| TERMII             | TERMINAL |      | TERMINAL                                                                                                                                                                                                                                                                                              |  |  |

|--------------------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO.           |          | 1/0† | DESCRIPTION                                                                                                                                                                                                                                                                                           |  |  |

| NAME               | PZ       |      |                                                                                                                                                                                                                                                                                                       |  |  |

| TEST 58            |          | I    | Extended system control register access bit. When the TEST pin is set to high, the part enters test mode and the extend system control registers can be accessed. The test terminal needs to be set to high for the external bias mode. The test terminal needs to be set to low for the normal mode. |  |  |

| TXM                | 82       | 0    | Analog output minus for TX channel                                                                                                                                                                                                                                                                    |  |  |

| TXP                | 81       | 0    | Analog output plus for TX channel                                                                                                                                                                                                                                                                     |  |  |

| VMID_ADC           | 11       | 0    | Decoupling 1.5 V for ADC. Add 10-μF X5R and 0.1-μF X7R ceramic capacitors to AVSS_ADC.                                                                                                                                                                                                                |  |  |

| VMID_REF 90        |          | 0    | Decoupling 1.5 V reference voltage. Add 10-μF X5R and 0.1-μFX7R ceramic capacitors to AVSS_REF.                                                                                                                                                                                                       |  |  |

| V <sub>SS</sub> 92 |          | I    | Substrate. Connect V <sub>SS</sub> to analog ground.                                                                                                                                                                                                                                                  |  |  |

| WETX 48            |          | Ī    | Parallel-port write enable for transmit channel from host processor                                                                                                                                                                                                                                   |  |  |

<sup>†</sup> I = input, O = output, I/O = 3-state input/output

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, AV <sub>DD</sub> to AGND, DVDD to DGND |                       |

|--------------------------------------------------------------|-----------------------|

| Analog input voltage range to AGND                           | 0.3 V to AVDD + 0.3 V |

| Digital input voltage range to DGND                          | 0.3 V to DVDD+ 0.3 V  |

| Operating virtual-junction temperature range, T <sub>J</sub> | –40°C to 150°C        |

| Operating free-air temperature range, T <sub>A</sub>         | –40°C to 85°C         |

| Storage temperature range, T <sub>Stq</sub>                  | –65°C to 150°C        |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# recommended operating conditions

### power supply

|                |                    | MIN | NOM | MAX | UNIT |

|----------------|--------------------|-----|-----|-----|------|

| Supply voltage | All power supplies | 3   | 3.3 | 3.6 | V    |

# digital inputs

|                                          |                           | MIN | NOM | MAX | UNIT |

|------------------------------------------|---------------------------|-----|-----|-----|------|

| High-level input voltage, VIH            | Input current = 0.75 mA   | 2   |     |     | V    |

| Low-level input voltage, V <sub>IL</sub> | Input current = - 0.75 mA |     |     | 8.0 | V    |

| Reset pulse width                        |                           | 80  |     |     | ns   |

| Input capacitance                        |                           | 5   | 10  |     | nf   |

# analog input

|                           |                                                                                            | MIN | NOM | MAX | UNIT |

|---------------------------|--------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Analog input signal range | AVDD_FIL_RX = 3.3 V. The input signal is measured differentially and CPGA is set to –20 dB |     | 30  |     | Vp-p |

#### clock

|                        |                | MIN | NOM    | MAX | UNIT |

|------------------------|----------------|-----|--------|-----|------|

| Input clock frequency  | DVDD CLK=3.3 V |     | 35.328 |     | MHz  |

| Input clock duty cycle |                |     | 50%    | ·   |      |

# electrical characteristics, typical at 25°C, analog power supply = 3.3 V, digital power supply = 3.3 V, $f_{CLKIN}$ = 35.328 MHz (unless otherwise noted)

# TX channel (measured differently, PAA=0 dB, unless otherwise noted)

|                                                    | PARAMETER                  | TEST CONDITIONS                                                        | MIN  | TYP   | MAX  | UNIT |

|----------------------------------------------------|----------------------------|------------------------------------------------------------------------|------|-------|------|------|

|                                                    |                            | G.Lite mode                                                            |      | 552   |      |      |

| l                                                  |                            | Full rate with reduced NEXT (with 138 kHz DHPF)                        |      | 1104  |      | kHz  |

|                                                    |                            | Full rate with EC                                                      |      | 1104  |      |      |

|                                                    | Conversion rate            |                                                                        |      | 8.832 |      | MHz  |

|                                                    | Channel gain error         | Test signal 43 kHz, full rate echo cancelled                           | -0.6 |       | -0.2 | dB   |

|                                                    | PAA attenuation step error |                                                                        |      | -0.4  | 0.1  | dB   |

| PSRR                                               | Power supply reject ratio  | Apply 250 mVp-p multitone to TX power supply and measure 300 kHz at TX |      | -54   | -45  | dB   |

|                                                    | Group delay                | Relative delay                                                         |      | 10    |      | μs   |

|                                                    | Output compliance voltage  | Load=2000 Ω                                                            |      | 3     |      | Vp-p |

| AC Per                                             | formance                   | •                                                                      |      |       |      |      |

| THD                                                | Total harmonic distortion  |                                                                        |      | -90   | -76  | dB   |

| SNR                                                | Signal to noise ratio      | Test signal 43 kHz, full rate echo cancelled                           | 68   | 74    |      | dB   |

| SNDR Signal-to-noise and harmonic distortion ratio |                            | Test signal 172 kHz, full rate and G.Lite reduced NEXT                 |      | 74    |      | dB   |

| MT                                                 | Missing tone test          | Apply multitone with 120 kHz and 250 kHz missing                       |      | -65   |      | dB   |

# RX channel (measured differently, PGA1=0 dB, PGA2=0 dB, unless otherwise noted)

|        | PARAMETER                                     | TEST CONDITIONS                                                       | MIN T  | ΥP    | MAX  | UNIT |

|--------|-----------------------------------------------|-----------------------------------------------------------------------|--------|-------|------|------|

|        | Channel bandwidth                             |                                                                       | 1      | 138   |      | kHz  |

|        | Clock rate                                    |                                                                       | 22     | 208   |      | kHz  |

|        | Channel gain error                            | CPGA = -2 dB, PGA1 =0dB, PGA2 =0dB, test signal = 10 kHz              | -0.25  |       | 0.25 | dB   |

|        |                                               | CPGA                                                                  | 0      | .10   |      |      |

|        | PGA gain step error                           | PGA1                                                                  |        | 0.2   |      | dB   |

|        |                                               | PGA2                                                                  |        | 0.1   |      |      |

| PSRR   | Power supply reject ratio                     | Apply 250 mVp-p multitone to RX power supply and measure 60 kHz at RX | -      | -65   | -60  | dB   |

|        | DC offset                                     |                                                                       | 0      | .09   |      | mV   |

|        | Cross talk                                    |                                                                       |        | 73    |      | dB   |

|        | Group delay                                   | Relative delay                                                        |        | 60    |      | μs   |

| CMRR   | Common mode reject ratio                      |                                                                       |        | 89    |      | dB   |

|        | Analog input self-bias dc voltage             |                                                                       | AVDD_F | FIL_R | X/2  | V    |

| AC Per | formance                                      |                                                                       |        |       |      |      |

| THD    | Total harmonic distortion                     |                                                                       | -      | -90   | -84  | dB   |

| SNR    | Signal to noise ratio                         | −<br>– Test signal 43 kHz @ −3 dB                                     | 70     | 75    |      | dB   |

| SNDR   | Signal-to-noise and harmonic distortion ratio | Tiost signal 40 N IZ & -0 ab                                          | 68     | 75    | _    | dB   |

| MT     | Missing tone test                             | Apply multitone with 120 kHz missing                                  |        | 65    |      | dB   |

# TLV320AD16 3.3-V INTEGRATED ADSL CODEC

SLWS107A – JUNE 2000 – REVISED OCTOBER 2000

electrical characteristics, typical at 25°C, analog power supply = 3.3 V, digital power supply = 3.3 V,  $f_{CLKIN}$  = 35.328 MHz (unless otherwise noted) (continued)

# reference voltage

|          | PARAMETER                         | TEST CONDITIONS | MIN                           | TYP | MAX | UNIT |

|----------|-----------------------------------|-----------------|-------------------------------|-----|-----|------|

| REFP     | ADC positive reference            |                 | 2.4                           | 2.5 | 2.6 | V    |

| REFM     | ADC negative reference            | AVDD REF=3.3V   | 2.4 2.5<br>0.4 0.5<br>1.4 1.5 | 0.5 | 0.6 | V    |

| VMID_REF |                                   | AVDD_REF=3.3V   | 1.4                           | 1.5 | 1.6 | V    |

| VMID_ADC | Receive channel mid-input voltage | ]               | 1.4                           | 1.5 | 1.6 | V    |

# power dissipation

| Ī | PARAMETER TEST CONDITIONS |                 | MIN                 | TYP | MAX | UNIT |       |

|---|---------------------------|-----------------|---------------------|-----|-----|------|-------|

| ł |                           |                 | Internal reference  | 600 |     |      |       |

|   | Power dissipation         | Active mode     | External reference  | 450 |     |      | mW    |

|   | Power dissipation         | Power-down mode | Hardware power down |     | 60  | 80   | mW    |

| - | Fower dissipation         | Power-down mode | Software power down |     | 60  | 80   | IIIVV |

# digital output

|     | PARAMETER                 | TEST CONDITIONS          | MIN | TYP | MAX | UNIT |

|-----|---------------------------|--------------------------|-----|-----|-----|------|

| Vон | High-level output voltage | Output current = 0.5 mA  | 2.4 |     |     | V    |

| VOL | Low-level output voltage  | Output current = -0.5 mA |     |     | 0.6 | V    |

timing requirements over recommended ranges of supply voltage and operating free-air temperature with 10 pF load(unless otherwise noted)

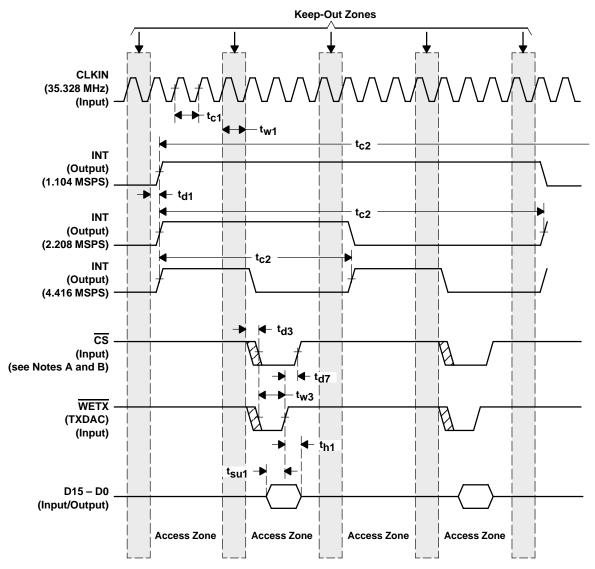

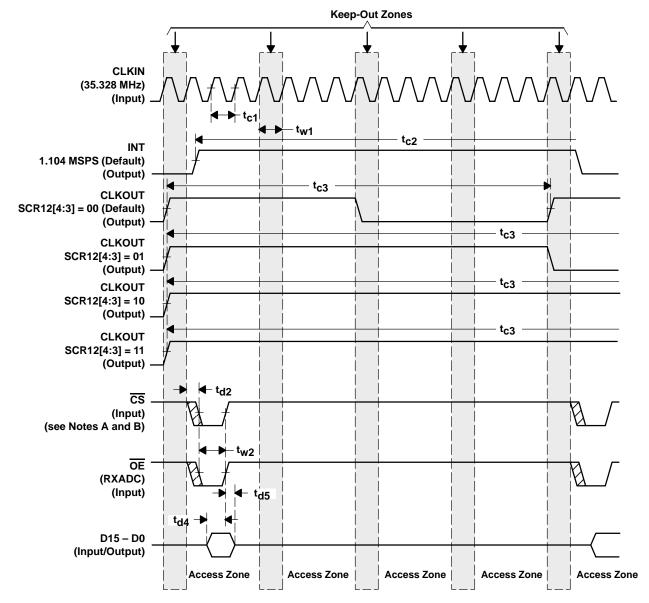

# parallel port (see Figures 1, 2 and 3)

|                  |                         | PARAMETER                           | MIN | TYP  | MAX   | UNIT  |

|------------------|-------------------------|-------------------------------------|-----|------|-------|-------|

| t <sub>c1</sub>  | Period, CLKIN           |                                     |     | 28.3 |       | ns    |

|                  |                         | OSEN/SCR8[4]=00                     |     | 32   |       |       |

| t <sub>c2</sub>  | Cycle time, INT         | OSEN/SCR8[4]=01/10                  |     | 16   |       |       |

|                  |                         | OSEN/SCR8[4]=11                     |     | 8    |       |       |

|                  |                         | SCR12[4:3]=00                       |     | 16   |       | CLKIN |

| ١.               | Dariad CLKOLIT          | SCR12[4:3]=01                       |     | 32   |       |       |

| t <sub>c3</sub>  | Period, CLKOUT          | SCR12[4:3]=10                       |     | 64   |       |       |

|                  |                         | SCR12[4:3]=11                       |     | 128  |       |       |

| t <sub>d1</sub>  | Delay time, keep-out 2  | zone end to INT↑                    |     |      | 16    | ns    |

| t <sub>w3</sub>  | Pulse width, WETX       |                                     | 28  |      |       | ns    |

| t <sub>d4</sub>  | Delay time, data valid  | after OE↓                           |     |      | 15    | ns    |

| t <sub>d5</sub>  | Delay time, data valid  | (before change to high–Z) after OE↑ |     |      | 5     | ns    |

| t <sub>d7</sub>  | Delay time, WETX↑ to    | <u>cs</u> ↑                         | 5   |      |       | ns    |

| t <sub>w2</sub>  | Pulse width, OE         |                                     | 20  |      |       | ns    |

| t <sub>d2</sub>  | Delay time, keep out z  | zone end (CLKIN↑) to CS↓/OE↓        | 0   |      |       | ns    |

| t <sub>d3</sub>  | Delay time, keep out z  | zone end (CLKIN↑) to CS√/WETX↓      | 0   |      |       | ns    |

| t <sub>su1</sub> | Setup time, data valid  | before WETX↑                        | 15  |      |       | ns    |

| t <sub>h1</sub>  | Hold time, data valid a | 5                                   |     |      | ns    |       |

| t <sub>w1</sub>  | Pulse width, keep-out   |                                     | 1   |      | CLKIN |       |

| t <sub>su2</sub> | Setup time, SYNC kee    | 10                                  |     |      | ns    |       |

| t <sub>h2</sub>  | Hold time, SYNC keep    | o high after CLKIN↑                 | 5   |      |       | ns    |

| t <sub>w4</sub>  | Pulse width, SYNC       |                                     |     | 28   |       | ns    |

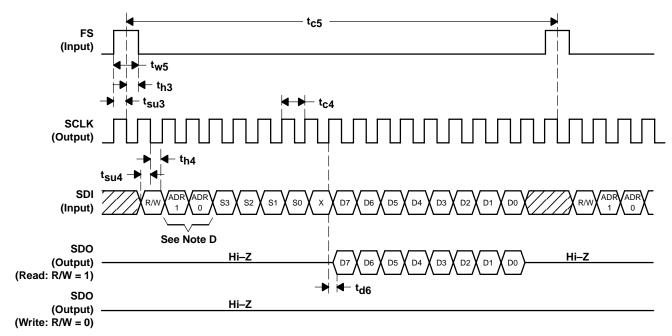

# serial port (see Figure 4)

|                  | PARAMETER                                 | MIN | TYP | MAX | UNIT  |

|------------------|-------------------------------------------|-----|-----|-----|-------|

| t <sub>su4</sub> | Setup time, SDI valid before SCLK↓        | 20  |     |     | ns    |

| t <sub>h4</sub>  | Hold time, SDI valid after SCLK↓          | 5   |     |     | ns    |

| t <sub>su3</sub> | FS become high before SCLK↓               | 20  |     |     | ns    |

| th3              | FS keep high after SCLK↓                  | 5   |     |     | ns    |

| t <sub>w5</sub>  | FS pulse width                            |     | 28  |     | ns    |

| t <sub>C4</sub>  | Cycle time, SCLK                          |     | 8   |     | CLKIN |

| t <sub>C5</sub>  | Cycle time, FS                            | 18  |     |     | SCLK  |

| t <sub>d6</sub>  | Delay time, SCLK rising edge to SOD valid |     |     | 15  | ns    |

- NOTES: A.  $\overline{\text{CS}}$  and  $\overline{\text{WETX}}$  may fall together or be skewed from each other, but the rising edge of  $\overline{\text{WETX}}$  must occur prior to the rising edge of  $\overline{\text{CS}}$

- B. The operation of  $\overline{\text{CS}}$  and  $\overline{\text{WETX}}$  shown above is under condition of OSEN/SCR8[4]=11, and is not a default function. As long as the write operation does not conflict with read operation, the write operation can occur at any place except the keep-out-zone.

Figure 1. Parallel Timing Diagram (TX)

- NOTES: A.  $\overline{\text{CS}}$  and  $\overline{\text{OE}}$  may fall/rise together or be skewed from each other. It does not matter which falls/rises first. However,  $t_{d4}$  is referenced from whichever falls last and  $t_{d5}$  is referenced from whichever rises first.

- B. The operation of  $\overline{\text{CS}}$  and  $\overline{\text{OE}}$  shown above is for default condition (SCR8[4:3]=00). As long as the read operation does not conflict with write operation, the read operation can occur at any place except the keep-out-zone.

Figure 2. Parallel Timing Diagram (RX)

NOTE A: SYNC is only used during multi-codec system to synchronous operation. The part can automatically meet the keep-out-zone requirement when used alone.

Figure 3. Sync Pulse Timing

NOTES: A. FS is sampled at the falling-edge of SCLK

- B. Data is latched at the falling-edge of SCLK.

- C. Data is sent out at the rising-edge of SCLK.

- D. ADR0 and ADR1 are the configuration of pin ADR0 and ADR1.

Figure 4. Serial Port Timing

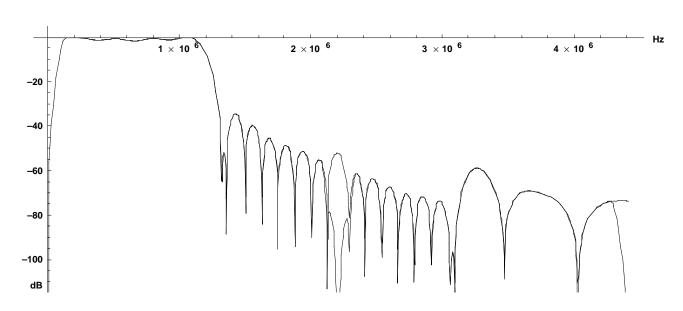

Figure 5. TLV320AD16 Transmitter Channel Frequency Response in Full Rate Mode With and Without Reduced Next High-Pass Over Frequency Range DC-4416 kHz

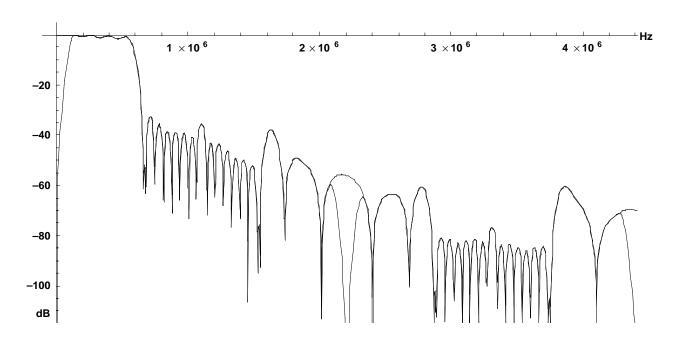

Figure 6. TLV320AD16 Transmitter Channel Frequency Response in G.lite Mode With and Without Reduced Next High-Pass Over Frequency Range DC-4416kHz.

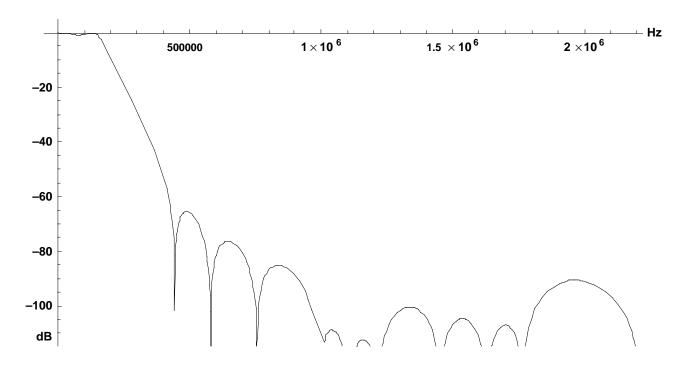

Figure 7. TLV320AD16 Receive Channel Frequency Response

# THERMAL INFORMATION

# thermal resistance characteristics (S-PQFP package)

| NO |                                       | °C/W | AIR FLOW<br>LFPM† |

|----|---------------------------------------|------|-------------------|

| 1  | R1 <sub>JC</sub> Junction-to-case     | 5.40 | N/A               |

| 2  | R1 <sub>JC</sub> Junction-to-free air | 30.4 | 0                 |

| 3  | R1 <sub>JC</sub> Junction-to-free air | 24.2 | 100               |

| 4  | R1 <sub>JC</sub> Junction-to-free air | 22.3 | 250               |

| 5  | R1 <sub>JC</sub> Junction-to-free air | 20   | 500               |

<sup>†</sup>LFPM - Linear feet per minute

# **PROGRAMMING INFORMATION**

Table 1. System Control Register (SCR)

|       | EM CONTROL<br>EGISTER | MODE | DEFAULT<br>VALUE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|-----------------------|------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | ADDRESS               |      | VALUE            |                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | S3, S2, S1, S0        |      |                  |                                                                                                                                                                                                                                                                                                                                                                                                            |

| SCR0  | 0000                  | R/W  | 00000000         | D0: S/W RESET (self-clearing). D1 to D6: Reserved. D7: ESCR access enable                                                                                                                                                                                                                                                                                                                                  |

| SCR1  | 0001                  | R/W  | 00000000         | TX channel PAA attenuation select. D[4:0] = 00000 for 0 dB and D[4:0] = 11000 for -24 dB                                                                                                                                                                                                                                                                                                                   |

| SCR2  | 0010                  | R/W  | 00000000         | RX channel PGA1 gain select. D[2:0] = 000 for 0 dB and D[2:0] = 110 for 6 dB                                                                                                                                                                                                                                                                                                                               |

| SCR3  | 0011                  | R/W  | 00000000         | RX channel PGA2 gain select. D[3:0] = 0000 for 0 dB and D[3:0] = 1001 for 9 dB                                                                                                                                                                                                                                                                                                                             |

| SCR4  | 0100                  |      |                  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                   |

| SCR5  | 0101                  |      |                  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                   |

| SCR6  | 0110                  | R/W  | 00000000         | D[7:0] = GP [7:0]                                                                                                                                                                                                                                                                                                                                                                                          |

| SCR7  | 0111                  | R/W  | 00000000         | MISC.1. Control (set to 1 to enable) D0: Reserved D1: S/W power down RX channel with reference on D2: S/W power down TX channel with reference on D3: Analog loop back. TXP and TXM are internally connected to RXP and RXM. D4: Digital loop back. RX channel digital output is internally connected to TX channel digital input. D5: TX data read back mode. D6: Rx signal read back mode. D7: Reserved. |

| SCR8  | 1000                  | R/W  | 00000000         | MISC.2. Control (set to 1 to enable) D0: TX INT1 BYP D1: TX HPF BYP D2: TX INT2 EN D3: TX DLPF BYP D4: MODE TX FULL D[7:5]: CPGA gain select. D[7:5]=000 for -20dB and D[7:5]=110 for +16dB.                                                                                                                                                                                                               |

| SCR9  | 1001                  | R/W  | 00000000         | RX offset word [7:0].                                                                                                                                                                                                                                                                                                                                                                                      |

| SCR10 | 1010                  | R/W  | 00000000         | RX offset word [5:8]                                                                                                                                                                                                                                                                                                                                                                                       |

| SCR11 | 1011                  | R/W  | 00000000         | D[7:4] = CTRL_DLPF1_GA[3:0]<br>D[3:0] = CTRL_DLPF3_GA[3:0]                                                                                                                                                                                                                                                                                                                                                 |

| SCR12 | 1100                  | R/W  | 00000000         | D[2:0] = CTRL-PHASE SEL[2:0] (see Figure 15) D[4:3] = CTRL_RATE SEL[1:0] (see Table 5)                                                                                                                                                                                                                                                                                                                     |

NOTE 1: All reserved bits should be filled with 0 during operations. All registers are set to 0 after reset.

# Table 2. Extended System Control Register (ESCR)

| 1     | SYSTEM CONTROL<br>REGISTER |     |          |                                                                        | DEFAULT<br>VALUE | FUNCTION |  |  |

|-------|----------------------------|-----|----------|------------------------------------------------------------------------|------------------|----------|--|--|

| NAME  | ADDRESS                    |     | VALUE    |                                                                        |                  |          |  |  |

|       | S3, S2, S1, S0             |     |          |                                                                        |                  |          |  |  |

| ESCR0 | 0000                       | R/W | 00000000 | D0: S/W RESET (self-cleaning) D7:ESCR access enable D1 to D6: Reserved |                  |          |  |  |

| ESCR4 | 0100                       | R/W | 00000000 | D4:IREF_BYP D1 to D3 and D5 to D7: Reserved                            |                  |          |  |  |

NOTE 2: SCR0 and ESCR0 refer to the same register.

#### SCR0 – system control register Address:0000b contents at reset: 01000000b

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | REG. VALUE (HEX) | DESCRIPTION                                                                     |

|----|----|----|----|----|----|----|----|------------------|---------------------------------------------------------------------------------|

| 0  | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 41               | D0=1:S/W reset (self clearing). All control registers are set to reset content. |

#### SCR1 – system control register Address:0001b contents at reset: 00000000b

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | REG. VALUE (HEX) | DESCRIPTION               |

|----|----|----|----|----|----|----|----|------------------|---------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00               | TX PAA attenuation = 0dB  |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 01               | TX PAA attenuation = 1dB  |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 02               | TX PAA attenuation = 2dB  |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 03               | TX PAA attenuation = 3dB  |

| 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 04               | TX PAA attenuation = 4dB  |

| 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 05               | TX PAA attenuation = 5dB  |

| 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 06               | TX PAA attenuation = 6dB  |

| 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 07               | TX PAA attenuation = 7dB  |

| 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 08               | TX PAA attenuation = 8dB  |

| 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 09               | TX PAA attenuation = 9dB  |

| 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0A               | TX PAA attenuation = 10dB |

| 0  | 0  | 0  | 0  | 1  | 0  | 1  | 1  | 0B               | TX PAA attenuation = 11dB |

| 0  | 0  | 0  | 0  | 1  | 1  | 0  | 0  | 0C               | TX PAA attenuation = 12dB |

| 0  | 0  | 0  | 0  | 1  | 1  | 0  | 1  | 0D               | TX PAA attenuation = 13dB |

| 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 0E               | TX PAA attenuation = 14dB |

| 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 0F               | TX PAA attenuation = 15dB |

| 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 10               | TX PAA attenuation = 16dB |

| 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 11               | TX PAA attenuation = 17dB |

| 0  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 12               | TX PAA attenuation = 18dB |

| 0  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 13               | TX PAA attenuation = 19dB |

| 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 14               | TX PAA attenuation = 20dB |

| 0  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 15               | TX PAA attenuation = 21dB |

| 0  | 0  | 0  | 1  | 0  | 1  | 1  | 0  | 16               | TX PAA attenuation = 22dB |

| 0  | 0  | 0  | 1  | 0  | 1  | 1  | 1  | 17               | TX PAA attenuation = 23dB |

| 0  | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 18               | TX PAA attenuation = 24dB |

| _  | _  | _  | _  | -  | _  | _  | _  | 19–FF            | TX PAA attenuation = 24dB |

# SCR2 - RX PGA1 control register Address:0010b contents at reset: 00000000b

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | REG. VALUE (HEX) | DESCRIPTION  |

|----|----|----|----|----|----|----|----|------------------|--------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00               | RX PGA1= 0dB |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 01               | RX PGA1= 1dB |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 02               | RX PGA1= 2dB |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 03               | RX PGA1= 3dB |

| 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 04               | RX PGA1= 4dB |

| 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 05               | RX PGA1= 5dB |

| 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 06               | RX PGA1= 6dB |

| _  | _  | _  | _  | _  | _  | _  | _  | 06-FF            | RX PGA1= 6dB |

# SCR3- RX PGA2 control register Address:0011b contents at reset: 00000000b

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | REG. VALUE (HEX) | DESCRIPTION   |

|----|----|----|----|----|----|----|----|------------------|---------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00               | RX PGA2= 0 dB |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 01               | RX PGA2= 1 dB |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 02               | RX PGA2= 2 dB |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 03               | RX PGA2= 3 dB |

| 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 04               | RX PGA2= 4 dB |

| 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 05               | RX PGA2= 5 dB |

| 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 06               | RX PGA2= 6 dB |

| 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 07               | RX PGA2= 7 dB |

| 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 08               | RX PGA2= 8 dB |

| 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 09               | RX PGA2= 9 dB |

| _  | _  | -  | -  | -  | -  | -  | -  | 0A-FF            | RX PGA2= 9 dB |

# SCR6- general-purpose output data register Address:0110b contents at reset: 00000000b

| D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | REG. VALUE (HEX) | DESCRIPTION          |

|-----|-----|-----|-----|-----|-----|-----|-----|------------------|----------------------|

| 0/1 | -   | -   | 1   | 1   | -   | -   | -   |                  | GP7 = low(0)/high(1) |

| _   | 0/1 | ı   | ı   | İ   | ı   | ı   | ı   |                  | GP6 = low(0)/high(1) |

| _   | -   | 0/1 | ı   | ı   | ı   | -   | -   |                  | GP5 = low(0)/high(1) |

| _   | -   | -   | 0/1 | ı   | -   | -   | -   |                  | GP4 = low(0)/high(1) |

| _   | -   | -   | ı   | 0/1 | -   | -   | -   |                  | GP3 = low(0)/high(1) |

| _   | -   | -   | ı   | 1   | 0/1 | -   | -   |                  | GP2 = low(0)/high(1) |

| _   | -   | -   | ı   | 1   | -   | 0/1 | -   |                  | GP1 = low(0)/high(1) |

| _   | -   | -   | ı   | İ   | -   | -   | 0/1 |                  | GP0 = low(0)/high(1) |

SCR7 - Miscellaneous control register 1 contents at reset: 00000000b Address:0111b

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | REG. VALUE (HEX) | DESCRIPTION                            |

|----|----|----|----|----|----|----|----|------------------|----------------------------------------|

| _  | -  | ı  | 1  | 1  | 1  | -  | 0  |                  | Reserved                               |

| _  | -  | 1  | 1  | 1  | -  | 1  | -  |                  | S/W power-down RX channel              |

| _  | -  | -  | -  | 1  | 1  | -  | -  |                  | S/W power-down TX channel              |

| _  | -  | -  | -  | 1  | -  | -  | -  |                  | Analog loopback (see Note 3)           |

| _  | -  | -  | 1  | -  | -  | -  | -  |                  | Digital loopback (see Note 4)          |

| _  | -  | 1  | -  | -  | -  | -  | -  |                  | TX data read back mode (see Note 5)    |

| _  | 1  | -  | -  | -  | -  | _  | _  |                  | RX analog input read back (see Note 6) |

| 0  | _  | -  | _  | _  | _  | _  | _  |                  | Reserved                               |

- NOTES: 3. Analog loopback: Analog output pins (TXP/TXM) are internally connected to RXP/RXM.

- 4. Digital loopback: RX digital output buffer (16-bit word) is internally connected to the TX digital input buffer.

- 5. The input digital data is read back from RX output buffer without going through DAC converter.

- 6. The input analog signal is read back from TX without going through ADC converter.

#### SCR8 – miscellaneous control register 2 (refer to block diagram for correspondent control pin) Address:1000b contents at reset: 00000000b

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | REG. VALUE (HEX) | DESCRIPTION                                  |

|----|----|----|----|----|----|----|----|------------------|----------------------------------------------|

| 0  | 0  | 0  | -  | -  | -  | -  | -  |                  | CPGA=-20dB                                   |

| 0  | 0  | 1  | -  | -  | -  | -  | -  |                  | CPGA=-14 dB                                  |

| 0  | 1  | 0  | -  | -  | ı  | -  | ı  |                  | CPGA=-8 dB                                   |

| 0  | 1  | 1  | -  | -  | ı  | -  | ı  |                  | CPGA=-2 dB                                   |

| 1  | 0  | 0  | -  | ı  | ı  | -  | ı  |                  | CPGA=4 dB                                    |

| 1  | 0  | 1  | -  | -  | -  | -  | -  |                  | CPGA=10 dB                                   |

| 1  | 1  | 0  | -  | -  | ı  | -  | -  |                  | CPGA=16 dB                                   |

| 1  | 1  | 1  | -  | -  | 1  | -  | -  |                  | Reserved                                     |

| _  | ı  | ı  | ı  | ı  | ı  | -  | 1  |                  | Bypass TX 2X interpolation 1 (see Note 7)    |

| _  | ı  | ı  | -  | ı  | ı  | 1  | ı  |                  | Bypass TX 138 kHz digital HPF (see Note 7)   |

| _  | ı  | ı  | -  | ı  | 1  | -  | ı  |                  | Enable TX 2X interpolation 2 (see Note 7)    |

| _  | -  | -  | -  | 1  | -  | -  | -  |                  | Bypass TX 552 kHz digital LPF 2 (see Note 7) |

| _  | -  | -  | 0  | -  | -  | _  | -  |                  | Select TX digital LPF1–1 (see Note 7)        |

| _  | -  | -  | 1  | -  | -  | _  | -  |                  | Select TX digital LPF1–2 (see Note 7)        |

NOTE 7: [4:0] are restricted by the following setting. Performance of the codec for invalid combination of bits is not guaranteed and such combinations should not be used. Figures 8 to 14 show the data path for each combination.

#### TLV320AD16 Transmit

|                   | D4 | D3 | D2                                                       | D1 | D0                                                 | COMMENTS                                              |  |

|-------------------|----|----|----------------------------------------------------------|----|----------------------------------------------------|-------------------------------------------------------|--|

|                   | 0  | 0  | 0                                                        | 0  | 0                                                  | G.Lite with reduced next mode (refer to Figure 8)     |  |

| OSEN =0 (default) | 0  | 0  | 0                                                        | 1  | 0                                                  | G.Lite with EC mode (refer to Figure 9)               |  |

| OSEN =0 (derault) | 1  | 1  | 1                                                        | 0  | 1                                                  | Full rate with reduced next mode (refer to Figure 10) |  |

|                   | 1  | 1  | 1                                                        | 1  | 1                                                  | Full rate with EC mode (refer to Figure 11)           |  |

|                   | 0  | 0  | 0 0 1 G.Lite with reduced next mode (refer to Figure 12) |    | G.Lite with reduced next mode (refer to Figure 12) |                                                       |  |

| OSEN =1           | 0  | 0  | 0                                                        | 1  | 1                                                  | G.Lite with EC mode (refer to Figure 13)              |  |

|                   | 1  | 1  | 0                                                        | 1  | 1                                                  | Full rate with EC mode (refer to Figure 14)           |  |

Figure 8. TLV320AD16 Transmit Block Diagram in G.Lite/Reduced NEXT Mode (SCR8[4:0]=00000 and OSEN=0, default)

Figure 9. TLV320AD16 Transmit Block Diagram in G.Lite/EC Mode (SCR8[4:0]=00010 and OSEN=0)

Figure 10. TLV320AD16 Transmit Block Diagram in Full/Reduced NEXT Mode (SCR8[4:0]=11101 and OSEN=0)

Figure 11. TLV320AD16 Transmit Block Diagram in Full/EC Mode (SCR8[4:0]=11111 and OSEN=0)

Figure 12. TLV320AD16 Transmit Block Diagram in G.Lite/Reduced NEXT Over-Sampling Mode (SCR8[4:0]=00001 and OSEN=1)

Figure 13. TLV320AD16 Transmit Block Diagram in G.Lite/EC Over-Sampling Mode (SCR8[4:0]=00011 and OSEN = 1)

Figure 14. TLV320AD16 Transmit Block Diagram in Full/EC Over-Sampling Mode (SCR8[4:0]=11011 and OSEN=1)

SCR9 – RX offset control register[7:0] Address:1001b contents at reset: 00000000b

SCR10 - RX offset control register [15:8] Address:1010b contents at reset: 00000000b

These two registers are concatenated to form a 16-bit word in 2s complement data format. The 16-bit word is used to adjust RX channel dc offset error. It adds to the 16-bit data from the RX digital filter before the data goes to RX output buffer.

SCR11 – TX gain adjustment register Address:1011b contents at reset: 00000000b

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | REG. VALUE (HEX) | DESCRIPTION                               |

|----|----|----|----|----|----|----|----|------------------|-------------------------------------------|

| 1  | 0  | 0  | 0  | -  | -  | -  | -  |                  | TX digital gain for DLPF1=-0.8 dB         |

| 1  | 0  | 0  | 1  | -  | -  | -  | -  |                  | TX digital gain for DLPF1=-0.7 dB         |

| 1  | 0  | 1  | 0  | -  | -  | -  | -  |                  | TX digital gain for DLPF1=-0.6 dB         |

| 1  | 0  | 1  | 1  | -  | -  | -  | -  |                  | TX digital gain for DLPF1=-0.5 dB         |

| 1  | 1  | 0  | 0  | -  | -  | -  | _  |                  | TX digital gain for DLPF1=-0.4 dB         |

| 1  | 1  | 0  | 1  | -  | -  | -  | -  |                  | TX digital gain for DLPF1=-0.3 dB         |

| 1  | 1  | 1  | 0  | -  | -  | -  | _  |                  | TX digital gain for DLPF1=-0.2 dB         |

| 1  | 1  | 1  | 1  | -  | -  | -  | _  |                  | TX digital gain for DLPF1=-0.1 dB         |

| 0  | 0  | 0  | 0  | -  | -  | -  | -  |                  | TX digital gain for DLPF1=0 dB (default)  |

| 0  | 0  | 0  | 1  | -  | -  | -  | -  |                  | TX digital gain for DLPF1=0.1 dB          |

| 0  | 0  | 1  | 0  | -  | -  | -  | -  |                  | TX digital gain for DLPF1=0.2 dB          |

| 0  | 0  | 1  | 1  | -  | -  | -  | _  |                  | TX digital gain for DLPF1=0.3 dB          |

| 0  | 1  | 0  | 0  | -  | -  | -  | _  |                  | TX digital gain for DLPF1=0.4 dB          |

| 0  | 1  | 0  | 1  | -  | -  | -  | _  |                  | TX digital gain for DLPF1=1.5 dB          |

| 0  | 1  | 1  | 0  | -  | -  | -  | -  |                  | TX digital gain for DLPF1=0.6 dB          |

| 0  | 1  | 1  | 1  | -  | -  | -  | _  |                  | TX digital gain for DLPF1=0.7 dB          |

| _  | _  | -  | -  | 1  | 0  | 0  | 1  |                  | TX digital gain for DLPF3=-1.4 dB         |

| _  | _  | _  | -  | 1  | 0  | 1  | 0  |                  | TX digital gain for DLPF3=-1.2 dB         |

| _  | _  | -  | -  | 1  | 0  | 1  | 1  |                  | TX digital gain for DLPF3=-1 dB           |

| _  | _  | _  | -  | 1  | 1  | 0  | 0  |                  | TX digital gain for DLPF3=-0.8 dB         |

| _  | _  | -  | -  | 1  | 1  | 0  | 1  |                  | TX digital gain for DLPF3=-0.6 dB         |

| _  | _  | _  | -  | 1  | 1  | 1  | 0  |                  | TX digital gain for DLPF3=-0.4 dB         |

| _  | _  | -  | -  | 1  | 1  | 1  | 1  |                  | TX digital gain for DLPF3=-0.2 dB         |

| _  | -  | -  | -  | 0  | 0  | 0  | 0  |                  | TX digital gain for DLPF3= 0 dB (default) |

| _  | -  | -  | -  | 0  | 0  | 0  | 1  |                  | TX digital gain for DLPF3=0.2 dB          |

| _  | _  | -  | -  | 0  | 0  | 1  | 0  |                  | TX digital gain for DLPF3=0.4 dB          |

| _  | -  | -  | -  | 0  | 0  | 1  | 1  |                  | TX digital gain for DLPF3=0.6 dB          |

| _  | -  | -  | -  | 0  | 1  | 0  | 0  |                  | TX digital gain for DLPF3=0.8 dB          |

| _  | _  | -  | -  | 0  | 1  | 0  | 1  |                  | TX digital gain for DLPF3= 1 dB           |

| _  | -  | -  | -  | 0  | 1  | 1  | 0  |                  | TX digital gain for DLPF3=1.2 dB          |

| _  | _  | _  | _  | 0  | 1  | 1  | 1  |                  | TX digital gain for DLPF3=1.4 dB          |

NOTE: Digital gain is used to compensate the TX channel gain error.

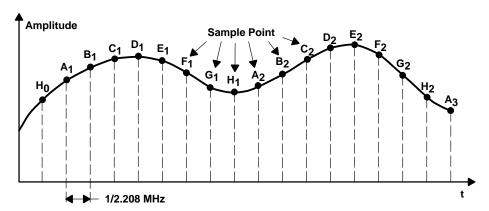

SCR12- RX data control register Address:1100b contents at reset: 00000000b

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | REG.<br>VALUE<br>(HEX) | DESCRIPTION<br>(see figure15)                                                                                                                                                                                                                                                                                             |

|----|----|----|----|----|----|----|----|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _  | -  | _  | 1  | 1  | 0  | 0  | 0  |                        | Sampling points A <sub>1</sub> , A <sub>2</sub> are used for RX data                                                                                                                                                                                                                                                      |

| _  | ı  | -  | 1  | 1  | 0  | 0  | 1  |                        | Sampling points B <sub>1</sub> , B <sub>2</sub> are used for RX data                                                                                                                                                                                                                                                      |

| _  | -  | _  | 1  | 1  | 0  | 1  | 0  |                        | Sampling points C <sub>1</sub> , C <sub>2</sub> are used for RX data                                                                                                                                                                                                                                                      |

| _  | _  | _  | 1  | 1  | 0  | 1  | 1  |                        | Sampling points D <sub>1</sub> , D <sub>2</sub> are used for RX data                                                                                                                                                                                                                                                      |

| _  | -  | _  | 1  | 1  | 1  | 0  | 0  |                        | Sampling points E <sub>1</sub> , E <sub>2</sub> are used for RX data                                                                                                                                                                                                                                                      |

| _  | -  | _  | 1  | 1  | 1  | 0  | 1  |                        | Sampling points F <sub>1</sub> , F <sub>2</sub> are used for RX data                                                                                                                                                                                                                                                      |

| _  | _  | -  | 1  | 1  | 1  | 1  | 0  |                        | Sampling points G <sub>1</sub> , G <sub>2</sub> are used for RX data                                                                                                                                                                                                                                                      |

| _  | -  | _  | 1  | 1  | 1  | 1  | 1  |                        | Sampling points H <sub>1</sub> , H <sub>2</sub> are used for RX data                                                                                                                                                                                                                                                      |

|    |    |    | 1  | 0  | _  | 0  | 0  |                        | Sampling points A <sub>1</sub> , E <sub>1</sub> , A <sub>2</sub> , E <sub>2</sub> are used for RX data                                                                                                                                                                                                                    |

|    |    |    | 1  | 0  | _  | 0  | 1  |                        | Sampling points B <sub>1</sub> , F <sub>1</sub> , B <sub>2</sub> , F <sub>2</sub> are used for RX data                                                                                                                                                                                                                    |

|    |    |    | 1  | 0  | _  | 1  | 0  |                        | Sampling points C <sub>1</sub> , G <sub>1</sub> , C <sub>2</sub> , G <sub>2</sub> are used for RX data                                                                                                                                                                                                                    |

|    |    |    | 1  | 0  | _  | 1  | 1  |                        | Sampling points D <sub>1</sub> , H <sub>1</sub> , D <sub>2</sub> , H <sub>2</sub> are used for RX data                                                                                                                                                                                                                    |

| _  | -  | _  | 0  | 1  | _  | _  | 0  |                        | Sampling points A <sub>1</sub> , C <sub>1</sub> , E <sub>1</sub> , G <sub>1</sub> , A <sub>2</sub> , C <sub>2</sub> , E <sub>2</sub> , G <sub>2</sub> are used for RX data                                                                                                                                                |

| _  | _  | _  | 0  | 1  | _  | _  | 1  |                        | Sampling points B <sub>1</sub> , D <sub>1</sub> , F <sub>1</sub> , H <sub>1</sub> , B <sub>2</sub> , D <sub>2</sub> , F <sub>2</sub> , H <sub>2</sub> are used for RX data                                                                                                                                                |

| _  | _  | _  | 0  | 0  | _  | -  | _  |                        | All sampling points (A <sub>1</sub> , B <sub>1</sub> , C <sub>1</sub> , D <sub>1</sub> , E <sub>1</sub> , F <sub>1</sub> , G <sub>1</sub> , H <sub>1</sub> , A <sub>2</sub> , B <sub>2</sub> , C <sub>2</sub> , D <sub>2</sub> , E <sub>2</sub> , F <sub>2</sub> , G <sub>2</sub> , H <sub>2</sub> ) are used for RX data |

NOTE: Performance of the codec for invalid combination of bits is not guaranteed and such combinations should not be used. The user should make no assumption that the code bits will saturate to a maximum or minimum value or wrap around to a valid combination.

Figure 15. Input Signal Sampling

# ESCR0 – extended system control register

Address:0000b Contents at reset: 00000000b

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | REG. VALUE (HEX) | DESCRIPTION                                                                                                                                                                             |