TENTATIVE

TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

**TC9332F****AUDIO DIGITAL SIGNAL PROCESSOR**

The TC9332F has a ROM area that holds application programs for digital filters such as equalizers, for dynamic range control of compressors, and for acoustic field control concert hall simulation. These application programs allow real-time digital processing of audio signals.

Thanks to 64kbit of built-in data delay (audio field control) RAM, no external RAM is necessary and the built-in voltage-controlled oscillator (VCO) allows easy phase-locked loop configuration.

**FEATURES**

- 24bit main bus

- The arithmetic operations block is as follows:

|                    |                                 |

|--------------------|---------------------------------|

| Multiplier / adder | : 24bit x 16bit + 43bit → 43bit |

| Accumulator        | : 43bit (code extension 4bit)   |

| Logic operator     | : 24bit (AND, OR, XOR, NOT)     |

| Work register      | : 32bit, 39bit                  |

| Temporary register | : 32bit                         |

| Shifter            | : +4bit, +1bit shift            |

- The structure of the program and internal data memory areas are as follows:

|                    |                     |

|--------------------|---------------------|

| Program ROM        | : 1024 word x 32bit |

| Data RAM           | : 128 word x 24bit  |

| Coefficient RAM    | : 320 word x 16bit  |

| Coefficient ROM    | : 256 word x 16bit  |

| Offset address RAM | : 64 word x 16bit   |

- The following five serial data ports are provided:

|                          |                                                 |

|--------------------------|-------------------------------------------------|

| Serial data input ports  | : 2 ports (SDI0, SDI1)                          |

| Serial data output ports | : 3 ports (SDO0, SDO1, SDO2)                    |

| Data word length         | : 24bit and 16bit                               |

| Data format              | : MSB / LSB first (input)<br>MSB first (output) |

- Built-in RAM for data delay

Delay RAM : 64kbit (4096word x 16bit)

- Built-in VCO circuit.

- Coefficient data and offset data can be set or changed via a microcontroller interface.

- CMOS silicon technology for higher speed.

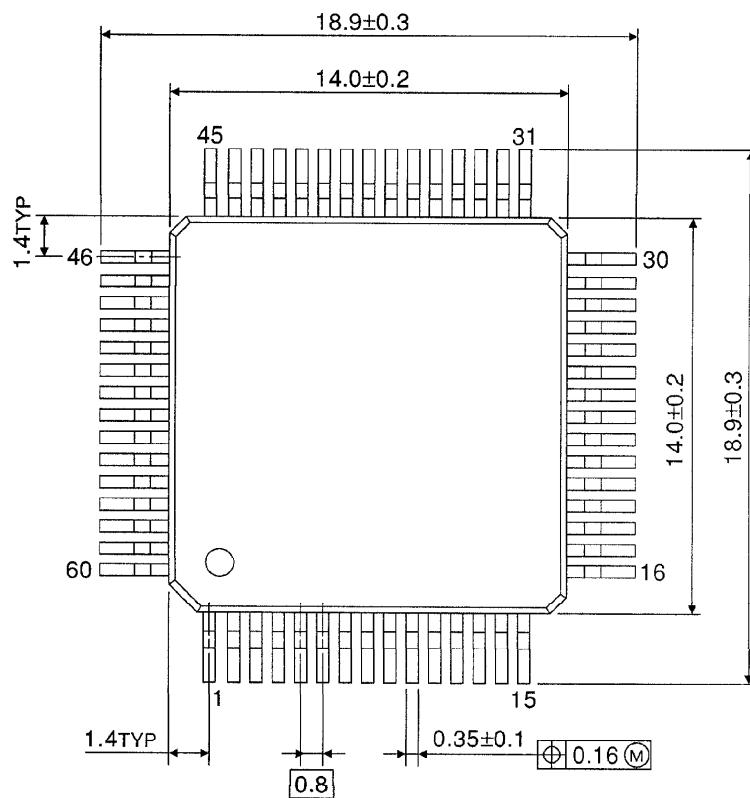

- 60 pin flat package.

QFP60-P-1414-0.80D

Weight : 1.08g (Typ.)

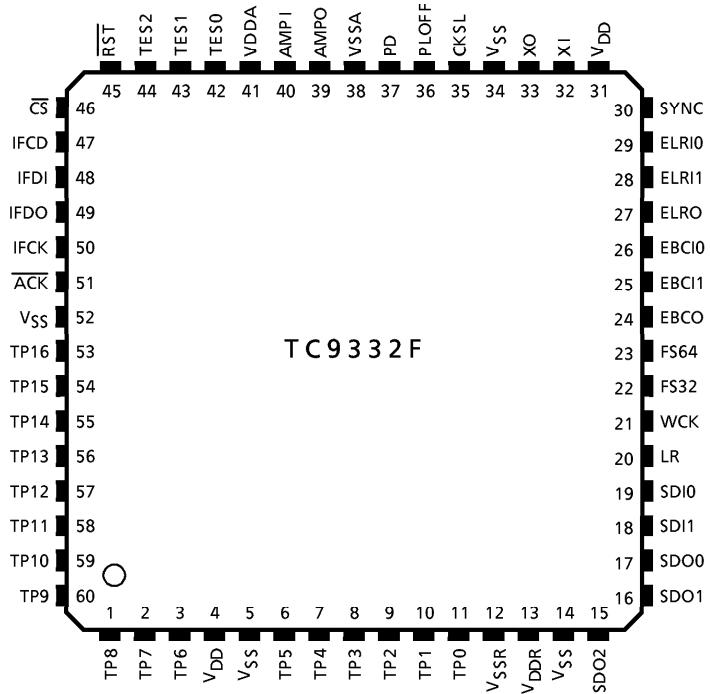

## PIN CONNECTION

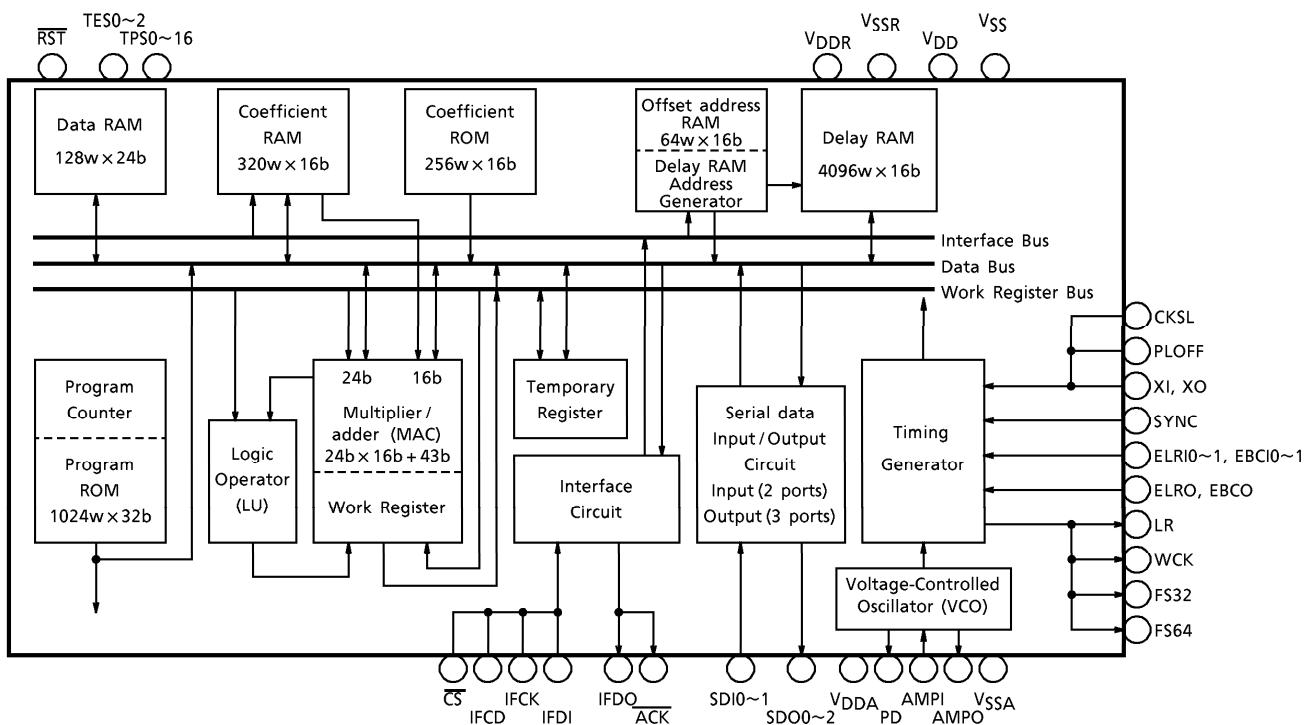

## BLOCK DIAGRAM

## PIN FUNCTION

| PIN No. | SYMBOL           | I/O | DESCRIPTION OF PIN FUNCTIONS                                                                                                                           | REMARKS       |

|---------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 1<br>3  | TP8<br>TP6       | O   | Test data output terminal, normally open.                                                                                                              | —             |

| 4       | V <sub>DD</sub>  | —   | Power supply terminal.                                                                                                                                 | —             |

| 5       | V <sub>SS</sub>  | —   | Ground terminal.                                                                                                                                       | —             |

| 6<br>11 | TP5<br>TP0       | O   | Test data output terminal, normally open.                                                                                                              | —             |

| 12      | V <sub>SSR</sub> | —   | Ground terminal for internal delay RAM (DLRAM).                                                                                                        | —             |

| 13      | V <sub>DDR</sub> | —   | Power supply terminal for internal delay RAM (DLRAM).                                                                                                  | —             |

| 14      | V <sub>SS</sub>  | —   | Ground terminal.                                                                                                                                       | —             |

| 15      | SDO2             | O   | Serial data output terminal.                                                                                                                           | —             |

| 16      | SDO1             |     | Output data length 24bit or 16bit, selectable by microcontroller.                                                                                      |               |

| 17      | SDO0             |     |                                                                                                                                                        |               |

| 18      | SDI1             | I   | Serial data input terminal.                                                                                                                            | —             |

| 19      | SDI0             |     | Input data length 24bit or 16bit, selectable by microcontroller.                                                                                       |               |

| 20      | LR               | O   | LR clock output terminal (1fs).                                                                                                                        | —             |

| 21      | WCK              | O   | Word clock output terminal (2fs).                                                                                                                      | —             |

| 22      | FS32             | O   | Bit clock output terminal (32fs).                                                                                                                      | —             |

| 23      | FS64             | O   | Bit clock output terminal (64fs).                                                                                                                      | —             |

| 24      | EBC0             | I   | Bit clock input terminals.<br>Inputs shift clock for SDO0/1/2 data output.                                                                             | Schmitt input |

| 25      | EBCI1            | I   | Bit clock input terminals.<br>Inputs shift clock for SDI0/1 data input.                                                                                | Schmitt input |

| 26      | EBCI0            |     | For SDI1 data input<br>For SDI0 data input                                                                                                             |               |

| 27      | ELRO             | I   | LR clock input terminal.<br>Inputs LR clock for SDO0/1/2 data output.                                                                                  | Schmitt input |

| 28      | ELRI1            | I   | LR clock input terminals.<br>Inputs LR clock for SDI0/1 data input.                                                                                    | Schmitt input |

| 29      | ELRI0            |     | For SDI1 data input<br>For SDI0 data input                                                                                                             |               |

| 30      | SYNC             | I   | Synchronous signal input terminal.<br>The synchronous signal forcibly reset the program counter to "zero", and the polarity is set by microcontroller. | Schmitt input |

| 31      | V <sub>DD</sub>  | —   | Power supply terminal.                                                                                                                                 | —             |

| 32      | XI               | I   | Crystal oscillator connection terminal / External clock input terminal.                                                                                | —             |

| 33      | XO               | O   | Crystal oscillator connection terminal.                                                                                                                | —             |

| 34      | V <sub>SS</sub>  | —   | Ground terminal.                                                                                                                                       | —             |

| PIN No.  | SYMBOL       | I/O | DESCRIPTION OF PIN FUNCTIONS                                                                                                 | REMARKS                                |

|----------|--------------|-----|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 35       | CKSL         | I   | Clock select terminal. "L" : 384fs<br>"H" : 512fs                                                                            | Pull-up resistor,<br>Schmitt input     |

| 36       | PLOFF        | I   | External oscillation / built-in VCO mode select terminal.<br>"L" : VCO mode<br>"H" : External oscillation mode               | Pull-down resistor                     |

| 37       | PD           | O   | Phase-difference output terminal.                                                                                            | Tri-state output                       |

| 38       | VSSA         | —   | Analog ground terminal.                                                                                                      | —                                      |

| 39       | AMPO         | O   | LPF amplifier output.                                                                                                        | —                                      |

| 40       | AMPI         | I   | LPF amplifier input.                                                                                                         | —                                      |

| 41       | VDDA         | —   | Analog power supply terminal.                                                                                                | —                                      |

| 42<br>44 | TES0<br>TES2 | I   | Test terminal, normally high or open.                                                                                        | Pull-up resistor,<br>Schmitt input     |

| 45       | RST          | I   | Reset signal input terminal.                                                                                                 | Pull-up resistor                       |

| 46       | CS           | I   | Chip select signal input terminal : when CS is at low active, data can be sent from the microcontroller.                     | Schmitt input                          |

| 47       | IFCD         | I   | Microcontroller command or data input mode select terminal.<br>"H" : commands, "L" : data.                                   | Schmitt input                          |

| 48       | IFDI         | I   | Microcontroller data input terminal. Commands and data are received LSB first.                                               | Schmitt input                          |

| 49       | IFDO         | O   | Data bus (DBUS) data output terminal.<br>Data bus data are sent to microcontroller LSB first.                                | Open-drain output,<br>Pull-up resistor |

| 50       | IFCK         | I   | Shift clock input terminal for microcontroller data.                                                                         | Schmitt input                          |

| 51       | ACK          | O   | Acknowledge signal output terminal for microcontroller.<br>Acknowledge signal output is when command and data parity are OK. | Open-drain output,<br>Pull-up resistor |

| 52       | VSS          | —   | Ground terminal.                                                                                                             | —                                      |

| 53<br>60 | TP16<br>TP9  | O   | Test data output terminal, normally open.                                                                                    | —                                      |

## DESCRIPTION OF OPERATION

### 1. Timing generator

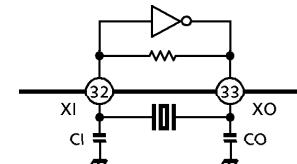

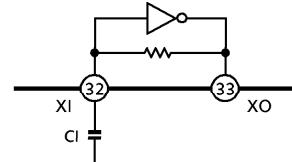

#### (1) Crystal oscillator

As Figure 1 shows, the clocks required for internal operations can be generated by connecting a crystal oscillator and capacitor. (Ploff = "H")

As Figure 2 shows, clocks can also be externally input to the XI terminal.

For external clock purposes, a crystal with a good starting potential and low CI value is recommended.

Fig.1 Self-exciting Crystal Oscillation

Fig.2 External Clock Input

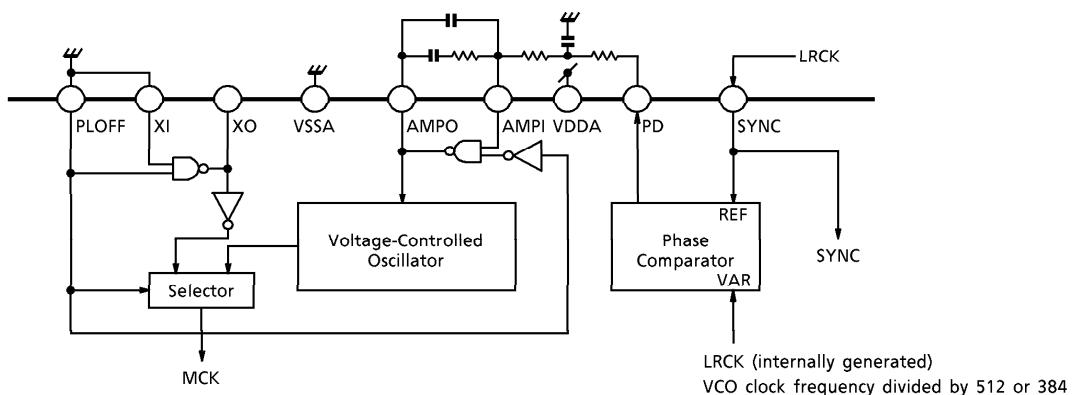

#### (2) Voltage-controlled oscillator (VCO)

The clocks required for internal operations are generated by an built-in VCO. The signal input from the SYNC pin is used as a reference. Configure the phase-locked loop as shown in Figure 3. A phase-difference (PD) signal is output from the PD terminal.

Fig.3 Example of Configuration of a Basic PLL Circuit

#### (2-1) Phase-difference output

A phase-difference (PD) signal between the REF and VAR signals are output from the PD terminal the PD signal as shown in Figure 4 below.

Fig.4 Example of Phase-Difference Output Timing

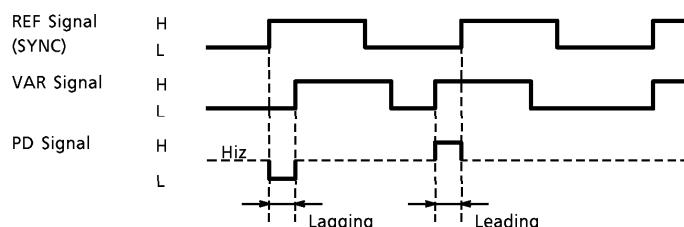

## 2. Setting audio data input/output format (data, channel clock, and bit clock)

The 16bit/24bit serial data input/output channel clocks (LR, ELRI0~1 and ELRO0~2) and bit clocks (FS64, FS32, EBCI0~1 and EBCO) can be either internally generated or externally input. The mode setting is effected by the microcontroller interface (control register). Figure 4 shows the data input/output clock pulse selector.

(1) The channel clock, bit clock and data format for data inputs SDI0~1 are selected by LRIS0~1, BCIS0~1 and SIFMT0~1 of control register 2 (CNT-R2). Table 1 (a) and (b) show setting modes for data inputs SDI0~1.

Table 1. (a) Setting Modes for Data Input SDI0

| CONTROL REGISTER 2<br>(CNT-R2) |       |        | FORMAT FOR DATA INPUT SDI0 |                                                         |                                             |                                                           |

|--------------------------------|-------|--------|----------------------------|---------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------|

| LRIS0                          | BCIS0 | SIFMT0 | DATA                       | BIT CLOCK                                               | CHANNEL CLOCK                               | DATA FORMAT                                               |

| 0                              | 0     | 0      | 16bit                      | 32fs (FS32 terminal)<br>Internally generated            | LR terminal<br>Internally generated         | MSB first                                                 |

| 0                              | 0     | 1      |                            | 64fs (FS64 terminal)<br>Internally generated            |                                             | LSB first                                                 |

| 0                              | 1     | 0      | 24bit                      | 32fs (EBCI0 terminal)<br>Externally input terminal      | ELRI0 terminal<br>Externally input terminal | MSB first, effective data before the change point of LRCK |

| 0                              | 1     | 1      |                            | 64fs (EBCI0 terminal)<br>Externally input terminal      |                                             | LSB first, effective data before the change point of LRCK |

| 1                              | 0     | 0      | 16bit                      | 32fs (EBCI0 terminal)<br>Externally input terminal      | ELRI0 terminal<br>Externally input terminal | MSB first                                                 |

| 1                              | 0     | 1      |                            | 64fs (EBCI0 terminal)<br>Externally input terminal      |                                             | LSB first                                                 |

| 1                              | 1     | 0      | 24bit                      | 48 / 64fs (EBCI0 terminal)<br>Externally input terminal | ELRI0 terminal<br>Externally input terminal | MSB first, effective data before the change point of LRCK |

| 1                              | 1     | 1      |                            | 48 / 64fs (EBCI0 terminal)<br>Externally input terminal |                                             | LSB first, effective data before the change point of LRCK |

Table 1. (b) Setting Modes for Data Input SDI1

| CONTROL REGISTER 2<br>(CNT-R2) |       |        | FORMAT FOR DATA INPUT SDI1 |                                                         |                                             |                                                           |

|--------------------------------|-------|--------|----------------------------|---------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------|

| LRIS1                          | BCIS1 | SIFMT1 | DATA                       | BIT CLOCK                                               | CHANNEL CLOCK                               | DATA FORMAT                                               |

| 0                              | 0     | 0      | 16bit                      | 32fs (FS32 terminal)<br>Internally generated            | LR terminal<br>Internally generated         | MSB first                                                 |

| 0                              | 0     | 1      |                            | 64fs (FS64 terminal)<br>Internally generated            |                                             | LSB first                                                 |

| 0                              | 1     | 0      | 24bit                      | 32fs (EBCI1 terminal)<br>Externally input terminal      | LR terminal<br>Internally generated         | MSB first, effective data before the change point of LRCK |

| 0                              | 1     | 1      |                            | 64fs (EBCI1 terminal)<br>Externally input terminal      |                                             | LSB first, effective data before the change point of LRCK |

| 1                              | 0     | 0      | 16bit                      | 32fs (EBCI1 terminal)<br>Externally input terminal      | ELRI1 terminal<br>Externally input terminal | MSB first                                                 |

| 1                              | 0     | 1      |                            | 64fs (EBCI1 terminal)<br>Externally input terminal      |                                             | LSB first                                                 |

| 1                              | 1     | 0      | 24bit                      | 48 / 64fs (EBCI1 terminal)<br>Externally input terminal | ELRI1 terminal<br>Externally input terminal | MSB first, effective data before the change point of LRCK |

| 1                              | 1     | 1      |                            | 48 / 64fs (EBCI1 terminal)<br>Externally input terminal |                                             | LSB first, effective data before the change point of LRCK |

(2) The channel clock, bit clock and data format for data outputs SDO0~2 are selected by LROS0~2, BCOS02 and SOFMT0~1 of control register 2 (CNT-R2).

Table 2 (a), (b), and (c) show setting modes for data outputs SDO0-2.

Table 2. (a) Setting Modes for Data Output SDO0

| CONTROL REGISTER |       |        |       |        | FORMATS FOR DATA OUTPUT SDO0 |                                              |                                         |                                          |                                                                                          |

|------------------|-------|--------|-------|--------|------------------------------|----------------------------------------------|-----------------------------------------|------------------------------------------|------------------------------------------------------------------------------------------|

| CNT-R2           |       |        |       | CNT-R1 | DATA                         | BIT CLOCK                                    |                                         | CHANNEL CLOCK                            | DATA FORMAT                                                                              |

| LROS0            | BCOS0 | SOFMT0 | LROS2 | EBCS   |                              |                                              |                                         |                                          |                                                                                          |

| 0                | 0     | 0      | *     | 0      | 16bit                        | 32fs (FS32 terminal)<br>Internally generated |                                         | LR terminal<br>Internally generated      | MSB first                                                                                |

| 0                | 1     | 0      | *     | 0      | 24bit                        | 64fs (FS64 terminal)<br>Internally generated |                                         | LR terminal<br>Internally generated      | MSB first, effective<br>data after the change<br>point of LRCK                           |

| *                | 0     | 0      | *     | 1      | 16bit                        | 32fs (FS32 terminal)<br>1/2 of EBC10 (64fs)  |                                         | ELRO terminal<br>Internally generated    | MSB first                                                                                |

| *                | 1     | 1      | 0     | 0      | 24bit                        | 64fs (FS64 terminal)<br>Internally generated |                                         | LR terminal (※1)<br>Internally generated | MSB first, effective<br>data after the change<br>point of LRCK<br>(8 clock shift output) |

| 1                | *     | 0      | *     | 0      | 16bit                        | 32fs                                         | EBCO<br>terminal<br>Externally<br>input | ELRO terminal<br>Externally input        | MSB first                                                                                |

|                  |       |        |       |        | 24bit                        | 48fs                                         |                                         |                                          | MSB first, effective<br>data after the change<br>point of LRCK                           |

| 1                | *     | 1      | 1     | 0      | 16bit                        | 48fs                                         |                                         | ELRO terminal<br>Externally input        | MSB first, effective<br>data after the change<br>point of LRCK<br>(8 clock shift output) |

|                  |       |        |       |        | 24bit                        | 64fs                                         |                                         |                                          |                                                                                          |

\* : Don't care

(※1) Clock output from LR terminal is input to ELRO terminal.

Table 2. (b) Setting Modes for Data Output SDO1

| CONTROL REGISTER |       |        |       |        | FORMATS FOR DATA OUTPUT SDO1 |                                              |                                   |                                          |                                                                                 |

|------------------|-------|--------|-------|--------|------------------------------|----------------------------------------------|-----------------------------------|------------------------------------------|---------------------------------------------------------------------------------|

| CNT-R2           |       |        |       | CNT-R1 | DATA                         | BIT CLOCK                                    |                                   | CHANNEL CLOCK                            | DATA FORMAT                                                                     |

| LROS1            | BCOS1 | SOFMT1 | LROS2 | EBCS   |                              |                                              |                                   |                                          |                                                                                 |

| 0                | 0     | 0      | *     | 0      | 16bit                        | 32fs (FS32 terminal)<br>Internally generated |                                   | LR terminal<br>Internally generated      | MSB first                                                                       |

| 0                | 1     | 0      | *     | 0      | 24bit                        | 64fs (FS64 terminal)<br>Internally generated |                                   | LR terminal<br>Internally generated      | MSB first, effective data after the change point of LRCK                        |

| *                | 0     | 0      | *     | 1      | 16bit                        | 32fs (FS32 terminal)<br>1/2 of EBCI0 (64fs)  |                                   | ELRO terminal<br>Internally generated    | MSB first                                                                       |

| *                | 1     | 1      | 0     | 0      | 24bit                        | 64fs (FS64 terminal)<br>Internally generated |                                   | LR terminal (※1)<br>Internally generated | MSB first, effective data after the change point of LRCK (8 clock shift output) |

| 1                | *     | 0      | *     | 0      | 16bit                        | 32fs                                         | EBCO terminal<br>Externally input | ELRO terminal<br>Externally input        | MSB first                                                                       |

|                  |       |        |       |        | 24bit                        | 48fs                                         |                                   |                                          | MSB first, effective data after the change point of LRCK                        |

| 1                | *     | 1      | 1     | 0      | 16bit                        | 48fs                                         |                                   |                                          | MSB first, effective data after the change point of LRCK (8 clock shift output) |

|                  |       |        |       |        | 24bit                        | 64fs                                         |                                   |                                          | MSB first, effective data after the change point of LRCK (8 clock shift output) |

Table 2. (c) Setting Modes for Data Output SDO2

| CONTROL REGISTER |       |       |      |        | FORMATS FOR DATA OUTPUT SDO2                 |                                   |                                          |                                                                                 |             |

|------------------|-------|-------|------|--------|----------------------------------------------|-----------------------------------|------------------------------------------|---------------------------------------------------------------------------------|-------------|

| CNT-R2           |       |       |      | CNT-R1 | DATA                                         | BIT CLOCK                         |                                          | CHANNEL CLOCK                                                                   | DATA FORMAT |

| LROS2            | BCOS2 | LROS2 | EBCS |        |                                              |                                   |                                          |                                                                                 |             |

| 0                | 0     | *     | 0    | 16bit  | 32fs (FS32 terminal)<br>Internally generated |                                   | LR terminal<br>Internally generated      | MSB first                                                                       |             |

| 0                | 1     | *     | 0    | 24bit  | 64fs (FS64 terminal)<br>Internally generated |                                   | LR terminal<br>Internally generated      | MSB first, effective data after the change point of LRCK                        |             |

| *                | 0     | *     | 1    | 16bit  | 32fs (FS32 terminal)<br>1/2 of EBCI0 (64fs)  |                                   | ELRO terminal<br>Internally generated    | MSB first                                                                       |             |

| *                | 1     | 0     | 0    | 24bit  | 64fs (FS64 terminal)<br>Internally generated |                                   | LR terminal (※1)<br>Internally generated | MSB first, effective data after the change point of LRCK (8 clock shift output) |             |

| 1                | *     | *     | 0    | 16bit  | 32fs                                         | EBCO terminal<br>Externally input | ELRO terminal<br>Externally input        | MSB first                                                                       |             |

|                  |       |       |      | 24bit  | 48fs                                         |                                   |                                          | MSB first, effective data after the change point of LRCK                        |             |

| 1                | *     | 1     | 0    | 16bit  | 48fs                                         |                                   |                                          | MSB first, effective data after the change point of LRCK (8 clock shift output) |             |

|                  |       |       |      | 24bit  | 64fs                                         |                                   |                                          | MSB first, effective data after the change point of LRCK (8 clock shift output) |             |

\* : Don't care

(※1) Clock output from LR terminal is input to ELRO terminal.

Fig.5 Data Input/Output Clock Selector

## 2. Data input and output circuits

### (1) Data input circuits

#### (1-1) Data input

Data are input in two's complement form, MSB first or LSB first, effective data before the change point of LRCK.

Input registers SIR0 and SIR1 are selectable for either 16bit or 24bit data length. The channel clock (LRCK) and bit clock (BCK) signals can be externally input independently as the timing signals for the data input to registers SIR0 and SIR1.

Mode using internally generated LRCK and BCK signals is also provided.

Input data are fetched by sensing the rise and fall of LRCK.

Input register SIR0 can select between input data SDI0 and SDI1 using the control registers of the microcontroller interface.

#### (1-2) Data input formats

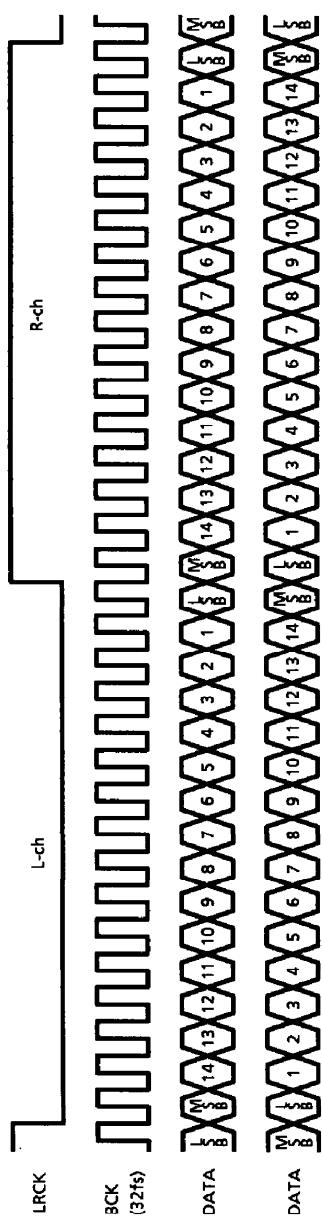

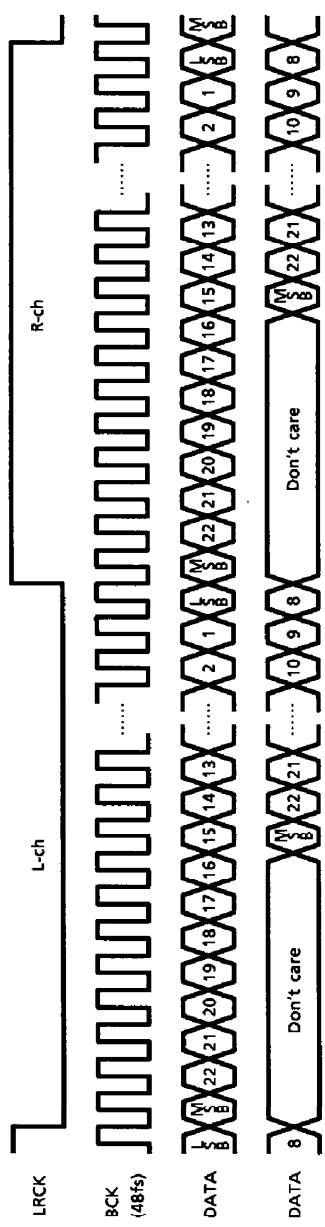

- When input data are 16bit/channel, see Figure 6 (a).

When BCK is 32fs, input is MSB first or LSB first.

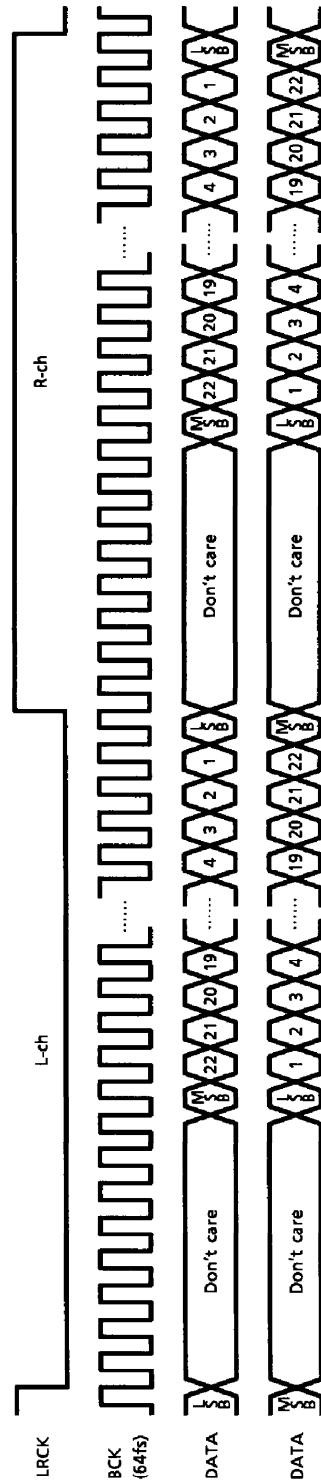

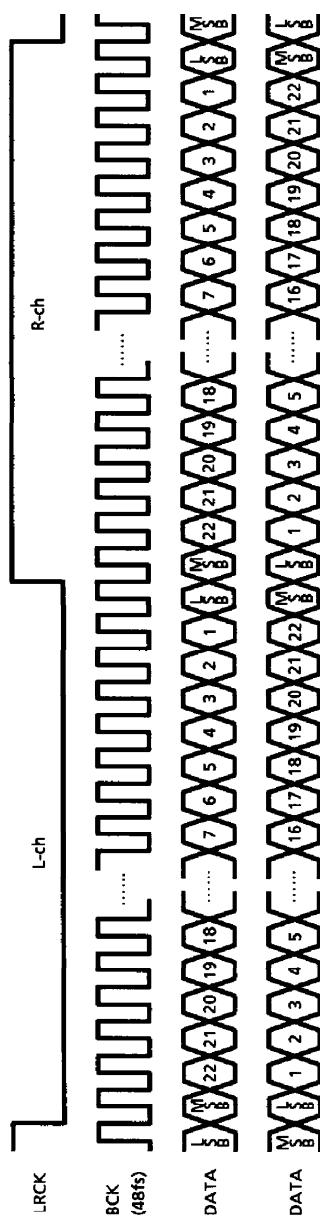

- When input data is 24bit/channel, see Figures 6 (b) and 6 (c).

When BCK is 48fs (external input), input is MSB first or LSB first.

When BCK is 64fs, input is MSB first or LSB first, with effective data before the change point of LRCK.

Fig.6 (a) 16bit Data Input Format

Fig.6 (b) 24bit Data Input Format

Fig.6 (c) 24bit Data Input Format

## (2) Data output circuits

### (2-1) Data output

Data are output in twos complement form, MSB first, with effective data after the change point of LRCK or 8 clock shift with effective data before the change point of LRCK.

Output registers SOR0, SOR1 and SOR2 are selectable for either 16bit or 24bit data.

The channel clock (LRCK) and bit clock (BCK) signals can be externally input independently as the timing signals for the data output to registers SOR0, SOR1 and SOR2.

Mode using internally generated LRCK and BCK signals is also provided.

Input data are output to registers SOR0, SOR1 and SOR2 by sensing the rise and fall of LRCK.

Output register SIR0 can select between output data SDI0 and SDI1 using the control registers of the microcontroller interface.

### (2-2) Data output formats

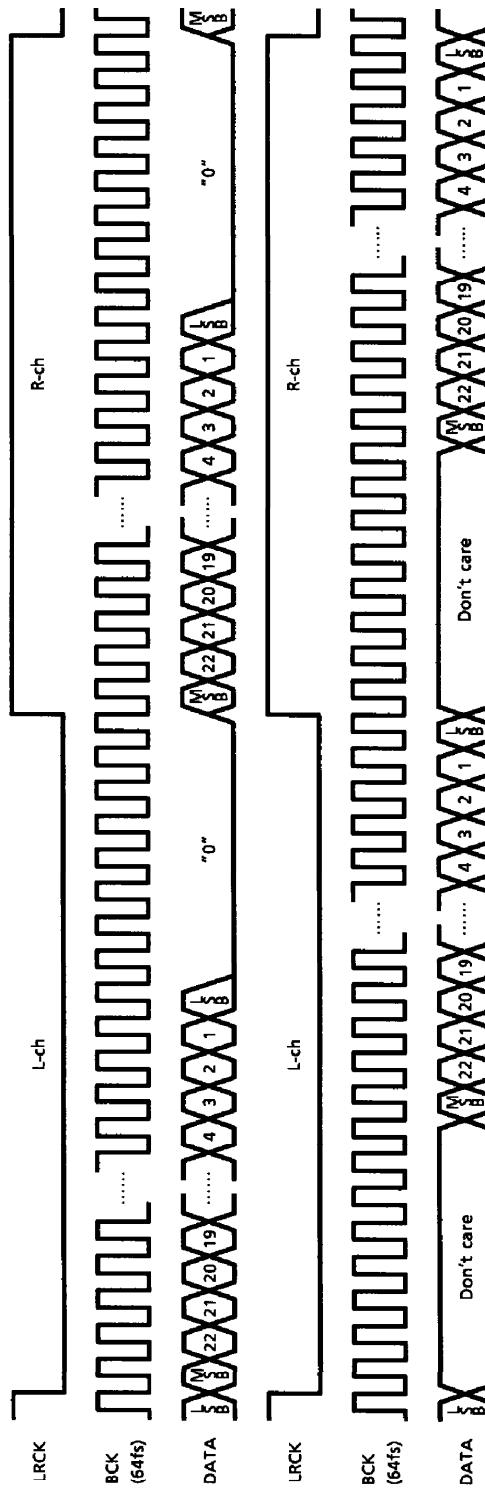

16bit or 24bit data are output from the data bus starting from the MSB.

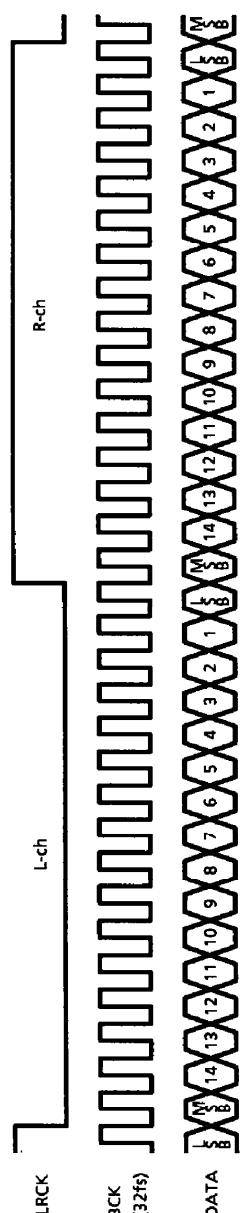

- When output data are 16bit/channel, see Figure 7 (a).

When BCK is 32fs, output is MSB first.

- When output data are 24bit/channel, see Figures 7 (b) and 7 (c).

When BCK is 48fs (external output), output is MSB first or the 8 clock shifted highest 16bit data with effective data before the change point of LRCK.

When BCK is 64fs, output is MSB first with effective data after the change point of LRCK or 8 clock shift with effective data before the change point of LRCK.

Fig. 7 (a) 16bit Data Output Format

Fig. 7 (b) 24bit Data Output Format

Fig. 7 (c) 24bit Data Output Format

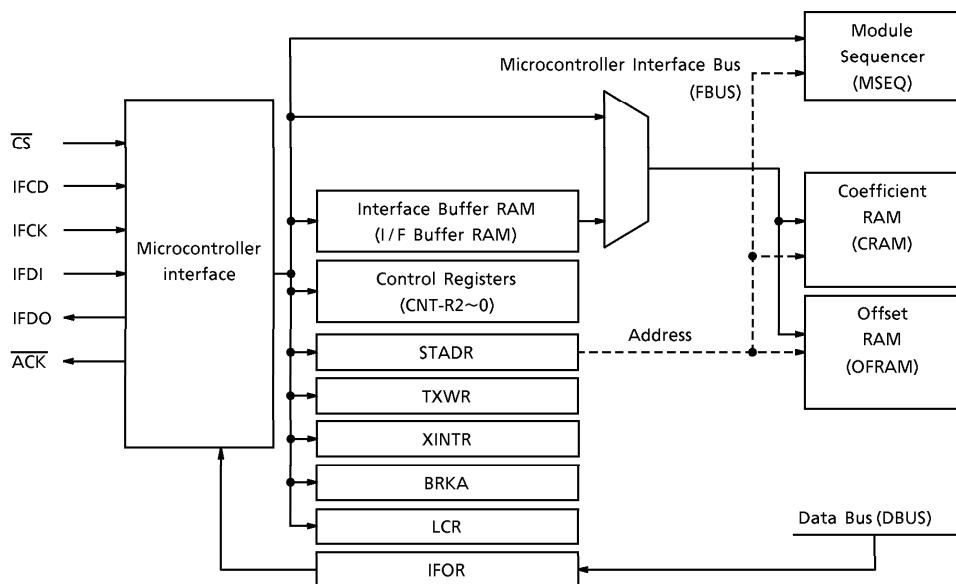

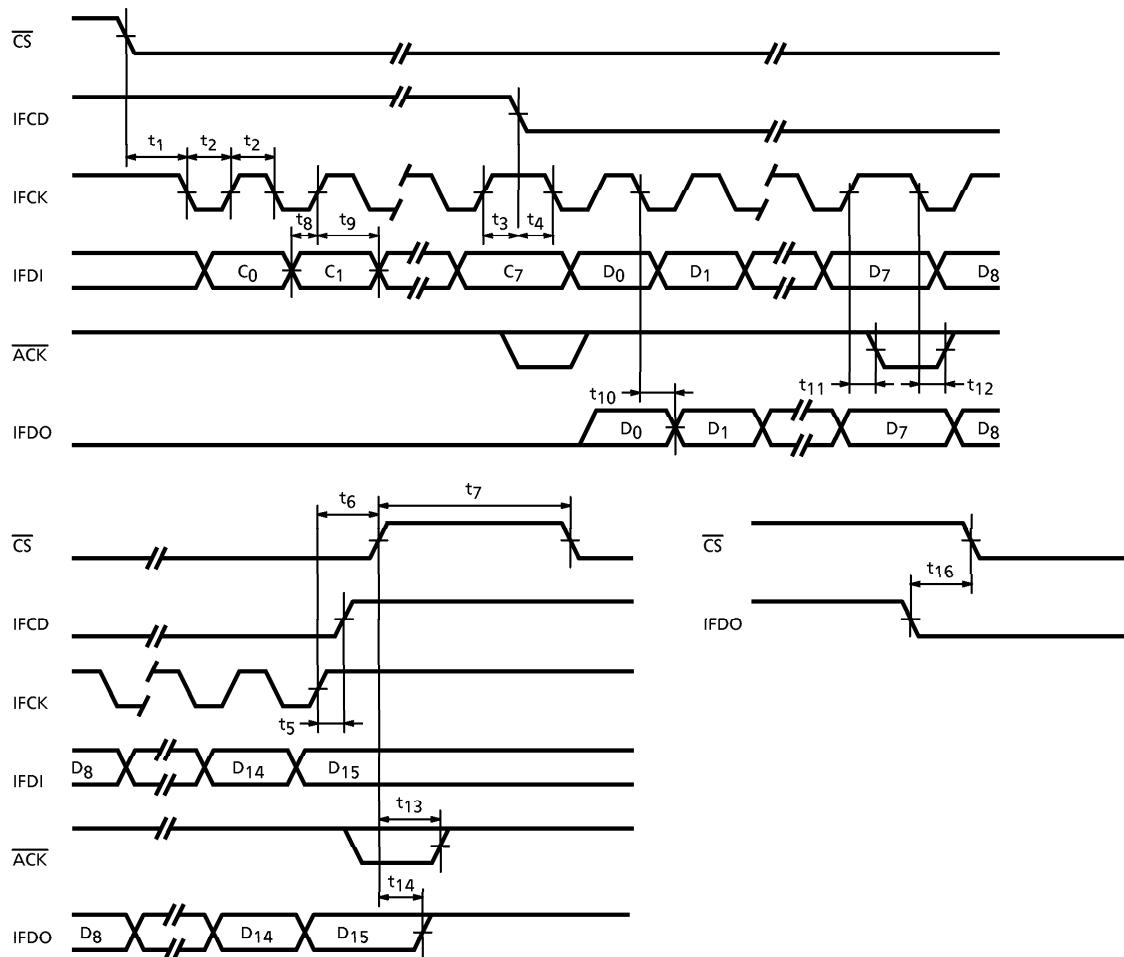

### 3. Microcontroller interface circuit

The TC9332F transfers synchronous serial data to the host microcontroller using the  $\overline{CS}$ , IFCD, IFCK, IFDI, IFDO and  $\overline{ACK}$  terminals. The microcontroller is used to set data modes, set data in the coefficient RAM (CRAM) and offset RAM (OFRAM), set the module sequencer (MSEQ), and read data from the internal data bus (DBUS).

Fig.8 Structure of Microcontroller Interface Block

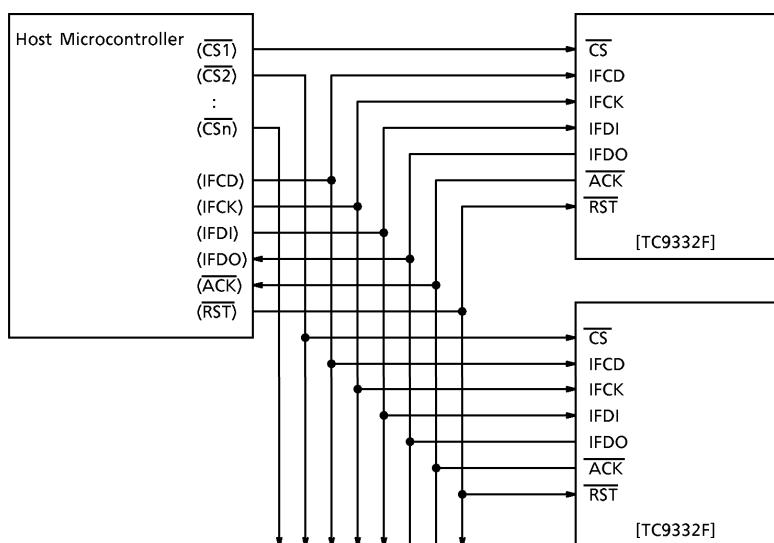

An example of a connection with the host microcontroller is shown below in Figure 9.

Fig.9 Relationship between Host Microcontroller and TC9332F

The functions of the signals on the microcontroller interface pins are as shown below:

- $\overline{CS}$  signal (input) : Sets TC9332F data receive to active.

- IFCD signal (input) : Distinguishes between command words and data words.

- IFCK signal (input) : Data signal shift clock

- IFDI signal (input) : Data input signal

- $\overline{ACK}$  signal (output) : Acknowledges result of parity check.

- IFDO signal (output) : Data output signal. Outputs data from the data bus (DBUS) starting from the LSB. Data are output at the rising edge of the IFCK signal.

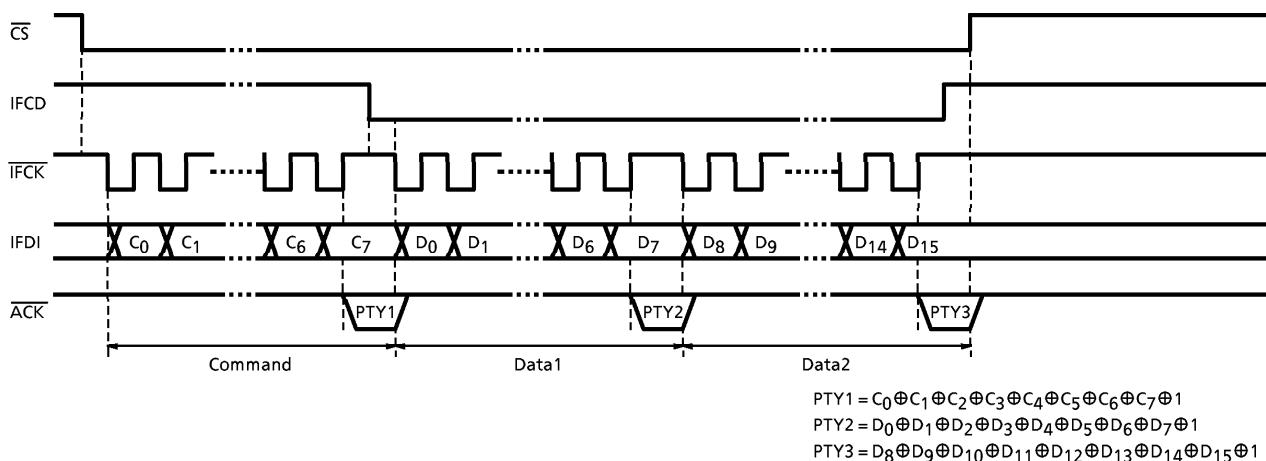

(1) Data transmission format

At idle, the  $\overline{CS}$ , IFCD, IFCK and IFDI signals are high-level.

There are two transfer modes that can be used, depending on the length of data to be transferred.

There are two types of data transmitted : 1 byte command words, and data words composed of either 1 or 2 bytes. The number of bytes per data word varies according to the command type. Data are transmitted LSB first, and the dummy bit at the MSB of the transmitted data is set to "0".

(1-1) 8bit transfer mode

Set ICKS on bit 3 of control register 1 to low. (Low is the initial value at reset). Efficient data transfer can be carried out over the serial I/O port of an ordinary microcontroller.

Figure10 (a) shows an example of timing for the 8bit transfer mode.

Fig.10 (a) Example of Timing for 8bit Transfer Mode

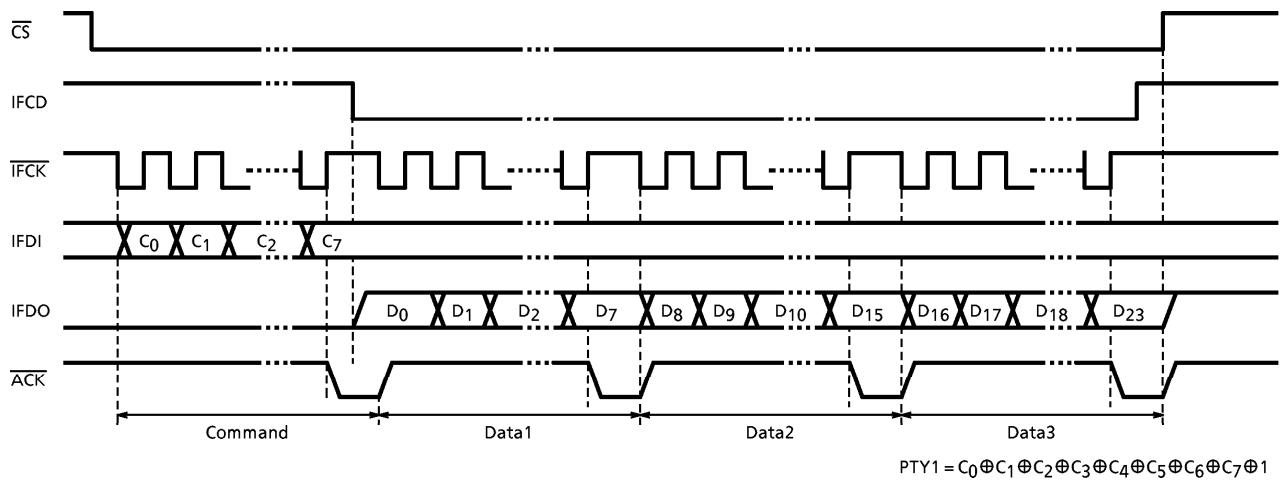

## (1-2) 9bit transfer mode

Set ICKS on bit 3 of control register 1 to high. Since low is the initial value at reset, 8bit data transfer can be performed until ICKS is set to high. The unit of transfer is 9bit, an 8bit data plus 1bit for ODD parity. If the result of the parity check is NG, the TC9332F does not fetch the set data, so always be sure to input the correct parity. Figure 10 (a) shows an example of timing for the 8bit transfer mode.

Fig.10 (b) Example of Timing for 9bit Transfer Mode

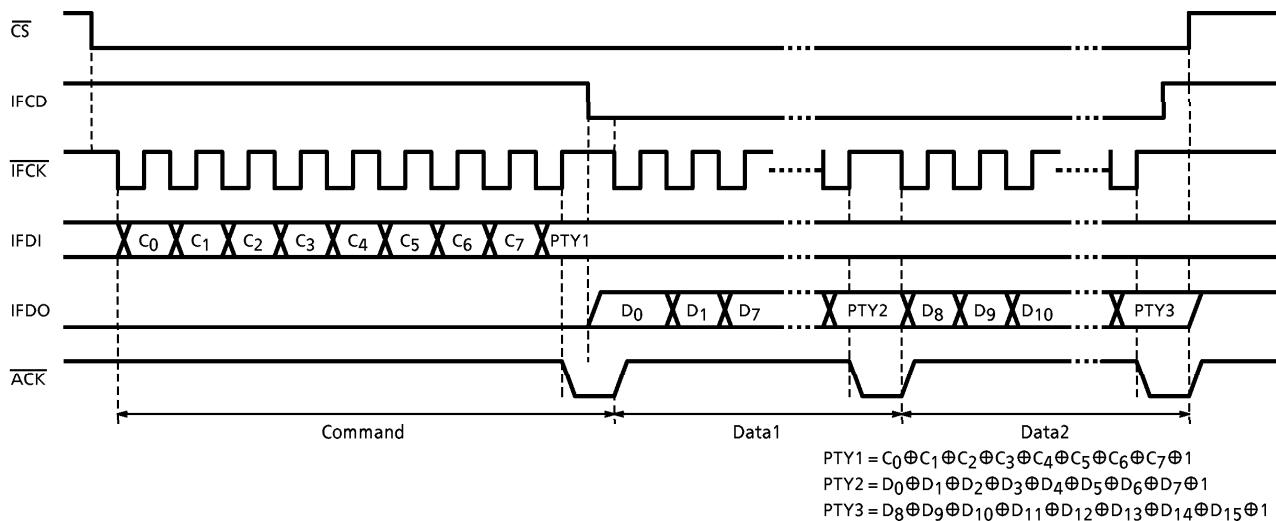

## (2) Data bus (DBUS) data output format

At idle, the CS, IFCD, IFCK and IFDI signals are "H" level.

There are two transfer modes that can be used, depending on the length of data to be transferred.

Figure 11 shows examples of timing for the 8bit and 9bit transfer modes.

The data transmitted from the microcontroller is a 1 byte command word.

The data output to the microcontroller are the 24bit on the internal DBUS or the upper 16bit, and are sent LSB first.

Fig.11 (a) Example of Timing for 8bit Transfer Mode (3byte Setting)

Fig.11 (b) Example of Timing for 9bit Transfer Mode (2byte Setting)

### (3) Control commands

There are 12 commands used to control the TC9332F from a microcontroller. Table 3 shows the commands and command data.

Table 3. Control Commands

| COMMAND WORD (HEX) | DATA WORD (Exclude parity bit) |                   | REGISTER / MEMORY |             | FETCH SYNC | CONTINUOUS TRANSMISSION |

|--------------------|--------------------------------|-------------------|-------------------|-------------|------------|-------------------------|

|                    | BIT LENGTH USED                | BYTES TRANSMITTED | WRITE DESTINATION | READ SOURCE |            |                         |

| FF~20              | —                              | —                 | Unused            | —           | —          | —                       |

| 1F                 | 16                             | 2                 | CNT-R2            | —           | Async      | No                      |

| 1E                 | 11                             | 2                 | CNT-R1            | —           | Async      | No                      |

| 1D                 | 9                              | 2                 | CNT-R0            | —           | sync       | No                      |

| 1C                 | 9                              | 2                 | STAD-R            | —           | Async      | No                      |

|                    | 4                              | 1                 |                   |             |            |                         |

| 1B                 | 4                              | 1                 | TXW-R             | —           | Async      | No                      |

| 1A                 | 10                             | 2                 | MSEQ              | —           | sync       | YES                     |

| 19                 | 16                             | 2                 | CRAM              | —           | Async      | YES                     |

| 18                 | 16                             | 2                 | OFRAM             | —           | Async      | YES                     |

| 17                 | 3                              | 1                 | XINT-R            | —           | sync       | No                      |

| 16                 | 10                             | 2                 | BRKA-R            | —           | Async      | No                      |

| 15                 | 8                              | 1                 | LC-R              | —           | Async      | No                      |

| 14                 | 24<br>Upper 16                 | 3<br>2            | —                 | IFDO-R      | —          | No                      |

| 13~00              | —                              | —                 | Unused            | —           | —          | —                       |

(Notes): Settings for STAD-R (1Ch) are as follows:

9bit : CRAM address

9bit : OFRAM address

4bit : MSEQ address

## (4) Control registers and dedicated interface registers

## (4-1) Control register 2 (CNT-R2)

(\* : default value)

| BIT | SYMBOL | DESCRIPTION OF FINCTION                                                                                                                   |                                                  |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| 15  | LRIS1  | Selects channel clock or bit clock for audio serial data input from the SDI1 terminal.                                                    | 0*                                               |

|     |        |                                                                                                                                           | 1 ELRI1 / EBCI1                                  |

| 14  | BCIS1  | Selects bit length of audio serial data input from the SDI1 terminal.                                                                     | 0* 16bit                                         |

|     |        |                                                                                                                                           | 1 24bit                                          |

| 13  | SIFMT1 | Selects format of audio serial data input from the SDI1 terminal.                                                                         | 0* MSB first                                     |

|     |        |                                                                                                                                           | 1 LSB first                                      |

| 12  | LRIS0  | Selects a channel clock or bit clock for audio serial data input from the SDI0 terminal.                                                  | 0* Generates internally                          |

|     |        |                                                                                                                                           | 1 ELRIO / EBCIO                                  |

| 11  | BCIS0  | Selects bit length of audio serial data input from the SDI0 terminal.                                                                     | 0* 16bit                                         |

|     |        |                                                                                                                                           | 1 24bit                                          |

| 10  | SIFMT0 | Selects format of audio serial data input from the SDI0 terminal.                                                                         | 0* MSB first                                     |

|     |        |                                                                                                                                           | 1 LSB first                                      |

| 9   | SISEL  | Selects input terminal for input register SDI0.                                                                                           | 0* SDI0                                          |

|     |        |                                                                                                                                           | 1 SDI1                                           |

| 8   | LROS2  | Selects a channel clock or bit clock for audio serial data output to the SDO2 terminal. (Note)                                            | 0* Generates internally                          |

|     |        |                                                                                                                                           | 1 ELRO / EBCO                                    |

| 7   | BCOS2  | Selects an internally generated bit clock for audio serial data output to the SDO2 terminal.                                              | 0* FS32 (16bit / ch)                             |

|     |        |                                                                                                                                           | 1 FS64 (32bit / ch)                              |

| 6   | SOFMT2 | Selects whether audio serial data output to the SDO2 pin are to be effective data after the change point of LRCK or 8 clock shifted.      | 0* Effective data after the change point of LRCK |

|     |        |                                                                                                                                           | 1 8 clock shifted                                |

| 5   | LROS1  | Selects a channel clock or bit clock for audio serial data output to the SDO1 terminal. (Note)                                            | 0* Generates internally                          |

|     |        |                                                                                                                                           | 1 ELRO / EBCO                                    |

| 4   | BCOS1  | Selects an internally generated bit clock for audio serial data output to the SDO1 terminal.                                              | 0* FS32 (16bit / ch)                             |

|     |        |                                                                                                                                           | 1 FS64 (32bit / ch)                              |

| 3   | SOFMT1 | Selects whether audio serial data output to the SDO1 terminal are to be effective data after the change point of LRCK or 8 clock shifted. | 0* Effective data after the change point of LRCK |

|     |        |                                                                                                                                           | 1 8 clock shifted                                |

| 2   | LROS0  | Selects a channel clock or bit clock for audio serial data output to the SDO0 terminal. (Note)                                            | 0* Generates internally                          |

|     |        |                                                                                                                                           | 1 ELRO / EBCO terminal input                     |

| 1   | BCOS0  | Selects an internally generated bit clock for audio serial data output to the SDO0 terminal.                                              | 0* FS32 (16bit / ch)                             |

|     |        |                                                                                                                                           | 1 FS64 (32bit / ch)                              |

| 0   | SOFMT0 | Selects whether audio serial data output to the SDO0 terminal are to be effective data after the change point of LRCK or 8 clock shifted. | 0* Effective data after the change point of LRCK |

|     |        |                                                                                                                                           | 1 8 clock shifted                                |

※ Normally set only once at initialization.

Data can be set in CNT-R2 asynchronously with the SYNC signal.

(Note) When a channel clock or bit clock is externally input, (LROS bits 2~0 set to "1"), the data can be output to pins SDO2~0 with 8 clock shifted by setting SOFMT~0.

Data can also be output with 8 clock shifted by program (operation) without the above setting.

## (4-2) Control register 1 (CNT-R1)

(\* : default value)

| BIT | SYMBOL     | DESCRIPTION OF FUNCTIONS                                                                                                                                                             |    |                      |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------------------|

| 10  | ZST        | Switches coefficient ROM mode (for dis logarithm table).                                                                                                                             | 0  | 2-cycle              |

|     |            |                                                                                                                                                                                      | 1* | 1-cycle              |

| 9   | EMU        | Test emulator mode                                                                                                                                                                   | 0* | Normal               |

|     |            |                                                                                                                                                                                      | 1  | SYNC = ELRI1         |

| 8   | SYNCS      | Selects internal generation or external input (from SYNC terminal) of SYNC signal.                                                                                                   | 0* | Generates internally |

|     |            |                                                                                                                                                                                      | 1  | Inputs externally    |

| 7   | SYNCP      | Switches SYNC signal polarity.                                                                                                                                                       | 0* | Fall                 |

|     |            |                                                                                                                                                                                      | 1  | Rise                 |

| 6   | SYRC       | Resets the coefficient pointer (CP) for each SYNC signal.                                                                                                                            | 0* | Enable               |

|     |            |                                                                                                                                                                                      | 1  | Disable              |

| 5   | SYRO       | Resets the offset address pointer (OFP) for each SYNC signal.                                                                                                                        | 0* | Enable               |

|     |            |                                                                                                                                                                                      | 1  | Disable              |

| 4   | EBCS       | Modifies LROS2-0, BCOS2-0 and LR terminal output signals.                                                                                                                            | 0* | Disable (normal)     |

|     |            |                                                                                                                                                                                      | 1  | Enable               |

| 3   | ICKS       | Selects transfer data length by microcontroller interface.                                                                                                                           | 0* | 8bit                 |

|     |            |                                                                                                                                                                                      | 1  | 9bit                 |

| 2   | IFOS       | Selects output format for data (24bit) read from IFOR (DBUS).                                                                                                                        | 0* | Upper 16bit          |

|     |            |                                                                                                                                                                                      | 1  | 24bit                |

| 1   | DLSEP      | Divides the delay RAM (DLRAM) into a delay area and a data table area.                                                                                                               | 0* | Divides.             |

|     |            |                                                                                                                                                                                      | 1  | Does not divide.     |

| 0   | ACMP<br>RQ | Overwrites when the value of the CRAM or OFRAM pointer matches the overwrite counter address (automatically set to "0" after executing batch overwrite of the interface buffer RAM.) | 0* | Disable              |

|     |            |                                                                                                                                                                                      | 1  | Enable               |

※ Normally set only once at initialization.

Data can be set in CNT-R1 asynchronously with the SYNC signal.

## (4-3) Control register 0 (CNT-R0)

(\* : default value)

| BIT | SYMBOL | DESCRIPTION OF FUNCTIONS                                                                                          |    |                   |

|-----|--------|-------------------------------------------------------------------------------------------------------------------|----|-------------------|

| 8   | SQALL  | Renders instruction non-operative and clears the flag.                                                            | 0  | Off (RUN)         |

|     |        |                                                                                                                   | 1* | On (NOP)          |

| 7   | BRKRQ  | Setting this bit to "1" after the break address (BRKA) of the program counter is set executes a break.            | 0* | Break off         |

|     |        |                                                                                                                   | 1  | Break on          |

| 6   | DBMRQ  | Requests data read from DBUS.                                                                                     | 0* | Does not request. |

|     |        |                                                                                                                   | 1  | Requests.         |

| 5   | LCMSK  | Compares the loop counter value during data read from DBUS.                                                       | 0* | Compares.         |

|     |        |                                                                                                                   | 1  | Does not compare. |

| 4   | LCSEL  | Selects the counter (LC0 or LC1) to be compared when comparing the loop counter value during data read from DBUS. | 0* | LC0               |

|     |        |                                                                                                                   | 1  | LC1               |

| 3   | INMT   | Mutes input from the SDI0 and SDI1 terminals.                                                                     | 0  | Mute off          |

|     |        |                                                                                                                   | 1* | Mute on           |

| 2   | OUTMT2 | Mutes output to the SDO2 terminal.                                                                                | 0  | Mute off          |

|     |        |                                                                                                                   | 1* | Mute on           |

| 1   | OUTMT1 | Mutes output to the SDO1 terminal.                                                                                | 0  | Mute off          |

|     |        |                                                                                                                   | 1* | Mute on           |

| 0   | OUTMT0 | Mutes output to the SDO0 terminal.                                                                                | 0  | Mute off          |

|     |        |                                                                                                                   | 1* | Mute on           |

※ Data are read from CNT-R0 synchronously with the SYNC signal.

## (4-4) Dedicated interface registers

## Start address register (STADR)

This register sets the address to start writing data to CRAM, OFRAM and MSEQ. It consists of a presetable up-counter. (9bit)

|       | 8          | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------------|-----|-----|-----|-----|-----|-----|-----|-----|

| CRAM  | RA8        | RA7 | RA6 | RA5 | RA4 | RA3 | RA2 | RA1 | RA0 |

| OFRAM | 0          | 0   | 0   | RA5 | RA4 | RA3 | RA2 | RA1 | RA0 |

| MSEQ  | don't care |     |     |     |     | RA3 | RA2 | RA1 | RA0 |

When data are set in MSEQ, data are sent 1 byte at a time.

※ Data are set in STADR asynchronously with the SYNC signal.

## Transfer exchange write address register (TXWR)

When ACMPRQ in control register 1 (CNT-R1) is set to "1", this register sets the length of data to be overwritten to CRAM or OFRAM using interface buffer RAM. Overwrites up to 16word are supported. (4bit)

| NUMBER OF WORDS<br>OVERWRITTEN | TXWR |      |      |      |

|--------------------------------|------|------|------|------|

|                                | TXW3 | TXW2 | TXW1 | TXW0 |

| 1                              | 0    | 0    | 0    | 0    |

| 2                              |      | :    |      | 1    |

| :                              |      |      |      |      |

| 15                             | 1    | 1    | 1    | 0    |

| 16                             | 1    | 1    | 1    | 1    |

※ Data can be set in TXWR asynchronously with the SYNC signal.

## Module sequencer (MSEQ)

The module sequencer sets the sequence in which the subroutines grouped in program ROM are called.

It has a 16word x 10bit structure, and data are set by the microcontroller one word at a time at the program ROM sequence start address. Set the 4bit address of the sequencer, which sets the data store sequence, in STADR.

Data cannot be transferred to the MSEQ using the interface buffer RAM.,

※ MSEQ data is read in synchronously with the SYNC signal.

## Coefficient RAM (CRAM)

The coefficient RAM has a 320word x 16bit structure, and data can be changed one word at a time during each sampling period by the microcontroller communication procedure. Using the interface buffer RAM, 16word can be overwritten during each sampling period.

※ Data can be set in CRAM asynchronously with the SYNC signal.

(during continuous setting)

## Offset RAM (OFRAM)

The offset RAM has a 64word x 16bit structure, and the overwriting procedure is similar to that of the CRAM.

※ Data can be set in OFRAM asynchronously with the SYNC signal.

(during continuous setting)

## External interrupt register (XINTR)

The external interrupt register sets data in IFF2-0, which are allocated to the conditional jump flag (F) field. (3bit)

| FLAG FIELD |      |      | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|------------|------|------|----------------|----------------|----------------|

| IFF2       | IFF1 | IFF0 |                |                |                |

| Off        | Off  | Off  | 0              | 0              | 0              |

| Off        | Off  | On   | 0              | 0              | 1              |

| Off        | On   | Off  | 0              | 1              | 0              |

| On         | Off  | Off  | 1              | 0              | 0              |

※ XINTR data are read synchronously with the SYNC signal.

**Break address (BRKAR) register**

This register sets the break address. Continuous comparison is made with the program counter (PC) and when BRKRQ of the control register is on, program execution is stopped. Since DBUS data are fetched to IFDOR when the value of the PC matches, it is possible to turn BRKRQ off and read the internal data while program execution is in progress. (10bit)

※ Data can be set in BRKAR asynchronously with the SYNC signal.

**Loop counter compare reference register (LCR)**

When reading break or DBUS data, either of loop counters LC0 or LC1 is being compared along with the PC value, this register stores the value of the loop counter to be compared. (8bit)

Which of the loop counters is being compared is set by LCSEL of control register 0 (CNT-R0). When break or DBUS data have been read, LCR is automatically decremented by 1.

※ Data can be set in LCR asynchronously with the SYNC signal.

**Interface data output register (IFDOR)**

This is a buffer register that can read DBUS data. (24bit)

The microcontroller can read data from IFDOR serially from the LSB. It is also possible to read only the upper 16bit by setting IFOS of control register 1 (CNT-R1).

**MAXIMUM RATINGS (Ta = 25°C)**

| CHARACTERISTIC        | SYMBOL           | RATING                     | UNIT |

|-----------------------|------------------|----------------------------|------|

| Power Supply Voltage  | V <sub>DD</sub>  | -0.3~6.0                   | V    |

| Input Voltage         | V <sub>IN</sub>  | -0.3~V <sub>DD</sub> + 0.3 | V    |

| Power Dissipation     | P <sub>D</sub>   | 1250                       | mW   |

| Operating Temperature | T <sub>opr</sub> | -40~85                     | °C   |

| Storage Temperature   | T <sub>stg</sub> | -55~150                    | °C   |

**ELECTRICAL CHARACTERISTICS (Unless otherwise specified, Ta = 25°C, V<sub>DD</sub> = 5V)****DC characteristics**

| CHARACTERISTIC                                            | SYMBOL           | TEST CIR-CUIT | TEST CONDITION               | MIN. | TYP. | MAX. | UNIT |

|-----------------------------------------------------------|------------------|---------------|------------------------------|------|------|------|------|

| Operating Power Supply Voltage                            | V <sub>DD</sub>  | —             | Ta = -40~85°C                | 4.75 | 5.0  | 5.25 | V    |

| Power Supply Current-1<br>(no load, external oscillation) | I <sub>DD1</sub> | —             | f <sub>opr</sub> = 24.576MHz | —    | 75   | 100  | mA   |

|                                                           |                  |               | f <sub>opr</sub> = 18.432MHz | —    | 55   | 75   |      |

| Power Supply Current-2<br>(no load, VCO oscillation)      | I <sub>DD2</sub> | —             | f <sub>opr</sub> = 24.576MHz | —    | 80   | 100  |      |

|                                                           |                  |               | f <sub>opr</sub> = 18.432MHz | —    | 65   | 85   |      |

| CHARACTERISTIC | SYMBOL | TEST CIR-UCIT | TEST CONDITION | MIN. | TYP. | MAX. | UNIT |

|----------------|--------|---------------|----------------|------|------|------|------|

|----------------|--------|---------------|----------------|------|------|------|------|

## Clock terminals (XI, XO)

|                                |                 |           |   |                          |             |     |     |     |            |

|--------------------------------|-----------------|-----------|---|--------------------------|-------------|-----|-----|-----|------------|

| Input Voltage                  | "H" Level       | $V_{IH1}$ | — | XI terminal              |             | 3.5 | —   | —   | V          |

|                                | "L" Level       | $V_{IL1}$ | — |                          |             | —   | —   | 1.5 |            |

| Output Voltage                 | "H" Level       | $V_{OH1}$ | — | $I_{OH} = -3.0\text{mA}$ | XO terminal | 4.5 | —   | —   |            |

|                                | "L" Level       | $V_{OL1}$ | — | $I_{OL} = 6.0\text{mA}$  |             | —   | —   | 0.5 |            |

| Operation Power Supply Voltage | R <sub>fb</sub> | —         | — |                          |             | —   | 100 | 500 | k $\Omega$ |

## Input terminals

|                       |           |           |   |                      |      |     |     |     |               |  |

|-----------------------|-----------|-----------|---|----------------------|------|-----|-----|-----|---------------|--|

| Input Voltage         | "H" Level | $V_{IH2}$ | — | (*1)                 |      | 4.2 | —   | —   | V             |  |

|                       | "L" Level | $V_{IL2}$ | — |                      |      | —   | —   | 0.8 |               |  |

| Input Leakage Current | "H" Level | $I_{IH2}$ | — | $V_{IN} = V_{DD}$    | (*1) | —   | —   | 10  | $\mu\text{A}$ |  |

|                       | "L" Level | $I_{IL2}$ | — | $V_{IN} = 0\text{V}$ |      | -10 | —   | —   |               |  |

| Threshold Voltage     | "H" Level | $V_P$     | — | (*2)                 |      | —   | 3.2 | —   | V             |  |

|                       | "L" Level | $V_N$     | — |                      |      | —   | 1.8 | —   |               |  |

| Hysteresis Voltage    |           | $V_H$     | — | (*2)                 |      | —   | 0.6 | —   | V             |  |

| Input Leakage Current | "H" Level | $I_{IH3}$ | — | $V_{IN} = V_{DD}$    | (*2) | —   | —   | 10  | $\mu\text{A}$ |  |

|                       | "L" Level | $I_{IL3}$ | — | $V_{IN} = 0\text{V}$ |      | -10 | —   | —   |               |  |

(\*1) SDI0~1, Ploff,  $\overline{RST}$  : CKSL, TEST0~2 (Schmitt input terminals with pull-up resistor)(\*2) SYNC, ELRI0~1, ELRO, EBCI0~1, EBCO,  $\overline{CS}$ , IFCD, IFDI, IFCK (Schmitt input terminals)

## Output terminals

|                |           |           |   |                          |      |     |   |     |   |

|----------------|-----------|-----------|---|--------------------------|------|-----|---|-----|---|

| Output Voltage | "H" Level | $V_{OH2}$ | — | $I_{OH} = -1.0\text{mA}$ | (*3) | 4.5 | — | —   | V |

|                | "L" Level | $V_{OL2}$ | — | $I_{OL} = 1.0\text{mA}$  |      | —   | — | 0.5 |   |

| Output Voltage | "H" Level | $V_{OH3}$ | — | $I_{OH} = -3.0\text{mA}$ | (*4) | 4.5 | — | —   |   |

|                | "L" Level | $V_{OL3}$ | — | $I_{OL} = 5.0\text{mA}$  |      | —   | — | 0.5 |   |

| Output Voltage | "H" Level | $V_{OH4}$ | — | $I_{OH} = -0.6\text{mA}$ | (*5) | 4.5 | — | —   |   |

|                | "L" Level | $V_{OL4}$ | — | $I_{OL} = 0.6\text{mA}$  |      | —   | — | 0.5 |   |

(\*3) SDO0~2

(\*4) FS64, FS32, WCK, LR

(\*5) AMPO

## Three state output terminals (PD)

|                            |           |           |   |                                          |   |     |   |          |               |

|----------------------------|-----------|-----------|---|------------------------------------------|---|-----|---|----------|---------------|

| Output Voltage             | "H" Level | $V_{OH5}$ | — | $I_{OH} = -3.0\text{mA}$                 | — | 4.5 | — | —        | V             |

|                            | "L" Level | $V_{OL5}$ | — | $I_{OL} = 5.0\text{mA}$                  |   | —   | — | 0.5      |               |

| Output Off-leakage Current | $I_{OZ5}$ |           | — | $V_{OH} = V_{DD}$ , $V_{OL} = 0\text{V}$ | — | —   | — | $\pm 10$ | $\mu\text{A}$ |

Open-drain output terminals (IFDO,  $\overline{ACK}$ )

|                             |           |   |                         |   |   |          |               |

|-----------------------------|-----------|---|-------------------------|---|---|----------|---------------|

| "L" Level Output Voltage    | $V_{OL7}$ | — | $I_{OL} = 5.0\text{mA}$ | — | — | 0.5      | V             |

| Output Open Leakage Current | $I_{OZ7}$ | — | $V_{OH} = V_{DD}$       | — | — | $\pm 10$ | $\mu\text{A}$ |

| CHARACTERISTIC | SYMBOL | TEST CIR-UCIT | TEST CONDITION | MIN. | TYP. | MAX. | UNIT |

|----------------|--------|---------------|----------------|------|------|------|------|

|----------------|--------|---------------|----------------|------|------|------|------|

Pull-up and pull-down register terminals

|                      |       |   |      |   |      |     |    |

|----------------------|-------|---|------|---|------|-----|----|

| Pull-up Resistor     | RUP   | — | (*6) | — | 35   | 200 | kΩ |

| Pull-down Resistor-1 | Rdwn1 | — | (*7) | — | 25   | 200 |    |

| Pull-down Resistor-2 | Rdwn2 | — | (*8) | — | 0.25 | 80  |    |

(\*6) IFDO,  $\overline{RST}$ ,  $\overline{ACK}$ , CKSL, TES0~2

(\*7) Ploff

(\*8) XI

#### AC CHARACTERISTICS

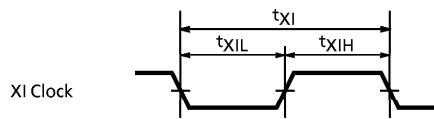

External clock input terminal (XI)

|                       |           |   |   |    |    |   |    |

|-----------------------|-----------|---|---|----|----|---|----|

| XI Clpck Cycle        | $t_{XI}$  | — | — | 40 | —  | — | ns |

| XI Clock "H" Duration | $t_{XIH}$ | — | — | —  | 20 | — |    |

| XI Clock "L" Duration | $t_{XIL}$ | — | — | —  | 20 | — |    |

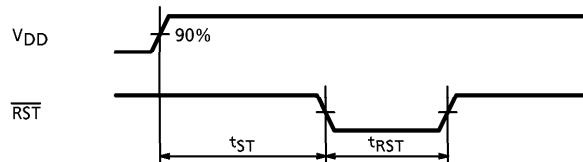

Reset terminal ( $\overline{RST}$ )

|                   |           |   |   |      |   |   |         |

|-------------------|-----------|---|---|------|---|---|---------|

| Stand-by Time     | $t_{ST}$  | — | — | 250  | — | — | $\mu s$ |

| Reset Pulse Width | $t_{RST}$ | — | — | 0.15 | — | — |         |

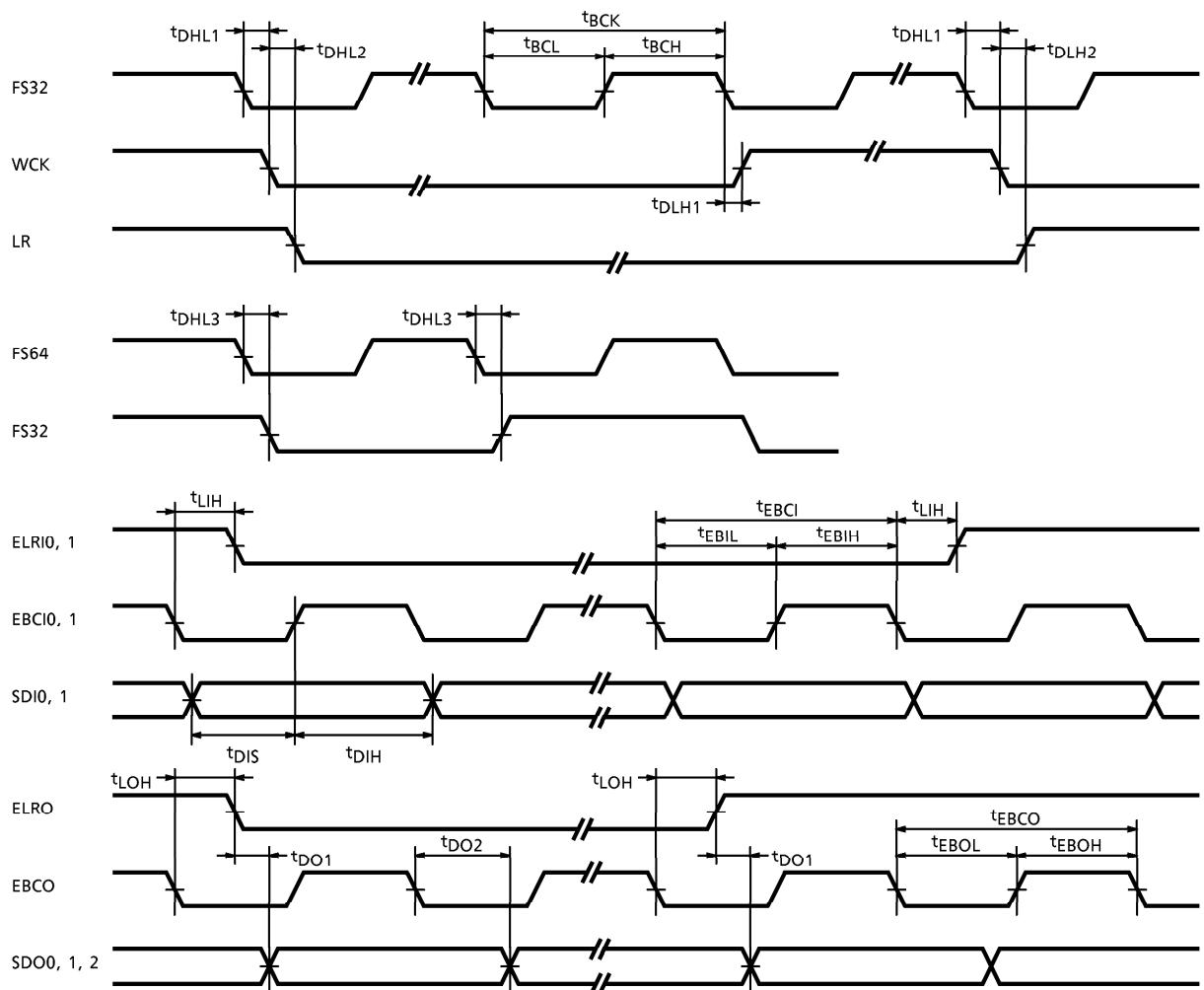

Audio serial interface ( $f_s = 48\text{kHz}$ )

|                                |            |   |                     |      |   |    |    |

|--------------------------------|------------|---|---------------------|------|---|----|----|

| ELRI Holding Time              | $t_{LIH}$  | — | $C_L = 30\text{pF}$ | — 75 | — | 75 | ns |

| SDI Data Setup Time            | $t_{DIS}$  | — | $C_L = 30\text{pF}$ | 50   | — | —  |    |

| SDI Data Hold Time             | $t_{DIH}$  | — | $C_L = 30\text{pF}$ | 50   | — | —  |    |

| EBCI Clock Cycle               | $t_{EBCI}$ | — | $C_L = 30\text{pF}$ | 325  | — | —  |    |

| EBCI Clock "H" Duration        | $t_{EBIH}$ | — | $C_L = 30\text{pF}$ | 162  | — | —  |    |

| EBCI Clock "L" Duration        | $t_{EBIL}$ | — | $C_L = 30\text{pF}$ | 162  | — | —  |    |

| ELRO Hold Time                 | $t_{LOH}$  | — | $C_L = 30\text{pF}$ | — 75 | — | 75 |    |

| SDO Data Output Delay Time (1) | $t_{DO1}$  | — | $C_L = 30\text{pF}$ | —    | — | 65 |    |

| SDO Data Output Delay Time (2) | $t_{DO2}$  | — | $C_L = 30\text{pF}$ | —    | — | 65 |    |

| EBCO Clock Cycle               | $t_{EBCO}$ | — | $C_L = 30\text{pF}$ | 325  | — | —  |    |

| EBCO Clock "H" Duration        | $t_{EBOH}$ | — | $C_L = 30\text{pF}$ | 162  | — | —  |    |

| EBCO Clock "L" Duration        | $t_{EBOL}$ | — | $C_L = 30\text{pF}$ | 162  | — | —  |    |

| WCK Output Delay Time (1)      | $t_{DHL1}$ | — | $C_L = 30\text{pF}$ | —    | — | 13 |    |

| LR Output Delay Time (1)       | $t_{DHL2}$ | — | $C_L = 30\text{pF}$ | —    | — | 17 |    |

| FS32 Output Delay Time (1)     | $t_{DHL3}$ | — | $C_L = 30\text{pF}$ | —    | — | 6  |    |

| WCK Output Delay Time (2)      | $t_{DLH1}$ | — | $C_L = 30\text{pF}$ | —    | — | 23 |    |

| LR Output Delay Time (2)       | $t_{DLH2}$ | — | $C_L = 30\text{pF}$ | —    | — | 27 |    |

| CHARACTERISTIC | SYMBOL | TEST CIR-UCIT | TEST CONDITION | MIN. | TYP. | MAX. | UNIT |

|----------------|--------|---------------|----------------|------|------|------|------|

|----------------|--------|---------------|----------------|------|------|------|------|

|                            |            |   |                     |     |   |    |    |

|----------------------------|------------|---|---------------------|-----|---|----|----|

| FS32 Output Delay Time (2) | $t_{DLH3}$ | — | $C_L = 30\text{pF}$ | —   | — | 17 | ns |

| BCK Clock Cycle            | $t_{BCK}$  | — | $C_L = 30\text{pF}$ | 650 | — | —  |    |

| BCK Clock "H" Duration     | $t_{BCH}$  | — | $C_L = 30\text{pF}$ | 325 | — | —  |    |

| BCK Clock "L" Duration     | $t_{BCL}$  | — | $C_L = 30\text{pF}$ | 325 | — | —  |    |

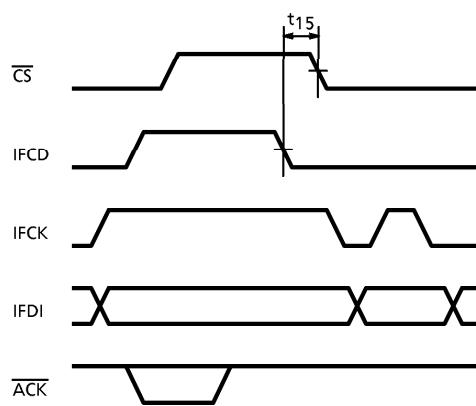

## Microcontroller interface

|                                                             |          |   |                                                 |        |   |      |               |

|-------------------------------------------------------------|----------|---|-------------------------------------------------|--------|---|------|---------------|

| $\bar{CS} \downarrow$ -IFCK $\downarrow$ Setup Time         | $t_1$    | — | $C_L = 10\text{pF}$ ,<br>$T = 1$ / system clock | 6T     | — | —    | ns            |

| I/F Clock "H" Duration                                      | $t_2$    | — | $C_L = 10\text{pF}$ ,<br>$T = 1$ / system clock | 6T     | — | —    |               |

| I/F Clock "L" Duration                                      | $t_3$    | — | $C_L = 10\text{pF}$ ,<br>$T = 1$ / system clock | 6T     | — | —    |               |

| IFCK $\uparrow$ -IFCD $\downarrow$ Setup Time               | $t_4$    | — | $C_L = 10\text{pF}$ ,<br>$T = 1$ / system clock | 6T     | — | —    |               |

| IFCD $\downarrow$ -IFCK $\downarrow$ Setup Time             | $t_5$    | — | $C_L = 10\text{pF}$ ,<br>$T = 1$ / system clock | 6T     | — | —    |               |

| IFCK $\uparrow$ -IFCD $\uparrow$ Setup Time                 | $t_6$    | — | $C_L = 10\text{pF}$ ,<br>$T = 1$ / system clock | 6T     | — | —    |               |

| $CS$ "H" Duration                                           | $t_7$    | — | $C_L = 10\text{pF}$                             | 1 / fs | — | —    | $\mu\text{s}$ |

| IFDI Data Setup Time                                        | $t_8$    | — | $C_L = 10\text{pF}$ ,<br>$T = 1$ / system clock | 1T     | — | —    | ns            |

| IFDI Data Hold Time                                         | $t_9$    | — | $C_L = 10\text{pF}$ ,<br>$T = 1$ / system clock | 5T     | — | —    |               |

| IFCK $\downarrow$ -IFDO $\uparrow$ Propagation Delay Time   | $t_{10}$ | — | $C_L = 10\text{pF}$ ,<br>$T = 1$ / system clock | —      | — | 168T |               |

| IFCK $\downarrow$ -IFDO $\downarrow$ Propagation Delay Time |          | — |                                                 | —      | — | 10T  |               |

| IFCK $\uparrow$ -ACK $\downarrow$ Propagation Delay Time    | $t_{11}$ | — | $C_L = 10\text{pF}$ ,<br>$T = 1$ / system clock | —      | — | 18T  |               |

| IFCK $\downarrow$ -ACK $\uparrow$ Propagation Delay Time    | $t_{12}$ | — | $C_L = 10\text{pF}$ ,<br>$T = 1$ / system clock | —      | — | 168T |               |

| $CS \uparrow$ -ACK $\uparrow$ Propagation Delay Time        | $t_{13}$ | — | $C_L = 10\text{pF}$ ,<br>$T = 1$ / system clock | —      | — | 168T |               |

| $CS \uparrow$ -IFDO $\uparrow$ Propagation Delay Time       | $t_{14}$ | — | $C_L = 10\text{pF}$ ,<br>$T = 1$ / system clock | —      | — | 168T |               |

| IFCD $\downarrow$ - $\bar{CS} \downarrow$ Setup Time        | $t_{15}$ | — | $C_L = 10\text{pF}$ ,<br>$T = 1$ / system clock | 2T     | — | —    |               |

| IFDO $\downarrow$ - $\bar{CS} \downarrow$ Setup Time        | $t_{16}$ | — | $C_L = 10\text{pF}$                             | 0      | — | —    |               |

## AC CHARACTERISTICS MEASUREMENT POINTS

## (1) External clock input terminal

## (2) Reset terminal

## (3) Audio serial interface

## (4) Microcontroller interface

## AT SERIES TRANSFER MODE

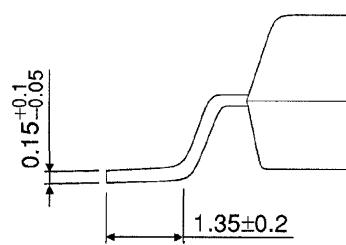

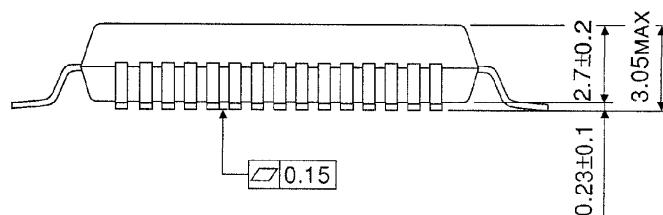

**PACKAGE DIMENSIONS**

QFP60-P-1414-0.80D

Unit : mm

Weight : 1.08g (Typ.)

## RESTRICTIONS ON PRODUCT USE

000707EBA

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.