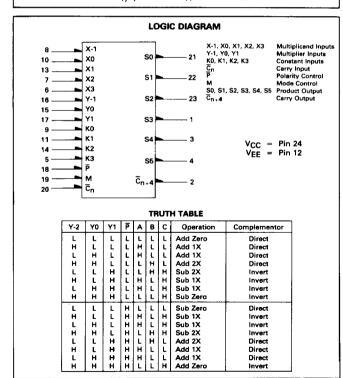

### 4 X 2 MULTIPLIER

The MC10183 is a 4  $\times$  2 bit multiplier that can multiply 2's complement numbers producing a 2's complement product without correction. The device can be used as a 4  $\times$  2 bit multiplier cell to build larger iterative arrays.

The part performs the function defined as F = XY + K, where K is an input field used to add partial products in an array or to add a constant to the least significant part of the array product. The algorithm used is a modified Booth's algorithm or multiplier coding technique. The device consists of a shift network and an adder/subtracter in which 0, 1 times X, or 2 times X is either added or subtracted to input constant K. The Y inputs control multiplication as shown in the Truth Table.

The most significant digit in a word carries a negative weight allowing 2's complement numbers of various lengths to be multiplied. An M-bit by N-bit multiplication produces an M  $\,+\,$  N bit product.

The  $\overline{P}$  polarity input allows multiplication in either positive logic ( $\overline{P}=$  high) or negative logic ( $\overline{P}=$  low) representation. Also, mode control M inverts  $\overline{C}_n$  when high and passes  $\overline{C}_n$  directly when left low.

PD = 760 mW typ/pkg (No Load)

$t_{pd} = 50 \text{ ns typ (8 x 8 bit product)}$

$t_r$ ,  $t_f = 3.5$  ns typ (20%-80%)

# MC10183

# MECL 10K SERRES

**4 X 2 MULTIPLIER**

3-153

# ELECTRICAL CHARACTERISTICS

Each MECL 10,000 series has been designed to meet the dc specifications shown in the test table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 linear fpm is maintained. Outputs are terminated through a 50-bhm resistor to -2.0 volts. Test procedures are shown for only selected inputs and outputs. Other inputs and outputs are tested in a similar manner.

| air now greater than 500 linear ipin is maintained. Outputs are terminated    | 3                                       | 2         |           | 5        | יי סום כון | 200      | ,                   |        |        | _        |                |            |                                      |            |          |          |

|-------------------------------------------------------------------------------|-----------------------------------------|-----------|-----------|----------|------------|----------|---------------------|--------|--------|----------|----------------|------------|--------------------------------------|------------|----------|----------|

| through a 50-ohm resistor to -2.0 volts. Test procedures are shown for only   | stor to -2.                             | .0 volts. | Test proc | edures a | are show   | n for on | >                   |        |        |          |                | TEST V     | TEST VOLTAGE VALUES                  | , UES      |          |          |

| selected inputs and outputs. Other inputs and outputs are tested in a similar | tputs. Oth                              | er input  | s and out | puts are | tested in  | a simila | _                   |        | · ·    | @Test    |                |            | Volts                                |            |          |          |

| manner.                                                                       |                                         |           |           |          |            |          |                     |        | _<br>  | Jre      | VIHmax         | VILmin     | VIHAmin                              | VILAmex    | VEE      |          |

|                                                                               |                                         |           |           |          |            |          |                     |        |        | 300€     | -0.890         | -1.890     | -1.205                               | -1.500     | -5.2     |          |

|                                                                               |                                         |           |           |          |            |          |                     |        |        | +25°C    | -0.810         | -1.850     | -1.105                               | -1.475     | -5.2     |          |

|                                                                               |                                         |           |           |          |            |          |                     |        |        | -85°C    | -0.700         | -1.825     | -1.035                               | -1.440     | -5.2     |          |

|                                                                               |                                         |           |           |          | ¥          | 10183 TE | MC10183 TEST LIMITS | ,,     |        |          |                |            |                                      |            |          |          |

|                                                                               |                                         | E         | −30°C     | ې        |            | +25°C    |                     | -85°C  | ي      |          | VOLT           | AGE APPLII | VOLTAGE APPLIED TO PINS LISTED BELOW | ISTED BELO |          | ر<br>کرک |

| Characteristic                                                                | Symbol                                  | Test      | Αin       | Max      | M.         | T,       | Max                 | Νin    | Μax    | , i      | VIHmax         | VILmin     | VIHAmin                              | VILAmax    | VEE      | 9        |

| Power Supply Drain                                                            | -E                                      | 12        | ,         | 201      | 1          | 146      | 183                 | -      | 102    | mAdc     | ı              | 1          | ì                                    | ı          | 12       | 24       |

| Inout Current                                                                 | 101                                     | 9         | 1         | 980      |            | ļ,       | 245                 | ,      | 245    | μAdc     | g              | 1          |                                      | 1          | 12       | 24       |

|                                                                               |                                         | - 00      | ı         | 350      | ı          | ı        | 220                 | 1      | 220    | _        | 80             | 1          | ı                                    | ı          |          |          |

|                                                                               |                                         | 81        | 1         | 320      | 1          | ı        | 200                 | 1      | 520    | >        | 8              | 1          | ı                                    | ì          | -        | -        |

|                                                                               | ابا <sub>.</sub>                        | œ         | 0.5       | ı        | 0.5        | _        | -                   | 0.3    | _      | "Adc     | -              | 80         | 1                                    | -          | 12       | 24       |

| Logic "1"<br>Outbut Voltage                                                   | ,<br>,                                  | 2         | -1.060    | -0.890   | 096:0-     | 1        | -0.810              | -0.890 | -0.700 | \<br>Vdc | 8, 16, 19      | 1          | ı                                    | ı          | 12       | 75       |

|                                                                               | 5                                       | 21        | -1.060    | -0.890   | -0.960     | ı        | -0.810              | -0.890 | -0.700 | Vdc      | 8,16,19        | 1          | 1                                    | 1          | 12       | 24       |

| Logic '0'                                                                     | ō<br>>                                  | 2         | -1.890    | -1.675   | -1.850     | ,        | -1.650              | -1.825 | -1.615 | Γ        | 17,18,19,20    |            | -                                    | -          | 12       | 24       |

| Output Voltage                                                                | ļ                                       | 21        | -1.890    | -1.675   | -1.850     | 1        | -1.650              | -1.825 | -1.615 | V dc     | 17, 18, 19, 20 | -          | ı                                    | I          | 12       | 24       |

| Logic "1"                                                                     | VОНА                                    | 2         | -1.080    |          | -0.980     | ,        | ,                   | -0.910 | 1      | Vdc      | 8,16,19        | 1          | F                                    | 2          | 12       | 24       |

| Threshold Voltage                                                             |                                         | 21        | -1.080    | 1        | -0.980     | ı        | 1                   | -0.910 | 1      | V dc     | 8,16,19        | -          | 1                                    | 15         | 12       | 24       |

| Logic0.                                                                       | VO.A                                    | 2         |           | -1.655   |            | 1        | -1.630              |        | -1.595 | ٧dc      | 8,16,19        | -          | 5                                    | ı          | 12       | 24       |

| Threshold Voltage                                                             | <b>;</b>                                | 21        | 1         | -1.655   | ,          | ı        | -1.630              | ı      | -1.595 | V dc     | 8,16,19        | ı          | 10                                   | F          | 12       | 24       |

| Switching Times                                                               |                                         |           |           |          |            |          |                     |        |        |          |                |            | Pulse In                             | Pulse Out  | -3.2 Vdc | -2.0 Vdc |

| (50 the Load)                                                                 |                                         | ,         | -         |          | 5          | 4        | 0.5                 | 0      | 5.5    | Š        | 1              | - (        | 20                                   | 2          | 12       | 24       |

| A CONTRACTOR                                                                  | -7+07-                                  | , ;       | 2 .       | ? ?      | : :        |          |                     |        |        | :        | 1              | ı          | 20                                   | 22         | _        | _        |

|                                                                               | +77+07                                  | ; «       | 2 2       | 4        |            | 8.0      | 0 00                | 8      | 8      |          | ,              | 1          | 50                                   | m          |          |          |

|                                                                               | - 5 - 5 - 5 - 5 - 5 - 5 - 5 - 5 - 5 - 5 |           | <u>.</u>  | 7.3      | 9          | 2        | 7.0                 | 1,6    | 7.7    |          | ,              | ı          | 6                                    | 2          |          |          |

|                                                                               | -7.E                                    | -         | 2.5       | =        | 2.5        | 8.0      | 10.5                | 2.5    | 1.5    |          | 1              | ı          | 6                                    | -          |          |          |

|                                                                               | 11443                                   | ო         | 2.5       | =        | 5.5        | 8.5      | 10.5                | 2.5    | 11.5   |          | ı              | 4          | 2                                    | 6          |          |          |

|                                                                               | t10-2+                                  | 2         | 8:        | 8.4      | 87         | 0.9      | 0:0                 | 8.1    | 8.8    |          | 1              | ı          | 10                                   | 2          |          |          |

|                                                                               | 113+23+                                 | 23        | 2.5       | =        | 2.5        | 9.5      | 10.5                | 2.5    | 1.5    | _        | 1              | ı          | 13                                   | 23         |          |          |

|                                                                               | 114-3+                                  | ო         | 2.5       | =        | 5.5        | 10.0     | 10.5                | 5.5    | 5.     |          | 1              | 1          | 4                                    | e          |          | _        |

|                                                                               | 115-2                                   | 2         | 3.2       | <u>1</u> | 3.2        | 10.5     | 13.5                | 3.2    | 14.8   |          | ı              | 1          | 5                                    | 2          |          |          |

|                                                                               | 115+23+                                 | 23        | _         | _        | _          | 10.5     | _                   |        |        |          | i              | ı          | 15                                   | 23         | -        |          |

|                                                                               | 115-3+                                  | 3         | ^         | >        | •          | 11.5     | -                   | >      | >      | -        | 1              | 1          | 15                                   | 3          | -        | -        |

| Rise Time                                                                     |                                         | Ę         | •         |          | ,          | 7        | ď                   |        | 4      | č        |                | ı          | σ                                    | 3          | 12       | 24       |

| (ZU% TO 8U%)                                                                  | <sup>1</sup> 22 <sup>+</sup>            | 3         | 2         | 3        | ?          | ;        | 3                   | 2      | 3      | 2        |                |            | ,                                    |            |          |          |

| Falt Time<br>  {20% to 80%}                                                   | t22-                                    | 22        | 1.0       | 6.3      | 0.1        | 3.5      | 9.0                 | 0.     | 9.9    | ž        | 1              | ı          | 6                                    | 22         | 12       | 24       |

|                                                                               |                                         |           |           |          |            | 1        | 1                   |        | 1      |          |                |            |                                      |            | İ        |          |

### MC10183 APPLICATIONS INFORMATION

The MC10183 is a 4  $\times$  2 bit multiplier that uses a modified Booth's algorithm or multiplier coding technique. The device generates the function: S = X  $\times$  Y + K

### where

X = 4-bit multiplicand

Y = 2-bit multiplier

K = 4-bit constant

The addition of the constant allows the device to be used in an iterative array of parts for larger words. The algorithm for multiplication is:

| Yi-1 | Υį | Yi+1 | Operation          |  |

|------|----|------|--------------------|--|

| 0    | 0  | 0    | add zero           |  |

| 1    | 0  | 0    | add multiplicand   |  |

| 0    | 1  | 0    | add multiplicand   |  |

| 1    | 9  | 0    | add 2 times multi- |  |

|      |    |      | plicand            |  |

| 0    | 0  | 1    | sub 2 times multi- |  |

|      |    |      | plicand            |  |

| 1    | 0  | 1    | sub multiplicand   |  |

| 0    | 3  | 1    | sub multiplicand   |  |

| 1    | 1  | 1    | sub zero           |  |

### **DEVICE OPERATION**

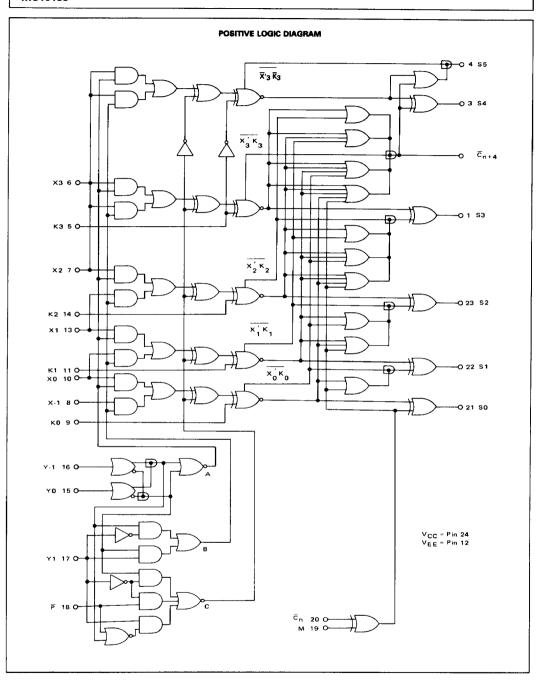

The device consists of three main sections; a decoder, a shifter, and a high speed look-ahead carry adder/subtractor.

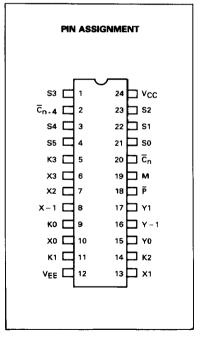

1. The decoder uses the Y inputs to generate the control signals for the shifter and the adder/subtractor. Also, the polarity control  $\overline{P}$  is used to allow operation in either positive or negative logic. Referring to the logic diagram, the control signals are:

$$\begin{array}{l} A = Y_{-1} \bigoplus Y_0 \ (1 \ times multiplicand) \\ B = Y_{-1}Y_0\overline{Y}_1 + \overline{Y}_{-1}\overline{Y}_0Y_1 \\ \{2 \ times \ multiplicand) \\ \overline{C} = \overline{PY}_1 + \overline{Y}_{-1}\overline{Y}_0\overline{Y}_1 + PY_1(\overline{Y}_{-1} + \overline{Y}_0) \end{array}$$

(add/subtract)

The  $\overline{P}$  input is tied to a high logic level or ground for positive logic operation.

2. The shift network is a multiplexer that ripples through number X (1 times multiplicand), shifts number X by one bit (2 times multiplicand), or sets the output to zero. The network is controlled by decoder functions A and B which are generated in accordance with the multiply algorithm.

3. The adder/subtractor follows the shift network which performs the actual multiplication. The adder/subtractor produces the sum or difference of the newly formed partial product and the accumulated partial product (constant K). Subtraction is accomplished by inverting the shifted product and doing a two's complement addition. The carry in of the least significant bit must be a logic one during subtraction.

The two most significant bits of the product are used for sign detection and overflow for a two's complement multiply. These outputs are used only as the two most significant bits of the accumulated product at each addition level within a multipolier array.

Overflow can occur either as the result of 2 times the multiplicand, and/or of an addition or subtraction. To show all possible conditions (including overflow), the most significant bit (S5) must carry a negative binary weight. To show this for a 4 X 2 bit multiply plus constant, consider the following addition:

The shift network produces 5 product bits (maximum value of 2 times multiplicand) and a 4-bit constant is added to the least significant end of the product. The K3 bit is repeated to hold the proper binary weight. Because S5 has a negative weight all possible combinations are represented properly.

If no overflow occurs S4 = S5, and S4 can be used as a sign bit. Under overflow conditions S4  $\neq$  S5, and overflow can be detected by EXCLUSIVE-ORing S4 and S5.

# **USAGE RULES**

The MC10183 can be used in larger arrays to produce a two's complement product of 2 two's complement numbers. The following rules apply:

- 1. For an M-bit by N-bit multiplier, an (M+N)-bit product is formed. The number of MC10183's equals (M\*N)/8. As an example, an 8  $\times$  8 bit (Figure 1) array requires  $(8\times8)/8 = 8$  packages.

- 2. The MC10183 can be used directly for both positive logic and negative logic representations. The  $\overline{P}$  input can be tied to ground or to a high logic level for positive logic operation, or left at a low logic level for negative logic operation.

- 3. The M mode control input is used to invert  $\overline{C}_n$  when placed at a high logic level or ground, or passes  $\overline{C}_n$  directly when left as a low logic level. When  $\overline{C}_n$  is driven from  $\overline{C}_{n+4}$  of a preceding device, M control is left in a low logic state. When  $\overline{C}_n$  is the least significant input carry bit for a level of addition within an array,  $\overline{C}_n$  is tled to  $Y_1$  of the same device, and the M input is placed at a high logic level.  $Y_1$  controls when subtraction occurs, and carry in must be equal to a logic one during subtraction.

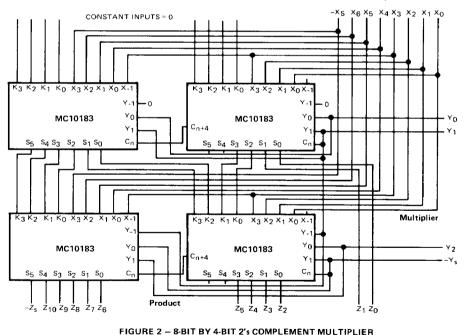

# 8 × 4 BIT EXAMPLE

Figure 2 shows 4 MC10183's in an 8 X 4 bit array. A 12-bit two's complement product is produced from a 4-bit multiplier and an 8-bit multiplicand. The array is used for positive logic representation, and all P inputs are tied to ground. At the first level of multiplication, the  $X_{-1}$  and  $Y_{-1}$  inputs are left open (logic "O") because the initial condition is treated as an add operation. The K inputs are used to add the accumulated partial product at each level of the array. If the initial partial product is zero, the least significant K inputs are left at a zero logic state (CONSTANT inputs in the figure). However, these inputs can also be used to add a constant to the least significant end of the product.

When the MC10183 is expanded to longer numbers, the carry out  $(\overline{C}_{n+4})$  of a device must be rippled to the carry in  $(\overline{C}_n)$  of the next most significant device at the same level of multiplication. The least significant device must have the carry input equal to zero for an add and equal to one for a subtraction. In observing the multiplication algorithm  $y_{i+1}$  is always equal to 1 for a subtraction, and the carry input can be tied to  $Y_1$ . However, the M mode input must be tied to ground for this device to invert the carry input  $(\overline{C}_n)$  because the input requires a complemented signal.

The S4 and S5 outputs are used only at the most significant part of the array. These two sum outputs only have meaning as the two most significant bits of a two's complement number.

# OTHER ARRAYS

The normal parallelogram structure consists of several stages, each multiplying two bits of multiplier times the multiplicand and adds the partial product. In larger arrays, faster configurations can be made by moving some multiplier blocks while maintaining the relative weight of each partial product. The typical times possible for various N-bit X N-bit arrays are:

| Number<br>of<br>Bits | Total<br>Multiply<br>Time (ns) | Package<br>Count |

|----------------------|--------------------------------|------------------|

| 8                    | 43                             | 8                |

| 12                   | 67                             | 18               |

| 16                   | 90                             | 32               |

The times do not include wiring delays.

Because of the versatility of the MC10183, many other types of arrays can also be built. Faster arrays using additional adders, pipeline techniques, one's complement and magnitude multipliers, and truncated product multipliers can all be built.

### Multiplicand

3-157