BR24C01A BR24C01AF BR24C02 BR24C02F BR24C04 BR24C04F EEPROM, serial, 2 wire (for use with I<sup>2</sup>C bus)

The BR24C01A/AF, BR24C02/F, and BR24C04/F are serial, 2-wire EEPROM ICs.

### **Features**

- available in DIP8 and SOP8 packages

- Available with the following memory:

- BR24C01A/AF: 1 kbit (128 × 8 bit)

- BR24C02/F: 2 kbit (256 × 8 bit)

- BR24C04/F: 4 kbit (512 × 8 bit)

- for use with I<sup>2</sup>C bus

- wide voltage supply range, 2.7 ~ 5.5 V (reading and writing)

- low current consumption, typically

- during operation: 0.2 mA at 5 V

- -- while standby: 1.0 μA at 5 V

- can be rewritten at least 10 000 times.

- data can be stored for 10 years without corruption

- addresses can be incremented automatically during read operations

- auto erase and auto complete functions can be used during write operations

- page write mode function

- BR24C01A/AF: 4 bytes

- BR24C02/F: 4 bytes

- BR24C04/F: 16 bytes

- write protection when:

- V<sub>CC</sub> is low

- IC is powered up

- includes noise filters on the SCL and SDA pins

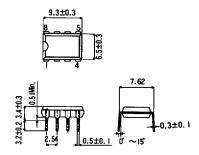

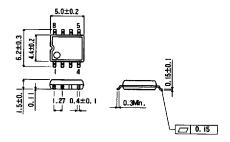

### Dimensions (Units : mm)

### BR24C01A, BR24C02, BR24C04 (DIP8)

### BR24C01AF, BR24C02F, BR24C04F (SOP8)

#### **Applications**

- video tape recorders

- televisions

- printers

- · car stereo radio cassette players

- cordless telephones

- short wave radios

- programmable DIP switches

**Note:** I<sup>2</sup>C is a registered trademark of Phillips Co.

Standard & Memory ICs

ROHM

119

**7828999 0012249 789 🖿**

## BR24C01A, BR24C01AF, BR24C02, BR24C02F, BR24C04, BR24C04F Serial EEPROM, 2 wire

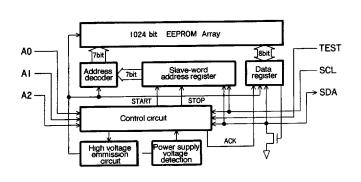

## Block diagram and pin connections—BR24C01A and BR24C01AF

| Pin name        | Function                  |

|-----------------|---------------------------|

| A0, A1, A2      | Slave address setting pin |

| SCL             | Serial data clock         |

| SDA             | Serial data input/output  |

| TEST            | Test connection           |

| V <sub>CC</sub> | Power supply              |

| GND             | Ground                    |

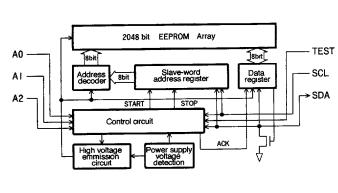

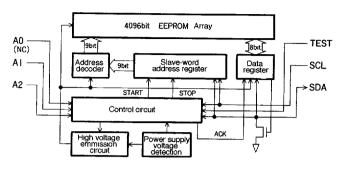

## Block diagram and pin connections—BR24C02 and BR24C02F

| Pin name        | Function                  |  |  |  |  |

|-----------------|---------------------------|--|--|--|--|

| A0, A1, A2      | Slave address setting pin |  |  |  |  |

| SCL             | Serial data clock         |  |  |  |  |

| SDA             | Serial data input/output  |  |  |  |  |

| TEST            | Test connection           |  |  |  |  |

| V <sub>CC</sub> | Power supply              |  |  |  |  |

| GND             | Ground                    |  |  |  |  |

120

ROHM

Standard & Memory ICs

7828999 0012250 4TO **=**

# Serial EEPROM, 2 wire BR24C01A, BR24C01AF, BR24C02, BR24C02F, BR24C04, BR24C04F

## Block diagram and pin connections—BR24C04 and BR24C04F

The SDA pin has an Nch open drain output. Therefore, make sure to use an external pull-up resistor.

|                 | GND 4 5 SDA               |

|-----------------|---------------------------|

| Pin name        | Function                  |

| A0              | Not used                  |

| A1, A2          | Slave address setting pin |

| SCL             | Serial data clock         |

| SDA             | Serial data input/output  |

| TEST            | Test connection           |

| V <sub>CC</sub> | Power supply              |

Ground

GND

7 TEST

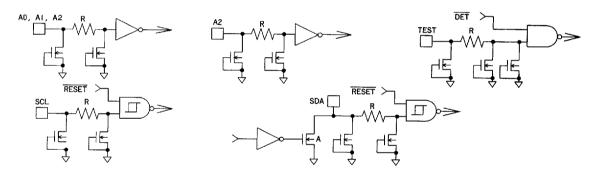

### Input/output circuits

## Absolute maximum ratings ( $T_a = 25^{\circ}C$ )

| Parameter Power supply                       |                                | Symbol           | Limits                   | Units | Conditions                                            |  |  |

|----------------------------------------------|--------------------------------|------------------|--------------------------|-------|-------------------------------------------------------|--|--|

|                                              |                                | V <sub>CC</sub>  | -0.3 ~ +6.5              | V     |                                                       |  |  |

| Power                                        | BR24C01A<br>BR24C02<br>BR24C04 | 1                | 500                      |       | Reduce power by 5.0 mW/°C for each degree above 25°C. |  |  |

| dissipation BR24C01A<br>BR24C02F<br>BR24C04F |                                | P <sub>d</sub>   | 350                      | mW    | Reduce power by 3.5 mW/°C for each degree above 25°C. |  |  |

| Voltage for                                  | each pin                       |                  | $-0.3 \sim V_{CC} + 0.3$ | V     |                                                       |  |  |

| Storage ter                                  | nperature                      | T <sub>stg</sub> | <b>−65</b> ~ <b>+125</b> | °C    |                                                       |  |  |

| Operating t                                  | emperature                     | Topr             | -40 ~ +85                | °C    |                                                       |  |  |

Standard & Memory ICs

ROHM

121

■ 7828999 0012251 337 **■**

# BR24C01A, BR24C01AF, BR24C02, BR24C02F, BR24C04, BR24C04F Serial EEPROM, 2 wire

## Recommended operating conditions ( $T_a = 25^{\circ}C$ )

| Parameter   |       | Symbol              | Limits            | Unit |

|-------------|-------|---------------------|-------------------|------|

| Supply      | Read  | V                   | 2.7 ~ 5.5         | V    |

| voltage     | Write | ─ V <sub>CC</sub> ├ | 2.7 ~ 5.5         | 7 .  |

| Input volta | ıge   | V <sub>IN</sub>     | 0~V <sub>CC</sub> | V    |

# Electrical characteristics (unless otherwise noted, $T_a$ = -40 ~ +85°C, $V_{CC}$ = 2.7 V ~ 5.5 V)

| Parameter                  | Symbol           | Min                 | Typical | Max                 | Unit | Conditions                                          |

|----------------------------|------------------|---------------------|---------|---------------------|------|-----------------------------------------------------|

| Input voltage high         | V <sub>IH</sub>  | 0.7 V <sub>CC</sub> |         |                     | ٧    |                                                     |

| Input voltage low          | V <sub>iL</sub>  |                     |         | 0.3 V <sub>CC</sub> | V    |                                                     |

| Output voltage low         | V <sub>OL</sub>  |                     |         | 0.4                 | ٧    | $I_{OL} = 3.0 \text{ mA (SDA)}$                     |

| Input leak current         | ILI              | - 10                |         | 10                  | μΑ   | $V_{IN} = 0 V - V_{CC}$                             |

| Output leak current        | ILO              | -10                 |         | 10                  | μΑ   | V <sub>OUT</sub> = 0 V ~ V <sub>CC</sub>            |

| Operating current consumed | Icc              |                     |         | 1.0                 | mA   | $V_{CC} = 5.5 \text{ V}, f_{SCL} = 100 \text{ kHz}$ |

| Stand-by current           | I <sub>SB</sub>  |                     |         | 2.0                 | μА   | $V_{CC} = 5.5 \text{ V}$ , SDA and SCL = $V_{CC}$   |

| SCL frequency              | f <sub>SCL</sub> |                     |         | 100                 | kHz  |                                                     |

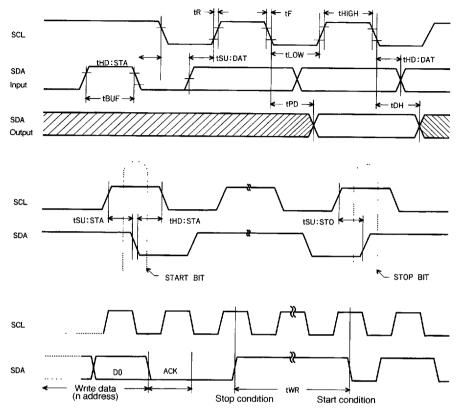

# Timing characteristics (unless otherwise noted, $T_a = -40 \sim +85^{\circ}C$ , $V_{CC} = 2.7 \sim 5.5 \text{ V}$ )

| Parameter                                  | Symbol               | Min | Typical | Max | Unit | Conditions                        |

|--------------------------------------------|----------------------|-----|---------|-----|------|-----------------------------------|

| Data clock time high                       | t <sub>HIGH</sub>    | 4.0 |         |     | μs   |                                   |

| Data clock time low                        | t <sub>LOW</sub>     | 4.7 |         |     | μs   |                                   |

| SDA and SCL rise time                      | t <sub>R</sub>       |     |         | 1.0 | μs   |                                   |

| SDA and SCL fall time                      | t <sub>F</sub>       |     |         | 0.3 | μs   |                                   |

| Start condition hold time                  | t <sub>HD</sub> :STA | 4.0 |         |     | μs   |                                   |

| Start condition setup time                 | t <sub>SU</sub> :STA | 4.7 |         |     | μs   |                                   |

| Input data hold time                       | t <sub>HD</sub> :DAT | 0   |         |     | ns   |                                   |

| Input data setup time                      | t <sub>SU</sub> :DAT | 250 |         |     | ns   |                                   |

| Output data delay time                     | t <sub>PD</sub>      | 0.3 |         | 3.5 | μs   |                                   |

| Output data hold time                      | t <sub>DH</sub>      | 0.3 |         |     | μs   |                                   |

| Stop condition setup time                  | t <sub>SU</sub> :STO | 4.7 |         |     | μs   |                                   |

| Bus open time before start of transfer     | t <sub>BUF</sub>     | 4.7 |         | " " | μs   |                                   |

| Internal write cycle time                  | t <sub>WR1</sub>     |     |         | 10  | ms   | $V_{CC} = 4.5 \sim 5.5 \text{ V}$ |

|                                            | t <sub>WR2</sub>     |     |         | 25  | ms   | $V_{CC} = 2.7 \sim 3.3 \text{ V}$ |

| Noise erase valid time<br>(SCL or SDA pin) | tı                   |     |         | 0.1 | μs   |                                   |

122 ■ 7828999 0012252 273 ■ ROHM Standard & Memory ICs

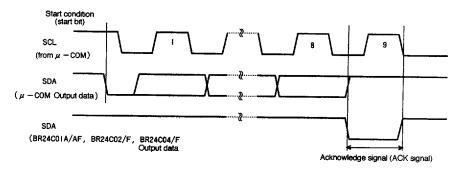

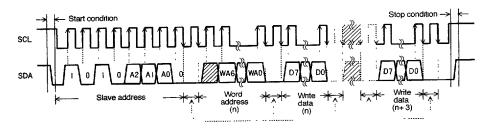

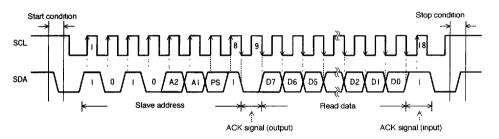

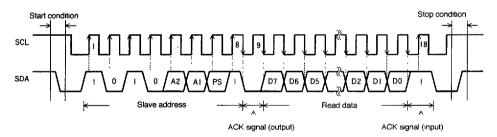

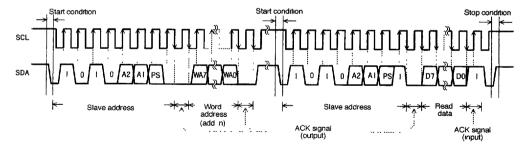

Figure 1 Timing chart

*Note:* Data is input on the rising edge of SCL. Data is output on the falling edge of SCL Circuit operation

## Start condition (recognition of start bit)

Before executing any command, a start condition (start bit) is required. A start bit is recognized when SDA falls from HIGH to LOW with SCL HIGH.

## Stop condition (recognition of stop bit)

To stop any command, the stop condition (stop bit) must be issued. A stop bit is defined as the condition when SDA is raised from LOW to HIGH with SCL HIGH.

#### Write command

In the WRITE mode, when the stop bit is not executed, the transferred data is not written to memory.

Standard & Memory ICs

ROHM

123

■ 7828999 0012253 10T ■

## Device addressing—BR24C01A/AF, BR24C02/F

Make sure to output the slave address from the master immediately after the start condition.

The upper four bits of the slave address are used to determine the device type. This IC has its device code fixed at 1010.

The next three bits of the slave address (A2, A1, A0 device address) are used to select the device. This IC can address up to eight devices on the same bus.

The lowermost bit of the slave address (R/W, READ/WRITE) is used to set the write or read mode as follows:

R/W set to 0 =write: R/W set to 1 =read

(Random read word address setting is also 0)

### Device addressing—BR24C04/F

Make sure to output the slave address from the master in continuation with the start condition.

The upper four bits of the slave address are used to determine the device type. This IC has its device code fixed at 1010.

The next two bits of the slave address (A2, A1 device address) are used to select the device. This IC can address up to four devices on the same bus.

The next bit of the slave address (PS page select) is used to select the page. As shown following, it can write or read to any of the 256 words in the 2 pages in memory.

PS set to 0 = page 1 (000 - 0FF): PS set to 1 = page 2 (100 - 1FF)

The lowermost bit of the slave address (R/W: READ/WRITE) is used to set the write or read mode as follows:

$R/\overline{W}$  set to 0 = write:  $R/\overline{W}$  set to 1 = read

(Random read word address setting is also 0)

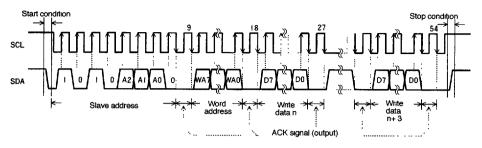

## **ACK** signal

124

The acknowledge signal (ACK signal) is determined by software and is used to indicate whether or not a data transfer is proceeding normally.

The transmitting device, whether the master or slave, opens the bus after an 8-bit data output ( $\mu$ -COM when a write or read command of the slave address input; this IC when reading data)

ROHM

Standard & Memory ICs

7828999 0012254 046

For the receiving device during the 9th clock cycle, SDA is set to LOW and an acknowledge signal (ACK signal) is sent to indicate that it received the 8-bit data (this IC when a write command or a read command of the slave address input,  $\mu$ -COM when a read command data output).

This IC outputs a LOW acknowledge signal (ACK signal) after recognizing the start condition and slave address (8 bits).

When data is being written to this IC, a LOW acknowledge signal (ACK signal) is output after the receipt of each 8 bits of data (word address and write data).

When data is being read from the IC, 8 bits of data (read data) are output and the IC waits for a returned LOW acknowledge signal (ACK signal). When an acknowledge signal (ACK signal) is detected and a stop condition is not sent from the master ( $\mu$ -COM) side, the IC sends the next 8 bits of data.

If an acknowledge signal (ACK signal) is not detected, the IC interrupts the data transfer and ceases read operations after recognizing the stop condition (stop bit). The IC enters a wait state.

Figure 2 Acknowledge (ACK) signal response (during read, write slave address input)

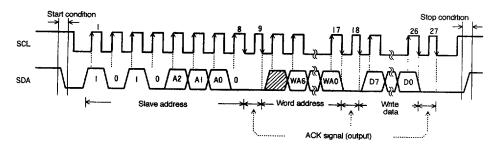

Figure 3 Byte write cycle—BR24C01A and BR24C01AF

Standard & Memory ICs

ROHM

125

7828999 OC12255 T82 🖿

Figure 4 Byte write cycle—BR24C02 and BR24C02F

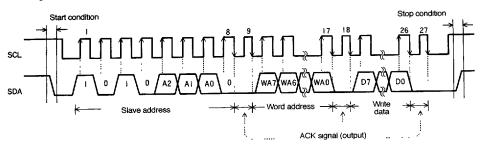

Figure 5 Byte write cycle—BR24C04 and BR24C04F

Data is written to the address designated by the word address (n address).

After 8 bits of data are input, the data is written to the memory cell by issuing the stop bit.

## Page write

Figure 6 Page write cycle—BR24C01A and BR24C01AF

A 4-byte write is possible using this command.

The page write command arbitrarily sets the upper five bits (WA6 - WA2) of the word address. The lower two bits (WA1 - WA0) can write up to four bytes of data with the address being incremented internally.

126

ROHM

Standard & Memory ICs

**7**828999 0012256 919 **=**

Figure 7 Page write cycle—BR24C02 and BR24C02F

A 4-byte write is possible using this command.

This page write command arbitrarily sets the upper six bits (WA7 - WA2) of the word address. The lower two bits (WA1 - WA0) can write up to four bytes of data with the address being incremented internally.

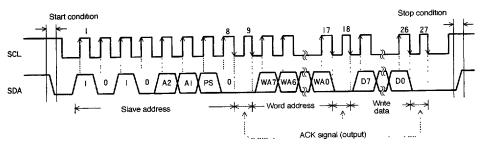

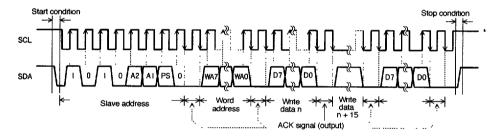

Figure 8 Page write cycle—BR24C04 and BR24C04F

A 16-byte write is possible using this command.

This page write command arbitrarily sets the upper four bits (WA7 - WA4) of the word address. The lower four bits (WA3 - WA0) can write up to 16 bytes of data with the address being incremented internally.

Standard & Memory ICs

ROHM

127

**7828999 0012257 855**

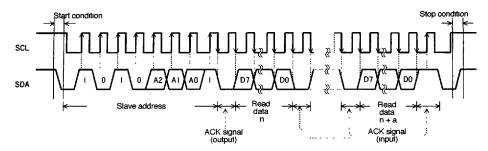

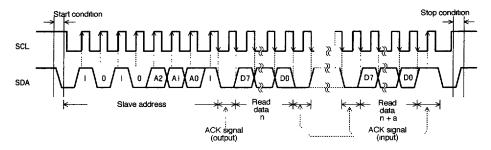

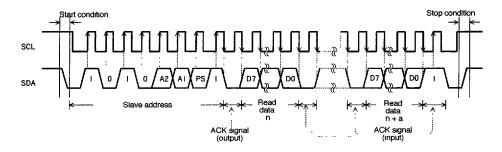

#### **Current read**

Figure 9 Current write cycle—BR24C01A and BR24C01AF

Figure 10 Current write cycle—BR24C02 and BR24C02F

Figure 11 Current write cycle—BR24C04 and BR24C04F

This IC increments the address by one position by using the internal circuit address count. It records the final word address (n address) of the executed write - read command.

This command reads the data of the next word address (n + 1 address) of the final write word address after the execution of the previous command.

When an ACK signal LOW is detected after D0 and a stop condition is not sent from the master  $(\mu$ -COM), the next word address data can be read. (Refer to Figures 15 - 17):

ROHM

Standard & Memory ICs

**7828999 0012258 791**

128

This command is ended by inputting HIGH to the ACK signal after D0 and raising the SDA signal (stop condition) by setting SCL HIGH.

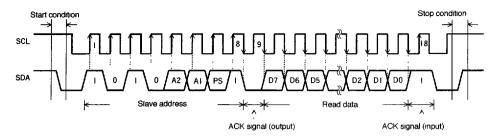

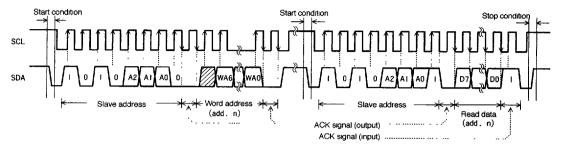

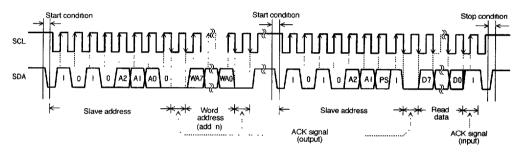

Figure 12 Random read—BR24C01A and BR24C01AF

Figure 13 Random read—BR24C02 and BR24C02F

Figure 14 Random read—BR24C04 and BR24C04F

This command can read the designated word address data.

When an ACK signal LOW is detected after D0 and a stop condition is not sent from the master  $(\mu$ -COM), the next word address data can be read. (Refer to Figures 15 - 17).

This command is ended by inputting a HIGH signal to the ACK signal after D0 and raising the SDA signal (stop condition) by raising SCL HIGH.

Standard & Memory ICs

ROHM

129

**2828999 0012259 628**

Figure 15 Sequential read—BR24C01A and BR24C01AF—Ex: for a current read

Figure 16 Sequential read—BR24C02 and BR24C02F—Ex: for a current read

Figure 17 Sequential read—BR24C04 and BR24C04F—Ex: for a current read

When an ACK signal "LOW" is detected after D0 and a stop condition is not sent from the master ( $\mu$ -COM), the next word address data can be read. (All words can be read)

This command is ended by inputting a HIGH to the ACK signal after D0 and raising the SDA signal (stop condition) using the SCL signal HIGH.

A sequential read is possible for a random read.

ROHM Standard & Memory ICs

7828999 0012260 347 📟

130

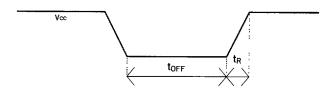

### Figure 18

#### Precautions for use

### Powering up the IC

When power is connected,  $V_{CC}$  rises through the low power supply voltage region in which the IC internal circuits do not operate. Thus, if the power supply voltage rises without completely resetting the internal logic, erroneous operation may occur. To avoid this, ensure the following sequence is followed:

- Set SCL = SDA = HIGH

- Raise the power supply voltage such that the Power on Reset (POR) circuit operates.

Note the following requirements to ensure that the POR functions correctly:

- Set the power supply voltage rise time (t<sub>R</sub>) to less than 10 ms.

- Set the OFF period (t<sub>OFF</sub>) after the power supply is isolated to greater than 100 ms.

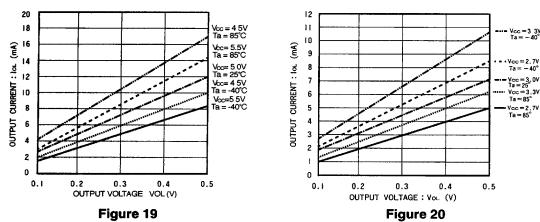

### SDA pin pull-up resistance

The SDA pin is an N channel open drain output. Therefore, a pull-up external resistor is required. Make sure to select an appropriate value for this pull-up resistance value based on the  $V_{OL}$  and  $I_{OL}$  characteristics of this IC, together with the measured data for  $V_{IL}$  and  $I_{LI}$  for personal computers and other devices that control this IC.

The recommended value for the resistor is  $2.0 \sim 10 \text{ k}\Omega$

Standard & Memory ICs

ROHM

131

### **Electrical characteristic curves**

Note: The memory data array is in the "FF" state when shipped from ROHM.

132 ROHM Standard & Memory ICs

**7828999 0012262 112 🖿**