# WEB-CUSTOMIZABLE ANY-FREQUENCY CMOS CLOCK GENERATOR

#### **Features**

- www.silabs.com/custom-timing

- Generates up to 8 non-integer-related frequencies from 8 kHz to 160 MHz

- Exact frequency synthesis at each output (0 ppm error)

- Glitchless frequency changes

- Low output period jitter: < 70 ps pp, typ

- Configurable Spread Spectrum selectable at each output

- User-configurable control pins:

- Output Enable (OEB\_0/1/2)

- Power Down (PDN)

- Frequency Select (FS\_0/1)

- Spread Spectrum Enable (SSEN)

- Supports static phase offset

- Rise/fall time control

- Operates from a low-cost, fixed frequency crystal: 25 or 27 MHz

- Separate voltage supply pins:

- Core VDD: 2.5 V or 3.3 V

- Output VDDO: 1.8V, 2.5 V or 3.3 V

- Excellent PSRR eliminates external power supply filtering

- Very low power consumption (<40 mA)</li>

- Available in 2 packages types:

- 10-MSOP: 3 outputs

- 20-QFN (4x4 mm): 8 outputs

- PCIE Gen 1 compatible

- Supports HCSL jitter compatible swing

#### **Applications**

- HDTV, DVD/Blu-ray, set-top box

- Audio/video equipment, gaming

- Printers, scanners, projectors

- Residential gateways

- Networking/communication

- Servers, storage

- XO replacement

#### **Description**

The Si5350A is a user-definable custom clock generator that is ideally suited for replacing crystals and crystal oscillators in cost-sensitive applications. Based on a PLL + high resolution fractional divider MultiSynth<sup>TM</sup> architecture, the Si5350A can generate any frequency up to 160 MHz on each of its outputs with 0 ppm error. Spread spectrum is selectable (on/off) on any of the outputs. Custom pin-controlled Si5350A devices can be requested using the ClockBuilder web-based part number utility (www.silabs.com/ClockBuilder).

#### **Functional Block Diagram**

# TABLE OF CONTENTS

| <u>Section</u>                                 | <u>Page</u> |

|------------------------------------------------|-------------|

| 1. Electrical Specifications                   | 4           |

| 2. Typical Application                         |             |

| 2.1. Si5350A Replaces Multiple Clocks and XOs  |             |

| 2.2. Applying a Reference Clock at XTAL Input  |             |

| 2.3. HCSL Compatible Outputs                   |             |

| 3. Functional Description                      |             |

| 4. Configuring the Si5350A                     |             |

| 4.1. Crystal Inputs (XA, XB)                   |             |

| 4.2. Output Clocks (CLK0–CLK7)                 |             |

| 4.3. Programmable Control Pins (P0–P4) Options |             |

| 4.4. Design Considerations                     |             |

| 5. Pin Descriptions                            |             |

| 5.1. 20-pin QFN                                |             |

| 5.2. 10-pin MSOP                               |             |

| 6. Ordering Information                        |             |

| 7. Package Outline                             |             |

| 7.1. 20-pin QFN                                |             |

| 7.2. 10-pin MSOP                               |             |

| Contact Information                            | 22          |

3

## 1. Electrical Specifications

**Table 1. Recommended Operating Conditions**

| Parameter             | Symbol            | Test Condition | Min  | Тур | Max  | Unit |

|-----------------------|-------------------|----------------|------|-----|------|------|

| Ambient Temperature   | T <sub>A</sub>    |                | -40  | 25  | 85   | °C   |

| Core Supply Voltage   | V                 |                | 3.0  | 3.3 | 3.60 | V    |

|                       | $V_{DD}$          |                | 2.25 | 2.5 | 2.75 | V    |

| Output Buffer Voltage | V <sub>DDOx</sub> |                | 1.71 | 1.8 | 1.89 | V    |

|                       |                   |                | 2.25 | 2.5 | 2.75 | V    |

|                       |                   |                | 3.0  | 3.3 | 3.60 | V    |

Note: All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions. Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise noted. VDD and VDDOx can be operated at independent voltages. Power supply sequencing for VDD and VDDOx requires that all VDDOx be powered up either before or at the same time as VDD.

**Table 2. DC Characteristics**

$(V_{DD} = 2.5 \text{ V} \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                  | Symbol             | Test Condition                                    | Min | Тур | Max | Unit |

|--------------------------------------------|--------------------|---------------------------------------------------|-----|-----|-----|------|

|                                            |                    | Enabled 3 outputs                                 | _   | 20  | 30  | mA   |

| Core Supply Current*                       | I <sub>DD</sub>    | Enabled 8 outputs                                 | _   | 25  | 40  | mA   |

|                                            |                    | Power Down (PDN = VDD)                            | _   | _   | 50  | μΑ   |

| Output Buffer Supply Current (Per Output)* | I <sub>DDOx</sub>  | C <sub>L</sub> = 5 pF                             | _   | 2.2 | 5.0 | mA   |

| Input Current                              | I <sub>P1-P4</sub> | Pins P1, P2, P3, P4<br>V <sub>P1-P4</sub> < 3.6 V | _   | _   | 10  | μΑ   |

|                                            | I <sub>P0</sub>    | Pin P0                                            | _   |     | 30  | μΑ   |

| Output Impedance                           | Z <sub>OI</sub>    | 3.3 V VDDO, default high drive.                   | _   | 50  | _   | Ω    |

| *Note: Output clocks less the              | nan or equal to    | ) 100 MHz.                                        |     |     |     |      |

#### **Table 3. AC Characteristics**

$(V_{DD} = 2.5 \text{ V } \pm 10\%, \text{ or } 3.3 \text{ V } \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                              | Symbol            | Test Condition                                                                             | Min  | Тур  | Max  | Unit |

|----------------------------------------|-------------------|--------------------------------------------------------------------------------------------|------|------|------|------|

| Powerup Time                           | T <sub>RDY</sub>  | From $V_{DD} = V_{DDmin}$ to valid output clock, $C_L = 5$ pF, $f_{CLKn} > 1$ MHz          | _    | 2    | 10   | ms   |

| Powerdown Time                         | T <sub>PD</sub>   | From $V_{DD} = V_{DDmin}$ , $C_L = 5 pF$ ,<br>$f_{CLKn} > 1 MHz$                           | _    | 5    | 100  | ms   |

| Output Enable Time                     | T <sub>OE</sub>   | From OEB assertion to valid clock output, C <sub>L</sub> = 5 pF, f <sub>CLKn</sub> > 1 MHz | 1    |      | 10   | μs   |

| Output Frequency Transition Time       | T <sub>FREQ</sub> | f <sub>CLKn</sub> > 1 MHz                                                                  |      | _    | 10   | μs   |

| Spread Spectrum Frequency<br>Deviation | SS <sub>DEV</sub> | Down spread                                                                                | -0.5 | _    | -2.5 | %    |

| Spread Spectrum Modulation Rate        | SS <sub>MOD</sub> |                                                                                            | 30   | 31.5 | 33   | kHz  |

#### **Table 4. Input Characteristics**

$(V_{DD} = 2.5 \text{ V} \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                | Symbol               | Test Condition | Min                   | Тур | Max                   | Unit |

|--------------------------|----------------------|----------------|-----------------------|-----|-----------------------|------|

| Crystal Frequency        | f <sub>XTAL</sub>    |                | 25                    | _   | 27                    | MHz  |

| P0-P4 Input Low Voltage  | V <sub>IL_P0-4</sub> |                | -0.1                  | _   | 0.3 x V <sub>DD</sub> | V    |

| P0-P4 Input High Voltage | V <sub>IH_P0-4</sub> |                | 0.7 x V <sub>DD</sub> | 1   | 3.60                  | V    |

#### **Table 5. Output Characteristics**

$(V_{DD} = 2.5 \text{ V } \pm 10\%, \text{ or } 3.3 \text{ V } \pm 10\%, \text{ T}_{A} = -40 \text{ to } 85 \text{ °C})$

| Parameter           | Symbol                         | Test Condition                            | Min                   | Тур | Max | Unit     |

|---------------------|--------------------------------|-------------------------------------------|-----------------------|-----|-----|----------|

| Frequency Range     | F <sub>CLK</sub>               |                                           | 0.008                 | _   | 160 | MHz      |

| Load Capacitance    | C <sub>L</sub>                 | F <sub>CLK</sub> < 100 MHz                | _                     |     | 15  | pF       |

| Duty Cycle          | DC                             | Measured at V <sub>DD</sub> /2            | 45                    | 50  | 55  | %        |

| Rise/Fall Time      | t <sub>r</sub> /t <sub>f</sub> | 20%–80%, C <sub>L</sub> = 5 pF            | _                     | 1   | 1.5 | ns       |

| Output High Voltage | V <sub>OH</sub>                |                                           | V <sub>DD</sub> - 0.6 | _   | _   | V        |

| Output Low Voltage  | V <sub>OL</sub>                |                                           | _                     | _   | 0.6 | V        |

| Period Jitter*      | l                              | 20-QFN, 4 outputs running,<br>1 per VDDO  | _                     | 40  | 95  | ne nk-nk |

|                     | J <sub>PER</sub>               | 10-MSOP or 20-QFN,<br>all outputs running | _                     | 70  | 140 | ps pk-pk |

\*Note: Measured over 10k cycles. Jitter is highly dependent on device frequency configuration. Specifications represent a "worst case, real world" frequency plan; actual performance may be substantially better. For 3 output 10-MSOP package, measured with clock outputs of 74.25, 24.576, 48 MHz. For 8 output 20-QFN package, measured with clock outputs of 33.33, 74.25, 27, 24.576, 22.5792, 28.322, 125, 48 MHz.

Rev. 0.75 5

#### **Table 5. Output Characteristics (Continued)**

$(V_{DD} = 2.5 \text{ V} \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                              | Symbol                                | Test Condition                         | Min | Тур | Max   | Unit  |

|----------------------------------------|---------------------------------------|----------------------------------------|-----|-----|-------|-------|

| Cycle-to-Cycle Jitter* J <sub>CC</sub> | 20-QFN, 4 outputs running, 1 per VDDO | _                                      | 50  | 90  | ps pk |       |

|                                        | JCC                                   | 10-MSOP or 20-QFN, all outputs running | _   | 70  | 130   | рз рк |

\*Note: Measured over 10k cycles. Jitter is highly dependent on device frequency configuration. Specifications represent a "worst case, real world" frequency plan; actual performance may be substantially better. For 3 output 10-MSOP package, measured with clock outputs of 74.25, 24.576, 48 MHz. For 8 output 20-QFN package, measured with clock outputs of 33.33, 74.25, 27, 24.576, 22.5792, 28.322, 125, 48 MHz.

## Table 6. 25 MHz Crystal Requirements<sup>1,2</sup>

| Parameter                    | Symbol            | Min | Тур | Max | Unit |

|------------------------------|-------------------|-----|-----|-----|------|

| Crystal Frequency            | f <sub>XTAL</sub> | _   | 25  | _   | MHz  |

| Load Capacitance             | C <sub>L</sub>    | 6   | _   | 12  | pF   |

| Equivalent Series Resistance | r <sub>ESR</sub>  | _   | _   | 150 | Ω    |

| Crystal Max Drive Level      | d <sub>L</sub>    | _   | _   | 150 | μW   |

#### Notes:

- 1. Crystals which require load capacitances of 6, 8, or 10 pF should use the device's internal load capacitance for optimum performance. See register 183 bits 7:6. A crystal with a 12 pF load capacitance requirement should use a combination of the internal 10 pF load capacitors in addition to external 2 pF load capacitors. Adding external 2 pF load capacitors can minimize jitter by 20%.

- 2. Refer to "AN551: Crystal Selection Guide" for more details.

Table 7. 27 MHz Crystal Requirements 1,2

| Parameter                    | Symbol            | Min | Тур | Max | Unit |

|------------------------------|-------------------|-----|-----|-----|------|

| Crystal Frequency            | f <sub>XTAL</sub> | _   | 27  | _   | MHz  |

| Load Capacitance             | C <sub>L</sub>    | 6   | _   | 12  | pF   |

| Equivalent Series Resistance | r <sub>ESR</sub>  | _   | _   | 150 | Ω    |

| Crystal Max Drive Level Spec | d <sub>L</sub>    | _   | _   | 150 | μW   |

#### Notes:

- 1. Crystals which require load capacitances of 6, 8, or 10 pF should use the device's internal load capacitance for optimum performance. See register 183 bits 7:6. A crystal with a 12 pF load capacitance requirement should use a combination of the internal 10 pF load capacitors in addition to external 2 pF load capacitors. Adding external 2 pF load capacitors can minimize jitter by 20%.

- 2. Refer to "AN551: Crystal Selection Guide" for more details.

#### **Table 8. Thermal Characteristics**

| Parameter           | Symbol            | Test Condition | Package | Value | Unit |

|---------------------|-------------------|----------------|---------|-------|------|

| Thermal Resistance  | Ο                 | Still Air      | 10-MSOP | 131   | °C/W |

| Junction to Ambient | $\theta_{\sf JA}$ | Still Air      | 20-QFN  | 51    | °C/W |

| Thermal Resistance  | 0                 | Still Air      | 10-MSOP | 43    | °C/W |

| Junction to Case    | nction to Case    | Suii Aii       | 20-QFN  | 16    | °C/W |

#### **Table 9. Absolute Maximum Ratings**

| Parameter            | Symbol               | Test Condition      | Value                          | Unit |

|----------------------|----------------------|---------------------|--------------------------------|------|

| DC Supply Voltage    | V <sub>DD_max</sub>  |                     | -0.5 to 3.8                    | V    |

|                      | V <sub>IN_P1-4</sub> | Pins P1, P2, P3, P4 | -0.5 to 3.8                    | V    |

| Input Voltage        | V <sub>IN_P0</sub>   | P0                  | -0.5 to (V <sub>DD</sub> +0.3) | V    |

|                      | V <sub>IN_XA/B</sub> | Pins XA, XB         | –0.5 to 1.3 V                  | V    |

| Junction Temperature | T <sub>J</sub>       |                     | -55 to 150                     | °C   |

**Note:** Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Rev. 0.75 7

## 2. Typical Application

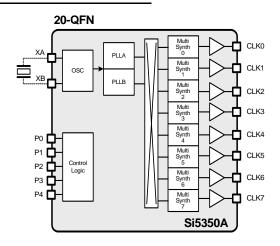

#### 2.1. Si5350A Replaces Multiple Clocks and XOs

The Si5350A is a user-definable custom clock generator that is ideally suited for replacing crystals and crystal oscillators in cost-sensitive applications. An example application is shown in Figure 1.

Figure 1. Example of an Si5350A in an Audio/Video Application

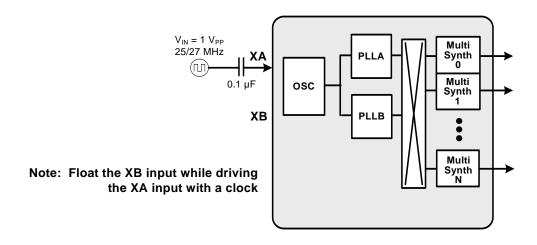

#### 2.2. Applying a Reference Clock at XTAL Input

The Si5350A can be driven with a clock signal through the XA input pin.

Figure 2. Si5350A Driven by a Clock Signal

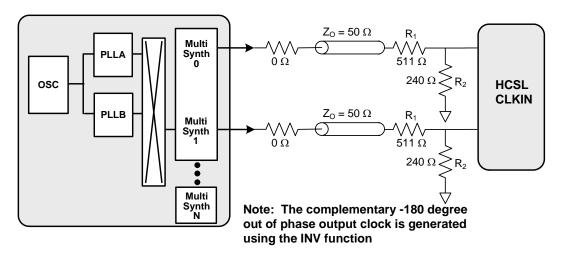

## 2.3. HCSL Compatible Outputs

The Si5350A can be configured to support HCSL compatible swing when the VDDO of the output pair of interest is set to 2.5 V (i.e., VDDOA must be 2.5 V when using CLK0/1; VDDOB must be 2.5 V for CLK2/3 and so on).

The circuit in Figure 3 must be applied to each of the two clocks used, and one of the clocks in the pair must also be inverted to generate a differential pair.

Figure 3. Si5350A Output is HCSL Compatible

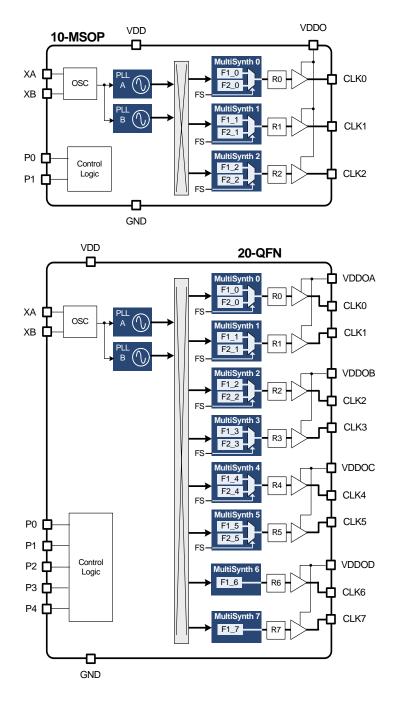

## 3. Functional Description

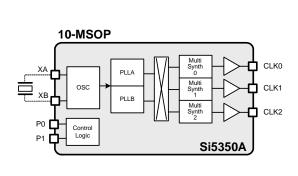

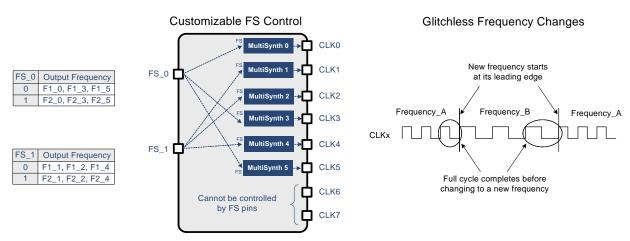

The Si5350A's synthesis architecture consists of two high-frequency PLLs in addition to one high-resolution fractional MultiSynth<sup>TM</sup> divider per output. A block diagram of both the 3-output and 8-output versions are shown in Figure 4. This unique architecture allows the Si5350A to simultaneously generate up to eight independent, non-integer-related frequencies. In addition, each MultiSynth<sup>TM</sup> is configurable with two different frequencies (F1\_x, F2\_x). This allows a pin controlled glitchless frequency change at each output (CLK0 to CLK5).

Figure 4. Block Diagrams of 3-Output and 8-Output Si5350A Devices

## 4. Configuring the Si5350A

The Si5350A is a factory-programmed custom clock generator that is user definable with a simple to use web-based utility (www.silabs.com/ClockBuilder). The ClockBuilder utility provides a simple graphical interface that allows the user to enter input and output frequencies along with other custom features as described in the following sections. All synthesis calculations are automatically performed by ClockBuilder to ensure an optimum configuration. A unique part number is assigned to each custom configuration.

#### 4.1. Crystal Inputs (XA, XB)

The Si5350A uses a fixed-frequency standard AT-cut crystal as a reference to synthesize its output clocks.

#### 4.1.1. Crystal Frequency

The Si5350A can operate using either a 27 MHz or a 25 MHz crystal.

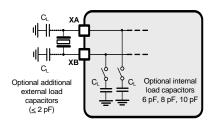

#### 4.1.2. Internal XTAL Load Capacitors

Internal load capacitors ( $C_L$ ) are provided to eliminate the need for external components when connecting a XTAL to the Si5350A. Options for internal load capacitors are 6, 8, or 10 pF. XTALs with alternate load capacitance requirements are supported using external load capacitors  $\leq$  2 pF as shown in Figure 5.

Figure 5. External XTAL with Optional Load Capacitors

### 4.2. Output Clocks (CLK0-CLK7)

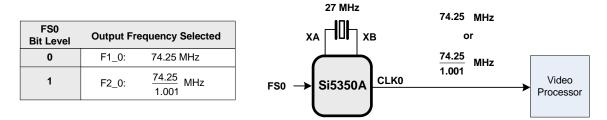

The Si5350A is orderable as a 3-output (10-MSOP) or 8-output (20-QFN) clock generator. Output clocks CLK0 to CLK5 can be ordered with two clock frequencies (F1\_x, F2\_x) which are selectable with the optional frequency select pins (FS0/1). See "4.3.3. Frequency Select (FS\_0, FS\_1)" for more details on the operation of the frequency select pins.

#### 4.2.1. Output Clock Frequency

Outputs can be configured at any frequency from 8 kHz up to 112.5 MHz. In addition, the device can generate any frequency up to 160 MHz on two of its outputs.

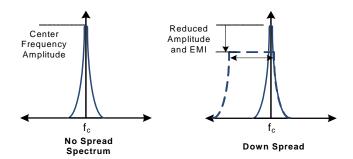

#### 4.2.2. .Spread Spectrum

Spread spectrum can be enabled on any of the clock outputs that use PLLA as its reference. Spread spectrum is useful for reducing electromagnetic interference (EMI). Enabling spread spectrum on an output clock modulates its frequency, which effectively reduces the overall amplitude of its radiated energy. Note that spread spectrum is not available on clocks synchronized to PLLB.

The Si5350A supports several levels of spread spectrum allowing the designer to choose an ideal compromise between system performance and EMI compliance.

An optional spread spectrum enable pin (SSEN) is configurable to enable or disable the spread spectrum feature. See "4.3.1. Spread Spectrum Enable (SSEN)" for details.

Figure 6. Available Spread Spectrum Profiles

#### 4.2.3. Invert/Non-Invert

By default, each of the output clocks are generated in phase (non-inverted) with respect to each other. An option to invert any of the clock outputs is also available.

#### 4.2.4. Output State When Disabled

There are up to three output enable pins configurable on the Si5350A as described in "4.3.4. Output Enable (OEB\_0, OEB\_1, OEB\_2)" . The output state when disabled for each of the outputs is configurable as output high, output low, or high-impedance.

#### 4.2.5. Powering Down Unused Outputs

Unused clock outputs can be completely powered down to conserve power.

#### 4.3. Programmable Control Pins (P0-P4) Options

Up to five programmable control pins (P0-P4) are configurable allowing direct pin control of the following features:

#### 4.3.1. Spread Spectrum Enable (SSEN)

An optional control pin allows disabling the spread spectrum feature for all outputs that were configured with spread spectrum enabled. Hold SSEN low to disable spread spectrum. The SSEN pin provides a convenient method of evaluating the effect of using spread spectrum clocks during EMI compliance testing.

#### 4.3.2. Power Down (PDN)

An optional power down control pin allows a full shutdown of the Si5350A to minimize power consumption when its output clocks are not being used. The Si5350A is in normal operation when the PDN pin is held low and is in power down mode when held high. Power consumption when the device is in power down mode is indicated in Table 2 on page 4.

#### 4.3.3. Frequency Select (FS\_0, FS\_1)

The Si5350A offers the option of configuring up to two frequencies per clock output on CLK0-CLK5. This is a useful feature for applications that need to support more than one clock rate on the same output. An example of this is shown in Figure 7 where the FS pins selects which frequency is generated from the clock output: F1\_0 is generated when FS is set low, and F2\_0 is generated when FS is set high.

Figure 7. Example of Generating Two Clock Frequencies from the Same Clock Output

Up to two frequency select pins are available on the Si5350A. Each of the frequency select pins can be linked to any of the clock outputs as shown in Figure 8. For example, FS\_0 can be linked to control clock frequency selection on CLK0, CLK3, and CLK5; FS\_1 can be used to control clock frequency selection on CLK1, CLK2, and CLK4. Any other combination is also possible.

The Si5350A uses control circuitry to ensure that frequency changes are glitchless. This ensures that the clock always completes its last cycle before starting a new clock cycle of a different frequency.

Figure 8. Example Configuration of a Pin-Controlled Frequency Select (FS)

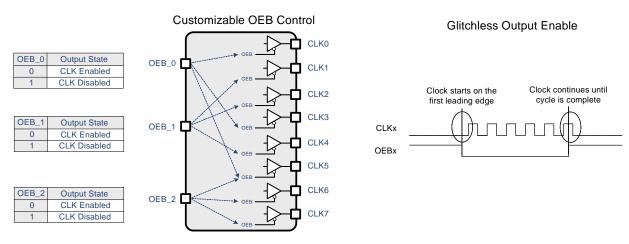

#### 4.3.4. Output Enable (OEB 0, OEB 1, OEB 2)

Up to three output enable pins (OEB\_0/1/2) are available on the Si5350A. Similar to the FS pins, each OEB pin can be linked to any of the output clocks. In the example shown in Figure 9, OEB\_0 is linked to control CLK0, CLK3, and CLK5; OEB\_1 is linked to control CLK6 and CLK7, and OEB\_2 is linked to control CLK1, CLK2, CLK4, and CLK5. Any other combination is also possible. If more than one OEB pin is linked to the same CLK output, the pin forcing a disable state will be dominant. Clock outputs are enabled when the OEB pin is held low.

The output enable control circuitry ensures glitchless operation by starting the output clock cycle on the first leading edge after OEB is asserted (OEB = low). When OEB is released (OEB = high), the clock is allowed to complete its full clock cycle before going into a disabled state. This is shown in Figure 9. When disabled, the output state is configurable as disabled high, disabled low, or disabled in high-impedance.

Figure 9. Example Configuration of a Pin-Controlled Output Enable

#### 4.4. Design Considerations

The Si5350A is a self-contained clock generator that requires very few external components. The following general guidelines are recommended to ensure optimum performance.

#### 4.4.1. Power Supply Decoupling/Filtering

The Si5350A has built-in power supply filtering circuitry to help keep the number of external components to a minimum. All that is recommended is one 0.1 to 1.0  $\mu$ F decoupling capacitor per power supply pin. This capacitor should be mounted as close to the VDD and VDDO pins as possible without using vias.

#### 4.4.2. Power Supply Sequencing

The VDD and VDDOx (i.e., VDDO0, VDDO1, VDDO2, VDDO3) power supply pins have been separated to allow flexibility in output signal levels. If a minimum output-to-output skew is important, then all VDDOx must be applied before or at the same time as VDD. Unused VDDOx pins should be tied to VDD.

#### 4.4.3. External Crystal

The external crystal should be mounted as close to the pins as possible using short PCB traces. The XA and XB traces should be kept away from other high-speed signal traces. See "AN551: Crystal Selection Guide" for more details.

#### 4.4.4. External Crystal Load Capacitors

The Si5350A provides the option of using internal and external crystal load capacitors. If external load capacitors are used, they should be placed as close to the XA/XB pads as possible. See "AN551: Crystal Selection Guide" for more details.

#### 4.4.5. Unused Pins

Unused control pins (P0-P4) should be tied to GND.

Unused output pins (CLK0–CLK7) should be left floating.

#### 4.4.6. Trace Characteristics

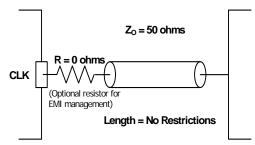

The Si5350A features various output drive strength settings. It is recommended to configure the trace characteristics as shown in Figure 10 when the default high output drive setting is used.

Figure 10. Recommended Trace Characteristics with Default Drive Strength Setting

Note: Jitter is only specified at default high drive strength.

## 5. Pin Descriptions

## 5.1. 20-pin QFN

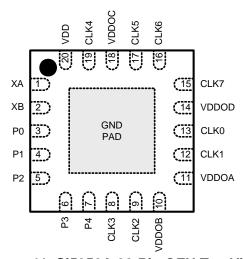

Figure 11. Si5350A 20-Pin QFN Top View

| Pin Name                                | Pin Number | Pin Type* | Function                                               |  |  |  |

|-----------------------------------------|------------|-----------|--------------------------------------------------------|--|--|--|

|                                         |            |           |                                                        |  |  |  |

| XA                                      | 1          | I         | Input pin for external XTAL                            |  |  |  |

| XB                                      | 2          | I         | Input pin for external XTAL                            |  |  |  |

| CLK0                                    | 13         | 0         | Output clock 0                                         |  |  |  |

| CLK1                                    | 12         | 0         | Output clock 1                                         |  |  |  |

| CLK2                                    | 9          | 0         | Output clock 2                                         |  |  |  |

| CLK3                                    | 8          | 0         | Output clock 3                                         |  |  |  |

| CLK4                                    | 19         | 0         | Output clock 4                                         |  |  |  |

| CLK5                                    | 17         | 0         | Output clock 5                                         |  |  |  |

| CLK6                                    | 16         | 0         | Output clock 6                                         |  |  |  |

| CLK7                                    | 15         | 0         | Output clock 7                                         |  |  |  |

| P0                                      | 3          | I         | User configurable input pin 0. See 4.4.5.              |  |  |  |

| P1                                      | 4          | I         | User configurable input pin 1. See 4.4.5.              |  |  |  |

| P2                                      | 5          | I         | User configurable input pin 2. See 4.4.5.              |  |  |  |

| P3                                      | 6          | I         | User configurable input pin 3. See 4.4.5.              |  |  |  |

| P4                                      | 7          | I         | User configurable input pin 4. See 4.4.5.              |  |  |  |

| VDD                                     | 20         | Р         | Core voltage supply pin. See 4.4.2                     |  |  |  |

| VDDOA                                   | 11         | Р         | Output voltage supply pin for CLK0 and CLK1. See 4.4.2 |  |  |  |

| VDDOB                                   | 10         | Р         | Output voltage supply pin for CLK2 and CLK3. See 4.4.2 |  |  |  |

| VDDOC                                   | 18         | Р         | Output voltage supply pin for CLK4 and CLK5. See 4.4.2 |  |  |  |

| VDDOD                                   | 14         | Р         | Output voltage supply pin for CLK6 and CLK7. See 4.4.2 |  |  |  |

| GND                                     | Center Pad | Р         | Ground                                                 |  |  |  |

| *Note: I = Input, O = Output, P = Power |            |           |                                                        |  |  |  |

Rev. 0.75 15

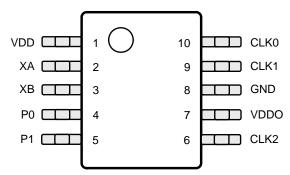

## 5.2. 10-pin MSOP

Figure 12. Si5350A 10-pin MSOP Top View

| Pin Name                                | Pin<br>Number | Pin Type* | Function                                                            |  |  |

|-----------------------------------------|---------------|-----------|---------------------------------------------------------------------|--|--|

| XA                                      | 2             | I         | Input pin for external XTAL                                         |  |  |

| XB                                      | 3             | I         | Input pin for external XTAL                                         |  |  |

| CLK0                                    | 10            | 0         | Output clock 0                                                      |  |  |

| CLK1                                    | 9             | 0         | Output clock 1                                                      |  |  |

| CLK2                                    | 6             | 0         | Output clock 2                                                      |  |  |

| P0                                      | 4             | I         | User configurable input pin 0                                       |  |  |

| P1                                      | 5             | I         | User configurable input pin 1                                       |  |  |

| VDD                                     | 1             | Р         | Core voltage supply pin. See 4.4.2                                  |  |  |

| VDDO                                    | 7             | Р         | Output clock voltage supply pin for CLK0, CLK1, and CLK2. See 4.4.2 |  |  |

| GND                                     | 8             | Р         | Ground                                                              |  |  |

| *Note: I = Input, O = Output, P = Power |               |           |                                                                     |  |  |

Rev. 0.75

16

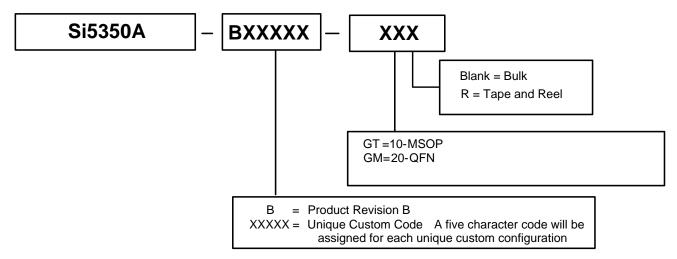

## 6. Ordering Information

Factory programmed Si5350A devices can be requested using the ClockBuilder web-based utility available at: www.silabs.com/ClockBuilder. A unique part number is assigned to each custom configuration as indicated in Figure 13.

Figure 13. Custom Clock Part Numbers

## 7. Package Outline

## 7.1. 20-pin QFN Package Outline

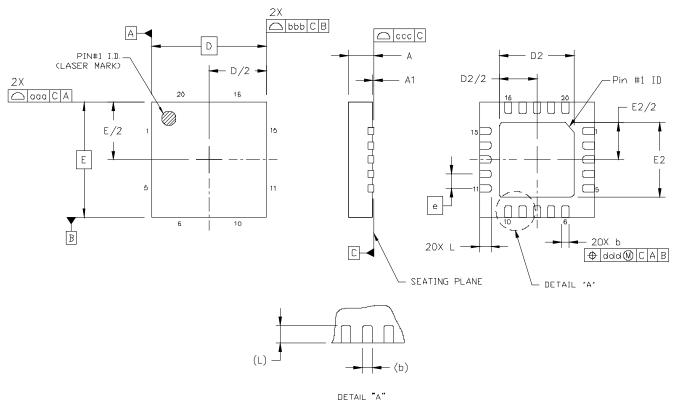

Figure 14 illustrates the package details for the Si5350A-B. Table 10 lists the values for the dimensions shown in the illustration.

Figure 14. 20-pin QFN Package Drawing

**Table 10. Package Dimensions**

| Dimension | Min      | Nom  | Max  |  |  |

|-----------|----------|------|------|--|--|

| A         | 0.80     | 0.85 | 0.90 |  |  |

| A1        | 0.00     | 0.02 | 0.05 |  |  |

| b         | 0.18     | 0.25 | 0.30 |  |  |

| D         | 4.00 BSC |      |      |  |  |

| D2        | 2.65     | 2.70 | 2.75 |  |  |

| е         | 0.50 BSC |      |      |  |  |

| E         | 4.00 BSC |      |      |  |  |

| E2        | 2.65     | 2.70 | 2.75 |  |  |

| L         | 0.30     | 0.40 | 0.50 |  |  |

| aaa       |          |      | 0.10 |  |  |

| bbb       |          |      | 0.10 |  |  |

| ccc       |          |      | 0.08 |  |  |

| ddd       |          |      | 0.10 |  |  |

| eee       |          |      | 0.10 |  |  |

#### Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to the JEDEC Outline MO-220, variation VGGD-8.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

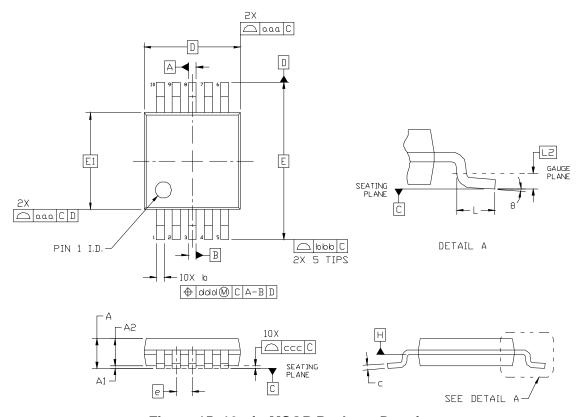

## 7.2. 10-pin MSOP Package Outline

Figure 15 illustrates the package details for the Si5350A-B. Table 11 lists the values for the dimensions shown in the illustration.

Figure 15. 10-pin MSOP Package Drawing

**Table 11. 10-MSOP Package Dimensions**

| Dimension | Min      | Nom  | Max  |  |  |  |

|-----------|----------|------|------|--|--|--|

| А         | _        | _    | 1.10 |  |  |  |

| A1        | 0.00     | _    | 0.15 |  |  |  |

| A2        | 0.75     | 0.85 | 0.95 |  |  |  |

| b         | 0.17     | _    | 0.33 |  |  |  |

| С         | 0.08     | _    | 0.23 |  |  |  |

| D         | 3.00 BSC |      |      |  |  |  |

| E         | 4.90 BSC |      |      |  |  |  |

| E1        | 3.00 BSC |      |      |  |  |  |

| е         | 0.50 BSC |      |      |  |  |  |

| L         | 0.40     | 0.60 | 0.80 |  |  |  |

| L2        | 0.25 BSC |      |      |  |  |  |

| q         | 0        | _    | 8    |  |  |  |

| aaa       | _        | _    | 0.20 |  |  |  |

| bbb       | _        | _    | 0.25 |  |  |  |

| CCC       | ccc —    |      | 0.10 |  |  |  |

| ddd —     |          | _    | 0.08 |  |  |  |

#### Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to the JEDEC Solid State Outline MO-137, Variation C

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## Si5350A-B

## **CONTACT INFORMATION**

Silicon Laboratories Inc.

400 West Cesar Chavez Austin, TX 78701 Tel: 1+(512) 416-8500

Fax: 1+(512) 416-9669 Toll Free: 1+(877) 444-3032

Please visit the Silicon Labs Technical Support web page: https://www.silabs.com/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request.

#### **Patent Notice**

Silicon Labs invests in research and development to help our customers differentiate in the market with innovative low-power, small size, analog-intensive mixed-signal solutions. Silicon Labs' extensive patent portfolio is a testament to our unique approach and world-class engineering team.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc.

Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.