# **5V Precision Data Acquisition Subsystems**

#### **Features**

- · Precision (up to 17-Bits) A/D Converter

- · 3-Wire Serial Port

- Flexible: User Can Trade Off Conversion Speed For Resolution

- · Single Supply Operation

- · -5V Output Pin

- 4 Input, Differential Analog MUX (TC530)

- Automatic Input Polarity and Overrange Detection

- · Low Operating Current: 5mA Max

- · Wide Analog Input Range: ±4.2V Max

- · Cost Effective

#### **Applications**

- · Precision Analog Signal Processor

- · Precision Sensor Interface

- · High Accuracy DC Measurements

#### **General Description**

The TC530/TC534 are serial analog data acquisition subsystems ideal for high precision measurements (up to 17-bits plus sign). The TC534 consists of a dual slope integrating A/D converter, negative power supply generator and 3 wire serial interface port. The TC530 is identical to the TC534, but adds a four channel differential input multiplexer. Key A/D converter operating parameters (Auto Zero and Integration time) are programmable, allowing the user to trade conversion time for resolution.

Data conversion is initiated when the RESET input is brought low. After conversion, data is loaded into the output shift register and  $\overline{EOC}$  is asserted, indicating new data is available. The converted data (plus Overrange and polarity bits) is held in the output shift register until read by the processor or until the next conversion is completed, allowing the user to access data at any time.

The TC530/TC534 timebase can be derived from an external crystal of 2MHz (max) or from an external frequency source. The TC530/TC534 requires a single 5V power supply and features a -5V, 10mA output which can be used to supply negative bias to other components in the system.

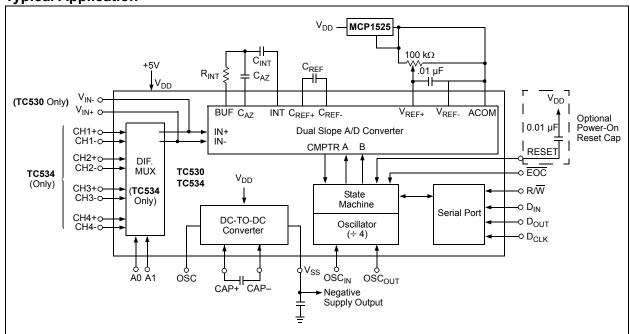

Typical Application

#### **Package Types** 28-Pin SOIC 40-Pin PDIP 28-Pin PDIP $V_{SS}$ 1 40 CAP-28 CAP- $V_{SS}$ 1 AGND 39 C<sub>INT</sub> 2 C<sub>INT</sub> 2 27 AGND 38 CAP+ C<sub>AZ</sub> 3 C<sub>AZ</sub> 3 26 CAP+ $V_{DD}$ BUF 4 37 BUF 4 25 V<sub>DD</sub> 36 N/C ACOM ACOM 5 24 N/C C<sub>REF-</sub> 35 N/C 23 OSC C<sub>REF-</sub> 6 TC530CPI C<sub>REF+</sub> 34 osc TC530COI 22 V<sub>CCD</sub> C<sub>REF+</sub> 7 33 $V_{REF-}$ 8 N/C V<sub>REF-</sub> 8 21 RESET V<sub>REF+</sub> 9 32 TC534CPL $V_{CCD}$ V<sub>REF+</sub> 9 20 EOC CH4- 10 31 N/C V<sub>IN-</sub> 10 19 R/W CH3-11 30 RESET V<sub>IN+</sub> 11 18 D<sub>IN</sub> 29 CH2-12 N/C DGND 12 17 D<sub>CLK</sub> 28 N/C CH1- 13 N/C 13 16 D<sub>OUT</sub> 27 EOC CH4+ 14 15 OSC<sub>IN</sub> OSC<sub>OUT</sub> 14 26 R/W 15 CH3+ CH2+ 25 $D_{IN}$ CH1+ 24 17 $D_{CLK}$ 23 $D_{\mathsf{OUT}}$ DGND 18 OSC<sub>IN</sub> 22 A1 19 A0 20 21 OSC<sub>OUT</sub> 44-Pin MQFP SINT Vss CAP. $C_{AZ}$ 44 43 42 41 40 36 35 39 38 37 N/C 1 33 N/C 32 OSC ACOM 2 31 N/C C<sub>REF-</sub> 3 C<sub>REF+</sub> 4 30 V<sub>CDD</sub> 29 N/C V<sub>REF-</sub> 5 TC534CKW V<sub>REF+</sub> 6 28 RESET CH4- 7 27 N/C CH3- 8 26 N/C CH2- 9 25 N/C CH1- 10 24 EOC CH4+ 11 23 R/W 16 13 17 OSC<sub>OUT</sub> 8 14

OSCIN

D<sub>CLK</sub>

DGND

CH3+

9

۲

# 1.0 ELECTRICAL CHARACTERISTICS

# **Absolute Maximum Ratings †**

† Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operation sections of the specifications is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL SPECIFICATIONS**

| Electrical Characteristics: Unless otherwise specifier, $V_{DD} = V_{CCD}$ , $C_{AZ} = C_{REF} = 0.47 \mu F$ |                  |                        |       |                               |                       |       |                       |        |                                          |

|--------------------------------------------------------------------------------------------------------------|------------------|------------------------|-------|-------------------------------|-----------------------|-------|-----------------------|--------|------------------------------------------|

|                                                                                                              | 0                | T <sub>A</sub> = +25°C |       | T <sub>A</sub> = 0°C to +70°C |                       |       |                       |        |                                          |

| Parameter                                                                                                    | Symbol           | Min                    | Тур   | Max                           | Min                   | Тур   | Max                   | Unit   | Conditions                               |

| Analog Power Supply<br>Voltage                                                                               | V <sub>DD</sub>  | 4.5                    | 5.0   | 5.5                           | 4.5                   | _     | 5.5                   | V      |                                          |

| Digital Power Supply Voltage                                                                                 | $V_{CCD}$        | 4.5                    | 5.0   | 5.5                           | 4.5                   | _     | 5.5                   | V      |                                          |

| Total Power Dissipation                                                                                      | $P_{D}$          | _                      | _     | 25                            | _                     |       | _                     | mW     | $V_{DD} = V_{CCD} = 5V$                  |

| Supply Current (V <sub>S</sub> + P <sub>IN</sub> )                                                           | I <sub>S</sub>   | _                      | 1.8   | 2.5                           | _                     | _     | 3.0                   | mA     |                                          |

| Supply Current (V <sub>CCD</sub> P <sub>IN</sub> )                                                           | I <sub>CCD</sub> | _                      | _     | 1.5                           | _                     | _     | 1.7                   | mA     | F <sub>OSC</sub> = 1 MHz                 |

| Analog                                                                                                       |                  |                        |       |                               |                       |       |                       |        |                                          |

| Resolution                                                                                                   | R                | _                      | _     | ±17                           | _                     |       | ±17                   | Bits   | Note 1                                   |

| Zero Scale Error with Auto<br>Zero Phase                                                                     | ZSE              | _                      | _     | 0.5                           | _                     | 0.005 | 0.012                 | % F.S. |                                          |

| End Point Linearity                                                                                          | ENL              | _                      | 0.015 | 0.030                         | _                     | 0.015 | 0.045                 | % F.S. | Note 1 and<br>Note 2                     |

| Max. Deviation from Best<br>Straight Line Fit                                                                | NL               | _                      | 0.008 | 0.015                         | _                     | _     | _                     | % F.S. | Note 1 and<br>Note 2                     |

| Zero Scale Temperature<br>Coefficient                                                                        | ZS <sub>TC</sub> | _                      | _     |                               | _                     | 1     | 2                     | μV/°C  |                                          |

| Rollover Error                                                                                               | SYE              | _                      | .012  | _                             | _                     | .03   | _                     | % F.S. | Note 3                                   |

| Full Scale Temperature<br>Coefficient                                                                        | FS <sub>TC</sub> | _                      | _     | _                             | _                     | 10    | _                     | ppm/°  | Ext. V <sub>REF</sub><br>T.C. = 0 ppm/°C |

| Input Current                                                                                                | I <sub>IN</sub>  | _                      | 6     | _                             | _                     | _     | l                     | pА     | V <sub>IN</sub> = 0V                     |

| Common-Mode Voltage<br>Range                                                                                 | V <sub>CMR</sub> | V <sub>SS</sub> + 1.5  | _     | V <sub>DD</sub> - 1.5         | V <sub>SS</sub> + 1.5 | _     | V <sub>DD</sub> - 1.5 | ٧      |                                          |

| Integrator Output Swing                                                                                      | V <sub>INT</sub> | V <sub>SS</sub> + 0.9  | _     | V <sub>DD</sub> - 0.9         | V <sub>SS</sub> + 0.9 | _     | V <sub>DD</sub> - 0.9 | V      |                                          |

| Analog Input Signal Range                                                                                    | V <sub>IN</sub>  | V <sub>SS</sub> + 1.5  | _     | V <sub>DD</sub> -1.5          | V <sub>SS</sub> + 1.5 | _     | V <sub>DD</sub> - 1.5 | V      |                                          |

| Voltage Reference Range                                                                                      | $V_{REF}$        | V <sub>SS</sub> + 1    | _     | V <sub>DD</sub> - 1           | V <sub>DD</sub> + 1   | _     | V <sub>DD</sub> - 1   | V      |                                          |

| Zero Crossing Comparator<br>Delay                                                                            | T <sub>D</sub>   | _                      | 2.0   | _                             | _                     | 3.0   | _                     | μS     |                                          |

- **Note 1:** Integrate time  $\geq$  66 ms. Auto Zero time  $\geq$  66 ms.  $V_{INT}$  (pk) = 4V.

- 2: End point linearity at ±1/4, ±1/2, and ±3/4. F.S. after full scale adjustment.

- 3: Rollover error is related to capacitor used for CINT. See Table 6-2, Recommended Capacitor for CINT.

- 4: TC534 Only.

# **ELECTRICAL SPECIFICATIONS (CONTINUED)**

| Electrical Characteristics: U              | Jnless othe                     | rwise spec             | ifier, V <sub>DI</sub> | o = V <sub>CCD</sub> , (      | C <sub>AZ</sub> = C <sub>REF</sub> = | = 0.47 µF | :          |      |                           |

|--------------------------------------------|---------------------------------|------------------------|------------------------|-------------------------------|--------------------------------------|-----------|------------|------|---------------------------|

| Parameter                                  | Symbol                          | T <sub>A</sub> = +25°C |                        | T <sub>A</sub> = 0°C to +70°C |                                      | 1114      | Conditions |      |                           |

| Parameter                                  | Syllibol                        | Min                    | Тур                    | Max                           | Min                                  | Тур       | Max        | Unit | Conditions                |

| Serial Port Interface                      |                                 |                        |                        |                               |                                      |           |            |      |                           |

| Input Logic HIGH Level                     | V <sub>IH</sub>                 | 2.5                    | _                      | _                             | 2.5                                  | _         | _          | V    |                           |

| Input Logic LOW Level                      | $V_{IL}$                        | 1                      | _                      | 0.8                           | _                                    | _         | 0.8        | V    |                           |

| Input Current (DI, DO, D <sub>CLK</sub> )  | I <sub>IN</sub>                 | 1                      | _                      | 10                            | _                                    | _         | _          | μA   |                           |

| Logic LOW Output Voltage (EOC)             | V <sub>OL</sub>                 |                        | 0.2                    | 0.3                           | _                                    |           | 0.35       | V    | I <sub>OUT</sub> = 250 μA |

| Rise and Fall Times (EOC, DI, DO)          | T <sub>R</sub> , T <sub>F</sub> | _                      | _                      | 250                           | _                                    | 250       |            | ns   | C <sub>L</sub> = 10 pF    |

| Crystal Frequency                          | F <sub>XTL</sub>                | _                      | _                      | 2.0                           | _                                    | _         | 2.0        | MHz  |                           |

| External Frequency on OSC <sub>IN</sub>    | F <sub>EXT</sub>                | _                      | _                      | 4.0                           | _                                    |           | 4.0        | MHz  |                           |

| Read Setup Time                            | T <sub>RS</sub>                 | 1                      | _                      | _                             | _                                    | 1         | _          | μs   |                           |

| Read Delay Time                            | T <sub>RD</sub>                 | 250                    | _                      | _                             | _                                    | 250       |            | ns   |                           |

| D <sub>CLK</sub> to D <sub>OUT</sub> Delay | T <sub>DRS</sub>                | 450                    | _                      | _                             | _                                    | 450       |            | ns   |                           |

| D <sub>CLK</sub> LOW Pulse Width           | T <sub>PWL</sub>                | 150                    | _                      | _                             | _                                    | 150       |            | ns   |                           |

| D <sub>CLK</sub> HIGH Pulse Width          | T <sub>PWH</sub>                | 150                    | _                      | _                             | _                                    | 150       |            | ns   |                           |

| Data Ready Delay                           | $T_{DR}$                        | 200                    | _                      | _                             | _                                    | 200       |            | ns   |                           |

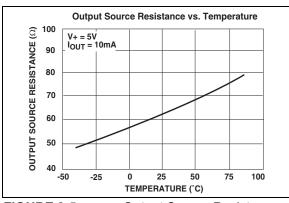

| Output Resistance                          | R <sub>OUT</sub>                |                        | 65                     | 85                            | _                                    | _         | 100        | Ω    | I <sub>OUT</sub> = 10 mA  |

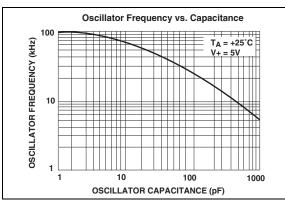

| Oscillator Frequency                       | F <sub>CLK</sub>                | _                      | 100                    | _                             | _                                    | _         |            | kHz  | C <sub>OSC</sub> = 0      |

| V <sub>SS</sub> Output Current             | I <sub>OUT</sub>                | _                      | _                      | 10                            | _                                    | _         | 10         | mA   |                           |

| Multiplexer                                |                                 |                        |                        |                               |                                      |           |            |      |                           |

| Maximum Input Voltage                      | V <sub>IMMAX</sub>              | -2.5                   | _                      | 2.5                           | -2.5                                 | _         | 2.5        | V    |                           |

| Drain/Source ON<br>Resistance              | R <sub>DSON</sub>               | _                      | 6                      | 10                            | _                                    | _         | _          | kΩ   |                           |

**Note 1:** Integrate time  $\geq$  66 ms. Auto Zero time  $\geq$  66 ms.  $V_{INT}$  (pk) = 4V.

<sup>2:</sup> End point linearity at  $\pm 1/4$ ,  $\pm 1/2$ , and  $\pm 3/4$ . F.S. after full scale adjustment.

<sup>3:</sup> Rollover error is related to capacitor used for CINT. See Table 6-2, Recommended Capacitor for C<sub>INT</sub>.

<sup>4:</sup> TC534 Only.

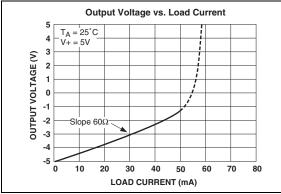

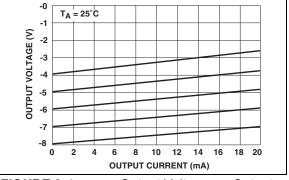

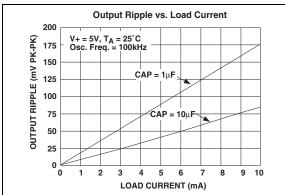

## 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range), and therefore outside the warranted range.

FIGURE 2-1: Output Voltage vs. Load Current.

**Output Voltage vs. Output Current**

FIGURE 2-4: Current.

Output Voltage vs. Output

FIGURE 2-2: Output Ripple vs. Load Current.

**FIGURE 2-5:** Output Source Resistance vs. Temperature.

FIGURE 2-3: Capacitance.

Oscillator Frequency vs.

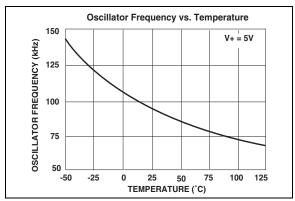

FIGURE 2-6:

Oscillator Frequency vs.

Temperature.

# 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| Pin Number<br>(TC530)<br>28-Pin PDIP | Pin Number<br>(TC530)<br>28-Pin SOIC | Pin Number<br>(TC534)<br>40-Pin PDIP | Pin<br>Number<br>(TC534)<br>44-Pin<br>MQFP | Sym                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                    | 1                                    | 1                                    | 40                                         | V <sub>SS</sub>    | Analog output. Negative power supply converter output and reservoir capacitor connection. This output can be used to provide negative bias to other devices in the system.                                                                                                                                                                                                                                                                                                                               |

| 2                                    | 2                                    | 2                                    | 41                                         | C <sub>INT</sub>   | Analog output. Integrator capacitor connection and integrator output.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3                                    | 3                                    | 3                                    | 42                                         | $C_{AZ}$           | Analog input. Auto Zero capacitor connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4                                    | 4                                    | 4                                    | 43                                         | BUF                | Analog output. Integrator capacitor connection and voltage buffer output.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5                                    | 5                                    | 5                                    | 2                                          | ACOM               | Analog input. This pin is ground for all of the analog switches in the A/D converter. It is grounded for most applications. ACOM and the input common pin (V <sub>IN</sub> - or CHX-) should be within the common mode range, CMR.                                                                                                                                                                                                                                                                       |

| 6                                    | 6                                    | 6                                    | 3                                          | C <sub>REF</sub> - | Analog Input. Reference cap negative connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7                                    | 7                                    | 7                                    | 4                                          | C <sub>REF</sub> + | Analog Input. Reference cap positive connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8                                    | 8                                    | 8                                    | 5                                          | V <sub>REF</sub> - | Analog Input. External voltage reference negative connection.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9                                    | 9                                    | 9                                    | 6                                          | V <sub>REF</sub> + | Analog Input. External voltage reference positive connection.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| _                                    | _                                    | 10                                   | 7                                          | CH4-               | Analog Input. Multiplexer channel 4 negative differential                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| _                                    | _                                    | 11                                   | 8                                          | CH3-               | Analog Input. Multiplexer channel 3 negative differential                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| _                                    | _                                    | 12                                   | 9                                          | CH2-               | Analog Input. Multiplexer channel 2 negative differential                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| _                                    | _                                    | 13                                   | 10                                         | CH1-               | Analog Input. Multiplexer channel 1 negative differential                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| _                                    | _                                    | 14                                   | 11                                         | CH4+               | Analog Input. Multiplexer channel 4 positive differential                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| _                                    | _                                    | 15                                   | 12                                         | CH3+               | Analog Input. Multiplexer channel 3 positive differential                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| _                                    | _                                    | 16                                   | 13                                         | CH2+               | Analog Input. Multiplexer channel 2 positive differential                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| _                                    | _                                    | 17                                   | 14                                         | CH1+               | Analog Input. Multiplexer channel 1 positive differential                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10                                   | 10                                   | _                                    | _                                          | V <sub>N</sub> -   | Analog Input. Negative differential analog voltage input.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11                                   | 11                                   | _                                    | _                                          | V <sub>IN</sub> +  | Analog Input. Positive differential analog voltage input.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12                                   | 12                                   | 18                                   | 15                                         | DGND               | Analog Input. Ground connection for serial port circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| _                                    | _                                    | 19                                   | 16                                         | A1                 | Logic Level Input. Multiplexer address MSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| _                                    | _                                    | 20                                   | 17                                         | A0                 | Logic Level Input. Multiplexer address LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 14                                   | 14                                   | 21                                   | 18                                         | OSC <sub>OUT</sub> | Analog Input. Timebase for state machine. This pin connects to one side of an AT-cut crystal having an effective series resistance of $100\Omega$ (typ) and a parallel capacitance of 20 pF. If an external frequency source is used to clock the TC530/TC534 this pin must be left floating.                                                                                                                                                                                                            |

| 15                                   | 15                                   | 22                                   | 19                                         | OSC <sub>IN</sub>  | Analog Input. This pin connects to the other side of the crystal described in $OSC_{OUT}$ above. The $TC530/TC534$ may also be clocked from an external frequency source connected to this pin. The external frequency source must be a pulse waveform with a minimum 30% duty cycle and rise and fall times 15nsec (Max). If an external frequency source is used, $OSC_{OUT}$ ) must be left floating. A maximum operating frequency of 2 MHz (crystal) or 4 MHz (external clock source) is permitted. |

TABLE 3-1: PIN FUNCTION TABLE (CONTINUED)

| Pin Number<br>(TC530)<br>28-Pin PDIP | Pin Number<br>(TC530)<br>28-Pin SOIC | Pin Number<br>(TC534)<br>40-Pin PDIP | Pin<br>Number<br>(TC534)<br>44-Pin<br>MQFP | Sym              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16                                   | 16                                   | 23                                   | 20                                         | D <sub>OUT</sub> | Logic Level Output. Serial port data output pin. This pin is enabled only when R/W is high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 17                                   | 17                                   | 24                                   | 21                                         | D <sub>CLK</sub> | Logic Input, Positive and Negative Edge Triggered. Serial port clock. When $R/\overline{W}$ is high, serial data is clocked out of the TC530/TC534A (on $D_{OUT}$ ) at each high-to-low transition of $D_{CLK}$ . A/D initialization data (LOAD VALUE) is clocked into the TC530/TC534 (on $D_{IN}$ ) at each low-to-high transition of $D_{CLK}$ . A maximum serial port $D_{CLK}$ frequency of 3 MHz is permitted.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 18                                   | 18                                   | 25                                   | 22                                         | D <sub>IN</sub>  | Logic Level Input. Serial port input pin. The A/D converter integration time ( $T_{INT}$ ) and Auto Zero time ( $T_{AZ}$ ) values are determined by the LOAD VALUE byte clocked into this pin. This initialization must take place at power up, and can be rewritten (or modified and rewritten) at any time. The LOAD VALUE is clocked into $D_{IN}$ MSB first.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 19                                   | 19                                   | 26                                   | 23                                         | R/W              | Logic Level Input. This pin must be brought low to perform a write to the serial port (e.g. initialize the A/D converter). The D <sub>OUT</sub> pin of the serial port is enabled only when this pin is high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 20                                   | 20                                   | 27                                   | 24                                         | EOC              | Open Drain Output. End-of-Conversion (EOC) is asserted any time the TC530/TC534 is in the AZ phase of conversion. This occurs when either the TC530/TC534 initiates a normal AZ phase or when RESET is pulled high. EOC is returned high when the TC530/TC534 exits AZ. Since EOC is driven low immediately following completion of a conversion cycle, it can be used as a DATA READY processor interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 21                                   | 21                                   | 30                                   | 28                                         | RESET            | Logic Level Input. It is necessary to force the TC530/TC534 into the Auto Zero phase when power is initially applied. This is accomplished by momentarily taking RESET high. Using an I/O port line from the microprocessor or by applying an external system reset signal or by connecting a 0.01 µF capacitor from the RESET input to V <sub>DD</sub> . Conversions are performed continuously as long as RESET is low and conversion is halted when RESET is high. RESET may therefore be used in a complex system to momentarily suspend conversion (for example, while the address lines of an input multiplexer are changing state). In this case, RESET should be pulled high only when the EOC is LOW to avoid excessively long integrator discharge times which could result in erroneous conversion. (See <i>Applications</i> Section). |

| 22                                   | 22                                   | 32                                   | 30                                         | V <sub>CCD</sub> | Analog Input. Power supply connection for digital logic and serial port. Proper power-up sequencing is critical, see the <i>Applications</i> section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 23                                   | 23                                   | 34                                   | 32                                         | OSC              | Input. The negative power supply converter normally runs at a frequency of 100 kHz. This frequency can be slowed down to reduce quiescent current by connecting an external capacitor between this pin and V <sup>+</sup> <sub>DD</sub> . See <b>Section 2.0 "Typical Performance Curves"</b> , Typical Characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 25                                   | 25                                   | 37                                   | 35                                         | V <sub>DD</sub>  | Analog Input. Power supply connection for the A/D analog section and DC-DC converter. Proper power-up sequencing is critical, (See the <i>Applications</i> section).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# TABLE 3-1: PIN FUNCTION TABLE (CONTINUED)

| Pin Number<br>(TC530)<br>28-Pin PDIP | Pin Number<br>(TC530)<br>28-Pin SOIC | Pin Number<br>(TC534)<br>40-Pin PDIP | Pin<br>Number<br>(TC534)<br>44-Pin<br>MQFP     | Sym  | Description                                                                  |

|--------------------------------------|--------------------------------------|--------------------------------------|------------------------------------------------|------|------------------------------------------------------------------------------|

| 26                                   | 26                                   | 38                                   | 36                                             | CAP+ | Analog Input. Storage capacitor positive connection for the DC/DC converter. |

| 27                                   | 27                                   | 39                                   | 37                                             | AGND | Analog Input. Ground connection for DC/DC converter.                         |

| 28                                   | 28                                   | 40                                   | 38                                             | CAP- | Analog Input. Storage capacitor negative connection for the DC/DC converter. |

| 13, 24                               | 13, 24                               | 28, 29, 31,<br>33, 35, 36            | 1, 25, 26,<br>27, 29, 31,<br>33, 34, 39,<br>44 | N/C  | No connect. Do not connect any signal to these pins.                         |

#### 4.0 DETAILED DESCRIPTION

## 4.1 Dual Slope Integrating Converter

The TC530/TC534 dual slope converter operates by integrating the input signal for a fixed time period, then applying an opposite polarity reference voltage while timing the period (counting clocks pulses) for the integrator output to cross 0V (deintegrating). The resulting count is read as conversion data.

A simple mathematical expression that describes dual slope conversion is:

#### **EQUATION 4-1:**

Integrate Voltage = De-integrate Voltage

#### **EQUATION 4-2:**

$$\boxed{\frac{1}{R_{INT}C_{INT}}\int\limits_{0}^{}T_{INT}V_{IN}(T)dT = \frac{1}{R_{INT}C_{INT}}\int\limits_{0}^{}T_{DEINT}V_{REF}}$$

from which:

#### **EQUATION 4-3:**

$$(V_{IN}) \left[ \frac{(T_{INT})}{(R_{INT})(C_{INT})} \right] = (V_{REF}) \left[ \frac{(T_{DEINT})}{(R_{INT})(C_{INT})} \right]$$

And therefore:

#### **EQUATION 4-4:**

$V_{IN} = V_{REF} \begin{bmatrix} T_{DEIN}T \\ T_{INT} \end{bmatrix}$

Where:

V<sub>REF</sub> = Reference Voltage T<sub>INT</sub> = Integrate Time

T<sub>DEINT</sub> = Reference Voltage De-integrate

Time

Inspection of Equation 4-4 shows dual slope converter accuracy is unrelated to integrating resistor and capacitor values, as long as they are stable throughout the measurement cycle. This measurement technique is inherently ratiometric (i.e., the ratio between the  $T_{INT}$  and  $T_{DEINT}$  times is equal to the ratio between  $V_{IN}$  and  $V_{REF}). \\$

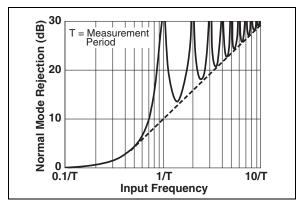

Another inherent benefit is noise immunity. Input noise spikes are integrated, or averaged to zero, during the integration period. The integrating converter has a noise immunity with an attenuation rate of at least -20 dB per decade. Interference signals with frequencies at integral multiples of the integration period are, for the most part, completely removed. For this reason, the integration

period of the converter is often established to reject 50/60 Hz line noise. The ability to reject such noise is shown by the plot of Figure 4-1.

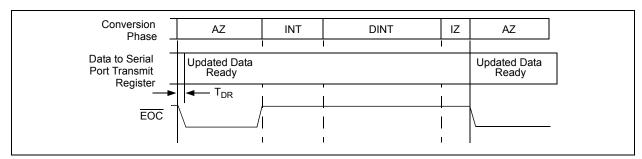

In addition to the two phases required for dual slope measurement (Integrate and De-integrate), the TC530/TC534 performs two additional adjustments to minimize measurement error due to system offset voltages. The resulting four internal operations (conversion phases) performed each measurement cycle are: Auto Zero (AZ), Integrator Output Zero (IZ), Input Integrate (INT) and Reference De-integrate (DINT). The AZ and IZ phases compensate for system offset errors and the INT and DINT phases perform the actual A/D conversion.

FIGURE 4-1: Integrating Converter Normal Mode Rejection.

## 4.2 Auto Zero Phase (AZ)

This phase compensates for errors due to buffer, integrator and comparator offset voltages. During this phase, an internal feedback loop forces a compensating error voltage on auto zero capacitor (C<sub>AZ</sub>). The duration of the AZ phase is programmable via the serial port (see **Section 5.1.1 "AZ and INT Phase Duration"**, AZ and INT Phase Duration).

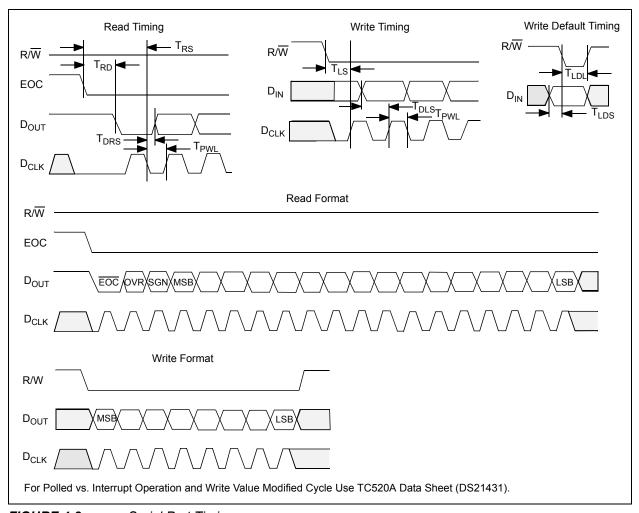

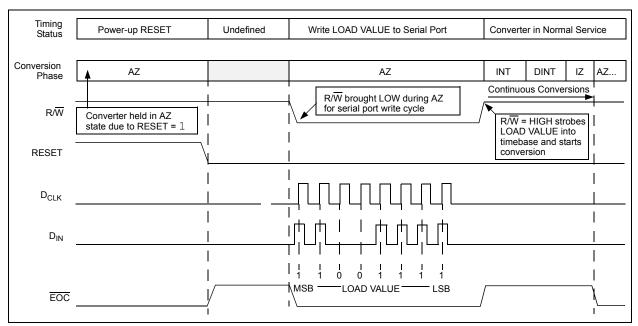

FIGURE 4-2: Serial Port Timing.

FIGURE 4-3: A/D Converter Timing.

## 4.3 Input Integrate Phase (INT)

In this phase, a current directly proportional to differential input voltage is sourced into integrating capacitor  $C_{\text{INT}}$ . The amount of voltage stored on  $C_{\text{INT}}$  at the end of the INT phase is directly proportional to the applied differential input voltage. Input signal polarity (sign bit) is determined at the end of this phase. Converter resolution and speed is a function of the duration of the INT phase, which is programmable by the user via the serial port (see **Section 5.1.1 "AZ and INT Phase Duration"**, AZ and INT Phase Duration). The shorter the integration time, the faster the speed of conversion (but the lower the resolution). Conversely, the longer the integration time, the greater the resolution (but at slower the speed of conversion).

# 4.4 Reference De-integrate Phase (DINT)

This phase consists of measuring the time for the integrator output to return (at a rate determined by the external reference voltage) from its initial voltage to 0V. The resulting timer data is stored in the output shift register as converted analog data.

## 4.5 Integrator Output Zero Phase (IZ)

This phase ensures the integrator output is at zero volts when the AZ phase is entered so that only true system offset voltages will be compensated for.

All internal converter timing is derived from the frequency source at  $OSC_{IN}$  and  $OSC_{OUT}$ . This frequency source must be either an externally provided clock signal or an external crystal. If an external clock is used, it must be connected to the  $OSC_{IN}$  pin and the  $OSC_{OUT}$  pin must remain floating. If a crystal is used, it must be connected between  $OSC_{IN}$  and  $OSC_{OUT}$  and be physically located as close to the  $OSC_{IN}$  and  $OSC_{OUT}$  pins as possible. In either case, the incoming clock frequency is divided by four, with the resulting clock serving as the internal TC530/TC534 timebase.

#### 5.0 TYPICAL APPLICATIONS

# 5.1 Programming the TC530/TC534

#### 5.1.1 AZ AND INT PHASE DURATION

These two phases have equal duration determined by the crystal (or external) frequency and the timer initialization byte (LOAD VALUE). Timing is selected as follows:

Select Integration Time

Integration time must be picked as a multiple of the period of the line frequency. For example,  $T_{\rm INT}$  times of 33 ms, 66 ms and 132 ms maximize 60 Hz line rejection.

2. Estimate Crystal Frequency

Crystal frequencies as high as 2 MHz are allowed. Crystal frequency is estimated using:

#### **EQUATION 5-1:**

$2(R_{ES})/T_{INT}$

Where:

$R_{ES}$  = Desired Converter Resolution (in

counts)

F<sub>IN</sub> = Input Frequency (in MHz)

INT = Integration Time (in seconds)

Calculate LOAD VALUE

#### **EQUATION 5-2:**

[LOAD VALUE]10 =

$$256 - \frac{(T_{INT})(F_{IN})}{1024}$$

F<sub>IN</sub> can be adjusted to a standard value during this step. The resulting base, -10 LOAD VALUE, must be converted to a hexadecimal number and then loaded into the serial port prior to initiating A/D conversion.

# 5.2 D<sub>INT</sub> and I<sub>Z</sub> Phase Timing

The duration of the  $D_{INT}$  phase is a function of the amount of voltage stored on the integrator capacitor during INT and the value of  $V_{REF}$ . The  $D_{INT}$  phase is initiated immediately following INT and terminated when an integrator output zero crossing is detected. In general, the maximum number of counts chosen for  $D_{INT}$  is twice that of INT (with  $V_{REF}$  chosen at  $V_{IN(MAX)}/2$ ).

## 5.3 System RESET

The TC530/TC534 must be forced into the AZ state when power is first applied. A .01  $\mu$ F capacitor connected from RESET to V<sub>DD</sub> (or external system reset logic signal) can be used to momentarily drive RESET high for a minimum of 100 ms.

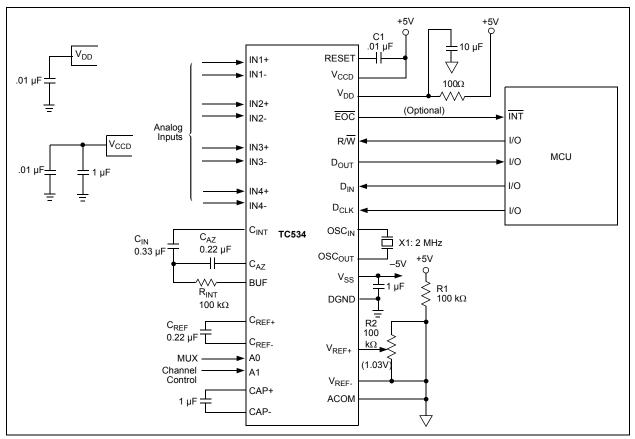

#### 5.4 Design Example

Figure 5-1 shows a typical TC530 interrupt-driven application. Timing and component values are calculated from equations and recommendations made in Section 4.1 "Dual Slope Integrating Converter" and Section 5.1 "Programming the TC530/TC534" of this document. The  $\overline{\text{EOC}}$  connection to the processor INT input is for interrupt-driven applications only. (In polled systems, the  $\overline{\text{EOC}}$  output is available on  $D_{\text{OUT}}$ ).

Given:

| Required Resolution (R <sub>FS</sub> ): | 16-bits (65,536 counts.) |

|-----------------------------------------|--------------------------|

| Maximum:                                | V <sub>IN</sub> ±2V      |

| Power Supply Voltage:                   | +5V                      |

| 60Hz System                             |                          |

- 1. Pick Integration time (T<sub>INT</sub>): 66 ms.

- 2. Estimate crystal frequency.

#### **EXAMPLE 5-1:**

$$F_{IN} = \frac{2R_{ES}}{T_{INT}} = \frac{2 \bullet 65536}{66ms} \approx 2MHz$$

3. Calculate LOAD VALUE

#### **EXAMPLE 5-2:**

LOAD VALUE =

$$256 - \frac{(T_{INT})(F_{IN})}{1024} = [128]_{10}$$

$[128]_{10} = 80 \text{ hex}$

4. Calculate R<sub>INT</sub>

#### **EXAMPLE 5-3:**

$$R_{INT} = \frac{V_{INMAX}}{20} = \frac{2}{20} = 100k\Omega$$

Calculate C<sub>INT</sub> for maximum (4V) integrator output swing:

#### **EXAMPLE 5-4:**

$$C_{INT} = \frac{(T_{INT})(20 \times 10^{6})}{(V_{s} - 0.9)}$$

$$= (.066)(20 \times 10^{-6})$$

$$= .32 \,\mu\text{F (use closest value: 0.33 }\mu\text{F})$$

**Note:** Microchip recommended capacitor: Evox-Rifa p/n: SMR5 334K50J03L

Choose C<sub>REF</sub> and C<sub>AZ</sub> based on conversion rate:

#### **EXAMPLE 5-5:**

$$Conversions/sec = 1/(T_{AZ} + T_{INT} + 2T_{INT} + 2ms)$$

$$= 1/(66ms + 66ms + 132ms + 2ms)$$

$$= 3.7 \ conversions/sec$$

$$from \ which \ C_{AZ} = C_{REF} = \underline{0.22\mu F} \ (Table \ 6-1)$$

**Note:** Microchip recommended capacitor: Evox-Rifa p/n: SMR5 224K50J02L4.

Calculate V<sub>REF</sub>.

#### **EXAMPLE 5-1:**

$$\begin{split} V_{REF} &= \frac{(V_S - 0.9)(C_{INT})(R_{INT})}{2(T_{INT})} \\ &= \frac{(4.1)(0.33 \times 1^{-6})(10^5)}{2(.066)} \\ &= 1.025 \, V \end{split}$$

## 5.5 Power Supply Sequencing

Improper sequencing of the power supply inputs ( $V_{DD}$  vs.  $V_{CCD}$ ) can potentially cause an improper power-up sequence to occur. See **Section 5.6 "Circuit Design/Layout Considerations"**, Circuit Design/Layout Considerations. Failing to insure a proper power-up sequence can cause spurious operation.

# 5.6 Circuit Design/Layout Considerations

- Separate ground return paths should be used for the analog and digital circuitry. Use of ground planes and trace fill on analog circuit sections is highly recommended EXCEPT for in and around the integrator section and C<sub>REF</sub>, C<sub>AZ</sub> (C<sub>INT</sub>, C<sub>REF</sub>, C<sub>AZ</sub>, R<sub>INT</sub>). Stray capacitance between these nodes and ground appears in parallel with the components themselves and can affect measurement accuracy.

- Improper sequencing of the power supply inputs (V<sub>DD</sub> vs. V<sub>CCD</sub>) can potentially cause an improper power-up sequence to occur in the internal state machines. It is recommended that the digital supply, V<sub>CCD</sub>, be powered up first. One method of insuring the correct power-up sequence is to delay the analog supply using a series resistor and a capacitor. See Figure 5-1, TC530/TC534 Typical Application.

- Decoupling capacitors, preferably a higher value electrolytic or tantulum in parallel with a small ceramic or tantalum, should be used liberally. This includes bypassing the supply connections of all active components and the voltage reference.

- Critical components should be chosen for stability and low noise. The use of a metal-film resistor for R<sub>INT</sub> and Polypropylene or Polyphenelyne Sulfide (PPS) capacitors for C<sub>INT</sub>, C<sub>AZ</sub> and C<sub>REF</sub> is highly recommended.

- The inputs and integrator section are very high impedance nodes. Leakage to or from these critical nodes can contribute measurement error. A guard-ring should be used to protect the integrator section from stray leakage.

- 6. Circuit assemblies should be exceptionally clean to prevent the presence of contamination from assembly, handling or the cleaning itself. Minute conductive trace contaminates, easily ignored in most applications, can adversely affect the performance of high impedance circuits. The input and integrator sections should be made as compact and close to the TC53X as possible.

- 7. Digital and other dynamic signal conductors should be kept as far from the TC53X's analog section as possible. The microcontroller or other host logic should be kept quiet during a measurement cycle. Background activities such as keypad scanning, display refreshing and power switching can introduce noise.

FIGURE 5-1: Typical Application.

# 6.0 SELECTING COMPONENT VALUES FOR THE TC530/TC534

1. Calculate Integrating Resistor (R<sub>INT</sub>)

The desired full scale input voltage and amplifier output current capability determine the value of  $R_{\text{INT}}.$  The buffer and integrator amplifiers each have a full scale current of 20  $\mu A.$  The value of  $R_{\text{INT}}$  is therefore directly calculated as follows:

#### **EQUATION 6-1:**

$$R_{INT}(M\Omega) = \frac{V_{INMAX}}{20}$$

Where:

$V_{IN(MAX)}$  = Maximum Input Voltage (full

count voltage)

$R_{INT}$  = Integrating Resistor (in MΩ) For loop stability,  $R_{INT}$  should be  $\geq$  50 kΩ.

Select Reference (C<sub>REF</sub>) and Auto Zero (C<sub>AZ</sub>) Capacitors.

$C_{REF}$  and  $C_{AZ}$  must be low leakage capacitors (such as polypropylene). The slower the conversion rate, the larger the value  $C_{REF}$  must be. Recommended capacitors for  $C_{REF}$  and  $C_{AZ}$  are shown in Table 6-1. Larger values for  $C_{AZ}$  and  $C_{REF}$  may also be used to limit rollover errors.

TABLE 6-1: C<sub>REF</sub> AND C<sub>AZ</sub> SELECTION

| Conversion<br>Per Second | Typical Value<br>of C <sub>REF</sub> , C <sub>AZ</sub><br>(µF) | Suggested <sup>(1)</sup> Part<br>Number |

|--------------------------|----------------------------------------------------------------|-----------------------------------------|

| >7                       | 0.1                                                            | SMR5 104K50J0IL                         |

| 2 to 7                   | 0.22                                                           | SMR5 224K50J2L                          |

| 2 or less                | 0.47                                                           | SMR5 474K50J04L                         |

Note 1: Manufactured by Evox-Rifa, Inc.

# 6.1 Calculate Integrating Capacitor (C<sub>INT</sub>)

The integrating capacitor must be selected to maximize integrator output voltage swing. The integrator output voltage swing is defined as the absolute value of  $V_{DD}$  (or  $V_{SS}$ ) less 0.9V (i.e.,IV $_{DD}-$ 0.9VI or IV $_{SS}$ +0.9VI). Using the 20  $\mu A$  buffer maximum output current, the value of the integrating capacitor is calculated using Equation 6-2.

#### **EQUATION 6-2:**

$$C_{INT}(\mu F) = \frac{(T_{INT})(20 \times 10^{-6})}{(V_S - 0.9)}$$

Where:

T<sub>INT</sub> = Integration Period

$V_S = IV_{DD}I$

$C_{INT}$  = Integrated Capacitor Value ( $\mu F$ )

It is critical that the integrating capacitor have a very low dielectric absorption. PPS capacitors are an example of one such dielectric. Table 6-2 summarizes various capacitors suitable for  $C_{\rm INT}$ .

TABLE 6-2: RECOMMENDED CAPACITOR FOR CINT

|            | 14 1                                 |

|------------|--------------------------------------|

| Value (μF) | Suggested Part Number <sup>(1)</sup> |

| 0.1        | SMR5 104K50J0IL                      |

| 0.22       | SMR5 224K50J2L                       |

| 0.33       | SMR5 334K50J03L4                     |

| 0.47       | SMR5 474K50J04L                      |

Note 1: Manufactured by Evox-Rifa, Inc.

# 6.2 Calculate V<sub>RFF</sub>

The reference de-integration voltage is calculated using the following equaton:

#### **EQUATION 6-3:**

$$V_{REF} = \frac{(V_S - 0.9)(C_{INT})(R_{INT})}{2(R_{INT})} V$$

#### 6.3 Serial Port

Communication with the TC530/TC534 is accomplished over a 3-wire serial port. Data is clocked into  $D_{\text{IN}}$  on the rising edge of  $D_{\text{CLK}}$  and clocked out of  $D_{\text{OUT}}$  on the falling edge of  $D_{\text{CLK}}$ . R/W must be HIGH to read converted data from the serial port and LOW to write the LOAD VALUE to the TC530/TC534.

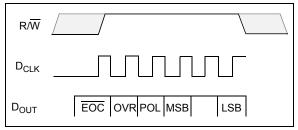

#### 6.4 Data Read Cycle

Data is shifted out of the <u>serial</u> port in the following order: End of Conversion (EOC), Overrange (OVR), Polarity (POL), conversion data (MSB first). When R/W is high, the state of the  $\overline{\rm EOC}$  bit can be polled by simply reading the state of D $_{\rm OUT}$ . This allows the processor to determine if new data is available without connecting an additional wire to the  $\overline{\rm EOC}$  output pin (this is especially useful in a polled environment). Refer to Figure 6-1.

FIGURE 6-1: Serial Port Data Read Cycle.

### 6.5 Load Value Write Cycle

Following the power-up reset pulse, the LOAD VALUE (which sets the duration of AZ and INT) must next be transmitted to the serial port. To accomplish this, the processor monitors the state of EOC (which is available as a hardware output or at  $D_{OUT}$ ).  $R/\overline{W}$  is taken low to initiate the write cycle only when  $\overline{EOC}$  is low (during the AZ phase). (Failure to observe  $\overline{EOC}$  low may cause an offset voltage to be developed across  $C_{INT}$ , resulting in erroneous readings). The 8-bit LOAD VALUE data on  $D_{IN}$  is clocked in by  $D_{CLK}$ . The  $\underline{pr}$ ocessor then terminates the write cycle by taking R/W high. (Data is

transferred from the serial input shift register to the time base counter on the rising edge of R/W and data conversion is initiated). See Figure 6-2.

## 6.6 Input Multiplexer (TC534 Only)

A 4-input, differential multiplexer is included in the TC534. The states of channel address lines A0 and A1 determine which differential  $V_{\rm IN}$  pair is routed to the converter input. A0 is the least significant address bit (i.e., channel 1 is selected when A0 = 0 and A1 = 0). The multiplexer is designed to be operated in a differential mode. For single-ended inputs, the CHx-input for the channel under selection must be connected to the ground reference associated with the input signal.

#### 6.7 DC/DC Converter

An on-board, TC7660H-type charge pump supplies negative bias to the converter circuitry, as well as to external devices. The charge pump develops a negative output voltage by moving charge from the power supply to the reservoir capacitor at  $V_{SS}$  by way of the commutating capacitor connected to the CAP+ and CAP- inputs.

The charge pump clock operates at a typical frequency of 100 kHz. If lower quiescent current is desired, the charge pump clock can be slowed by connecting an external capacitor from the OSC pin to  $V_{DD}$ . Reference typical characteristics curves.

FIGURE 6-2: TC530/TC534 Initialization and Load Value Write Cycle.

## 7.0 PACKAGING INFORMATION

# 7.1 Package Marking Information

28-Lead SPDIP

### Example

#### 28-Lead SOIC (.300")

#### Example

#### 40-Lead PDIP

# Example

## 44-Lead MQFP

#### Example

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

© Pb-free JEDEC designator for Matte Tin (Sn)

\* This package is Pb-free. The Pb-free JEDEC designator (©3)

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

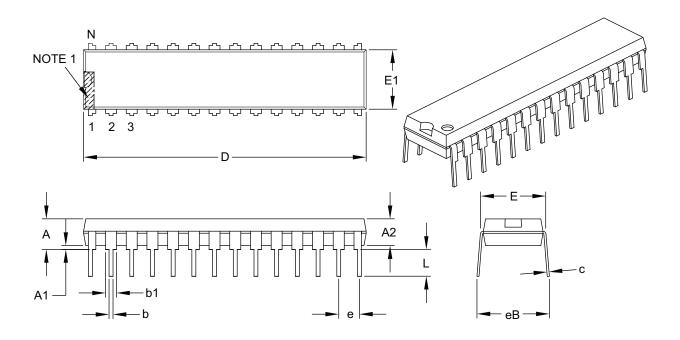

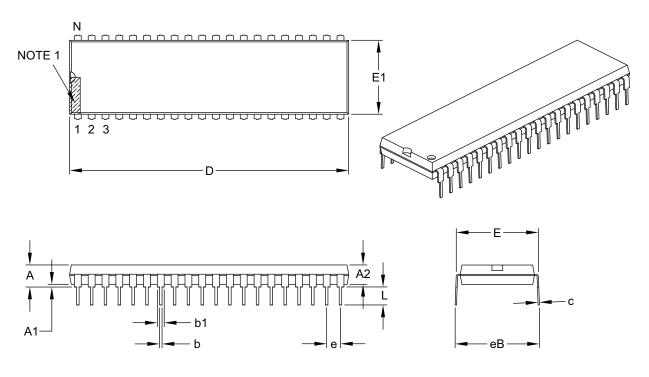

# 28-Lead Skinny Plastic Dual In-Line (PJ) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |       | INCHES   |       |

|----------------------------|----------|-------|----------|-------|

| Dimension                  | n Limits | MIN   | NOM      | MAX   |

| Number of Pins             | N        |       | 28       |       |

| Pitch                      | е        |       | .100 BSC |       |

| Top to Seating Plane       | Α        | _     | _        | .200  |

| Molded Package Thickness   | A2       | .120  | .135     | .150  |

| Base to Seating Plane      | A1       | .015  | _        | _     |

| Shoulder to Shoulder Width | Е        | .290  | .310     | .335  |

| Molded Package Width       | E1       | .240  | .285     | .295  |

| Overall Length             | D        | 1.345 | 1.365    | 1.400 |

| Tip to Seating Plane       | L        | .110  | .130     | .150  |

| Lead Thickness             | С        | .008  | .010     | .015  |

| Upper Lead Width           | b1       | .040  | .050     | .070  |

| Lower Lead Width           | b        | .014  | .018     | .022  |

| Overall Row Spacing §      | eB       | -     | _        | .430  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

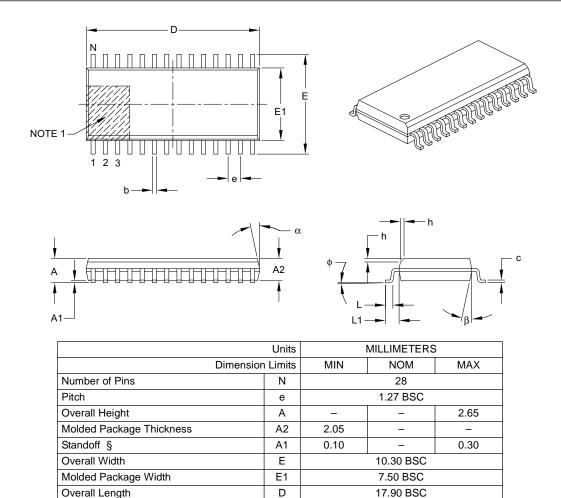

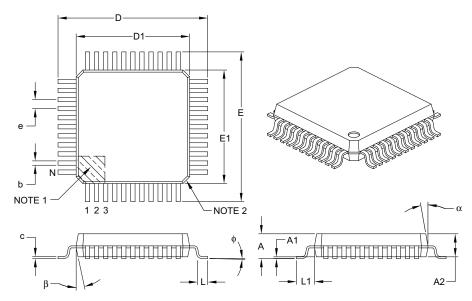

# 28-Lead Plastic Small Outline (OI) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

h

L1

φ

С

b

β

0.25

0.40

0°

0.18

0.31

5°

5°

1.40 REF

4. Dimensioning and tolerancing per ASME Y14.5M.

Chamfer (optional)

Foot Length

Foot Angle Top

Lead Thickness

Mold Draft Angle Top

Mold Draft Angle Bottom

Lead Width

Footprint

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-052B

0.75

1.27

8°

0.33

0.51

15°

15°

# 40-Lead Plastic Dual In-Line (PL) - 600 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |       | INCHES   |       |

|----------------------------|------------------|-------|----------|-------|

|                            |                  |       |          |       |

|                            | Dimension Limits | MIN   | NOM      | MAX   |

| Number of Pins             | N                |       | 40       | •     |

| Pitch                      | е                |       | .100 BSC |       |

| Top to Seating Plane       | A                | _     | _        | .250  |

| Molded Package Thickness   | A2               | .125  | _        | .195  |

| Base to Seating Plane      | A1               | .015  | _        | _     |

| Shoulder to Shoulder Width | E                | .590  | -        | .625  |

| Molded Package Width       | E1               | .485  | -        | .580  |

| Overall Length             | D                | 1.980 | -        | 2.095 |

| Tip to Seating Plane       | L                | .115  | -        | .200  |

| Lead Thickness             | С                | .008  | -        | .015  |

| Upper Lead Width           | b1               | .030  | -        | .070  |

| Lower Lead Width           | b                | .014  | -        | .023  |

| Overall Row Spacing §      | eB               | _     | _        | .700  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-016B

# 44-Lead Plastic Metric Quad Flatpack (KW) - 10x10x2 mm Body, 3.20 mm Footprint [MQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units         |      | MILLIMETERS | 3    |

|--------------------------|---------------|------|-------------|------|

| Dim                      | ension Limits | MIN  | NOM         | MAX  |

| Number of Leads          | N             |      | 44          |      |

| Lead Pitch               | е             |      | 0.80 BSC    |      |

| Overall Height           | А             | _    | _           | 2.45 |

| Molded Package Thickness | A2            | 1.80 | 2.00        | 2.20 |

| Standoff §               | A1            | 0.00 | _           | 0.25 |

| Foot Length              | L             | 0.73 | 0.88        | 1.03 |

| Footprint                | L1            |      | 1.60 REF    |      |

| Foot Angle               | ф             | 0°   | _           | 7°   |

| Overall Width            | E             |      | 13.20 BSC   |      |

| Overall Length           | D             |      | 13.20 BSC   |      |

| Molded Package Width     | E1            |      | 10.00 BSC   |      |

| Molded Package Length    | D1            |      | 10.00 BSC   |      |

| Lead Thickness           | С             | 0.11 | _           | 0.23 |

| Lead Width               | b             | 0.29 | _           | 0.45 |

| Mold Draft Angle Top     | α             | 5°   | _           | 16°  |

| Mold Draft Angle Bottom  | β             | 5°   | _           | 16°  |

# Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. § Significant Characteristic.

Microchip Technology Drawing C04-071B

NOTES:

# APPENDIX A: REVISION HISTORY

# **Revision C (September 2007)**

• Change status from active to end-of-life (EOL).

# Revision B (May 2002)

• Changes not documented.

# Revision A (April 2002)

• Original Release of this Document.

**NOTES:**

# PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.  Device Te | X /XX<br>emperature Package<br>Range                                                                                                                                                                         | Examples:  a) TC530CPJ: 0°C to +70°C, 28LD SPD b) TC530COI: 0°C to +70°C, 28LD SOIC |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|

| Device              | TC530: Precision Data Acquisition Subsystem TC534: Precision Data Acquisition Subsystem                                                                                                                      | a) TC534CPL: 0°C to +70°C, 40LD PDIF<br>b) TC534CKW: 0°C to +70°C, 44LD MQF         |  |

| Temperature Rang    | e C = 0°C to +70°C (Commercial)                                                                                                                                                                              |                                                                                     |  |

| Package             | KW = Plastic Metric Quad Flatpack (10x10x2 mm), 44-lead PJ = Skinny Plastic Dual In-Line (300 mil), 28-lead PL = Plastic Dual In-Line (600 mil), 40-lead OI = Plastic Small Outline (wide, 7.50 mm), 28-lead |                                                                                     |  |

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."