# High Speed CMOS 3.3V 16-Bit Bus Registered Transceiver with Bus Hold and Output Resistor

QS74LCX162H646

## FEATURES/BENEFITS

- 5V tolerant inputs and outputs

- · Industry standard pinouts

- $25\Omega$  series resistor for low switching noise

- Bus Hold feature holds last active state during 3-state operation

- 10μA I<sub>CCO</sub> quiescent power supply current

- · Hot insertable

- 2.0V–3.6V V<sub>CC</sub> supply operation

- ±12mA balanced output drive

- Meets or exceeds JEDEC Standard 36 specifications

- $t_{PD} = 5.3$ ns

- · Input hysteresis for noise immunity

- · Multiple power and ground pins for low noise

- Operating temperature range: -40°C to +85°C

- Latch-up performance exceeds 500mA

- ESD performance: Human body model > 2000V Machine model > 200V

- Packages available: 56-pin TSSOP 56-pin SSOP

## **DESCRIPTION**

The LCX162H646 is a 16-bit bus registered transceiver with three-state outputs that is ideal for driving address and data buses. The LCX162H646 is organized for transmission of data between A bus and B bus either directly or from the internal storage registers. The 3.3V LCX family features low power, low switching noise, and fast switching speeds for low power portable applications as well as high-end advanced workstation applications. 5V tolerant inputs and outputs allow this LCX product to be used in mixed 5V and 3.3V applications. The QS74LCX162H646 with integrated output resistor is ideally suited for low noise environments where reduced output overshoot and undershoot are critical requirements. Bus Hold circuitry on the data inputs retains the last active state during 3-state operation, eliminating the need for external pull-up resistors. Easy board layout is facilitated by the use of flow-through pinouts and byte enable controls provide architectural flexibility for systems designers. To accommodate hot-plug or live insertion applications, this product is designed not to load an active bus when  $V_{\text{CC}}$  is removed.

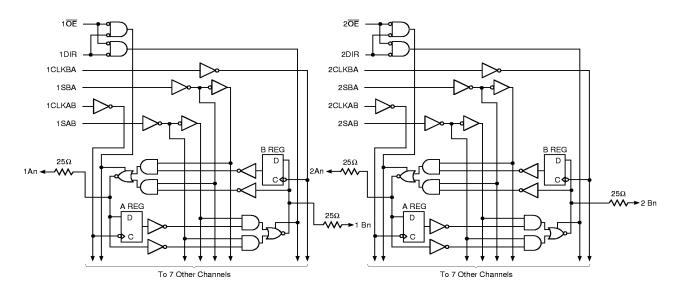

Figure 1. Functional Block Diagram

MDSL-00207-01 July 31, 1997 QUALITY SEMICONDUCTOR, INC.

1

Figure 2. Pin Configuration (All Pins Top View) SSOP, TSSOP

| 1DIR         | Ъ        | 1  | 56 | 10E                    |

|--------------|----------|----|----|------------------------|

| 1CLKAB       | <b>a</b> | 2  | 55 | TCLKBA                 |

| 1SAB         | д:       | 3  | 54 | 1SBA                   |

| GND          | d.       | 4  | 53 | GND                    |

| 1A1          | d:       | 5  | 52 | ] 1B1                  |

| 1A2          | d,       | 6  | 51 | ] 1B2                  |

| $V_{CC}$     | <b>d</b> | 7  | 50 | $\Box$ $\lor_{\rm cc}$ |

| 1A3          | Ц:       | 8  | 49 | ] 1B3                  |

| 1A4          | Ц:       | 9  | 48 | ] 1B4                  |

| 1A5          | 4        | 10 | 47 | ] 1B5                  |

| GND          | П        | 11 | 46 | GND                    |

| 1A6          | П        | 12 | 45 | ] 1B6                  |

| 1A7          | П        | 13 | 44 | ] 1B7                  |

| 1A8          | П        | 14 | 43 | ] 1B8                  |

| 2A1          | П        | 15 | 42 | ] 2B1                  |

| 2A2          | П        | 16 | 41 | ] 2B2                  |

| 2A3          | 4        | 17 | 40 | ] 2B3                  |

| GND          | 4        | 18 | 39 | GND                    |

| 2A4          | _        | 19 | 38 | ] 2B4                  |

| 2 <b>A</b> 5 | Ц:       | 20 | 37 | ] 2B5                  |

| 2A6          | Ц:       | 21 | 36 | 2B6                    |

| $V_{CC}$     | _        | 22 | 35 | □ v <sub>cc</sub>      |

| 2A7          | _        | 23 | 34 | 2B7                    |

| 2A8          | _        | 24 | 33 | 2B8                    |

| GND          | _        | 25 | 32 | GND                    |

| 2SAB         | п.       | 26 | 31 | 2SBA                   |

| 2CLKAB       | 7        | 27 | 30 |                        |

| 2DIR         | 4        | 28 | 29 | 20E                    |

**Table 1. Pin Description**

| Name                  | Description                                                            |

|-----------------------|------------------------------------------------------------------------|

| xAx                   | Data Register A Inputs<br>Data Register B Outputs<br>(Bus Hold Inputs) |

| xBx                   | Data Register B Inputs<br>Data Register A Outputs<br>(Bus Hold Inputs) |

| xCLKAB, xCLKBA        | Clock Inputs                                                           |

| xSAB, xSBA            | Output Source Select Inputs                                            |

| xDIR, x <del>OE</del> | Output Enable Inputs                                                   |

**Table 2. Function Table**

| Inputs            |      |          |        | Data | I/O(1) |        |        |                           |

|-------------------|------|----------|--------|------|--------|--------|--------|---------------------------|

| χ <mark>ΟΕ</mark> | xDIR | xCLKAB   | xCLKAB | xSAB | xSBA   | xAx    | хВх    | Operation or Function     |

| Н                 | Х    | H or L   | H or L | х    | х      | Input  | Input  | Isolation                 |

| Н                 | Х    | <u> </u> | T      | Х    | X      |        |        | Store A and B Data        |

| L                 | L    | X        | Х      | Х    | L      | Output | Input  | Real Time B Data to A Bus |

| L                 | L    | Х        | H or L | Х    | Н      |        |        | Stored B Data to A Bus    |

| L                 | Н    | X        | Х      | L    | X      | Input  | Output | Real Time A Data to B Bus |

| L                 | Η    | H or L   | Х      | Н    | X      | -      | •      | Stored A Data to B Bus    |

- 1. The data output functions may be enabled or disabled by various signals at the xOE or xDIR inputs. Data input functions are always enabled, i.e. data at the bus pins will be stored on every LOW-to-HIGH transition on the clock

- 2. H = HIGH Voltage Level L = LOW Voltage Level

- X = Don't Care

↑ = LOW-to-HIGH Transition

Table 3. Capacitance

| Symbol           | Pins                             | Тур | Unit | Conditions                                              |

|------------------|----------------------------------|-----|------|---------------------------------------------------------|

| $C_{IN}$         | Input Capacitance                | 7.0 | pF   | $V_{IN} = 0V$ , $V_{OUT} = 0V$ , $f = 1MHz$             |

| C <sub>I/O</sub> | I/O Capacitance                  | 8.0 | pF   | $V_{IN} = 0V$ , $V_{OUT} = 0V$ , $f = 1MHz$             |

| C <sub>PD</sub>  | Power Dissipation<br>Capacitance | 20  | pF   | $V_{CC} = 3.3V$ , $V_{IN} = 0$ or $V_{CC}$<br>f = 10MHz |

**Note:** Capacitance is characterized but not production tested.

**Table 4. Absolute Maximum Ratings**

| Supply Voltage to Ground                                          | 0.5V to +7.0V              |

|-------------------------------------------------------------------|----------------------------|

| DC Output Voltage V <sub>OUT</sub>                                |                            |

| Outputs HIGH-Z                                                    | 0.5V to +7.0V              |

| Outputs Active                                                    | $-0.5V$ to $V_{CC} + 0.5V$ |

| DC Input Voltage V <sub>IN</sub>                                  |                            |

| DC Input Diode Current with V <sub>IN</sub> < 0                   |                            |

| DC Output Diode Current                                           |                            |

| V <sub>O</sub> < 0                                                | –50mA                      |

| V <sub>O</sub> > V <sub>CC</sub>                                  | +50mA                      |

| DC Output Source/Sink Current (I <sub>OH</sub> /I <sub>OL</sub> ) | ±50mA                      |

| DC Supply Current per Supply Pin                                  | ±100mA                     |

| DC Ground Current per Ground Pin                                  | ±100mA                     |

| T <sub>STG</sub> Storage Temperature                              | –65° to +150°C             |

**Note:** Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to this device resulting in functional or reliability type failures.

**Table 5. Recommended Operating Conditions**

| Symbol                           | Parameter            |                        | Min             | Max          | Unit |

|----------------------------------|----------------------|------------------------|-----------------|--------------|------|

| V <sub>CC</sub>                  | Supply Voltage, Op   | perating               | 2.0             | 3.6          | V    |

|                                  | Supply Voltage, Da   | ata Retention Only     | 1.5             | 3.6          |      |

| $V_{IN}$                         | Input Voltage        |                        | 0               | 5.5          | V    |

| V <sub>out</sub>                 | Output Voltage in A  | Active State           | 0               | $V_{\rm cc}$ | ٧    |

|                                  | Output Voltage in "  | OFF" State             | 0               | 5.5          |      |

| I <sub>OH</sub> /I <sub>OL</sub> | Output Current       | $V_{CC} = 3.0 - 3.6 V$ |                 | ±12          | mA   |

|                                  | $V_{\rm CC} = 2.7V$  |                        | _               | ±6           |      |

| Δt/Δν                            | Input Transition Sle | ew Rate                |                 | 10           | ns/V |

| T <sub>A</sub>                   | Operating Free Air   | Temperature            | <del>-4</del> 0 | +85          | °C   |

MDSL-00207-01 July 31, 1997 QUALITY SEMICONDUCTOR, INC.

## **Table 6. DC Electrical Characteristics Over Operating Range**

Industrial Temperature Range,  $T_A = -40$ °C to +85°C

| Symbol           | Parameter                           | Test Condition                                                                                       | ons                                             | Min                                | Typ <sup>(1)</sup> | Max                | Unit     |

|------------------|-------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------|--------------------|--------------------|----------|

| $V_{IH}$         | Input HIGH Voltage                  | Logic HIGH fo                                                                                        | r All Inputs                                    | 2.0                                |                    | _                  | <b>\</b> |

| V <sub>IL</sub>  | Input LOW Voltage                   | Logic LOW for                                                                                        | r All Inputs                                    | _                                  | _                  | 0.8                | ٧        |

| V <sub>OH</sub>  | Output HIGH Voltage                 | $V_{CC} = 2.7V, I_{C}$<br>$V_{CC} = 3.0V, I_{C}$                                                     | <sub>H</sub> = -12mA                            | V <sub>CC</sub> -0.2<br>2.4<br>2.2 | _                  | _                  | <b>V</b> |

| V <sub>OL</sub>  | Output Low Voltage                  | $V_{CC} = 3.0V, I_{O}$<br>$V_{CC} = 2.7V, I_{O}$<br>$V_{CC} = 3.0V, I_{O}$<br>$V_{CC} = 3.0V, I_{O}$ | <sub>L</sub> = 100μA<br><sub>L</sub> = 12mA     | —<br>—<br>—                        |                    | 0.2<br>0.55<br>0.8 | V        |

| R <sub>OUT</sub> | Output Resistance                   | $V_{\rm CC} = 3.0 \text{V}, I_{\rm O}$                                                               | <sub>L</sub> = 12mA                             | _                                  | 28                 | _                  | Ω        |

| $\Delta V_{T}$   | Input Hysteresis(2)                 | V <sub>TLH</sub> - V <sub>THL</sub> for All Inputs                                                   |                                                 | _                                  | 150                | _                  | mV       |

| I <sub>I</sub>   | Input Leakage Current               | $V_1 = 0V$ , $V_1 = 5$                                                                               | 5.5V                                            | _                                  | _                  | ±1.0               | μА       |

| I <sub>BH</sub>  | Input Current<br>Inputs High or Low | $V_{CC} = 3.6V, V_{CC}$                                                                              | $_{\rm IN}$ = 0V or $V_{\rm IN}$ = $V_{\rm CC}$ | _                                  |                    | 50                 | μА       |

|                  | Bus Hold Inputs(2,3)                | $V_{CC} = 3.6V, 0.$                                                                                  | $8V < V_{IN} < 2.0V$                            | _                                  |                    | 500(4)             | μΑ       |

| I <sub>BHH</sub> | Bus Hold Sustaining<br>Current      | $V_{\rm CC} = 3.0V$                                                                                  | V <sub>IN</sub> = 2.0V                          | <del>-</del> 75                    | _                  | _                  | μΑ       |

| I <sub>BHL</sub> | Bus Hold Inputs                     |                                                                                                      | $V_{IN} = 0.8V$                                 | +75                                | _                  |                    | μΑ       |

| l <sub>oz</sub>  | High-Z I/O Leakage                  | $V_O = 0V, V_O = V_I = V_{IH} \text{ or } V_{IL}$                                                    | 5.5V                                            | _                                  |                    | ±1.0               | μА       |

| I <sub>os</sub>  | Short Circuit Current(2,5)          | $V_{CC} = 3.6V, V_O = GND$                                                                           |                                                 | -60                                | _                  | -200               | mA       |

| I <sub>OR</sub>  | Current Drive                       | $V_{CC} = 3.6V, V_{OUT} = 2.0V$                                                                      |                                                 | 40                                 | _                  | _                  | mA       |

| I <sub>OFF</sub> | Power Off Leakage                   | $V_{CC} = 0V, V_1 o$                                                                                 | $V_{CC} = 0V$ , $V_I$ or $V_O = 5.5V$           |                                    | _                  | 10                 | μА       |

| V <sub>IK</sub>  | Input Clamp Voltage                 | $V_{CC} = 2.7V, I_{IN}$                                                                              | <sub>I</sub> = -18mA                            |                                    | -0.7               | -1.2               | V        |

Notes: 1. Typical values indicate  $V_{CC} = 3.3V$ , and  $T_A = 25^{\circ}C$ . 2. These parameters are guaranteed by characterization but not production tested.

<sup>3.</sup> Pins with Bus Hold are identified in the Pin Description.

<sup>4.</sup> An external driver must provide at least  $|I_{BH}|$  during transition to guarantee that the Bus Hold input will change states.

<sup>5.</sup> Not more than one output should be tested at one time. Duration of test should not exceed one second.

**Table 7. Power Supply Characteristics**

| Symbol           | Parameter                                       | Test Conditions(1)                                                                                                                                       |                                           | Typ(2) | Max    | Unit       |

|------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------|--------|------------|

| I <sub>cc</sub>  | Quiescent Power<br>Supply Current               | $V_{CC} = 3.6V$ , Freq = 0<br>$V_{IN} = GND \text{ or } V_{CC}$                                                                                          |                                           | 0.1    | 10     | μΑ         |

| $\Delta I_{CC}$  | Supply Current per                              | $V_{CC} = 3.6V$                                                                                                                                          | Control Inputs                            | 2.0    | 30     | μА         |

|                  | Input @ TTL HIGH                                | $V_{IN} = V_{CC} - 0.6V^{(3)}$                                                                                                                           | Bus Hold Inputs                           |        | 500    | μA         |

| I <sub>CCD</sub> | Supply Current per Input per MHz <sup>(4)</sup> | V <sub>CC</sub> = 3.6V, Outputs Open<br>One Bit Toggling<br>@ 50% Duty Cycle<br>xDIR = xOE = GND                                                         | $V_{IN} = V_{CC}$ $V_{IN} = GND$          | 65     | 100    | μA/<br>MHZ |

| lc               | Total Power<br>Supply Current <sup>(6)</sup>    | V <sub>CC</sub> = 3.6V, Outputs Open<br>One Bit Toggling<br>@ 50% Duty Cycle<br>f = 5MHz,<br>f <sub>CP</sub> = 10MHz (xCLKBA)<br>xDIR = xOE = GND,       | $V_{IN} = V_{CC}$ -0.6V<br>$V_{IN} = GND$ | 0.5(5) | 0.8(5) | mA         |

|                  |                                                 | V <sub>CC</sub> = 3.6V, Outputs Open<br>Sixteen Bits Toggling<br>@ 50% Duty Cycle<br>f = 2.5MHz,<br>f <sub>CP</sub> = 10MHz (xCLKBA)<br>xDIR = xOE = GND | $V_{IN} = V_{CC}$ -0.6V<br>$V_{IN} = GND$ | 2.0(5) | 3.3(5) | mA         |

- 1. For conditions shown as Min. or Max., use the appropriate values specified under Recommended Operating Conditions for applicable device type.

- 2. Typical values are at  $V_{CC} = 3.3V$ , +25°C ambient. 3. Per TTL driven input. All Other Inputs at  $V_{CC}$  or GND.

- 4. This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.

- 5. Values for these conditions are examples of the lcc formula. These limits are guaranteed by design but not tested.

6.  $I_C = I_{QUIESCENT} + I_{INPUTS} + I_{DYNAMIC}$ .  $I_C = I_{CCQ} + \Delta I_{CC} D_H N_T + I_{CCD} f N_O$ .  $I_{CCQ} = Quiescent Current (<math>I_{CCL}$ ,  $I_{CCH}$ , and  $I_{CCZ}$ ).  $\Delta I_{CC} = Power Supply Current for a TTL-High Input (<math>V_{IN} = V_{CC} - 0.6V$ ).

D<sub>H</sub> = Duty Cycle for TTL High Inputs.

$N_T$  = Number of TTL High Inputs.

I<sub>CCD</sub> = Dynamic Current Caused by an Input Transition Pair (HLH or LHL).

f = Average Switching Frequency per Output.

N<sub>O</sub> = Number of Outputs Switching.

Table 8. Dynamic Switching Characteristics(1)

| Symbol           | Parameter                                   | Conditions                               | V <sub>cc</sub> | T <sub>A</sub> = 25°C | Units    |

|------------------|---------------------------------------------|------------------------------------------|-----------------|-----------------------|----------|

|                  |                                             |                                          | (V)             | Typical               |          |

| $V_{OLP}$        | Quiet Output Dynamic Peak V <sub>OL</sub>   | $C_L = 30pF, V_{IH} = 3.3V, V_{IL} = 0V$ | 3.3             | 0.8                   | ٧        |

| V <sub>OLV</sub> | Quiet Output Dynamic Valley V <sub>OL</sub> | $C_L = 30pF, V_{IH} = 3.3V, V_{IL} = 0V$ | 3.3             | 0.8                   | <b>V</b> |

1. Characterized but not production tested.

MDSL-00207-01 July 31, 1997

QUALITY SEMICONDUCTOR, INC.

5

## **Table 9. Switching Characteristics Over Operating Range**

Industrial Temperature Range,  $T_A = -40^{\circ}\text{C}$  to +85°C.  $C_{LOAD} = 30\text{pF}, \ R_{LOAD} = 500\Omega$  unless otherwise noted.

|                                      |                                                          |                       | LCX16      | 2H646             |     |      |

|--------------------------------------|----------------------------------------------------------|-----------------------|------------|-------------------|-----|------|

|                                      |                                                          | V <sub>CC</sub> = 3.3 | $3\pm0.3V$ | V <sub>cc</sub> = |     |      |

| Symbol                               | Description <sup>(2)</sup>                               | Min                   | Max        | Min               | Max | Unit |

| $f_{MAX}$                            | Clock Pulse Frequency(2)                                 | 170                   | _          |                   |     | MHz  |

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay<br>Bus to Bus                          | 2.0                   | 5.3        | 2.0               | 6.3 | ns   |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Output Enable Time xDIR or xOE toBus                     | 2.0                   | 7.5        | 2.0               | 8.5 | ns   |

| t <sub>PHZ</sub><br>t <sub>PLZ</sub> | Output Disable Time <sup>(2)</sup><br>xDIR or xOE to Bus | 2.0                   | 6.0        | 2.0               | 7.0 | ns   |

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay<br>Clock to Bus                        | 2.0                   | 6.3        | 2.0               | 7.3 | ns   |

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay<br>xSAB or xSBA to Bus                 | 2.0                   | 6.3        | 2.0               | 7.3 | ns   |

| t <sub>su</sub>                      | Setup Time HIGH or LOW<br>Bus to Clock                   | 2.5                   | _          | 2.5               |     | ns   |

| t <sub>H</sub>                       | Hold Time HIGH or LOW<br>Bus to Clock                    | 1.5                   | _          | 1.5               |     | ns   |

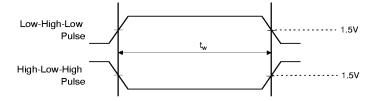

| t <sub>W</sub>                       | Clock Pulse Width <sup>(2)</sup><br>LOW or HIGH          | 3.0                   | _          | 3.0               |     | ns   |

| t <sub>SK(O)</sub>                   | Output Skew <sup>(3)</sup>                               | _                     | 0.5        | _                 | _   | ns   |

### Notes:

- 1. Minimums guaranteed but not tested on propagation delays. See Test Circuit and Waveforms.

- 2. Guaranteed by characterization

- 3. Skew between any two outputs of the same package switching in the same direction. This parameter is guaranteed by characterization but not production tested.

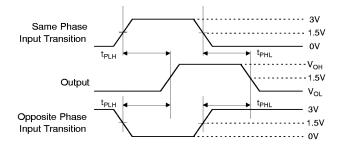

## **TEST CIRCUIT AND WAVEFORMS**

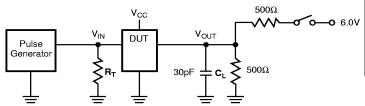

Figure 3. Test Circuit

## **SWITCH POSITION**

| Test             | Switch |

|------------------|--------|

| Open Drain       |        |

| Disable LOW      | 6V     |

| Enable LOW       |        |

| Disable HIGH     | GND    |

| Enable HIGH      |        |

| All Other Inputs | Open   |

**DEFINITIONS:**

$\mathbf{C_L} = \text{Load}$  capacitance: includes jig and probe capacitance.  $\mathbf{R_T} = \text{Termination resistance}$ : should be equal to Zout of the Pulse generator.

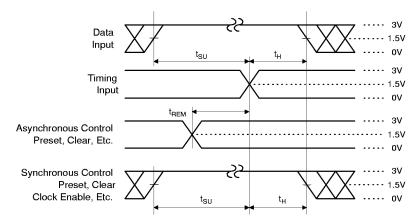

Figure 4. Setup, Hold, and Release Timing

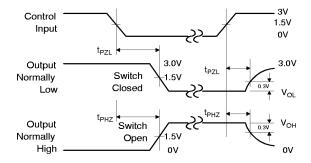

Figure 5. Enable and Disable Timing

## Notes:

- Input Control Enable = LOW and input Control Disable = HIGH.

- 2. Pulse Generator for All Pulses: Rate  $\leq$  1.0MHz;  $Z_{OUT} \leq 50\Omega$ ;  $t_F, t_R \leq$  2.5ns.

MDSL-00207-01 July 31, 1997 QUALITY SEMICONDUCTOR, INC.

7

Figure 6. Pulse Width

Figure 7. Propagation Delay

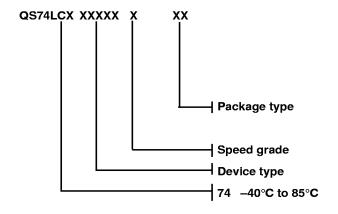

## **ORDERING INFORMATION**

Device Type:

162H646

Speed Grades:

Blank - Standard

Package Type:

PV – SSOP, 300 mil PA – TSSOP, 240 mil