## **LAN91C93I**

# Non-PCI Single-Chip Full Duplex Ethernet Controller

## **Datasheet**

## **Product Features**.

- Non-PCI Single-Chip Ethernet Controller

- Fully Supports Full Duplex Switched Ethernet

- Supports Enhanced Transmit Queue Management

- 6K Bytes of On-Chip RAM

- Supports IEEE 802.3 (ANSI 8802-3) Ethernet Standards

- Automatic Detection of TX/RX Polarity Reversal

- Simultasking Early Transmit and Early Receive Functions

- Enhanced Early Transmit Function

- Receive Counter for Enhanced Early Receive

- Hardware Memory Management Unit

- Optional Configuration via Serial EEPROM Interface (Jumperless)

- Supports single 5V or 3.3V VCC Design

- Supports Mixed Voltage External PHY Designs

- Supports Industrial Temp -40°C to 85°C

- Low Power CMOS Design

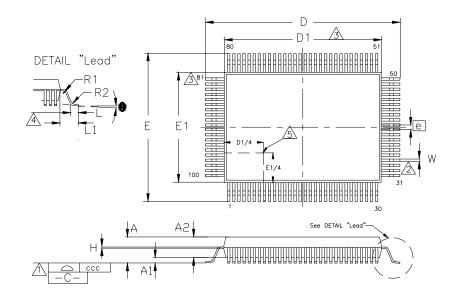

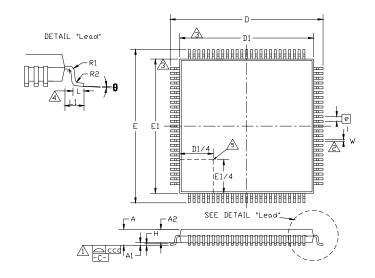

- 100 Pin QFP and TQFP (1.0mm body Thickness) packages; green, lead-free packages also available

- Direct Interface to local bus, with No Wait States

- 16 Bit Data and Control Paths

- Fast Access Time

- Pipelined Data Path

- Handles Block Word Transfers for any Alignment

- High Performance Chained ("Back-to-Back")

Transmit and Receive

- Dynamic Memory Allocation Between Transmit and Receive

- Flat Memory Structure for Low CPU Overhead

- Buffered Architecture, Insensitive to Bus Latencies (No Overruns/Underruns)

- Supports Boot PROM for Diskless local bus Applications

## **Network Interface**

- Integrated 10BASE-T Transceiver Functions:

- Driver and Receiver

- Link Integrity Test

- Receive Polarity Detection and Correction

- Integrated AUI Interface

- 10 Mb/s Manchester Encoding/Decoding and Clock Recovery

- Automatic Retransmission, Bad Packet Rejection, and Transmit Padding

- External and Internal Loopback Modes

- Four Direct Driven LEDs for Status/ Diagnostics

## **Software Drivers**

- LAN9000 Drivers for Major Network Operating Systems Utilizing local bus Interface

- Software Drivers Utilize Full Capability of 32 Bit Microprocessor

## ORDERING INFORMATION

## Order Number(s):

LAN91C93I-MC for 100 pin QFP package

LAN91C93I-ME for 100 pin TQFP package

LAN91C93I-MS for 100 pin QFP package (green, lead-free)

LAN91C93I-MU for 100 pin TQFP package (green, lead-free)

80 Arkay Drive Hauppauge, NY 11788 (631) 435-6000 FAX (631) 273-3123

Copyright © SMSC 2004. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE.

IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Rev. 11/17/2004 Page 2 SMSC DS – LAN91C93I

## **TABLE OF CONTENTS**

| Chapter 1        | General Description                                    |    |  |

|------------------|--------------------------------------------------------|----|--|

| Chapter 2        | Overview                                               | 7  |  |

| Chapter 3        | Pin Configurations                                     | 9  |  |

|                  | al Bus Pin Requirements                                | 12 |  |

| Chapter 4        | Description of Pin Functions                           | 12 |  |

|                  | er Symbols                                             |    |  |

| 4.1 Dulle        | •                                                      |    |  |

| Chapter 5        |                                                        |    |  |

|                  | er Memory                                              |    |  |

|                  | rupt Structure                                         |    |  |

|                  | et Logic                                               |    |  |

| 5.4 Power        | er Down Logic States                                   | 25 |  |

| Chapter 6        | Packet Format in Buffer Memory for Ethernet            | 26 |  |

| Chapter 7        |                                                        |    |  |

|                  | Space Access                                           |    |  |

|                  | Space Registers Description                            |    |  |

| 7.2.1            | Bank Select Register                                   | 30 |  |

| Chapter 8        | Theory of Operation                                    | 53 |  |

|                  | Duplex Support                                         |    |  |

|                  | cal Flow of Events for Transmit (Auto Release = 0)     |    |  |

| 8.3 Typic        | cal Flow of Events for Transmit (Auto Release = 1)     | 56 |  |

| 8.4 Typic        | cal Flow of Events for Receive                         | 57 |  |

| 8.5 Mem          | nory Partitioning                                      | 63 |  |

| Chapter 9        | Functional Description of the Blocks                   | 67 |  |

|                  | nory Management Unit                                   |    |  |

|                  | ter                                                    |    |  |

|                  | Interface                                              |    |  |

|                  | State Policy                                           |    |  |

|                  | tration Considerations                                 |    |  |

| 9.6 DMA          | A Block                                                | 69 |  |

| 9.7 Pack         | ket Number FIFOs                                       | 70 |  |

|                  | MA Bock                                                |    |  |

|                  | vork Interface                                         |    |  |

|                  | base-T                                                 |    |  |

|                  | ال                                                     |    |  |

|                  | nysical Interface                                      |    |  |

|                  | ansmit Functions                                       |    |  |

| 9.13.1<br>9.13.2 | Manchester Encoding Transmit Drivers                   |    |  |

| 9.13.3           | Jabber Function                                        |    |  |

| 9.13.4           | SQE Function                                           | _  |  |

| 9.14 Re          | eceive Functions                                       | 75 |  |

| 9.14.1           | Receive Drivers                                        |    |  |

| 9.14.2           | Manchester Decoder and Clock Recovery                  |    |  |

| 9.14.3           | Squelch Function                                       |    |  |

| 9.14.4<br>9.14.5 | Reverse Polarity Function Collision Detection Function |    |  |

| 9.14.6           | Link Integrity                                         |    |  |

|                  | — · · · · · · · · · · · · · · · · · · ·                |    |  |

| Chapte    | r 10         | Board Setup Information                                                                   | 77  |

|-----------|--------------|-------------------------------------------------------------------------------------------|-----|

|           |              | stic LEDs                                                                                 |     |

| 10.2      | Bus Clo      | ock Considerations                                                                        | 78  |

| Cl4       | 11           | O                                                                                         | 00  |

| Chapte    |              | Operational Description                                                                   |     |

|           |              | um Guaranteed Ratings*                                                                    |     |

| 11.2      | DC Ele       | ctrical Characteristics                                                                   |     |

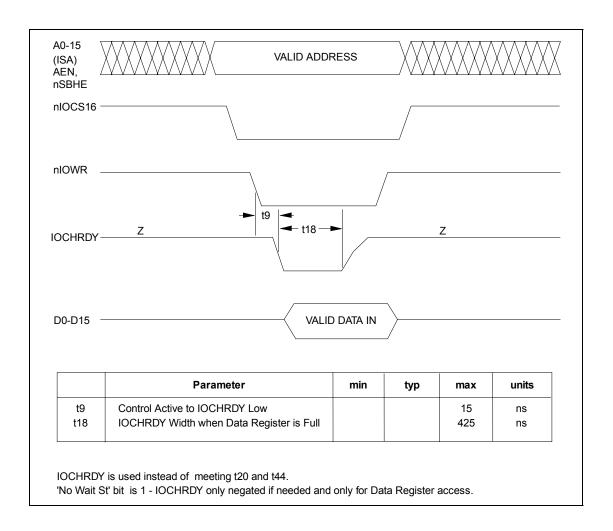

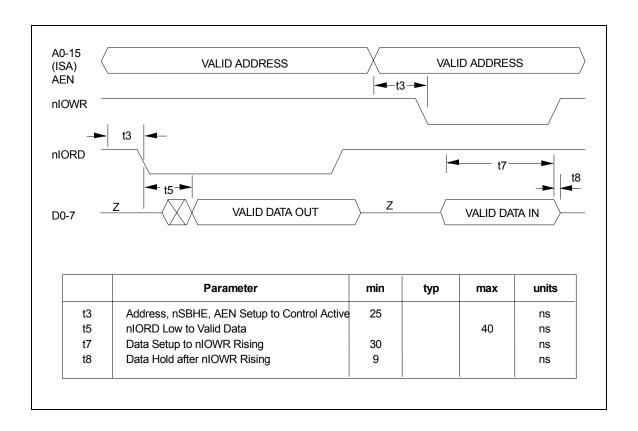

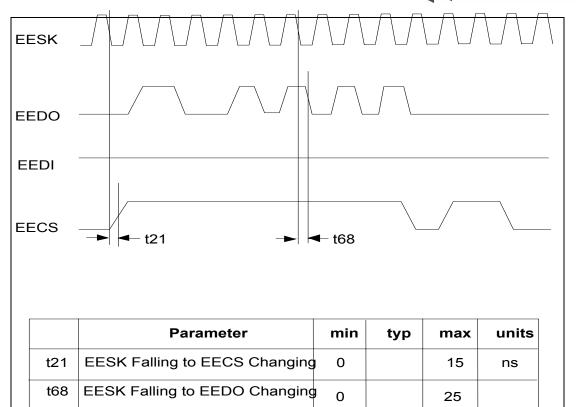

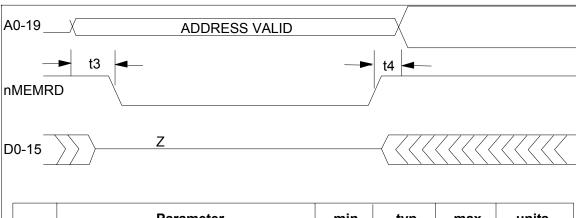

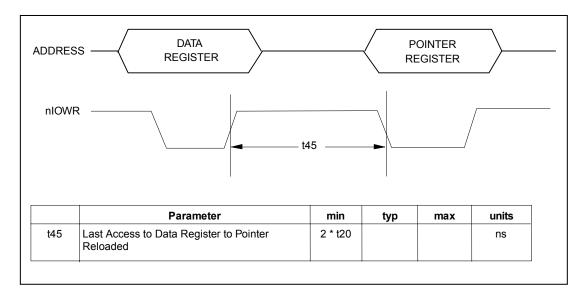

| Chapte    | r 12         | Timing Diagrams                                                                           | 85  |

| Chapte    | r 13         | LAN91C93I Revisions                                                                       | 102 |

| •         |              |                                                                                           |     |

|           |              |                                                                                           |     |

|           |              | LIGT OF FIGURES                                                                           |     |

|           |              | LIST OF FIGURES                                                                           |     |

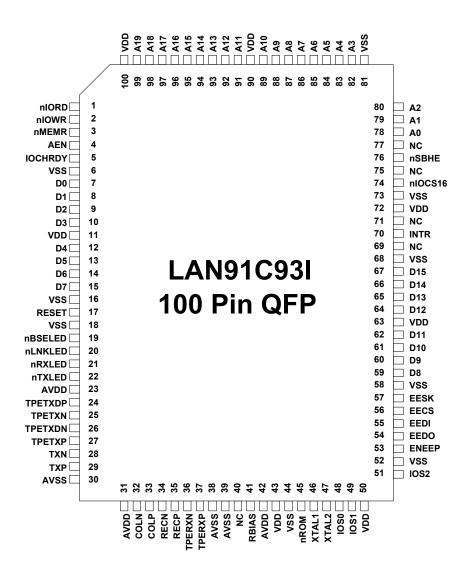

| Figure 3. | .1 – Pin (   | Configuration of LAN91C93I QFP                                                            | 9   |

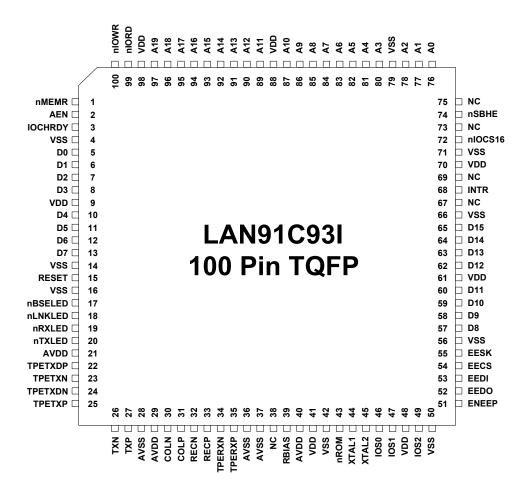

| Figure 3. | .2 – Pin (   | Configuration of LAN91C93I TQFP                                                           | 10  |

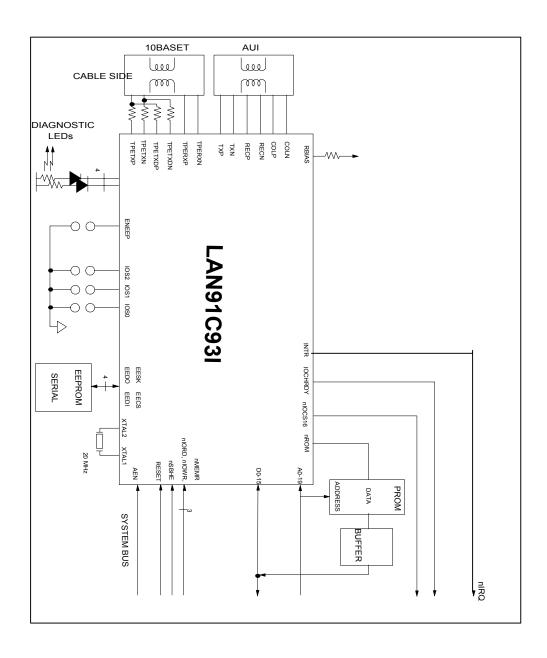

| Figure 3. | .3 – Syst    | em Diagram for Local Bus with Boot Prom                                                   | 11  |

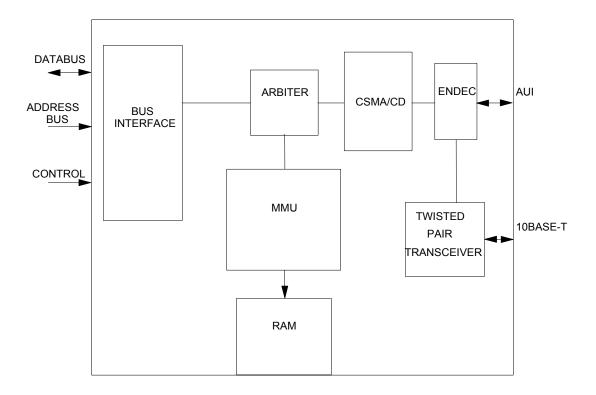

| Figure 4. | .1 - LAN9    | 91C93I Internal Block Diagram                                                             | 16  |

|           |              | ping and Paging vs. Receive and Transmit Area                                             |     |

|           |              | smit Queues and Mapping                                                                   |     |

|           |              | eive Queues and Mapping                                                                   |     |

| Figure 5. | 4 – LAN      | 91C93I Internal Block Diagram with Data Pathcal Address Generation and Relevant Registers | 22  |

|           |              | Packet Format                                                                             |     |

|           |              | 91C93I Registers                                                                          |     |

|           |              | rupt Structure                                                                            |     |

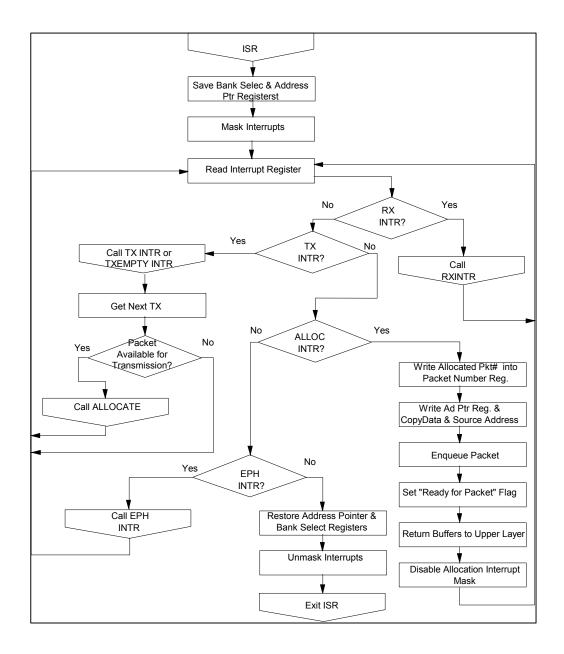

| Figure 8. | .1 - Interi  | rupt Service Routine                                                                      | 58  |

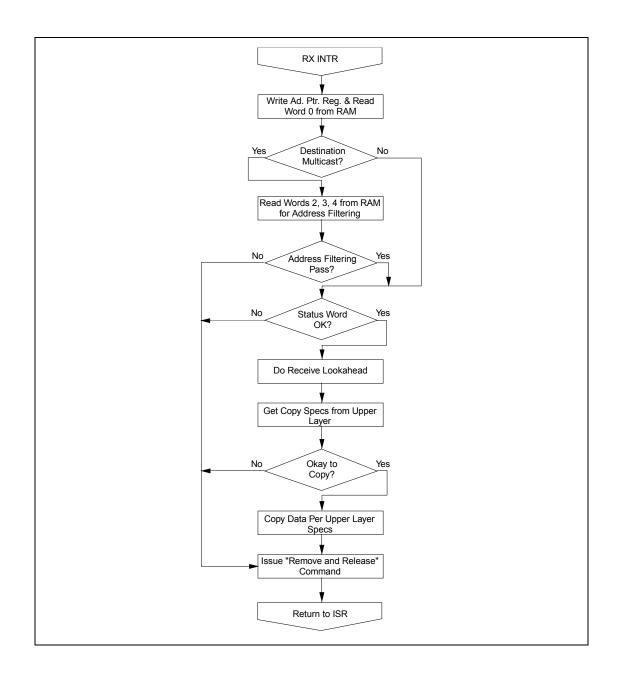

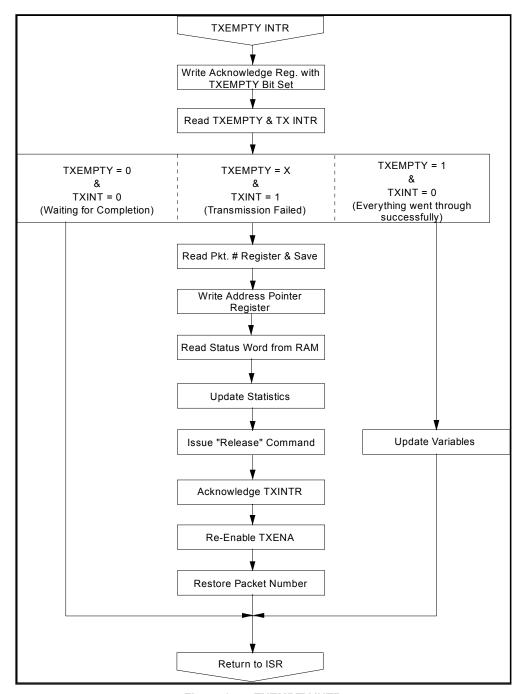

|           |              | NTR                                                                                       |     |

|           |              | NTR                                                                                       |     |

|           |              | MPTY INTR                                                                                 |     |

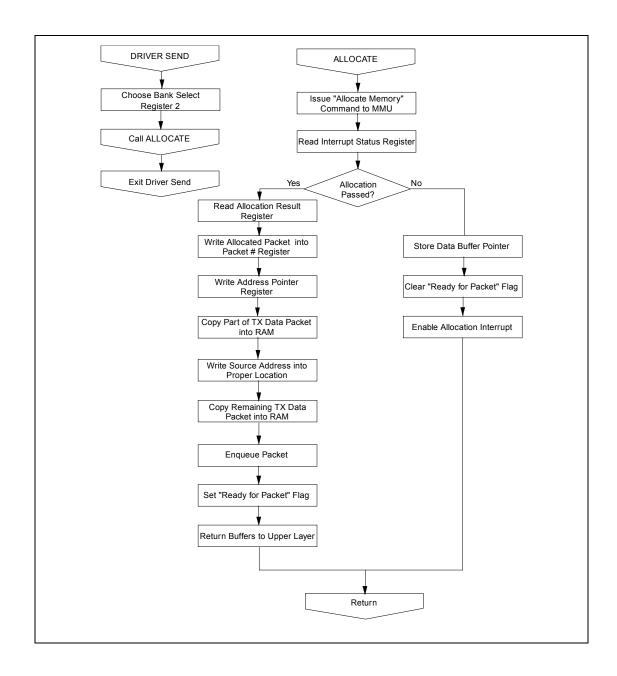

|           |              | er Send and Allocate Routines                                                             |     |

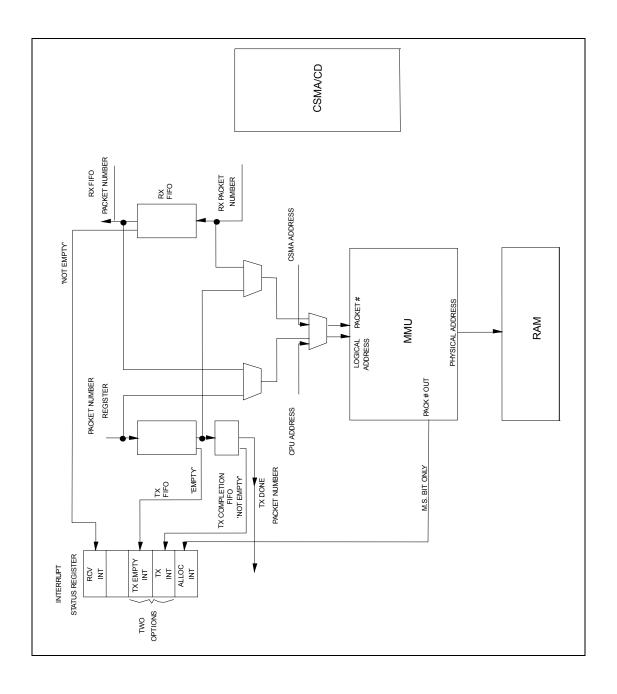

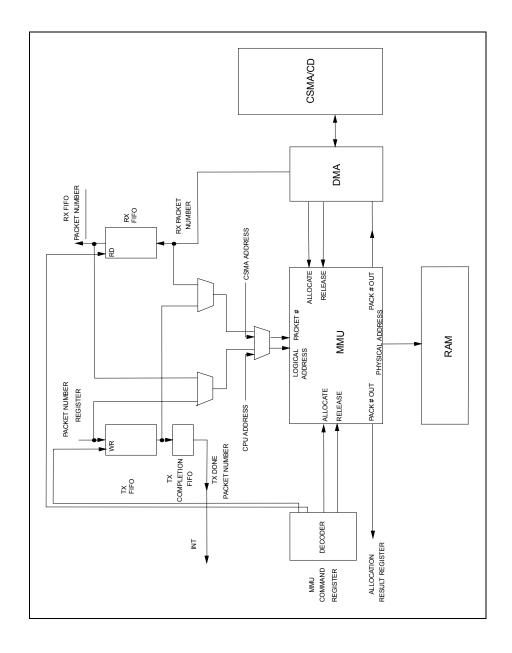

|           |              | rupt Generation for Transmit; Receive, MMU                                                |     |

|           |              | X 16 Serial EEPROM Map                                                                    |     |

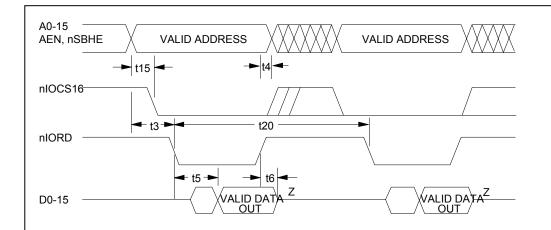

|           |              | cal Bus Consecutive Read Cycles                                                           |     |

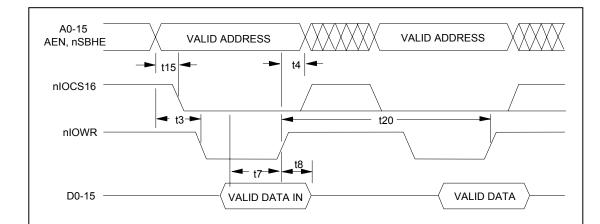

|           |              | cal Bus Consecutive Write Cycles                                                          |     |

| Figure 12 | 2.3 - Loc    | cal Bus Consecutive Read and Write Cycles                                                 | 87  |

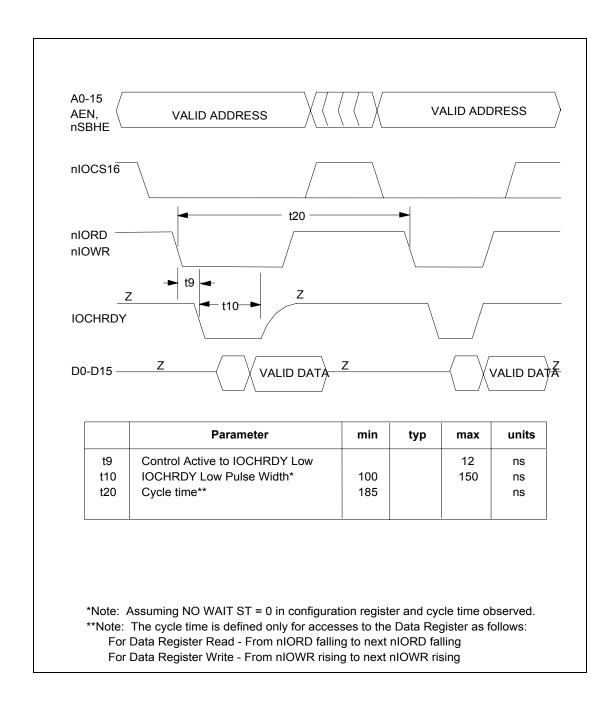

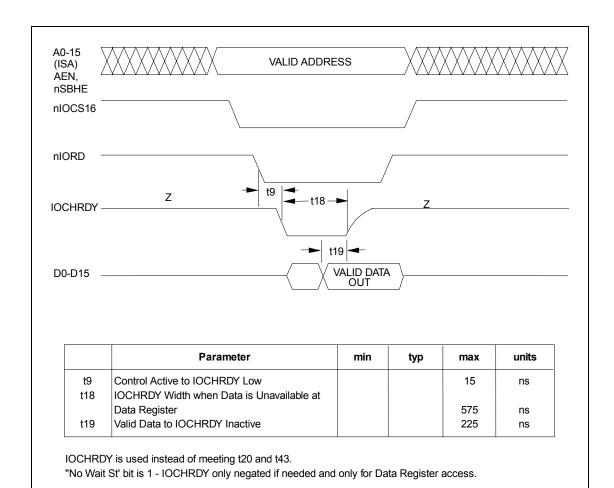

|           |              | ta Register Special Read Access                                                           |     |

|           |              | ta Register Special Write Access                                                          |     |

|           |              | it Mode Register Cycles                                                                   |     |

|           |              | PROM Read                                                                                 |     |

| •         |              | ternal ROM Read Access                                                                    |     |

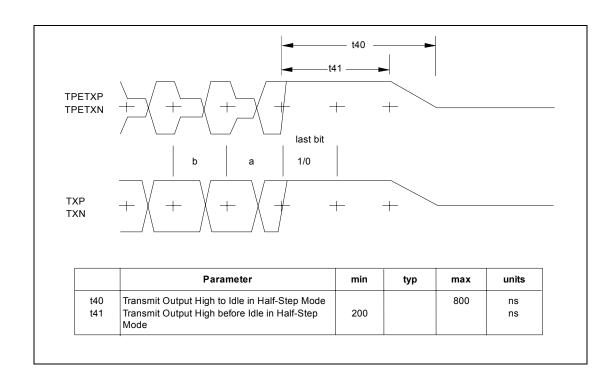

|           |              | PROM Writeifferential Output Signal Timing (10BASE-T and AUI)                             |     |

|           |              | eceive Timing – Start of Frame (AUI and 10BASE-T)                                         |     |

|           |              | eceive Timing – End of Frame (AUI and 10BASE-T)                                           |     |

|           |              | ransmit Timing – End of Frame (AUI and 10BASE-T)                                          |     |

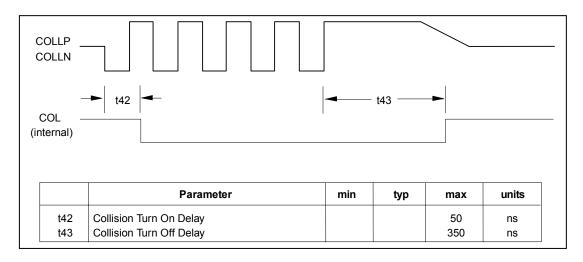

|           |              | ollision and Timing (AUI)                                                                 |     |

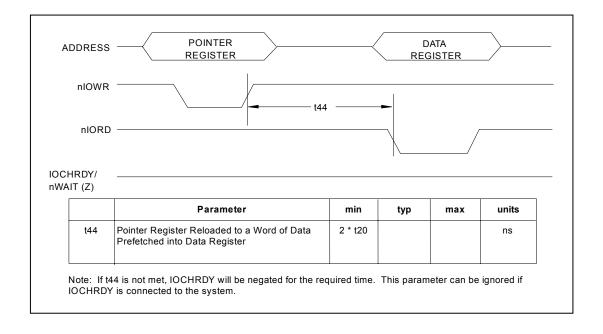

|           |              | emory Read Timing                                                                         |     |

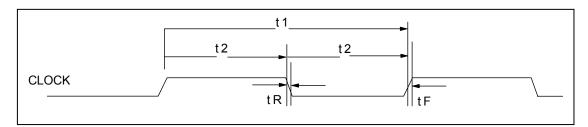

|           |              | put Clock Timing                                                                          |     |

|           |              | emory Write Timing                                                                        |     |

|           |              | 00 PIN QFP Package                                                                        |     |

| rigule 12 | ۱۱ – ۱۲ د. ا | 00 PIN TQFP Package                                                                       | 101 |

|           |              | LIST OF TABLES                                                                            |     |

| Table 5   | 1 _ Ι ΔΝΙΩ   | 1C93I Address Space                                                                       | 24  |

|           |              | ransactions in Local Bus Mode                                                             |     |

| 0.2       |              |                                                                                           |     |

|           |              |                                                                                           |     |

| Table 5.3 – Interrupt Merging                                                                    | 24 |

|--------------------------------------------------------------------------------------------------|----|

| Table 5.4 – Reset Logic                                                                          |    |

| Table 5.5 - Local Bus Mode Defined States (Refer To Table 5.6 For Next States To Wake-Up Events) | 2  |

| Table 5.6 – Local Bus Mode                                                                       |    |

| Table 7.1- Transmit Loon                                                                         | 3  |

# **Chapter 1** General Description

The LAN91C93I is a VLSI, local bus interface Ethernet Controller. LAN91C93I integrates all MAC and physical layer functions, as well as the packet RAM, needed to implement a high performance 10BASE-T (twisted pair) node. For 10BASE5 (thick coax), 10BASE2 (thin coax), and 10BASE-F (fiber) implementations, the LAN91C93I interfaces to external transceivers via the provided AUI port. Only one additional IC is required for most applications. The LAN91C93I comes with Full Duplex Switched Ethernet (FDSWE) support allowing the controller to provide much higher throughput. 6K bytes of RAM is provided to support enhanced throughput and compensate for any increased system service latencies. The controller implements multiple advanced powerdown modes to conserve power and operate more efficiently. The LAN91C93I can directly interface with the local bus and deliver no-wait-state operation. For local bus interfaces, the LAN91C93I occupies 16 I/O locations and no memory space.

The same I/O space is used for local bus operations. Its shared memory is sequentially accessed with 40ns access times to any of its registers, including its packet memory. DMA services are not used by the LAN91C93I, virtually decoupling network traffic from local or system bus utilization. For packet memory management, the LAN91C93I integrates a unique hardware Memory Management Unit (MMU) with enhanced performance and decreased software overhead when compared to ring buffer and linked list architectures. The LAN91C93I is portable to different CPU and bus platforms due to its flexible bus interface, flat memory structure (no pointers), and its loosely coupled buffered architecture (not sensitive to latency).

The LAN91C93I is available in 100-pin QFP and TQFP (1.0 mm body thickness) packages; green, lead-free packages are also available. The low profile TQFP is ideal for mobile applications such as PC Card LAN adapters. The LAN91C93I operates with a single power supply voltage of 5V or 3.3V.

## **Chapter 2** Overview

A unique architecture allows the LAN91C93I to combine high performance, flexibility, high integration and simple software interface.

The LAN91C93I incorporates the LAN91C92 functionality for local bus environments. The LAN91C93I consists of the same logical I/O register structure in local bus modes. The MMU (Memory Management Unit) architecture used by the LAN91C93I combines the simplicity and low overhead of fixed areas with the flexibility of linked lists providing improved performance over other methods.

Packet reception and transmission are determined by memory availability. All other resources are always available if memory is available. To complement this flexible architecture, bus interface functions are incorporated in the LAN91C93I, as well as a 6144 byte packet RAM - and serial EEPROM-based setup. The user can select or modify configuration choices. The LAN91C93I integrates most of the 802.3 functionality, incorporating the MAC layer protocol, the physical layer encoding and decoding functions with the ability to handle the AUI interface. For twisted pair networks, LAN91C93I integrates the twisted pair transceiver as well as the link integrity test functions.

The LAN91C93I is a true 10BASE-T single chip device able to interface to a system or a local bus.

Support for direct-driven LEDs for installation and run-time diagnostics is provided. 802.3 statistics are gathered to facilitate network management.

The LAN91C93I is a single chip Ethernet controller designed to be 100% software compatible with the LAN91C92, LAN91C94 and LAN91C96 in local bus mode.

The LAN91C93I has been designed to support full duplex switched Ethernet and provides Fully independent transmit and receive operations.

The LAN91C93I internal packet memory is extended to 6k bytes, and the MMU will continue to manage memory in 256 byte pages. The increase in memory size accommodates the potential for simultaneous transmit and receive traffic in some full duplex applications as well as support for enhanced performance on systems that introduce increased latency.

The LAN91C93I has the ability to retrieve configuration information from a serial EEPROM on reset or power-up. In local bus mode, the serial EEPROM acts as storage of configuration and IEEE Ethernet address information compatible with the existing LAN91C90, LAN91C92, LAN91C94, and LAN91C96 local bus Ethernet controllers. External Flash ROM is required for CIS storage.

The LAN91C93I offers:

## High integration:

- Single chip controller including:

- Packet RAM

- local bus interface

- EEPROM interface

- Encoder/decoder with AUI interface

- 10BASE-T transceiver

## High performance:

- Chained ("Back-to-back") packet handling with no CPU intervention:

- Queues transmit packets

- Queues receive packets

- Stores results in memory along with packet

- Queues interrupts

- Optional single interrupt upon completion of transmit chain

### Fast block move operation for load/unload:

- CPU sees packet bytes as if stored continuously.

- Handles 16 bit transfers regardless of address alignment.

- Access to packet through fixed window.

#### Fast bus interface:

Compatible with local bus type and faster buses.

### Flexibility:

- Flexible packet and header processing:

- Can be set to Simultasking Early Receive and Transmit modes. With enhanced Early Receive functions.

- Can access any byte in the packet.

- Can immediately remove undesired packets from gueue.

- Can move packets from receive to transmit queue.

- Can alter receive processing order without copying data.

- Can discard or enqueue again a failed transmission.

### Resource allocation:

- Memory dynamically allocated for transmit and receive.

- Can automatically release memory on successful transmission.

## Configuration:

- local bus:

- Uses non-volatile jumperless setup via serial EEPROM.

- nROM on LAN91C93I, is left open with a pullup. This pin is sampled at the end of RESET.

# **Chapter 3 Pin Configurations**

## **Pin Configuration**

Figure 3.1 - Pin Configuration of LAN91C93I QFP

## **Pin Configuration**

Figure 3.2 - Pin Configuration of LAN91C93I TQFP

Rev. 11/17/2004 Page 10 SMSC DS – LAN91C93I

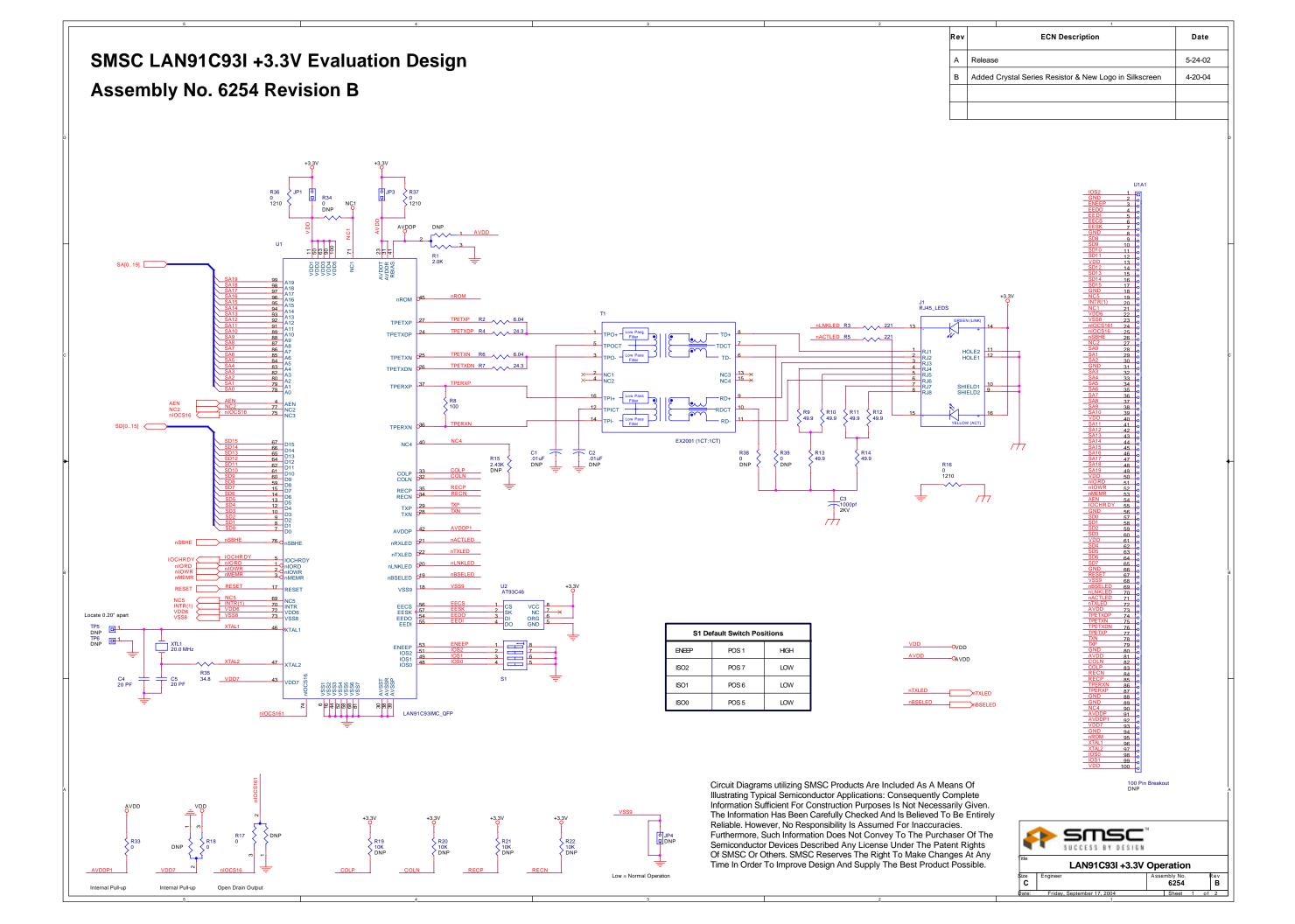

Figure 3.3 – System Diagram for Local Bus with Boot Prom

# 3.1 Local Bus Pin Requirements

| FUNCTION           | LOCAL BUS          | MAX NUMBER OF PINS |

|--------------------|--------------------|--------------------|

| SYSTEM ADDRESS BUS | A0                 | 21                 |

|                    | A1-9               |                    |

|                    | A10                |                    |

|                    | A11                |                    |

|                    | A12-14             |                    |

|                    | A15                |                    |

|                    | A16-18             |                    |

|                    | A19                |                    |

|                    | AEN                |                    |

| SYSTEM DATA BUS    | D0-15              | 16                 |

| SYSTEM CONTROL BUS | RESET              | 8                  |

|                    | nIORD              |                    |

|                    | nIOWR              |                    |

|                    | nMEMR              |                    |

|                    | IOCHRDY            |                    |

|                    | nIOCS16            |                    |

|                    | nSBHE              |                    |

| CEDIAL FEDDOM      | INTR<br>EEDI       | 8                  |

| SERIAL EEPROM      | EEDO               | 0                  |

|                    | EECS               |                    |

|                    | EESK               |                    |

|                    | ENEEP              |                    |

|                    | IOS0               |                    |

|                    | IOS1               |                    |

|                    | IOS2               |                    |

| CRYSTAL OSC.       | XTAL1,             | 2                  |

|                    | XTAL2              |                    |

| POWER              | VDD, AVDD          | 10                 |

| GROUND             | VSS, AVSS          | 12                 |

| 10BASE-T interface | TPERXP             | 6                  |

|                    | TPERXN             |                    |

|                    | TPETXP             |                    |

|                    | TPETXN             |                    |

|                    | TPETXDP<br>TPETXDN |                    |

| AUI interface      | RECP RECN          | 6                  |

| 7.51 111011000     | COLP COLN          |                    |

|                    | TXP TXN            |                    |

| LEDs               | nLNKLED            | 4                  |

|                    | nRXLED             |                    |

|                    | nBSELED            |                    |

| MISC.              | nTXLED<br>RBIAS    | 2                  |

| IVIIOU.            | nROM               |                    |

| NC                 | NC                 | 5                  |

| NC                 | INC                | ၁                  |

# **Chapter 4 Description of Pin Functions**

| PIN NO.                      |                                     |         |                                                                                                                                                                                                                                          |                                                                                                                                                                                                        |  |

|------------------------------|-------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TQFP                         | TQFP QFP PIN NAME                   |         | TYPE                                                                                                                                                                                                                                     | DESCRIPTION                                                                                                                                                                                            |  |

| 43                           | 45                                  | nROM    | I/O4 with pullup  This pin is sampled at the end of RESET. For local bus operation this pin is left open and it is used as a ROM chip select output that goes active when nMEMR is low and the address bus contains a valid ROM address. |                                                                                                                                                                                                        |  |

| 76-78<br>80-87               | 78-80, 82-<br>89                    | A0-10   | I Input address lines 0 through 10.                                                                                                                                                                                                      |                                                                                                                                                                                                        |  |

| 89-97                        | 91-99                               | A11-19  | <br>* *                                                                                                                                                                                                                                  | Input address lines 11 through 19.                                                                                                                                                                     |  |

| 2                            | 4                                   | AEN     | I with pullup                                                                                                                                                                                                                            | Local bus - Address enable input. Used as an address qualifier. Address decoding is only enabled when AEN is low.                                                                                      |  |

| 74                           | 76                                  | nSBHE   | I with pullup                                                                                                                                                                                                                            | Local bus - Byte High Enable input. Asserted (low) by the system to indicate a data transfer on the upper data byte.                                                                                   |  |

| 3                            | 5                                   | IOCHRDY | OD24<br>with<br>pullup                                                                                                                                                                                                                   | Local bus - Output. Optionally used by the LAN91C93I to extend host cycles.                                                                                                                            |  |

| 5-8 10-<br>13 57-60<br>62-65 | 7-10, 12-<br>15,<br>59-62,<br>64-67 | D0-15   | I/O24                                                                                                                                                                                                                                    | I/O24 Bi-directional. 16 bit data bus used to access the LAN91C93 internal registers. The data bus has weak internal pullups. Supports direct connection to the system bus without external buffering. |  |

| 15                           | 17                                  | RESET   | IS with pullup                                                                                                                                                                                                                           | Input. Active high Reset. This input is not considered active unless it is active for at least 100ns to filter narrow glitches.                                                                        |  |

| 68                           | 70                                  | INTR    | O24                                                                                                                                                                                                                                      | Local bus - Active high interrupt signal.                                                                                                                                                              |  |

| 72                           | 74                                  | nIOCS16 | OD24                                                                                                                                                                                                                                     | Local bus - Active low output asserted in 16 bit mode when AEN is low and A4-A15 decode to the LAN91C93I address programmed into the high byte of the Base Address Register.                           |  |

| 99                           | 1                                   | nIORD   | IS with pullup                                                                                                                                                                                                                           | Local bus, - Input. Active low read strobe used to access the LAN91C93I IO space.                                                                                                                      |  |

| 100                          | 2                                   | nIOWR   | IS with pullup                                                                                                                                                                                                                           | Local bus - Input. Active low write strobe used to access the LAN91C93I IO space.                                                                                                                      |  |

| 1                            | 3                                   | nMEMR   | IS with pullup                                                                                                                                                                                                                           | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                |  |

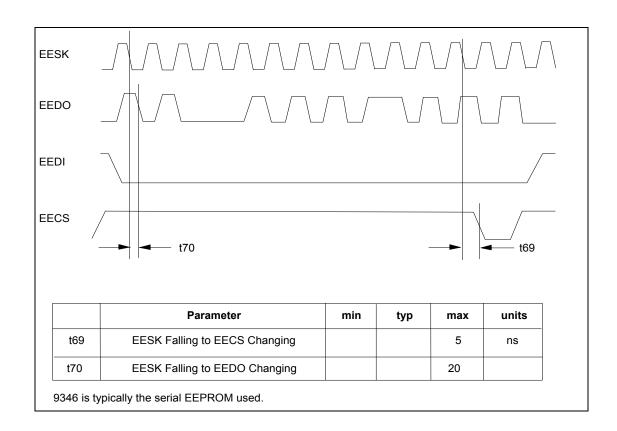

| 55                           | 57                                  | EESK    | O4                                                                                                                                                                                                                                       | Output. 4usec clock used to shift data in and out of a serial EEPROM.                                                                                                                                  |  |

| 54                           | 56                                  | EECS    | 04                                                                                                                                                                                                                                       | Output. Serial EEPROM chip select.                                                                                                                                                                     |  |

| 52                           | 54                                  | EEDO    | 04                                                                                                                                                                                                                                       | Output. Connected to the DI input of the serial EEPROM.                                                                                                                                                |  |

| 53                           | 55                                  | EEDI    | I with<br>pull-<br>down<br>**                                                                                                                                                                                                            | Input. Connected to the DO output of the serial EEPROM.                                                                                                                                                |  |

| PIN NO.                     |                                |             |                        |                                                                                                                                                                                                             |  |

|-----------------------------|--------------------------------|-------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TQFP                        | QFP                            | PIN<br>NAME | TYPE                   | DESCRIPTION                                                                                                                                                                                                 |  |

| 46,47                       | 48,49                          | IOS0-1      | I with<br>pullup       | Input. External switches can be connected to these lines to select between predefined EEPROM configurations. The values of these pins are readable.                                                         |  |

| 49                          | 51                             | IOS2        | I with<br>pullup<br>** | Input. External switches can be connected to these lines to select between predefined EEPROM configurations. The values of these pins are readable.                                                         |  |

| 20                          | 22                             | nTXLED      | OD16                   | Transmit LED output.                                                                                                                                                                                        |  |

| 17                          | 19                             | nBSELED     | OD16                   | Board Select LED activated by accesses to I/O space (nIORD or nIOWR active with AEN low and valid address decode for local bus). The pulse is stretched beyond the access duration to make the LED visible. |  |

| 19                          | 21                             | nRXLED      | OD16                   | Receive LED output.                                                                                                                                                                                         |  |

| 18                          | 20                             | nLNKLED     | OD16                   | Link LED output.                                                                                                                                                                                            |  |

| 51                          | 53                             | ENEEP       | I with pullup          | Input. This active high input enables the EEPROM to be read or written by the LAN91C93I. Internally pulled up. Must be connected to ground if no serial EEPROM is used.                                     |  |

| 44                          | 46                             | XTAL1       | Iclk<br>**             | An external parallel resonance 20MHz crystal should be connected across these pins. If an external clock source is used, it should be connected to this pin (XTAL1) and XTAL2 should be left open.          |  |

| 45                          | 47                             | XTAL2       | Iclk                   | An external parallel resonance 20MHz crystal should be connected across these pins. If an external clock source is used, it should be connected to XTAL1 and this pin (XTAL2) should be left open.          |  |

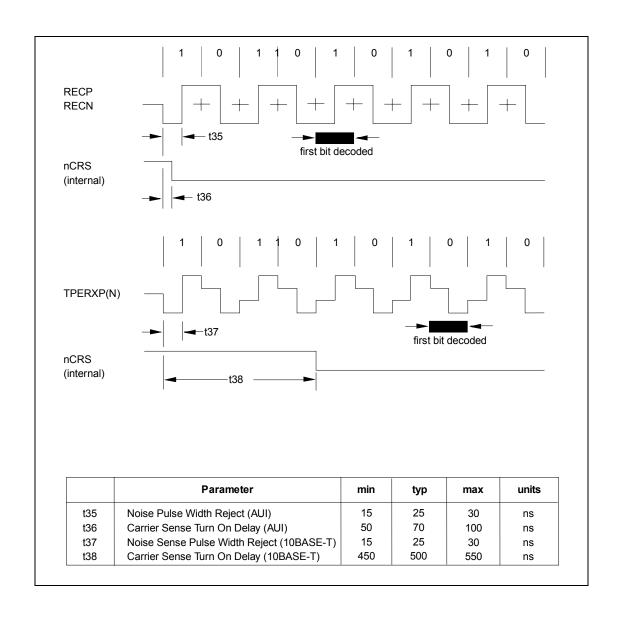

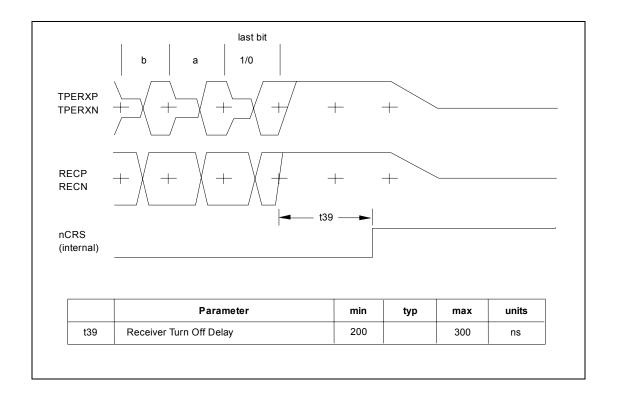

| 33                          | 35                             | RECP/       | Diff.                  | AUI receive differential inputs.                                                                                                                                                                            |  |

| 32                          | 34                             | RECN        | Input<br>**            |                                                                                                                                                                                                             |  |

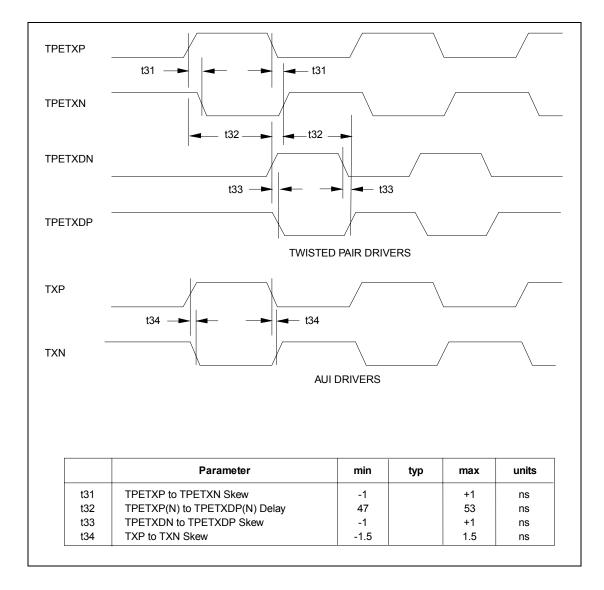

| 27                          | 29                             | TXP         | Diff.                  | TXP and TXN are the AUI transmit differential outputs. They                                                                                                                                                 |  |

| 26                          | 28                             | TXN         | Output                 | must be externally pulled up using 150 ohm resistors.                                                                                                                                                       |  |

| 31                          | 33                             | COLP        | Diff.                  | AUI collision differential inputs. A collision is indicated by a                                                                                                                                            |  |

| 30                          | 32                             | COLN        | Input<br>**            | 10MHz signal at this input pair.                                                                                                                                                                            |  |

| 35                          | 37                             | TPERXP      | Diff.                  | 10BASE-T receive differential inputs.                                                                                                                                                                       |  |

| 34                          | 36                             | TPERXN      | Input<br>* *           |                                                                                                                                                                                                             |  |

| 25                          | 27                             | TPETXP      | Diff.                  | INTERNAL ENDEC - 10BASE-T transmit differential outputs.                                                                                                                                                    |  |

| 23                          | 25                             | TPETXN      | Output                 |                                                                                                                                                                                                             |  |

| 22                          | 24                             | TPETXDP     | Diff.                  | 10BASE-T delayed transmit differential outputs. Used in                                                                                                                                                     |  |

| 24                          | 26                             | TPETXD<br>N | Output                 | combination with TPETXP and TPETXN to generate the 10BASE-T transmit pre-distortion.                                                                                                                        |  |

| 39                          | 41                             | RBIAS       | Analog<br>Input        | A resistor should be connected between this pin and analog ground to determine the receive threshold voltage of TX Receive, AUI Receive, AUI Collision Receive, and AUI transmit voltage.                   |  |

| 61,70,<br>98,9,<br>48,88,41 | 63, 72<br>,90,100,<br>11,50,43 | VDD         |                        | +5.0V power supply pins or 3.3V power supply pins                                                                                                                                                           |  |

| 21,29,<br>40                | 23,31,<br>42                   | AVDD        |                        | +5.0V analog power supply pins or 3.3V power supply pins                                                                                                                                                    |  |

| PIN NO.                  |                       |             |      |                     |

|--------------------------|-----------------------|-------------|------|---------------------|

| TQFP                     | QFP                   | PIN<br>NAME | TYPE | DESCRIPTION         |

| 50,56,<br>71,79          | 52,58,68,<br>73,81,   | VSS         |      | Ground pins.        |

| 4,14,42,<br>66, 16       | 6,16,<br>44, 18,      |             |      |                     |

| 28,36,<br>37             | 30,38,39              | AVSS        |      | Analog ground pins. |

| 75, 73,<br>69, 67,<br>38 | 40, 77, 75,<br>71, 69 | NC          | NC   | No-Connected pins   |

# 4.1 Buffer Symbols

| O4    | Output buffer with 2mA source and 4mA sink at 5V.            |

|-------|--------------------------------------------------------------|

|       | Output buffer with 1mA source and 2mA sink at 3.3V           |

| I/O4  | Output buffer with 2mA source and 4mA sink at 5V.            |

|       | Output buffer with 1mA source and 2mA sink at 3.3V.          |

| O162  | Output buffer with 2mA source and 16mA sink at 5V.           |

|       | Output buffer with 1mA source and 8mA sink at 3.3V.          |

| O24   | Output buffer with 12mA source and 24mA sink at 5V.          |

|       | Output buffer with 6mA source and 12mA sink at 3.3V.         |

| OD16  | Open drain buffer with 16mA sink at 5V.                      |

|       | Open drain buffer with 8mA sink at 3.3V.                     |

| OD24  | Open drain buffer with 24mA sink at 5V.                      |

|       | Open drain buffer with 12mA sink at 3.3V.                    |

| I/O24 | Bi-directional buffer with 12mA source and 24mA sink at 5V.  |

|       | Bi-directional buffer with 6mA source and 16mA sink at 3.3V. |

| I     | Input buffer with TTL levels.                                |

| IS    | Input buffer with Schmitt Trigger Hysteresis.                |

| lclk  | Clock input buffer.                                          |

| **    | Signal is 5.0V input tolerant when $V_{cc}$ =3.3V.           |

|       |                                                              |

DC levels and conditions defined in the DC Electrical Characteristics section.

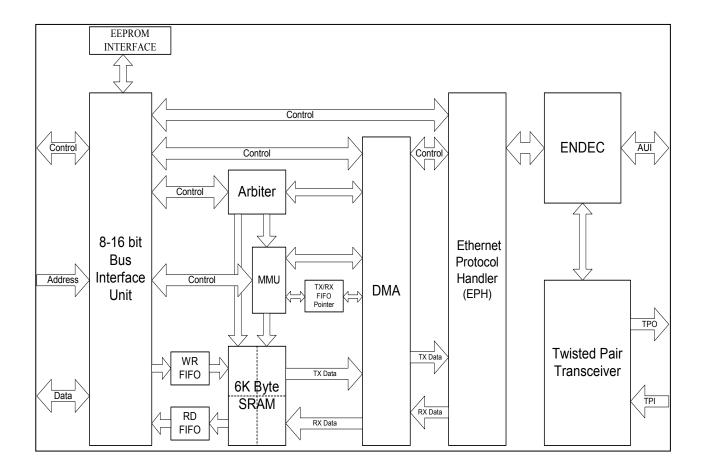

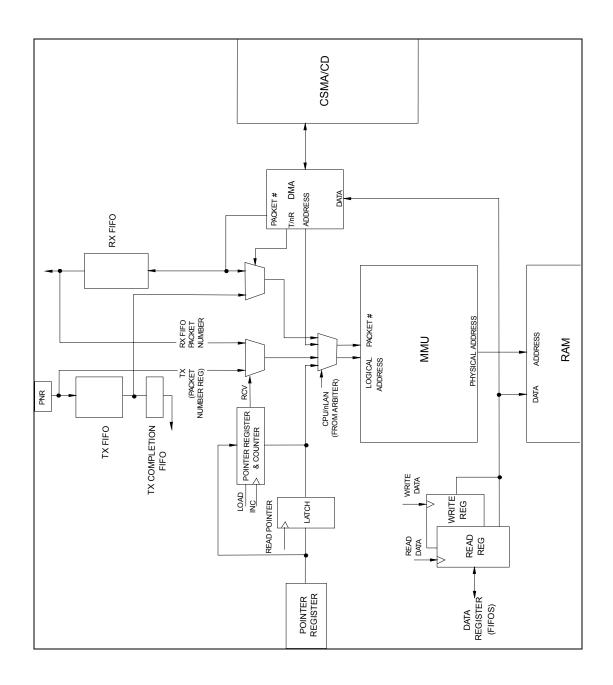

Figure 4.1 - LAN91C93I Internal Block Diagram

# **Chapter 5** Functional Description

The LAN91C93I includes an arbitrated-shared memory of 6144 bytes. Any portion of this memory can be used for receive or transmit packets.

The MMU unit allocates RAM memory to be used for transmit and receive packets, using 256 byte pages.

The arbitration is transparent to the CPU in every sense. There is no speed penalty for local bus type of machines due to arbitration. There are no restrictions on what locations can be accessed at any time. RAM accesses as well as MMU requests are arbitrated.

The RAM is accessed by mapping it into I/O space for sequential access. Except for the RAM accesses and the MMU request/release commands, I/O accesses are not arbitrated.

The I/O space is 16 bits wide. Provisions for 8 bit systems are handled by the bus interface.

In the system memory space, up to 64 kbytes are decoded by the LAN91C93I as expansion ROM. The ROM expansion area is 8 bits wide.

Device configuration is done using a serial EEPROM, with support for modifications to the EEPROM at installation time.

The CSMA/CD core implements the 802.3 MAC layer protocol. It has two independent interfaces, the data path and the control path.

In local bus mode, serial EEPROM is used for configuration and IEEE Node address making it software compatible to the LAN9xxx family of Ethernet LAN Controllers. The EEPROM is optional for local bus requiring a Minimum size of 64 X 16 bit word addresses. Both interfaces are 16 bits wide. The control path provides a set of registers used to configure and control the block. These registers are accessible by the CPU through the LAN91C93I I/O space. The data path is of sequential access nature and typically works in one direction at any given time. An internal DMA type of interface connects the data path to the device RAM through the arbiter and MMU.

The CSMA/CD data path interface is not accessible to the host CPU.

The internal DMA interface can arbitrate for RAM access and request memory from the MMU when necessary.

An encoder/decoder block interfaces the CSMA/CD block on the serial side. The encoder will do the Manchester encoding of the transmit data at 10 Mb/s, while the decoder will recover the receive clock, and decode received data.

Carrier and Collision detection signals are also handled by this block and relayed to the CSMA/CD block.

The encoder/decoder block can interface the network through the AUI interface pairs, or it can be programmed to use the internal 10BASE-T transceiver and connect to a twisted pair network.

The twisted pair interface takes care of the medium dependent signaling for 10BASE-T type of networks. It is responsible for line interface (with external pulse transformers and pre-distortion resistors), collision detection as well as the link integrity test function.

The LAN91C93I provides a 16-bit data path into RAM. The RAM is private and can only be accessed by the system via the arbiter. RAM memory is managed by the MMU. Byte and word accesses to the RAM are supported.

If the system to SRAM bandwidth is insufficient the LAN91C93I will automatically use its IOCHRDY line for flow control. However, for local bus, IOCHRDY will never be negated. The LAN91C93I consists of an integrated Ethernet controller mapped entirely in I/O space.

The Ethernet controller function includes a built-in 6kbyte RAM for packet storage. This RAM buffer is accessed by the CPU through sequential access regions of 256 bytes each. The RAM access is internally arbitrated by the LAN91C93I, and dynamically allocated between transmit and receive packets. Each packet may consist of one or more 256-byte page. The Ethernet controller functionality is identical to the LAN91C94 and LAN91C95 except where indicated otherwise.

The LAN91C93I Memory Management Unit parameters are:

| RAM size               | 6kbytes                              |

|------------------------|--------------------------------------|

| Max. number of pages   | 24                                   |

| Max. number of packets | 24 (FIFOs have 24 entries of 5 bits) |

| Max. pages per packet  | 6                                    |

| Page Size              | 256 bytes                            |

## 5.1 Buffer Memory

The logical addresses for RAM access are divided into TX area and RX area.

The TX area is seen by the CPU as a window through which packets can be loaded into memory before queuing them in the TX FIFO of packets. The TX area can also be used to examine the transmit completion status after packet transmission.

The RX area is associated to the output of the RX FIFO of packets, and is used to access receive packet data and status information.

The logical address is specified by loading the address pointer register. The pointer can automatically increment on accesses.

All accesses to the RAM are done via I/O space.

A bit in the address pointer also specifies if the address refers to the TX or RX area.

In the TX area, the host CPU has access to the next transmit packet being prepared for transmission. In the RX area, it has access to the first receive packet not processed by the CPU yet.

The FIFO of packets, existing beneath the TX and RX areas, is managed by the MMU. The MMU dynamically allocates and releases memory to be used by the transmit and receive functions.

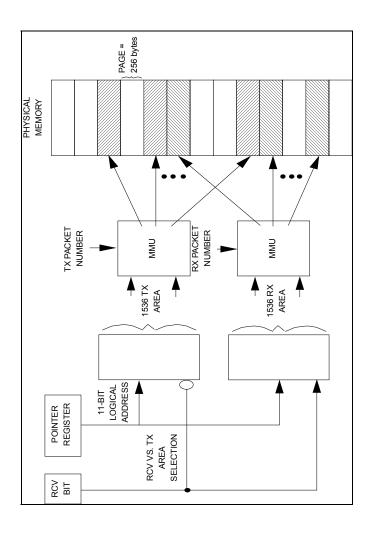

Figure 5.1 – Mapping and Paging vs. Receive and Transmit Area

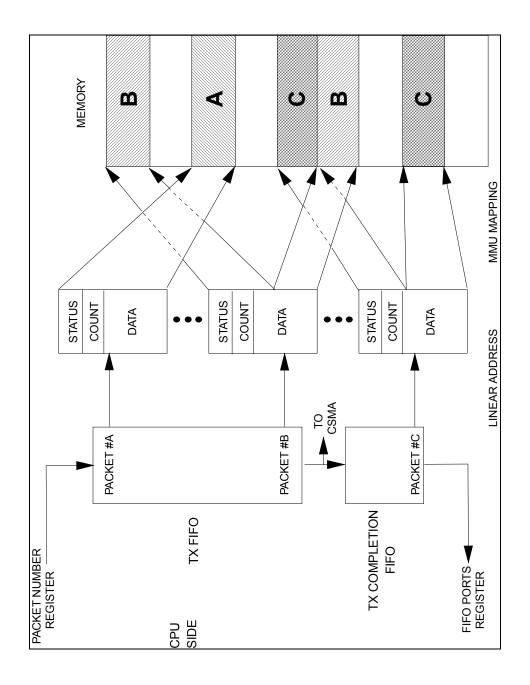

Figure 5.2 - Transmit Queues and Mapping

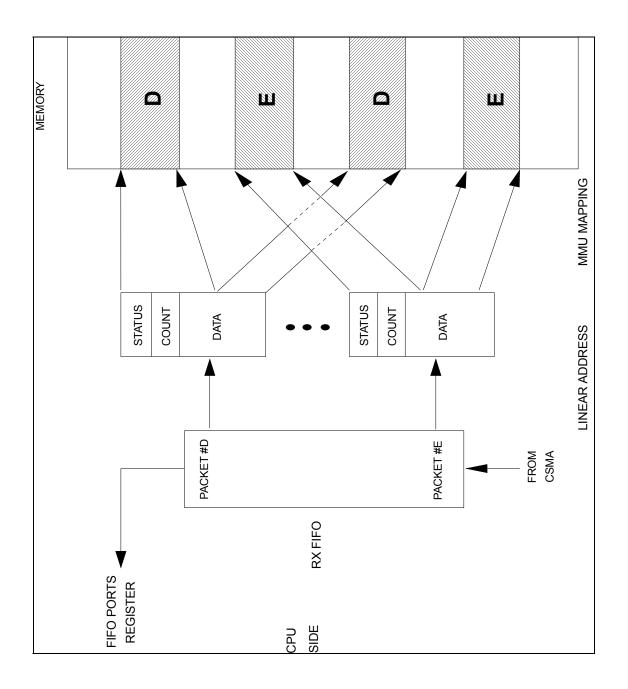

Figure 5.3 – Receive Queues and Mapping

Figure 5.4 – LAN91C93l Internal Block Diagram with Data Path

Figure 5.5 – Logical Address Generation and Relevant Registers

Table 5.1 - LAN91C93I Address Space

|                        | SIGNALS<br>USED | LOCAL<br>BUS | ON-<br>CHIP | DEPTH        | WIDTH           |

|------------------------|-----------------|--------------|-------------|--------------|-----------------|

| Ethernet I/O space (1) | nIORD/<br>nIOWR | Y            | Y           | 16 locations | 8 or 16<br>bits |

Table 5.2 - Bus Transactions in Local Bus Mode

|                          | A0 | NSBHE | D0-7      | D8-15    |

|--------------------------|----|-------|-----------|----------|

| 8 BIT MODE<br>(16BIT=0)) | 0  | ×     | Even byte | -        |

|                          | 1  | Х     | Odd byte  | -        |

| 16 BIT MODE              | 0  | 0     | Even byte | Odd byte |

| Otherwise                |    |       |           |          |

|                          | 0  | 1     | Even byte | -        |

|                          | 1  | 0     | -         | Odd byte |

|                          | 1  | 1     | Invalid   | cycle    |

16 BIT: CONFIGURATION REGISTER bit 7

8 Bit mode: (nMIS16 = 1)

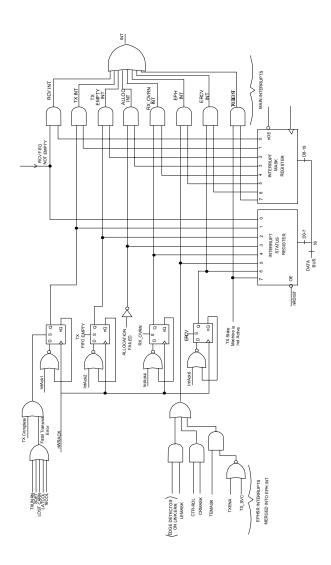

## 5.2 Interrupt Structure

The Ethernet interrupt is conceptually equivalent to the LAN91C94 interrupt line, it is the  $\underline{or}$  function of all enabled interrupts within the Ethernet core.

Table 5.3 - Interrupt Merging

| FUNCTION                  | LOCAL BUS MODE                                                                                                       |

|---------------------------|----------------------------------------------------------------------------------------------------------------------|

| Interrupt Output          | INTR                                                                                                                 |

| Ethernet Interrupt Source | OR function of all interrupt bits specified in the Interrupt Status Register ANDed with their respective Enable bits |

| Ethernet Interrupt Enable | Not Applicable in local bus mode                                                                                     |

## 5.3 Reset Logic

The pins and bits involved in the different reset mechanisms are:

RESET - Input Pin

SOFT RST - EPH Soft Reset bit in RCR

Table 5.4 - Reset Logic

|           | RESETS THE FOLLOWING FUNCTIONS                                             | SAMPLES<br>LOCAL BUS<br>MODE | TRIGGERS<br>EEPROM<br>READ |

|-----------|----------------------------------------------------------------------------|------------------------------|----------------------------|

| RESET pin | All internal logic                                                         | Yes                          | Yes                        |

| SOFT RST  | The Ethernet controller itself except for the IA, CONF and BASE registers. | No                           | No                         |

## 5.4 Power Down Logic States

The following tables describe the power down states of the LAN91C93I. The bits involved in power down are:

- PWRDN Legacy power down bit in Control Register

- LAN91C93I Power Down States

Table 5.5 - Local Bus Mode Defined States (Refer To Table 5.6 For Next States To Wake-Up Events)

|     | CURRENT STATE  |                       |                          |  |  |  |  |  |

|-----|----------------|-----------------------|--------------------------|--|--|--|--|--|

| NO. | CTR PWRDWN BIT | POWERS DOWN           | DOES NOT<br>POWER DOWN   |  |  |  |  |  |

| 1   | X              | Everything.           |                          |  |  |  |  |  |

| 2   | 0              |                       | Ethernet Tx, Rx,<br>Link |  |  |  |  |  |

| 3   | 0              | Ethernet Tx           | Ethernet Rx, Link        |  |  |  |  |  |

| 4   | 1              | Ethernet Tx, Rx, Link |                          |  |  |  |  |  |

| 5   | 1              | Ethernet Tx, Rx, Link |                          |  |  |  |  |  |

Table 5.6 - Local Bus Mode

|     |                                         | NEXT            |                   |                                                       |

|-----|-----------------------------------------|-----------------|-------------------|-------------------------------------------------------|

| NO. | WAKES UP BY                             | CTR PWR-DWN BIT | CTR WAKEUP_EN BIT | COMMENTS                                              |

| 1   |                                         | 0               | 0                 | Fully Awake                                           |

| 2   | By writing a 0 to CTR<br>PWRDWN bit = 0 | 0               | 0                 | The CTR PWRDWN bit has precedence unlike the LAN91C95 |

| 3   | By writing 0 to CTR<br>PWRDWN bit       | 0               | 0                 |                                                       |

# **Chapter 6 Packet Format in Buffer Memory for Ethernet**

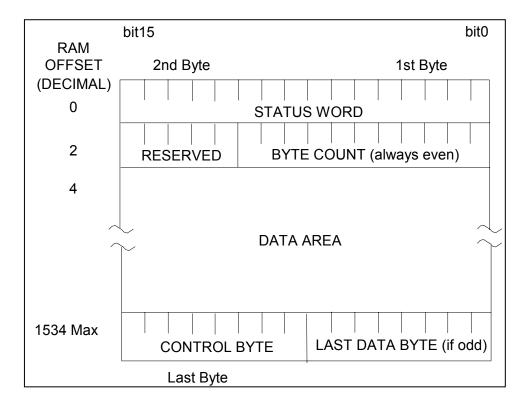

The packet format in memory is similar to that in the TRANSMIT and RECEIVE areas. The first word is reserved for the status word, the next word is used to specify the total number of bytes, and that in turn is followed by the data area. The data area holds the packet itself, and its length is determined by the byte count. The packet memory format is word oriented.

Figure 6.1 - Data Packet Format

|              | TRANSMIT PACKET                                                | RECEIVE PACKET                                                     |

|--------------|----------------------------------------------------------------|--------------------------------------------------------------------|

| STATUS WORD  | Written by CSMA upon transmit completion (see Status Register) | Written by CSMA upon receive completion (see RX Frame Status Word) |

| BYTE COUNT   | Written by CPU                                                 | Written by CSMA                                                    |

| DATA AREA    | Written/modified by CPU                                        | Written by CSMA                                                    |

| CONTROL BYTE | Written by CPU to control ODD/EVEN data bytes                  | Written by CSMA. Also has ODD/EVEN bit                             |

BYTE COUNT - Divided by two, it defines the total number of words, including the STATUS WORD, the BYTE COUNT WORD, the DATA AREA and the CONTROL BYTE. The receive byte count always appears as even, the ODDFRM bit of the receive status word indicates if the low byte of the last word is

Rev. 11/17/2004 Page 26 SMSC DS – LAN91C93I

relevant. The transmit byte count least significant bit will be assumed 0 by the controller regardless of the value written in memory. The maximum size of the frame can be stored in 6 pages (256 bytes per page), the maximum BYTE COUNT number is 1536.

## DATA AREA (in RAM)

The data area starts at offset 4 of the packet structure, and it can extend for up to 1531 bytes. The data area contains six bytes of DESTINATION ADDRESS followed by six bytes of SOURCE ADDRESS, followed by a variable length number of bytes.

On transmit, all bytes are provided by the CPU, including the source address. The LAN91C93I does not insert its own source address. On receive, all bytes are provided by the CSMA side.

The 802.3 Frame Length word (Frame Type in Ethernet) is not interpreted by the LAN91C93I. It is treated transparently as data for both transmit and receive operations.

## **CONTROL BYTE (in RAM)**

The CONTROL BYTE always resides on the high byte of the last word. For transmit packets the CONTROL BYTE is written by the CPU as:

| ХХ | ODD | CRC | 0 | 0 | 0 | 0 |

|----|-----|-----|---|---|---|---|

|----|-----|-----|---|---|---|---|

ODD - If set, indicates an odd number of bytes, with the last byte being right before the CONTROL BYTE. If clear, the number of data bytes is even and the byte before the CONTROL BYTE is not transmitted.

CRC - When set, CRC will be appended to the frame. This bit has only meaning if the NOCRC bit in the TCR is set.

For receive packets the CONTROL BYTE is written by the controller as:

| 0 | 1 | ODD | 0 | 0 | 0 | 0 | 0 |

|---|---|-----|---|---|---|---|---|

ODD - If set, indicates an odd number of bytes, with the last byte being right before the CONTROL BYTE. If clear, the number of data bytes is even and the byte before the CONTROL BYTE should be ignored.

## RECEIVE FRAME STATUS WORD (in RAM)

This word is written at the beginning of each receive frame in memory. It is not available as a register.

| ALGN<br>ERR | BROD<br>CAST | BADCRC | ODDFRM | TOOLNG | TOO<br>SHORT |   |              |

|-------------|--------------|--------|--------|--------|--------------|---|--------------|

| -           |              |        |        |        |              |   |              |

| HASH VALUE  |              |        |        |        |              |   | MULT<br>CAST |

|             | 5            | 4      | 3      | 2      | 1            | 0 |              |

ALGNERR - Frame had alignment error.

BRODCAST - Receive frame was broadcast.

BADCRC - Frame had CRC error.

ODDFRM - This bit when set indicates that the received frame had an odd number of bytes.

TOOLNG - The received frame is longer than the 802.3 maximum size (1518 bytes on the cable).

TOOSHORT - The received frame is shorter than the 802.3 minimum size (64 bytes on the cable).

HASH VALUE - Provides the hash value used to index the Multicast Registers. Can be used by receive routines to speed up the group address search. The hash value consists of the six most significant bits of the CRC calculated on the Destination Address, and maps into the 64 bit multicast table. Bits 5,4,3 of the hash value select a byte of the multicast table, while bits 2,1,0 determine the bit within the byte selected.

Examples of the address mapping are shown in the table below:

| ADDRESS           | HASH VALUE 5-0 | MULTICAST TABLE BIT |

|-------------------|----------------|---------------------|

| ED 00 00 00 00 00 | 000 000        | MT-0 bit 0          |

| 0D 00 00 00 00 00 | 010 000        | MT-2 bit 0          |

| 01 00 00 00 00 00 | 100 111        | MT-4 bit 7          |

| 2F 00 00 00 00 00 | 111 111        | MT-7 bit 7          |

MULTCAST - Receive frame was multicast. If hash value corresponds to a multicast table bit that is set, and the address was a multicast, the packet will pass address filtering regardless of other filtering criteria.

# **Chapter 7** Registers Map in I/O Space

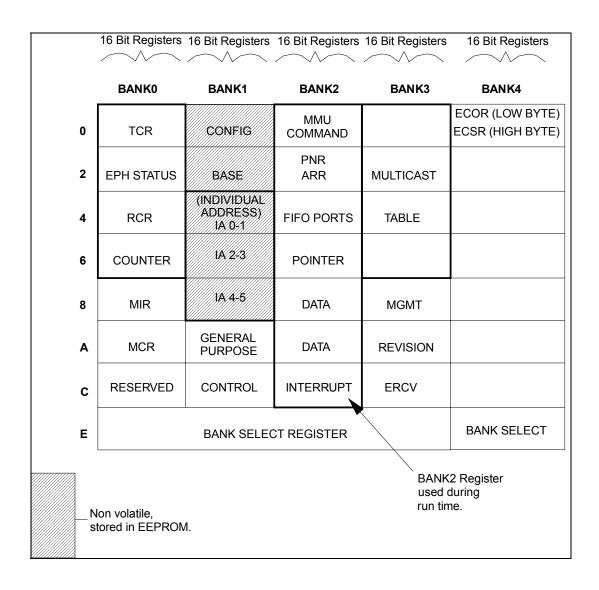

Figure 7.1 - LAN91C93I Registers

## 7.1 I/O Space Access

The address is determined by the Ethernet I/O Base Registers. The Ethernet I/O space can be configured as an 8 or 16 bit I/O space, and is similar to the LAN91C94, LAN91C92, etc. I/O space mapping. To limit the I/O space requirements to 16 locations, the registers are Split into 4 banks in LOCAL BUS mode. The last word of the I/O area is shared by all banks and can be used to change the bank in use. Banks 0 through 3 functionally correspond to the LAN91C94 banks.

Registers are described using the following convention:

| OFF    | SET   | NAME   |                         | TYPE   |            | SYM   | BOL   |

|--------|-------|--------|-------------------------|--------|------------|-------|-------|

| E      | E     |        | BANK SELECT<br>REGISTER |        | READ/WRITE |       | SR    |

| BIT 15 | BIT14 | BIT 13 | BIT 12                  | BIT 11 | BIT 10     | BIT9  | BIT8  |

| RST    | RST   | RST    | RST                     | RST    | RST        | RST   | RST   |

| Val    | Val   | Val    | Val                     | Val    | Val        | Val   | Val   |

| BIT 7  | BIT 6 | BIT 5  | BIT 4                   | BIT 3  | BIT 2      | BIT 1 | BIT 0 |

| RST    | RST   | RST    | RST                     | RST    | RST        | RST   | RST   |

| Val    | Val   | Val    | Val                     | Val    | Val        | Val   | Val   |

OFFSET - Defines the address offset within the IOBASE where the register can be accessed at, provided the bank select has the appropriate value. The offset specifies the address of the even byte (bits 0-7) or the address of the complete word. The odd byte can be accessed using address (offset + 1).

Some registers (e.g. the Interrupt Ack. or the Interrupt Mask) are functionally described as two eight bit registers. In such case, the offset of each one is independently specified.

Regardless of the functional description, when the LAN91C93I is in 16 bit mode, all registers can be accessed as words or bytes.

RST Val - The default bit values upon hard reset are highlighted below each register.

## 7.2 I/O Space Registers Description

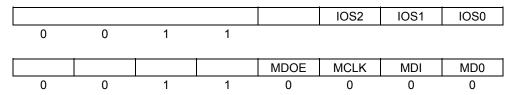

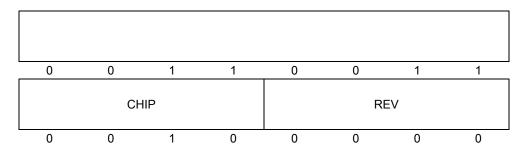

## 7.2.1 Bank Select Register

|             | OFFSET<br># IN HEX |                    | NAME<br>BANK SELECT |            | TYPE<br>READ/WRITE |     | BOL<br>SR |

|-------------|--------------------|--------------------|---------------------|------------|--------------------|-----|-----------|

| <i>"</i> "' |                    | REGISTER NEAD/WITE |                     | READ/WRITE |                    |     |           |

| 0           | 0                  | 1                  | 1                   | 0          | 0                  | 1   | 1         |

| 0           | 0                  | 1                  | 1                   | 0          | 0                  | 1   | 1         |

|             |                    |                    |                     |            | BS2                | BS1 | BS0       |

| X           | Х                  | Х                  | Х                   | Х          | 0                  | 0   | 0         |

BS2, BS1, BS0 - Determine the bank presently in use.

This register is always accessible except in power down mode and is used to select the register bank in use.

The upper byte always reads as 33h and can be used to help determine the I/O location of the LAN91C93I.

The BANK SELECT REGISTER is always accessible regardless of the value of BS0-2.

Accesses to non-existing banks will ignore writes and reads will return 0x33 on byte reads.

| BS2 | BS1 | BSO | BANK# |

|-----|-----|-----|-------|

| 0   | 0   | 0   | 0     |

| 0   | 0   | 1   | 1     |

| 0   | 1   | 0   | 2     |

| 0   | 1   | 1   | 3     |

| 1   | X   | X   | None  |

### I/O SPACE - BANK0

| OFFSET | NAME                      | TYPE       | SYMBOL |

|--------|---------------------------|------------|--------|

| 0      | TRANSMIT CONTROL REGISTER | READ/WRITE | TCR    |

This register holds bits programmed by the CPU to control some of the protocol transmit options.

| FDSE   | ETEN- | EPH  | STP  | FDUPLX | MON_   |      | NOCRC |

|--------|-------|------|------|--------|--------|------|-------|

|        | TYPE  | LOOP | SQET |        | CSN    |      |       |

| 0      | 0     | 0    | 0    | 0      | 0      | Х    | 0     |

| PAD_EN |       |      |      | TXP_EN | FORCOL | LOOP | TXENA |

| 0      | Х     | Χ    | Χ    | 0      | 0      | 0    | 0     |

NOCRC - Does not append CRC to transmitted frames when set, allows software to insert the desired CRC. Defaults to zero, namely CRC inserted.

FDSE - Full Duplex Switched Ethernet. When set, the LAN91C93I is configured for Full Duplex Switched Ethernet, it defaults clear to normal CSMA/CD protocol. In FDSE mode the LAN91C93I transmit and receive processes are fully independent, namely no deferral and no collision detection are implemented. When FDSE is set, FDUPLX is internally assumed high and MON\_CSN is assumed low regardless of their actual values.

ETEN-TYPE - Early transmit underrun function type. When low, ETEN bit in the PTR register will enable the Early transmit underrun function as it was implemented in the LAN91C94. I.e. "The Early Transmit function allows the CPU to enqueue the first transmit packet before it is fully loaded in packet memory. The loading operation proceeds in parallel with the transmission, and in the case that the transmitter gets ahead of the CPU, the LAN91C93I will prevent the transmission of erroneous data by forcing an Underrun condition. Underruns will be triggered by starving the transmit DMA if the LAN91C93I detects that the DMA TX address exceeds the pointer address."

With ETEN -TYPE set to one (1), ETEN bit set to one (1) in the pointer register will mean the following:

"For underrun detection purposes the RAM logical address and packet numbers of the packet being loaded are compared against the logical address and packet numbers of the packet being transmitted. If the packet numbers match and the logical address of the packet being transmitted exceeds the address being loaded, the LAN91C93I will prevent the transmission of erroneous data by forcing an Underrun condition. Underruns will be triggered by starving the transmit DMA if the LAN91C93I detects that the DMA TX address exceeds the pointer address."

EPH\_LOOP - Internal loopback at the EPH block. Does not exercise the encoder decoder. Serial data is looped back when set. Defaults low.

STP\_SQET - Stop transmission on SQET error. If set, stops and disables transmitter on SQE test error. Does not stop on SQET error and transmits next frame if clear. Defaults low.

FDUPLX - When set it enables full duplex operation. This will cause frames to be received if they pass the address filter regardless of the source for the frame. When clear the node will not receive a frame sourced by itself. Clearing this bit (Normal Operation), allows in promiscuous mode, not to receive it's own packet.

TXP EN - This bit is reserved and should always be set to 0 on the LAN91C93I.

MON\_CSN - When set the LAN91C93I monitors carrier while transmitting. It must see its own carrier by the end of the preamble. If it is not seen, or if carrier is lost during transmission, the transmitter aborts the frame without CRC and turns itself off.

When this bit is clear the transmitter ignores its own carrier. Defaults low.

PAD\_EN - When set, the LAN91C93I will pad transmit frames shorter than 64 bytes with 00. For TX, CPU should write the actual BYTE COUNT before padded by the LAN91C93I to the buffer RAM, excludes the padded 00. When this bit is cleared, the LAN91C93I does not pad frames.

FORCOL - When set the transmitter will force a collision by not deferring deliberately. After the collision this bit is reset automatically. This bit defaults low to normal operation.

LOOP - Local Loopback. When set, transmit frames are internally looped to the receiver after the encoder/decoder. Collision and Carrier Sense are ignored. No data is sent out. Defaults low to normal mode.

TXENA - Transmit enabled when set. Transmit is disabled if clear. When the bit is cleared the LAN91C93I will complete the current transmission before stopping. When stopping due to an error, this bit is automatically cleared.

| AUI | FDSE | FDUPLX | EPH_LOOP | LOOP | LOOPS AT                                                | TRANSMITS<br>TO NETWORK |

|-----|------|--------|----------|------|---------------------------------------------------------|-------------------------|

| Х   | Х    | Х      | 1        | Х    | EPH Block                                               | No                      |

| 1   | 0    | 1      | 0        | 0    | Cable                                                   | Yes                     |

| 0   | 0    | 1      | 0        | 0    | 10BASE-T Driver                                         | Yes                     |

| Х   | 0    | 0      | 0        | 0    | NORMAL CSMA/CD -<br>No Loopback                         | Yes                     |

| X   | 1    | 1      | 0        | 0    | FULL DUPLEX SWITCHED ETHERNET - No loopback and No SQET | Yes                     |

**Table 7.1- Transmit Loop**

### I/O SPACE - BANK0

| OFFSET | NAME                | TYPE      | SYMBOL |

|--------|---------------------|-----------|--------|

| 2      | EPH STATUS REGISTER | READ ONLY | EPHSR  |

This register stores the status of the last transmitted frame. This register value, upon individual transmit packet completion, is stored as the first word in the memory area allocated to the packet. Packet interrupt processing should use the copy in memory as the register itself will be updated by subsequent packet transmissions. The register can be used for real time values (like TXENA and LINK OK). If TXENA is cleared the register holds the last packet completion status.

| TX   | LINK |      | CTR   | EXC  | LOST | LATCOL |        |

|------|------|------|-------|------|------|--------|--------|

| UNRN | OK _ | RES  | _ROL  | _DEF | CARR |        |        |

| 0    | 0    | 0    | 0     | 0    | 0    | 0      | Х      |

| TX   | LTX  | SQET | 16001 | LTX  | MUL  | SNGL   | TV CHC |

| DEFR | BRD  | SQET | 16COL | MULT | COL  | COL    | TX_SUC |

| 0    | 0    | 0    | 0     | 0    | 0    | 0      | 0      |

TXUNRN - Transmit Under run. Set if Under run occurs, it also clears TXENA bit in TCR. Cleared by setting TXENA high. This bit should never be set under normal operation.

LINK\_OK - State of the 10BASE-T Link Integrity Test. A transition on the value of this bit generates an interrupt when the LE ENABLE bit in the Control Register is set.

RES – This bit is reserved and will always return a zero(0). CTR\_ROL - Counter Roll over. When set one or more 4 bit counters have reached maximum count (15). Cleared by reading the ECR register.

EXC\_DEF - Excessive deferral. When set last/current transmit was deferred for more than 1518 \* 2 byte times. Cleared at the end of every packet sent.

LOST\_CARR - Lost carrier sense. When set indicates that Carrier Sense was not present at end of preamble. Valid only if MON\_CSN is enabled. This condition causes TXENA bit in TCR to be reset. Cleared by setting TXENA bit in TCR.

LATCOL - Late collision detected on last transmit frame. If set a late collision was detected (later than 64 byte times into the frame). When detected the transmitter JAMs and turns itself off clearing the TXENA bit in TCR. Cleared by setting TXENA in TCR.

TX\_DEFR - Transmit Deferred. When set, carrier was detected during the first 6.4 uSec of the inter frame gap. Cleared at the end of every packet sent.

LTX\_BRD - Last transmit frame was a broadcast. Set if frame was broadcast. Cleared at the start of every transmit frame.

SQET - Signal Quality Error Test. The transmitter opens a 1.6 us window 0.8 us after transmission is completed and the receiver returns inactive. During this window, the transmitter expects to see the SQET signal from the transceiver. The absence of this signal is a 'Signal Quality Error' and is reported in this status bit. Transmission stops and EPH INT is set if STP\_SQET is in the TCR is also set when SQET is set. This bit is cleared by setting TXENA high.

16COL- 16 collisions reached. Set when 16 collisions are detected for a transmit frame. TXENA bit in TCR is reset. Cleared when TXENA is set high.

LTX\_MULT - Last transmit frame was a multicast. Set if frame was a multicast. Cleared at the start of every transmit frame.

MULCOL - Multiple collision detected for the last transmit frame. Set when more than one collision was experienced. Cleared when TX SUC is high at the end of the packet being sent.

SNGLCOL - Single collision detected for the last transmit frame. Set when a collision is detected. Cleared when TX\_SUC is high at the end of the packet being sent.

TX\_SUC - Last transmit was successful. Set if transmit completes without a fatal error. This bit is cleared by the start of a new frame transmission or when TXENA is set high.

#### Fatal errors are:

- 16 collisions

- SQET fail and STP\_SQET = 1

- FIFO Underrun

- Carrier lost and MON CSN = 1

- Late collision

### I/O SPACE - BANK0

| OFFSET | NAME                     | TYPE       | SYMBOL |

|--------|--------------------------|------------|--------|

| 4      | RECEIVE CONTROL REGISTER | READ/WRITE | RCR    |

| SOFT<br>RST | FILT<br>CAR | 0 | 0 | 0 | 0     | STRIP<br>CRC | RXEN         |