TLCS-90 Series TMP90P802A

### **CMOS 8-Bit Microcontrollers**

### TMP90P802AP/TMP90P802AM

### 1. Outline and Characteristics

The TMP90P802A is a system evaluation LSI having a built in One-Time PROM for TMP90C802A.

A programming and verification for internal PROM is achieved by using a general EPROM programmer with an adapter socket.

The function of this device is exactly same as the TMP90C802A by programming to the internal PROM.

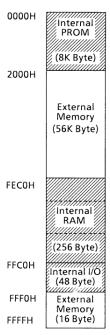

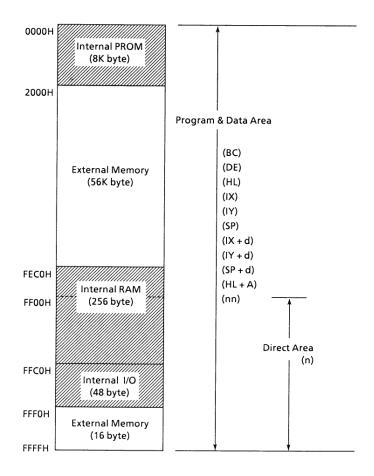

The following are the memory map of TMP91C640 and TMP90C840A.

TMP90P802A Memory Map

| Parts No.   | ROM         | RAM        | Package | Adapter Socket No. |

|-------------|-------------|------------|---------|--------------------|

| TMP90P802AP | OTP         | 256 x 8bit | 40-DIP  | BM1158             |

| TMP90P802AM | 8192 x 8bit | 250 X 001t | 40-DIP  | BM1159             |

The information contained here is subject to change without notice.

The information contained herein is presented only as guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others. These TOSHIBA products are intended for usage in general electronic equipments, communication equipment, measuring equipment, domestic electrification, etc.) Please make sure that you consult with us before you use these TOSHIBA products in equipments which require high quality and/or reliability, and in equipments which could have major impact to the welfare of human life (atomic energy control, spaceship, traffic signal, combustion control, all types of safety devices, etc.). TOSHIBA cannot accept liability to any damage which may occur in case these TOSHIBA products were used in the mentioned equipments without prior consultation with TOSHIBA.

TOSHIBA CORPORATION 1/14

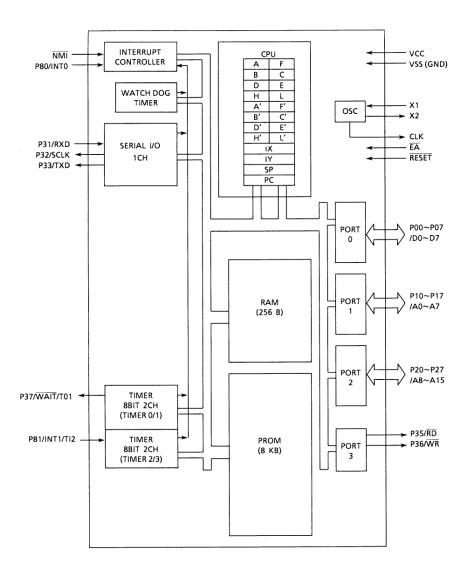

Figure 1. TMP90C802A Block Diagram

2/14 TOSHIBA CORPORATION

# 2. Pin Assignment and Functions

### 2.1 Pin Assignment

The assignment of input/output pins, their names and functions are described below.

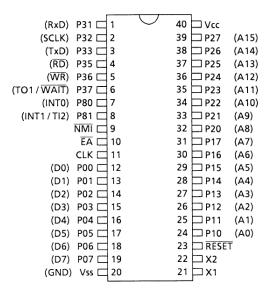

Figure 2.1 (1) shows pin assignment of the TMP90P802A.

Figure 2.1 (1). Pin Assignment

Figure 2.1 (2) shows pin assignment of the TMP90P802A.

## 2.2 Pin Names and Functions

The TMP90P802A has MCU mode and PROM mode.

(1) MCU Mode (The TMP90P802A and the TMP90C802A are pin compatible).

**Table 2.2 Pin Names and Functions**

| Pin Name              | No. of pins | I/O 3 states     | Function                                                                                                                |

|-----------------------|-------------|------------------|-------------------------------------------------------------------------------------------------------------------------|

| P00 ~ P07             | 0           | 1/0              | Port 0: 8-bit I/O port that allows selection of input/output on byte basis                                              |

| /D0 ~ D7              | 8           | 3 states         | Data Bus: Also functions as 8-bit bidirectional data bus for external memory                                            |

| P10 ~ P17             |             | 1/0              | Port 1: 8-bit I/O port that allows selection on byte basis                                                              |

| /A0 ~ A7              | 8           | Output           | Addrress Bus: The lower 8 bits address bus for external memory                                                          |

| P20 ~ P27             | 0           | 1/0              | Port 2: 8-bit I/O port that allows selection on byte basis                                                              |

| /A8 ~ A 15            | 8           | Output           | Addrress Bus: The uppper 8 bits address bus for external memory                                                         |

| P31                   | 4           | lanut            | Port 31: 1-bit input port                                                                                               |

| /RxD                  | 1           | Input            | Receives serial data                                                                                                    |

| P32                   |             |                  | Port 32: 1-bit output port                                                                                              |

| /TxD<br>/RTS<br>/SCLK | 1           | Output           | Serial clock output                                                                                                     |

| P33                   | 1           | Output           | Port 33: 1-bit output port                                                                                              |

| /TxD                  | 1           | Output           | Transmits serial data                                                                                                   |

| P35                   | 1           | Output           | Port 35: 1-bit output port                                                                                              |

| /RD                   | !           | Output           | Read: Generates strobe signal for reading external memory                                                               |

| P <u>36</u>           | 1           | Output           | Port 36: 1-bit output port                                                                                              |

| /WR                   |             | Output           | Writes: Generates strobe signal for writing external memory                                                             |

| P37                   | 1           | Input            | Port 37: 1-bit input port                                                                                               |

| /WAIT                 |             |                  | Wait: Input pin for connecting slow speed memory or peripheral LSI                                                      |

| D00                   |             |                  | Port 80: 1-bit input port                                                                                               |

| P80<br>/INTO          | 1           | Input            | Interrupt request pin 0: Interrupt request pin (Level/rising edge is programmable)                                      |

|                       |             |                  |                                                                                                                         |

|                       |             |                  | Port 81: 1-bit input port                                                                                               |

| P81<br>/INT1          | 1           | Input            | Interrupt request pin 1: Interrupt request pin (Rising/falling edge is programmable)                                    |

| /TI4                  | '           | IIIput           |                                                                                                                         |

|                       |             |                  | Timer input 4: Counter/capture trigger signal for Timer 4                                                               |

| NMI                   | 1           | Input            | Non-maskable interrupt request pin: Falling edge interrupt request pin                                                  |

| INIVII                | '           | Input            |                                                                                                                         |

| CLK                   | 1           | Output           | Clock output: Generates clock pulse at 1/4 frequency of clock oscillation. It is Pulled up internally during resetting. |

| ĒĀ                    | 1           | Input            | Connects with $V_{CC}$ pin .                                                                                            |

| RESET                 | 1           | Input            | Reset: Initializes the TMP90P802A (Built-in pull-up resistor)                                                           |

| X1/X2                 | 2           | Input/<br>Output | Pin for quartz crystal or ceramic resonator (1 ~ 12.5MHz)                                                               |

| V <sub>CC</sub>       | 1           | -                | Power supply (+5V)                                                                                                      |

| V <sub>SS</sub> (GND) | 1           | _                | Ground (0V)                                                                                                             |

# 2) PROM Mode

**Table 2.2.2**

| Pin Function<br>Name | No. of pins | I/O             | Function                            | Pin Name<br>(MCU mode) |  |  |

|----------------------|-------------|-----------------|-------------------------------------|------------------------|--|--|

| A7 ~ A0              | 8           | Input           | Address Input                       | P17 ~ P10              |  |  |

| A12 ~ A8             | 5           | Input           | Audiess iliput                      | P24 ~ P20              |  |  |

| A15 ~ A13            | 3           | Input           | Be fixed to "L" level.              | P27 ~ P25              |  |  |

| D7 ~ D0              | 8           | 1/0             | Data Input/Output                   | P07 ~ P00              |  |  |

| ŌĒ                   | 1           | Input           | Output Enable Input                 | P35                    |  |  |

| CE                   | 1           | Input           | Chip Enable Input                   | P36                    |  |  |

| VPP                  | 1           | Power<br>Supply | 12.5V/5V (Programming Power Supply) | ĒĀ                     |  |  |

| VCC                  | 1           | Power Supply    | 5V                                  |                        |  |  |

| VSS                  | 1           | Power Supply    | 0V                                  |                        |  |  |

| Pin Name             | No. of pins | I/O             | Pin Setting                         |                        |  |  |

| P31                  | 1           | Input           | Be fixed level.                     |                        |  |  |

| P32 ~ P34            | 3           | Output          | Open                                |                        |  |  |

| P37                  | 1           | Input           | Be fixed level.                     |                        |  |  |

| P80 , P81            | 2           | Input           | Be fixed to "H" level.              |                        |  |  |

| NMI                  | 1           | Input           | Be fixed to level.                  |                        |  |  |

| RESET                | 1           | Input           | Be fixed to "L" level.              |                        |  |  |

| CLK                  | 1           | Input           | Be fixed to "L" level.              |                        |  |  |

| X1                   | 1           | Input           | Pecaneter connection nin            |                        |  |  |

| X2                   | 1           | Output          | Resonator connection pin            |                        |  |  |

## 3. Operation

The TMP90P802A is the OTP version of the TMP90C802A that is replaced an internal ROM from Mask ROM to EPROM.

The function of TMP90P802A is exactly same as that of TMP90C840A.

Refer to the TMP90C802A except the functions which are not described this section.

The following is an explanation of the hardware configuration and operation in the relation to the TMP90P802A.

The TMP90P802A has an MCU mode and a PROM mode.

### 3.1 MCU Mode

(1) Mode Setting and Function

The MCU mode is set by opening the CLK pin (Output status).

In the MCU mode, the operation is the same as that of TMP90C802A.

(2) Memory Map

Figure 3.1 shows the memory map of TMP90P802A, and the accessing area by the respective addressing mode.

Figure 3.1. TMP90P802A Memory Map

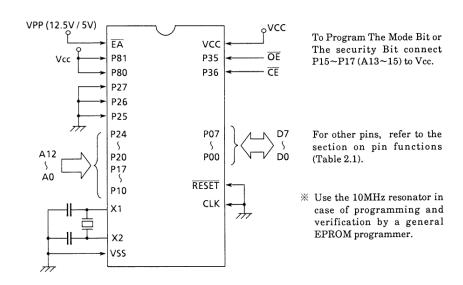

#### 3.2 PROM Mode

#### (1) Mode Setting and Function

PROM mode is set by setting the RESET and CLK pins to the "L" level.

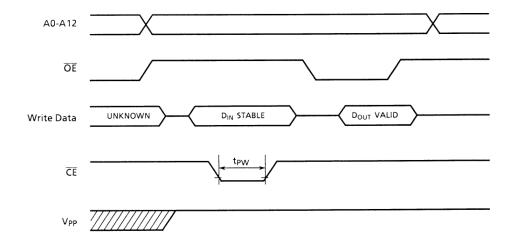

The programming and verification for the internal PROM is achieved by using a general PROM programmer with the adaptor socket. The device selection (ROM Type) should be "27256" with following conditions. size: 256Kbit (32K x 8-bit) VPP: 12.5V TPW: 1ms Figure 3.2 shows the setting of pins in PROM mode.

Figure 3.2. PROM Mode Pin Setting

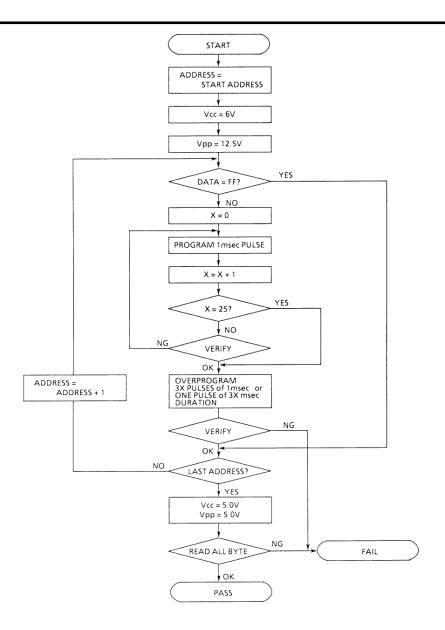

#### (2) Programming Flow Chart

The programming mode is set by applying 12.5V (programming voltage) to the VPP pin when the following pins are set as follows,

(Vcc : 6.0V) \*These conditions can be (RESET : "L" level) obtained by using adaptor (CLK : "L" level) socket.

After the address and data have been fixed, a data on the Data Bus is programmed when the  $\overline{CE}$  pin is set to "Low" (1ms plus is required).

General Programming procedure of an EPROM programmer is as follows,

- Write a data to a specified address for 1ms.

- Verify the data. If the read-out data does not match the expected data, another writing is performed until the correct data is written (Max. 25 times).

After the correct data is written, an additional writing is performed by using three times longer programming pulse width (1ms x programming times), or using three times more programming pulse number. Then, verify the data and increment the address.

The verification for all data is done under the condition of Vpp = Vcc = 5V after all data were written.

Figure 3.3 shows the programming flow chart.

Figure 3.3. Flow Chart

### (3) The Mode Bit and the Security Bit

The TMP90P802A has the Security Bit in PROM cell. If the Sercuity Bit is programmed to "0", the content of the PROM is disable to read in PROM mode.

How to Program the Security Bit.

- 1) Connect A15 pins to  $V_{CC}$ . [Otherwise connect them to GND to program PROM]

- 2) Set programming address to 0000H.

- 3) To program the Security Bit, set D0 to "0".

- 4) Set D2  $\sim$  D7 to "1" respectively.

The following table shows the 8-bit data to program The Security Bit.

Table 3.1 Data to Program

|                      | 1 1 2 1 1 3 |          |                             |

|----------------------|-------------|----------|-----------------------------|

| Bit to Program       | D0 ~ D7     | A0 ~ A12 | A13, A14, A15               |

| The Security Bit     | FEH         | All "0"  | A13, A14 = "0"<br>A15 = "1" |

| PROM (0000H ~ 1FFFH) | -           | -        | All "0"                     |

# 4. Electrical Characteristics

TMP90P802AP/TMP90P802AM

# 4.1 Absolute Maximum Ratings

| Symbol              | Parameter                      | Rating                       | Unit  |

|---------------------|--------------------------------|------------------------------|-------|

| V <sub>CC</sub>     | Supply voltage                 | -0.5 ~ + 7                   | V     |

| V <sub>IN</sub>     | Input voltage                  | -0.5 ~ V <sub>CC</sub> + 0.5 | V     |

| D                   | Power dissipation (Ta = 85°C)  | F 500                        | mW    |

| $P_{D}$             | 1 ower dissipation (1a = 65 G) | N 600                        | IIIVV |

| T <sub>SOLDER</sub> | Soldering temperature (10s)    | 260                          | °C    |

| $T_{STG}$           | Storage temperature            | -65 ~ 150                    | °C    |

| T <sub>OPR</sub>    | Operating temperature          | -40 ~ 85                     | °C    |

## 4.2 DC Characteristics

$V_{CC} = 5V \pm 10\% \quad TA = -40 \sim 85^{\circ}C \quad (1 \sim 10 MHz) \\ TA = -20 \sim 70^{\circ} \quad (1 \sim 16 MHz)$

| Symbol                                                  | Parameter                                      | Min                                              | Max                   | Unit           | Test Conditions                                                  |

|---------------------------------------------------------|------------------------------------------------|--------------------------------------------------|-----------------------|----------------|------------------------------------------------------------------|

| V <sub>IL</sub>                                         | Input Low Voltage (P0)                         | -0.3                                             | 0.8                   | V              | -                                                                |

| V <sub>IL1</sub>                                        | P1, P2, P3, P8                                 | -0.3                                             | 0.3V <sub>CC</sub>    | V              | _                                                                |

| V <sub>IL2</sub>                                        | RESET, INTO, NMI                               | -0.3                                             | 0.25V <sub>CC</sub>   | V              | -                                                                |

| $V_{IL3}$                                               | EA                                             | -0.3                                             | 0.3                   | V              | _                                                                |

| V <sub>IL4</sub>                                        | X1                                             | -0.3                                             | 0.2V <sub>CC</sub>    | V              | -                                                                |

| V <sub>IH</sub>                                         | Input Low Voltage (D0 ~ D7)                    | 2.2                                              | V <sub>CC</sub> + 0.3 | V              | -                                                                |

| V <sub>IH1</sub>                                        | P1, P2, P3, P8                                 | 0.7V <sub>CC</sub>                               | V <sub>CC</sub> + 0.3 | V              | -                                                                |

| V <sub>IH2</sub>                                        | RESET, INTO, NMI                               | 0.75V <sub>CC</sub>                              | V <sub>CC</sub> + 0.3 | V              | -                                                                |

| V <sub>IH4</sub>                                        | X1                                             | 0.8V <sub>CC</sub>                               | V <sub>CC</sub> + 0.3 | V              | -                                                                |

| V <sub>OL</sub>                                         | Output Low Voltage                             | -                                                | 0.45                  | V              | I <sub>OL</sub> = 1.6mA                                          |

| V <sub>0H</sub><br>V <sub>0H1</sub><br>V <sub>0H2</sub> | Output High Voltage                            | 2.4<br>0.75V <sub>CC</sub><br>0.9V <sub>CC</sub> | -                     | V<br>V<br>V    | $I_{OH} = -400 \mu A$ $I_{OH} = -100 \mu A$ $I_{OH} = -20 \mu A$ |

| I <sub>DAR</sub>                                        | Darlington Drive Current (8 I/O pins)          | -1.0                                             | -3.5                  | mA             | $V_{EXT} = 1.5V$ $R_{EXT} = 1.1k\Omega$                          |

| I <sub>LI</sub>                                         | Input Leakage Current                          | 0.02 (Typ)                                       | ±5                    | μA             | 0.0 ≤ Vin ≤ V <sub>CC</sub>                                      |

| I <sub>LO</sub>                                         | Output Leakage Current                         | 0.05 (Typ)                                       | ±10                   | μΑ             | 0.2 ≤ Vin ≤ V <sub>CC</sub> - 0.2                                |

| I <sub>CC</sub>                                         | Operating Current (RUN) Idle 1 Idle 2          | 17 (Тур)<br>1.5 (Тур)<br>6 (Тур)                 | 30<br>5<br>15         | mA<br>mA<br>mA | tosc = 10MHz<br>(25% Up @ 12.5MHz)                               |

|                                                         | STOP (TA = -20 ~ 70°C)<br>STOP (TA = 0 ~ 50°C) | 0.2 (Typ)                                        | 50<br>10              | μA<br>μA       | 0.2 ≤ Vin ≤ V <sub>CC</sub> - 0.2                                |

| V <sub>STOP</sub>                                       | Power Down Voltage (@STOP)                     | 2<br>RAM BACK UP                                 | 6                     | ΚΩ             | $V_{IL2} = 0.2V_{CC},$<br>$V_{IH2} = 0.8V_{CC}$                  |

| R <sub>RST</sub>                                        | RESET Pull Up Register                         | 50                                               | 150                   | КΩ             | -                                                                |

| CIO                                                     | Pin Capacitance                                | _                                                | 10                    | pF             | testfreq = 1MHz                                                  |

| V <sub>TH</sub>                                         | Schmitt width RESET, NMI, INTO                 | 0.4                                              | 1.0 (Typ)             | V              | _                                                                |

Note:  $\ensuremath{\text{I}_{\text{DAR}}}$  is guaranteed for a total of up to 8 optional ports.

TOSHIBA CORPORATION 9/14

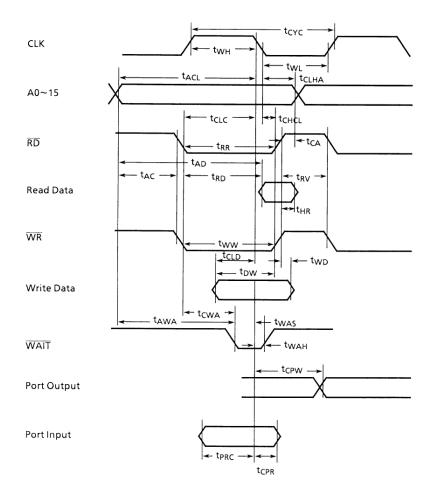

### 4.3 AC Characteristics

| Oh.a.l            | Davamatav                      | Vai       | riable     | 10MH | z Clock | 12.5M | Hz Clock | IIm!A |

|-------------------|--------------------------------|-----------|------------|------|---------|-------|----------|-------|

| Symbol            | Parameter                      | Min       | Max        | Min  | Max     | Min   | Max      | Unit  |

| t <sub>OSC</sub>  | OSC. Period = x                | 80        | 1000       | 100  | _       | 80    | _        | ns    |

| t <sub>CYC</sub>  | CLK Period                     | 4x        | 4x         | 400  | -       | 320   | -        | ns    |

| t <sub>WL</sub>   | CLK Low width                  | 2x - 40   | -          | 160  | -       | 120   | -        | ns    |

| t <sub>WH</sub>   | CLK High width                 | 2x - 40   | -          | 160  | -       | 120   | -        | ns    |

| t <sub>AC</sub>   | Address Setup to RD, WR        | x - 45    | -          | 55   | -       | 35    | -        | ns    |

| t <sub>RR</sub>   | RD Low width                   | 2.5x - 40 | -          | 210  | -       | 160   | -        | ns    |

| t <sub>CA</sub>   | Address Hold Time After RD, WR | 0.5x - 30 | -          | 20   | -       | 10    | -        | ns    |

| t <sub>AD</sub>   | Address to Valid Data In       | -         | 3.5x - 95  | -    | 255     | -     | 185      | ns    |

| t <sub>RD</sub>   | RD to Valid Data In            | -         | 2.5x - 80  | -    | 170     | _     | 120      | ns    |

| t <sub>HR</sub>   | Input Data Hold After RD       | 0         | -          | 0    | _       | 0     | -        | ns    |

| t <sub>WW</sub>   | WR Low width                   | 2.5x - 40 | -          | 210  | -       | 160   | -        | ns    |

| t <sub>DW</sub>   | Data Setup to WR               | 2x - 50   | -          | 150  | -       | 110   | -        | ns    |

| t <sub>WD</sub>   | Data Hold After WR             | 20        | 90         | 20   | 90      | 20    | 90       | ns    |

| t <sub>CWA</sub>  | RD, WR to Valid WAIT           | -         | 1.5x - 100 | -    | 50      | _     | 20       | ns    |

| t <sub>AWA</sub>  | Address to Valid WAIT          | -         | 2.5x - 130 | -    | 120     | _     | 70       | ns    |

| t <sub>WAS</sub>  | WAIT Setup to CLK              | 70        | _          | 70   | _       | 70    | _        | ns    |

| t <sub>WAH</sub>  | WAIT Hold After CLK            | 0         | _          | 0    | _       | 0     | _        | ns    |

| t <sub>RV</sub>   | RD/WR Recovery Time            | 1.5x - 35 | -          | 115  | _       | 85    | _        | ns    |

| t <sub>CPW</sub>  | CLK to Port Data Output        | _         | x + 200    | _    | 300     | _     | 260      | ns    |

| t <sub>PRC</sub>  | Port Data Setup to CLK         | 200       | -          | 200  | _       | 200   | _        | ns    |

| t <sub>CPR</sub>  | Port Data Hold After CLK       | 100       | -          | 100  | _       | 100   | _        | ns    |

| t <sub>CHCL</sub> | RD/WR Hold After CLK           | x - 60    | _          | 40   | _       | 20    | _        | ns    |

| t <sub>CLC</sub>  | RD/WR Setup to CLK             | 1.5x - 50 | -          | 100  | _       | 70    | _        | ns    |

| t <sub>CLHA</sub> | Address Hold After CLK         | 1.5x - 80 | _          | 70   | _       | 40    | _        | ns    |

| t <sub>ACL</sub>  | Address Setup to CLK           | 2.5x - 80 | _          | 170  | _       | 120   | _        | ns    |

| t <sub>CLD</sub>  | Data Setup to CLK              | x - 50    | _          | 50   | _       | 30    | _        | ns    |

<sup>•</sup> AC output level High 2.2V/Low 0.8V

High 0.8V<sub>CC</sub>/Low 0.2V<sub>CC</sub> (excluding D0 – D7)

<sup>•</sup> AC input level High 2.4V/Low 0.45V (D0 – D7)

#### 4.4 Zero - Cross Characteristics

$V_{CC} = 5V \pm 10\% \ TA = -40 \sim 85^{\circ}C \ (1 \sim 10MHz)$   $TA = -20 \sim 70^{\circ}C \ (1 \sim 12.5MHz)$

| Symbol          | Parameter                            | Condition                   | Min  | Max | Unit      |

|-----------------|--------------------------------------|-----------------------------|------|-----|-----------|

| V <sub>ZX</sub> | Zero-cross detection input           | AC coupling $C = 0.1 \mu F$ | 1    | 1.8 | VAC p - p |

| A <sub>ZX</sub> | Zero-cross accuracy                  | 50/60Hz sine wave           | _    | 135 | mV        |

| F <sub>ZX</sub> | Zero-cross detection input frequency | _                           | 0.04 | 1   | KHz       |

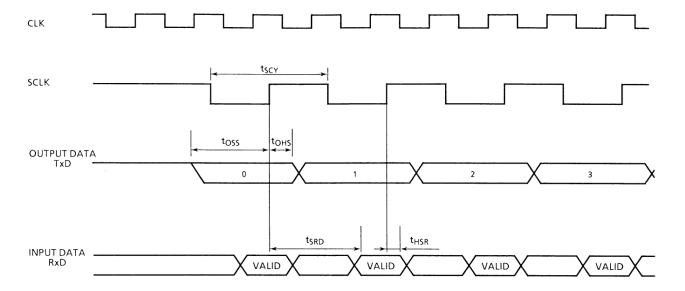

## 4.5 Serial Channel Timing - I/O Interface Mode

$V_{CC} = 5V \pm 10\% \ TA = -40 \sim 85^{\circ}C \ (1 \sim 10 MHz) \\ CL = 50 pF \ TA = -20 \sim 70^{\circ}C \ (1 \sim 12.5 MHz)$

| Symbol           | Parameter                               | Variable |          | 10MHz Clock |     | 12.5MHz Clock |     | Unit  |

|------------------|-----------------------------------------|----------|----------|-------------|-----|---------------|-----|-------|

| Symbol           | raiailletei                             | Min      | Max      | Min         | Max | Min           | Max | Uiiii |

| t <sub>SCY</sub> | Serial Port Clock Cycle Time            | 8x       | -        | 800         | -   | 640           | -   | ns    |

| t <sub>OSS</sub> | Output Data Setup SCLK Rising Edge      | 6x - 150 | -        | 450         | -   | 330           | -   | ns    |

| t <sub>OHS</sub> | Output Data Hold After SCLK Rising Edge | 2x - 120 | -        | 80          | -   | 40            | -   | ns    |

| t <sub>HSR</sub> | Input Data Hold After SCLK Rising Edge  | 0        | -        | 0           | -   | 0             | -   | ns    |

| t <sub>SRD</sub> | SCLK Rising Edge to Input DATA Valid    | -        | 6x - 150 | -           | 450 | -             | 330 | ns    |

### 4.6 8-bit Event Counter

| Symbol Parameter  | Variable                   |          | 10MHz Clock |     | 12.5MHz Clock |     | Unit |       |

|-------------------|----------------------------|----------|-------------|-----|---------------|-----|------|-------|

| Syllibul          | raiailletei                | Min      | Max         | Min | Max           | Min | Max  | UIIIL |

| t <sub>VCK</sub>  | TI4 clock cycle            | 8x + 100 | -           | 900 | -             | 740 | -    | ns    |

| t <sub>VCKL</sub> | TI4 Low clock pulse width  | 4x + 40  | -           | 440 | _             | 360 | -    | ns    |

| t <sub>VCKH</sub> | TI4 High clock pulse width | 4x + 40  | -           | 440 | -             | 360 | -    | ns    |

### 4.7 Interrupt Operation

| Symbol             | Parameter                         | Var      | Variable |     | 10MHz Clock |     | 12.5MHz Clock |      |

|--------------------|-----------------------------------|----------|----------|-----|-------------|-----|---------------|------|

|                    | rarameter                         | Min      | Max      | Min | Max         | Min | Max           | Unit |

| t <sub>INTAL</sub> | NMI, INTO Low level pulse width   | 4x       | -        | 400 | -           | 320 | -             | ns   |

| t <sub>INTAH</sub> | NMI, INTO High level pulse width  | 4x       | -        | 400 | -           | 320 | -             | ns   |

| t <sub>INTBL</sub> | INT1, INT2 Low level pulse width  | 8x + 100 | -        | 900 | -           | 740 | -             | ns   |

| t <sub>INTBH</sub> | INT1, INT2 High level pulse width | 8x + 100 | -        | 900 | _           | 740 | _             | ns   |

TOSHIBA CORPORATION 11/14

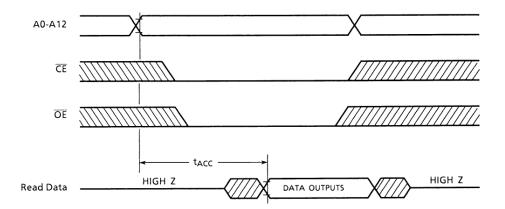

## 4.8 Read Operation (PROM Mode)

## DC Characteristic, AC Characterisc

TA =  $-40 \sim 85^{\circ}$ C Vcc = 5V  $\pm 10\%$

| Symbol           | Parameter                                                         | Condition             | Min                   | Max                 | Unit |

|------------------|-------------------------------------------------------------------|-----------------------|-----------------------|---------------------|------|

| V <sub>PP</sub>  | VPP Read Voltage                                                  | -                     | 4.5                   | 5.5                 | V    |

| V <sub>IH1</sub> | Input High Voltage (A0 ~ A15, $\overline{CE}$ , $\overline{OE}$ ) | -                     | 0.7 x V <sub>CC</sub> | Vcc + 0.3           | V    |

| V <sub>IL1</sub> | Input Low Voltage (A ~ A15, $\overline{CE}$ , $\overline{OE}$ )   | -                     | -0.3                  | $0.3 \times V_{CC}$ | V    |

| t <sub>ACC</sub> | Address to Output Delay                                           | C <sub>L</sub> = 50pf | 2.25TCYC + α          |                     | ns   |

TCYC = 400ns (10MHz Clock)

$\alpha$  = 200ns

## 4.9 Programming Operation (PROM Mode)

# DC Characteristic, AC Characteristic

TA = 25  $\pm\,5^{\circ}$  C Vcc = 6V  $\pm\,0.25$  V

| Symbol           | Parameter                                                                      | Condition         | Min                      | Тур   | Max                      | Unit |

|------------------|--------------------------------------------------------------------------------|-------------------|--------------------------|-------|--------------------------|------|

| $V_{PP}$         | Programming Voltage                                                            | -                 | 12.25                    | 12.50 | 12.75                    | V    |

| V <sub>IH</sub>  | Input High Voltage (D0 ~ D7)                                                   | _                 | 0.2V <sub>CC</sub> + 1.1 |       | V <sub>CC</sub> + 0.3    | V    |

| V <sub>II</sub>  | Input Low Voltage (D0 ~ D7)                                                    | _                 | -0.3                     |       | 0.2V <sub>CC</sub> - 0.1 | V    |

| V <sub>IH1</sub> | Input High Voltage (A0 ~ A15, $\overline{CE}$ , $\overline{OE}$ )              | _                 | 0.7V <sub>CC</sub>       |       | V <sub>CC</sub> + 0.3    | V    |

| $V_{IL1}$        | Input Low Voltage (A0 ~ A15, $\overline{\text{CE}}$ , $\overline{\text{OE}}$ ) | _                 | -0.3                     |       | 0.3V <sub>CC</sub>       | V    |

| I <sub>CC</sub>  | V <sub>CC</sub> Supply Current                                                 | $t_{OSC} = 10MHz$ | -                        |       | 50                       | mA   |

| I <sub>PP</sub>  | V <sub>PP</sub> Supply Current                                                 | $V_{PP} = 13.00V$ | _                        |       | 50                       | mA   |

| t <sub>PW</sub>  | CE Programming Pulse Width                                                     | $C_L = 50_P^F$    | 0.95                     | 1.00  | 1.05                     | ms   |

## 4.10 I/O Interface Mode Timing

12/14 TOSHIBA CORPORATION

# 4.11 Timing Chart

# 4.12 Read Operation Timing Chart (PROM Mode)

TOSHIBA CORPORATION 13/14

# 4.13 Programming Operation Timing Chart (PROM Mode)