# R2J20701NP

## Peak Current Mode Synchronous Buck Controller with Power MOS FETs

REJ03G1459-0300

Rev.3.00

Jun 20, 2007

### Description

This all-in-one SiP for POL (point-of-load) applications is a multi-chip module incorporating a high-side MOS FET, low-side MOS FET, and PWM controller in a single QFN package. The on and off timing of the power MOS FET is optimized by the built-in driver circuit, making this device suitable for large-current high-efficiency buck converters.

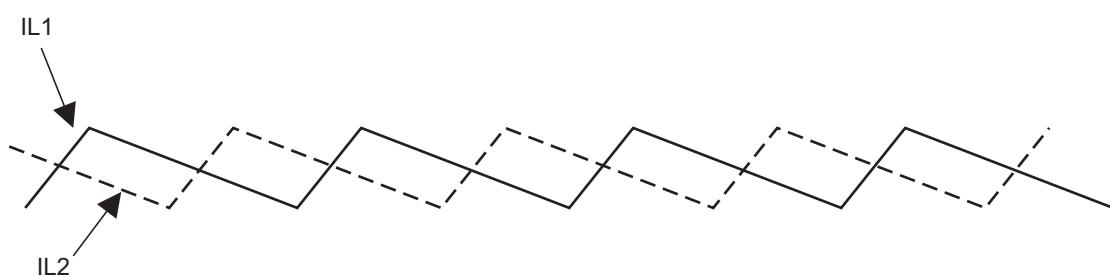

In a simple peak-current mode topology, stable operation is obtained in a closed power loop, and a fast converter is easily realized with the addition of simple components. Furthermore, the same topology can be applied to realize converters for parallel synchronized operation with current sharing, and two-phase operation.

The package also incorporates a high-side bootstrap Schottky barrier diode (SBD), eliminating the need for an external SBD for this purpose.

### Features

- Three chips in one package for high-efficiency and space saving

- Large average output current (35 A)

- Wide input voltage range: 8 to 14 V

- 0.6 V reference voltage accurate to within 1%

- Wide programmable switching frequency: 200 kHz to 1 MHz

- Fast response by peak-current-mode topology.

- Simple current sharing (up to five modules in parallel)

- Two-phase operation in parallel operation

- Built-in SBD for boot strapping

- On/off control

- Hiccup operation under over load condition

- Tracking function

- Thin small package: 56-pin QFN (8 mm × 8 mm)

### Applications

- Network equipment

- Telecommunications equipment

- Servers

- POL modules

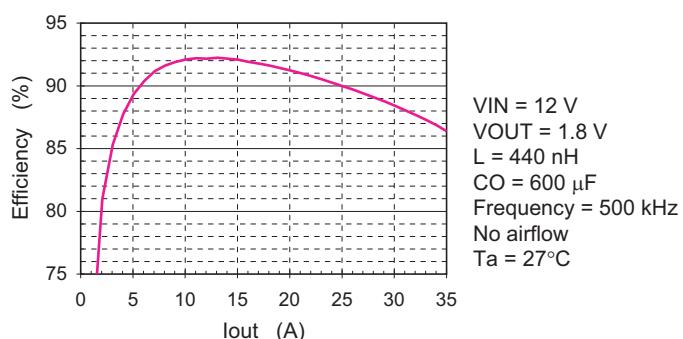

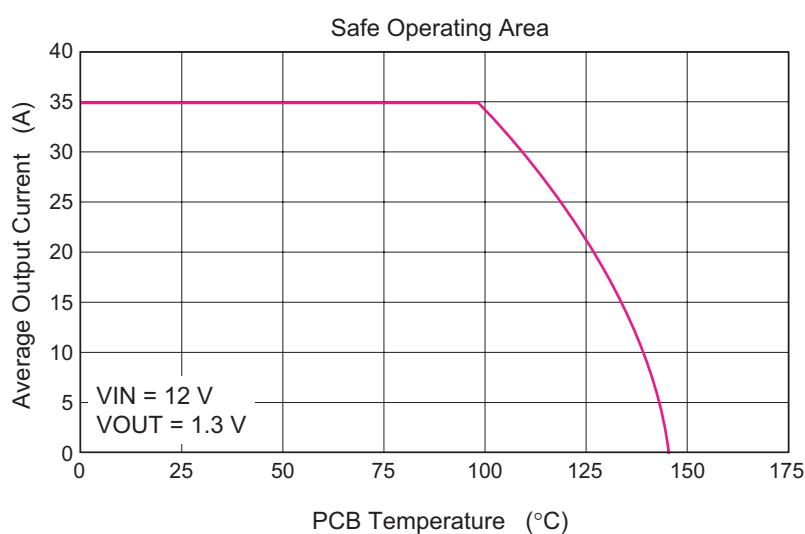

### Typical Characteristic Curve

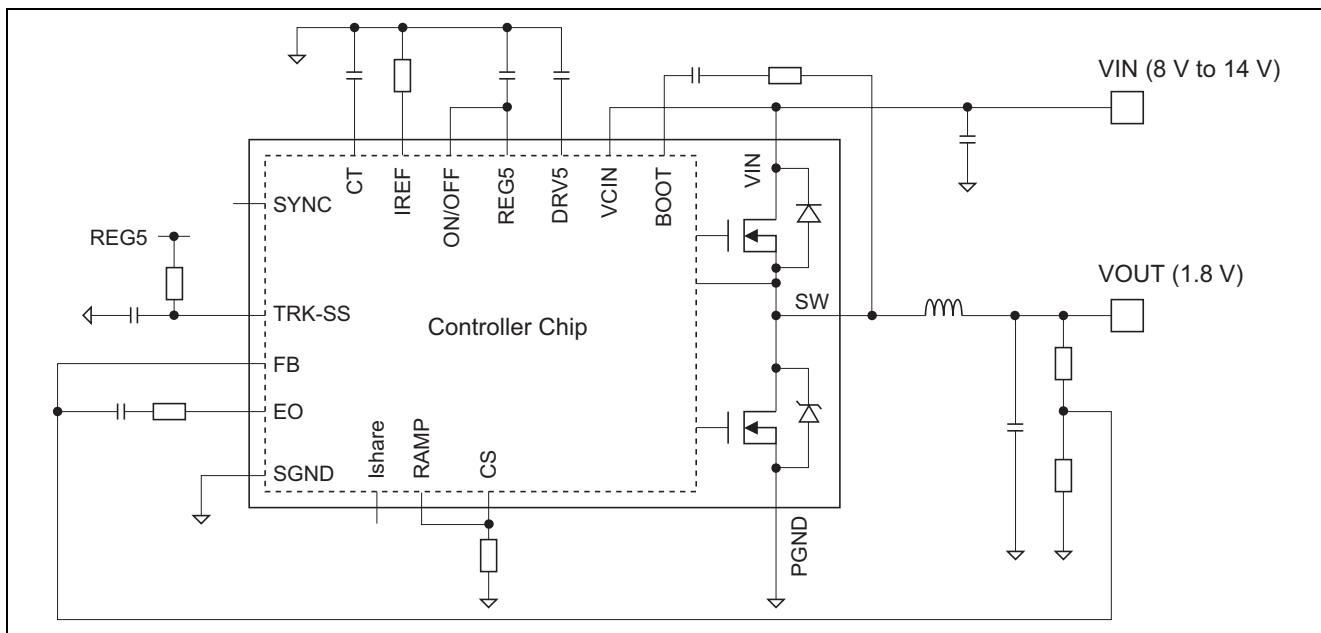

## Application Circuit Example

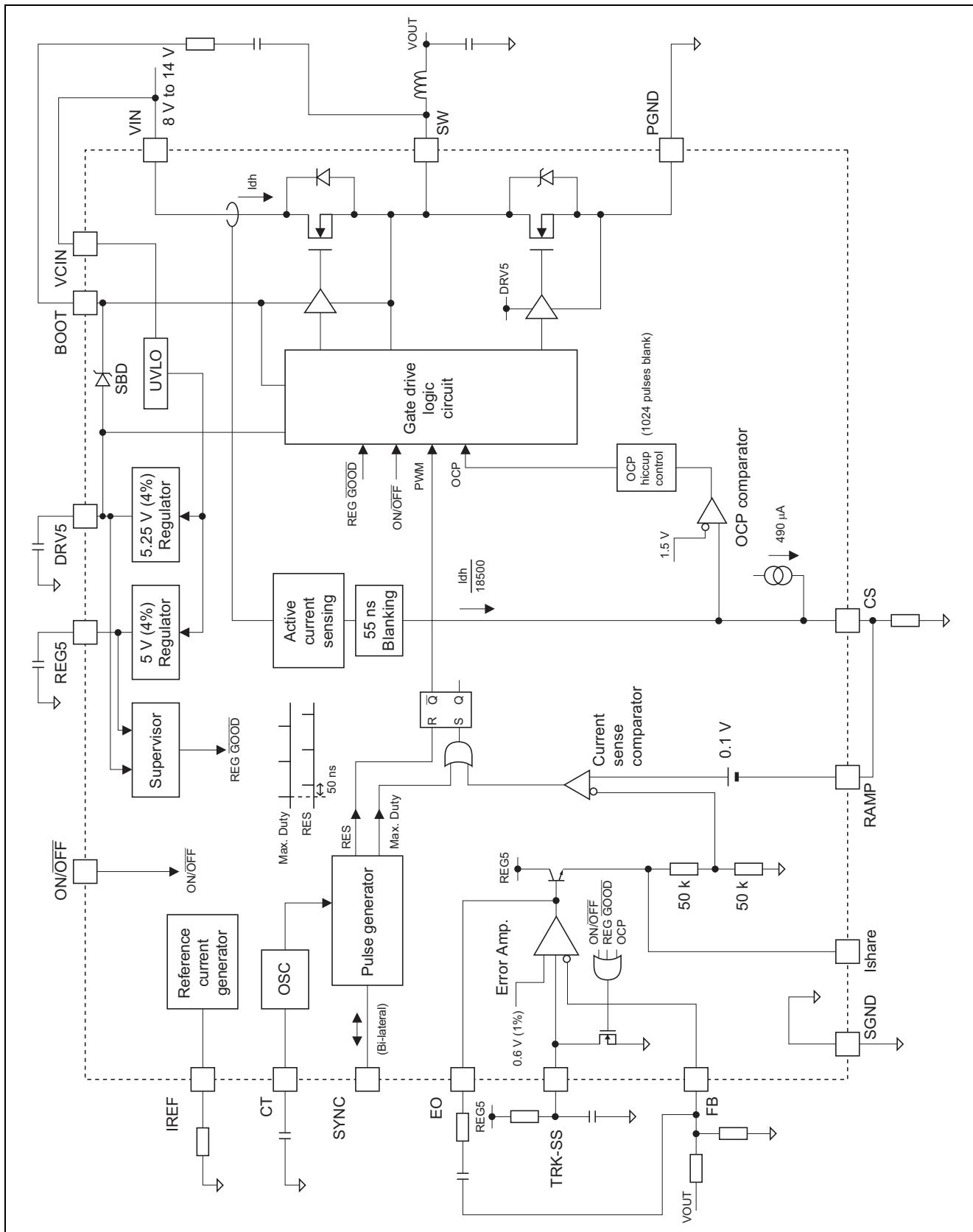

## Block Diagram

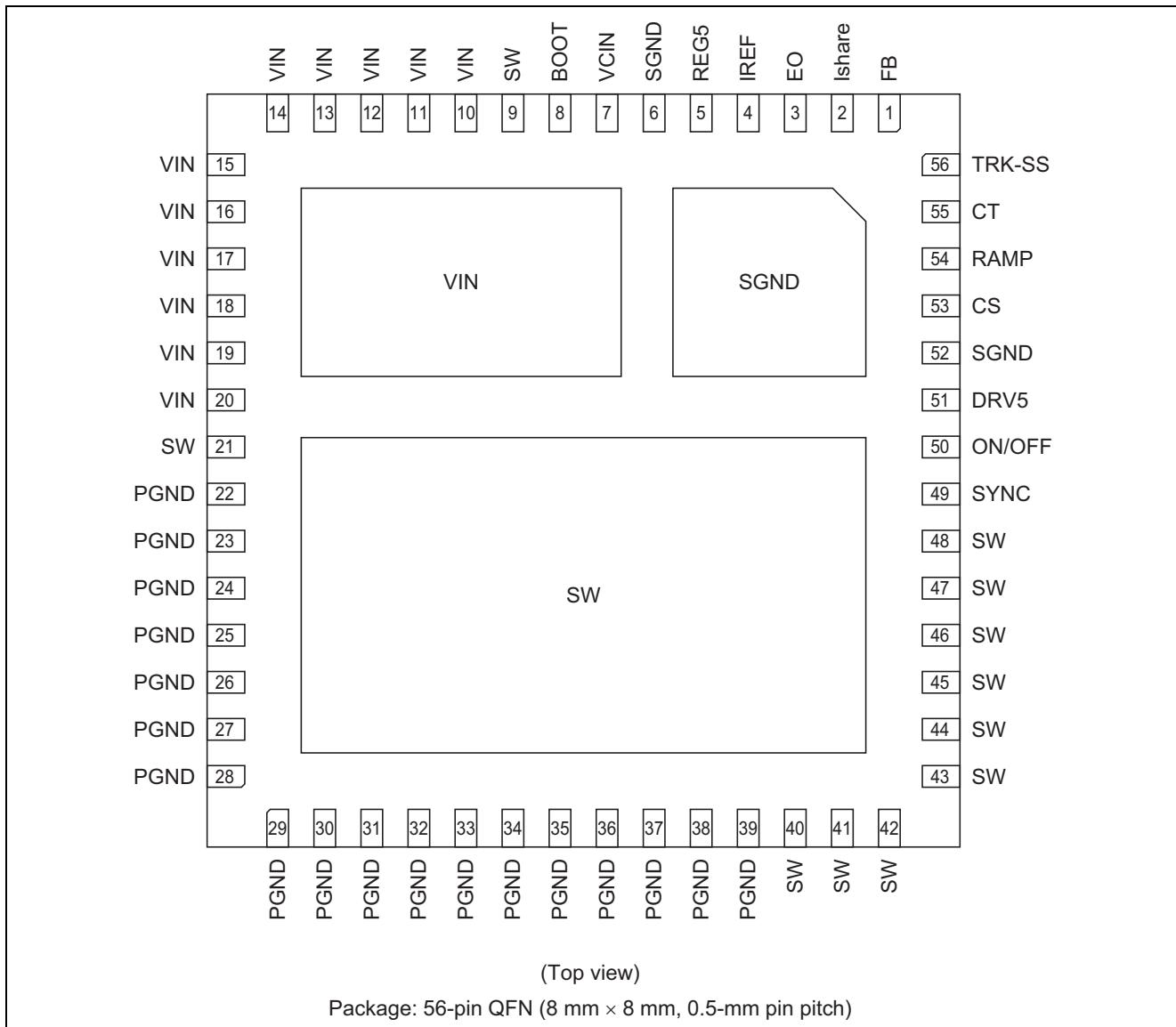

## Pin Arrangement

Note: All die-pads (three pads in total) should be soldered to PCB.

## Pin Description

| Pin Name | Pin No.         | Description                                                                                          | Remarks                                                                                  |

|----------|-----------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| VIN      | 10 to 20        | Input voltage for the buck converter.                                                                |                                                                                          |

| SW       | 9, 21, 40 to 48 | Switching node. Connect a choke coil between the SW pin and dc output node of the converter.         |                                                                                          |

| PGND     | 22 to 39        | Ground of the power stage.                                                                           | Should be externally connected to SGND.                                                  |

| SGND     | 6, 52           | Ground of the IC chip.                                                                               | Should be externally connected to PGND.                                                  |

| VCIN     | 7               | Input voltage for the control circuit.                                                               | Should be externally connected to VIN.                                                   |

| BOOT     | 8               | Bootstrap voltage pin. A bootstrap capacitor should be connected between the BOOT and SW pin.        | To be supplied +5 V through the internal SBD.                                            |

| REG5     | 5               | +5 V logic power-supply output.                                                                      | Requires decoupling from the GND plane by a capacitance 0.1 $\mu$ F.                     |

| ON/OFF   | 50              | Signal disable pin.                                                                                  | Disabled when ON/OFF pin is in the low state.                                            |

| IREF     | 4               | Reference current generator for the IC.                                                              | Should be connected via 27 k $\Omega$ to the SGND pin.                                   |

| CT       | 55              | Timing capacitor pin for the oscillator. This pin has a select function for operation in slave mode. | If the pin voltage is <1 V or >4 V, the IC operates in slave mode.                       |

| SYNC     | 49              | I/O pin for synchronous operation.                                                                   |                                                                                          |

| TRK-SS   | 56              | Start-up timing control input.                                                                       |                                                                                          |

| FB       | 1               | Feedback voltage input for the closed loop.                                                          |                                                                                          |

| EO       | 3               | Error amplifier output pin.                                                                          | Requires connection to an RC circuit for loop compensation.                              |

| Ishare   | 2               | For current-sharing bus.                                                                             | Simply connect the Ishare pins of all devices to get balanced current.                   |

| RAMP     | 54              | RAMP signal input pin for peak current mode PWM control.                                             |                                                                                          |

| CS       | 53              | Current output pin of active current sensing circuit.                                                | Appropriate resistance is required between CS and the GND plane.                         |

| DRV5     | 51              | +5.25 V generator output for driving power MOS FETs.                                                 | Requires decoupling from the GND plane by a capacitance from 0.1 $\mu$ F to 1.0 $\mu$ F. |

**Absolute Maximum Ratings**

(Ta = 25°C)

| Item                           | Symbol              | Rating               | Unit | Note |

|--------------------------------|---------------------|----------------------|------|------|

| Power dissipation              | Pt(25)              | 25                   | W    | 1    |

|                                | Pt(100)             | 8                    |      | 1    |

| Average output current         | Iout                | 35                   | A    |      |

| Input voltage                  | Vin (dc), Vcin (dc) | -0.3 to +16          | V    | 2    |

|                                | Vin (ac), Vcin (ac) | 20                   |      | 2, 4 |

| Switch node voltage            | Vsw (dc)            | 16                   | V    | 2    |

|                                | Vsw (ac)            | 20                   |      | 2, 4 |

| BOOT pin voltage               | Vboot (dc)          | 22                   | V    | 2    |

|                                | Vboot (ac)          | 25                   |      | 2, 4 |

| ON/OFF pin voltage             | Von/off             | -0.3 to VIN          | V    | 2    |

| SYNC pin voltage               | Vsync               | -0.3 to +5.5         | V    | 2    |

| Voltage on other pins          | Vic                 | -0.3 to (REG5 + 0.3) | V    | 2    |

| REG5 current                   | Ireg5               | -10 to 0             | mA   | 3    |

| Ishare current                 | Ishare              | -500 to 0            | µA   | 3    |

| TRK-SS dc current              | Itrk                | 0 to 1               | mA   | 3    |

| IREF current                   | Iref                | -120 to 0            | µA   | 3    |

| EO sink current                | Ieo                 | 0 to 2               | mA   | 3    |

| Operating junction temperature | Tj-opr              | -40 to +150          | °C   |      |

| Storage temperature            | Tstg                | -55 to +150          | °C   |      |

Notes: 1. Pt(25) represents a PCB temperature of 25°C, and Pt(100) represents 100°C.

2. Rated voltages are relative to voltages on the SGND and PGND pins.

3. For rated current, (+) indicates inflow to the chip and (–) indicates outflow.

4. Ratings for which "ac" is indicated are limited to within 100 ns.

## Electrical Characteristics

(Ta = 25°C, VIN = VCIN = 12 V, unless otherwise specified)

| Item                              |                                           | Symbol    | Min  | Typ                 | Max  | Unit | Test Conditions                 |

|-----------------------------------|-------------------------------------------|-----------|------|---------------------|------|------|---------------------------------|

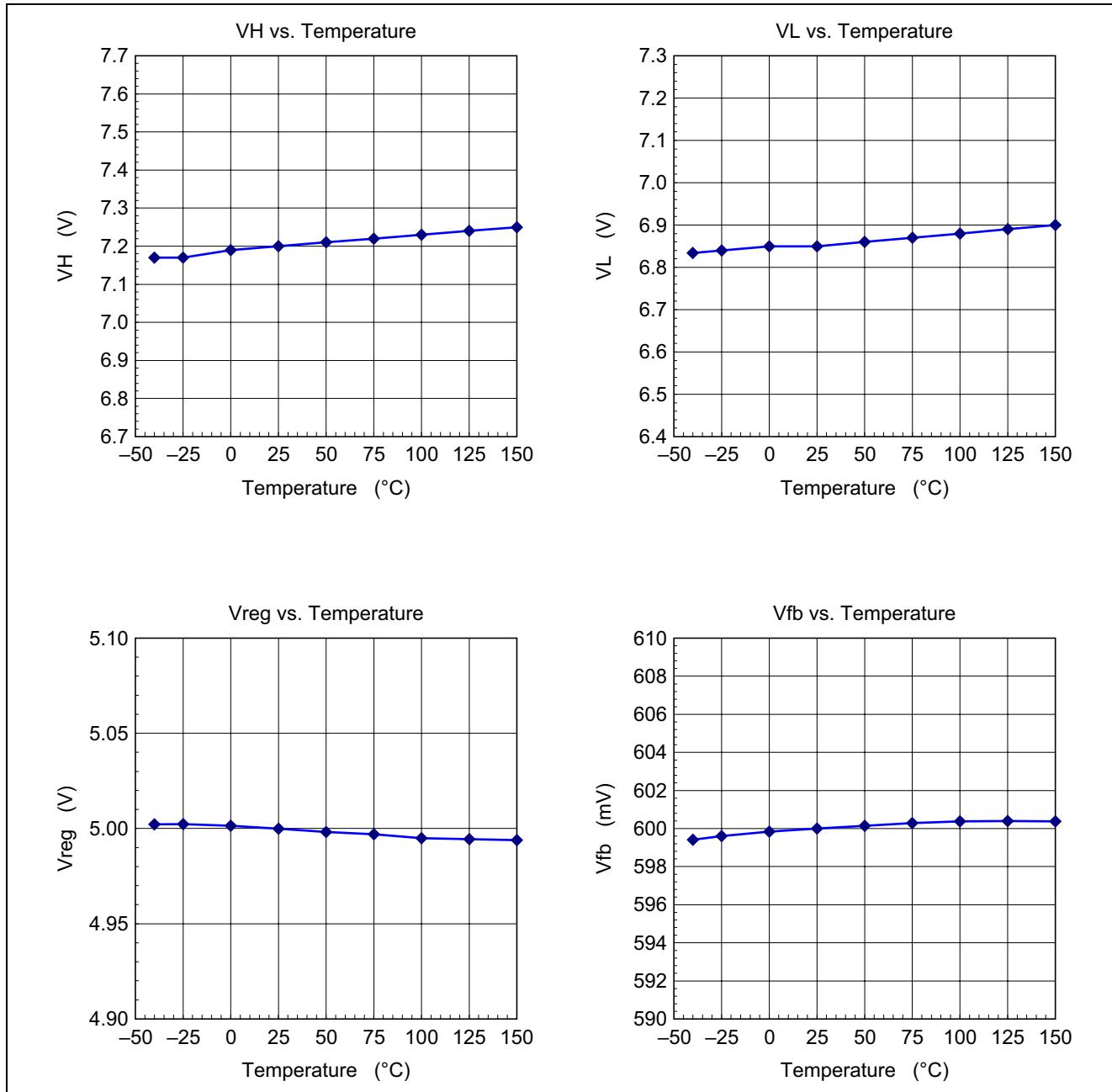

| Supply                            | VIN start threshold                       | VH        | 6.8  | 7.2                 | 7.6  | V    |                                 |

|                                   | VIN shutdown threshold                    | VL        | 6.45 | 6.85                | 7.25 | V    |                                 |

|                                   | UVLO hysteresis                           | dUVL      | —    | 0.35 * <sup>1</sup> | —    | V    |                                 |

|                                   | Input bias current                        | Iin       | 36   | 73                  | 110  | mA   | CT = 68 pF,<br>Duty cycle = 50% |

|                                   | Input shutdown current                    | Isd       | 3.0  | 4.5                 | 6.0  | mA   | On/off = 0 V                    |

| 5-V<br>regulator                  | Output voltage                            | Vreg      | 4.8  | 5.0                 | 5.2  | V    |                                 |

|                                   | Line regulation                           | Vreg-line | -5   | 0                   | +5   | mV   | VIN = 10 to 16 V                |

|                                   | Load regulation                           | Vreg-load | -8   | -3                  | +2   | mV   | Ireg = 0 to 10 mA               |

| 5.25-V<br>regulator               | Output voltage                            | Vdrv      | 5.04 | 5.25                | 5.46 | V    |                                 |

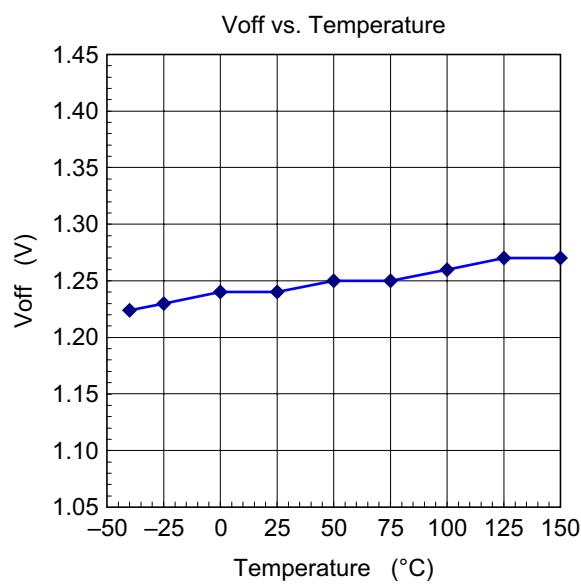

| Remote<br>On/off                  | Disable threshold                         | Voff      | 1.0  | 1.3                 | 1.6  | V    |                                 |

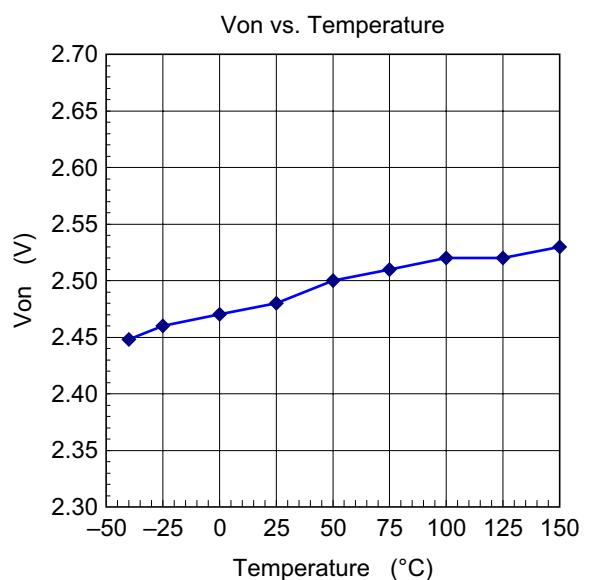

|                                   | Enable threshold                          | Von       | 2.0  | 2.5                 | 3.0  | V    |                                 |

|                                   | Input current                             | Ion/off   | 0.5  | 2.0                 | 5.0  | µA   | Von/off = 1 V                   |

| Reference<br>current<br>generator | IREF pin voltage                          | VIref     | 2.6  | 2.7                 | 2.8  | V    | Riref = 27 kΩ                   |

| Oscillator                        | CT oscillating frequency                  | Fct       | —    | 930 * <sup>1</sup>  | —    | kHz  | CT = 68 pF                      |

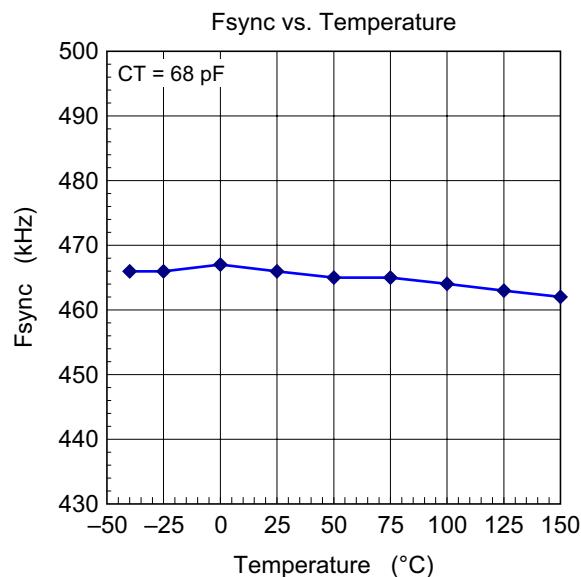

|                                   | SW switching frequency                    | Fsw       | 418  | 465                 | 512  | kHz  | CT = 68 pF                      |

|                                   | CT higher trip voltage                    | Vhct      | —    | 3 * <sup>1</sup>    | —    | V    | CT = 68 pF                      |

|                                   | CT lower trip voltage                     | VLct      | —    | 2 * <sup>1</sup>    | —    | V    | CT = 68 pF                      |

|                                   | CT source current                         | Ict-src   | -170 | -160                | -150 | µA   | CT = 1.5 V                      |

|                                   | CT sink current                           | Ict-snk   | 150  | 160                 | 170  | µA   | CT = 3.5 V                      |

|                                   | CT threshold for two-<br>phase operation  | Vct-two   | 3.6  | 4.0                 | 4.4  | V    |                                 |

|                                   | CT threshold for<br>synchronous operation | Vct-one   | 0.8  | 1.0                 | 1.2  | V    |                                 |

| SYNC and<br>pulse<br>generator    | SYNC frequency                            | Fsync     | 418  | 465                 | 512  | kHz  | CT = 68 pF                      |

|                                   | SYNC high voltage                         | Vh-sync   | 4.0  | 5.0                 | —    | V    | Rsync = 51 kΩ to GND            |

|                                   | SYNC low voltage                          | VL-sync   | 0    | —                   | 1.0  | V    | Rsync = 51 kΩ to REG5           |

|                                   | SYNC input threshold                      | Vsync     | 1.0  | 2.0                 | 3.0  | V    | CT = 0 V or 5 V                 |

| Error<br>amplifier                | Feedback voltage                          | Vfb       | 594  | 600                 | 606  | mV   | TRK-SS = 1 V                    |

|                                   | Input bias current                        | Ifb       | -0.1 | 0                   | +0.1 | µA   | FB = 0.6 V                      |

|                                   | Output source current                     | Io-src    | 150  | 200                 | 250  | µA   | EO = 4 V, FB = 0 V              |

|                                   | Output sink transient<br>current          | Io-snk    | 5.0  | 10.6                | 19.0 | mA   | EO = 1 V, FB = 1 V              |

|                                   | Voltage gain                              | Av        | —    | 80 * <sup>1</sup>   | —    | dB   |                                 |

|                                   | Band width                                | BW        | —    | 15 * <sup>1</sup>   | —    | MHz  |                                 |

|                                   | Resistance connected to<br>the Ishare pin | Rshare    | 70   | 100                 | 130  | kΩ   | EO = 0 V. Ishare = 1 V          |

Note: 1. These are reference values for design and have not been 100% tested in production.

(Ta = 25°C, VIN = VCIN = 12 V, unless otherwise specified)

| Item          |                                    | Symbol   | Min  | Typ                 | Max  | Unit | Test Conditions |

|---------------|------------------------------------|----------|------|---------------------|------|------|-----------------|

| Current sense | CS current ratio                   | Idh/lcs  | —    | 18500 <sup>*1</sup> | —    | —    |                 |

|               | Leading edge blanking time         | TLD      | —    | 55 <sup>*1</sup>    | —    | ns   |                 |

|               | CS comparator delay to output      | Td-cs    | —    | 50 <sup>*1</sup>    | —    | ns   |                 |

|               | OCP comparator threshold on CS pin | Vocp     | 1.43 | 1.5                 | 1.57 | V    |                 |

|               | Hiccup interval                    | Tocp     | 1.98 | 2.20                | 2.42 | ms   | CT = 68 pF      |

|               | RAMP offset voltage                | Vramp-dc | 77   | 92                  | 107  | mV   |                 |

|               | CS offset current                  | Ics-dc   | —    | 490 <sup>*1</sup>   | —    | µA   | CS = 0 V        |

Note: 1. These are reference values for design and have not been 100% tested in production.

## Description of Operation

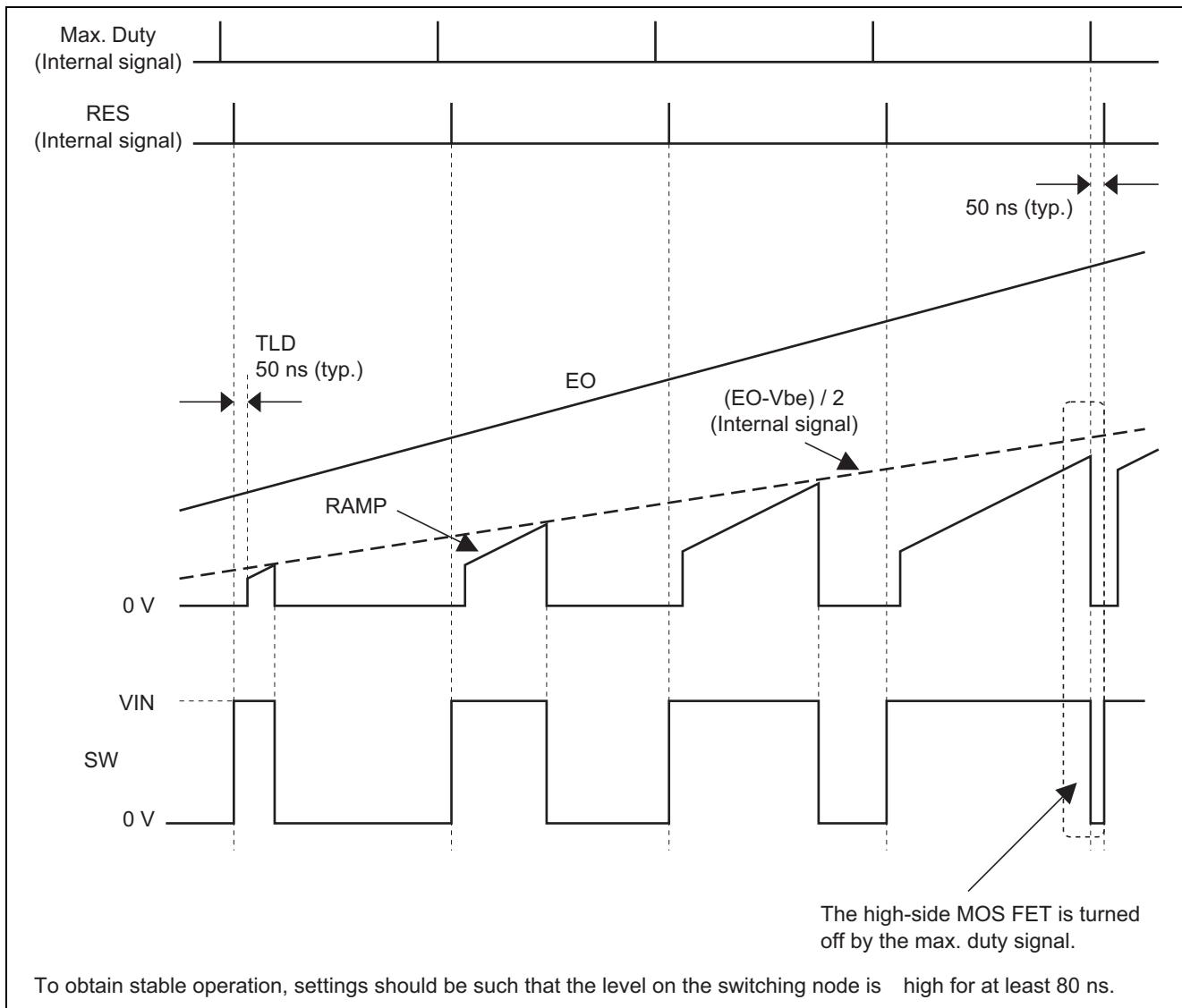

### Peak Current Control

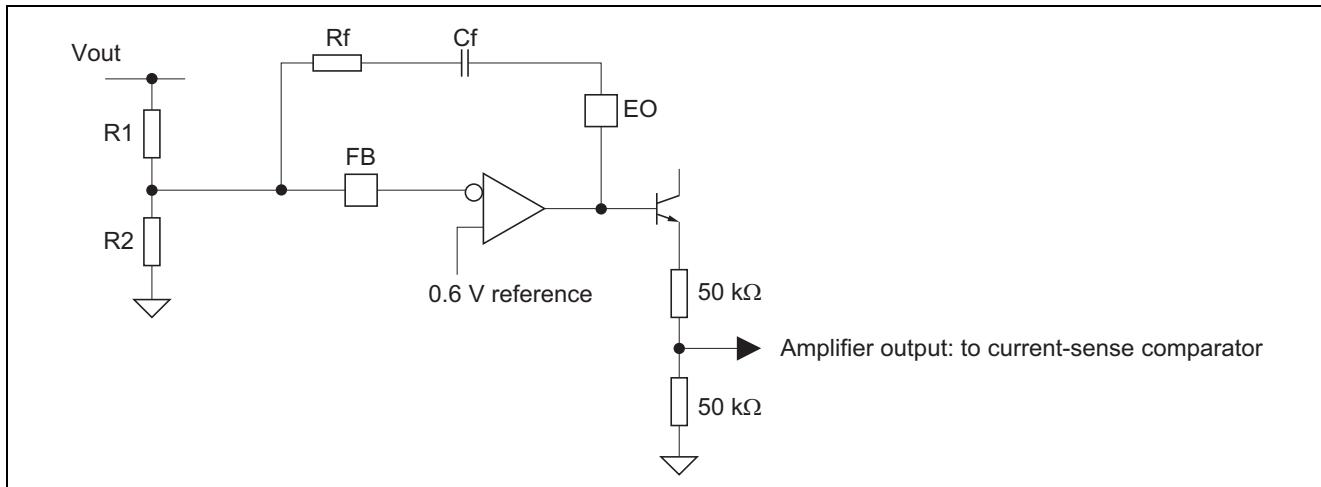

The control IC operates in a current-programmed control mode, in which the output of the converter is controlled by the choice of the peak current from the high-side MOS FET. The current from this MOS FET is sensed by an active current-sensing circuit (ACS), the output current of which is 1/18500 (54 ppm) of the MOS FET current. The ACS current is then converted to a certain voltage by the external resistor on the CS pin. The CS voltage is fed to the RAMP pin by an external connection, then compared with the current-control signal which is determined from the error amplifier output voltage (EO) via an NPN transistor and resistor network.

To start with, the RES pulse from the pulse generator resets a latch, then the high-side MOS FET is turned on. The latch output (Q bar) is toggled when the voltage on RAMP reaches the level of the current-control signal on EO, the high-side MOS FET is turned off, and the low-side MOS FET is turned off after a certain dead-time interval. The IC remains in this state until the arrival of the next RES pulse.

Since current information is used in the control loop, loop compensation design for the converter is simple and easy.

### Maximum Duty-Cycle Limitation

If the current-sense comparator output is not toggled 50-ns prior to the arrival of the next RES pulse, an internal maximum duty pulse is generated and forces toggling of the SR latch. So, the duty cycle of the high-side MOS FET is limited by the maximum duty period.

The maximum duty period of the high-side MOS FET depends on its switching frequency.

$$\text{Maximum duty period} = 1 - 50 \text{ ns} \times F_{sw}$$

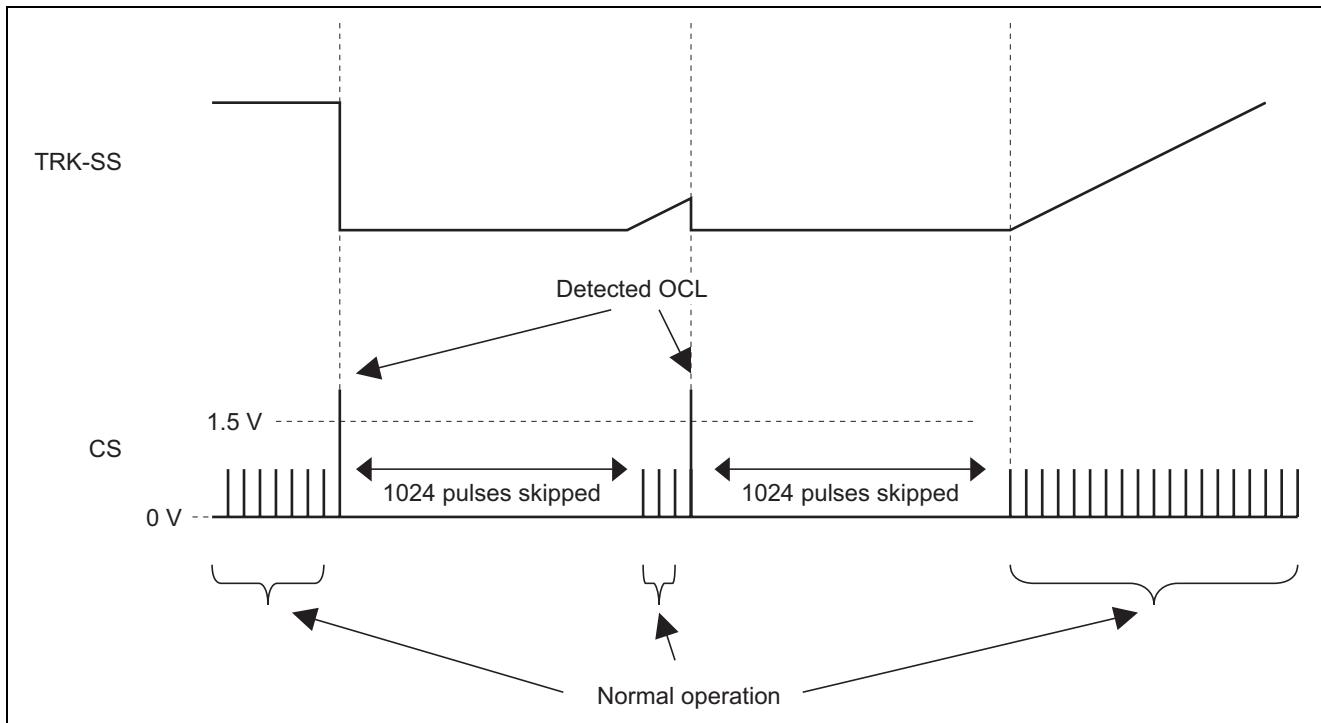

### OCP Hiccup Operation

Once the voltage of CS exceeds 1.5 V, OCP hiccup circuit disables switching operation of the IC and MOS FETs.

Internal circuitry also pulls the TRK-SS pin down to SGND. The IC is turned off for a period of 1024 RES pulses; after this has elapsed, switching operation of the IC is restarted from the soft-start state.

### UVLO and On/off Control

When VIN (=V<sub>cin</sub>) is below the start-up voltage, that is, is in the UVLO condition, functioning of the IC is disabled. The oscillator is turned off, both high- and low-side MOS FETs are turned off, and the TRK-SS pin is pulled down.

Furthermore, if the ON/OFF pin is in the low state or left open, functioning of the IC is disabled and both MOS FETs are turned off.

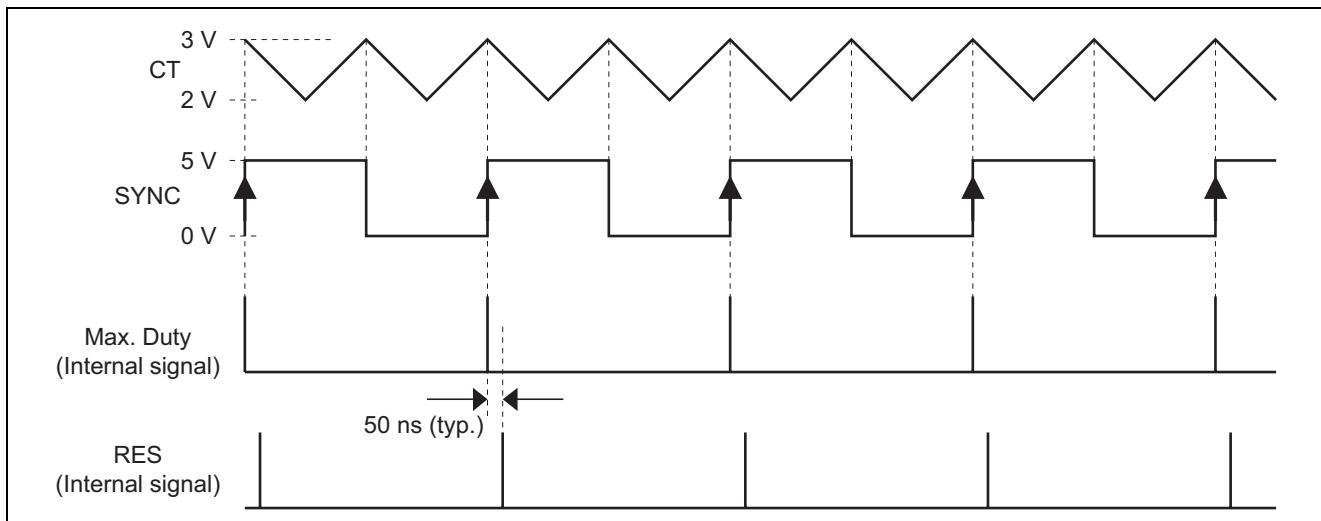

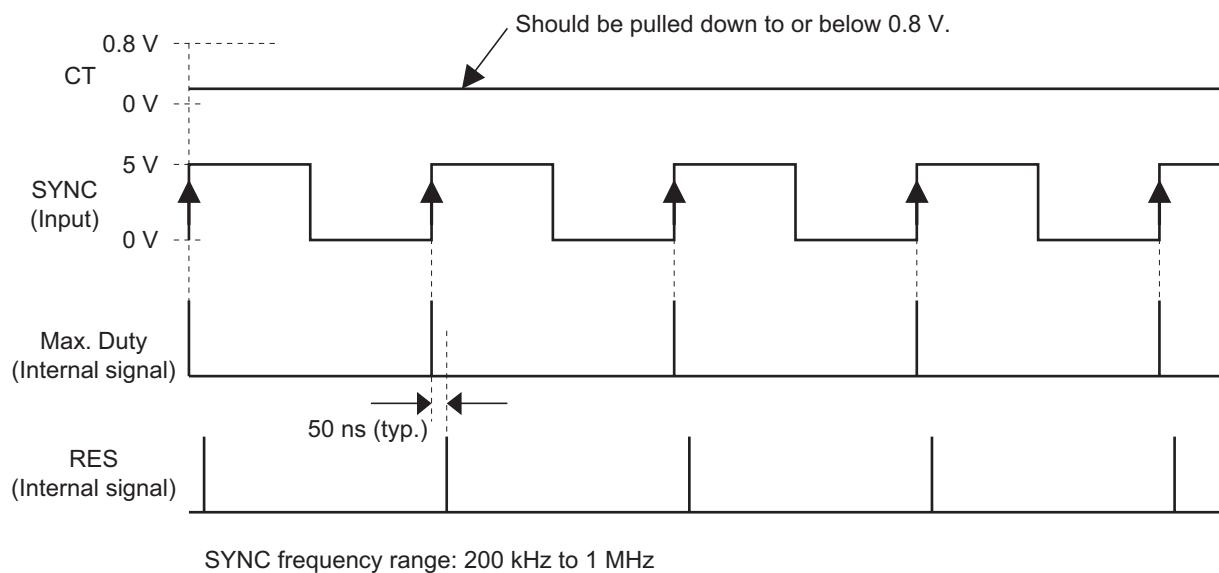

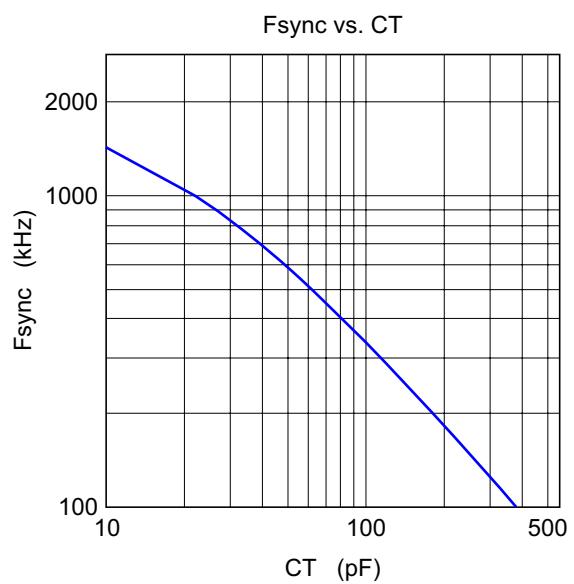

## Oscillator and Pulse Generator

The frequency of oscillation is set by the value of the external capacitor connected to the CT pin. This frequency is twice as high as the actual switching frequency. The frequencies are determined by the following equations:

$$\text{Oscillator frequency; } F_{ct} = 160 \mu\text{A} / \{2 \times (\text{CT}(F) + 18 \text{ pF}) \times 1 \text{ V}\} \quad (\text{in Hz})$$

$$\text{Switching frequency; } F_{sw} = 0.5 \times F_{ct} \quad (\text{Hz})$$

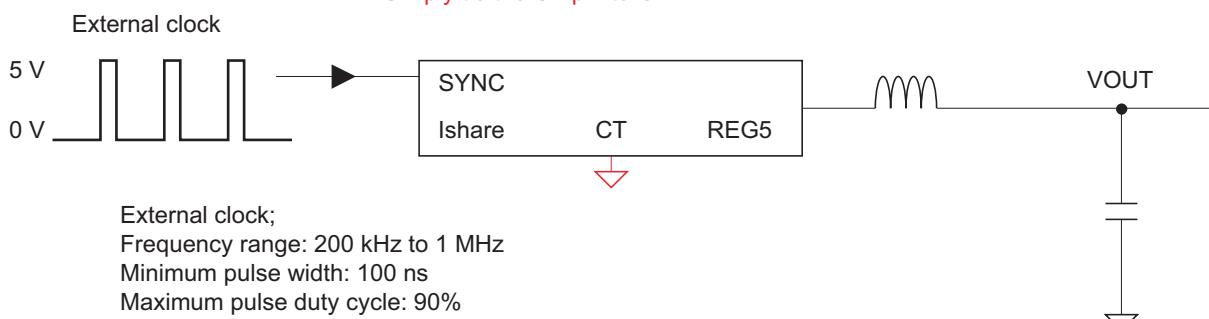

When the chip is operating in standalone mode or as the master chip for parallel operation, it requires a capacitor on the CT pin. In this case, the SYNC pin outputs a synchronization signal with a frequency of  $F_{sw}$ .

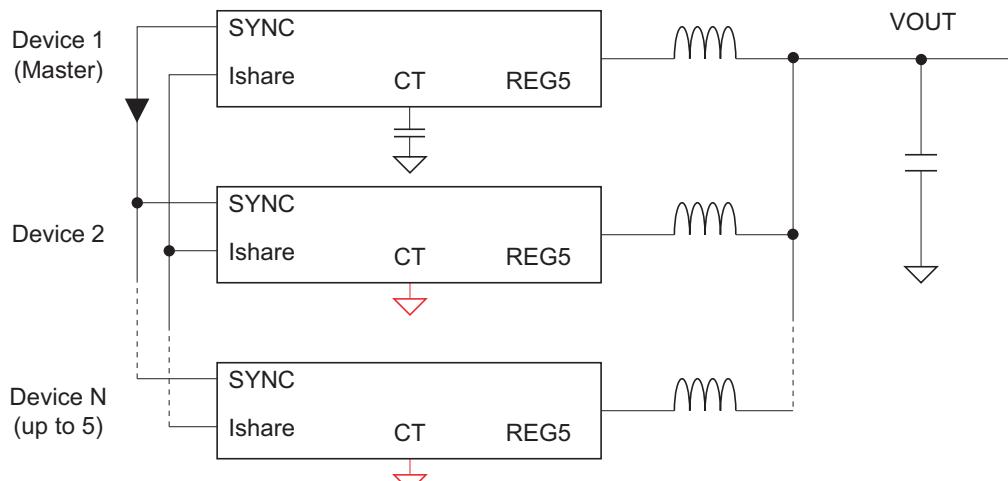

In operation as a slave chip, the CT pin must be connected to SGND or REG5, after which it acts as an input pin for the synchronized operation by external clock. The internal circuit is synchronized its rising edge when  $\text{CT} < 0.8 \text{ V}$ , falling edge when  $\text{CT} > 4.4 \text{ V}$ . In two-phase operation in parallel configuration, the CT pin should be at a voltage over 4.4 V.

| Item                  | Mode        |             |            |             |

|-----------------------|-------------|-------------|------------|-------------|

|                       | Standalone  | Master      | Slave -0°  | Slave -180° |

| CT pin                | Has a cap.  | Has a cap.  | < 0.8 V    | > 4.4 V     |

| SYNC pin              | Output mode | Output mode | Input mode | Input mode  |

| Synchronizing trigger | —           | —           | Rising     | Falling     |

The internal RES pulse and maximum duty-cycle-control pulses are produced from the signal at half the oscillator frequency in standalone and master operating modes. In slave mode, internal pulses are produced from the externally supplied input signal on the SYNC pin.

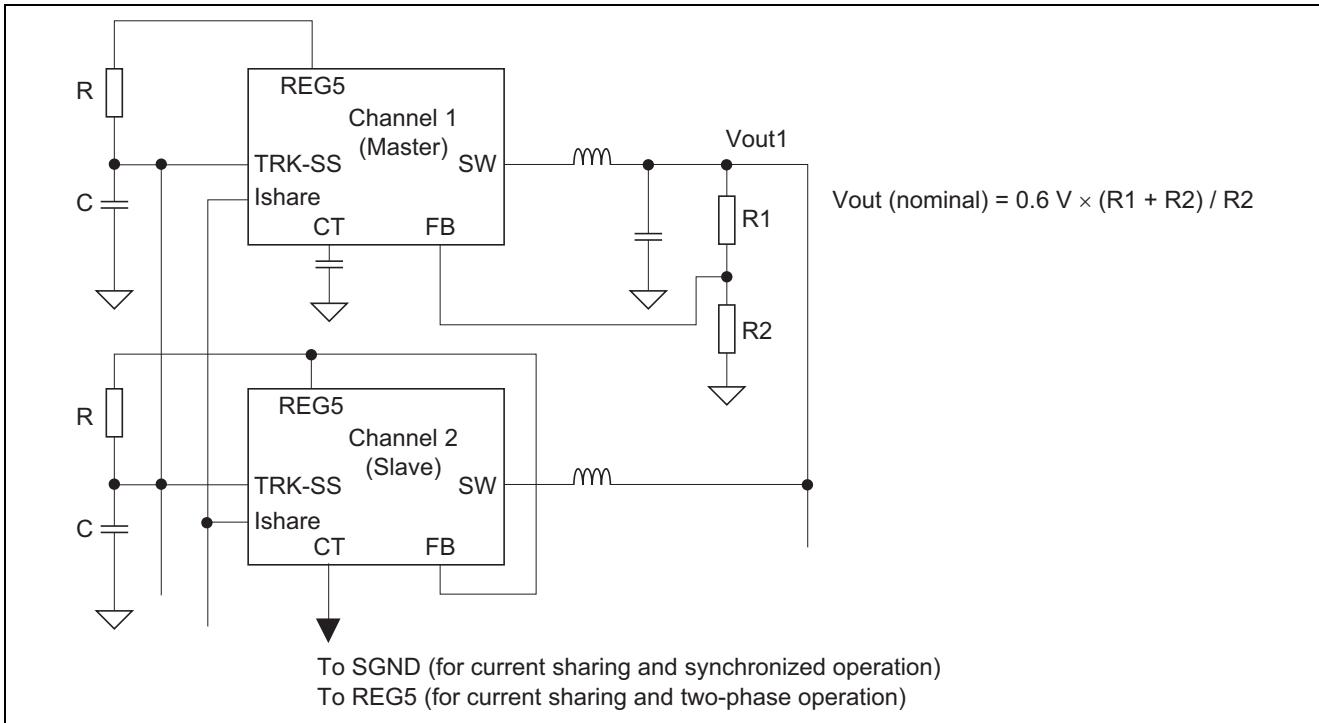

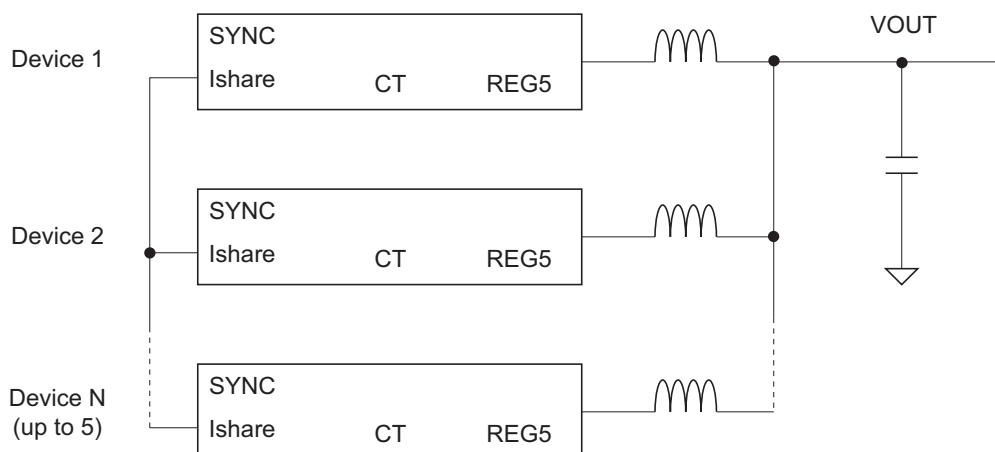

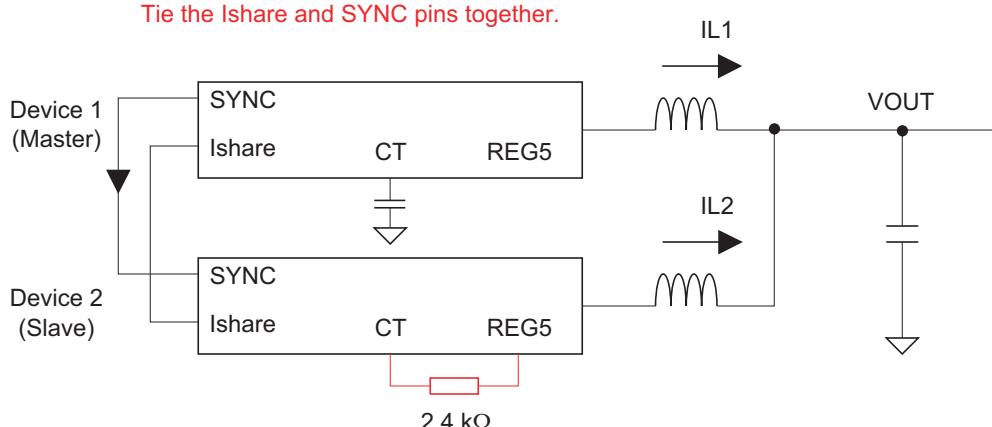

## Current Sharing

It is easy to obtain balanced-current operation in a parallel configuration due to the application of peak current control.

To obtain current-sharing operation, simply tie the buffered error-amplifier outputs of all of the devices (Ishare pins) together.

No more than five devices can operate in parallel.

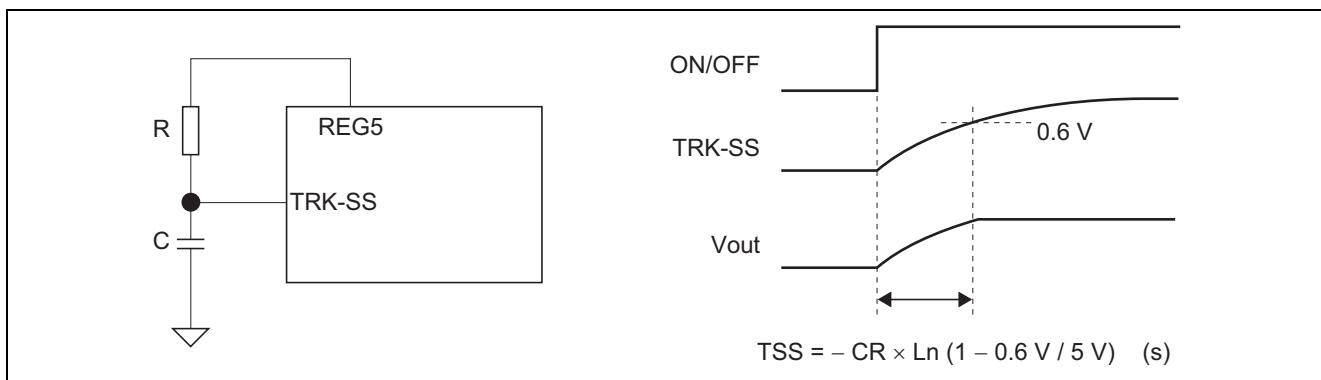

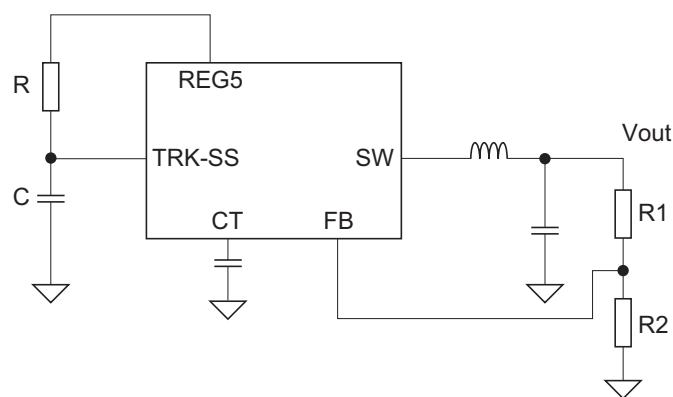

## Soft Start

Both simple soft starting and tracking start-up can be realized with the setup of the TRK-SS pin provided for soft-starts. The error amplifier has three inputs, two of which are designed to give priority to low-level non-inverting inputs for the amplifier. All that is required to realize soft-start operation is to simply attach an RC charging circuit to the TRK-SS pin.

The soft-start period is determined by the following equation, with C and R as the values for the RC charging circuit attached to the TRK-SS pin.

$$T_{ss} = -C \cdot R \cdot \ln(1 - 0.6 \text{ V} / \text{REG5}) \quad (\text{s})$$

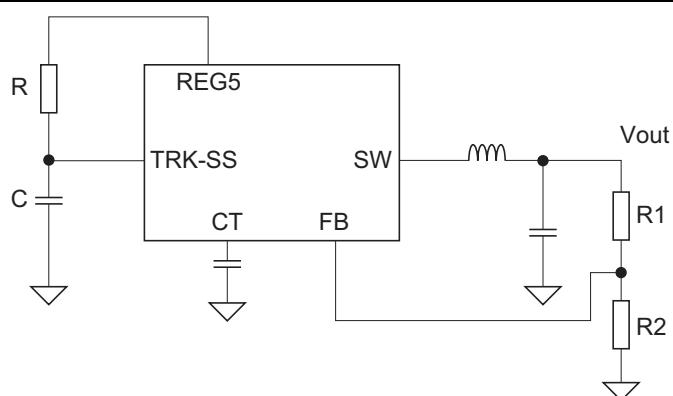

## Application Example

### Start-up Settings

Case 1) Standalone or master chip in parallel operation

With the RC network on the TRK-SS pin, the voltage on the pin should ramp up slowly.

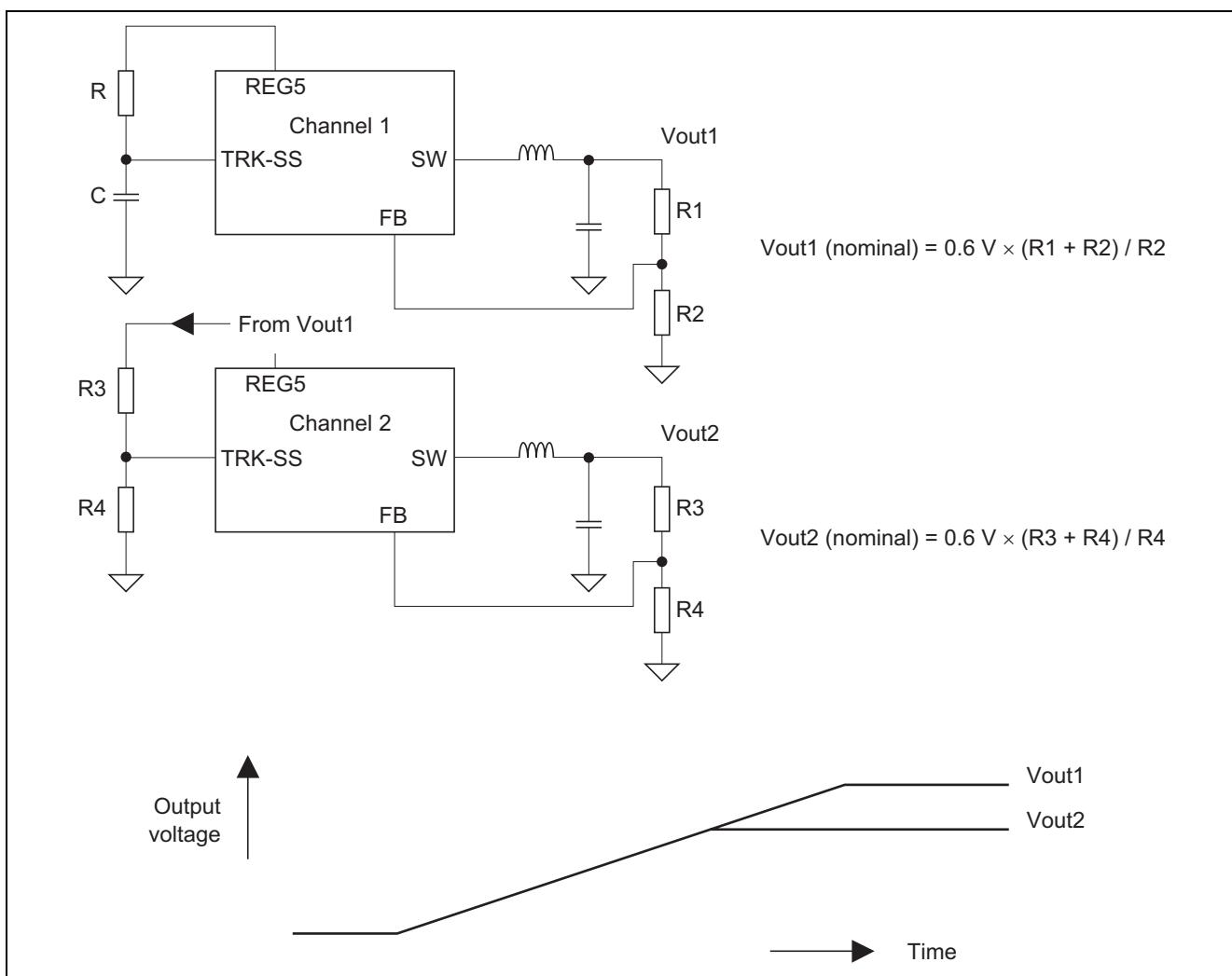

Case 2) Coincident tracking

The TRS-SS signal for channel two is the voltage from Vout1 after division by a resistor network. Vout1 must be greater than Vout2. Cross-talk is not generated between the channels.

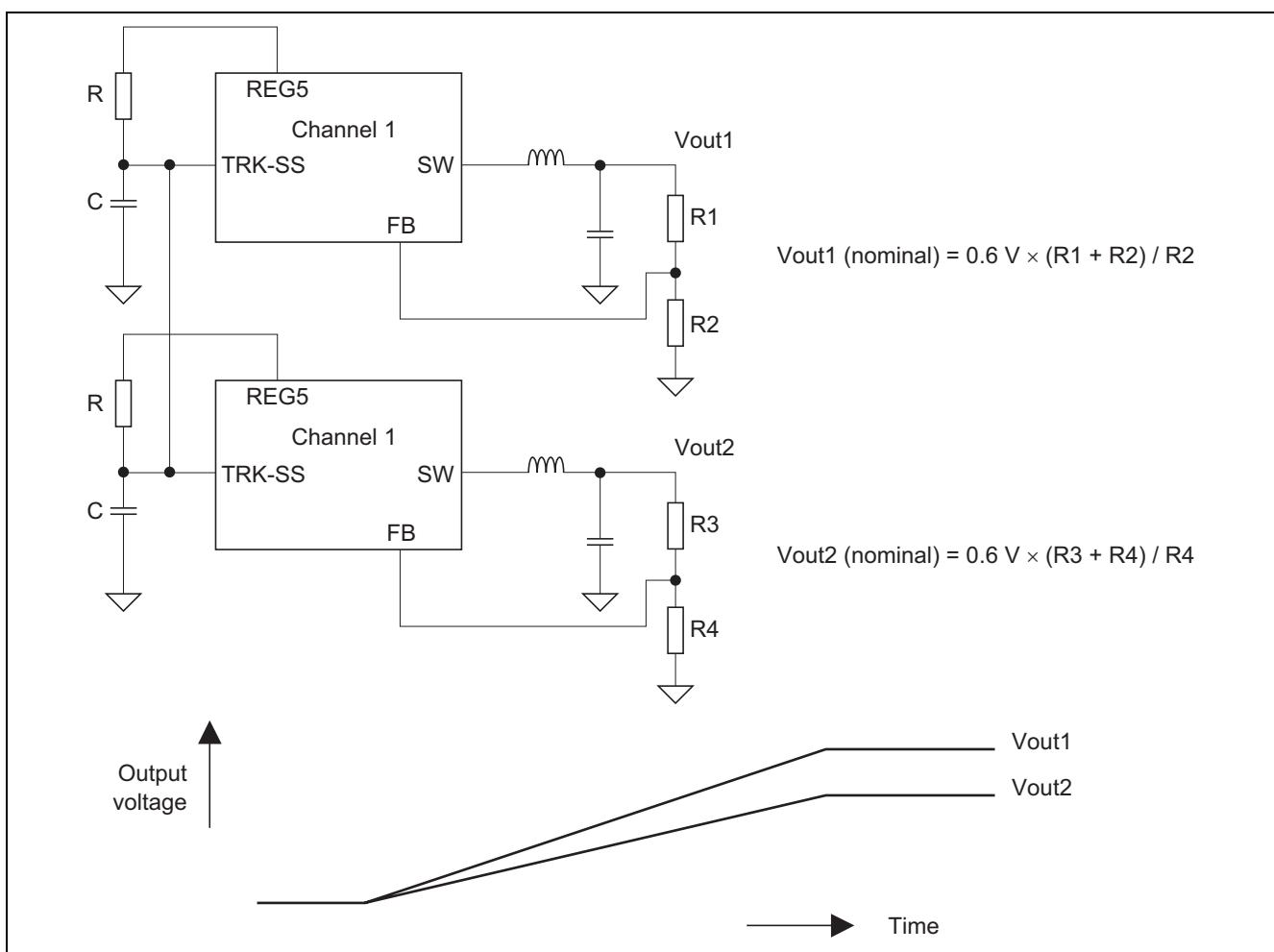

## Case 3) Retiometric tracking

The TRS-SS of channel two is tied to TRK-SS of channel 1.

No cross talk is observed between the channels.

## Case 4) Current sharing or two-phase operation

In the case of master-slave operation, the TRK-SS pin on the master device should be attached to an RC network for soft starts. TRK-SS pins of slave devices should be tied to the master's TRK-SS pin. The error amplifiers on the slave devices can be disabled by pulling up the corresponding FB pins to REG5, and the slave devices do not require loop-compensation networks.

## Choice of The Resistance of CS Pin

The CS pin is a current-output pin. A current 1/18500 of that of the high-side MOS FET flows through this pin, which also has a dc current offset of 490  $\mu\text{A}$ . The converter's maximum current is determined by the voltage on the CS pin, i.e. 1.5 V, and by the value of the external resistor attached to this pin. The resistance is determined as shown below.

Specification:  $L = 360 \text{ nH}$ ,  $V_{in} = 12 \text{ V}$ ,  $V_{out} = 1.8 \text{ V}$ ,  $F_{sw} = 500 \text{ kHz}$ ,  $I_{out(\text{max})} = 25 \text{ A}$

Current through the choke coil is

$$I_{Lpp} = (V_{in} - V_{out}) \times V_{out} / (L \times V_{in} \times F_{sw}) = 8.5 \text{ A (p-p)}$$

Peak choke current is the current when  $I_o$  is at its maximum, i.e.

$$I_{lmax} = I_{o(\text{max})} + 0.5 \times I_{Lpp} = 25 \text{ A} + 4.25 \text{ A} = 29.25 \text{ A}$$

Maximum CS pin output current is;

$$I_{csmax} = I_{lmax} / 18500 + I_{cs-dc} = 29.25 \text{ A} / 18500 + 490 \mu\text{A} = 2.071 \text{ mA}$$

The ideal resistance for attachment to the CS pin is

$$R_{CS} = V_{cl} / I_{csmax} = 1.5 \text{ V} / 2.071 \text{ mA} = 724 \Omega$$

Therefore choose  $750 \Omega$  as the value of the resistor for attachment to the CS pin.

## Output Voltage Setting

The error amplifier of the device has an accurate 0.6 V reference voltage. Feedback thus leads to a voltage of about 0.6 V on the FB pin once the converter system has stabilized, so the output voltage is

$$V_{out} = 0.6 \text{ V} \times (R1 + R2) / R2$$

## Loop Compensation

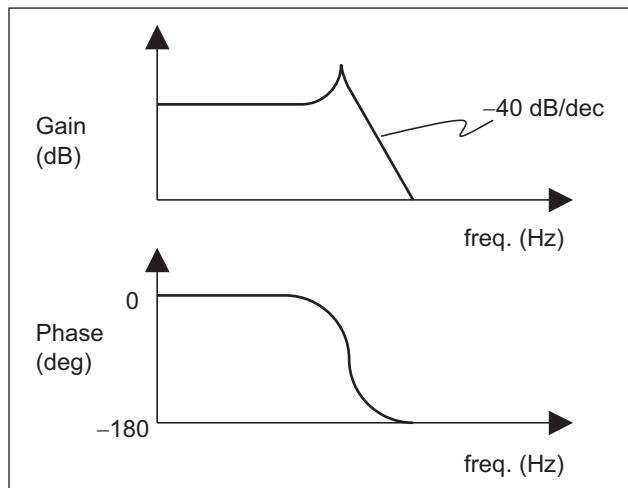

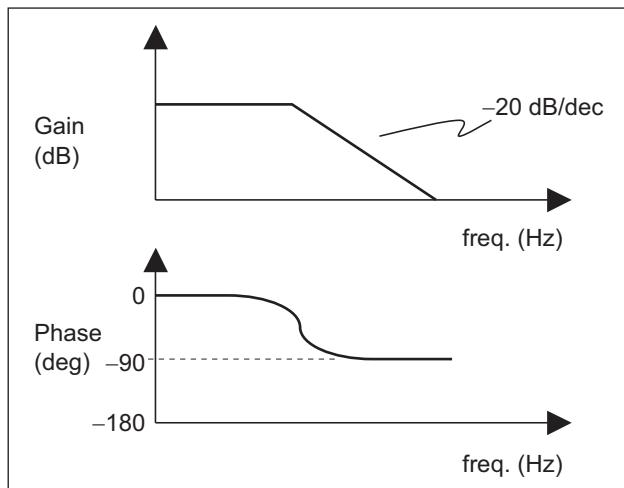

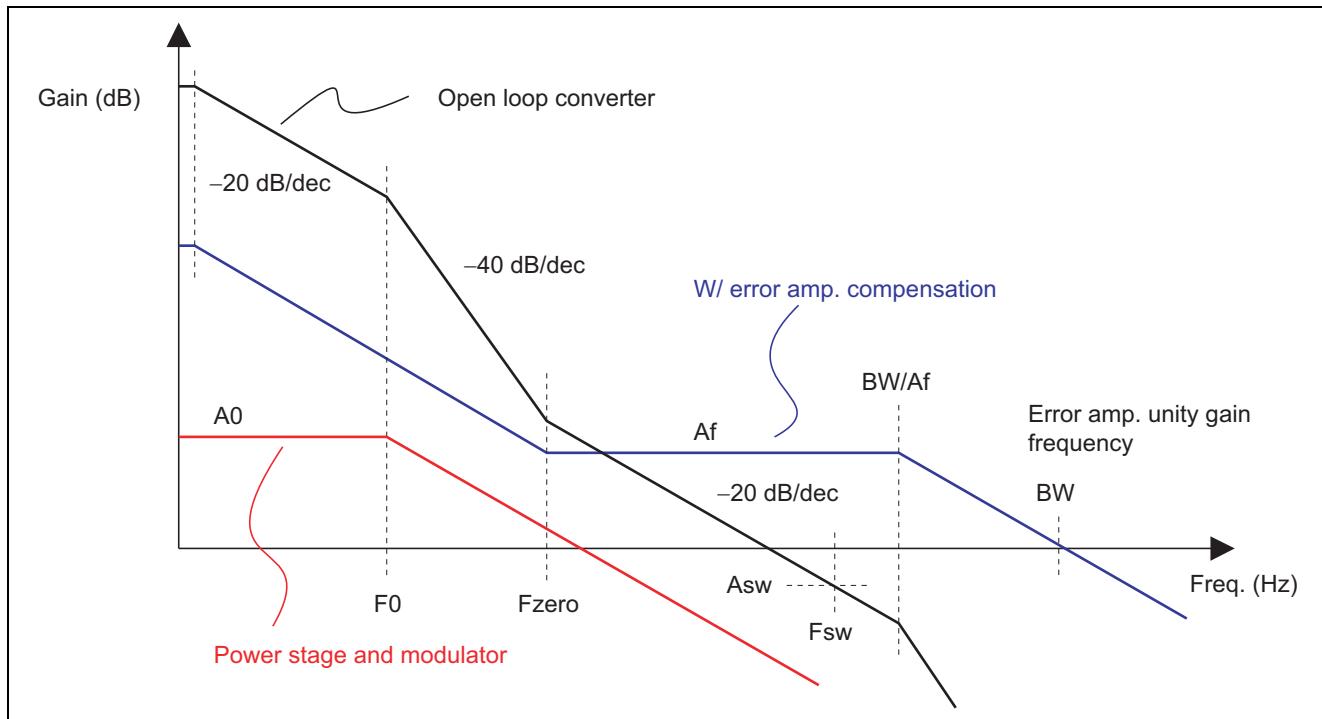

Peak-current control makes design in terms of phase margins easier than is the case with voltage control. This is because of differences between the characteristics of the PWM modulator and power stage in the two methods.

Figures 1 and 2 show the behavior of the PWM modulator and power stage in the cases of voltage control and peak current control, respectively.

**Figure 1 Bode Plot of Modulator + Power Stage (Voltage Mode)**

**Figure 2 Bode Plot of Modulator + Power Stage (Peak Current Mode)**

Feed-forward current to the modulator in the case of peak-current control means that the system is single pole, so we see a  $-20 \text{ dB/decade}$  cutoff and phase margin of  $90^\circ$  in the Bode plot. In voltage control, the system configures a two-pole pole system. That is why rather complicated loop compensation of the error amplifier is required, such as type-III compensation.

The design of effective compensation is thus much simpler in the case of peak-current control (refer to figure 3).

Figure 3 Error Amplifier Compensation

## Design example

Specification:  $L = 360 \text{ nH}$ ,  $C_o = 600 \mu\text{F}$ ,  $F_{sw} = 500 \text{ kHz}$ ,  $V_{in} = 12 \text{ V}$ ,  $V_{out} = 1.8 \text{ V}$ ,  $R_1 = 2 \text{ k}\Omega$ ,  $R_2 = 1 \text{ k}\Omega$ ,  $R_{CS} = 750 \Omega$

## 1. Flat-band gain of error amplifier

The flat-band gain is;  $A_f = R_f / (R_1 // R_2) / 2 \times \{R_2 / (R_1 + R_2)\}$

$$\text{Hence, } R_f = 2 \times A_f \times R_1 \dots \dots (1)$$

In the Bode plot, the total gain should be less than 1 (0 dB) at the switching frequency.

The total gain at  $F_{sw}$  ( $= A_{sw}$ ) depends on the flat-band gain, so  $A_f$  should be expressed as follows.

$$A_f = A_{sw} \times 2 \pi \times F_{sw} \times C_o \times R_{CS} / N_t \dots \dots (2)$$

$$\text{Here, } N_t = I_{dh} / I_{cs} = 18500$$

In the typical way, the value chosen for  $A_{sw}$  is in the range from 0.1 to 0.5, since this produces a stable control loop.

The transient response will be faster if a larger  $A_{sw}$  is adopted, but the system might be unstable.

We choose 0.2 for  $A_{sw}$  in the example below.

$$A_f = 0.2 \times 2 \pi \times 500 \text{ kHz} \times 600 \mu\text{F} \times 750 \Omega / 18500 = 15.283$$

$$R_f = 2 \times 15.283 \times 2 \text{ k}\Omega = 61.132 \text{ k}\Omega$$

Therefore, we select a value of 62 kΩ for  $R_f$ .

2. Selecting the  $C_f$  value to determine the frequency of the zero

The frequency of the zero established by  $C_f$  and  $R_f$  is about ten times the frequency of the pole for the power stage and modulator.

We must start with the dc gain of the power stage and modulator.

$$A_0 = \frac{2 \times N_t / R_{CS} \times L \times V_{in} \times F_{sw}}{\text{SQRT} \{V_{in}^2 - 8 \times L \times V_{in} \times F_{sw} \times (V_{CS0} \times N_t / R_{CS})\}} \dots \dots (3)$$

Here  $V_{CS0}$  is the peak ac voltage on the CS pin when the load current is zero, thus

$$V_{CS0} = 0.5 \times R_{CS} \times (V_{in} - V_{out}) \times V_{out} / (L \times V_{in} \times F_{sw}) / 18500 \dots \dots (4)$$

$$= 0.5 \times 750 \Omega \times (12 \text{ V} - 1.8 \text{ V}) \times 1.8 \text{ V} / (360 \text{ nH} \times 12 \text{ V} \times 500 \text{ kHz}) / 18500$$

$$= 0.172 \text{ V}$$

Equation (3)

$$\begin{aligned}

A_0 &= \frac{2 \times N_t / RCS \times L \times V_{in} \times F_{sw}}{\text{SQRT} \{V_{in}^2 - 8 \times L \times V_{in} \times F_{sw} \times (V_{CS0} \times N_t / RCS)\}} \quad \dots \dots (3) \\

&= \frac{2 \times 18500 / 750 \Omega \times 360 \text{ nH} \times 12 \text{ V} \times 500 \text{ kHz}}{\text{SQRT} \{12 \text{ V}^2 - 8 \times 360 \text{ nH} \times 12 \text{ V} \times 500 \text{ kHz} \times (0.172 \text{ V} \times 18500 / 750 \Omega)\}} \\

&= \frac{106.56}{\text{SQRT} \{70.687\}} \\

&= 12.674

\end{aligned}$$

The frequency of the pole established by the power stage and modulator is

$$F_0 = N_t / (2 \pi \times C_0 \times RCS \times A_0) \quad \dots \dots (5)$$

Thus,

$$F_0 = 18500 / (2 \pi \times 600 \mu\text{F} \times 750 \Omega \times 12.674) = 516 \text{ Hz}$$

Therefore, the frequency of the zero established by  $C_f$  and  $R_f$  is

$$F_{zero} = 10 \times F_0 = 5.16 \text{ kHz}$$

$$C_f = (2 \pi \times F_{zero} \times R_f)^{-1} = (2 \pi \times 5.16 \text{ kHz} \times 62 \text{ k}\Omega)^{-1} = 497 \text{ pF}$$

Therefore, we select the value 510 pF for  $C_f$ .Basically, the transient response is faster when  $C_f$  is smaller, but too small a value will make the system-loop unstable.

Figure 4

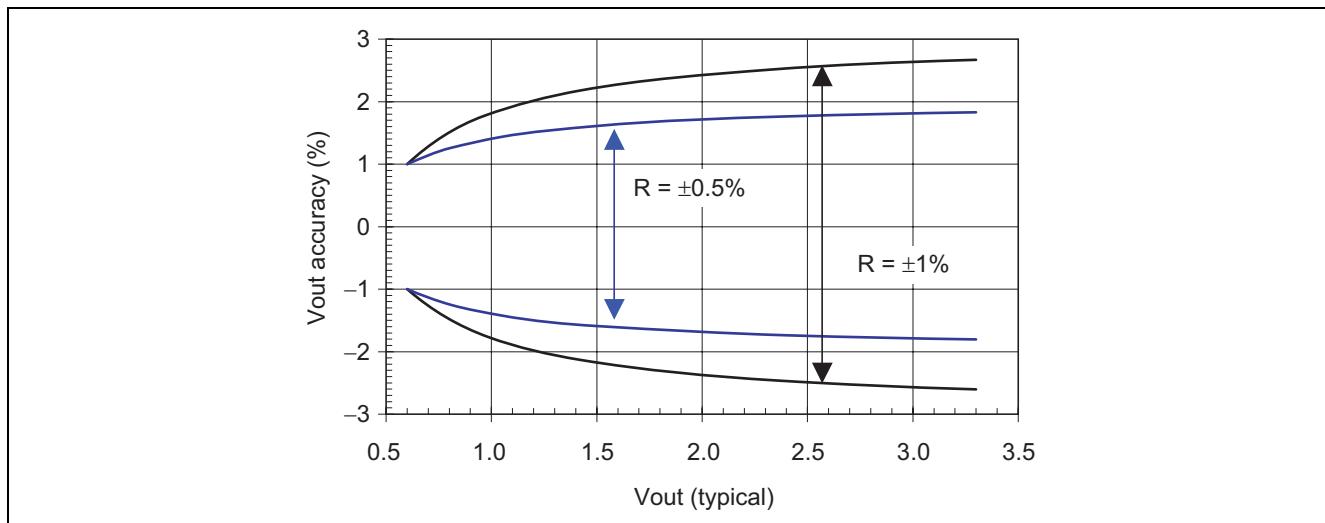

### Study of Vout Accuracy

The nominal output voltage is calculated as

$$V_{out} = V_{FB} \times (R_1 + R_2) / R_2 \dots\dots(6)$$

Here, the typical feedback voltage is 0.6 V.

The accuracy of  $V_{out}$  is strongly dependent on the variation of  $V_{FB}$ ,  $R_1$  and  $R_2$ .  $V_{FB}$  has a variation of 1% and resistance intrinsically has a certain variation. When we take the variation in resistance into account, equation (6) is extended to produce equation (7).

$$\begin{aligned} V_{out} &= \frac{R_1 \times K_1 + R_2 \times K_2}{R_2 \times K_2} \times V_{FB} \\ &= \frac{R_1 \times K_1 / K_2 + R_2}{R_2} \times V_{FB} \dots\dots(7) \end{aligned}$$

Here,  $K_1$  and  $K_2$  are coefficients. Both are 1.00 in the ideal case.

By equation (6),  $R_1$  is chosen as

$$R_1 = \left[ \frac{V_{out} \text{ (typical)}}{V_{FB} \text{ (typical)}} - 1 \right] \times R_2 \dots\dots(8)$$

Substituting this expression for  $R_1$  into equation (7) yields the following.

$$V_{out} = V_{FB} \times \left\{ \left[ \frac{V_{out} \text{ (typical)}}{V_{FB} \text{ (typical)}} - 1 \right] \times \frac{K_1}{K_2} + 1 \right\} \dots\dots(9)$$

Therefore, variation in  $V_{out}$  is expressed as

$$\frac{V_{out}}{V_{out} \text{ (typical)}} = \left\{ \frac{V_{FB}}{V_{out} \text{ (typical)}} \times \left[ \left[ \frac{V_{out} \text{ (typical)}}{V_{FB} \text{ (typical)}} - 1 \right] \times \frac{K_1}{K_2} + 1 \right] - 1 \right\} \times 100 \text{ (%)} \dots\dots(10)$$

The accuracy of  $V_{out}$  can be estimated by using equation (10).

For example, if  $V_{out}$  (typical) = 1.8 V, resistance variation is 1% (i.e.  $K_1, K_2 = 1.01$  and  $0.99$ ), and  $V_{FB} = 594$  mV to 606 mV:

$$\frac{V_{out}}{V_{out} (\text{typical})} = \left[ \frac{V_{FB}}{V_{out} (\text{typical})} \times \left\{ \left[ \frac{V_{out} (\text{typical})}{V_{FB} (\text{typical})} - 1 \right] \times \frac{K_1}{K_2} + 1 \right\} - 1 \right] \times 100 \text{ (%)} \quad \dots \dots (10)$$

$$= \left[ \frac{606 \text{ mV}}{1.8 \text{ V}} \times \left\{ \left[ \frac{1.8 \text{ V}}{600 \text{ mV}} - 1 \right] \times \frac{1.01}{0.99} + 1 \right\} - 1 \right] \times 100 \text{ (%)}$$

$$= 2.36\%$$

or

$$= \left[ \frac{594 \text{ mV}}{1.8 \text{ V}} \times \left\{ \left[ \frac{1.8 \text{ V}}{600 \text{ mV}} - 1 \right] \times \frac{0.99}{1.01} + 1 \right\} - 1 \right] \times 100 \text{ (%)}$$

$$= -2.31\%$$

Therefore, the output accuracy will be  $\pm 2.3\%$  under the above conditions.

Figure 5 shows the relationship between the accuracy of the resistance and the accuracy of the output voltage. The resistor value must have an accuracy of 0.5% if the variation in output voltage from the system is to be kept within two percent across the voltage range from 0.6 to 3.3 V.

Figure 5 Vout Accuracy vs. Vout Set Voltage

**Current Sharing**

Simply tie the Ishare pins together

**External Synchronization**

Simply tie the CT pin to GND

## Current Sharing and Synchronization

Tie the Ishare and SYNC pins together

## Two-Phase Operation

Tie the Ishare and SYNC pins together.

## Timing Chart

### Peak Current Control

Note: Propagation delay is ignored.

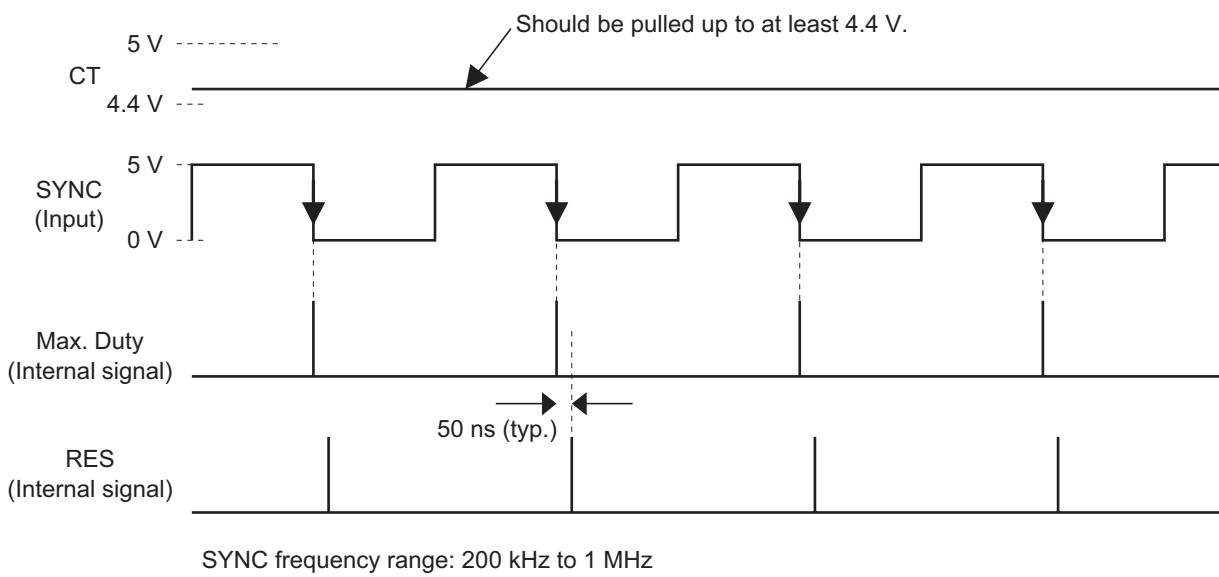

**Oscillator and Pulse Generator**

1. Standalone operation or operation as the master chip in a parallel configuration with other chips.

Note: Propagation delay is ignored.

Frequency of oscillation for CT:

$$F_{ct} = \frac{160 \mu A}{2 \times (CT(F) + 18 pF) \times 1 V} \quad (\text{Hz})$$

Switching frequency

$$F_{sw} = 0.5 \times F_{ct} \quad (\text{Hz})$$

Frequency setting range (for Fsw): 200 kHz to 1 MHz (i.e. 400 kHz to 2 MHz for Fct)

## 2. Operation as a slave chip (simple synchronous operation)

Note: Propagation delay is ignored.

## 3. Operation as a slave chip in a parallel configuration (two-phase operation)

Note: Propagation delay is ignored.

**Hiccup Operation when the Over-Current Limit (OCL) is Reached**

Note: Propagation delay is ignored.

## Main Characteristics

## Package Dimensions

| JEITA Package Code | RENESAS Code | Previous Code | MASS[Typ.] |

|--------------------|--------------|---------------|------------|

| —                  | PWQNN056KB-A | —             | 0.17g      |

| Reference Symbol | Dimension in Millimeters |      |      |

|------------------|--------------------------|------|------|

|                  | Min                      | Nom  | Max  |

| D                | 7.90                     | 8.00 | 8.10 |

| E                | 7.90                     | 8.00 | 8.10 |

| A <sub>2</sub>   | —                        | —    | —    |

| A                | —                        | —    | 0.80 |

| A <sub>1</sub>   | 0                        | —    | 0.05 |

| b                | 0.18                     | 0.23 | 0.28 |

| b <sub>1</sub>   | —                        | —    | —    |

| [E]              | —                        | 0.50 | —    |

| L <sub>p</sub>   | 0.30                     | 0.40 | 0.50 |

| x                | —                        | —    | 0.10 |

| y                | —                        | —    | 0.08 |

| y <sub>1</sub>   | —                        | —    | 0.10 |

| t                | —                        | —    | 0.15 |

| H <sub>D</sub>   | —                        | —    | —    |

| H <sub>E</sub>   | —                        | —    | —    |

| Z <sub>D</sub>   | —                        | —    | —    |

| Z <sub>E</sub>   | —                        | —    | —    |

| c                | —                        | 0.20 | —    |

| C <sub>1</sub>   | —                        | —    | —    |

## Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg. 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

### Notes:

1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (<http://www.renesas.com>)

5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guarantees regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implants

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

9. Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

10. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

11. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

12. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

13. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

14. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

### RENESAS SALES OFFICES

<http://www.renesas.com>

Refer to "<http://www.renesas.com/en/network>" for the latest and detailed information.

**Renesas Technology America, Inc.**

450 Holger Way, San Jose, CA 95134-1368, U.S.A.

Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

**Renesas Technology Europe Limited**

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.

Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

**Renesas Technology (Shanghai) Co., Ltd.**

Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120

Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7898

**Renesas Technology Hong Kong Ltd.**

7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong

Tel: <852> 2265-6688, Fax: <852> 2730-6071

**Renesas Technology Taiwan Co., Ltd.**

10th Floor, No.99, Fushing North Road, Taipei, Taiwan

Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

**Renesas Technology Singapore Pte. Ltd.**

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632

Tel: <65> 6213-0200, Fax: <65> 6278-8001

**Renesas Technology Korea Co., Ltd.**

Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea

Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

**Renesas Technology Malaysia Sdn. Bhd**

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia

Tel: <603> 7955-9390, Fax: <603> 7955-9510