# Single and Dual Single Supply Ultra-Low Noise, Ultra-Low Distortion, Rail-to-Rail Output, Op Amp

### ISL28190, ISL28290

The ISL28190 and ISL28290 are tiny single and dual ultra-low noise, ultra-low distortion operational amplifiers. Fully specified to operated down to +3V single supply. These amplifiers have outputs that swing rail-to-rail, and an input common mode voltage that extends below ground (ground sensing).

The ISL28190 and ISL28290 are unity gain stable with an input referred voltage noise of  $1nV/\sqrt{\text{Hz}}$ . Both parts feature 0.00017% THD+N @ 1kHz.

The ISL28190 is available in the space-saving 6 Ld UTDFN (1.6mmx1.6mm) and 6 Ld SOT-23 packages. The ISL28290 is available in the 10 Ld UTQFN (1.8mmx1.4mm) , 10 Ld MSOP and 8 LD SOIC packages. All devices are guaranteed over -40°C to +125°C.

### **Ordering Information**

| PART NUMBER<br>(Note 5)      | PART<br>MARKING  | PACKAGE<br>(Pb-free) | PKG.<br>DWG. # |  |

|------------------------------|------------------|----------------------|----------------|--|

| ISL28190FHZ-T7 (Notes 1, 2)  | GABH<br>(Note 4) | 6 Ld SOT-23          | P6.064A        |  |

| ISL28190FRUZ-T7 (Notes 1, 3) | M7               | 6 Ld UTDFN           | L6.1.6x1.6A    |  |

| ISL28290FUZ (Note 2)         | 8290Z            | 10 Ld MSOP           | M10.118A       |  |

| ISL28290FUZ-T7 (Note 1)      | 8290Z            | 10 Ld MSOP           | M10.118A       |  |

| ISL28290FRUZ-T7 (Notes 1, 3) | E                | 10 Ld UTQFN          | L10.1.8x1.4A   |  |

| ISL28290FBZ (Note 2)         | 28290 FBZ        | 8 Ld SOIC            | M8.15E         |  |

| ISL28290FBZ-T7 (Note 1)      | 28290 FBZ        | 8 Ld SOIC            | M8.15E         |  |

| ISL28190EVAL1Z               | Evaluation Board |                      |                |  |

| ISL28290EVAL1Z               | Evaluation Board |                      |                |  |

#### NOTES:

- 1. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and NiPdAu plate - e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 4. The part marking is located on the bottom of the part.

- For Moisture Sensitivity Level (MSL), please see device information page for <u>ISL28190</u>. ISL28290. For more information on MSL please see tech brief <u>TB363</u>.

1

#### **Features**

- 1nV/√Hz input voltage noise

- 1kHz THD+N typical 0.00017% at 2V<sub>P-P</sub> V<sub>OUT</sub>

- Harmonic Distortion -87dBc, -90dBc, fo = 1MHz

- 170MHz -3dB bandwidth

- 50V/µs slew rate

- 700µV maximum offset voltage

- · 10µA typical input bias current

- 103dB typical CMRR

- · 3V to 5.5V single supply voltage range

- · Rail-to-rail output

- · Ground sensing

- . Enable pin (not available in the 8 Ld SOIC package option)

- Pb-free (RoHS compliant)

### **Applications**

- · Low noise signal processing

- · Low noise microphones/preamplifiers

- · ADC buffers

- · DAC output amplifiers

- Digital scales

- · Strain gauges/sensor amplifiers

- · Radio systems

- · Portable equipment

- · Infrared detectors

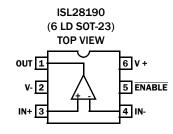

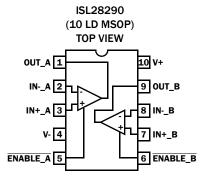

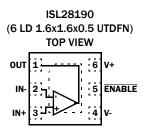

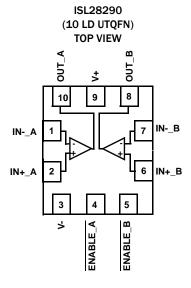

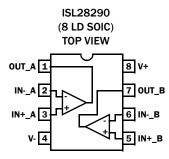

# **Pin Configurations**

# **Pin Descriptions**

| ISL28190<br>(6 Ld SOT-23) | ISL28190<br>(6 Ld UTDFN) | ISL28290<br>(10 Ld MSOP) | ISL28290<br>(10 Ld UTQFN) | ISL28290<br>(8 Ld SOIC) | PIN<br>NAME           | FUNCTION                                                                                                                     | EQUIVALENT<br>CIRCUIT |

|---------------------------|--------------------------|--------------------------|---------------------------|-------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 4                         | 2                        | 2 (A)<br>8 (B)           | 1 (A)<br>7 (B)            | 2 (A)<br>6 (B)          | IN-<br>INA<br>INB     | Inverting input                                                                                                              | IN- U- UV- Circuit 1  |

| 3                         | 3                        | 3 (A)<br>7 (B)           | 2 (A)<br>6 (B)            | 3 (A)<br>5 (B)          | IN+<br>IN+_A<br>IN+_B | Non-inverting input                                                                                                          | (See Circuit 1)       |

| 2                         | 4                        | 4                        | 3                         | 4                       | V-                    | Negative supply                                                                                                              |                       |

| 1                         | 1                        | 1 (A)<br>9 (B)           | 10 (A)<br>8 (B)           | 1 (A)<br>7 (B)          | OUT_A<br>OUT_B        | Output                                                                                                                       | OUT OUT Circuit 2     |

| 6                         | 6                        | 10                       | 9                         | 8                       | V+                    | Positive supply                                                                                                              |                       |

| 5                         | 5                        | 5 (A)<br>6 (B)           | 4 (A)<br>5 (B)            | N/A                     | EN<br>EN_A<br>EN_B    | Enable BAR pin<br>internal pull-down;<br>Logic "1" selects<br>the disabled state;<br>Logic "0" selects<br>the enabled state. | EN U-V-Circuit 3      |

Submit Document Feedback 3 intersil FN6247.10

July 22, 2014

#### Absolute Maximum Ratings (TA = +25°C)

| Supply Voltage                   | 5.57 |

|----------------------------------|------|

| Supply Turn On Voltage Slew Rate | V/µs |

| Differential Input Current       | 5mA  |

| Differential Input Voltage       | 0.5V |

| Input Voltage                    | 0.5V |

| ESD Tolerance                    |      |

| Human Body Model                 | 3kV  |

| Machine Model                    | 300V |

| Charged Device Model12           | 200V |

#### **Thermal Information**

| Thermal Resistance (Typical)        | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (°C/W) |

|-------------------------------------|----------------------|----------------------|

| 6 Ld SOT-23 Package (Notes 6, 9)    | 170                  | 105                  |

| 6 Ld UTDFN Package (Notes 7, 8)     | 125                  | 80                   |

| 8 Ld SOIC Package (Notes 6, 9)      | 110                  | 82                   |

| 10 Ld MSOP Package (Notes 6, 9)     | 175                  | 90                   |

| 10 Ld UTQFN Package (Notes 6, 9)    | 190                  | 140                  |

| Ambient Operating Temperature Range | 4                    | 0°C to +125°C        |

| Storage Temperature Range           | 6                    | 5°C to +150°C        |

| Operating Junction Temperature      |                      | +125°C               |

| Pb-Free Reflow Profile              |                      | . see link below     |

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTE

- 6.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief <u>TB379</u> for details.

- 7. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 8. For  $\theta_{\text{JC}}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

- 9. For  $\theta_{\text{JC}},$  the "case temp" location is taken at the package top center.

**Electrical Specifications** V+=5.0V, V-=GND,  $R_L=Open$ ,  $R_F=1k\Omega$ ,  $A_V=-1$  unless otherwise specified. Parameters are per amplifier. Typical values are at V+=5V,  $T_A=+25$ °C. Boldface limits apply over the operating temperature range, -40°C to +125°C, temperature data established by characterization.

| PARAMETER                        | DESCRIPTION                            | CONDITIONS                                | MIN<br>(Note 10) | TYP  | MAX<br>(Note 10) | UNIT  |

|----------------------------------|----------------------------------------|-------------------------------------------|------------------|------|------------------|-------|

| DC SPECIFICATION                 | DNS                                    |                                           | l l              |      |                  | .1    |

| V <sub>OS</sub>                  | Input Offset Voltage                   |                                           | -1100            | 240  | 700              | μV    |

|                                  |                                        |                                           |                  |      | 900              | -     |

| $\frac{\Delta V_{OS}}{\Delta T}$ | Input Offset Drift vs Temperature      | See Figure 21                             |                  | 1.9  |                  | μV/°C |

| I <sub>IO</sub>                  | Input Offset Current                   |                                           |                  | 40   | 500              | nA    |

|                                  |                                        |                                           |                  |      | 900              |       |

| IB                               | Input Bias Current                     |                                           |                  | 10   | 16               | μΑ    |

|                                  |                                        |                                           |                  |      | 18               |       |

| V <sub>CM</sub>                  | Common-Mode Voltage Range              |                                           | 0                |      | 3.8              | V     |

| CMRR                             | Common-Mode Rejection Ratio            | V <sub>CM</sub> = 0V to 3.8V              | 78               | 103  |                  | dB    |

| PSRR                             | Power Supply Rejection Ratio           | V <sub>S</sub> = 3V to 5V                 | 74               | 80   |                  | dB    |

| A <sub>VOL</sub>                 | Large Signal Voltage Gain              | $V_0 = 0.5V$ to 4V, $R_L = 1k\Omega$      | 94               | 102  |                  | dB    |

|                                  |                                        |                                           | 90               |      |                  |       |

| V <sub>OUT</sub>                 | Maximum Output Voltage Swing           | Output low, $R_L = 1 k\Omega$             |                  | 20   | 50               | m۷    |

|                                  |                                        |                                           |                  |      | 80               |       |

|                                  |                                        | Output high, $R_L = 1k\Omega$ , $V+ = 5V$ | 4.95             | 4.97 |                  | V     |

|                                  |                                        |                                           | 4.92             |      |                  |       |

| I <sub>S,ON</sub>                | Supply Current per Channel,<br>Enabled |                                           |                  | 8.5  | 11               | mA    |

|                                  |                                        |                                           |                  |      | 13               |       |

| I <sub>S,OFF</sub>               | Supply Current, Disabled               |                                           |                  | 26   | 35               | μA    |

|                                  |                                        |                                           |                  |      | 52               |       |

| I <sub>0</sub> +                 | Short-Circuit Output Current           | $R_L = 10\Omega$                          | 95               | 144  |                  | mA    |

|                                  |                                        |                                           | 90               |      |                  |       |

Submit Document Feedback 4 intersil FN6247.10

July 22, 2014

**Electrical Specifications** V+ = 5.0V, V- = GND,  $R_L$  = Open,  $R_F$  = 1k $\Omega$ ,  $A_V$  = -1 unless otherwise specified. Parameters are per amplifier. Typical values are at V+ = 5V,  $T_A$  = +25°C. Boldface limits apply over the operating temperature range, -40°C to +125°C, temperature data established by characterization. (Continued)

| PARAMETER                                    | DESCRIPTION                                                            | CONDITIONS                                                                                                                                                                    | MIN<br>(Note 10) | TYP         | MAX<br>(Note 10) | UNIT       |

|----------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|------------------|------------|

| I <sub>0</sub> -                             | Short-Circuit Output Current                                           | $R_L = 10\Omega$                                                                                                                                                              | 95               | 135         |                  | mA         |

|                                              |                                                                        |                                                                                                                                                                               | 90               |             |                  |            |

| V <sub>SUPPLY</sub>                          | Supply Operating Range                                                 | V+ to V-                                                                                                                                                                      | 3                |             | 5.5              | ٧          |

| V <sub>ENH</sub>                             | EN High Level                                                          | Referred to V-                                                                                                                                                                | 2                |             |                  | ٧          |

| VENL                                         | EN Low Level                                                           | Referred to V-                                                                                                                                                                |                  |             | 0.8              | ٧          |

| IENH                                         | EN Pin Input High Current                                              | V <sub>EN</sub> = V+                                                                                                                                                          |                  | 0.8         | 1.2              | μΑ         |

|                                              |                                                                        |                                                                                                                                                                               |                  |             | 1.4              | 1          |

| IENL                                         | EN Pin Input Low Current                                               | V <sub>EN</sub> = V-                                                                                                                                                          |                  | 20          | 80               | nA         |

|                                              |                                                                        |                                                                                                                                                                               |                  |             | 100              |            |

| AC SPECIFICATIO                              | NS                                                                     | ,                                                                                                                                                                             | TI.              |             | I                |            |

| GBW                                          | -3dB Unity Gain Bandwidth                                              | $R_F = 0\Omega C_L = 20pF, A_V = 1, R_L = 10k\Omega$                                                                                                                          |                  | 170         |                  | MHz        |

| THD+N                                        | Total Harmonic Distortion + Noise                                      | f = 1kHz, VOUT + $2V_{P-P}$ , $A_V$ = +1, $R_L$ = $10$ k $\Omega$                                                                                                             |                  | 0.000<br>17 |                  | %          |

| HD                                           | 2nd Harmonic Distortion                                                | $V_{OUT} = 2V_{P-P}, A_V = 1$                                                                                                                                                 |                  | -87         |                  | dBc        |

| (1MHz)                                       | 3rd Harmonic Distortion                                                |                                                                                                                                                                               | -90              |             | dBc              |            |

| ISO                                          | Off-state Isolation<br>f <sub>O</sub> = 100kHz                         | $A_V$ = +1; $V_{IN}$ = 100m $V_{P-P}$ ; $R_F$ = 0 $\Omega$ , $C_L$ = 20pF, $A_V$ = 1, $R_L$ = 10k $\Omega$                                                                    |                  | -38         |                  | dB         |

| X-TALK<br>ISL28290                           | Channel-to-Channel Crosstalk f <sub>0</sub> = 100kHz                   | $V_S = \pm 2.5V$ ; $A_V = +1$ ; $V_{IN} = 1V_{P-P}$ , $R_F = 0\Omega$ , $C_L = 20$ pF, $A_V = 1$ , $R_L = 10$ k $\Omega$                                                      |                  | -105        |                  | dB         |

| PSRR                                         | Power Supply Rejection Ratio<br>f <sub>0</sub> = 100kHz                | $\begin{aligned} &V_S=\pm 2.5 \text{V; A}_V=+1\text{; V}_{SOURCE}=1 \text{V}_{P\text{-P}},  R_F=0 \Omega, \\ &C_L=20 \text{pF, A}_V=1,  R_L=10 \text{k} \Omega \end{aligned}$ |                  | -70         |                  | dB         |

| CMRR                                         | Common Mode Rejection Ratio f <sub>0</sub> = 100kHz                    | $V_S = \pm 2.5V$ ; $A_V = +1$ ; $V_{CM} = 1V_{P-P}$ , $R_F = 0\Omega$ , $C_L = 20$ pF, $A_V = 1$ , $R_L = 10$ k $\Omega$                                                      |                  | -65         |                  | dB         |

| e <sub>n</sub>                               | Input Referred Voltage Noise                                           | f <sub>O</sub> = 1kHz                                                                                                                                                         |                  | 1           |                  | nV/√H<br>z |

| i <sub>n</sub>                               | Input Referred Current Noise                                           | f <sub>O</sub> = 10kHz                                                                                                                                                        |                  | 2.1         |                  | pA/√H<br>z |

| TRANSIENT RESI                               | PONSE                                                                  | ,                                                                                                                                                                             | TI.              |             | I                |            |

| SR                                           | Slew Rate                                                              |                                                                                                                                                                               | 30               | 50          |                  | V/µs       |

|                                              |                                                                        |                                                                                                                                                                               | 25               |             |                  |            |

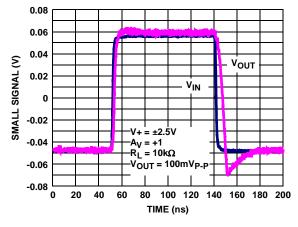

| t <sub>pd</sub>                              | Propagation Delay<br>10% V <sub>IN</sub> - 10% V <sub>OUT</sub>        | $A_V = 1$ , $V_{OUT} = 100 \text{mV}_{P-P}$ , $R_F = 0\Omega$ , $C_L = 1.2 \text{pF}$                                                                                         |                  | 1.0         |                  | ns         |

| t <sub>r</sub> , t <sub>f</sub> , Small      | Rise Time, t <sub>r</sub> 10% to 90%                                   | $A_V = +1, V_{OUT} = 0.1V_{P-P}, R_F = 0\Omega, C_L = 1.2pF$                                                                                                                  |                  | 3.3         |                  | ns         |

| Signal                                       | Fall Time, t <sub>f</sub> 10% to 90%                                   |                                                                                                                                                                               |                  | 6.3         |                  | ns         |

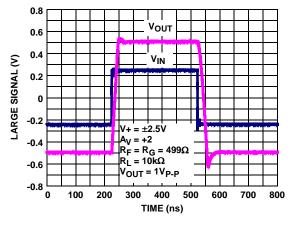

| t <sub>r</sub> , t <sub>f</sub> Large Signal | Rise Time, t <sub>r</sub> 10% to 90%                                   | $A_V = +2$ , $V_{OUT} = 1V_{P-P}$ , $R_F = R_G = 499\Omega$ , $R_L = 10k\Omega$ ,                                                                                             |                  | 44          |                  | ns         |

|                                              | Fall Time, t <sub>f</sub> 10% to 90%                                   | C <sub>L</sub> = 1.2pF                                                                                                                                                        |                  | 51          |                  | ns         |

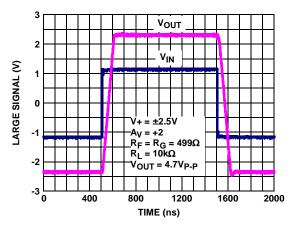

|                                              | Rise Time, t <sub>r</sub> 10% to 90%                                   | $A_V = +2$ , $V_{OUT} = 4.7V_{P-P}$ , $R_F = R_G = 499\Omega$ ,                                                                                                               |                  | 190         |                  | ns         |

|                                              | Fall Time, t <sub>f</sub> 10% to 90%                                   | $R_L = 10k\Omega$ , $C_L = 1.2pF$                                                                                                                                             |                  | 187         |                  | ns         |

| t <sub>s</sub>                               | Settling Time to 0.1%<br>90% V <sub>OUT</sub> to 0.1% V <sub>OUT</sub> | $A_V = 1$ , $V_{OUT} = 1V_{P-P}$ , $R_F = 0\Omega$ , $C_L = 1.2pF$                                                                                                            |                  | 45          |                  | ns         |

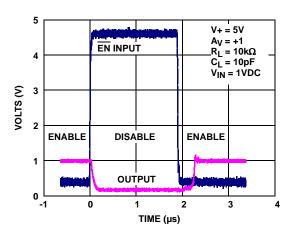

| t <sub>EN</sub>                              | ENABLE to Output Turn-on Delay<br>Time; 10% EN - 10% V <sub>OUT</sub>  | $A_V = 1$ , $V_{OUT} = 1$ VDC, $R_L = 10$ k $\Omega$ , $C_L = 1.2$ pF                                                                                                         |                  | 330         |                  | ns         |

|                                              | ENABLE to Output Turn-off Delay<br>Time; 10% EN - 10% V <sub>OUT</sub> | $A_V = 1$ , $V_{OUT} = OVDC$ , $R_L = 10k\Omega$ , $C_L = 1.2pF$                                                                                                              |                  | 50          |                  | ns         |

NOTE:

10. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

Submit Document Feedback 5 Intersil 5 Intersil 5 July 22, 2014

# **Typical Performance Curves**

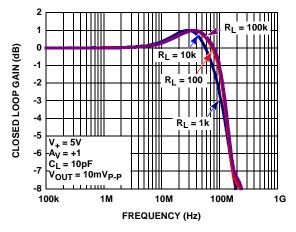

FIGURE 1. GAIN vs FREQUENCY FOR VARIOUS RLOAD

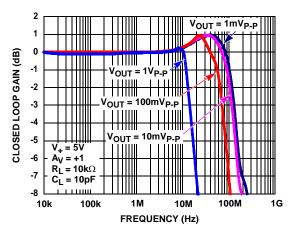

FIGURE 3. -3dB BANDWIDTH vs Vout

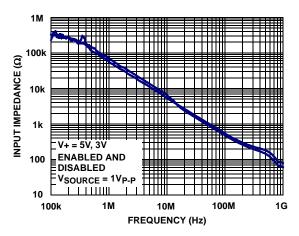

FIGURE 5. INPUT IMPEDANCE vs FREQUENCY

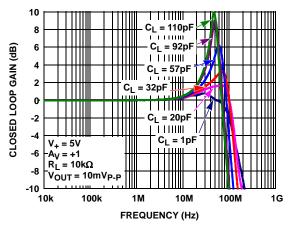

FIGURE 2. GAIN vs FREQUENCY FOR VARIOUS CLOAD

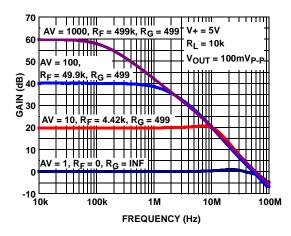

FIGURE 4. FREQUENCY RESPONSE vs CLOSED LOOP GAIN

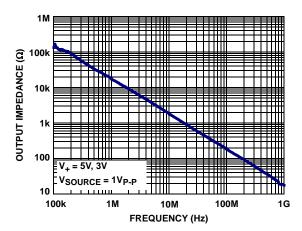

FIGURE 6. DISABLED OUTPUT IMPEDANCE vs FREQUENCY

Submit Document Feedback 6 Intersil FN6247.10

July 22, 2014

### Typical Performance Curves (Continued)

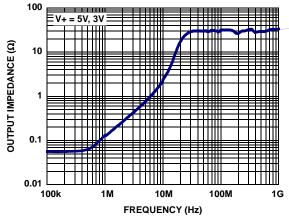

FIGURE 7. ENABLED OUTPUT IMPEDANCE vs FREQUENCY

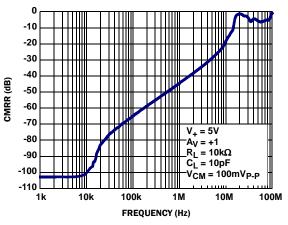

FIGURE 8. CMRR vs FREQUENCY

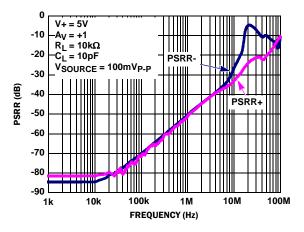

FIGURE 9. PSRR vs FREQUENCY

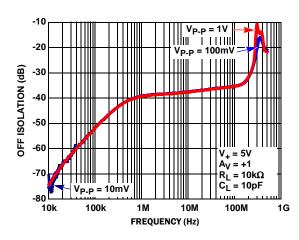

FIGURE 10. OFF ISOLATION vs FREQUENCY

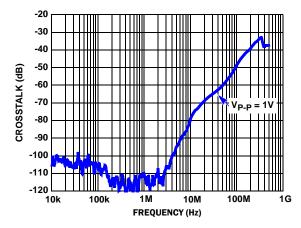

FIGURE 11. CHANNEL-TO-CHANNEL CROSSTALK vs FREQUENCY

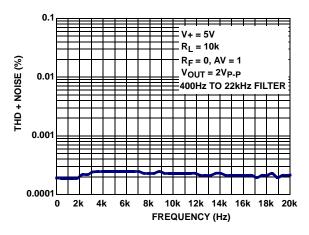

FIGURE 12. THD+N vs FREQUENCY

Submit Document Feedback FN6247.10 intersil July 22, 2014

### Typical Performance Curves (Continued)

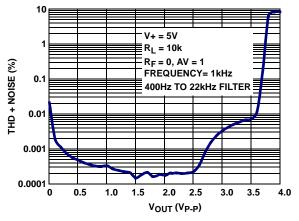

FIGURE 13. THD+N @ 1kHz vs V<sub>OUT</sub>

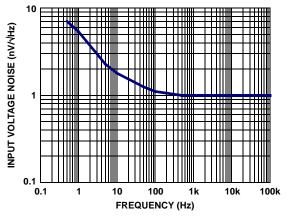

FIGURE 14. INPUT REFERRED NOISE VOLTAGE vs FREQUENCY

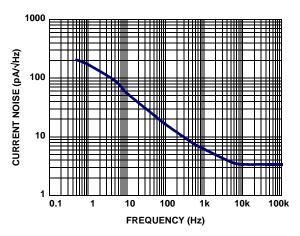

FIGURE 15. INPUT REFERRED NOISE CURRENT vs FREQUENCY

FIGURE 16. ENABLE/DISABLE TIMING

FIGURE 17. SMALL SIGNAL STEP RESPONSE

FIGURE 18. LARGE SIGNAL (1V) STEP RESPONSE

Submit Document Feedback FN6247.10 intersil July 22, 2014

6.0

### Typical Performance Curves (Continued)

FIGURE 19. LARGE SIGNAL (4.7V) STEP RESPONSE

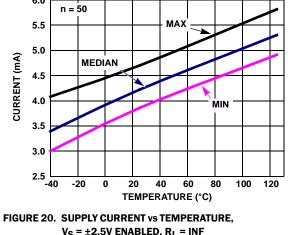

$V_S = \pm 2.5V$  ENABLED,  $R_L = INF$

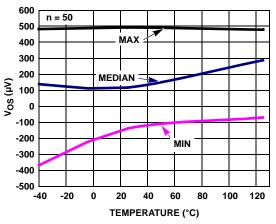

FIGURE 21.  $V_{OS}$  vs TEMPERATURE  $V_S = \pm 2.5V$

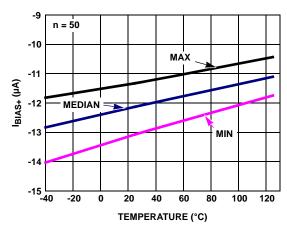

FIGURE 22.  $I_{BIAS+}$  vs TEMPERATURE  $V_S = \pm 2.5V$

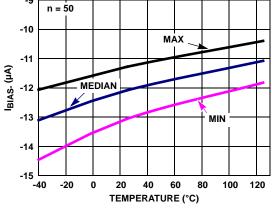

FIGURE 23.  $I_{BIAS}$  vs TEMPERATURE  $V_S = \pm 2.5V$

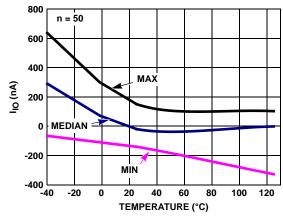

FIGURE 24.  $I_{10}$  vs TEMPERATURE  $V_S = \pm 2.5V$

Submit Document Feedback intersil FN6247.10 July 22, 2014

### Typical Performance Curves (Continued)

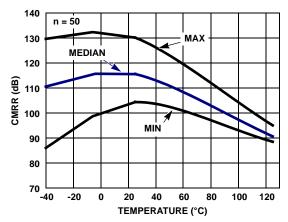

FIGURE 25. CMRR vs TEMPERATURE, VCM = 3.8V,  $V_{S} = \pm 2.5V$

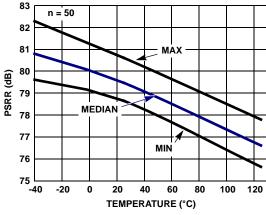

FIGURE 26. PSRR vs TEMPERATURE ±1.5V TO ±2.5V

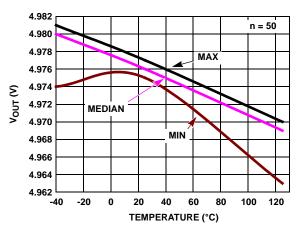

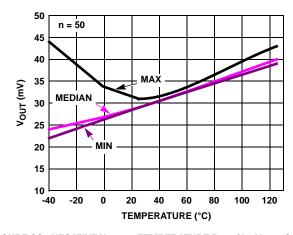

FIGURE 27. POSITIVE  $V_{OUT}$  vs TEMPERATURE  $R_L = 1k$ ,  $V_S = \pm 2.5V$

FIGURE 28. NEGATIVE  $V_{OUT}$  vs TEMPERATURE  $R_L = 1k$ ,  $V_S = \pm 2.5V$

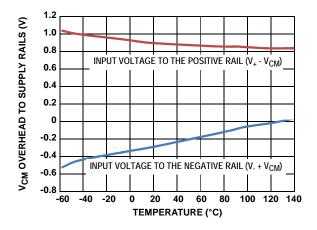

FIGURE 29. INPUT COMMON MODE VOLTAGE vs TEMPERATURE

10 intersil FN6247.10 July 22, 2014

### **Applications Information**

#### **Product Description**

The ISL28190 and ISL28290 are voltage feedback operational amplifiers designed for communication and imaging applications requiring low distortion, very low voltage and current noise. Both parts feature high bandwidth while drawing moderately low supply current. The ISL28190 and ISL28290 use a classical voltage-feedback topology, which allows them to be used in a variety of applications where current-feedback amplifiers are not appropriate because of restrictions placed upon the feedback element used with the amplifier.

#### **Enable/Power-Down**

The ISL28190 and ISL28290 amplifiers are disabled by applying a voltage greater than 2V to the EN pin, with respect to the V- pin. In this condition, the output(s) will be in a high impedance state and the amplifier(s) current will be reduced to 13µA/Amp. By disabling the part, multiple parts can be connected together as a MUX. The outputs are tied together in parallel and a channel can be selected by the  $\overline{EN}$  pin. The  $\overline{EN}$  pin also has an internal pull-down. If left open, the EN pin will pull to the negative rail and the device will be enabled by default.

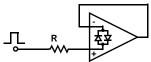

#### **Input Protection**

All input terminals have internal ESD protection diodes to both positive and negative supply rails, limiting the input voltage to within one diode beyond the supply rails. Both parts have additional back-to-back diodes across the input terminals (as shown in Figure 30). In pulse applications where the input Slew Rate exceeds the Slew Rate of the amplifier, the possibility exists for the input protection diodes to become forward biased. This can cause excessive input current and distortion at the outputs. If overdriving the inputs is necessary, the external input current must never exceed 5mA. An external series resistor may be used to limit the current, as shown in Figure 30.

FIGURE 30. LIMITING THE INPUT CURRENT TO LESS THAN 5mA

#### **Using Only One Channel**

The ISL28290 is a Dual channel op amp. If the application only requires one channel when using the ISL28290, the user must configure the unused channel to prevent it from oscillating. Oscillation can occur if the input and output pins are floating. This will result in higher than expected supply currents and possible noise injection into the channel being used. The proper way to prevent this oscillation is to short the output to the negative input and ground the positive input (as shown in Figure 31).

FIGURE 31. PREVENTING OSCILLATIONS IN UNUSED CHANNELS

### **Power Supply Bypassing and Printed Circuit Board Layout**

As with any high frequency device, good printed circuit board layout is necessary for optimum performance. Low impedance ground plane construction is essential. Surface mount components are recommended, but if leaded components are used, lead lengths should be as short as possible. The power supply pins must be well bypassed to reduce the risk of oscillation. The combination of a 4.7µF tantalum capacitor in parallel with a 0.01µF capacitor has been shown to work well when placed at each supply pin.

For good AC performance, parasitic capacitance should be kept to a minimum, especially at the inverting input. When ground plane construction is used, it should be removed from the area near the inverting input to minimize any stray capacitance at that node. Carbon or Metal-Film resistors are acceptable with the Metal-Film resistors giving slightly less peaking and bandwidth because of additional series inductance. Use of sockets. particularly for the SO package, should be avoided if possible. Sockets add parasitic inductance and capacitance, which will result in additional peaking and overshoot.

#### **Current Limiting**

The ISL28190 and ISL28290 have no internal current-limiting circuitry. If the output is shorted, it is possible to exceed the Absolute Maximum Rating for output current or power dissipation, potentially resulting in the destruction of the device. This is why output short circuit current is specified and tested with  $R_L = 10\Omega$ .

Submit Document Feedback FN6247.10 11 intersil July 22, 2014

#### **Power Dissipation**

It is possible to exceed the +125°C maximum junction temperatures under certain load and power-supply conditions. It is therefore important to calculate the maximum junction temperature (T<sub>JMAX</sub>) for all applications to determine if power supply voltages, load conditions, or package type need to be modified to remain in the safe operating area. These parameters are related as follows:

$$T_{JMAX} = T_{MAX} + (\theta_{JA} x PD_{MAXTOTAL})$$

(EQ. 1)

#### where:

- P<sub>DMAXTOTAL</sub> is the sum of the maximum power dissipation of each amplifier in the package (PD<sub>MAX</sub>)

- ullet PD<sub>MAX</sub> for each amplifier can be calculated as follows:

$$PD_{MAX} = 2*V_S \times I_{SMAX} + (V_S - V_{OUTMAX}) \times \frac{V_{OUTMAX}}{R_L}$$

(EQ. 2)

where T<sub>MAX</sub> = Maximum ambient temperature

- $\theta_{JA}$  = Thermal resistance of the package

- PD<sub>MAX</sub> = Maximum power dissipation of 1 amplifier

- V<sub>S</sub> = Supply voltage

- IMAX = Maximum supply current of 1 amplifier

- V<sub>OUTMAX</sub> = Maximum output voltage swing of the application

- R<sub>L</sub> = Load resistance

For additional products, see <a href="www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

Submit Document Feedback 12 intersil FN6247.10

July 22, 2014

### **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest revision.

| DATE             | REVISION  | CHANGE                                                                                                     |

|------------------|-----------|------------------------------------------------------------------------------------------------------------|

| July 22, 2014    | FN6247.10 | page 4 - Updated Thermal Information table.                                                                |

|                  |           | Updated location of note references.                                                                       |

|                  |           | Updated POD L10.1.8x1.4A: Bottom view- added chamfer dimension C0.10.                                      |

|                  |           | Land pattern - removed the chamfer lead footprint, added footprint tip to tip dimension (2.20 & 1.80).     |

|                  |           | Added SOIC package for ISL28290 to description on page 1.                                                  |

| January 18, 2012 | FN6247.9  | "Ordering Information" on page 1:                                                                          |

|                  |           | Added Eval Board ISL28190EVAL1Z                                                                            |

|                  |           | ISL28190FHZ-T7 - Pkg. Dwg. # changed from MDP0038 TO P6.064A                                               |

|                  |           | ISL28290FUZ - Pkg. Dwg. # changed from MDP0043 to M10.118A                                                 |

|                  |           | ISL28290FBZ - Pkg. Dwg. # changed from MDP0027 to M8.15E                                                   |

|                  |           | Changed µTDFN and TQFN to ultra matching package outline drawing descriptions                              |

|                  |           | Added MSL Note 5 and SOT-23 Note 4                                                                         |

|                  |           | "Thermal Information" on page 4:                                                                           |

|                  |           | 10 Ld UTQFN $\theta_{JA}$ changed from "180" to "143"                                                      |

|                  |           | 8 LD SOIC $\theta_{JA}$ changed from "125" to "110"                                                        |

|                  |           | "Electrical Specifications" table change on page 5:                                                        |

|                  |           | Updated note in Min Max column of spec tables from "Parameters with MIN and/or MAX limits are 100% tested  |

|                  |           | at +25°C, unless otherwise specified. Temperature limits established by characterization and are not       |

|                  |           | production tested." to "Compliance to datasheet limits is assured by one or more methods: production test, |

|                  |           | characterization and/or design."                                                                           |

|                  |           | "Typical Performance Curves" change on page 10:                                                            |

|                  |           | Added Figure 29 "INPUT COMMON MODE VOLTAGE vs TEMPERATURE"                                                 |

|                  |           | Updated Package Outline Drawings:                                                                          |

|                  |           | Page 14 - MDP0038 to P6.064A - chgd from multiple pkgs to individual no dimension changes                  |

|                  |           | Page 17 - MDP0027 to M8.15E - chgd from multiple pkgs to individual no dimension changes                   |

|                  |           | Page 18 - MDP0043 to M10.118A - chgd from multiple pkgs to individual no dimension changes                 |

### **About Intersil**

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at www.intersil.com.

You may report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at www.intersil.com/support

Submit Document Feedback 13 intersil FN6247.10

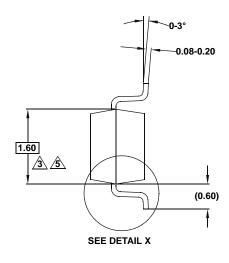

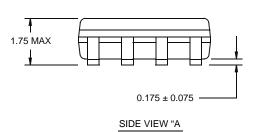

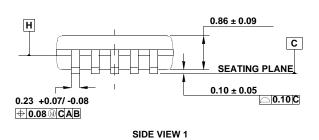

#### P6.064A

6 LEAD SMALL OUTLINE TRANSISTOR PLASTIC PACKAGE Rev  $0,\,2/10$

**END VIEW**

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to ASME Y14.5M-1994.

- 3. Dimension is exclusive of mold flash, protrusions or gate burrs.

- 4. Foot length is measured at reference to guage plane.

- 5. This dimension is measured at Datum "H".

- 6. Package conforms to JEDEC MO-178AA.

Submit Document Feedback 14 intersil FN6247.10

July 22, 2014

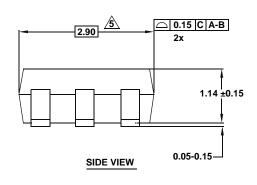

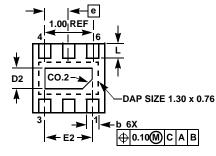

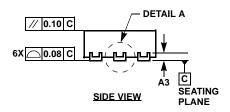

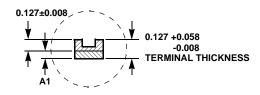

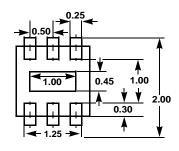

### Ultra Thin Dual Flat No-Lead Plastic Package (UTDFN)

**BOTTOM VIEW**

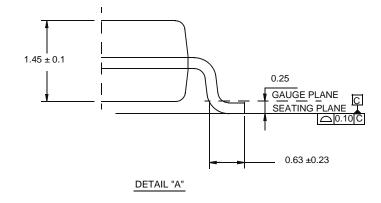

**DETAIL A**

LAND PATTERN 6

L6.1.6x1.6A 6 LEAD ULTRA THIN DUAL FLAT NO-LEAD PLASTIC PACKAGE

| SYMBOL | MIN      | NOMINAL   | MAX  | NOTES |  |

|--------|----------|-----------|------|-------|--|

| Α      | 0.45     | 0.50      | 0.55 | -     |  |

| A1     | -        | -         | 0.05 | -     |  |

| А3     |          | 0.127 REF |      |       |  |

| b      | 0.15     | 0.20      | 0.25 | -     |  |

| D      | 1.55     | 1.60      | 1.65 | 4     |  |

| D2     | 0.40     | 0.45      | 0.50 | -     |  |

| E      | 1.55     | 1.60      | 1.65 | 4     |  |

| E2     | 0.95     | 1.00      | 1.05 | -     |  |

| е      | 0.50 BSC |           |      | -     |  |

| L      | 0.25     | 0.30      | 0.35 | -     |  |

Rev. 1 6/06

#### NOTES:

- 1. Dimensions are in mm. Angles in degrees.

- 2. Coplanarity applies to the exposed pad as well as the terminals. Coplanarity shall not exceed 0.08mm.

- 3. Warpage shall not exceed 0.10mm.

- 4. Package length/package width are considered as special characteristics.

- 5. JEDEC Reference MO-229.

- 6. For additional information, to assist with the PCB Land Pattern Design effort, see Intersil Technical Brief TB389.

Submit Document Feedback 15 intersil FN6247.10

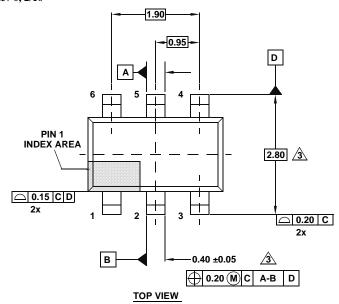

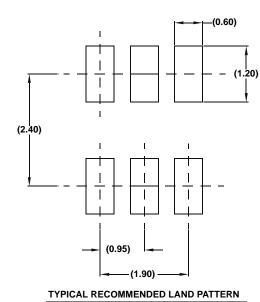

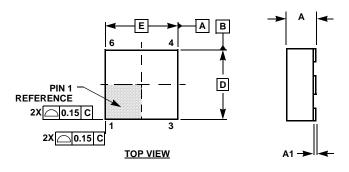

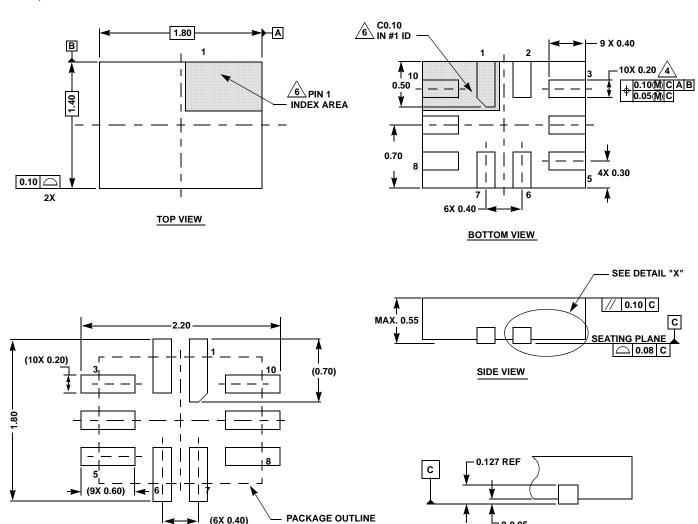

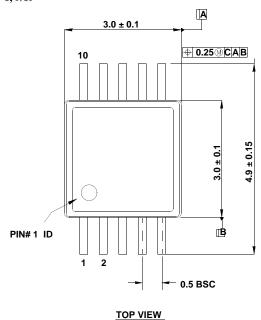

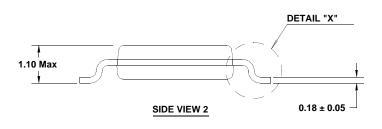

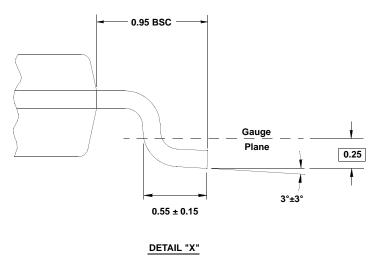

#### L10.1.8x1.4A

10 LEAD ULTRA THIN QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 6, 8/13

(6X 0.40)

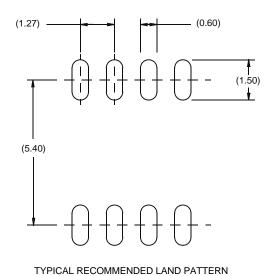

TYPICAL RECOMMENDED LAND PATTERN

#### NOTES:

- 1. Dimensions are in millimeters. Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to ASME Y14.5m-1994.

- Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

0-0.05

DETAIL "X"

- Lead width dimension applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. JEDEC reference MO-255.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

Submit Document Feedback 16 intersil FN6247.10 July 22, 2014

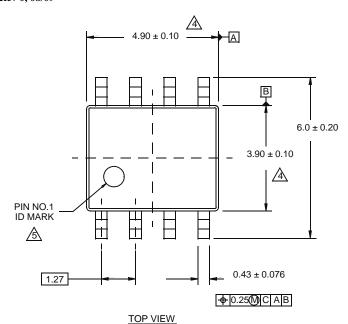

#### M8.15E

8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE Rev 0, 08/09

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal ± 0.05

- Dimension does not include interlead flash or protrusions.

Interlead flash or protrusions shall not exceed 0.25mm per side.

- 5. The pin #1 identifier may be either a mold or mark feature.

- 6. Reference to JEDEC MS-012.

Submit Document Feedback 17 intersil FN6247.10

July 22, 2014

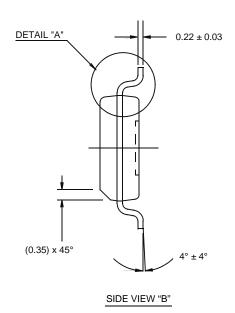

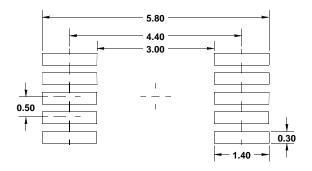

M10.118A (JEDEC MO-187-BA)

10 LEAD MINI SMALL OUTLINE PLASTIC PACKAGE (MSOP)

Rev 0, 9/09

TYPICAL RECOMMENDED LAND PATTERN

#### NOTES:

- 1. Dimensions are in millimeters.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Plastic or metal protrusions of 0.15mm max per side are not included.

- Plastic interlead protrusions of 0.25mm max per side are not included.

- 5. Dimensions "D" and "E1" are measured at Datum Plane "H".

- 6. This replaces existing drawing # MDP0043 MSOP10L.

Submit Document Feedback 18 intersil FN6247.10

July 22, 2014

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

### **Intersil**:

<u>ISL28190EVAL1Z</u> <u>ISL28190FHZ-T7</u> <u>ISL28190FRUZ-T7</u> <u>ISL28290EVAL1Z</u> <u>ISL28290FBZ</u> <u>ISL28290FBZ-T7</u> ISL28290FRUZ-T7 ISL28290FUZ ISL28290FUZ-T7