# ConnectCore<sup>™</sup> 9M 2443 and Wi-9M 2443 Hardware Reference

90000952\_F

Release date: May 2011

© 2011 Digi International Inc. All rights reserved.

Digi, Digi International, the Digi logo, a Digi International Company, Digi JumpStart Kit and ConnectCore are trademarks or registered trademarks of Digi International, Inc. in the United States and other countries worldwide. All other trademarks are the property of their respective owners.

All other trademarks mentioned in this document are the property of their respective owners. Information in this document is subject to change without notice and does not represent a commitment on the part of Digi International.

Digi provides this document "as is," without warranty of any kind, either expressed or implied, including, but not limited to, the implied warranties of fitness or merchantability for a particular purpose. Digi may make improvements and/or changes in this manual or in the product(s) and/or the program(s) described in this manual at any time.

This product could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes may be incorporated in new editions of the publication.

| Cha | pter 1: About the Module                 | . 10     |

|-----|------------------------------------------|----------|

|     | Features and functionality               |          |

|     | Block diagrams                           | 15       |

|     | CPU                                      | 15       |

|     | Module                                   | 16       |

|     | Detailed module description              | 17       |

|     | Configuration                            | 17       |

|     | Power Supply                             | 17       |

|     | Power management                         | 18       |

|     | NORMAL mode                              |          |

|     | IDLE mode                                | 19       |

|     | STOP mode                                | 19       |

|     | SLEEP mode                               | 20       |

|     | Wake-up event                            |          |

|     | Reset                                    |          |

|     | Memory                                   |          |

|     | DDR SDRAM memory                         |          |

|     | NAND Flash memory                        |          |

|     | Configuration pins - CPU module          |          |

|     | Chip selects                             |          |

|     | Chip select memory map                   |          |

|     | Multiplexed GPIO pins                    |          |

|     | S3C2443X Port Configuration              |          |

|     | Interfaces                               |          |

|     | RTC                                      |          |

|     | UART interface                           |          |

|     | SPI interface                            |          |

|     | I2C interface                            |          |

|     | USB interface                            |          |

|     | Ethernet interface                       |          |

|     | WLAN interface                           |          |

|     | A/D converter and touch screen interface |          |

|     | Touch screen interface modes             |          |

|     | Reset controller                         |          |

|     | JTAG                                     |          |

|     | Common features                          |          |

|     | Watchdog timer                           |          |

|     | IIS-Bus interface                        |          |

|     | IIS block diagram:                       |          |

|     | IIS-Bus format                           |          |

|     | Camera interface                         |          |

|     | AC97 Controller                          |          |

|     | SD host interface                        |          |

|     | PWM timer                                | 44<br>45 |

|     | Clock output                             |          |

| CF/ATA                                 | 45 |

|----------------------------------------|----|

| PC card controller                     | 45 |

| ATA controller                         | 46 |

| High-speed MMC                         | 46 |

| High speed SPI                         | 47 |

| External address/data bus              | 47 |

| WLAN connectors                        | 47 |

| LCD controller display features        | 49 |

| STN LCD displays                       | 49 |

| TFT LCD displays                       | 49 |

| Common features                        | 50 |

| Module pinout                          | 50 |

| System connector X1                    | 50 |

| System connector X2                    | 56 |

| Configuration pins - CPU               | 61 |

|                                        |    |

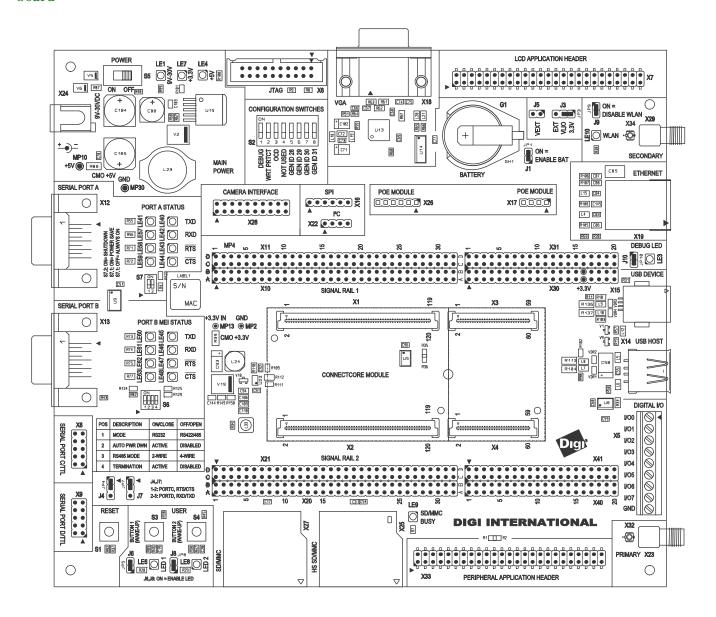

| Chapter 2: About the Development Board | 62 |

| What's on the development board?       |    |

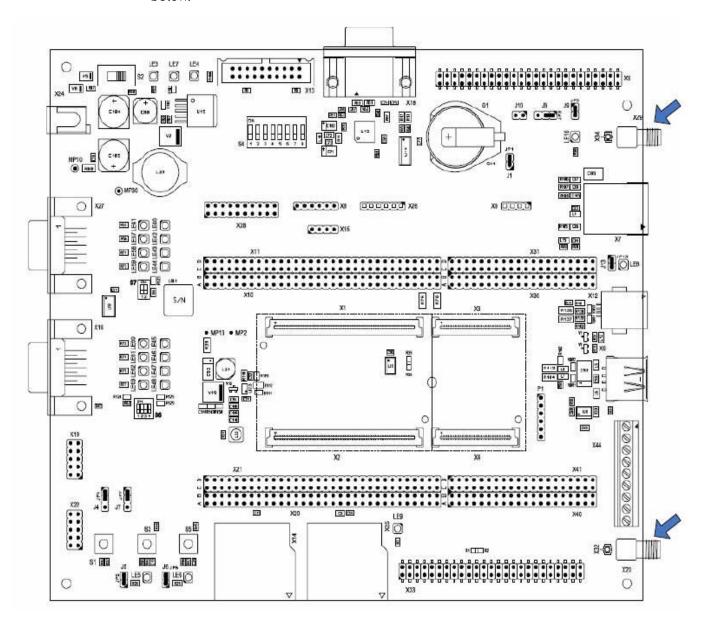

| The development board                  | 63 |

| User interface                         | 64 |

| Power management                       |    |

| General information                    |    |

| Power supply                           |    |

| 3.3VDC power controller - VLIO         |    |

| Power LEDs                             | 65 |

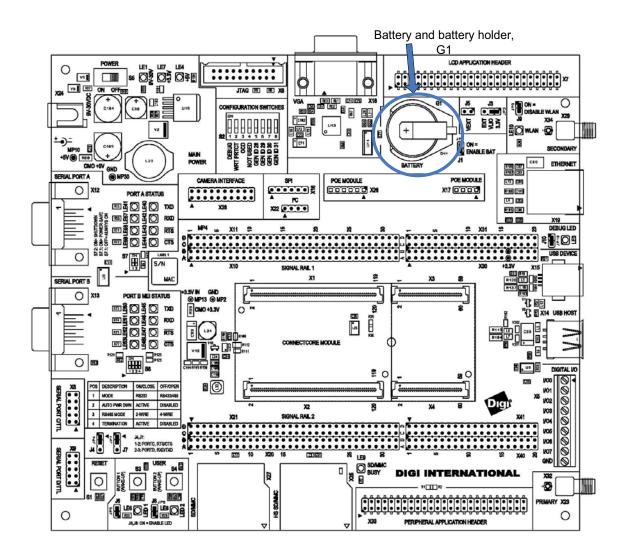

| Coin cell for RTC                      |    |

| Current measuring option               |    |

| Reset                                  |    |

| JTAG interface                         | 65 |

| I <sup>2</sup> C interface             |    |

| PoE connectors                         | 65 |

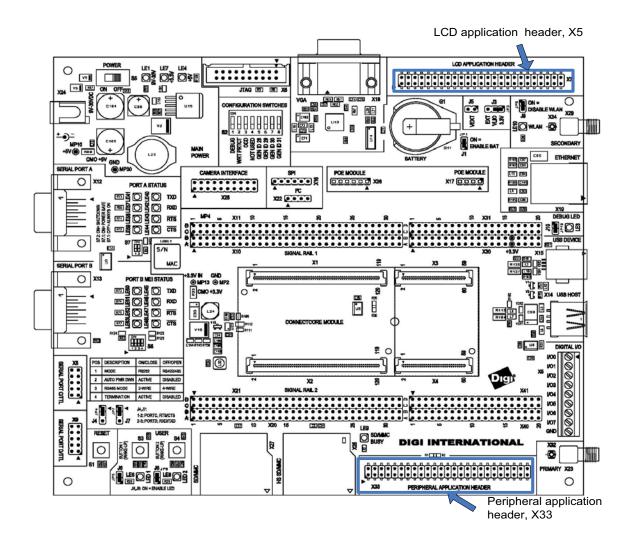

| Peripheral application connector       | 66 |

| LCD Application Kit Connector          | 66 |

| VGA interface                          | 66 |

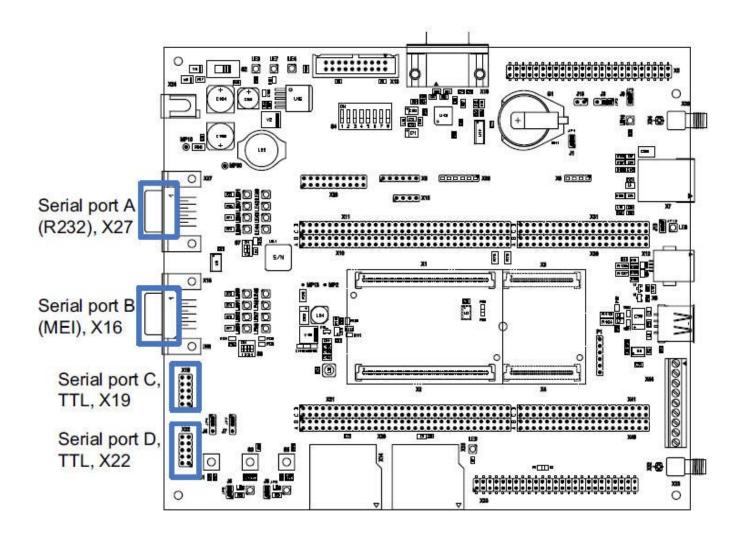

| UARTs                                  | 66 |

| UART A - console                       | 66 |

| UART B - UART / MEI                    | 66 |

| UART C - TTL interface                 | 66 |

| UART D - TTL interface                 | 66 |

| SPI interface(s)                       |    |

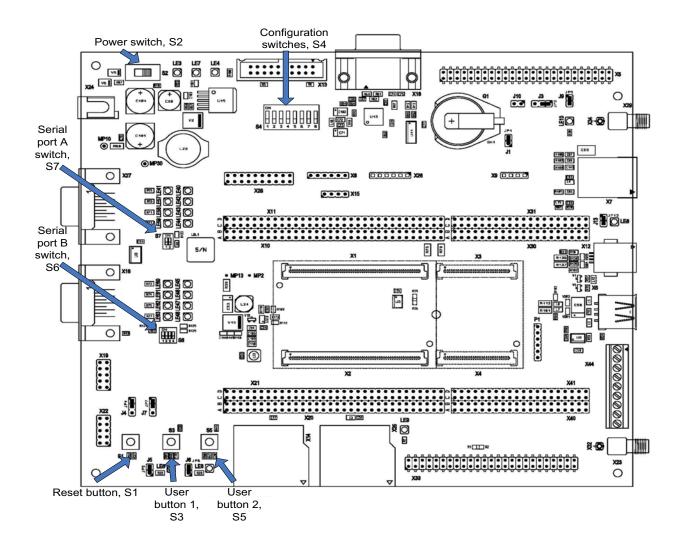

| Switches and push-buttons              | 68 |

| Reset control, S1                      |    |

| Power switch, S2                       |    |

| Legend for multi-pin switches          | 69 |

| Module configuration switches, \$4     | 69 |

| Serial port B MEI configuration switches                      | . 69 |

|---------------------------------------------------------------|------|

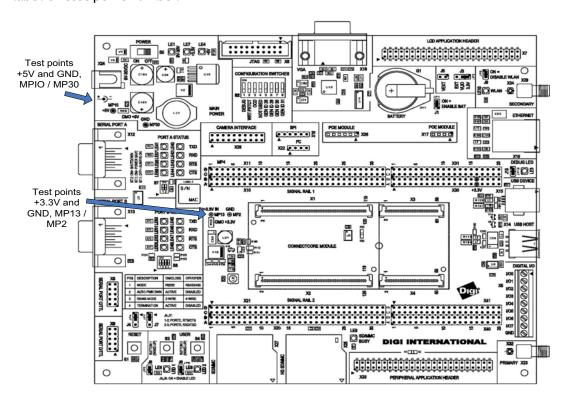

| Test points                                                   | . 70 |

| Numbers and description                                       | . 70 |

| Factory default interface configuration for development board | . 71 |

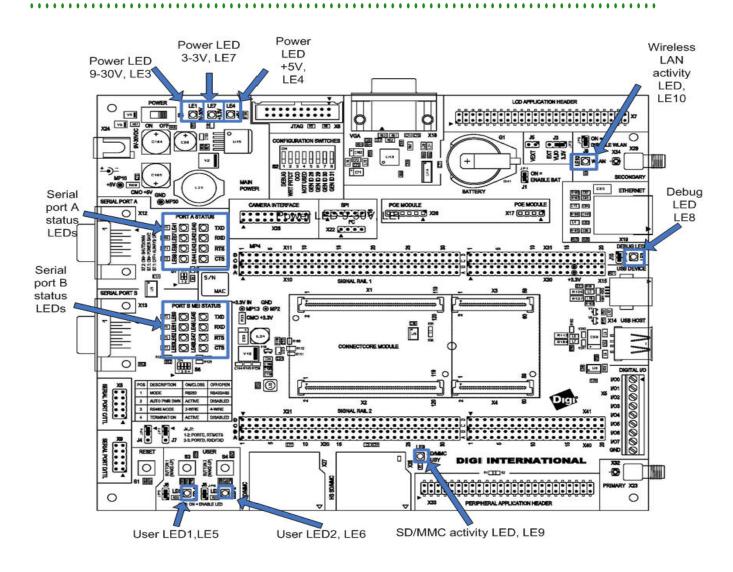

| LEDs                                                          | . 72 |

| WLAN, LE10                                                    | . 72 |

| Power LEDs, LE3, LE4, and LE7                                 | . 72 |

| User LEDs, LE5 and LE6                                        | . 73 |

| Serial status LEDs                                            | . 73 |

| Status LEDs Serial port A                                     | . 73 |

| Status LEDs Serial port B                                     | . 73 |

| Debug, LE8                                                    | . 73 |

| Battery and battery holder                                    | . 74 |

| Serial UART ports                                             | . 75 |

| Serial port A, RS232, X27                                     | . 75 |

| Serial port B, MEI interface, X16                             | . 77 |

| Serial port C, TTL interface, X19                             | . 77 |

| Serial port D, TTL interface, X22                             | . 78 |

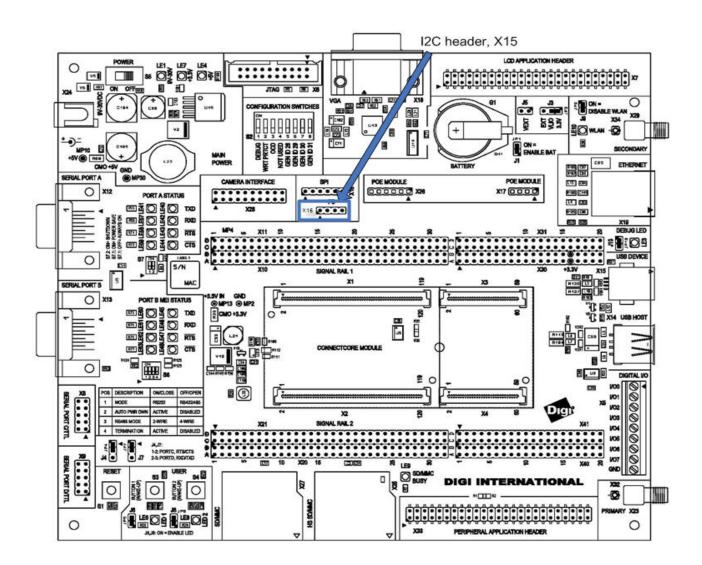

| I2C interface                                                 | . 79 |

| I2C connector, X15                                            | . 79 |

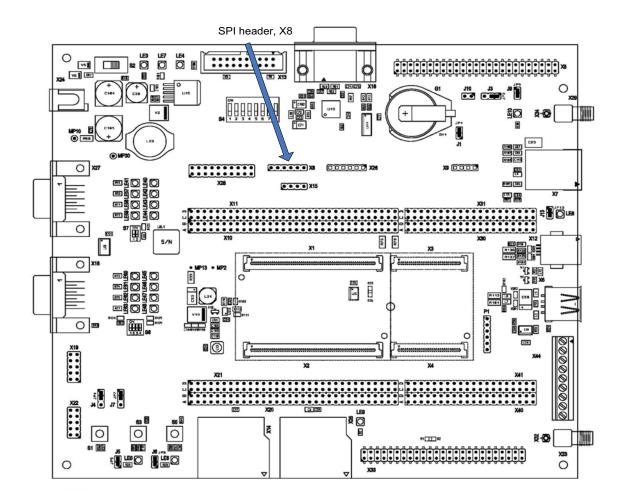

| SPI interface                                                 | . 80 |

| X8-SPI connector                                              | . 80 |

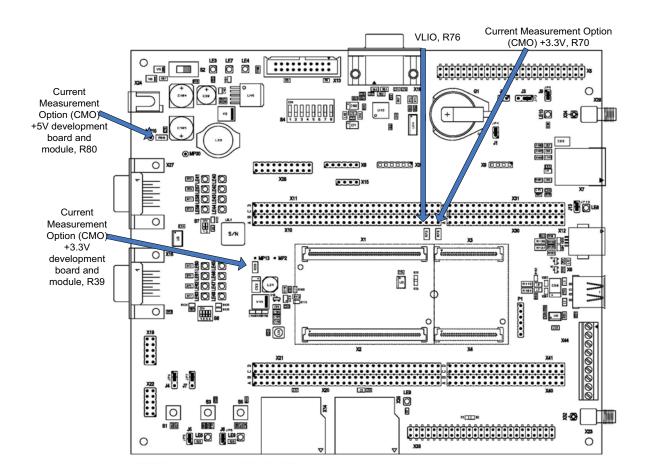

| Current Measurement Option                                    | . 81 |

| Measurement options                                           | . 81 |

| How the CMO works                                             | . 82 |

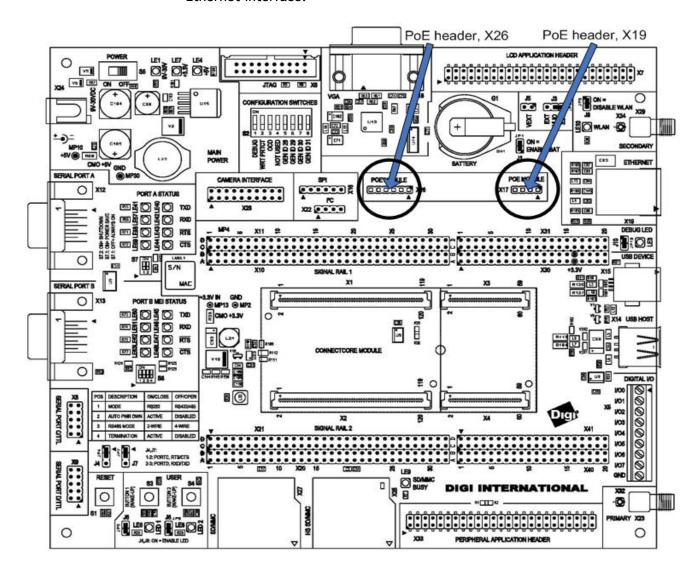

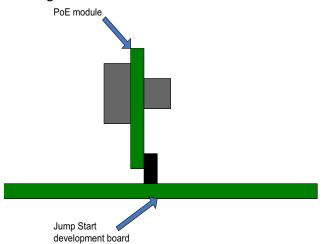

| PoE module connectors - IEEE802.3af                           | . 83 |

| The PoE module                                                | . 84 |

| PoE connector (power in), X19                                 | . 84 |

| PoE connector (power out), X26                                | . 84 |

| POE_GND                                                       | . 84 |

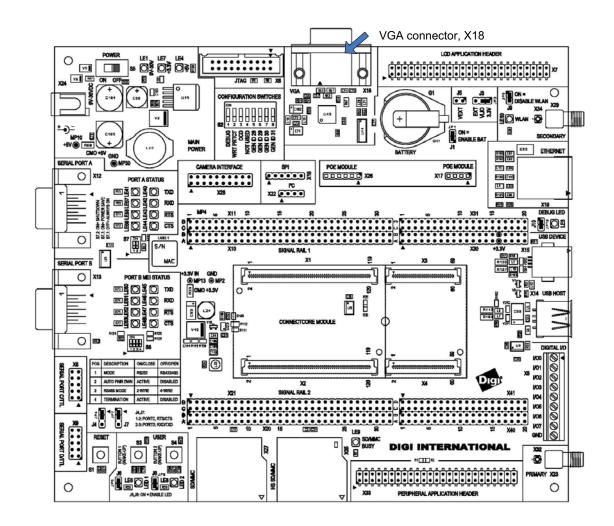

| VGA connector                                                 | . 85 |

| VGA connector, X18                                            | . 85 |

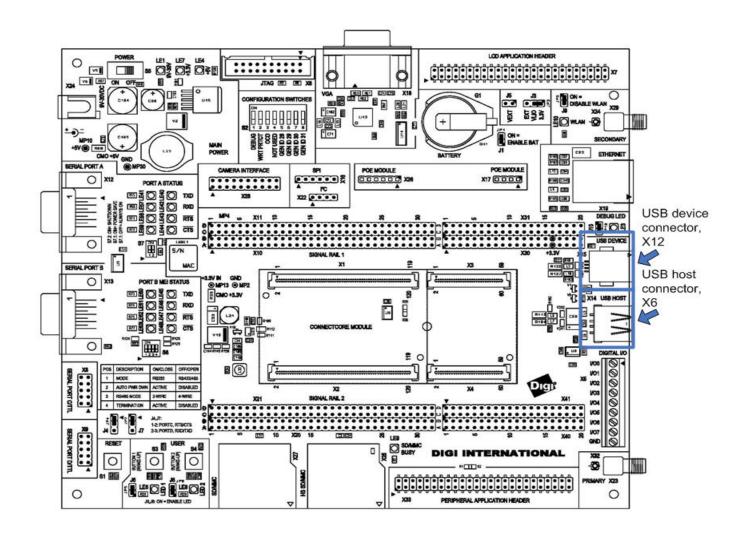

| USB connectors                                                | . 87 |

| USB device connector, X12                                     | . 87 |

| USB host connector, X6                                        | . 87 |

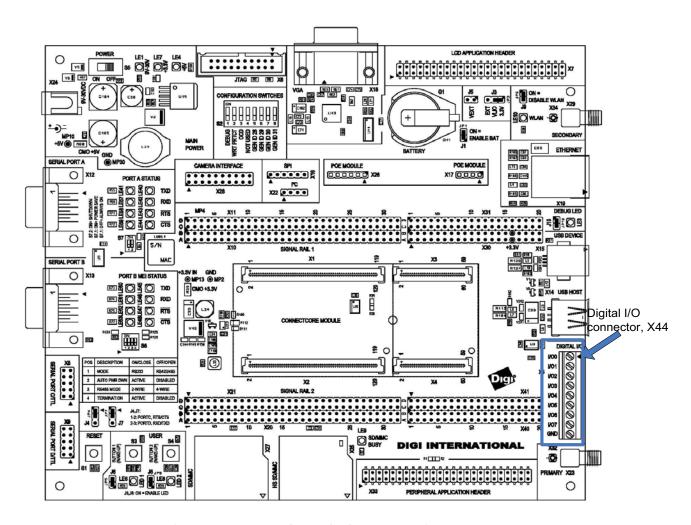

| Digital I/O                                                   | . 88 |

| I2C digital I/O expansion, X44                                | . 88 |

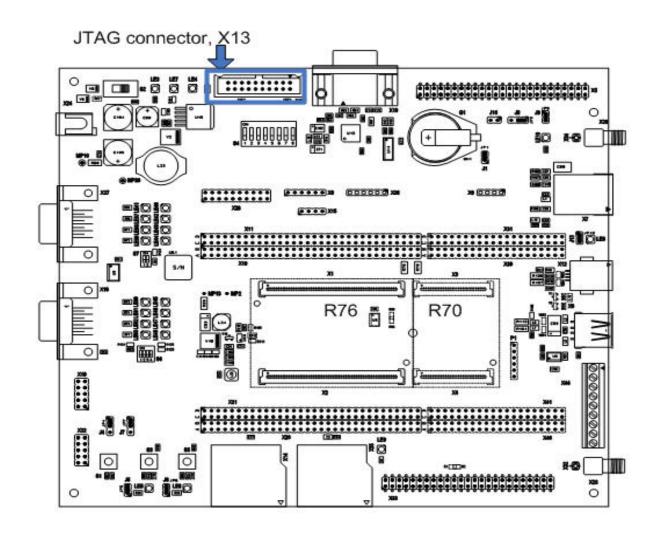

| JTAG interface                                                | . 89 |

| Standard JTAG ARM connector, X13                              | . 90 |

| Peripheral (extension) headers                                |      |

| LCD application header, X5                                    |      |

| Peripheral application header, X33                            |      |

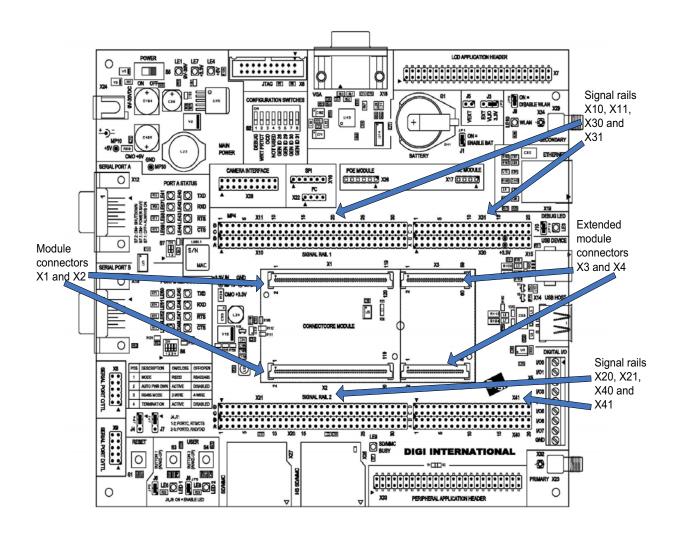

| Module connectors and signal rails                            |      |

| Signal rails                                                  |      |

| Y10 pinout                                                    | 05   |

|     | X11 pinout                                 | 96  |

|-----|--------------------------------------------|-----|

|     | X20 pinout                                 | 97  |

|     | X21 pinout                                 | 98  |

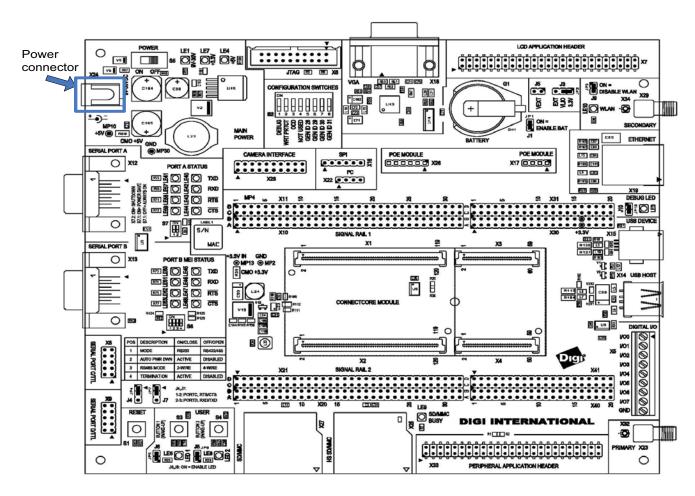

|     | Power connector                            | 99  |

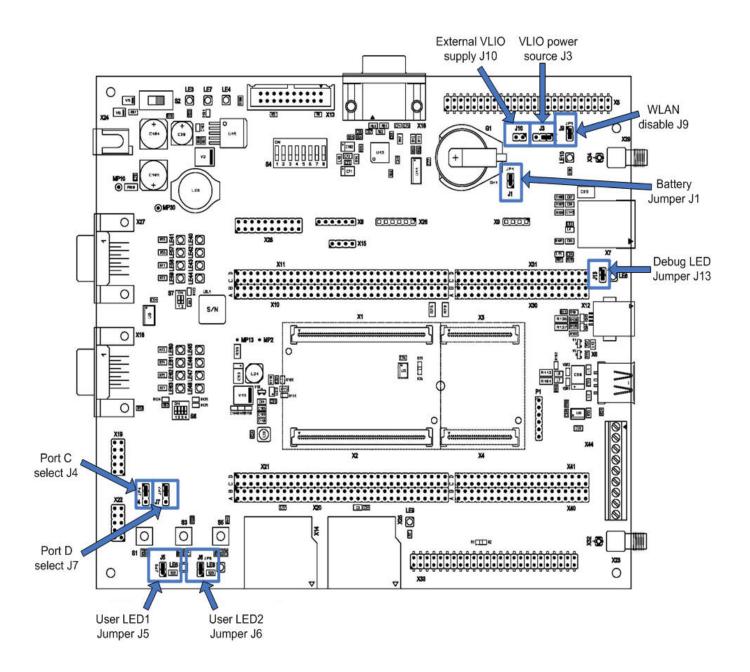

|     | Jumpers                                    | 100 |

|     | Jumpers                                    | 101 |

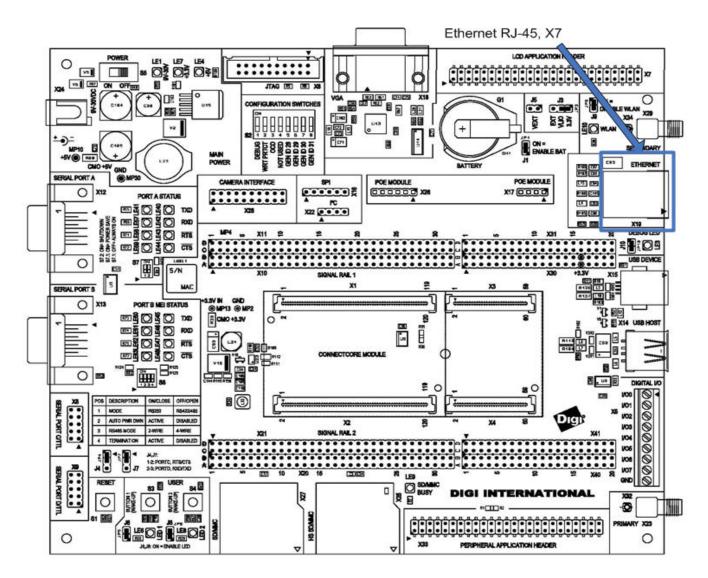

|     | Ethernet interface                         | 102 |

|     | RJ-45 pin allocation, X7                   | 103 |

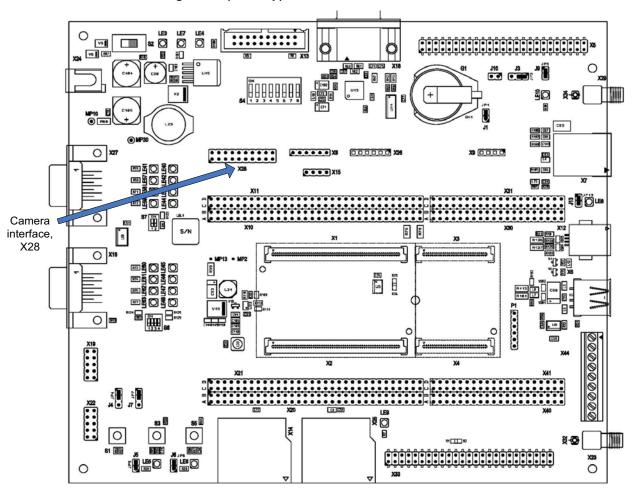

|     | Camera interface                           | 104 |

|     | WLAN Interface                             | 106 |

|     | Interfaces without special connectors      | 107 |

|     | ADC signals                                | 107 |

|     | CF signals                                 | 107 |

|     | I2S/AC97 signals                           | 108 |

|     | SPI1 signal                                | 108 |

|     | Module and test connectors                 | 109 |

|     | X1 pinout                                  | 109 |

|     | X2 pinout                                  | 119 |

|     |                                            |     |

| App | endix A: Specifications                    | 126 |

|     | Network interface                          | 126 |

|     | WLAN interface                             | 126 |

|     | Environmental specifications               | 129 |

|     | ConnectCore                                |     |

|     | 9M 2443                                    | 129 |

|     | ConnectCore                                |     |

|     | Wi-9M 2443                                 | 129 |

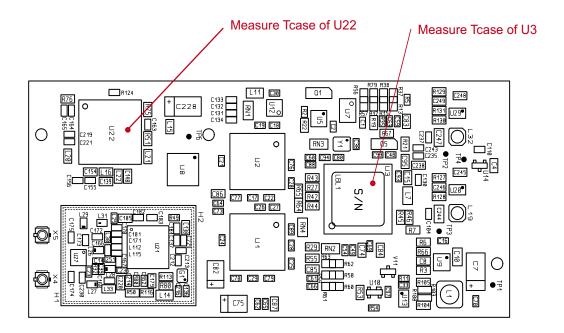

|     | Thermal specifications                     | 130 |

|     | Standard Operating Temperature Ranges      | 130 |

|     | Recommendations                            | 131 |

|     | Power requirements                         | 132 |

|     | Typical Power Requirements                 | 132 |

|     | ConnectCore 9M 2443                        | 132 |

|     | ConnectCore Wi-9M 2443                     | 133 |

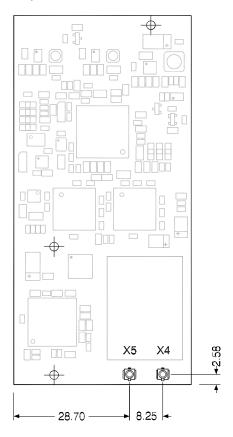

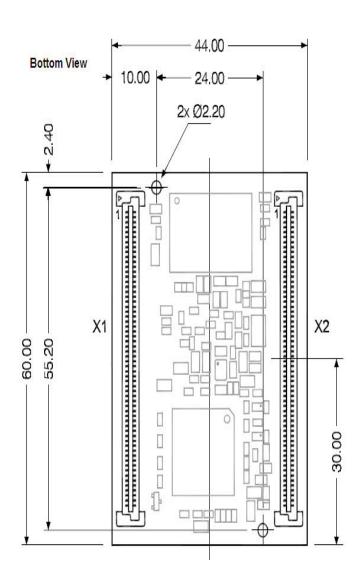

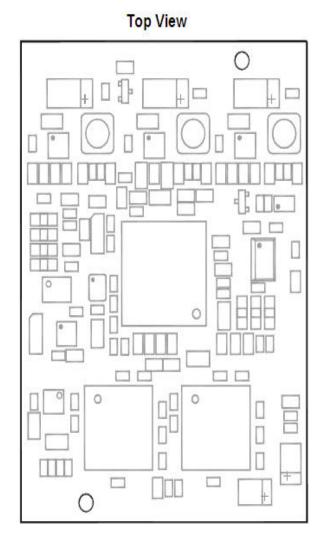

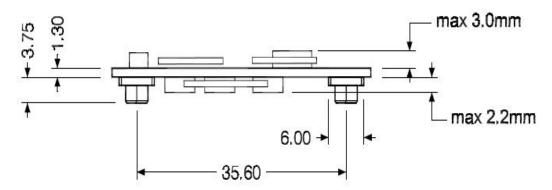

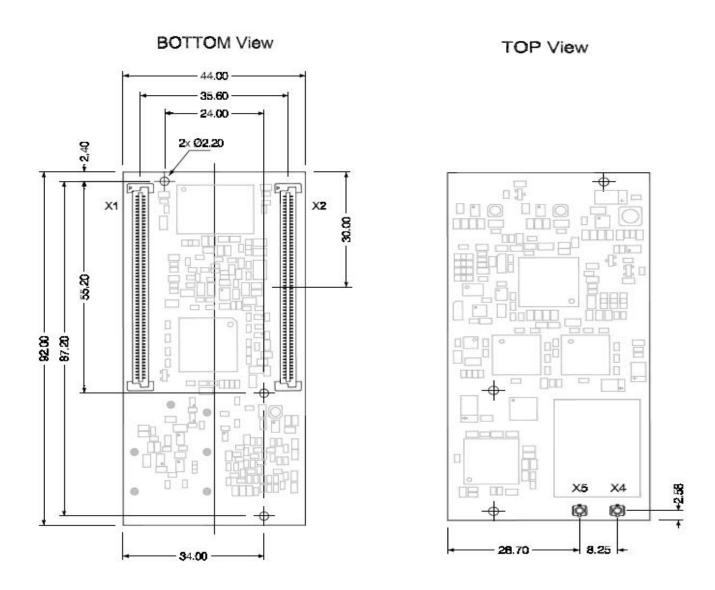

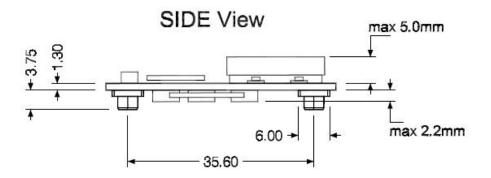

|     | Mechanical specifications                  | 135 |

|     | ConnectCore 9M 2443                        | 135 |

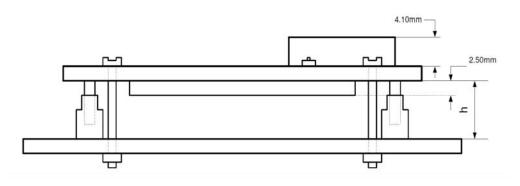

|     | ConnectCore                                |     |

|     | Wi-9M 2443                                 | 137 |

|     | Connector Reference Parts                  | 138 |

|     | Base Board Connector X1, X2                | 138 |

|     | Base Board Connector X3, X4                | 138 |

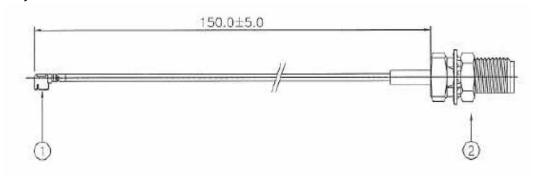

|     | Cable specification: U.FL/W.FL to RP-SMA   |     |

|     | Attributes                                 |     |

|     | Dimensions                                 | 139 |

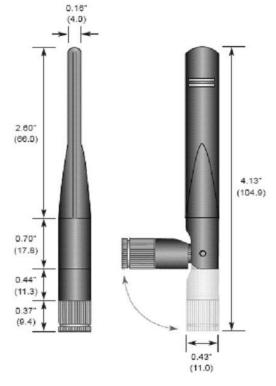

|     | Antenna specification: 802.11a/b/g antenna |     |

| Attributes                               | 140 |

|------------------------------------------|-----|

| Dimensions                               | 140 |

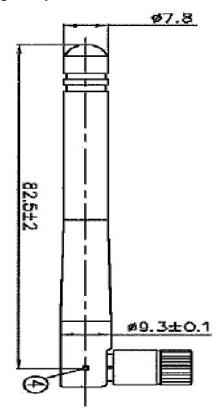

| Antenna Specification: 802.11b/g antenna | 141 |

| Attributes                               | 141 |

| Dimensions                               | 141 |

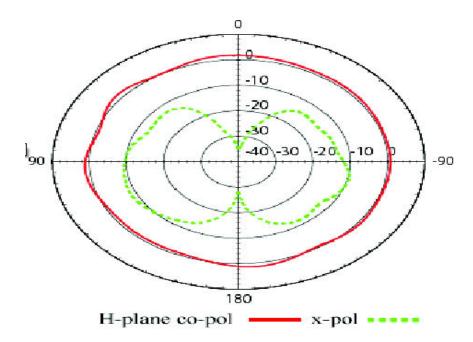

| Polar Plots                              | 142 |

| Safety statements                        | 143 |

| Appendix B: Certifications               | 144 |

| FCC Part 15 Class B                      | 144 |

# Using this Guide

This guide provides information about the Digi ConnectCore 9M and ConnectCore Wi-9M embedded core modules.

To access current technical documentation available for the S3C2443 processor please visit the Samsung website:

$http://www.samsung.com/global/business/semiconductor/productInfo.do?fmly\_id=2\\29\&partnum=S3C2443$

### Conventions used in this guide

This table describes the typographic conventions used in this guide:

| This convention | Is used for                                          |  |

|-----------------|------------------------------------------------------|--|

| italic type     | Emphasis, new terms, variables, and document titles. |  |

| monospaced type | Filenames, pathnames, and code examples.             |  |

#### Digi information

### Documentation updates

Please always check the product specific section on the Digi support website for the most current revision of this document: www.digiembedded.com/support.

### **Contact Information**

For more information about your Digi products, or for customer service and technical support, contact Digi International.

| To contact Digi International by | Use                                  |

|----------------------------------|--------------------------------------|

| Mail                             | Digi International                   |

|                                  | 1101 Bren Road East                  |

|                                  | Minnetonka, MN 55343                 |

|                                  | U.S.A                                |

| World Wide Web                   | http://www.digiembedded.com/support/ |

| email                            | http://www.digiembedded.com/support/ |

| Telephone (U.S.)                 | (952) 912-3444 or (877) 912-3444     |

| Telephone (other locations)      | +1 (952) 912-3444 or (877) 912-3444  |

#### Change Log

- 1 Added WLan information for the ConnectCore Wi-9M 2443.

- 2 Added WLan information under environmental specifications in Appendix A.

- 3 Added a new drawing on page 136.

- 4 Made minor document updates.

- 5 Revised the module pinout table for pins X1-27, X1-45, X1-46, and X2-4.

- 6 Updated the Standard Module Variants table in Chapter 1.

- 7 Added Declaration of Conformity information for the ConnectCore Wi-9M 2443.

- 8 Removed barcode (last page) from document.

- 9 Removed the mention of "EEPROM" from the Module Block Diagram in Chapter 1.

- 10 Added a note to the USB Interface table in Chapter 1.

### About the Module

C H A P T E R 1

he network-enabled ConnectCore 9M 2443 core module family delivers leading performance, low power operation, and rich peripheral interface support for a wide variety of applications, including medical devices, transportation, security/access control, networked displays, and more.

The modules utilize an innovative and power-efficient Samsung S3C2443 processor with up to 533 MHz and a multilayered memory bus architecture that allows simultaneous data transfer between processor, memory and peripherals. This optimized design eliminates the traditional bus bandwith bottlenecks that are common on other platforms. For example, updating graphical information through the LCD controller and retrieving relevant data from memory at the same time can now be realized without compromising overall performance and user experience.

Designed from the ground up with power budget conscious applications in mind, the ConnectCore 9M 2443 module family is an ideal system platform for mobile and battery-operated product designs with full off-the-shelf hard- and software support for all power management modes. The modules also offer a wide variety of onboard peripherals such as network connectivity options, a TFT/CSTN LCD controller, camera interface, audio codec interfaces, hi-speed USB device, full-speed USB host, high-speed memory card support, external mass storage, and other interfaces.

#### Features and functionality

#### 32-bit Samsung S3C2443 processor

- ARM920T core at 400/533 MHz

- 16 KB of instruction/data cache

- Up to 133 MHz memory bus speed

- Up to 1 GB of NAND Flash

- Up to 256 MB DDR SDRAM

#### LCD controller (CSTN/TFT)

- Up 1024x1024 pixels resolution

- Up to 16 grey levels/4096 colors (STN)

- Up to 24 bpp, two overlay windows (TFT)

#### Camera interface

- ITU-R BT 601/656 8-bit mode support

- 4096x4096 pixels / 2048x2048 scaling

- Mirror, 180° rotation, digital zoom in

- RGB 16/24-bit, YCbCr 4:2:0/4:2:2 output

#### I2S and AC'97 audio codec controllers

#### **Ethernet Interface**

■ 10/100 Mbit Ethernet MAC and PHY

#### **WLAN Interface**

802.11a/b/g WLAN interface with dual-diversity antenna setup

#### **USB** support with integrated PHYs

USB 2.0 device, 1-port, high-/full-speed

- USB 1.1 host, 2-port, low-/full-speed

- Ethernet interface

- 10/100 Mbit Ethernet MAC and PHY

- WLAN interface

- 802.11a/b/g WLAN interface with dual-diversity antenna setup

#### 4-channel UART

■ Up to 921 kbps, IrDA 1.0 SIR mode

#### 2-port SPI/Single-port HS-SPI

- Master and slave mode

- Up to 33 MHz

#### **I2C-Bus Interface**

- 1-ch Multi-Master IIC-Bus

- Serial, 8-bit oriented and bi-directional data transfers up to 100 Kbit/s in Standard mode or up to 400 Kbit/s in fast mode

#### SD/SDIO/MMC

- 1-/4-bit and block/stream, up to 25 MHzHigh-Speed (HS) MMC

- SD HC 1.0, SD MC 2.1, SDIO 1.0, MMC 4.2

- 1-/4-/8-bit modes, up to 50 MHz

- CE-ATA mode support

#### CF/ATA

- Compact Flash 3.0 PC card mode

- ATA/ATAPI-6 mode with PIO/UDMA

#### 10-bit ADC & Touch Screen Interface

■ 10-channel multiplexed, 500k samples/s

### Chapter 1

#### Timers/PWM

4-ch 16-bit timer/PWM, 1-ch 16-bit internal

#### 8-/16-bit external memory bus interface

#### Power management modes

- Normal, idle, stop, and sleep

- Ext IRQ, RTC alarm, tick interrupt wake-up

#### **GPIO** options

- Up to 15 external IRQs

- Up to 134 multiplexed GPIOs on the ConnectCore 9M 2443

- Up to 132 multiplexed GPIOs on the ConnectCore Wi-9M 2443

#### Watchdog Timer (16-bit)

Real-time clock with calendar function

Two 120-pin board-to-board connectors

JTAG signals available on module connectors

#### Standard module variants

The ConnectCore 9M 2443 module is currently available in the standard variants below.

| Speed   | Flash  | SDRAM | Operating temperature | P/N            |

|---------|--------|-------|-----------------------|----------------|

| 533 MHz | 128 MB | 64 MB | -40 to 85C            | CC-9M-NA37-Z1  |

| 533 MHz | 64MB   | 32 MB | -40 to 85C            | CC-9M-NA26-Z1  |

| 400 MHz | 32 MB  | 32 MB | 0 to 70C              | CC-9M-QA25-Z1  |

| 533 MHz | 128 MB | 64 MB | -40 to 65C*           | CC-W9M-NA37-XE |

| 533 MHz | 64MB   | 32 MB | -40 to 65C*           | CC-W9M-NA26-XE |

| 400 MHz | 32 MB  | 32 MB | 0 to 65C*             | CC-W9M-QA25-XE |

<sup>\*</sup> See section "Thermal specifications" in this document for details.

Please visit the Digi web site, www.digiembedded.com/support, or contact Digi for additional population options.

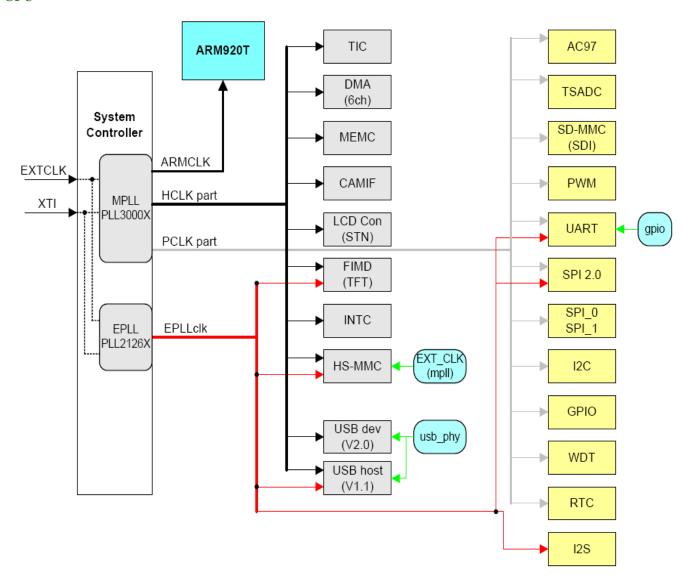

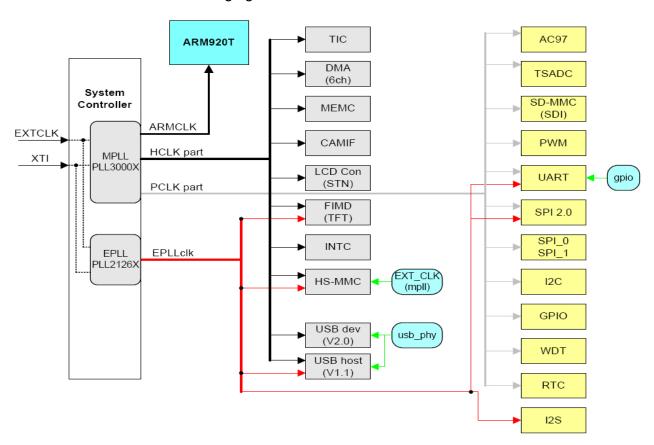

# Block diagrams

**CPU**

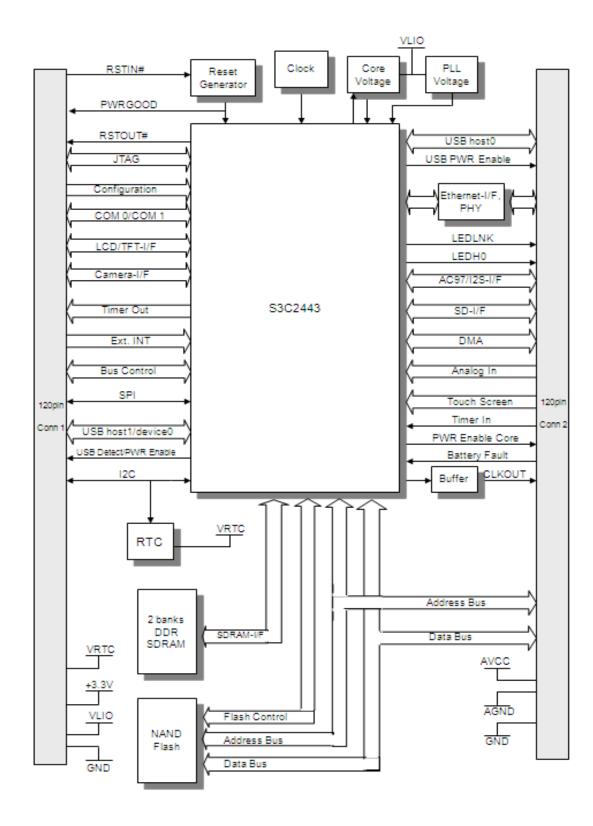

#### Module

#### Detailed module description

#### Configuration

The ConnectCore 9M 2443 Module supports 8 configuration pins:

- 4 pins provided for software configuration, which are routed to standard pin locations on the development board (CONF[7:4]).

- 4 pins provided for hardware configuration, routed to the base board at standard pin locations, including debug enable (DEBUG\_EN#) and NAND flash write protect (NAND\_FWP#).

#### **Power Supply**

The common power supply for the module is 3.3VDC. VLIO has to be connected to 3.3V on the base board.

The CPU specific core voltage of 1.2V@300MHz (1.3V@400MHz) and the voltage for VDD alive will be generated on the module from the VLIO input, while the voltage for memory power supply and I/OS is fed directly from the 3.3V.

The following requirements have to be met by the power supply:

| Power Supply                      | @400MHz                 | @533MHz                 |

|-----------------------------------|-------------------------|-------------------------|

| Module Power Supply 3.3V          | 3.3V ±5%                | $3.3V \pm 5\%$          |

| Module Power Supply VLIO          | 3.3V ±5%                | 3.3V ±5%                |

| Core Voltage                      | 1.3V (1.25V - 1.35V)    | 1.375 (1.325V - 1.425V) |

| VDD alive                         | 1.15V - 1.35V           | 1.15V - 1.2V            |

| Voltage for internal RTC          | 3V (1.8V - 3.6V)        | 3V (1.8V - 3.6V)        |

| Power Supply for ext. RTC<br>VRTC | 3V (e.g. Li-Battery)    | 3V (e.g. Li-Battery)    |

| Analog Voltage                    | 3.3V (3V - 3.6V)        | 3.3V (3V - 3.6V)        |

| VIN at common CPU pins            | $-0.3V - 3.3V \pm 0.3V$ | $-0.3V - 3.3V \pm 0.3V$ |

The voltage at pin RTCVDD has been connected to 3.3V, even though the RTC is not used. If VDD\_RTC is not used, it has to be high (VDD\_RTC=3.3V).

The S3C2443 supports DVS (dynamic voltage scaling). This means that the core voltage may be reduced to 1V in idle mode while clock frequency is also reduced.

VRTC is used to connect a battery on the base board for the external RTC on the module. If the external RTC is not used, pin VRTC doesn't need to be connected. VRTC is only used to power the external RTC on the module.

If a battery supplies the power for the module, the pin BATT\_FLT# can be connected to a comparator output on the base board. The comparator may supervise the battery voltage on the base board. The CPU does not wake up at power-off mode in case of

low battery state. If this feature is not used, the pin has to be left open, because a 10k pull up resistor is provided at the module.

Analog voltage AVCC and AGND, e.g. for a touch screen, are also provided on the module system connector.

For the power control logic, the S3C2443 has various power management schemes to keep optimal power consumption for a given task. These schemes are related to PLL, clock control logics (ARMCLK, HCLK, and PCLK) and wake up signals.

- ARMCLK is used for ARM920T core.

- HCLK is the reference clock for internal AHB bus and peripherals such as the memory controller, the interrupt controller, LCD controller, the DMA, USB host block, System Controller, Power down controller and etc.

- PCLK is used for internal APB bus and peripherals such as WDT, IIS, I2C, PWM timer, ADC, UART, GPIO, RTC and SPI etc.

The following figure shows the clock distribution:

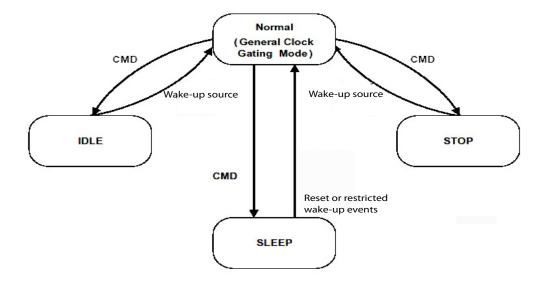

Power management

The power management block in the S3C2443 can activate four modes: NORMAL, STOP, IDLE, and SLEEP. These are described below.

#### Chapter 1

#### NORMAL mode

In General Clock Gating mode, the On/Off clock gating of the individual clock source of each IP block is performed by controlling each corresponding clock source enable bit. The Clock Gating is applied instantly whenever the corresponding bit is changed.

#### **IDLE** mode

In IDLE mode, the clock to the CPU core is stopped. The IDLE mode is activated just after the execution of the STORE instruction that enables the IDLE Mode bit. The IDLE Mode bit should be cleared after wake-up from IDLE state.

#### **STOP** mode

All clocks are stopped for minimum power consumption. Therefore, the PLL and oscillator circuits are also stopped (oscillator circuit is controlled by PWRCFG register). The STOP mode is activated after the execution of the STORE instruction that enables the STOP mode bit. The STOP Mode bit should be cleared after wake-up from STOP state.

To exit from STOP mode, external interrupt, RTC alarm, RTC Tick, or BATT\_FLT has to be activated. During the wake-up sequence, the crystal oscillator and PLL may begin to operate. The crystal oscillator settle-down time and the PLL lock-time is required for a stable ARMCLK and automatically inserted by the hardware of S3C2443X. During these lock and settle-down times, no clock is supplied to the internal logic circuitry.

The following describes the sequence initiating STOP mode:

- 1 Set the STOP Mode bit (by the main CPU).

- 2 System controller requests bus controller to finish pending transaction.

- 3 Bus controller sends acknowledgement to system controller after bus transactions are completed.

- 4 System controller requests memory controller to enter self-refresh mode, preserving SDRAM contents.

- 5 System controller waits for self-refresh acknowledgement from memory controller.

- 6 After receiving the self-refresh acknowledge, system controller disables system clocks, and switches SYSCLK source to MPLL reference clock.

- Disables PLLs and Crystal (XTI) oscillation. If OSC\_EN\_STOP bit in PWRCFG register is 'high,' then system controller does not disable crystal oscillation.

**Note:** DRAM has to be in self-refresh mode during STOP and SLEEP mode to retain valid memory data. LCD must be stopped before STOP and SLEEP mode, because DRAM can not be accessed when it is in self-refresh mode.

#### **SLEEP** mode

The block disconnects power to CPU, and the internal logic, with the exception of the wake-up logic. Activating the SLEEP mode requires two independent power sources. One of the two power sources supplies the power for the wake-up logic. The other power source supplies the CPU and internal logic, and should be controlled for power on/off. In SLEEP mode, the second power supply source for the CPU and internal logic will be turned off. The wake-up from SLEEP mode can be issued by EINT[15:0].

In SLEEP mode, VDDi, VDDiarm, VDDMPLL and VDDEPLL will be turned off, and are controlled by PWREN. If the PWREN signal is activated (H), VDDi and VDDiarm are supplied by an external voltage regulator. If PWREN pin is inactive (L), VDDi and VDDiarm are turned off.

In Power\_OFF mode 1.2V have to be supplied to the VDD alive pin, and it is also necessary to provide the I/O-voltages of 1.8V/3.3V. Therefore the LDO, which supplies VDD alive will not be switched off.

The following describes the sequence of entering SLEEP mode:

- One of the SLEEP Mode entering events is triggered by the system software or by the hardware.

- 2 System controller requests bus controller to finish pending transaction.

- 3 Bus controller sends acknowledgement to system controller after bus transactions are completed.

- 4 System controller requests memory controller to enter self-refresh mode, preserving SDRAM contents.

- 5 System controller waits for self-refresh acknowledgement from memory controller.

- 6 After receiving the self-refresh acknowledge, disables the XTAL and PLL oscillation and also disables the external power source for the internal logic by asserting the PWR\_EN pin to low state. The PWR\_EN pin is the regulator disable control signal for the internal logic power source.

The SLEEP mode exit sequence is as follows.

- System controller enables external power source by deasserting PWR\_EN to high state and initiates power settle down programmable through a register in the PWRSETCNT field of RSTCON register.

- System controller releases the System Reset (synchronously, relatively to the system clock) after the power supply is stabilized.

#### Wake-up event

When S3C2443X wakes up from the STOP Mode by an External Interrupt, an RTC alarm interrupt and other interrupts, the PLL is turned on automatically. The initial-state of S3C2443X after wake-up from the SLEEP Mode is almost the same as the Power-On-Reset state except for the contents of the external DRAM is preserved. In contrast, S3C2443X automatically recovers the previous working state after wake-up from the STOP Mode. The following table shows the states of PLLs and internal clocks after wake-ups from the power-saving modes.

| Mode before wake-up | PLL on/off after wake-up                              | SYSCLK after wake-up and before the lock time | SYSCLK after the lock<br>time by internal logic              |

|---------------------|-------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------|

| IDLE                | Unchanged                                             | PLL output                                    | PLL output                                                   |

| STOP                | PLL state ahead of entering STOP mode (PLL ON or not) | PLL reference clock                           | SYSCLK ahead of entering<br>STOP mode (PLL output or<br>not) |

| SLEEP               | Off                                                   | PLL reference clock                           | PLL reference (input) clock                                  |

- To enter sleep mode by BATT\_FLT, BATF\_CFG bits of PWRCFG register must be configured.

- Do not exit from sleep mode when BATT\_FLT is LOW; SLEEP\_CFG bit of PWRCFG register must be configured.

A Battery Fault Signal (BATT\_FLT#) is provided at the CPU to recognize the battery state of the battery at the base board, which powers the module. Therefore this pin is routed to the system connector. At the base board a comparator has to supervise the battery state and the output of the comparator delivers the BATT\_FLT# signal.

The figure below shows the power management state diagram:

#### Reset

There are 3 reset signals defined, which are routed to the system connector:

- a reset input to the module (RSTIN#)

- an output of the reset controller from the module (PWRGOOD)

- a reset output from the CPU (RSTOUT#)

- RSTIN# signal from the base board is connected to the reset generator device on the module. At the base board there could be a reset switch connected to the RSTIN# signal. A 10k pull up resistor is connected to the RSTIN# signal on the module.

- PWRGOOD must be held to low level at least 4 FCLKs to recognize the reset signal.

The low active reset of the reset controller is connected to the system via a 470R series resistor.

RSTOUT# can be used for external device reset control. RSTOUT# is a function of Watchdog Reset and Software Reset (RSTOUT# = PWRGOOD & WDTRST# & SW\_RESET).

#### Memory

### DDR SDRAM memory

On the module there are two banks provided for DDR SDRAM memory. Both banks can support a 16-bit mobile DDR memory chip. Bank 1 provides one part of a 16bit DDR SDRAM in a FBGA60 package, with 1.8V power supply.

Total size of memory is possible from 16MB (only one bank) up to 256MB (128MB each bank).

Both banks have to be populated with equal devices since they share all control signals with the exception of their chip selects. These are defined in the bank control registers BANKCFG and BANKCON1-3 and Refresh Control Register.

### NAND Flash memory

NAND Flash memory is provided, as a single Flash device. In order to support NAND flash boot loader, the S3C2443 is equipped with an internal SRAM buffer called Steppingstone. When booting, the first 4 KBytes of the NAND flash memory will be loaded into Steppingstone and the boot code loaded into Steppingstone will be executed.

Generally, the boot code will copy NAND flash content to DDR-SDRAM. Using hardware ECC, the NAND flash data validity will be checked. Upon the completion of the copy, the main program will be executed on the DDR-SDRAM.

#### Features:

- NAND Flash memory I/F: Supports 512Bytes and 2KBytes Page.

- Interface: 8-bit NAND flash memory interface bus.

- Hardware ECC generation, detection and indication (Software correction).

- SFR I/F: Supports Little Endian Mode, Byte/half word/word access to Data and ECC Data register, and Word access to other registers.

- Steppingstone I/F: Supports Little/Big Endian, Byte/half word/word access.

- The Steppingstone 4-KB internal SRAM buffer can be used for another purpose after NAND flash booting.

The write protect pin of the Flash device is routed to the hardware configuration pin of the system connector FWP#. The device can be write protected at the base board by connecting this pin to GND. At the module, a pull-up resistor is equipped.

#### Configuration pins - CPU module

There are eight configuration pins provided on the system connector. Four of them are provided as hardware configuration pins, and the other four can be used as software configuration pins. A 10k pull up resistor is provided on each signal line of the configuration pins.

The following pins on the connector are defined as hardware configuration pins:

| Signal                | Description                             |

|-----------------------|-----------------------------------------|

| DEBUGEN# Debug enable |                                         |

| FWP#                  | Write protect of internal flash         |

| CONF2                 | Hardware configuration 2 (not yet used) |

| CONF3                 | Hardware configuration 3 (not yet used) |

The following port pins are defined as software configuration pins:

| Signal | Port Pin | Description              |

|--------|----------|--------------------------|

| CONF4  | GPF2     | Software configuration 0 |

| CONF5  | GPF3     | Software configuration 1 |

| CONF6  | GPF4     | Software configuration 2 |

| CONF7  | GPF5     | Software configuration 3 |

The signal DEBUGEN# (CONFO) from the base board to the module is necessary to allow switching a connection on and off between the system reset and the JTAG reset.

| Signal   | State | Description                                             |

|----------|-------|---------------------------------------------------------|

| DEBUGEN# | High  | Switch is on, TRST# and PWRGOOD are connected (default) |

| DEBUGEN# | Low   | Switch is off, TRST# and PWRGOOD are disconnected       |

At the module a pull up resistor is provided on the DEBUGEN# signal. Therefore only a jumper to GND is necessary on the base board.

#### Chip selects

### Chip select memory map

| Name  | CPU Signal<br>name | Pin | Address<br>Range            | Size [Mb] | Usage           | Comments                        |

|-------|--------------------|-----|-----------------------------|-----------|-----------------|---------------------------------|

| SCS0# | SCS0#              | H15 | 0x3000_0000-<br>0x37FF_FFFF | 128       | SDRAM bank 0    | First bank on module            |

| SCS1# | SCS1#              | D17 | 0x3800_0000-<br>0x3FFF_FFFF | 128       | SDRAM bank 1    |                                 |

| RCS0# | RCS0#              | A2  | 0x0000_0000-<br>0x03FF_FFFF | 64        | not available   |                                 |

| RCS1# | RCS1#              | A1  | 0x0800_0000-<br>0x083F_FFFF | 64        | external, RCS1# |                                 |

| RCS2# | RCS2#              | В3  | 0x1000_0000-<br>0x103F_FFFF | 64        | external, RCS2# |                                 |

| RCS3# | RCS3#              | C1  | 0x1800_0000-<br>0x183F_FFFF | 64        | external, RCS3# |                                 |

| RCS4# | RCS4#              | C4  | 0x2000_0000-<br>0x203F_FFFF | 64        | external, RCS4# |                                 |

| RCS5# | RCS5#              | E4  | 0x2800_0000-<br>0x283F_FFFF | 64        | internal, RCS5# | Used for Ethernet<br>Controller |

## Multiplexed GPIO pins

S3C2443X Port Configuration

| Port A | Se          | On module,<br>default used as |   |         |

|--------|-------------|-------------------------------|---|---------|

| GPA15  | Output only | nWE_CF                        | - | Output  |

| GPA14  | Output only | RSMAVD                        | - | Output  |

| GPA13  | Output only | RSMCLK                        | - | Output  |

| GPA12  | Output only | nRCS5                         | - | nRCS5   |

| GPA11  | Output only | nOE_CF                        | - | Output  |

| GPA10  | RDATA_OEN   | RADDR25                       | - | RADDR25 |

| GPA9   | Output only | RADDR24                       | - | RADDR24 |

| GPA8   | Output only | RADDR23                       | - | RADDR23 |

| GPA7   | Output only | RADDR22                       | - | RADDR22 |

| GPA6   | Output only | RADDR21                       | - | RADDR21 |

| GPA5   | Output only | RADDR20                       | - | RADDR20 |

| GPA4   | Output only | RADDR19                       | - | RADDR19 |

| GPA3   | Output only | RADDR18                       | - | RADDR18 |

| GPA2   | Output only | RADDR17                       | - | RADDR17 |

| GPA1   | Output only | RADDR16                       | - | RADDR16 |

| GPA0   | Output only | RADDR0                        | - | RADDR0  |

| Port B | Sele         | On module,<br>default used as |        |                    |

|--------|--------------|-------------------------------|--------|--------------------|

| GPB10  | Input/Output | nXDREQ0                       | XDREQ0 | Input              |

| GPB9   | Input/Output | nXDACK0                       | XDACK0 | Input              |

| GPB8   | Input/Output | nXDREQ1                       | XDREQ1 | Input              |

| GPB7   | Input/Output | nXDACK1                       | XDACK1 | Input              |

| GPB6   | Input/Output | nXBREQ                        | XBREQ  | Input              |

| GPB5   | Input/Output | nXBACK                        | XBACK  | Input              |

| GPB4   | Input/Output | TCLK                          | -      | Input              |

| GPB3   | Input/Output | TOUT3                         | -      | not used, reserved |

| GPB2   | Input/Output | TOUT2                         | -      | Input              |

| GPB1   | Input/Output | TOUT1                         | -      | Input              |

| GPB0   | Output only  | TOUT0                         | -      | Input              |

| Port C | Selectable Pin Functions |           |   | On module,<br>default used as |

|--------|--------------------------|-----------|---|-------------------------------|

| GPC15  | Input/Output             | VD7       | - | VD7                           |

| GPC14  | Input/Output             | VD6       | - | VD6                           |

| GPC13  | Input/Output             | VD5       | - | VD5                           |

| GPC12  | Input/Output             | VD4       | - | VD4                           |

| GPC11  | Input/Output             | VD3       | - | VD3                           |

| GPC10  | Input/Output             | VD2       | - | VD2                           |

| GPC9   | Input/Output             | VD1       | - | Input                         |

| GPC8   | Input/Output             | VD0       | - | Input                         |

| GPC7   | Input/Output             | LCD_VF[2] | - | LCD_VF[2]                     |

| GPC6   | Input/Output             | LCD_VF[1] | - | LCD_VF[1]                     |

| GPC5   | Input/Output             | LCD_VF[0] | - | LCD_VF[0]                     |

| GPC4   | Input/Output             | VM        | - | VM                            |

| GPC3   | Input/Output             | VFRAME    | - | VFRAME                        |

| GPC2   | Input/Output             | VLINE     | - | VLINE                         |

| GPC1   | Input/Output             | VCLK      | - | Output                        |

| GPC0   | Input/Output             | LEND      | - | Input                         |

### Chapter 1

| Port D | Sele         | ons   | On module, default used as |       |

|--------|--------------|-------|----------------------------|-------|

| GPD15  | Input/Output | VD23  | -                          | VD23  |

| GPD14  | Input/Output | VD22  | -                          | VD22  |

| GPD13  | Input/Output | VD21  | -                          | VD21  |

| GPD12  | Input/Output | VD20  | -                          | VD20  |

| GPD11  | Input/Output | VD193 | -                          | VD193 |

| GPD10  | Input/Output | VD18  | -                          | VD18  |

| GDA9   | Input/Output | VD17  | -                          | Input |

| GPD8   | Input/Output | VD16  | -                          | Input |

| GPD7   | Input/Output | VD15  | -                          | VD15  |

| GPD6   | Input/Output | VD14  | -                          | VD14  |

| GPD5   | Input/Output | VD13  | -                          | VD13  |

| GPD4   | Input/Output | VD12  | -                          | VD12  |

| GPD3   | Input/Output | VD11  | -                          | VD11  |

| GPD2   | Input/Output | VD10  | -                          | VD10  |

| GPD1   | Input/Output | VD9   | -                          | Input |

| GPA0   | Input/Output | VD8   | -                          | Input |

| Port E | Selectable Pin Functions |          |            | On module,<br>default used as |

|--------|--------------------------|----------|------------|-------------------------------|

| GPE15  | Input/Output             | IICSDA   | -          | IICSDA                        |

| GPE14  | Input/Output             | IICSCL   | -          | IICSCL                        |

| GPE13  | Input/Output             | SPICLK0  | -          | SPICLK0                       |

| GPE12  | Input/Output             | SPIMOSI0 | -          | SPIMOSI0                      |

| GPE11  | Input/Output             | SPIMISO0 | -          | SPIMISO0                      |

| GPE10  | Input/Output             | SD0_DAT3 | -          | SD0_DAT3                      |

| GPE9   | Input/Output             | SD0_DAT2 | AC_nRESET  | SD0_DAT2                      |

| GPE8   | Input/Output             | SD0_DAT1 | AC_SYNC    | SD0_DAT1                      |

| GPE7   | Input/Output             | SD0_DAT0 | AC_SDO     | SD0_DAT0                      |

| GPE6   | Input/Output             | SD0_CMD  | AC_SDI     | SD0_CMD                       |

| GPE5   | Input/Output             | SD0_CLK  | AC_BIT_CLK | SD0_CLK                       |

| GPE4   | Input/Output             | I2SSDO   | AC_SDO     | Input                         |

| GPE3   | Input/Output             | I2SSDI   | AC_SDI     | Input                         |

| GPE2   | Input/Output             | CDCLK    | AC_BIT_CLK | Input                         |

| GPE1   | Input/Output             | I2SSCLK  | AC_SYNC    | Input                         |

| GPE0   | Input/Output             | I2SLRCK  | AC_nRESET  | Input                         |

| Port F | Selectable Pin Functions |       |   | On module,<br>default used as |

|--------|--------------------------|-------|---|-------------------------------|

| GPF7   | Input/Output             | EINT7 | - | Input                         |

| GPF6   | Input/Output             | EINT6 | - | Input                         |

| GPF5   | Input/Output             | EINT5 | - | Input                         |

| GPA4   | Input/Output             | EINT4 | - | Internal Input                |

| GPF3   | Input/Output             | EINT3 | - | Internal Input                |

| GPF2   | Input/Output             | EINT2 | - | Internal Input                |

| GPF1   | Input/Output             | EINT1 | - | Input                         |

| GPF0   | Input/Output             | EINT0 | - | Input                         |

| Port G | Selectable Pin Functions |        |            | On module,<br>default used as |

|--------|--------------------------|--------|------------|-------------------------------|

| GPA15  | Input/Output             | EINT23 | CARD_PWREN | Input                         |

| GPA14  | Input/Output             | EINT22 | RESET_CF   | Input                         |

| GPG13  | Input/Output             | EINT21 | nREG_CF    | Input                         |

| GPG12  | Input/Output             | EINT20 | nlNPACK    | Input                         |

| Port G | Selectable Pin Functions |        |           | On module,<br>default used as |

|--------|--------------------------|--------|-----------|-------------------------------|

| GPG11  | Input/Output             | EINT19 | nlREQ_CF  | Input                         |

| GPG10  | Input/Output             | EINT18 | -         | Input                         |

| GPG9   | Input/Output             | EINT17 | -         | Input                         |

| GPG8   | Input/Output             | EINT16 | -         | Input                         |

| GPG7   | Input/Output             | EINT15 | -         | Internal Input                |

| GPG6   | Input/Output             | EINT14 | -         | Input                         |

| GPG5   | Input/Output             | EINT13 | -         | Input                         |

| GPG4   | Input/Output             | EINT12 | LCD_PWREN | Internal Input                |

| GPG3   | Input/Output             | EINT11 | -         | Input                         |

| GPG2   | Input/Output             | EINT10 | -         | Internal output               |

| GPG1   | Input/Output             | EINT9  | -         | Internal Input                |

| GPG0   | Input/Output             | EINT8  | -         | Input                         |

| Port H | Selectable Pin Functions |            |       | On module, default used as |

|--------|--------------------------|------------|-------|----------------------------|

| GPH14  | Input/Output             | CLKOUT1    | -     | CLKOUT1                    |

| GPH13  | Input/Output             | CLKOUT0    | -     | CLKOUT0                    |

| GPH12  | Input/Output             | EXTUARTCLK | -     | Internal Input             |

| GPH11  | Input/Output             | nRTS1      | -     | nRTS1                      |

| GPH10  | Input/Output             | nCTS1      | -     | nCTS1                      |

| GPH9   | Input/Output             | mRTS0      | -     | mRTS0                      |

| GPH8   | Input/Output             | nCTS0      | -     | nCTS0                      |

| GPH7   | Input/Output             | RXD3       | nCTS2 | RXD3                       |

| GPH6   | Input/Output             | TXD2       | nRTS2 | TXD2                       |

| GPH5   | Input/Output             | TXD2       | -     | TXD2                       |

| GPH4   | Input/Output             | RXD1       | -     | RXD1                       |

| GPH3   | Input/Output             | RXD1       | -     | RXD1                       |

| GPH2   | Input/Output             | TXD1       | -     | TXD1                       |

| GPH1   | Input/Output             | RXD0       | -     | RXD0                       |

| GPH0   | Input/Output             | TXD0       | -     | TXD0                       |

| Port J | Sele                   | ctable Pin Funct | On module,<br>default used as |       |

|--------|------------------------|------------------|-------------------------------|-------|

| GPJ15  | Input/Output           | nSD1_WP          | -                             | Input |

| GPJ14  | Input/Output nSD1_CD - |                  |                               | Input |

| Port J | Selectable Pin Functions |           | On module,<br>default used as |       |

|--------|--------------------------|-----------|-------------------------------|-------|

| GPJ13  | Input/Output             | SD1_LED   | -                             | Input |

| GPJ12  | Input/Output             | CAMRESET  | -                             | Input |

| GPJ11  | Input/Output             | CAMCLKOUT | -                             | Input |

| GPJ10  | Input/Output             | CAMHREF   | -                             | Input |

| GPJ9   | Input/Output             | CAMVSYNC  | -                             | Input |

| GPJ8   | Input/Output             | CAMPCLK   | -                             | Input |

| GPJ7   | Input/Output             | CAMDATA7  | -                             | Input |

| GPJ6   | Input/Output             | CAMDATA6  | -                             | Input |

| GPJ5   | Input/Output             | CAMDATA5  | -                             | Input |

| GPJ4   | Input/Output             | CAMDATA4  | -                             | Input |

| GPJ3   | Input/Output             | CAMDATA3  | -                             | Input |

| GPJ2   | Input/Output             | CAMDATA2  | -                             | Input |

| GPJ1   | Input/Output             | CAMDATA1  | -                             | Input |

| GPJ0   | Input/Output             | CAMDATA0  | -                             | Input |

| Port L | Selectable Pin Functions |          |   | On module,<br>default used as |

|--------|--------------------------|----------|---|-------------------------------|

| GPL14  | Input/Output             | SS1      | - | Input                         |

| GPL13  | Input/Output             | SS0      | - | Input                         |

| GPL12  | Input/Output             | SPIMISO1 | - | Input                         |

| GPL11  | Input/Output             | SPIMOSI1 | - | Input                         |

| GPL10  | Input/Output             | SPICLK1  | - | Input                         |

| GPL9   | Input/Output             | SD1_CLK  | - | SD1_CLK                       |

| GPL8   | Input/Output             | SD1_CMD  | - | SD1_CMD                       |

| GPL7   | Input/Output             | SD1_DAT7 | - | SD1_DAT7                      |

| GPL6   | Input/Output             | SD1_DAT6 | - | SD1_DAT6                      |

| GPL5   | Input/Output             | SD1_DAT5 | - | SD1_DAT5                      |

| GPL4   | Input/Output             | SD1_DAT4 | - | SD1_DAT4                      |

| GPL3   | Input/Output             | SD1_DAT3 | - | SD1_DAT3                      |

| GPL2   | Input/Output             | SD1_DAT2 | - | SD1_DAT2                      |

| GPL1   | Input/Output             | SD1_DAT1 | - | SD1_DAT1                      |

| GPL0   | Input/Output             | SD1_DAT0 | - | SD1_DAT0                      |

| Port M |       |          |   | On module,<br>default used as |

|--------|-------|----------|---|-------------------------------|

| GPM1   | Input | FRnB     | - | FRnB                          |

| GPM0   | Input | RSMBWAIT | - | Internal Input                |

#### Interfaces

#### **RTC**

Instead of using the S3C2443-internal RTC, an external RTC (Dallas D1337) is implemented on the module to optimize the power consumption characteristics in sleep modes. Therefore the pin RTCVDD has to be connected to 3.3V and the pin XTIrtc has also to be connected to 3.3V, while pin XTOrtc has to be left floating. An external quartz is not necessary, if the internal RTC is not used.

The on-module RTC is connected to the I2C bus and powered by a 3V battery, which has to be mounted on the base board. If no RTC is used, the pin VRTC at the system connector can be left floating, because two Schottky diodes are used to power the RTC either from 3.3V, or from the battery. The state of this battery will not be supervised on the module.

The on-module RTC is a CMOS real time clock/calendar optimized for low power consumption. An interrupt output is provided. All address and data are transferred serially via a two-line bidirectional I2C-bus. Maximum bus speed is 400 kbit/s.

The low active interrupt output (CLK\_INT#) of the RTC is connected to interrupt input EINT7 of the CPU.

The I2C device address of the RTC is 0x68 (bits A7..A1), or 0xD0/0xD1 if expressed in an 8-bit format, including the R/W bit at the end (bits A7..A1 + R/W bit).

#### **UART** interface

The S3C2443 Universal Asynchronous Receiver and Transmitter (UART) provide four independent asynchronous serial I/O (SIO) ports, each of which can operate in Interrupt-based or DMA-based mode. In other words, the UART can generate an interrupt or a DMA request to transfer data between CPU and the UART. The UART can support bit rates up to 921.6K bps using system clock. Each UART channel contains two 64-byte FIFOs for receiver and transmitter.

On the system connector, there are the signals for two UART interfaces provided. Each interface consists of the data lines RXD/TXD and the handshake lines RTS#/CTS#. The UARTs are part of the CPU. If the handshake lines of the third UART interface (RTS2#/CTS2#) are not used, they could be used as data lines for a fourth UART interface (TXD3/RXD3).

The S3C2443 UART includes programmable baud rates, infrared (IR) transmit/receive, one or two stop bit insertion, 5-bit, 6-bit, 7-bit or 8-bit data width and parity checking.

Each UART provides a baud-rate generator, transmitter, receiver and a control unit. The baud-rate generator can be clocked by PCLK or EPLLCLK/n. UEXTCLK (external input clock) is used on the module as GPIO. The transmitter and the receiver contain 64-byte FIFOs and data shifters. Data is written to FIFO and then copied to the transmit shifter before being transmitted. The data is then shifted out by the transmit data pin (TxDn). Meanwhile, received data is shifted from the receive data pin (RxDn), and then copied to FIFO from the shifter.

The S3C2443 UART block supports also infra-red (IR) transmission and reception, which can be selected by setting the Infra-red-mode bit in the UART line control register (ULCONn).

There are four UART baud rate divisor registers including UBRDIV0, UBRDIV1, UBRDIV2 and UBRDIV3 in the UART block. The value stored in the baud rate divisor register (UBRDIVn) and dividing slot register (UDIVSLOTn), are used to determine the serial Tx/Rx clock rate (baud rate) as follows:

$DIV_VAL = (SRCCLK / (baud rate x 16)) -1$

Where DIV\_VAL should be from 1 to (216-1) and SRCCLK is either PCLK or divided EPLL clock.

DIV\_VAL can be programmed in the S3C2443 registers the following way:

DIV\_VAL = UBRDIVn + (num of 1's in UDIVSLOTn)/16

Where UBRDIVn is integer part of DIV\_VAL - and UDIVSLOTn the floating point part of DIV\_VAL.

For example, if the baud rate is 115200 bps and SRCCLK is 66 MHz, UBRDIVn and UDIVSLOTn are:

$DIV_VAL = (66000000 / (115200 x 16)) -1$

= 35.8 - 1

= 34.8

\* UBRDIVn = 34

(num of 1's in UDIVSLOTn)/16 = 0.8

(num of 1's in UDIVSLOTn) =  $12.8 \Rightarrow 13$

The table below shows the recommended value table of UDIVSLOTn register.

| Num of 1's | UDIVSLOTn                    | Num of 1's | UDIVSLOTn                    |

|------------|------------------------------|------------|------------------------------|

| 0          | 0x0000(0000_0000_0000_0000b) | 8          | 0x5555(0101_0101_0101_0101b) |

| 1          | 0x0080(0000_0000_0000_1000b) | 9          | 0xD555(1101_0101_0101_0101b) |

| 2          | 0x0808(0000_1000_0000_1000b) | 10         | 0xD5D5(1101_0101_1101_0101b) |

| 3          | 0x0888(0000_1000_1000_1000b) | 11         | 0xDDD5(1101_1101_1101_0101b) |

| 4          | 0x2222(0010_0010_0010_0010b) | 12         | 0xDDDD(1101_1101_1101_1101b) |

| 5          | 0x4924(0100_1001_0010_0100b) | 13         | 0xDFDD(1101_1111_1101_1101b) |

| 6          | 0x4A52(0100_1010_0101_0010b) | 14         | 0xDFDF(1101_1111_1101_1111b) |

| 7          | 0x54AA(0101_0100_1010_1010b) | 15         | 0xFFDF(1111_1111_1100_1111b) |

As a result, DIV\_VAL = 34.8125 = 34+13x(1/16)

The baud rate is finally:

66000000/(34.8125+1)/16 = 115167.2 baud

#### **SPI** interface

The S3C2443 provides two SPI-interfaces, each of which have two 8-bit shift registers for transmission and receiving, respectively. During an SPI transfer, data is simultaneously transmitted (shifted out serially) and received (shifted in serially).

Four I/O pin signals are associated with SPI transfers: SCK (SPICLK0,1), MISO (SPIMISO0,1) data line, MOSI (SPIMOSI0,1) data line, and the active low /SS (nSS0,1) pin.

Both 4-pin SPI interfaces are provided at the system connector (Clock, Chip-Select, Data-In and Data-Out). SPI0 interface is located at the general pins of the system connector, while SPI1 interface shares its pins with interrupt functions at the specific pins of the system connector.

#### Features:

- SPI Protocol (ver. 2.11) compatible

- 8-bit Shift Register for transmit

- 8-bit Shift Register for receive

- 8-bit Prescaler logic

- Polling, Interrupt, and DMA transfer mode

#### **I2C** interface

The I2C signals clock and data are provided at the system connector.

#### USB interface

The S3C2443 provides two USB ports. One port can only be used as host interface, the other port can be configured either as host or device interface.

S3C2443 supports 2-port USB host interfaces as follows:

- OHCI Rev 1.0 compatible

- USB Rev1.1 compatible

- Two down stream ports

- Support for both LowSpeed and FullSpeed USB devices

The Samsung USB 2.0 Controller is designed to aid the rapid implementation of the USB 2.0 peripheral device. The controller supports both High and Full speed mode. Using the standard UTMI interface and AHB interface the USB 2.0 Controller can support up to 9 Endpoints (including Endpoint0) with programmable Interrupt, Bulk and Isochronous transfer mode.

#### Features:

- Compliant to USB 2.0 specification

- Supports FS/HS dual mode operation

- EP 0 FIFO: 64 bytes

- EP 1/2/3/4 FIFO: 512 bytes double buffering

- EP 5/6/7/8 FIFO: 1024 bytes double buffering

- Convenient Debugging

- Support Interrupt, Bulk, Isochronous Transfer

One USB interface is provided at the general pins of the system connector, consisting of the data lines USBP and USBN as well as the additional signal USB\_DT/PW.

Depending on the base board, the USB interface can be realized either as host1 or device0, the signals have the following meaning:

| Signal    | USB host1              | USB device0              |

|-----------|------------------------|--------------------------|

| USBP      | Differential data+ DP1 | Differential data + PDPO |

| USBN      | Differential data- DN1 | Differential data- PDNO  |

| USB_DT/PW | USB Power Enable       | USB Detect               |

Note: The USBP and USBN lines should have 15k pull down resistors to prevent the module from hanging on bootup. Please see the development board schematic for more information.

At the module specific pins of the system connector a second host interface (host0) is provided with the differential data lines DP0 and DN0.

#### **Ethernet interface**

The ConnectCore 9M 2443 module has a 10/100Mbit Ethernet controller with integrated MAC and PHY on board.

#### Features:

- Embedded 16Kbyte FIFO for packet buffers

- Support burst-mode read for highest performance applications

- Configurable Interrupt pin with programmable hold-off timer

- Compatible with IEEE802.3, 802.3u standards

- Integrate Fast Ethernet MAC/PHY transceiver in one chip

- 10Mbps and 100Mbps data rate

- Full and half duplex operations

- 10/100Mbps Auto-negotiation operation

- Twisted pair crossover detection and auto-correction (HP Auto-MDIX)

- IEEE 802.3x flow control for full-duplex operation

- Back-pressure flow control for half-duplex operation

- Wake-on-LAN capabilities:

- Detection of a change in the network link state

- Receipt of a Magic Packet

- LED pins for various network activity indications

The Ethernet controller is connected to CS5#. Its programmable polarity interrupt output is connected to the interrupt input EINT9 of the CPU.

Global signals on the system connector only indicate the Link/Activity-LED is being used.

On the base board a transformer with 1:1 turns ratio on TX and 1:1 on RX should be used. For instance, PULSE H11022.

#### **WLAN** interface

In addition to the on-module wired Ethernet interface, the ConnectCore Wi-9M 2443 module also provides an integrated 802.11a/b/g WLAN interface. The WLAN interface is based on the Digi WM500ABG baseband processor and specifically designed for embedded products with long-term product availability requirements.

The WM500ABG is connected to the S3C2443 processor via the external 16 bit data bus and RCS4#. To write to the WM500ABG the software has to latch the most significant word by writing at addr+1 and then write the LSW to adr. The onboard logic provides a 32 bit cycle to the WM500ABG when addr is accessed. To read the WM500ABG the software has to read at addr and then read the latched MSW at addr+1.

The WLAN baseband controller can be reset through GPB3. When this signal is low, the baseband controller is in reset mode. When high, the controller is active. The interrupt signal connected to the baseband controller is EINT\_15.

Note: Please use HIROSE U.FL-LP-N-2 extraction tool for removing an U.FL cable from the ConnectCore Wi-9M 2443.

#### A/D converter and touch screen interface

The 10-bit /10-channels CMOS ADC (Analog to Digital Converter) converts the analog input signal into 10-bit binary digital codes at a maximum conversion rate of 500KSPS with 2.5MHz A/D converter clock. A/D converter operates with on-chip sample-and-hold function and power down mode is supported.

The touch screen Interface can control/select pads (ConnectCore 9M 2443, XP, XM, YP, YM) of the Touch Screen for X, Y position conversion. The touch Screen Interface provides Touch Screen Pads control logic and ADC interface logic with interrupt generation.

#### Features:

Resolution: 10-bit

Differential linearity error: 1.0 LSB

■ Integral linearity error: 2.0 LSB

Maximum conversion rate: 500 KSPS

Low power consumption

Power supply voltage: 3.3V

Analog input range: 0 ~ 3.3V

On-chip sample-and-hold function

Normal conversion mode

- Separate X/Y position conversion mode

- Auto (Sequential) X/Y position conversion mode

- Waiting for interrupt mode

## Touch screen interface modes

### 1. Normal conversion mode

Single Conversion Mode is used for General Purpose ADC Conversion. This mode can be activated by:

- 1 Set the ADCCON (ADC Control Register), and

- 2 Set the read and write to the ADCDATO (ADC Data Register 0).

- 2. Separate X/Y position conversion mode is activated as follows:

- 1 X-Position Mode writes X-Position Conversion Data to ADCDATO, so Touch Screen Interface generates the Interrupt source to Interrupt Controller.

- 2 Y-Position Mode writes Y-Position Conversion Data to ADCDAT1, so Touch Screen Interface generates the Interrupt source to Interrupt Controller.

- 3. Auto (Sequential) X/Y Position Conversion Mode is activated as follows:

- 1 Touch Screen Controller sequentially converts the X-Position or Y-Position that is touched.

- 2 After touch controller writes X-measurement data to ADCDAT0 and writes Y-measurement data to ADCDAT1, the Touch Screen Interface generates Interrupt source to Interrupt Controller in Auto Position Conversion Mode.

- 4. Waiting for Interrupt Mode is activated as follows:

- The Touch Screen Controller generates an interrupt (INT\_TC) signal when the stylus is down. Waiting for Interrupt Mode setting value is rADCTSC=0xd3; // XP\_PU, XP\_Dis, XM\_Dis, YP\_Dis, YM\_En.

- After the Touch Screen Controller generates interrupt signal (INT\_TC), the user must wait for the interrupt mode to be cleared (XY\_PST sets to the No operation Mode).

### 5. Standby Mode

Standby Mode is activated when ADCCON [2] is set to '1.'

In this mode, A/D conversion operation is halted and ADCDAT0, ADCDAT1 register contains the previous converted data.

### Reset controller

On the module there is an Analog Devices ADM811SARTZ used. This device monitors 3.3V and has RSTIN# as debounced manual reset input and through a series resistor of 470R produces PWRGOOD as output. The voltage threshold is 2.93V. Reset output length is typically 240ms.

### **JTAG**

The standard JTAG signals are provided at the system connector. A JTAG/Multi-ICE connector has to be provided at the base board for debugging.

The signal DEBUGEN# (CONFO) from the base board to the module is necessary, to be able to switch on and off a connection between the system reset and the JTAG reset.

The pull-up resistors, belonging to the JTAG interface, are placed on the module.

#### Common features

The LCD controller has a dedicated DMA that supports to fetch the image data from video buffer located in system memory. Its features also include:

- Dedicated interrupt functions (INT\_FrSyn and INT\_FiCnt)

- The system memory is used as the display memory

- Supports Multiple Virtual Display Screen (Supports Hardware Horizontal/Vertical Scrolling)

- Programmable timing control for different display panels

- Supports little and big-endian byte ordering, as well as WinCE data formats

### Watchdog timer

The S3C2443 watchdog timer is used to resume the controller operation whenever it is disturbed by malfunctions such as noise and system errors. It can be used as a normal 16-bit interval timer to request interrupt service. The watchdog timer generates the reset signal for 128 PCLK cycles.

### Features:

- 16-bit Watchdog Timer

- Interrupt request or system reset at time-out

The prescaler value and the frequency division factor are specified in the watchdog timer control (WTCON) register. Valid prescaler values range from 0 to 28-1. The frequency division factor can be selected as 16, 32, 64, or 128.

Use the following equation to calculate the watchdog timer clock frequency and the duration of each timer clock cycle:

t\_watchdog = 1/(PCLK / (Prescaler value + 1) / Division\_factor)

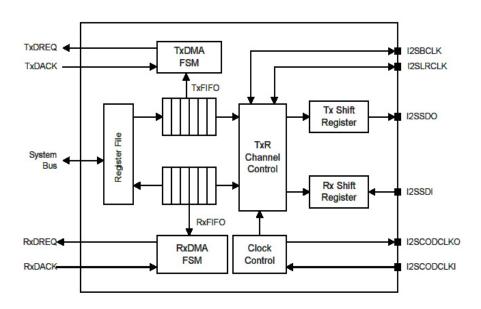

### **IIS-Bus interface**

IIS (Inter-IC Sound) interface transmits or receives sound data from or to external stereo audio code cs. For transmit and receive data, two 32x16 FIFOs (First-In-First-Out) data structures are included and DMA transfer mode for transmitting or receiving samples can be supported. IIS-specific clock can be supplied from internal system clock controller through IIS clock divider or direct clock source.

### Features:

1-ch IIS-bus for audio interface with DMA-based operation

- Serial, 8-/16-bit per channel data transfers

- 128 Bytes (64-Byte + 64-Byte) FIFO for Tx/Rx

- Supports two IIS formats (MSB-justified or LSB-justified data format)

## IIS block diagram:

### **IIS-Bus format**

The IIS bus has four lines including serial data input I2SSDI, serial data output I2SSDO, left/right channel select clock I2SLRCLK, and serial bit clock I2SBCLK; the device generating I2SLRCLK and I2SBCLK is the master.

Serial data is transmitted in 2's complement with the MSB first with a fixed position, whereas the position of the LSB depends on the word length. The transmitter sends the MSB of the next word at one clock period after the I2SLRCLK is changed. Serial data sent by the transmitter may be synchronized with either the trailing or the leading edge of the clock signal. However, the serial data must be latched into the receiver on the leading edge of the serial clock signal, and so there are some restrictions when transmitting data that is synchronized with the leading edge.

The LR channel select line indicates the channel being transmitted. I2SLRCLK may be changed either on a trailing or leading edge of the serial clock, but it does not need to be symmetrical. In the slave, this signal is latched on the leading edge of the clock signal. The I2SLRCLK line changes one clock period before the MSB is transmitted. This allows the slave transmitter to derive synchronous timing of the serial data that will be set up for transmission. Furthermore, it enables the receiver to store the previous word and clear the input for the next word.

MSB (Left) Justified

MSB-Justified (Left-Justified) format is similar to IIS bus format, except that in MSB-justified format, the transmitter always sends the MSB of the next word at the same time whenever the I2SLRCLK is changed.

LSB (Right) Justified

LSB-Justified (Right-Justified) format is opposite to the MSB-justified format. In other word, the transferring serial data is aligned with ending point of I2SLRCLK transition.

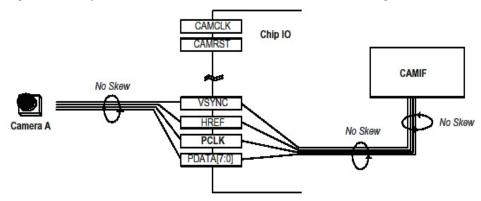

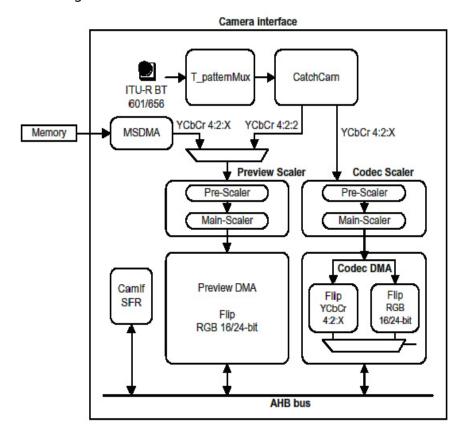

### Camera interface

The CAMIF (Camera Interface) within the S3C2443X consists of eight parts: pattern mux, capturing unit, MSDMA (Memory Scaling DMA), preview scaler, codec scaler, preview DMA, codec DMA, and SFR. The camera interface supports:

- ITU R BT-601/656 YCbCr 8-bit standard and Memory

- Maximum input size of 4096x4096 pixels (2048x2048 pixels for scaling)

- Two scalers:

One is the preview scaler, which is dedicated to generating smaller size images for previewing. The other one is the codec scaler, which is dedicated to generating codec useful images like plane type YCbCr 4:2:0 or 4:2:2. Two master DMAs can do mirror and rotate of the captured image for mobile environments. And test pattern generation can be used to calibration of input sync signals as HREF, VSYNC. Also, video sync signals and pixel clock polarity can be inverted in the camera interface side with using register setting.

### Features:

- ITU-R BT 601/656 8-bit mode support

- DZI (Digital Zoom In) capability

- Programmable polarity of video sync signals

- Max. 4096 x 4096 pixels input support (non-scaling)

- Max. 2048 x 2048 pixels input support for codec scaling and 640 x 480 pixels input support for preview scaling

- Image mirror and rotation (X-axis mirror, Y-axis mirror and 180° rotation)

- Preview DMA output image generation (RGB 16/24-bit format)

- Codec DMA output image generation (RGB 16/24-bit format or YCbCr 4:2:0/4:2:2 format)

- Capture frame control support in codec\_path

- Scan line offset support in codec\_path (YCbCr)

- YCbCr 4:2:2 codec image format interleave support

- MSDMA supports memory data for preview path input

- Image effect

CAMIF supports the following video standards:

- ITU-R BT 601 YCbCr 8-bit mode

- ITU-R BT 656 YCbCr 8-bit mode

The figure below provides an overview of the CAMIF interface signals.

All camera interface signals should have the same length.

Buffers should be Schmitt-triggered.

Below is the block diagram of the camera interface.

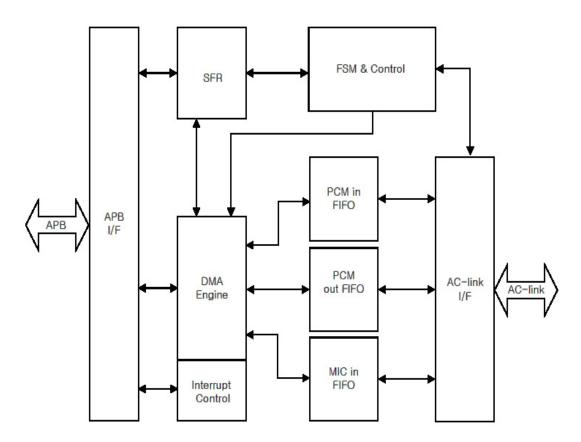

### **AC97 Controller**

The AC97 Controller Unit of the S3C2443 supports AC97 revision 2.0 features. AC97 Controller communicates with AC97 Codec using an audio controller link (AC-link). Controller sends the stereo PCM data to Codec. The external digital-to-analog converter (DAC) in the Codec then converts the audio sample to an analog audio waveform. Also, the Controller receives the stereo PCM data and the mono Mic data from the Codec and then stores them in the memories. This chapter describes the programming model for the AC97 Controller Unit. The information in this chapter requires an understanding of the AC97 revision 2.0 specifications.

Note: The AC97 Controller and the IIS Controller must not be used at the same time.

### Features:

- Independent channels for stereo PCM In, stereo PCM Out, mono MIC In.

- DMA-based operation and interrupt based operation.

- All of the channels support only 16-bit samples.

- Variable sampling rate AC97 Codec interface (48 KHz and below).

- 16-bit, 16 entry FIFOs per channel

- Only Primary CODEC support

The following shows the functional block diagram of the S3C2443 AC97 Controller. The AC97 signals form the AClink, which is a point-to-point synchronous serial

interconnect that supports full-duplex data transfers. All digital audio streams and command/status information are communicated over the AC-link.

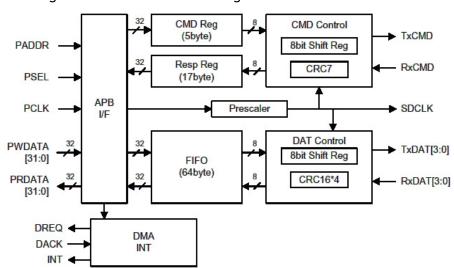

SD host interface

The S3C2443 Secure Digital Interface (SDI) can interface for SD memory card, SDIO device and Multi-Media Card (MMC).

### Features:

- SD Memory Card Spec. (ver. 1.0) / MMC Spec. (2.11) compatible

- SDIO Card Spec (ver. 1.0) compatible

- 16 words (64 bytes) FIFO (depth 16) for data Tx/Rx

- 40-bit Command Register

- 136-bit Response Register

- 8-bit Prescaler logic (Freq. = System Clock / (P + 1))

- Normal, and DMA Data Transfer Mode (byte, halfword, word transfer)

- 1bit / 4bit (wide bus) Mode & Block / Stream Mode Switch support

- DMA burst4 access support (only word transfer)

The following shows the SD host block diagram:

**PWM** timer

The S3C2443 has five 16-bit timers. Timer 0, 1, 2, and 3 have Pulse Width Modulation (PWM) function. Timer 4 has an internal timer only with no output pins. The timer 0 has a dead-zone generator, which is used with a large current device. The timer 0 and 1 share an 8-bit prescaler, while the timer 2, 3 and 4 share other 8-bit prescaler. Each timer has a clock divider, which generates 5 different divided signals (1/2, 1/4, 1/8, 1/16, and TCLK). Each timer block receives its own clock signals from the clock divider, which receives the clock from the corresponding 8-bit prescaler. The 8-bit prescaler is programmable and divides the PCLK according to the loading value, which is stored in TCFG0 and TCFG1 registers.

The timer count buffer register (TCNTBn) has an initial value which is loaded into the down-counter when the timer is enabled. The timer compare buffer register (TCMPBn) has an initial value which is loaded into the compare register to be compared with the down-counter value. This double buffering feature of TCNTBn and TCMPBn makes the timer generate a stable output when the frequency and duty ratio are changed.

Each timer has its own 16-bit down counter, which is driven by the timer clock. When the down counter reaches zero, the timer interrupt request is generated to inform the CPU that the timer operation has been completed. When the timer counter reaches zero, the value of corresponding TCNTBn is automatically loaded into the down counter to continue the next operation. However, if the timer stops, for example, by clearing the timer enable bit of TCONn during the timer running mode, the value of TCNTBn will not be reloaded into the counter.

The value of TCMPBn is used for pulse width modulation (PWM). The timer control logic changes the output level when the down-counter value matches the value of the compare register in the timer control logic. Therefore, the compare register determines the turn-on time (or turn-off time) of a PWM output.

### Features:

- Five 16-bit timers

- Two 8-bit prescalers & Two 4-bit divider

- Programmable duty control of output waveform (PWM)

- Auto reload mode or one-shot pulse mode

- Dead-zone generator

All of the Timer outputs are connected to the system connector.

### **Clock output**

At the global pins of the system connector there is a clock signal available (BCLKOUTO), which is buffered by a clock buffer and can be chosen to be either MPLL CLK, EPLL CLK, FCLK, HCLK, PCLK or DCLK. The source of this clock signal is the CLKOUTO port at the CPU, which can be programmed to different clocks, by the CLKSELO register.

The following table shows the bits [6:4] of the CLKSELO register:

| CLKSELO [6.4] | 000      | 001      | 010  | 011  | 100  | 101   | 11x      |

|---------------|----------|----------|------|------|------|-------|----------|

| CLKOUT0       | MPLL CLK | EPLL CLK | FCLK | HCLK | PCLK | DCLK0 | Reserved |

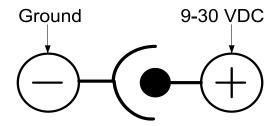

### CF/ATA