SLLS544 - SEPTEMBER 2002

# LOW POWER DISSIPATION ADSL LINE DRIVER

#### **FEATURES**

- Low Power Dissipation Increases ADSL Line **Card Density**

- Low THD of -88 dBc (100- $\Omega$ , 1 MHz)

- Low MTPR Driving +20 dBm on the Line

- -76 dBc With High Bias Setting

- 74 dBc With Low Bias Setting

- Wide Output Swing of 44VPP Differential Into a 200  $\Omega$  Differential Load (V<sub>CC</sub> = ±12 V)

- High Output Current of 600 mA (Typ)

- Wide Supply Voltage Range of  $\pm 5$  V to  $\pm 15$  V

- Pin Compatible with EL1503C and EL1508C

- Multiple Package Options

- **Multiple Power Control Modes**

- 11 mA/ch Full Bias Mode

- 7.5 mA/ch Mid Bias Mode

- 4 mA/ch Low Bias Mode

- 0.25 mA/ch Shutdown Mode

- IADJ Pin for User Controlled Bias Current

- Stable Operation Down to 3 mA/ch

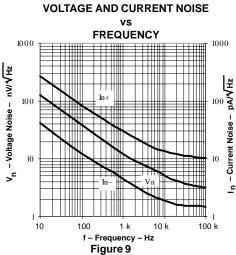

- Low Noise for Increased Receiver Sensitivity

- 3.2 nV/√Hz Voltage Noise

- 1.5 pA/√Hz Noninverting Current Noise

- 10 pA/√Hz Inverting Current Noise

#### APPLICATIONS

Ideal for Full Rate ADSL Applications

#### DESCRIPTION

The THS6182 is a current feedback differential line driver ideal for full rate ADSL systems. Its extremely low power dissipation is ideal for ADSL systems that must achieve high densities in ADSL central office rack applications. The unique architecture of the THS6182 allows the quiescent current to be much lower than existing line drivers while still achieving very high linearity without the need for excess open loop gain. Fixed multiple bias settings of the amplifiers allow for enhanced power savings for line lengths where the full performance of the amplifier is not required. To allow for even more flexibility and power savings, an IADJ pin is available to further lower the bias currents while maintaining stable operation with as little as 3 mA per channel. The wide output swing of 44 Vpp differentially with ±12V power supplies allows for more dynamic headroom, keeping distortion at a minimum. With a low 3.2 nV/ $\sqrt{\text{Hz}}$  voltage noise coupled with a low 10 pA/ $\sqrt{\text{Hz}}$  inverting current noise, the THS6182 increases the sensitivity of the receive signals, allowing for better margins and reach.

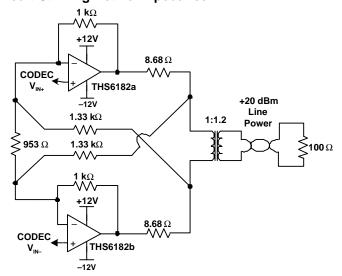

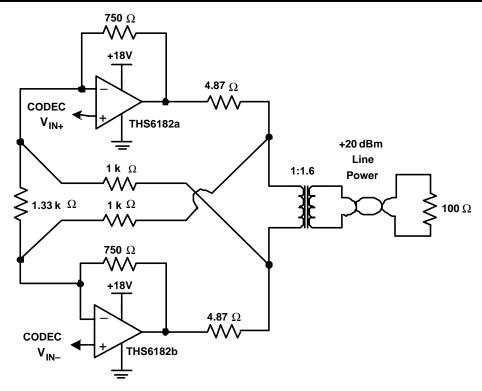

#### Typical ADSL CO Line Driver Circuit Utilizing Active Impedance

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage.

#### ORDERING INFORMATION

| PRODUCT    | PACKAGE                                   | PACKAGE<br>CODE | SYMBOL    | TA            | ORDER NUMBER | TRANSPORT<br>MEDIA |

|------------|-------------------------------------------|-----------------|-----------|---------------|--------------|--------------------|

| THOCA CODD | TSSOP-20                                  | DIA/D 00        | TI 100400 |               | THS6182PWP   | Tube               |

| THS6182PwP | PowerPAD™                                 | PWP-20          | THS6182   |               | THS6182PWPR  | Tape and reel      |

| THS6182RGU | Leadless 24-pin 5,mm x<br>4, mm PowerPAD™ | RGU–24          | 6182      | -40°C to 85°C | THS6182RGUR  | Tape and reel      |

| THS6182D   | 2010 46                                   | D 46            | TUC6492   | 40 0 10 03 0  | THS6182D     | Tube               |

| THS6182D   | SOIC-16                                   | D-16            | THS6182   |               | THS6832DR    | Tape and reel      |

| THOMASODW  | 0010.00                                   | DW 00           | TI 100400 |               | THS6182DW    | Tube               |

| THS6182DW  | SOIC-20                                   | DW-20           | THS6182   |               | THS6182DWR   | Tape and reel      |

#### PACKAGE DISSIPATION RATINGS

| PACKAGE | ΘJA      | ΘJC      | T <sub>A</sub> ≤ 25°C<br>POWER RATING <sup>(1)</sup> | T <sub>A</sub> = 70°C<br>POWER RATING <sup>(1)</sup> | T <sub>A</sub> = 85°C<br>POWER RATING(1) |

|---------|----------|----------|------------------------------------------------------|------------------------------------------------------|------------------------------------------|

| RGU-24  | 32°C/W   | 1.7°C/W  | 3.28 W                                               | 1.87 W                                               | 1.41 W                                   |

| PWP-20  | 32.6°C/W | 1.4°C/W  | 3.22 W                                               | 1.84 W                                               | 1.38 W                                   |

| D-16    | 62.9°C/W | 25.7°C/W | 1.67 W                                               | 0.95 W                                               | 0.72 W                                   |

| DW-20   | 45.4°C/W | 16.4°C/W | 2.31 W                                               | 1.32 W                                               | 0.99 W                                   |

<sup>(1)</sup> Power rating is determined with a junction temperature of 130°C. This is the point where distortion starts to substantially increase. Thermal management of the final PCB should strive to keep the junction temperature at or below 125°C for best performance.

# **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted (1)

|                   |                                                                                                  | THS6132       |  |  |

|-------------------|--------------------------------------------------------------------------------------------------|---------------|--|--|

| Supply voltage    | , V <sub>CC</sub> <sup>(2)</sup>                                                                 | ±16.5 V       |  |  |

| Input voltage, \  | /1                                                                                               | ±VCC          |  |  |

| Output current    | , I <sub>O</sub> <sup>(2)</sup>                                                                  | 1000 mA       |  |  |

| Differential inpu | ut voltage, V <sub>IO</sub>                                                                      | ±2 V          |  |  |

| Maximum junct     | Maximum junction temperature, T <sub>J</sub> (see Dissipation Rating Table for more information) |               |  |  |

| Operating free-   | -air temperature, T <sub>A</sub>                                                                 | -40°C to 85°C |  |  |

| Storage tempe     | rature, T <sub>Sgt</sub>                                                                         | 65°C to 150°C |  |  |

| Lead temperat     | ure, 1,6 mm (1/16–inch) from case for 10 seconds                                                 | 300°C         |  |  |

|                   | НВМ                                                                                              | 1000 V        |  |  |

| ESD ratings       | CDM                                                                                              | 500 V         |  |  |

|                   | MM                                                                                               | 200 V         |  |  |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> The THS6182 may incorporate a PowerPAD on the underside of the chip. This acts as a heatsink and must be connected to a thermally dissipating plane for proper power dissipation. Failure to do so may result in exceeding the maximum junction temperature that could permanently damage the device. See TI Technical Brief SLMA002 for more information about utilizing the PowerPAD thermally enhanced package.

## **RECOMMENDED OPERATING CONDITIONS**

|                                                      |               | MIN | NOM | MAX | UNIT |

|------------------------------------------------------|---------------|-----|-----|-----|------|

| Owner bound to many to M                             | Dual supply   | ±5  | ±12 | ±15 | V    |

| Supply voltage, V <sub>CC+</sub> to V <sub>CC-</sub> | Single supply | 10  | 24  | 30  | V    |

| Operating free-air temperature, TA                   |               | -40 |     | 85  | °C   |

## **ELECTRICAL CHARACTERISTICS**

over recommended operating free-air temperature range, T<sub>A</sub> = 25°C, V<sub>CC</sub> =  $\pm 12$  V, R<sub>F</sub> = 2 k $\Omega$ , Gain = +5, I<sub>ADJ</sub> = Bias1 = Bias2 = 0 V, R<sub>L</sub> = 50  $\Omega$  (unless otherwise noted)

| MOISE | /DISTORTION PI                            |                    | Г                                                               |                                  | 1     |       |     | ı       |

|-------|-------------------------------------------|--------------------|-----------------------------------------------------------------|----------------------------------|-------|-------|-----|---------|

|       | PARAMET                                   | ER                 | TEST COI                                                        |                                  | MIN   | TYP   | MAX | UNIT    |

| MTPR  | Multitone power r                         | atio               | Gain =+9.5, 163 kHz to 1.1 I<br>+20 dBm Line Power, See F       |                                  |       | -76   |     | dBc     |

|       | Receive band spi                          | ll-over            | Gain =+5, 25 kHz to 138 kHz<br>See Figure 1 for circuit         | z with MTPR signal applied,      |       | -95   |     | dBc     |

|       |                                           |                    | and                                                             | Differential load = $200 \Omega$ |       | -88   |     | JD.     |

| b     | HD Harmonic distortion, $V_{O(PP)} = 2 V$ |                    | 2 <sup>nd</sup> harmonic                                        | Differential load = $50 \Omega$  |       | -70   |     | dBc     |

| Ηυ    |                                           |                    | 3 <sup>rd</sup> harmonic                                        | Differential load = $200 \Omega$ |       | -107  |     | dD.     |

|       |                                           |                    | 3 <sup>rd</sup> narmonic                                        | Differential load = $50 \Omega$  |       | -84   |     | dBc     |

| Vn    | Input voltage nois                        | e                  | $V_{CC} = \pm 5 \text{ V}, \pm 12 \text{ V}, \pm 15 \text{ V},$ | f = 100 kHz                      |       | 3.2   |     | nV/√Hz  |

|       | Input current                             | +Input             |                                                                 |                                  | 1.5   |       |     | - A 6/I |

| In    | noise                                     | -Input             | $V_{CC} = \pm 5 \text{ V}, \pm 12 \text{ V}, \pm 15 \text{ V},$ | T = 100 KHZ                      | 10    |       |     | pA/√Hz  |

|       | Createlle                                 |                    | $f = 1 \text{ MHz}, V_{O(PP)} = 2 \text{ V},$                   | R <sub>L</sub> = 100 Ω           |       | -65   |     | dBc     |

|       | Crosstalk                                 |                    | $V_{CC} = \pm 5 \text{ V}, \pm 12 \text{ V}, \pm 15 \text{ V}$  | R <sub>L</sub> = 25 Ω            |       | -60   |     | dBc     |

| OUTPU | UT CHARACTER                              | ISTICS             |                                                                 |                                  |       |       |     |         |

|       |                                           | VCC = ±5 V         | V 15 V                                                          | R <sub>L</sub> = 100 Ω           | ±3.9  | ±4.1  |     | V       |

|       |                                           |                    | $VCC = \pm 5 V$                                                 | R <sub>L</sub> = 25 Ω            | ±3.7  | ±3.9  |     |         |

| \/-   | Cinala andadau                            | mutualta aa ausina | V 140 V                                                         | R <sub>L</sub> = 100 Ω           | ±10.8 | ±11.0 |     | V       |

| VO    | Single-ended ou                           | tput voltage swing | $V_{CC} = \pm 12 \text{ V}$                                     | $R_L = 25 \Omega$                | ±10.2 | ±10.6 |     | V       |

|       |                                           |                    | Vaa - +15 V                                                     | R <sub>L</sub> = 100 Ω           | ±13.6 | ±13.9 |     | V       |

|       |                                           |                    | V <sub>CC</sub> = ±15 V                                         | $R_L = 25 \Omega$                | ±12.9 | ±13.4 |     | V       |

|       |                                           |                    | $R_L = 5 \Omega$                                                | V <sub>CC</sub> = ±5 V           | ±350  | ±400  |     |         |

| lo    | Output current (1                         | )                  | R <sub>I</sub> = 10 Ω                                           | V <sub>CC</sub> = ±12 V          | ±450  | ±600  |     | mA      |

|       |                                           |                    | KL = 10 22                                                      | $V_{CC} = \pm 15 \text{ V}$      | ±450  | ±600  |     |         |

| I(SC) | Short-circuit curre                       | ent (1)            | R <sub>L</sub> = 1 Ω                                            | V <sub>CC</sub> = ±12 V          |       | 1000  |     | mA      |

|       | Output resistance                         | )                  | Open-loop                                                       |                                  |       | 6     |     | Ω       |

|       | Output resistance                         | -terminate mode    | f = 1 MHz,                                                      | Gain = +10                       |       | 0.05  |     | Ω       |

|       | Output resistance                         | -shutdown mode     | f = 1 MHz,                                                      | Open-loop                        |       | 8.5   |     | kΩ      |

<sup>(1)</sup> A heatsink is rsequired to keep the junction temperature below absoulte maximum rating when an output is heavily loaded or shorted. See Absolute Maximum Ratings section for more information.

# **ELECTRICAL CHARACTERISTICS (continued)**

over recommended operating free-air temperature range,  $T_A = 25^{\circ}C$ ,  $V_{CC} = \pm 12 \text{ V}$ ,  $R_F = 2 \text{ k}\Omega$ , Gain = +5,  $I_{ADJ} = Bias1 = Bias2 = 0 \text{ V}$ ,  $R_L = 50 \Omega$  (unless otherwise noted)

| POWE            | R SUPPLY                                                                      |                                                |                             |     |      |         |      |  |

|-----------------|-------------------------------------------------------------------------------|------------------------------------------------|-----------------------------|-----|------|---------|------|--|

|                 | PARAMETER                                                                     | TEST                                           | CONDITIONS                  | MIN | TYP  | MAX     | UNIT |  |

| Voc             | Operatingrange                                                                | Dual supply                                    | Dual supply                 |     | ±12  | ±16.5   | V    |  |

| VCC             | Operating range                                                               | Single supply                                  |                             | 9.0 | 24   | 33      | V    |  |

|                 |                                                                               | Vcc = ± 5 V                                    | T <sub>A</sub> = 25°C       |     | 8    | 9       | mA   |  |

|                 | (4)                                                                           | ∧CC = ∓ 2 ∧                                    | T <sub>A</sub> = full range |     |      | 10      | IIIA |  |

|                 | Quiescent current (each driver)(1) Full-bias mode (Bias-1 = 0, Bias-2 = 0)    | V <sub>CC</sub> = ± 12 V                       | T <sub>A</sub> = 25°C       |     | 11   | 12      | mA   |  |

|                 |                                                                               |                                                | T <sub>A</sub> = full range |     |      | 12.5    |      |  |

| I <sub>CC</sub> |                                                                               | Voo - + 15 V                                   | T <sub>A</sub> = 25°C       |     | 11.5 | 12.5 mA | A    |  |

|                 |                                                                               | $V_{CC} = \pm 15 \text{ V}$                    | T <sub>A</sub> = full range |     |      | 13      | mA   |  |

|                 |                                                                               | Mid; Bias-1 = 1, Bias-                         | -2 = 0                      |     | 7.5  | 8.5     |      |  |

|                 | Quiescent current (each driver) Variable bias modes, V <sub>CC</sub> = ± 12 V | Low; Bias-1 = 0, Bias-                         | -2 = 1                      |     | 4    | 5       | mA   |  |

|                 | variable bias modes, vCC = ± 12 v                                             | Shutdown; Bias-1 = 1                           | , Bias-2 = 1                |     | 0.25 | 0.9     |      |  |

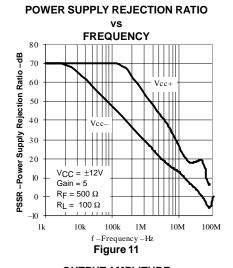

|                 |                                                                               | $V_{CC} = \pm 5 V$ ,                           | T <sub>A</sub> = 25°C       | -63 | -69  |         |      |  |

| DCDD            | Power supply rejection ratio                                                  | $\Delta V_{CC} = \pm 0.5 V$                    | T <sub>A</sub> = full range | -60 |      |         | V    |  |

| PSRR            | $(\Delta V_{CC(x)} = \pm 1 \text{ V})$                                        | $V_{CC} = \pm 12 \text{ V}, \pm 15 \text{ V},$ | T <sub>A</sub> = 25°C       | -64 | -70  |         | ¬ v  |  |

|                 |                                                                               | $\Delta V_{CC} = \pm 1 \text{ V}$              | T <sub>A</sub> = full range | -61 |      |         |      |  |

<sup>(1)</sup>  $_{0.5}\,\mathrm{mA}$  flows from  $\mathrm{V}_{CC+}$  to GND for internal logic control bias.

| DYNAMIC PERFORMANCE |                                           |                                       |                                |          |     |     |      |  |

|---------------------|-------------------------------------------|---------------------------------------|--------------------------------|----------|-----|-----|------|--|

|                     | PARAMETER                                 | TES                                   | TCONDITIONS                    | MIN      | TYP | MAX | UNIT |  |

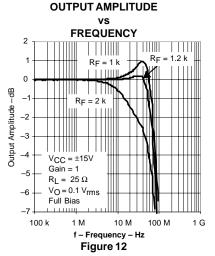

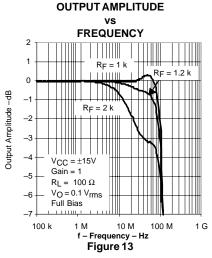

|                     |                                           |                                       | Gain = +1, RF = 1.2 k $\Omega$ |          | 100 |     |      |  |

|                     |                                           | D: 400.0                              | Gain = +2, RF = 1 k $\Omega$   |          | 80  |     |      |  |

|                     |                                           | $R_L = 100 \Omega$                    | Gain = +5, RF = 1 k $\Omega$   | 35<br>20 |     | MHz |      |  |

| D) 47               | Single-endedsmall-signalbandwidth         |                                       | Gain = +10, RF = 1 k $\Omega$  |          |     |     |      |  |

| BW                  | $(-3 \text{ dB}), V_0 = 0.1 \text{ Vrms}$ |                                       | Gain = +1, RF = $1.5k \Omega$  |          | 65  |     |      |  |

|                     |                                           | D 05.0                                | Gain = +2, RF = 1 k $\Omega$   |          | 60  |     |      |  |

|                     |                                           | $R_L = 25 \Omega$                     | Gain = +5, RF = 1 k $\Omega$   |          | 40  |     | MHz  |  |

|                     |                                           |                                       | Gain = +10, RF = 1 k $\Omega$  |          | 22  |     |      |  |

| SR                  | Single-endedslew-rate <sup>(1)</sup>      | V <sub>O</sub> = 10 V <sub>PP</sub> . | Gain =+5                       |          | 450 |     | V/µs |  |

<sup>(2)</sup> Slew-rate is defined from the 25% to the 75% output levels

| DC PE                | RFORMANCE                       |                                                                |                             |     |     |     |       |

|----------------------|---------------------------------|----------------------------------------------------------------|-----------------------------|-----|-----|-----|-------|

|                      | PARAMETER                       | TEST CONDIT                                                    | TIONS                       | MIN | TYP | MAX | UNIT  |

|                      | Innut effect voltage            | and the same                                                   |                             |     | 1   | 20  |       |

|                      | Input offset voltage            |                                                                | T <sub>A</sub> = full range |     |     | 25  | mV    |

| $V_{OS}$             | VOS Differential offset voltage | V <sub>CC</sub> = ± 5 V, ±12 V, ±15 V                          | T <sub>A</sub> = 25°C       |     | 0.5 | 10  | IIIV  |

|                      |                                 |                                                                | T <sub>A</sub> = full range |     |     | 15  |       |

|                      | Offset drift                    |                                                                | T <sub>A</sub> = full range |     | 50  |     | μV/°C |

|                      | Input bigg ourrent              |                                                                | T <sub>A</sub> = 25°C       |     | 8   | 15  |       |

|                      | -Input bias current             | Vac 15V 142V 145V                                              | T <sub>A</sub> = full range |     |     | 20  |       |

| $I_{IB}$             | . Input bing gurrant            | $V_{CC} = \pm 5 \text{ V}, \pm 12 \text{ V}, \pm 15 \text{ V}$ | T <sub>A</sub> = 25°C       |     | 8   | 15  | μΑ    |

| + Input bias current |                                 |                                                                | T <sub>A</sub> = full range |     |     | 20  |       |

| Z <sub>OL</sub>      | Open loop transimpedance        | $R_L = 1 \text{ k}\Omega, V_{CC} = \pm 12 \text{ V}, \pm$      | 15 V,                       | 450 | 900 |     | kΩ    |

# **ELECTRICAL CHARACTERISTICS (CONTINUED)**

over recommended operating free-air temperature range,  $T_A = 25^{\circ}C$ ,  $V_{CC} = \pm 12$  V,  $R_F = 2$  k $\Omega$ , Gain = +5,  $I_{ADJ} = Bias1 = Bias2 = 0$  V,  $R_L = 50$   $\Omega$  (unless otherwise noted)

| INPUT          | CHARACTERISTICS                       |                                                |                                    |         |                       |      |      |  |   |

|----------------|---------------------------------------|------------------------------------------------|------------------------------------|---------|-----------------------|------|------|--|---|

|                | PARAMETER                             | TEST C                                         | ONDITIONS                          | MIN     | TYP                   | MAX  | UNIT |  |   |

|                |                                       | V 15.V                                         | T <sub>A</sub> = 25°C              | ±2.7    | ±3.0                  | . V  | V    |  |   |

|                |                                       | $V_{CC} = \pm 5 \text{ V}$                     | T <sub>A</sub> = full range        | ±2.6    |                       |      | V    |  |   |

| .,             | CR Input common-mode voltage range(1) | 1                                              | Input common mode veltore range(1) | V 140 V | T <sub>A</sub> = 25°C | ±9.5 | ±9.8 |  | W |

| $V_{ICR}$      |                                       | $V_{CC} = \pm 12 \text{ V}$                    | T <sub>A</sub> = full range        | ±9.3    |                       |      | V    |  |   |

|                |                                       | V 145.V                                        | T <sub>A</sub> = 25°C              | ±12.4   | ±12.7                 |      | V    |  |   |

|                |                                       | $V_{CC} = \pm 15 \text{ V}$                    | T <sub>A</sub> = full range        | ±12.1   |                       |      | V    |  |   |

| 01400          | Common mode valenting vation          | V                                              | T <sub>A</sub> = 25°C              | 62      | 72                    |      | 5    |  |   |

| CMRR           | Common-mode rejection ratio           | $V_{CC(L)} = \pm 5 \text{ V}, \pm 6 \text{ V}$ | T <sub>A</sub> = full range        | 58      |                       |      | dB   |  |   |

| _              | Innut reciptores                      | + Input                                        |                                    |         | 800                   |      | kΩ   |  |   |

| R <sub>I</sub> | Inputresistance                       | - Input                                        |                                    |         | 30                    |      | Ω    |  |   |

| C <sub>I</sub> | Input capacitance                     |                                                |                                    |         | 1.7                   |      | pF   |  |   |

| LOCA | LOCAL CONTROL CHARACTERISTICS                     |                                    |     |     |     |      |  |  |

|------|---------------------------------------------------|------------------------------------|-----|-----|-----|------|--|--|

|      | PARAMETER                                         | TEST CONDITIONS                    | MIN | TYP | MAX | UNIT |  |  |

| VIH  | Bias pin voltage for logic 1                      | Relative to GND pin voltage        | 2.0 |     |     | V    |  |  |

| VIL  | Bias pin voltage for logic 0                      | Relative to GND pin voltage        |     |     | 0.8 | V    |  |  |

| lіН  | Bias pin current for logic 1                      | V <sub>IH</sub> = 3.3 V, GND = 0 V |     | 4   | 30  | μΑ   |  |  |

| IIL  | Bias pin current for logic 0                      | V <sub>IL</sub> = 0.5 V, GND = 0 V |     | 1   | 10  | μΑ   |  |  |

|      | Transition time—logic 0 to logic 1(1)             |                                    |     | 1   |     | μs   |  |  |

|      | Transition time—logic 1 to logic 0 <sup>(1)</sup> |                                    |     | 1   |     | μs   |  |  |

(1) Transition time is defined as the time from when the logic signal is applied to the time when the supply current has reached half its final value.

| LOGIC ' | LOGIC TABLE |                |                                                                                     |  |  |  |  |  |

|---------|-------------|----------------|-------------------------------------------------------------------------------------|--|--|--|--|--|

| BIAS-1  | BIAS-2      | FUNCTION       | DESCRIPTION                                                                         |  |  |  |  |  |

| 0       | 0           | Full bias mode | Amplifiers ON with lowest distortion possible (default state)                       |  |  |  |  |  |

| 1       | 0           | Mid bias mode  | Amplifiers ON with power savings with a reduction in distortion performance         |  |  |  |  |  |

| 0       | 1           | Low bias mode  | Amplifiers ON with enhanced power savings and a reduction of distortion performance |  |  |  |  |  |

| 1       | 1           | Shutdown mode  | Amplifiers OFF and output has high impedance                                        |  |  |  |  |  |

NOTE: The default state for all logic pins is a logic zero (0).

Figure 1. Single-Supply ADSL CO Line Driver Circuit Utilizing Active Impedance (SF = 4)

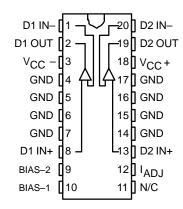

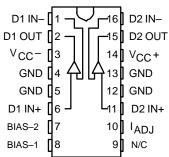

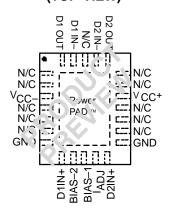

## **PIN ASSIGNMENTS**

#### **THS6182**

TSSOP PowerPAD™ (PWP) and SOIC-20 (DW) PACKAGE<sup>(1)</sup> (TOP VIEW)

THS6182 SOIC-16 (D) PACKAGE (TOP VIEW)

(1) Product preview

THS6182 Leadless 24-pin PowerPAD™ 5mm X 4mm (RGU) PACKAGE (TOP VIEW)

# **TYPICAL CHARACTERISTICS**

**Table of Graphs**

|                               |                        | FIGURE  |

|-------------------------------|------------------------|---------|

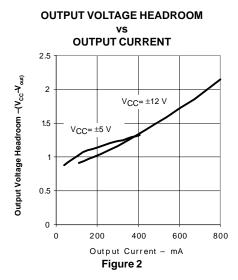

| Output voltage headroom       | vs Output current      | 2       |

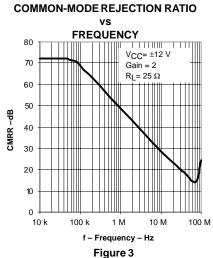

| Common-mode rejection ratio   | vs Frequency           | 3       |

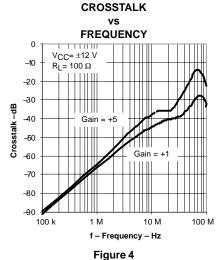

| Crosstalk                     | vs Frequency           | 4       |

| Total quiescent current       |                        | 5       |

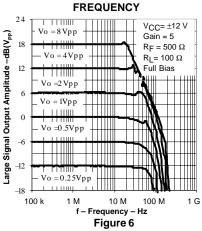

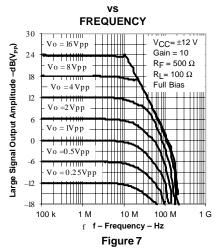

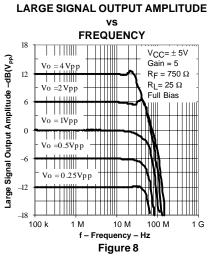

| Large signal output amplitude | vs Frequency           | 6-8     |

| Voltage and current noise     | vs Frequency           | 9       |

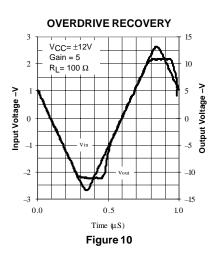

| Overdrive recovery            |                        | 10      |

| Power supply rejection ratio  | vs Frequency           | 11      |

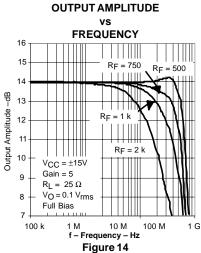

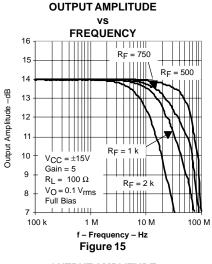

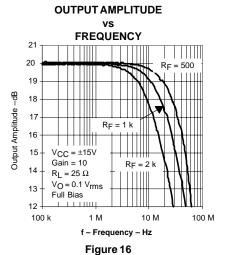

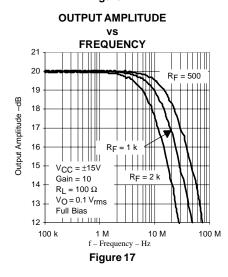

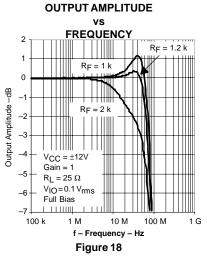

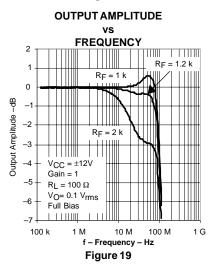

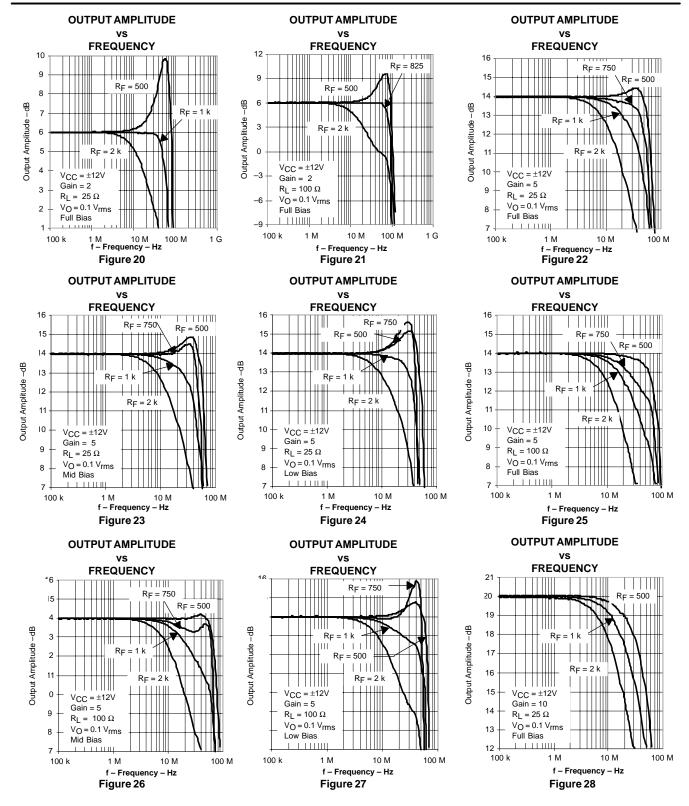

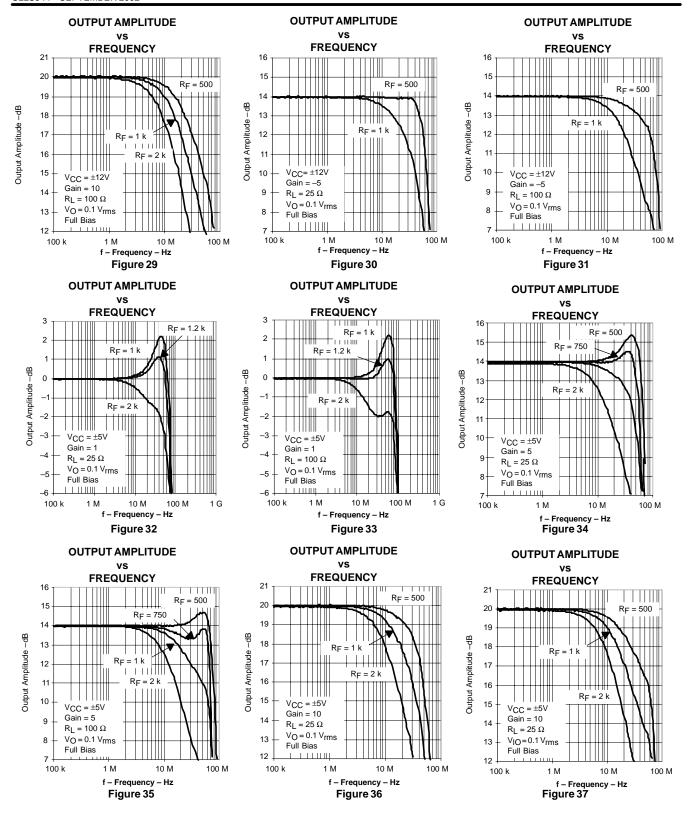

| Outputamplitude               | vs Frequency           | 12 – 37 |

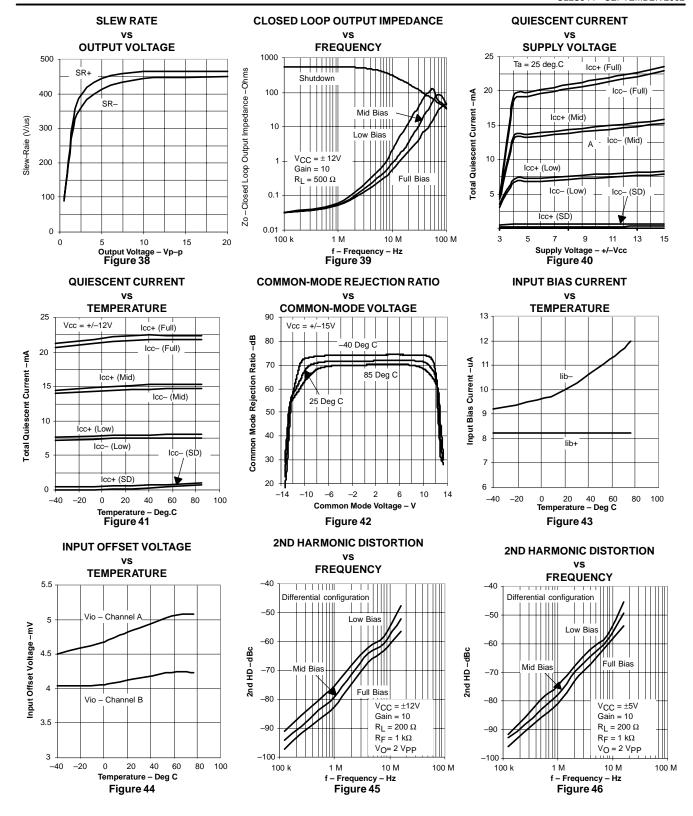

| Slew rate                     | vs Output voltage      | 38      |

| Closed-loop output impedance  | vs Frequency           | 39      |

| Quiescent current             | vs Supply voltage      | 40      |

| Quiescent current             | vs Temperature         | 41      |

| Common-mode rejection ratio   | vs Common-mode voltage | 42      |

| Input bias current            | vs Temperature         | 43      |

| Input offset voltage          | vs Temperature         | 44      |

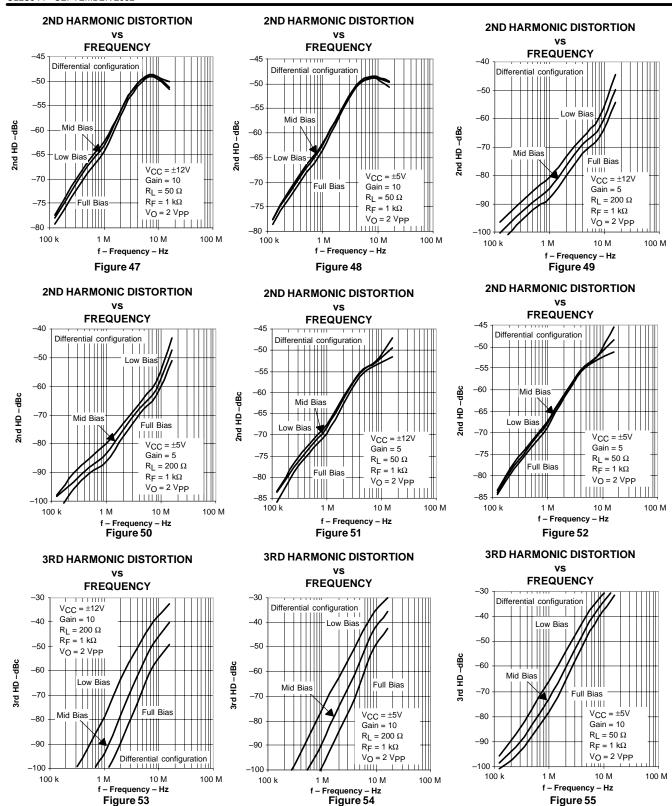

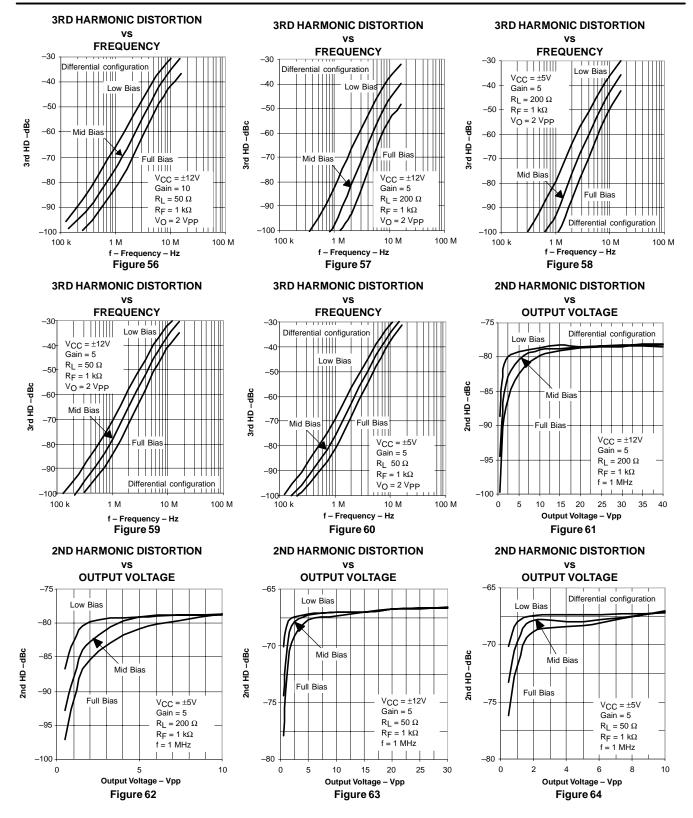

| 2nd Harmonic distribution     | vs Frequency           | 45 – 52 |

| 3rd Harmonic distribution     | vs Frequency           | 53 – 60 |

| 2nd Harmonic distribution     | vs Output voltage      | 61 – 64 |

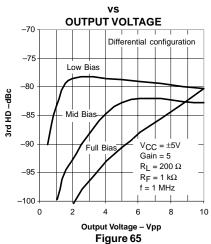

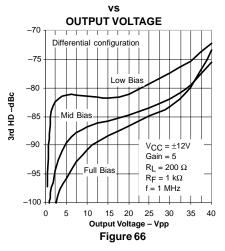

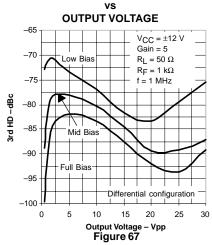

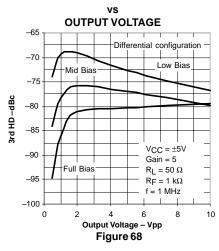

| 3rd Harmonic distribution     | vs Output voltage      | 65 – 68 |

#### TYPICAL CHARACTERISTICS

25 1111111 **§** 20 15

Current (

Quiescent

10

0

**TOTAL QIESCENT CURRENT** V<sub>CC</sub>= ±12 V Mid Bias Mode Low Bias Mode 0.01 0.1 100 Rset to  $GND-k\Omega$ Figure 5

LARGE SIGNAL OUTPUT AMPLITUDE vs

LARGE SIGNAL OUTPUT AMPLITUDE

#### 3RD HARMONIC DISTORTION

#### **3RD HARMONIC DISTORTION**

# 3RD HARMONIC DISTORTION

#### 3RD HARMONIC DISTORTION

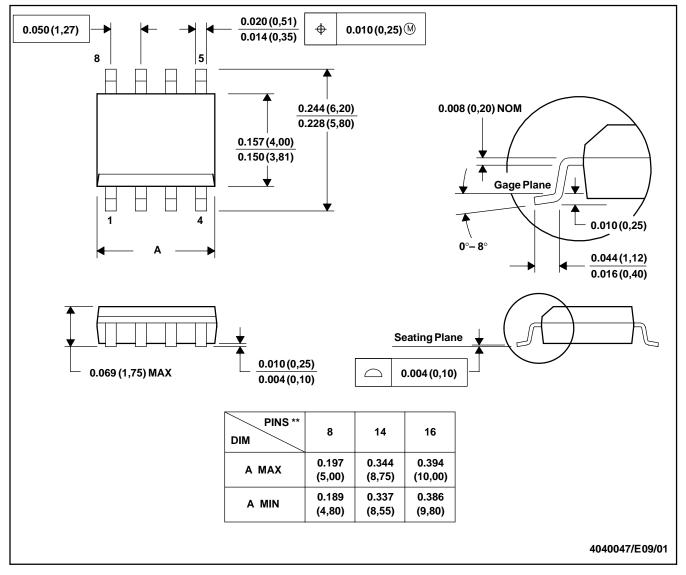

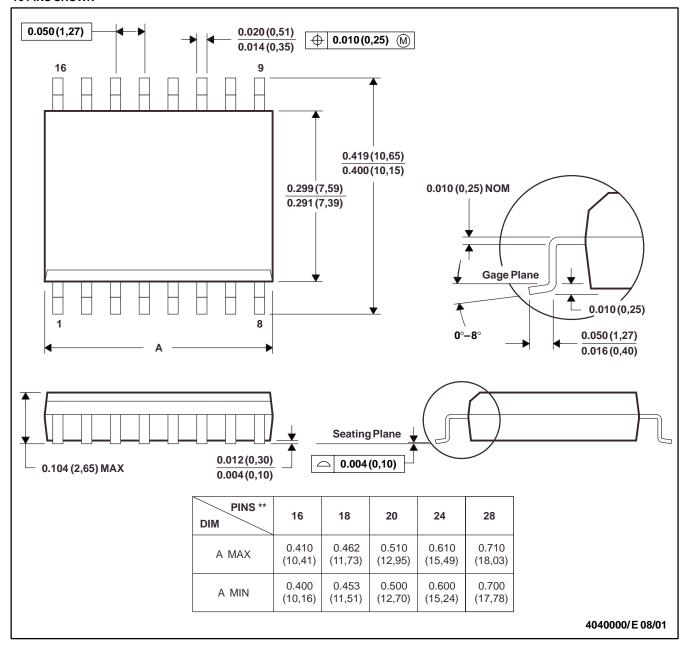

# D (R-PDSO-G\*\*)

# 8 PINS SHOWN

## PLASTIC SMALL-OUTLINE PACKAGE

- NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion, not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-012

# DW (R-PDSO-G\*\*)

#### 16 PINS SHOWN

# PLASTIC SMALL-OUTLINE PACKAGE

- NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-013

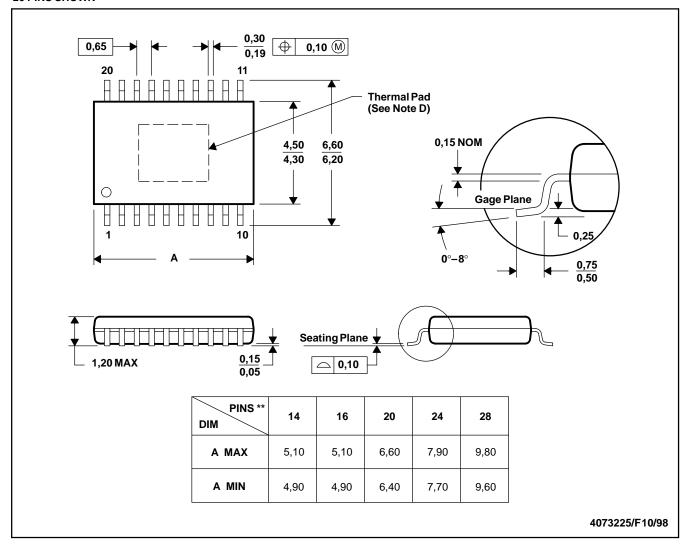

# PWP (R-PDSO-G\*\*)

## **PowerPAD™ PLASTIC SMALL-OUTLINE**

# 20 PINS SHOWN

- NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusions.

- D. The package thermal performance may be enhanced by bonding the thermal pad to an external thermal plane. This pad is electrically and thermally connected to the backside of the die and possibly selected leads.

- E. Falls within JEDEC MO-153

# RGU (R-PQFP-N24) PLASTIC QUAD FLATPACK 5,15 4,85 <u>4,15</u> 3,85 **PIN 1 INDEX AREA TOP AND BOTTOM** 0,80 0,20 REF. **SEATING PLANE** 0,08 0,05 0,00 3,25 MAX 0,50 $24X \frac{0,75}{0,35}$ 6 24 2,25 MAX 12 **EXPOSED THERMAL DIE PAD** (SEE NOTE D) 13 24X 0,30 0,18 2,50 $\Phi$ Ø 0,10 M 4203496/A01/02

- NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Quad Flatpack, No-leads (QFN) package configuration.

- D. The package thermal performance may be enhanced by bonding the thermal die pad to an external thermal plane.

- E. Falls within JEDEC MO-220.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated